INCOTERM®

## SPD<sup>®</sup> Symbolic Assembly Language Reference Manual

Växjö Data System AB

This manual, assembled in March 1976 by VÄXJÖ DATA SYSTEM AB, SWEDEN, consists of

- 1. SPD Symbolic Assembly Language Reference Manual MS-7215.0

- 2. SPD Relocatable Assembly System (75-06-24)

83

n

.

•

# SPD SYMBOLIC ASSEMBLY LANGUAGE REFERENCE MANUAL

ORDER NUMBER: MS-7215.0

DATE: AUGUST, 1975

#### PREFACE

This manual supercedes the SPD 10/20 Assembler Manual, MS-7113, and is the only assembler manual required for the SPD 10/20, SPD 10/24, SPD 10/25, and SPD 20/20.

It should be noted that the SPD 10/24 was especially designed for overseas customers. This system is built and sold solely by a licensee, TRANSAC.

The SPD 10/24 is not available within the U.S.A.

Copyright © 1974 by INCOTERM Corporation Copyright © 1975 by INCOTERM Corporation

The information in this manual is presented for informational purposes and is not intended or licensed to be used for the construction of equipment. The information is believed to be accurate, but no responsibility is assumed for inaccuracies or for consequences of using the information.

Further, INCOTERM Corporation makes no representation that use of the information in this manual will not infringe on existing or future patent rights of INCOTERM or of others.

#### Table of Contents

|                                             | Page           |

|---------------------------------------------|----------------|

| SECTION I INTRODUCTION                      | 1 - 1          |

| General                                     | 1 - I<br>I - 2 |

| Notation                                    | 1-2            |

| SECTION II ASSEMBLY SOURCE FORMAT           | 2 - 1          |

| General                                     | 2-1            |

| Character Set                               | 2-1            |

| Operation Format                            | 2-2            |

| Comment Lines                               | 2-3            |

| Title Lines                                 | 2-3            |

|                                             |                |

| SECTION III EXPRESSIONS                     | 3-1            |

| General                                     | 3-1            |

| Operands                                    | 3-1            |

| Symbols                                     | 3-1            |

| Constants                                   | 3-2            |

| Special Symbols                             | 3 – 3          |

| Operators                                   | 3-4            |

| Addition                                    | 3-4            |

| Compare Equal                               | 3-4            |

| Compare Greater Than or Equal               | 3-4            |

| Compare Greater Than                        | 3-5            |

| Compare Less Than or Equal                  | 3 - 5          |

| Compare Less Than                           | 3 - 5          |

| Compare Not Equal                           | 3-6            |

| Division                                    | 3-6            |

| Left Shift                                  | 3-7            |

| Logical And                                 | 3-7            |

| Logical Exclusive Or                        | 3 – 7          |

| Logical Or                                  | 3 - 8          |

| Multiplication                              | 3-8            |

| Right Shift                                 | 3-8            |

| Subtraction                                 | 3-9            |

| Operator Precedence and Order of Operations | 3-10           |

| Omission of Zero Operands                   | 3-11           |

| Examples                                    | 3-11           |

### Table of Contents (contid)

|                                                       | Page  |

|-------------------------------------------------------|-------|

| SECTION IV MACHINE OPERATIONS                         | 4-1   |

| General                                               | 4-1   |

| Word Class Instructions                               | 4-1   |

| Byte Class Instructions                               | 4 - 3 |

| Indexing                                              | 4-4   |

| Operate Class Instructions                            | 4-5   |

| Immediate Class Instructions                          | 4-6   |

| Jump on Condition Instructions                        | 4-7   |

| Compare and Jump Instructions                         | 4-8   |

| Input-Output Instructions                             | 4-9   |

| Extended Mnemonics                                    | 4-10  |

| SECTION V ASSEMBLER PSEUDO-OPERATIONS                 | 5 – 1 |

| General                                               | 5-1   |

| ADDR Generate two-byte data                           | 5-1   |

| ALGN Align to word boundary                           | 5-2   |

| BOOT Set boot mode                                    | 5 - 3 |

| BSS Reserve storage                                   | 5-4   |

| BSZ Generate zeros                                    | 5 - 5 |

| BYTE Generate byte data                               | 5-6   |

| CNFG Specify configuration mode                       | 5 - 7 |

| DAC Generate address constant                         | 5-9   |

| DUP Duplicate source line                             | 5-10  |

| EJECT Eject assembly listing to new page              | 5-11  |

| END End assembly                                      | 5-11  |

| ENDF End conditional assembly range                   | 5-11  |

| EQU Equate symbol to value                            | 5-12  |

| ESEG End overlay segment                              | 5-13  |

| HEX Generate hexadecimal data                         | 5-13  |

| IF Start conditional assembly range                   | 5-14  |

| LBL Generate label data                               | 5-14  |

| LIF Control Listing of IF Ranges                      | 5-15  |

| LIST Control Listing Mode                             | 5-16  |

| LTXT Generate lower case text string                  | 5-17  |

| LTX8 Generate lower case text string with 8th bit set | 5-17  |

| NOBJ Turn off object output mode                      | 5-18  |

| OBJ Turn on object output mode                        | 5-19  |

| ORG Set assembly origin                               | 5-20  |

| PAGE Set page depth                                   | 5-21  |

| SEG Start of overlay segment                          | 5-22  |

## Table of Contents (cont<sup>1</sup>d)

|                                              | Page    |

|----------------------------------------------|---------|

| SET Set symbol to value                      | 5-23    |

| SIZE Specify memory size                     | 5-24    |

| TEXT Generate text string                    | 5-26    |

| TXT8 Generate text string with 8th bit       | 5-27    |

| WORD Generate word data                      | 5-28    |

| XORG Set execution origin                    | 5 - 2.9 |

| XREF Set cross reference mode                | 5-20    |

| SECTION VI ADDRESSING RESTRICTIONS           | 6-1     |

| General                                      | 6-1     |

| CNFG 10 Addressing                           | 6-1     |

| CNFG 20 Addressing                           | 6-1     |

| CNFG 24 Addressing                           | 6-2     |

| CNFG 25 Addressing                           | 6-2     |

| CNFG 0 Addressing                            | 6-3     |

| Size 0                                       | 6-4     |

| Effect of Restrictions                       | 6-4     |

| External Memory                              | 6-5     |

| Loader Considerations                        | 6-5     |

| Literal Pool                                 | 6-5     |

| BSS Operations                               | 6-6     |

| SECTION VII FORMAT OF PRINTED LISTING        | 7 - 1   |

| General                                      | 7-1     |

| Title Lines                                  | 7-1     |

| Generated Machine Instructions               | 7-2     |

| Comment Lines                                | 7-2     |

| Pseudo-Operations                            | 7-3     |

| Update/Deletion Flags                        | 7-5     |

| Literal Table                                | 7 - 5   |

| Cross Reference Listing                      | 7-6     |

| Error Flags                                  | 7-6     |

| APPENDIX A ASSEMBLER SYNTAX, QUICK REFERENCE | A-1     |

| Expression Operands                          | A-1     |

| Expression Operators                         | A-2     |

| Title Lines                                  | A - 2   |

| Operation Formats                            | A - 3   |

| Key to Symbols                               | A-6     |

## Table of Contents (cont'd)

|                                                                                                                                                                                                    | Page                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| APPENDIX B ERROR FLAGS, QUICK REFERENCE                                                                                                                                                            | B-1                                                                       |

| APPENDIX C COMPATIBILITY WITH PREVIOUS VERSIONS                                                                                                                                                    | C-1                                                                       |

| APPENDIX D SPD/DOS ASSEMBLE OPERATING NOTES                                                                                                                                                        | D-1                                                                       |

| Source Input Format Object Output Format Operating Procedures Option Letters File Allocation Definition of Standard Symbols Display Messages Examples Listing Format Format of Listing on Diskette | D-1<br>D-8<br>D-8<br>D-11<br>D-12<br>D-13<br>D-14<br>D-14<br>D-16<br>D-19 |

| APPENDIX E LIST OF USEFUL PUBLICATIONS                                                                                                                                                             | E-1                                                                       |

#### List of Illustrations

|             |                                                                                                   | Page |

|-------------|---------------------------------------------------------------------------------------------------|------|

| Figure 2-1. | Sample Coding Form                                                                                | 2-5  |

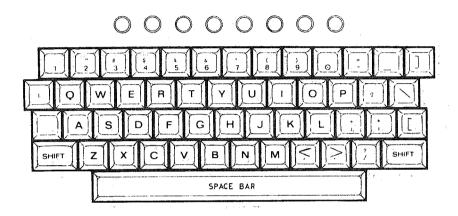

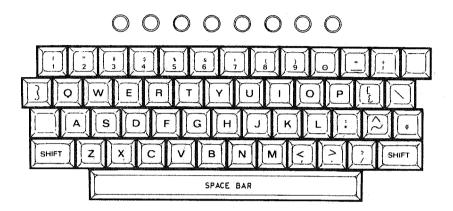

| Figure D-1. | Keyboard Layout for Preparation of Input to SPD/DOS<br>ASSEMBLE (10/20 Upper Case Only Keyboard)  | D-3  |

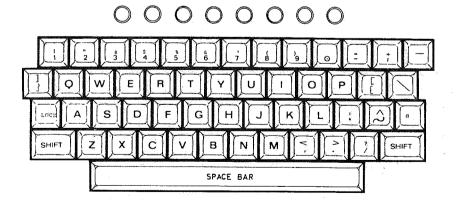

| Figure D-2. | Keyboard Layout for Preparation of Input to SPD/DOS<br>ASSEMBLE (10/20 Upper/Lower Case Keyboard) | D-3  |

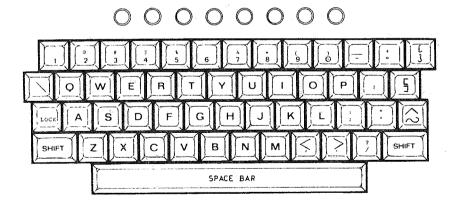

| Figure D-3. | Keyboard Layout for Preparation of Input to SPD/DOS<br>ASSEMBLE (20/20 Upper Case Only Keyboard)  | D-4  |

| Figure D-4. | Keyboard Layout for Preparation of Input to SPD/DOS<br>ASSEMBLE (20/20 Upper/Lower Case Keyboard) | D-4  |

#### List of Tables

|           |                                                | rage |

|-----------|------------------------------------------------|------|

| Table D-1 | Card Punch Codes for Input to SPD/DOS ASSEMBLE | D-5  |

| Table D-2 | ASSEMBLE Work File Capacity                    | D-10 |

#### SECTION I

#### INTRODUCTION

#### GENERAL

The SPD symbolic assembly language is designed to aid in the preparation of programs for execution on any of the following INCOTERM processing units:

SPD 10/20 SPD 10/24 SPD 10/25 SPD 20/20

The assembler relieves the programmer of many of the burdensome tasks which would be associated with programming in machine language while permitting full access to the capabilities of the processing unit.

Mnemonic operation codes are provided for the various machine instructions and the assembler outputs the appropriate bit patterns. A location counter maintained by the assembler allows symbols to be defined as labels for instructions. These labels may be referenced by other instructions to obtain the corresponding location values, thus relieving the programmer of the task of assigning storage locations. A separately maintained load counter controls the final load location. The load counter's value is normally the same as that of the location counter, but the values may be separated to allow assembly of code at one location for eventual execution at some other location.

For locations equipped with an SPD D-250 Dual Diskette and printer, the SPD DOS Assembler is available (See also Appendix D).

This assembler translates SPD assembly language into machine language. It is basically a utility program which runs under control of the SPD/DOS system on an SPD 10/20, 10/24, 10/25, or 20/20. The output is a DOS loadable object file on disk.

The DOS COPY utility can be used to obtain object copies on other media.

#### Notation

A word surrounded by angle brackets, e.g. < label> represents a generic type of operand. The ensuing text describes the allowed possibilities for the operand.

A section of syntax enclosed in square brackets, e.g. [code], indicates an optional part of the construction which may be omitted. The text explains the effect of including or excluding such components.

#### SECTION II

#### ASSEMBLY SOURCE FORMAT

#### GENERAL

An SPD assembly language program consists of a series of lines each containing a single statement. The length of these lines is 1-80 characters, although for convenient use of the SPD/DOS EDIT facility, it may be desirable to restrict the length of all lines to 64 characters for compatibility with the SPD 10/20 screen format.

#### CHARACTER SET

The character set used is the upper case ASCII set (corresponding to codes X'20' - X'5F'). Any of the 64 characters of this set may appear in character and text constants, but only the following have specific syntactic use:

| \$    | dollar            |

|-------|-------------------|

| &     | ampersand         |

| 1     | quote             |

| · (   | left parenthesis  |

| )     | right parenthesis |

| *     | asterisk          |

| #     | hash              |

| +     | plus              |

| ,     | comma             |

|       | minus             |

| •     | period            |

| 1     | slash             |

| 0-9   | digits            |

| =     | equal             |

| @     | at                |

| A - Z | letters           |

#### OPERATION FORMAT

The basic operation format is shown below:

label opcode operands comments

The label, if present, starts in column 1. The first character of the label must be a letter and the remaining characters are from the set 0-9 (digits),

A-Z (letters), \$ (dollar) and & (ampersand). The label length is from 1-8 characters. If no label is present, column one must be blank.

The opcode is either a machine operation or pseudo-operation mnemonic. It normally starts in column 10 and it must be separated by at least one blank from the label or, if there is no label, must start in or after column 2. In the event that indirect addressing is permitted, it is specified by immediately following the opcode with \* (asterisk).

The operands field, if present, consists of one or more operands separated by commas. The number of operands depends on the opcode as described in Section IV. No blanks may appear in the operands except within character or text constants, thus a blank is used as a terminator. The operands field must be separated by at least one and not more than nine blanks from the opcode field. In the case where indirect addressing is specified, no separating blanks are required, but they may be present.

The comments field, which is optional, consists of any sequence of ASCII characters including blanks. The first character of this field must be separated from the operands field by at least one blank. In the case where there is no operands field, the comment field must be separated from the opcode field by at least ten blanks.

Although the above rules allow "free format" input, standard INCOTERM coding conventions require the following format to be followed where possible. See Figure 2-1 for a sample coding form.

cols 1-8 label

cols 10-15 opcode

cols 16-29 operands

cols 30-n comment

#### COMMENT LINES

Any assembly source line which contains \* (asterisk) or # (hash) in column one is treated as a comment by the assembler. It will be printed if the listing mode is specified (see LIST, LIF pseudo-operations) but will otherwise be ignored. It is also possible to selectively list only the comments starting with \*.

#### TITLE LINES

The printed output has two title lines of forty characters each. The main title is initially set from the source file label, or if no such label is

available, from columns 2-41 of the initial source line.

Subsequently, this main title can be modified by the occurrence of one or more title modification lines in the source program with the following format:

cols 1 & (ampersand)

cols 2-41 title modification data

Blanks in columns 2-41 have no effect. Non-blank characters replace the corresponding character positions of the main title. These title modification lines are interpreted in order in pass one of the assembly and the resulting title used to label the object output and to head the printed output throughout pass two (i.e. title modification lines have no effect in pass two).

Title modification lines are not recognized if deleted by IF-ENDF or DUP.

Thus conditional assembly operations may be used to select an appropriate main title.

8

PAGE\_

Figure 2-1. Sample Coding Form

The sub-title printed on the listing is initially blank. It may be set by a sub-title line in the source with the following format:

col 1 ' (quote)

cols 2-41 sub-title data (40 ASCII characters)

The occurrence of such a line implies an automatic page eject so that subsequent pages (up to the next sub-title line in the source) are printed with the correct sub-title. Sub-title lines are only effective if they occur in a listed section of code (see LIST, LIF pseudo-operations).

#### SECTION III

#### EXPRESSIONS

#### GENERAL

The power of a symbolic assembler lies in its ability to reference values in a symbolic manner. This is achieved by allowing expressions to be used wherever a value is required (e.g. operand location, I/O function code, immediate operand value).

Expressions may either be simple operands (e.g. constants or label references), or they may be calculations involving the use of operators.

It is important to understand that such calculations are performed entirely at assembly time and do not correspond to the execution of code at execution time.

#### OPERANDS

Operands may stand on their own as expressions or they may be joined together with operators to form complex expressions.

#### Symbols

Any symbol which has been given a value somewhere, by appearing in the label field of a suitable machine or pseudo-operation line, may be used as an operand. The value is the symbol value which is normally (i.e. except in the special cases of EQU, SET, SEG) the location counter value at the definition point.

The syntax of symbol references is the same as that previously described for labels. The length of symbols varies from 1-8 characters and the reference

must be identical to the definition.

Due to the two-pass nature of the assembler, labels may usually be referenced before they are defined. In certain pseudo-operations, such "forward" references are not permitted. These exceptions are noted in the pseudo-operation section.

#### Constants

Constant operands may be in any of the following formats:

- nnn... Decimal integer. The n's are decimal digits (0-9). Values larger than 65535 are interpreted modulo 65536.

- D'nnn...' An alternate form for a decimal integer. Used particularly in conjunction with repeat counts in ADDR, BYTE, WORD operands (see separate descriptions).

- B'bbbb...' Binary integer. The b's are binary digits (0 or 1). The integer may have one or more digits, the result being right justified. Only the low order 16-bits are retained.

- O'cc...' Octal integer. The c's are octal digits (0-7). The integer may have one or more digits. Numbers larger than O'177777' are interpreted modulo O'200000'.

- X'xxx...' Hexadecimal integer. The x's are hexadecimal digits (0-9, A-F). The number may have one or more digits. Only the low order four digits are retained, the result being right justified if fewer than four digits are given.

- Single character ASCII constant. a is any legal ASCII character except quote. The value of the operand is the corresponding ASCII code for the character. If a constant quote is required, it can be expressed in hexadecimal (i.e. X'27').

- Double character ASCII constant. a, b are any legal ASCII characters except quote. The value of the operand is 256\*

(ASCII code for a) + (ASCII code for b).

#### Special Symbols

Special symbols are predefined as follows and may be used as operands.

- \$ The current value of the location counter. This is always the value at the start of the referencing line before generating any code or otherwise interpreting the line.

- \$B A sixteen-bit value which can be set externally without affecting the source. The method of setting \$B depends on the assembler in use (see separate appendices on specific assemblers). The use of \$B allows one source program to assemble more than one version of a program by means of conditional assembly operations.

- \$C The location of the cursor register: X'0FFE' in CNFG 10 or CNFG 25 assembly, X'7FFE' in a CNFG 0, CNFG 24, or CNFG 20 assembly. \$C has the same value as \$X but \$C is preferred usage if the register is being used as a cursor register.

- Duplication count. When a line is duplicated by means of the DUP pseudo-operation, \$D has successive values of 1, 2, 3,...for duplications of the line. The value of \$D is zero in non-DUPed lines.

- \$L The current value of the load counter. This is always the value at the start of the referencing line before generating any code or otherwise interpreting the line.

- \$X The location of the index register: X'0FFE! in CNFG 10 or CNFG 25 assembly, X'7FFE! in CNFG 0, CNFG 20, or CNFG 24 assembly. \$X has the same value as \$C but \$X is preferred usage when the register is used as an index register.

- \*\* An alternate form of a constant zero operand. This form is conventionally used when the value is to be set at execution time (e.g. DAC \*\* for the entry point of a subroutine called by JSR.)

#### OPERATORS

Operators are written between two operands and perform a computational operation on the two operand values. The following paragraphs describe the available operators in alphabetical order.

#### Addition

The addition operator + adds its two operands as 16-bit unsigned quantities, ignoring overflow. This is equivalent to a twos-complement add if the operands are regarded as signed twos-complement values.

Examples:

$$X'8000' + X'8000' = 0$$

$$4+X'FFFF' = 3$$

$$X'4000'+X'4000' = X'8000'$$

#### Compare Equal

The compare equal operator .EQ. compares its two 16-bit operands and gives a result of one if the operands are identical and zero otherwise.

Examples:

$$X'FFFF'.EQ.X'FFFF' = 1$$

= 0

#### Compare Greater Than or Equal

The compare greater than or equal operator .GE. compares its two 16-bit operands as unsigned integers and gives a result of one if the left operand is greater than or equal to its right operand and zero otherwise.

Examples:

$$3.GE.3 = 1$$

$$X'FFFF'.GE.0 = 1$$

= 0

#### Compare Greater Than

The compare greater than operator .GT. compares its two 16-bit operands as unsigned integers and gives a result of one if the left operand is strictly greater than its right operand and zero otherwise.

Examples:

= 0

$$X'FFFF'.GT.0 = 1$$

= 0

#### Compare Less Than or Equal

The compare less than or equal operator. LE. compares its two 16-bit operands as unsigned integers and gives a result of one if the left operand is less than or equal to the right operand and zero otherwise.

Examples:

-- 1

$X^{\dagger}FFFF^{\dagger}$ , LE. 0 = 0

1. LE. 2

= 1

#### Compare Less Than

The compare less than operator .LT. compares its two 16-bit operands as unsigned integers and gives a result of one if the left operand is strictly less than the right operand and zero otherwise.

$$X'FFFF'.LT.0 = 0$$

#### Compare Not Equal

The compare not equal operator .NE. compares its two 16-bit operands and gives a result of zero if they are identical and one otherwise.

Examples:

$$X^{t}FFFF^{t}.NE.0 = 1$$

#### Division

The division operator / yields the quotient of the result of dividing the left operand by the right operand. Both operands are regarded as unsigned 16-bit operands and the result is truncated to an integer by dropping the fractional part. Division by zero is undefined and results in an error.

$$3/2 = 1$$

$$X'1234'/256 = X'0012'$$

$$X'FEDC'/256 = X'00FE'$$

$$1/X'FFFF'$$

= 0

$$2/0 = (error)$$

#### Left Shift

The left shift operator. LS. shifts its left operand to the left the number of bits indicated by the right operand. The shift is a logical end-off shift with zero bits entering on the right as required. The shift count must be in the range 0-15 inclusive.

Examples:

$$B^{\dagger}101010^{\dagger}$$

. LS. 2 =  $B^{\dagger}10101000^{\dagger}$

$$X'FF7F'$$

, LS. 4 =  $X'F7F0'$

#### Logical And

The logical and operator .AND. performs a 16-bit bit-wise "and" operation on its two operands.

Examples:

$$^{1}34^{1}$$

. AND.  $X^{1}0F0F^{1} = X^{1}0304^{1}$

$$B'0011'$$

. AND.  $0101' = B'0001'$

#### Logical Exclusive Or

The logical exclusive or operator .XOR. performs a 16-bit bit-wise "exclusive or" operation on its two operands.

$$X'41'$$

, XOR,  $X'41'$  = 0

$$B'0011'$$

, XOR,  $B'0101' = B'0110'$

$$X'FFF'$$

,  $XOR$ ,  $X'F0F0' = X'FF0F'$

#### Logical Or

The logical or operator .OR. performs a 16-bit bit-wise "inclusive or" operation on its two operands.

Examples:

$$= B'0111'$$

#### Multiplication

The multiplication operator \* yields the product of its two operands which are treated as unsigned 16-bit integers. If necessary, the result is truncated by dropping all but the least significant bits.

Examples:

$$X^{1}4000^{1}*X^{1}10^{1} = 0$$

$$X^{\dagger}FEDC^{\dagger}*X^{\dagger}100^{\dagger}=X^{\dagger}DC00^{\dagger}$$

#### Right Shift

The right shift operator . RS. shifts its left operand to the right the number of bits indicated by the right operand. The shift is a logical 16-bit end-off shift with zero bits entering on the left as required. The shift count must be in the range 0-15 inclusive.

$$B^{1}101010^{1}$$

. RS. 3 =  $B^{1}101^{1}$

$$X'FF7F.RS.5 = X'07FB'$$

#### Subtraction

The subtraction operator - subtracts its right operand from its left operand to yield a result. The subtraction is performed on 16-bit unsigned quantities ignoring overflow. This is equivalent to a twos-complement subtract if the operands are regarded as signed twos-complement values.

$$3-4 = X'FFFF'(-1)$$

$$200-X^{t}FFFF^{t} = 201 (200-(-1))$$

#### OPERATOR PRECEDENCE AND ORDER OF OPERATIONS

It is permissible to write an alternating sequence of operands and operators in an expression. In this case, the question arises of which operator is performed first, and is resolved by the following precedence table.

| Precedence<br>Level | Operators            |

|---------------------|----------------------|

| 7                   | * /                  |

| 6                   | <b>+</b> -           |

| 5                   | .RSLS.               |

| 4                   | .EQNEGT.<br>.LTLEGE. |

| 3                   | .AND.                |

| 2                   | .OR.                 |

| 1                   | .XOR.                |

When two operators have a common operand, the operator with the higher precedence is always performed first. If two such operators have the same precedence, the one on the left is performed first. Parentheses may be used to group sub-expressions and alter the normal order of operations as specified by above rules. For example, the following two examples are equivalent:

Up to five levels of parentheses are permitted.

#### OMISSION OF ZERO OPERANDS

If the left operand of + or - is zero:

0+

0-

the zero may be omitted and is understood to be present. Thus:

-5 is the same as 0-5 (=X'FFFB')

+A\*B is the same as 0+A\*B

(-A)\*(-B) is the same as (0-A)\*(0-B)

1\*-2 is the same as 1\*0-2

#### EXAMPLES

The following examples illustrate the rules for forming expressions and also show several techniques which are made possible by the expression evaluation mechanism:

A\*(A.GE.B)+B\*(B.GT.A)

(maximum of A, B)

10+10\*(\$X, RS. 14)

(10 if CNFG 10 or 25, else 20)

X-X/Y\*Y

(remainder of X divided by Y)

(A. XOR. X'8000'), GE. (B. XOR. X'8000') (signed comparison)

NLINES\*64

(screen size)

\$X-4\*(3+D)-2

(auto-exec area, device D)

\$B. RS. 4. AND. 1

(isolate bit 4 of \$B)

${}^{1}0^{1} + N + ({}^{1}A^{1} - {}^{1}({}^{1}-1)*(N.GT.9)$

(ASCII-hex value of N (0 (N (15))

#### SECTION IV

#### MACHINE OPERATIONS

#### GENERAL

This section describes assembler operations used to generate code for executable machine operations. They are grouped by functional class.

Note that automatic word alignment takes place for all machine instructions just as if they had been preceded by an ALGN pseudo-operation. As indicated, any instruction may be labeled, in which case the symbol used as <label> is defined to have the value of the location counter after any required word alignment.

#### WORD CLASS INSTRUCTIONS

|                    | MNEN<br>OP CO | MONIC<br>DDE | HEXADECIMAL<br>OP CODE | DESCRIPTION        |

|--------------------|---------------|--------------|------------------------|--------------------|

| [< label >]        | CMC           | < a >        | { X'70aa' }            | compare cursor     |

| [< label >]        | CMX           | < a >        | { X'70aa' }            | compare index      |

| [< label >]        | DEC           | < a >        | { X'58aa' }            | decrement          |

| [< label >]        | INC           | < a >        | { X'50aa' }            | increment          |

| [< label >]        | IN2           | < a >        | { X'60aa' }            | increment by two   |

| [< label >]        | ЈМР           | < a, >       | { X'B8aa' }            | jump               |

| [< label >]        | JSR           | < a >        | { X'78aa' }            | jump to subroutine |

| [ <label>]</label> | LDC           | < a >        | { X'40aa' }            | load cursor        |

| [< label >]        | LDX           | < a >        | { X'40aa' }            | load index         |

| [< label >]        | STC           | < a >        | {X'48aa'}              | store cursor       |

| [ <label>]</label> | STX           | < a >        | { X'48aa' }            | store index        |

The listed operations generate one word (short address) instructions which reference a word location in memory. < a > is an expression whose value is the operand address which must be even. The assembler sets the sector reference and addressing bits of the instruction in accordance with the appropriate hardware rules. In the event that the referenced sector is not directly accessible, an automatic entry is made in the literal table (called a desectorizing link) which points to the desired address and the generated instruction is setup to reference indirectly through this location.

Another possibility for the operand < a > is a literal consisting of an expression immediately preceded by =. In this case, a word containing the 16 bit value of the expression is created in the literal table and the instruction references this word. See description of the SIZE pseudo-operation for details of the positioning of this table.

Any of the above instructions may specify indirect addressing by the use of an \* immediately following the opcode. In this case, the indirect bit of the instruction (if the sector is directly referenceable) and the desectorizing link (if one is created) is set on to obtain indirect addressing.

| Examples: | BGLOOP | JMP  | \$               |            |

|-----------|--------|------|------------------|------------|

|           |        | JSR  | SUBR             |            |

|           |        | INC* | \$X              |            |

|           |        | LDX  | =0               |            |

| ·         |        | СМС  | =NLINES*64       |            |

|           |        | JMP* | =XX (forces dese | ctorizing) |

#### BYTE CLASS INSTRUCTIONS

| ·           | MNEMONI<br>OP CODE | C <sup>.</sup> | HEXADECIMAL<br>OP CODE | DESCRIPTION   |

|-------------|--------------------|----------------|------------------------|---------------|

| [< label >] | AD                 | ;<'a.>         | { X'10aa' }            | add byte      |

| [< label>]  | AN                 | < a >          | { X'28aa' }            | and byte      |

| [< label>]  | CM                 | < a >          | { X'20aa' }            | compare byte  |

| [< label>]  | LD                 | < a >          | { X'00aa' }            | load byte     |

| [< label >] | OR                 | <a>&gt;</a>    | { X'30aa' }            | or byte       |

| [< label >] | SB                 | < a, >         | { X'18aa' }            | subtract byte |

| [< label >] | ST                 | < a >          | { X'08aa' }            | store byte    |

The above operations generate one-word (short address) instructions which reference a byte location in memory. <a> is an expression whose value is the operand address. The assembler sets the sector reference and addressing bits of the instruction in accordance with the appropriate hardware rules. In the event that the referenced sector is not directly accessible, an automatic entry is made in the literal table (called a desectorizing link) which points to the desired address and the generated instruction is set up to reference indirectly through this location. Except as described below, literals may not be used as operands for byte class instructions.

Any of the above instructions may specify indirect addressing by the use of a \* immediately following the opcode. In this case the indirect bit of the instruction (if the sector is referencable) and the desectorizing link (if one is created) is set on to obtain desectorizing. Indirectly addressed byte

class instructions are treated as word class instructions. This means that the specified address must be even and that literal references are permitted.

Examples:

LD A+4

ST# \$X

LBL CM\* =A (forces desectorizing)

#### INDEXING

On the 20/20 only (i.e. in CNFG 20), indexing notation can be used on any word class or byte class instruction. Preceding the operand field with @ (at sign) causes the assembler to generate an indexing (X'C94F') instruction prior to generating code for the instruction itself. In this case, <label>, if present, is set to the location counter value prior to generating the indexing instruction.

For word class and indirectly addressed byte class instructions, it is permissible to use indexing in conjunction with a literal reference, the @ sign precedes the = in this case.

Examples:

LOAD LD @4

LDX @LINKP

CM\* @=NEXT (forces desectorizing)

#### OPERATE CLASS INSTRUCTIONS

|                    | MNEMONIC<br>OPCODE | HEXADECIMAL<br>OPCODE | DESCRIPTION               |

|--------------------|--------------------|-----------------------|---------------------------|

| [<1abel>]          | NOP                | {X'C000'}             | no operation              |

| [ <label>]</label> | HALT               | {X'C001'}             | halt                      |

| [ <label>]</label> | MLA                | {X'C002'}             | move LIR to ACR           |

| [ <label>]</label> | MAL                | {X'C003'}             | move ACR to LIR           |

| [ <label>]</label> | MCA                | {X'C004'}             | move CHR to ACR           |

| [<1abe1>]          | MAC                | {X'C005'}             | move ACR to CHR           |

| [ <label>]</label> | ENB                | {X'C006'}             | enable interrupts         |

| [ <label>]</label> | DSB                | {X'C007'}             | disable interrupts        |

| [ <label>]</label> | IOR                | {X¹C008¹}             | I/O reset                 |

| [ <label>]</label> | SHL4               | {X' C009'}            | shift left four           |

| [ <label>]</label> | RTL1               | {X'C00A'}             | rotate left one           |

| [ <label>]</label> | SRL1               | { X' C00B'}           | shift and rotate left one |

| [ <label>]</label> | CLL                | { X' G00G'}           | clear LIR                 |

| [ <label>]</label> | CLC                | {X'C00D'}             | clear CHR                 |

| [ <label>]</label> | WAIT               | {X'C00F'}             | wait                      |

The above operations generate one-word operate class instructions as shown. No operands are permitted. MLA, MAL, MCA, MAC, CLL, CLC may be used only in CNFG 10 or CNFG 24 or CNFG 25 modes. RTL1 may be used only in CNFG 20 mode. SRL1 may be used only in CNFG 24 mode.

# IMMEDIATE CLASS INSTRUCTIONS

|                    | MNEMONIC<br>OP CODE | HEXADECIMAL<br>OPCODE                | DESCRIPTION            |

|--------------------|---------------------|--------------------------------------|------------------------|

| [< label>]         | LDI <v></v>         | { X'80vv¹}                           | load immediate         |

| [< label>]         | ADI <v></v>         | { X <sup>1</sup> 90vv <sup>1</sup> } | add immediate          |

| [< label>]         | SBI <v></v>         | { X' 98vv'}                          | subtract immediate     |

| [ <label>]</label> | ANI < v>            | { X'A8vv'}                           | and immediate          |

| [< label>]         | ORI < v>            | { X'B0vv'}                           | or immediate           |

| [< label>]         | XOR < v>            | $\{X^tD0vv^t\}$                      | exclusive or immediate |

The above operations generate one-word immediate class instructions. The operand < v > is an expression whose value is the immediate operand. This value must be in the range 0 to 255 or -128 to -1 (X'FF80' to X'FFFF'). Indirect addressing is not permitted.

Examples:

ADI '0'

ANI X'FF'

XOR \$.AND.X'FF'

# JUMP ON CONDITION INSTRUCTIONS

|                    | MNEMONIC<br>OP CODE |             | HEXADECIMAL<br>OP CODE | DESCRIPTION                   |

|--------------------|---------------------|-------------|------------------------|-------------------------------|

| [ <label>]</label> | JCFAL               | <a>&gt;</a> | { X'8800aaaa'}         | never jump                    |

| [ <label>]</label> | JCLT                | <a>&gt;</a> | { X'8900aaaa'}         | jump on less than             |

| [ <label>]</label> | JCEQ                | <a>&gt;</a> | {X'8A00aaaa'}          | jump on equal                 |

| [ <label>]</label> | JCLE                | <a>&gt;</a> | {X'8B00aaaa'}          | jump on less than or equal    |

| [ <label>]</label> | JCTRU               | <a>&gt;</a> | { X'8C00aaaa'}         | always jump                   |

| [ <label>]</label> | JCGE                | <a>&gt;</a> | { X'8D00aaaa'}         | jump on greater than or equal |

| [ <label>]</label> | JCNE                | <a>&gt;</a> | {X'8E00aaaai}          | jump on not equal             |

| [ <label>]</label> | JCGT                | <a></a>     | {X'8F00aaaaf}          | jump on greater than          |

| [ <label>]</label> | JCNG                | <a>&gt;</a> | { X'8801aaaa'}         | jump on negative              |

| [ <label>]</label> | JCPO                | <a></a>     | {X'8C01aaaa'}          | jump on positive              |

| [ <label>]</label> | JCEV                | <a>&gt;</a> | { X'8C02aaaa'}         | jump on even                  |

| [ <label>]</label> | JCOD                | <a.></a.>   | {X'8802aaaa'}          | jump on odd                   |

| [ <label>]</label> | JCNC                | <a>&gt;</a> | {X'8900aaaa'}          | jump on no carry              |

| [ <label>]</label> | JCCO                | <a></a>     | { X' 8D00aaaa'}        | jump on carry                 |

| [ <label>]</label> | WJMP                | <a></a>     | {X'8C00aaaa!}          | word jump                     |

The above operations generate two-word jump on condition instructions as shown. The operand <a> is an expression whose value, which must be even, is the target jump address.

Indirect addressing may be specified by placing a \* after the opcode. In this case the indirect addressing bit of the second word generated is set on.

Examples:

JCGT

LOC+8

JCEQ\*

RTNAD

HANG

**JCTRU**

HANG

JCNE

\$-10

# COMPARE AND JUMP INSTRUCTIONS

|                          | MNEMOI |                                   | HEXADECIMAL<br>OPCODE                   | DESCRIPTION                               |

|--------------------------|--------|-----------------------------------|-----------------------------------------|-------------------------------------------|

| [< label >]              | CJFAL  | <'v'>,< a >                       | {X'A0vvaaaa'}                           | compare and never jump                    |

| [< label>]               | CJLT   | < <sub>v</sub> >,< <sub>a</sub> > | {X'Alvvaaaa'}                           | compare and jump on<br>less than          |

| [ label >]               | CJEQ   | < v > , < a >                     | $\{X^{t}A2vvaaaa^{t}\}$                 | compare and jump on equal                 |

| [k label >]              | CJLE   | < v >,< a >                       | {X'A3vvaaaa'}                           | compare and jump on<br>less than or equal |

| <pre>[k label&gt;]</pre> | CJTRU  | < v >,< a >                       | {X <sup>1</sup> A4vvaaaa <sup>1</sup> } | compare and always jump                   |

| [ label >]               | CJGE   | < v >,< a >                       | {X'A5vvaaaa'}                           | compare and jump on greater than or equal |

| <pre>[ label&gt;]</pre>  | CJNE   | < v >,< a >                       | {X'A6vvaaaa'}                           | compare and jump on not equal             |

| <pre>{ label&gt;]</pre>  | CJGT   | <v>, &lt; a &gt;</v>              | {X'A7vvaaaa'}                           | compare and jump on greater than          |

The above operations generate two-word compare and jump class instructions. The first field < v > is an expression whose value is the comparison operand. The value of this expression must be in the range 0 to 255 or -128 to -1 (X'FF80' - X'FFFF'). The second field < a > is an expression whose value,

which must be even, is the target jump address.

Indirect addressing may be specified by placing a \* after the opcode.

In this case, the most significant bit of the second word generated is set on.

Examples: LBL CJEQ X'F0', \$+8

CJNE \$. AND. X'FF', MATCH

CJGE\* 'C', ENTRY

CJEQ -1, BOR

### INPUT-OUTPUT INSTRUCTIONS

| 3                  | MNEMONIC<br>OP CODE |                       | HEXADECIMAL<br>OP CODE | DESCRIPTION |

|--------------------|---------------------|-----------------------|------------------------|-------------|

| [ <label>]</label> | CIO                 | <f>, &lt; d &gt;</f>  | { X'C9fd' }            | control I/O |

| [ <label>]</label> | RIO                 | <f> , &lt; d &gt;</f> | { X'CAfd' }            | read I/O    |

| [ <label>]</label> | WIO                 | <f>, &lt; d &gt;</f>  | { X'CBfd' }            | write I/O   |

The above operations generate the one word input-output instructions.

< f>, <d> are expressions whose value is in the range 0 to 15 which are used to provide the function and device codes as shown.

|                    | MNEMONIC<br>OP CODE |                           | HEXADECIMAL<br>OP CODE | DESCRIPTION                   |

|--------------------|---------------------|---------------------------|------------------------|-------------------------------|

| [ <label>]</label> | JFACK               | < f>, <d>, <a></a></d>    | {X'CCfdaaaa'}          | jump on no<br>I/O acknowledge |

| [ <label>]</label> | JTACK               | <f>, <d>, <a></a></d></f> | {X'C8fdaaaa'}          | jump on I/O<br>acknowledge    |

The above operations generate the two word test input-output instructions.

< f>, <d> are two expressions whose value is in the range 0 to 15 which are used to provide the function and device codes as shown. < a> is an expression whose value is the target jump address which must be even. Indirect addressing may be specified by placing a \* immediately following the opcode, in which case the most significant bit of the second word is set on.

| Examples: |      | CIO    | 4, X'A'           |

|-----------|------|--------|-------------------|

|           | Þ    | RIO    | SDATA, SYNC       |

|           | LOOP | JFACK* | 1,2,WRITE         |

|           |      | JTACK  | BUSY, DISK, \$    |

|           |      | OIW    | 1, \$B. AND. X'F' |

#### EXTENDED MNEMONICS

The assembler provides a set of opcodes representing special purpose uses of standard instructions. Although these are not individual machine operations, they may be regarded as such by the assembly language programmer.

| MNEMONIC<br>OP CODE |     | HEXADECIMAL OPCODE DESCRIPTI |                   |

|---------------------|-----|------------------------------|-------------------|

| [ label>]           | CLA | { X'8000'}                   | clear accumulator |

CLA takes no operands, and as can be seen from the generated code, is actually equivalent to LDI 0.

| MNEMONIC<br>OPCODE |     | HEXADECIMAL OPCODE DESCRIPTION |                       |

|--------------------|-----|--------------------------------|-----------------------|

| [< label>]         | SKP | { X'88.00'}                    | skip next instruction |

SKP takes no operands, and as can be seen from the generated code, is equivalent to the first word of a JCFAL instruction, the skipped word actually being the unreferenced address operand.

#### SECTION V

# ASSEMBLER PSEUDO-OPERATIONS

#### GENERAL

Assembler pseudo-operations are written in normal LABEL OPCODE

OPERANDS COMMENT format but do not correspond to actual hardware

instructions. Instead, they are used to generate data in various ways or to

control the assembly process. This chapter lists all pseudo-operations in

alphabetical order.

### ADDR -- Generate two-byte data

The ADDR pseudo-operation is used to assemble one or more two-byte values. These values are generated in sequence and are not necessarily aligned to a word boundary.

The form is:

As shown, the number of <operand >s is variable from one to as many as will fit on a single line.

Any expression may be used as an operand>, resulting in generation of

two bytes containing its value.

Alternately, an operand> can have the following format:

<repeat><constant>

where < repeat > is an explicit decimal integer and <constant > is one of the following:

B'.... binary constant

O'....' octal constant

D'.... decimal constant

X'.... hexadecimal constant

'x' one character ASCII constant

'xx' two character ASCII constant

The result of such a specification is to generate two bytes containing the constant value the number of times specified by repeat. A zero repeat factor results in no code being generated.

Examples:

ADDR

'AB', 3D' 999'

(generates 4 words)

KONS A

ADDR

B'101', 99'\*\*1

(generates 100 words)

# ALGN -- Align to word boundary

The ALGN pseudo-operation increments the load and location counter if the location counter is odd. It thus ensures that the following data is generated starting on an even byte (i.e. word) boundary. In the event that the location counter is already even, ALGN has no effect. The form is:

[<label>] ALGN

As shown, there is no operand. < label>, if given, is assigned the location counter value following incrementation (if any) of the counters i.e. the label value will always be even. Note that the incrementation in the odd case is equivalent to BSS 1; no zero byte is generated.

Examples:

WORDST

ALGN

BOOT -- Set boot mode

The BOOT pseudo-operation sets the assembler in boot mode. The form

is: BOOT

As shown, no operand or label is permitted.

Boot must precede the first object code generation. It is used to assemble a program which is intended to load directly using the hardware bootstrap mechanism. The following restrictions are placed on a boot mode program:

ORG operations are not allowed. BOOT sets the origin to zero (X'000') automatically. The normal prohibition against code below location X'100' is not enforced.

XORG may not specify a second operand.

BSS is not allowed.

Literals may not be used.

Cross-sector references not resolvable by the hardware are not permitted.

SEG and ESEG operations are not permitted.

END may not specify an entry point.

BSS -- Reserve storage

The BSS pseudo-operation is used to reserve storage without assembling any data. The form is:

[<label>] BSS <count>

< label>, if present, is set to the location counter value at the start. No word alignment takes place.

<count> is an expression whose value is the number of bytes to reserve.

This value is added to both the location and load counters. Any symbols used must have been previously defined.

Note: INCOTERM standard loaders do not clear memory before loading.

This means that the contents of any BSS areas following initial load is whatever was there before the load started, since these areas are not included in the object output.

Examples: BUFR BSS 128

HERE BSS 0 (no effect, except to define label)

ALGNR BSS \$.AND.1 (like ALGN)

BSZ -- Generate zeros

The BSZ pseudo-operation is used to generate a specified number of zeros.

The form is:

[<label>] BSZ <count>

< label>, if present, is set to the location counter value at the start. No word alignment takes place.

<count> is an expression giving the number of zero bytes to be generated.

A value of zero is permitted, resulting in generation of no data. Any

symbols appearing in the expression must be previously defined.

Note that the use of BSZ with large counts can result in increasing the size of the generated object program considerably depending on the medium.

Where possible, it is desirable to replace such BSZ operations with initialization code which performs the required zeroing operation.

| Examples: | BUFFER | BSZ | 128            | (generates 128 zeros)                                                |

|-----------|--------|-----|----------------|----------------------------------------------------------------------|

|           |        | BSZ | 1256-\$        | (zeros up to location<br>1256 decimal)                               |

|           |        | BSZ | \$. AND. 1     | (acts like ALGN, except<br>that a byte of zeros may<br>be generated) |

|           | •      | BSZ | 64-(\$.AND.63) | (zero to end of 10/20 screen line)                                   |

BYTE -- Generate byte data

The BYTE pseudo-operation is used to assemble one or more bytes of data according to the value of expressions given. The form is as follows:

[< label>]

BYTE < operand>, <operand>, ... <operand >

<label>, if present, is set to the value of the location counter prior to

generation of the first value. No word alignment takes place.

As shown, the number of operands is variable from one to as many as will fit on a single line.

Any expression whose value is in the range 0 to 255 or -128 to -1 (X'FF80' to X'FFFF') may be used as an operand > with the resulting generation of a single byte of data (upper X'FF' byte is ignored for 'negative' values).

Alternately, an operand > can have the following format:

< repeat > < constant >

where repeat> is an explicit decimal integer and <constant > is one of the following:

B'....' binary constant

O'....' octal constant

D'....' decimal constant

X'....' hexadecimal constant

'x' single character ASCII constant

The result of such a specification is to generate a byte containing the constant value the number of times specified by repeat. A zero repeat value is legal and causes no data to be generated for that value.

| Examples: | LOOP | BYTE | X'FF'                                                                                     |                      |

|-----------|------|------|-------------------------------------------------------------------------------------------|----------------------|

|           |      | BYTE | A+B*C, -1                                                                                 |                      |

|           | L1   | BYTE | <sup>1</sup> E <sup>1</sup> , <sup>1</sup> R <sup>1</sup> , 3 <sup>1</sup> * <sup>1</sup> | (generates 5 bytes)  |

|           |      | BYTE | \$. AND. X'FF', 79B'1001'                                                                 | (generates 80 bytes) |

|           |      | BYTE | 'E', 0'*1, 'R'                                                                            | (generates 2 bytes)  |

CNFG -- Specify configuration mode

The CNFG pseudo-operation sets the configuration mode to match the hardware in use. The form is:

CNFG [< mode>]

As shown, no label is permitted.

<mode > is an expression which has one of the following five values:

- 10 10/20 mode assembly. AXN, RTL1, SRL1 instructions not recognized. Addressing restrictions and link resolution compatible with SPD 10/20 architecture.

- 20 20/20 mode assembly. MCA, MAC, MAL, MLA, CLC, CLL, SRL1 operations not recognized. Addressing restrictions and link resolution compatible with SPD 20/20 architecture.

- 24 10/24 mode assembly. AXN, RTL1 operations not recognized. Addressing restrictions and link resolution compatible with SPD 10/24 architecture.

- 25 10/25 mode assembly. AXN, RTL1, SRL1 operations not recognized. Addressing restrictions and link resolution compatible with SPD 10/25 architecture.

- O Compatible mode assembly. AXN, RTL1, MCA, MAC, MLA, CLC, CLL, MAL, SRL1 operations not recognized. Addressing restrictions and link resolution compatible with SPD 10/20, 10/24, 10/25 and 20/20 architectures.

Any symbols appearing in the expression for mode must have been previously defined. See section on addressing for further details on address restrictions and link resolution.

The first CNFG pseudo-operation in the program specifies the program configuration mode and must occur before the first generation of object code. Subsequent CNFG operations may occur but they affect only the allowed operation set, not the addressing mode. This may be useful, for example, in assembling a section of code in a CNFG 0 assembly which is executed only in the 20/20 case and uses RTL1.

If the <mode > operand is omitted, the effect is to return to the mode of the program (i.e. that of the first CNFG). The mode operand may not be omitted on the initial CNFG line.

If no CNFG operation appears in a program, CNFG 10 is assumed throughout.

Examples:

CNFG 10

(set 10/20 mode)

CNFG 0

(set compatible mode)

CNFG 10+10\*(\$B.AND.1) (10 or 20 depending on \$B)

DAC -- Generate address constant

The DAC pseudo-operation is used to generate a single word containing an address. The form is:

[<label>] DAC[\*] <address>

<label>, if present, is set to the location counter value prior to generation

of the word (following possible word alignment).

<address> is an expression which evaluates to an address in the permissible range (see section on addressing). If indirect addressing is specified, the indirect addressing bit of the result is set. (DAC is the only pseudo-operation which permits indirect addressing).

Examples: KPTR DAC K

DAC \$+3\*4

DAC\* 256

#### DUP -- Duplicate source line

The DUP pseudo-operation allows the effects of a specified source line to be duplicated. The form is:

The effect is as if <source line> had appeared consecutively the number of times specified by the value of the count expression. Any line may be duplicated in this manner except DUP, END, IF, ENDF, sub-title and comment lines.

Any symbols appearing in <count> must be previously defined. As shown, no label is permitted.

A duplication count of zero is valid, and causes < source line > to be assembled zero times (i.e. to be deleted).

Within expressions appearing in <source line>, the special symbol \$D takes on values of 1, 2, 3,... for the successive duplications.

| Examples: | DUP<br>DAC  | X.NE.0<br>X                | (assemble if X non-zero)        |

|-----------|-------------|----------------------------|---------------------------------|

|           | DUP<br>BYTE | 26<br>'A'-1+\$D            | (26 ASCII letter codes)         |

|           | DUP<br>BYTE | 64-(\$.AND.63)             | (blanks to end of 10/20 line)   |

|           | DUP<br>BYTE | 16 '0'-1+\$D+7*(\$D.GE.10) | (16 ASCII codes for hex digits) |

EJECT -- Eject assembly listing to new page

The EJECT pseudo-operation causes the assembly listing to eject to a

fresh page. The form is:

EJECT

As shown, no label or operand is permitted. The use of EJECT has no effect on the generated code. EJECT is effective only in LIST 2 or LIST 3 mode.

END -- End assembly

The END pseudo-operation occurs once at the end of the source text as the last source line and marks the end of the text. The form is:

END [< entry >]

<entry> is an expression whose value (which must be in address range) specifies the location to which control is to be passed following loading the program. As shown, it is optional. If omitted, the entry point is set to the first assembled location in segment zero. As shown, no label is permitted.

Examples: END

END BEGIN

ENDF -- End conditional assembly range

The ENDF pseudo-operation marks the end of a conditional assembly range and occurs only in conjunction with a previously occuring matching IF pseudo-operation.

The form is:

ENDF

As shown, no label or operand is permitted.

# EQU -- Equate symbol to value

The EQU pseudo-operation is used to assign a given value to a specified symbol. The form is:

<label> EQU <value>

<label>, which is required, is the symbol whose value is to be set.

<value> is an expression giving the value to be set. Any symbols appearing in <value> must have been previously defined.

| Examples: | SYMQ | EQU | X'27' | (value of ASCII quote)          |

|-----------|------|-----|-------|---------------------------------|

|           | HERE | EQU | \$    | (like HERE BSS 0)               |

| l.        | PRA  | EQU | \$X-2 | (location of power restart)     |

|           | F2   | EQU | F1+1  | (F1 must be previously defined) |

ESEG -- End overlay segment

The ESEG pseudo-operation terminates an overlay segment. The form is:

ESEG [k entry >]

<entry> is an expression whose value specifies the segment entry point. If omitted, the segment entry point is set to the first assembled location in the segment. The significance of this entry point is defined by the routines used to load the segment. It is normally the location to which control is passed initially if the segment is executed. As shown, no label is permitted.

Following the ESEG, the load and location counters are unchanged and assembly resumes in segment zero (the main segment). All literals and links required by the code in overlay segments are added to the main (segment zero) literal table which is always resident.

Examples: ESEG SEGMENT

ESEG

HEX -- Generate hexadecimal data

The HEX pseudo-operation is used to generate a string of bytes whose value is given in hexadecimal. The form is:

[<label>] HEX <hex>

<label>, if present, is set to the location counter value prior to generation

of the first data byte. No word alignment takes place.

<hex> is an even length string of two or more hexadecimal digits (0-9, A-F).

Each successive pair of digits corresponds to a single byte of generated

data.

Examples: ENDREF HEX 7474

HEX A3FF010D

HEX 4142 (like TEXT 'AB')

IF -- Start conditional assembly range

The IF pseudo-operation provides for conditional assembly of a section of code. The form is:

IF <test>

<test> is an expression which is evaluated. If the value is non-zero, there is no effect. If the value is zero, than all code between the IF and its matching ENDF is ignored. Any symbols appearing in < test> must have been previously defined. As shown, no label is permitted. IF -ENDF pairs may be nested to any reasonable level.

Examples: IF \$B.AND. X'200' (test bit 9 of \$B)

IF X.GT.Y

IF X.GE. 3. AND. X. LT. 17

LBL -- Generate label data

The LBL pseudo-operation is used to generate the primary title data. The form is:

[< label>] LBL

<label>, if given, is set to the location counter value prior to the generation

of the first byte. No word alignment takes place. As shown, no operand is

permitted.

The effect of LBL is to assemble 40 bytes corresponding to the ASCII codes for the 40 characters of the primary title, as modified by any assembled & lines in the text. The result is exactly as if this title had been assembled by TEXT. This operation may be useful in controlling program version number information.

Examples:

LABELD

LBL

LIF -- Control Listing of IF Ranges

The LIF pseudo-operation is used to control the listing of IF's, ENDF's and code deleted in conditional ranges. The form is:

LIF <code>

As shown, no label is permitted.

<code> is an expression with a value of 0, 1, or 2. Any symbols used must

have been predefined. The effects are as follows:

- <code> = 0 IF and ENDF lines are never printed and code deleted by

"false" ranges is also not printed. The effect is to generate

an assembly listing which (except for line numbers) is identical

to that which would have been obtained if no IF's had been used.

- <code> = 1 (The default setting if no LIF appears). Code deleted by "false" ranges is not listed. IF and ENDF lines list except when they are contained within a deleted range.

- < code> = 2 All IF and ENDF lines are printed. Deleted code is also printed.

In LIST 0 mode, IF and ENDF lines and deleted code are not printed regardless of the LIF setting. Note that the assembler has an option to control LIF mode externally, thus overriding the affect of LIF operations in the source.

#### LIST -- Control Listing Mode

The LIST pseudo-operation is used to control the format of the listing.

The form is:

LIST < code>

As shown, no label is permitted.

<code> is an expression with a value of 0, 1, 2, or 3. Any symbols used

must have been predefined. The effects are as follows:

- <code> = 0 Only flagged lines are printed, no sub-titles are printed.

- <code> = 1 All lines are printed except comments starting with #.

EJECT and subtitle lines are printed as comments but have

no other effect. No sub-titles are printed.

- <code> = 3 All lines are printed including comments starting with #.

EJECT and sub-title lines are interpreted and used to format

the listing.

In the case of IF, ENDF and lines deleted by IF-ENDF, both the LIF and LIST conditions must be met in order for unflagged lines to print. Note that the assembler has options to control LIST mode externally, thus overriding the effect of LIST operations in the source.

LTXT -- Generate lower case text string

The LTXT pseudo-operation is used to generate a string of bytes corresponding to ASCII values of characters in a supplied text string except that any letters are converted to lower case (other characters unaffected). The form is:

[<label>] LTXT <d> < text >< d >

<label>, if present, is set to the location counter prior to generation of the first byte. No word alignment occurs.

<d> is any non-blank character not appearing in (text). It acts as a delimiter and is not included in the generated data.

<text> is a string of any characters except the delimiter character. It may range in length from zero (no data generated) to as long as is permitted by the restriction to a single source line.

Examples: LTXT '0123' (like TEXT '0123')

XX LTXT \*AB\* (generates X'6162')

LTX8 -- Generate lower case text string with 8th bit set.

The LTX8 pseudo-operation is used to generate a string of bytes corresponding to ASCII values of characters in a supplied text string except that letters are converted to lower case as in LTXT and the most significant (parity) bit of each byte is set. The form is:

[<label>] LTX8 <d><text><d>

<label>, if present, is set to the location counter prior to generation of the first byte. No word alignment occurs.

<d> is any non-blank character not appearing in <text>. It acts as a delimiter and is not included in the generated data.

<text> is a string of any characters except the delimiter character. It may

range in length from zero (no data generated) to as long as is permitted by

the restriction to a single source line.

Examples:

LTX8 '0123'

(like TXT8 '0123')

LB

LTX8 \*AB\*

(generates X'E1E2')

NOBJ -- Turn off object output mode

The NOBJ pseudo-operation is used to discontinue generation of object code.

The form is:

NOBJ .

As shown, no label or operand is permitted.

Following the occurence of NOBJ and until an OBJ pseudo-operation is encountered no object data will be generated. However, in all other respects the assembly proceeds as usual, with the load and location counters being incremented in the normal manner.

NOBJ may be useful in assembling prototype (dummy) sections of code for purposes of documentation or symbol definition. OBJ mode is automatically

set when an END or ESEG line is encountered, thus literals and entry point records are always generated.

OBJ -- Turn on object output mode

The OBJ pseudo-operation is used to resume generation of object code.

The form is:

OBJ

12 To 12 Erec

And the second of the second of the second

As shown, no label or operand is permitted.

Following the occurrence of OBJ, normal output of generated code is resumed. Since this is the normal (default) mode, OBJ is used only in conjunction with NOBJ to selectively inhibit object code generation for parts of the program.

ORG -- Set assembly origin

The ORG pseudo-operation is used to set or reset the location and load counters. The form is:

[< label>]

ORG

<loc>

<label>, if present, is set to the value of the location counter after the

origin operation is completed (i.e. to the value of loc).

<loc> is an expression whose value is used to reset both the load and location counters. All symbols appearing in the expression must be previously defined.

Note: In the absence of an ORG statement at the start of an assembly, the default starting value for both load and location counters is X'100'.

Examples:

ORG

\$+10

(like BSS 10)

TOPS

ORG

X'7E00'

ORG

\$X. AND. X'7E00'

(CNFG independent top sector)

ORG

\$L

(resets location counter to match load counter) PAGE -- Set page depth

The PAGE pseudo-operation allows specification of the page depth for the assembly listing. The form is:

PAGE < count >

As shown, no label is permitted.

count> is an expression whose value is the maximum number of lines per printed assembly page (not counting the title lines). When this value is exceeded, an automatic eject occurs. The allowed range is 1-255. Any symbols used must have been previously defined.

More than one PAGE pseudo-operation may occur in assembly, in which case each one affects the listing for the following section. If no PAGE pseudo-operation is used, an appropriate default which depends on the assembler and environment is set.

The use of PAGE does not affect the generated code.

Examples: PAGE 41 (41 lines/page)

PAGE 255 (max allowed value)

SEG -- Start of overlay segment

The SEG pseudo-operation specifies the start of an overlay segment. The form is:

dabel> SEG [<org>]

<label>, which is required, is set to the segment number. Segments are numbered serially starting at 1 and ranging up to a maximum value of 250.

<org> is an expression whose value is used to set the load and location

counters in the same manner as the ORG pseudo-operation. It is optional

and, if omitted, the load and location counters are unchanged. Any symbols

appearing in <org> must have been previously defined.

The range of segment code is from the SEG operation to its matching ESEG.

No nesting of SEG-ESEG pairs is permitted. ORG and XORG pseudooperations may be used within the segment to modify the location and load

counters.

Standard INCOTERM loaders load only segment zero and ignore other segments. The loading of overlay segments is accomplished using special routines appropriate to the load medium.

Examples: SEG1 SEG

SEG2 SEG SEGORG

SET -- Set symbol to value

The SET pseudo-operation is used to assign or reassign the value of a specified symbol. The form is:

<label > SET <value >

<label>, which is required, is the symbol whose value is to be set.

<value> is an expression giving the value to be set. Any symbols appearing in <value> must have been previously defined.

SET is the only operation which permits a symbol to be assigned more than one value. This is accomplished by having more than one SET for the same symbol. In this case the value of the symbol is whatever was assigned by the most recent SET operation. If a SET symbol is referenced before any SET for the SYMBOL has occurred, the value (in pass 2) is that set by the last SET in pass 1.

A symbol defined by SET must not be defined by any other method (i.e. must not appear in the label field except on another SET operation).

Examples: Q SET Q+1 (increment previously SET value)

SEGHI SET SEGHI+(\$-SEGHI)\*(\$.GT.SEGHI) (SEGHI=max(SEGHI,\$))

#### SIZE -- Specify memory size

The SIZE pseudo-operation is used to specify the memory size and the origin for literals. The form is:

As shown, no label is permitted.

< size> gives the address of the last byte in memory and must have one of the following values:

| CNFG 0  |    | X'0FFF' | (4K)  |

|---------|----|---------|-------|

|         | or | X'IFFF' | (8K)  |

|         | or | X'3FFF' | (16K) |

|         | or | X'7FFF' | (32K) |

| CNFG 10 |    | X'0FFF' | (4K)  |

| CNFG 20 |    | X'3FFF' | (16K) |

|         | or | X'7FFF' | (32K) |

| CNFG 24 |    | X'IFFF' | (8K)  |

|         | or | X'3FFF' | (16K) |

| CNFG 25 |    | X'0FFF' | (4K)  |

|         |    |         |       |

In the cases where more than one operand can be given, the significance is that the value given represents the minimum workable memory size for the program.

In addition to the values shown, X'0000' (zero) may be used. See special section "SIZE 0" in Chapter VI for details.

dinks > gives the origin for the literal table. Literals and desectorizing links are built downward from the specified location and extend down as far as necessary. Thus the specified even (word) location is the lowest unused address above the table (i.e. the lowest reserved location). A high memory address suitable to the program CNFG must be specified. As shown, the links operand is optional. If omitted, the following default values are used:

| CNFG 0  | X'7FBA'                          |

|---------|----------------------------------|

| CNFG 10 | X'FD2'                           |

| CNFG 20 | X'7FBA'                          |

| CNFG 24 | X <sup>1</sup> 7FD2 <sup>1</sup> |

| CNFG 25 | X'FD2'                           |

<xsize > is omitted in normal assemblies. If set it allows the load counter (but not the location counter) to exceed the normal limit and range up to xsize without error. The resulting program will not be loadable by standard INCOTERM loaders, but special purpose loaders may load such data into external memory for use in overlay systems. The low order byte of the value must be X'FF'.

The SIZE line may be omitted entirely, in which case the size defaults to X'FFF' (CNFG 0, CNFG 10, CNFG 25), X'3FFF' (CNFG 20), or X'1FFF' (CNFG 24). If present, it must precede the occurence of any generated object code.

| Examples: | SIZE<br>SIZE | X'3FFF', X'7FBA'<br>X'FFF', X'FEO' | (CNFG 20 default)<br>(CNFG 10, links higher<br>than default) |

|-----------|--------------|------------------------------------|--------------------------------------------------------------|

|           | STZE         | XIZEFEI XIZEBA! XIEFEFI            | (32K external memory)                                        |

TEXT -- Generate text string

The TEXT pseudo-operation is used to generate a string of bytes corresponding to ASCII values of characters in a supplied text string.

The form is:

[] TEXT

$$\langle d \rangle \langle \text{text} \rangle \langle d \rangle$$

dabel>, if present, is set to the location counter prior to generation of the first byte. No word alignment occurs.

< d > is any non-blank character not appearing in <text>. It acts as a delimiter and is not included in the generated data.

< text > is a string of any characters except the delimiter character. It may range in length from zero (no data generated) to as long as is permitted by the restriction to a single source line.

Examples:

TEXT

'THIS IS A MESSAGE'

MSG TEXT

/QUOTE --1/

TEXT

\*AB\*

(generates X'4142')

TXT8 -- Generate text string with 8th bit

The TXT8 pseudo-operation is used to generate a string of bytes corresponding to ASCII values of the characters in a supplied text string with the X'80' (parity) bit set. The form is:

[

$$\langle label \rangle$$

] TXT8  $\langle d \rangle \langle text \rangle \langle d \rangle$

< label>, if present, is set to the location counter prior to generation of the first byte. No word alignment occurs.

<d> is any non-blank character not appearing in < text >. It acts as a delimiter and is not included in the generated data.

<text> is a string of any characters except the delimiter character. It may range in length from zero (no data generated) to as long as is permitted by the restriction to a single source line.

Examples: BMS TXT8 'BLINK MESSAGE'

TXT8 \*AB\* (generates X'C1C2')

WORD -- Generate word data

The WORD pseudo-operation is used to assemble one or more word values.

These values are generated in sequence and are word aligned. The form

is:

[<label>] WORD operand>, , , operand>

< label>, if present, is set to the value of the location counter prior to generation of the first value. Normal word alignment takes place.