# INTEL iLBX<sup>™</sup> BUS SPECIFICATION

# $\textbf{INTEL iLBX}^{^{\text{TM}}}$ **BUS SPECIFICATION** Order Number: 145695-Rev. A Copyright 1983, Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051

| REV. | REVISION HISTORY | PRINT<br>DATE |

|------|------------------|---------------|

| Α    | Original Issue.  | 1/83          |

| i    | ·                |               |

|      |                  |               |

|      |                  |               |

|      |                  |               |

|      |                  |               |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a) (9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP                 | Insite                 | iRMX            | MULTICHANNEI  |

|---------------------|------------------------|-----------------|---------------|

| CREDIT              | Intel                  | iSBC            | MULTIMODULE   |

| i                   | IntelBOS               | iSBX            | Plug-A-Bubble |

| I <sup>2</sup> -ICE | Intelevision           | iSDM            | PROMPT        |

| ICE                 | inteligent Identifier  | iSXM            | Ripplemode    |

| iCS                 | inteligent Programming | Library Manager | RMX/80        |

| iDIS                | Intellec               | MCS             | RUPI          |

| iLBX                | Intellink              | Megachassis     | System 2000   |

| im                  | iOSP                   | MICROMAINFRAME  | UPI           |

| iMMX                | iPDS                   | MULTIBUS        |               |

Copyright 1983, Intel Corporation

Printed in U.S.A./OM-006/3K/0283/AP

#### **PREFACE**

The iLBX bus is one of the subsidiary buses within the overall Multibus Interface System. The iLBX bus is stand-alone to the extent that its interface and protocol do not require the existence of the general purpose Multibus interface or any of the other subsidiary buses. The iLBX bus uses the form factor of the Multibus P2 connector and imposes restrictions on board designs implementing both the general purpose Multibus interface and the iLBX bus.

This specification describes the operation protocol of the iLBX bus and defines the electrical and mechanical requirements of the iLBX bus. A section of design guideline examples provide additional insight for implementing the iLBX bus in a system. This specification does not duplicate specification information from the Multibus Interface Specification or any of the subsidiary bus specifications. Information on the Multibus interface or a subsidiary bus is provided in the following specifications.

- Intel Multibus® Interface Specification, Order Number: 9800683

- Intel iSBX TM Bus Specification, Order Number: 142686

- Intel Multichannel TM Bus Specification, Order Number: 144330

This specification follows the general guidelines in the "Recommendations on Terminology for IEEE Computer Society Interface Standards" review draft dated September 9, 1981, and revised November 3, 1981, and June 3, 1982. In compliance with the terminology recommendations, this specification use decimal notation when numbering bus lines with bit 0 as the least significant bit. This specification also uses the trailing asterisk to designate active Low signal lines. Where Multibus interface signal names (or subsidiary bus signal names) are used in this specification, these names are converted to comply with the terminology recommendations. For example, the Multibus address extension line ADR14/ is listed in this specification as ADR20\*.

# **CONTENTS**

| TITLE SH                                                              | EET NO. | TITLE                               | SHEET NO.                |

|-----------------------------------------------------------------------|---------|-------------------------------------|--------------------------|

| 1. Introduction                                                       | 7       | 4. Mechanical Specification         | 28                       |

| 1.1 Multibus® Interface Overview                                      | 7       | 4.1 Introduction                    |                          |

| 1.1.1 iSBX <sup>TM</sup> Bus                                          |         | 4.2 iLBX <sup>TM</sup> Bus Form Fa  | ctor 28                  |

| 1.1.2 Multichannel <sup>TM</sup> Bus                                  | 7       | 4,2.1 Connector Loca                | ations and Board         |

| 1.1.3 iLBX <sup>TM</sup> Bus                                          | 8       | Outline                             |                          |

| 1.2 iLBX <sup>TM</sup> Bus General Description                        | 8       | 4.2.2 Pin Numbering                 | Convention 31            |

| 1.2 IEBA Bus General Besemption 111111                                |         | 4.2.3 Component La                  | yout Considerations 31   |

| 2. Functional Description                                             | 9       | 4.2.4 iLBX <sup>TM</sup> Bus Pir    | Assignments 31           |

| 2.1 Introduction                                                      | 9       | 4.2.5 Connector Key                 | Slot 31                  |

| 2.2 Notation Conventions                                              | 9       | 4 3 Battery Back-Up and             | Front Panel Interface 33 |

| 2.3 iLBX <sup>TM</sup> Bus Devices                                    | 10      | 4 4 iL RX <sup>TM</sup> Bus Connect | ors and Cabling 34       |

| 2.3.1 Primary Master                                                  |         | 4 4 1 iL BX <sup>TM</sup> Bus Ca    | ble                      |

| 2.3.2 Secondary Master                                                | 11      |                                     | onnectors                |

| 2.3.3 Slave                                                           | 11      |                                     | ble Assembly 37          |

| 2.4 Signal Line Descriptions                                          | . 11    | 4.4.5 ILBA Bus Cu                   | tole resembly            |

| 2.4.1 Address and Data Lines                                          | 12      |                                     |                          |

| 2.4.1.1 Data Lines (DB15 - DB0)                                       | 12      |                                     |                          |

| 2.4.1.1 Data Lines (DB13 - DB6) (1.1.2 Address Lines (AB0 - AB23)     |         |                                     | ystem Applications 37    |

| 2.4.1.2 Address Ellies (ABO - AB23)                                   |         |                                     |                          |

| 2.4.1.3 Transfer rarry (Tr Akw)                                       | 13      | 5.2 Primary Master Desi             | gn Example — 16-Bit 39   |

| 2.4.2 Control Lines                                                   | 13      | 5.2.1 Address Decod                 | le 39                    |

| 2.4.2.1 Read-Not-write (R/W)<br>2.4.2.2 Data Element Select Control L |         | 5.2.2 Data Drivers .                |                          |

|                                                                       |         |                                     | rs 40                    |

| (BHEN)                                                                |         |                                     | ommand Drivers 41        |

| 2.4.3 Command Lines                                                   | 1.4     | 5.2.5 Interface Disab               | oling 41                 |

| 2.4.3.1 Address Strobe (ASTB*)                                        |         |                                     | e Timing 42              |

| 2.4.3.2 Data Strobe (DSTB*)                                           |         |                                     | gn Example — 8-Bit 42    |

| 2.4.3.3 Acknowledge (ACK*)                                            |         | 5.4 Secondary Master De             | esign Example 44         |

| 2.4.4 Bus Access Lines                                                |         | 5.4.1 Bus Request Ci                | ircuit 44                |

| 2.4.4.1 Lock (LOCK*)                                                  | 16      |                                     | Acknowledge Delay        |

| 2.4.4.2 Secondary Master Request                                      |         | Circuit                             |                          |

| (SMRQ*)                                                               | 1/      |                                     | Conversion 45            |

| 2.4.4.3 Secondary Master Acknowledg                                   | ge      |                                     | le 46                    |

| (SMACK*)                                                              |         |                                     | Circuit 46               |

| 2.5 iLBX <sup>TM</sup> Bus Pin Assignments                            | 17      |                                     | Acknowledge Delay        |

| 2.6 iLBX <sup>TM</sup> Bus Operation Protocol                         |         |                                     |                          |

| 2.6.1 Bus Access                                                      |         |                                     | siderations 47           |

| 2.6.2 Data Transfer Operations                                        | 19      |                                     | derations 47             |

| 2.6.2.1 Write Data-to-Memory                                          | 20      |                                     | Examples 48              |

| 2.6.2.1.1 Optimized Operation                                         | 20      | 3.0.2 Road 1 mmg =                  |                          |

| 2.6.2.1.2 Non-Optimized Operation                                     | 21      |                                     |                          |

| 2.6.2.1.3 Operation Completion                                        | 22      |                                     | 5.0                      |

| 2.6.2.2 Read Data-From-Memory                                         |         | 6. Levels of Compliance             | 50                       |

| 2.6.2.2.1 Non-Optimized Operation                                     | 23      | 6.1 Introduction                    |                          |

| 2.6.2.2.2 Optimized Operation                                         | 23      | 6.2 Data Path                       |                          |

| 2.6.2.2.3 Operation Completion                                        | 24      | 6.3 Address Path                    |                          |

|                                                                       |         | 6.4 Signal Line Connect             | ions 51                  |

| 3. Electrical Specification                                           | 24      | 6.5 Documentation                   | 52                       |

| 3.1 Introduction                                                      | 24      | 6.6 Compliance Markin               | g 52                     |

| 3.2 Electrical State Relationships                                    |         |                                     |                          |

| 3.3 Environmental Requirements                                        | 25      |                                     |                          |

| 3.4 DC Specifications                                                 | 25      | Appendix A — Signal Line            | e Summary 53             |

| 3.5 Termination                                                       | 25      | A.1 Introduction                    |                          |

| 3.6 AC Specifications                                                 | 25      | A.2 Signal Line Summa               | ry 53                    |

|                                                                       |         | <b>3 3 3 3 3 3 3 3 3 3</b>          |                          |

# **FIGURES**

| TITLE     | SHEET NO                                               | TIT      | LE         | SHEET NO.                                      |   |

|-----------|--------------------------------------------------------|----------|------------|------------------------------------------------|---|

| Figure 1  | Multibus ® Interface System                            | 8 Figure | <u> 12</u> | Typical iLBX <sup>TM</sup> Bus Interface Cable |   |

| Figure 2  | iLBX <sup>TM</sup> Bus Granting Timing Relationship 20 | 0        |            | Assembly 39                                    | ) |

| Figure 3  | Write Data-To-Memory, 16-Bit Transfer                  |          | 13         | Connector Installation 40                      |   |

|           | Timing 2                                               |          |            | Connector Installation 40                      |   |

| Figure 4  | Read Data-From-Memory, 16-Bit Transfer                 |          |            | Interface Circuit Example — 16-Bit Primary     |   |

|           | Timing 2.                                              |          |            | Master                                         | , |

| Figure 5  | iLBX <sup>TM</sup> Bus Data Transfer Timing Chart . 29 |          | 16         | T-State Generator Circuit 45                   |   |

| Figure 6  | iLBX <sup>TM</sup> Bus Control Transfer Timing         |          |            | The 8-Bit Data Transceiver Circuit 47          |   |

|           | Chart 29                                               | 9 Figure |            | Interface Circuit Example — Secondary          |   |

| Figure 7  | Typical Acceptable Waveform 3                          | 1        |            | Master                                         | , |

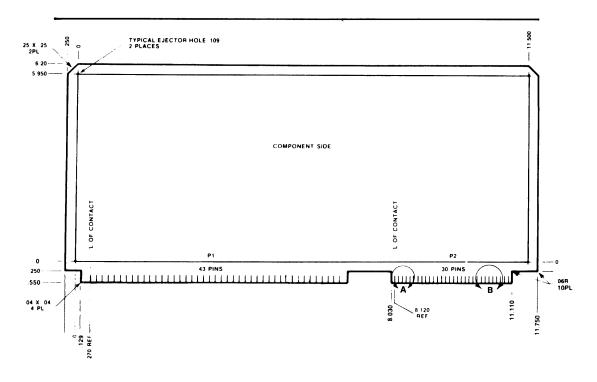

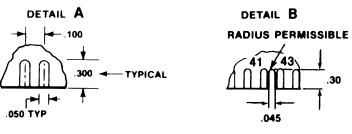

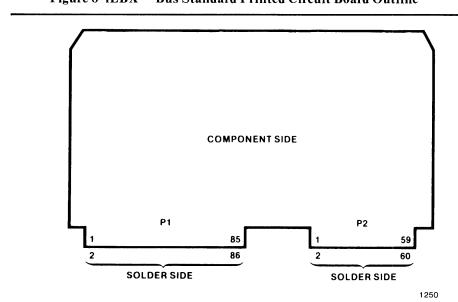

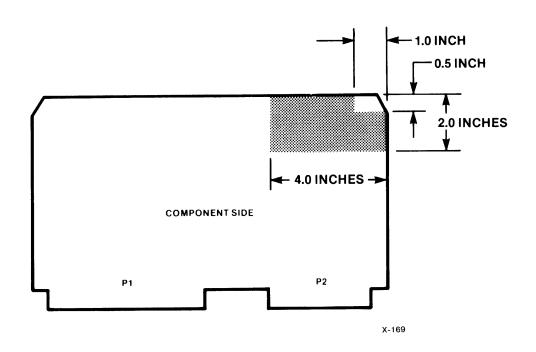

| Figure 8  | iLBX <sup>TM</sup> Bus Standard Printed Circuit Board  |          | : 19       | Interface Circuit Example — Slave 50           |   |

|           | Outline 33                                             |          |            | Read Data Optimization Timing —                |   |

| Figure 9  | iLBX <sup>TM</sup> Bus Connector And Pin Numbering     | _        |            | Basic Example                                  |   |

|           | Conventions 34                                         | 4 Figure | 21         | Read Data Optimization Timing —                |   |

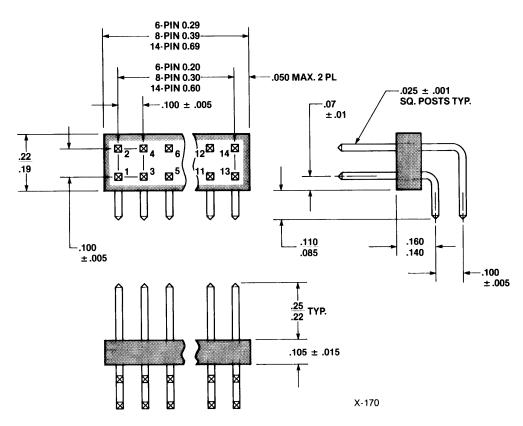

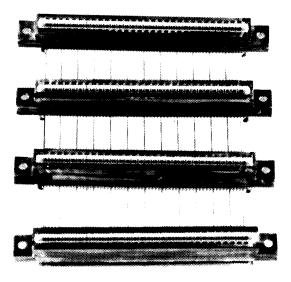

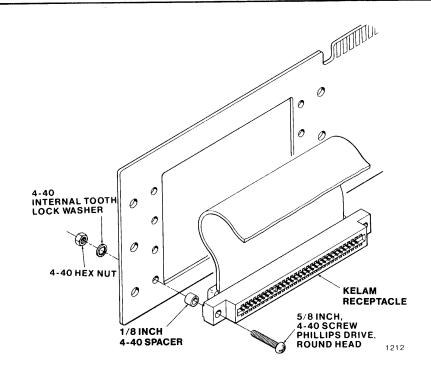

| Figure 10 | Auxiliary (P3) Connector Location Area . 36            | 6        |            | Non-adjustable 52                              |   |

| Figure 11 | Auxiliary Connector Mechanical                         |          | 22         | Read Data Optimization Timing,                 |   |

|           | Specifications                                         | 7        |            | Adjustable 53                                  |   |

# **TABLES**

| Table 2 Table 3 Table 4 Table 5 Table 6 | Notational Summary  16-Bit Data Frame  Element Selection  iLBX <sup>TM</sup> Bus Pin Assignments, P2 Edge  Connector  Notational Summary  DC Specif ations | 13<br>13<br>19<br>24<br>26 | Table 9<br>Table 10<br>Table 11 | iLBX <sup>TM</sup> Bus Pin Assignments, P2 Edge Connector Auxiliary (P3) Connector Pin Assignments Cable And Receptacle Vendors iLBX <sup>TM</sup> Bus Address Range Select Jumpers iLBX <sup>TM</sup> Bus Pin Assignments, P2 Edge Connector | 30<br>4 |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Table 7                                 | iLBX <sup>TM</sup> Bus Timing Parameters                                                                                                                   | 27                         |                                 |                                                                                                                                                                                                                                               | ,       |

#### 1. Introduction

The Local Bus Extension (iLBX) bus is a specialized electrical and mechanical interfacing protocol operating within the overall Multibus interfacing system. The iLBX bus provides local memory expansion which is physically off-board, without loss of execution speed. A typical iLBX installation would have a master iSBC processor board attached to an additional memory board via the iLBX bus lines. Because of the increased execution speed of the iLBX bus, this off-board memory will be used as local on-board memory by the processor board. Up to five boards may use the iLBX bus in one system.

#### 1.1 Multibus® Interface Overview

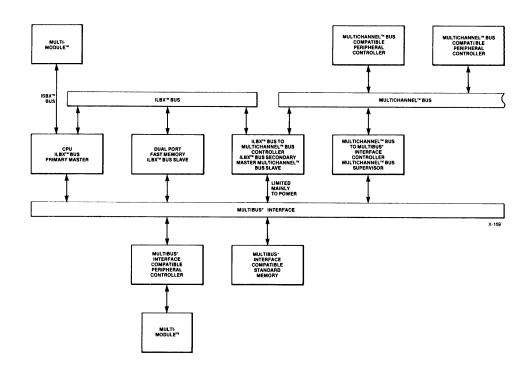

Figure 1 illustrates the overall Multibus interfacing system. The foundation of the Multibus interfacing system is the general purpose Multibus interface, the flexible bus structure used to interface the family of Intel's 80/86 products including both 8- and 16-bit products. The Multibus interface supports both 8- and 16-bit data transfers and direct addressability of up to 16 megabytes of memory. In many systems, the Multibus interface provides all of the required interconnect capability for the system.

As systems grow in complexity and performance, the throughput demands on the interconnect architecture increase. The Multibus interfacing system meets these demands by off-loading specific interconnect needs to the following subsidiary buses:

- iSBX<sup>TM</sup> bus

- Multichannel<sup>TM</sup> bus

- iLBX<sup>TM</sup> bus

In a fully expanded Multibus interface system, the Multibus interface is used mainly for system control and low to medium-speed data transfers.

#### 1.1.1 iSBXTM Bus

Increasing the number of functions residing on each system board attached to the Multibus interface increases the system performance. The improved system performance results because the resident functions are accessed without bus arbitration. The trade-off becomes choosing the resident functions when designing the system board. The iSBX bus extension of the Multibus interfacing system helps reduce the need to make design choices. The special functions are designed onto individual small boards and connected to a system board using the iSBX bus interface. When installed on the system board, the special function operates as though it were residing on the system board. Thus a system designer can have resident on the system boards those special functions most advantageous to his system.

#### 1.1.2 Multichannel<sup>TM</sup> Bus

Reducing the impact of burst-type peripherals (e.g. most disk peripherals) on the Multibus® interface provides a second means of increasing system performance. The actual data transfers from a burst type peripheral can saturate a general purpose interface such as the Multibus interface. Adding more burst-type peripherals to a system often decreases the computing performance of the system. The Multichannel bus extension to the Multibus interfacing system helps reduce the bussaturation problem. The Multichannel bus protocol specifically accommodates burst-type data transfers. The full performance improvement requires use of dual port memory accessed over both the Multichannel bus and the Multibus interface.

Figure 1 Multibus® Interface System

#### 1.1.3 iLBX<sup>TM</sup> Bus

Dramatically increasing the local (on-board) memory resources of a high performance processor provides a third means of increasing system performance. As with other special functions, memory residing on the processor board improves system performance because the processor directly addresses the memory without waiting for bus arbitration. However, there is a physical limitation to the amount of memory that can reside on the processor board. The iLBX bus helps to reduce the physical space limitation. Using the iLBX bus, the additional memory no longer needs to be located on the processor board or on a multimodule attached to the processor board. The full 16 megabytes of memory addressable by the processor can be accessed over the iLBX bus and appear to the processor as though it were resident on the processor board. Dual porting the memory between the iLBX bus and the Multibus interface makes the same memory resources available to other system components.

# 1.2 iLBX<sup>™</sup> Bus General Description

The iLBX bus configuration uses the form-factor of the standard 60-pin Multibus P2 connector. It occupies 56 of the P2 connector pins (55 defined signal lines and one reserved signal line). The four Multibus address extension lines (pins 55 through 58) on the Multibus P2 connector retain the standard Multibus interface functions.

The iLBX bus is designed for direct high-speed Master-Slave data transfers and provides the following features.

- A minimum of two and up to five devices can be connected over the iLBX bus.

- Two (maximum) masters can share the bus, limiting the need for bus arbitration.

- Bus arbitration is asynchronous to the data transfers.

- Slave devices are defined as byte-addressed memory resources.

- Slave device functions are directly controlled from iLBX bus signal lines.

#### 2. Functional Description

#### 2.1 Introduction

The Functional Description defines the various elements of the iLBX bus interface. These elements include descriptions of the device categories using the iLBX bus, the signal line grouping and functions, the timing requirements, and the bus communication protocol.

#### 2.2 Notation Conventions

The general notational conventions used in this manual conform to the notational conventions used in the Multibus Specification. The following paragraphs summarize the notational conventions. The iLBX bus lines are assigned unique names and, for brevity, unique mnemonics. The signal line names are shown with initial capital letters when used in text. The corresponding signal line mnemonics are shown in all capital letters. Signal mnemonics for lines that are Active when electrically High (also called positive true) or Active when either electrically High or Low (the data lines for example) do not have a special terminating character as the last character in the mnemonic. Signal mnemonics for lines Active when electrically Low (also called negative true) have an asterisk (\*) character as the last (terminating) character in the mnemonic.

The descriptions of electrical signal characteristics use the terms High and Low (in initial capital letters) corresponding to the relative voltage level of the signal. The terms true, false, 1, and 0 are avoided to reduce misinterpretation. Thus an Active Low signal is asserted when its relative voltage level is Low. Table 1 relates the electrical signal characteristics to the corresponding logical and state notations. The Example mnemonic, XMPL, illustrates the notational conventions.

The address and data bit numbering scheme used with the iLBX bus has bit 0 as the least significant bit, and decimal numbers are used to identify the lines. Thus, Data line 0 (DB0) carries the least significant bit and Data line 15 (DB15) carries the most significant bit.

**Table 1 Notational Summary**

| 0.0            | NOTATION   |          |                  |  |  |  |

|----------------|------------|----------|------------------|--|--|--|

| SIGNAL<br>NAME | ELECTRICAL | LOGICAL  | STATE            |  |  |  |

| XMPL           | H, High    | 1, True  | Active, Asserted |  |  |  |

|                | L, Low     | 0, False | Inactive         |  |  |  |

| XMPL*          | H, High    | 0, False | Inactive         |  |  |  |

|                | L, Low     | 1, True  | Active, Asserted |  |  |  |

#### 2.3 iLBX<sup>TM</sup> Bus Devices

Three device categories interface to the iLBX bus. The device categories are the following:

- Primary Master

- Secondary Master

- Slave

At most, five devices can be simultaneously attached to the iLBX bus. The set of devices must include a *Primary Master* and one *Slave* device. The remaining three devices are optional and may include additional Slave devices and one *Secondary Master*. The Slave device(s) contain the memory resources used by the Primary Master and the Secondary Master. The combined, directly accessible, memory total for the Slave devices is 16 megabytes.

#### 2.3.1 Primary Master

The Primary Master controls the iLBX bus and manages the Secondary Master access to the Slave memory resources. Every implementation of the iLBX bus must have a device performing all, or an allowed subset, of the Primary Master functions. A maximum of one Primary Master can be attached to the iLBX bus. Typically the system processor board includes the Primary Master function as an on-board function with the iLBX bus as an extension of the Primary Master's on-board local bus.

The Primary Master must perform three specific functions in addition to general iLBX-bus control. The Primary Master must actively drive all iLBX bus signal lines (except Slave Acknowledge and Secondary Master Request) unless it relinquishes signal line control to the Secondary Master. It must provide a +5VDC pull-up termination for those iLBX bus lines requiring termination. It must monitor the Secondary Master Request signal line and release control of the iLBX bus to a Secondary Master for data transfer.

Single-master implementations are allowed where a limited Primary Master does not monitor the Secondary Master Request signal line. When the Primary Master lacks the ability to monitor the Secondary Master Request signal line, a Secondary Master cannot be attached to the iLBX bus.

#### 2.3.2 Secondary Master

The optional Secondary Master provides alternate access over the iLBX bus to the Slave resources. The Secondary Master transfers data over the iLBX bus in the same manner as a Primary Master; however, the Secondary Master must first request control and the Primary Master must acknowledge the request to pass iLBX bus control to the Secondary Master. The specified maximum of two masters (one Primary Master and one Secondary Master) reduces bus arbitration to a simple request and acknowledgement process. Bus control arbitration occurs asynchronously to the data transfers.

When the Secondary Master controls the iLBX bus, the Secondary Master must actively drive all signal lines (except Slave Acknowledge and Secondary Master Acknowledge) until it returns signal line control to the Primary Master. The Secondary Master must not provide additional signal line termination.

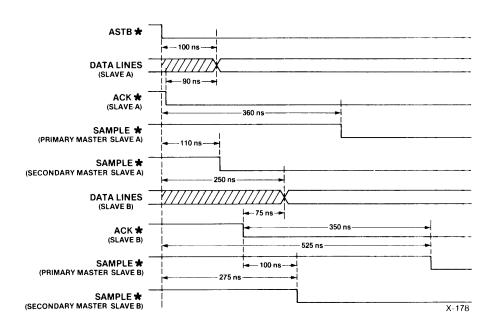

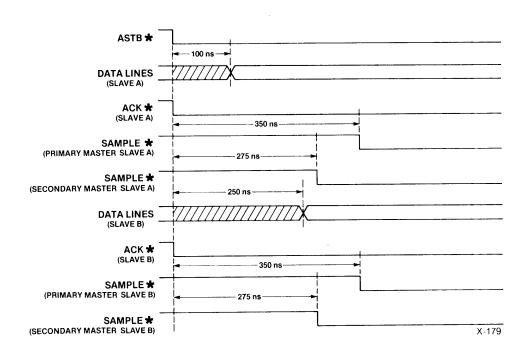

The Secondary Master must provide a means for varying the timing of its response to the Slave Acknowledge. The iLBX bus data-transfer-timing allows closely coupling (optimizing) the Slave device's data-transfer rate to the Primary Master's data-transfer rate. When the close coupling is implemented, part of the Slave device's access overhead occurs concurrently with the Primary Master's acknowledge acceptance overhead. When implementing the iLBX bus in a system, the Secondary Master's acknowledge acceptance timing must be adjusted to match the Primary Master's acknowledge acceptance timing to assure reliable data transfers.

#### 2.3.3 Slave

The Slave device(s) contain the memory resources used by the Primary Master and the Secondary Master. The combined, directly accessible, memory total for the Slave devices is 16 megabytes. Any given iLBX bus implementation is limited to a maximum of four Slave devices.

The Slave devices must continually monitor the iLBX bus Address lines and the Address Strobe line. The Slave device detecting an assigned memory address on the Address lines assumes selection, and data transfer initiation occurs when the Slave device detects the Address Strobe signal. The iLBX bus protocol requires a positive response to complete any selection, and Slave devices must be able to actively drive the Slave Acknowledge line.

The iLBX-bus data-transfer-timing allows closely coupling (optimizing) the Slave device's data-transfer rate to the Primary Master's data-transfer rate. When the close coupling is implemented, part of the Slave device's access overhead occurs concurrently with the Primary Master's acknowledge acceptance overhead. Use of the optimized operation is optional, and a Slave device designed to implement optimized operation must provide a means for varying the timing of its Slave Acknowledge. Refer to the timing specifications and timing adjustment requirements in the hardware reference manual for iLBX bus compatible devices.

#### 2.4 Signal Line Descriptions

The following four signal line categories make up the physical structure of the iLBX bus interface:

- address and data lines

- control lines

- command lines

- bus access lines

#### 2.4.1 Address and Data Lines

The bus has 16 data lines and 24 address lines.

**2.4.1.1 DATA LINES (DB15 - DB0).** All 8-bit and 16-bit data transfers between the active bus master and the selected Slave device use the 16 bi-directional data lines exclusively. The 16-bit data transfers use all 16 data lines. The 8-bit data transfers within the 16-bit data frame use the appropriate low-order (DB7 through DB0) or high-order (DB15 through DB8) data lines.

Byte data is transferred between 8-bit devices using data lines DB7 through DB0. The state of unused data lines during 8-bit data transfers is undefined.

The general data signal line implementation specifications are as follows.

- The data lines require tri-state drivers and any iLBX bus device can drive the data lines.

- The data lines are positive true lines and only the *transmitting* device (master or slave) drives the lines. The *receiving* device and all inactive devices must hold their data line drivers in the high-impedance state during the data transfer.

- **2.4.1.2** Address Lines (AB0 AB23). The active bus master uses 24 address lines to select a Slave device and to specify a location in memory. The use of 24 address lines provides the ability to address 16-megabytes of memory space.

Only the active bus master drives the address lines in the iLBX bus. The condition of the address lines during the data time is undefined, and the Slave device must store (latch-in) the address information when the Slave device detects the Address Strobe signal (see Section 2.4.3.1).

The general address signal line implementation specifications are as follows.

- The address lines are positive true lines.

- Primary Masters and Secondary Masters must provide tri-state drivers for the address lines. Limited Primary Masters that do not share the iLBX bus with a Secondary Master can use standard TTL drivers with drive characteristics comparable to the specified tri-state driver.

- 2.4.1.3 Transfer Parity (TPAR\*). The Transfer Parity signal is an optional line and is available to improve data-transfer integrity. The Transfer Parity operates as an additional data line with identical timing requirements. The iLBX bus uses odd parity defined as follows: when there is an even number of one bits in the transfer element (byte, 16-bit word), the transmitting device drives the Transfer Parity line Low. Because the state of unused data lines is undefined, parity generation and checking is limited to the active data lines for the transfer element used. The iLBX bus does not provide a means for reporting a detected transfer parity error.

The general Transfer Parity signal line implementation specifications are as follows.

- The option must be available on all devices, both masters and slaves, if a transfer parity option is to be used on the iLBX bus.

- Any device designed with the parity option must provide a means for disabling recognition of a transfer parity error.

- All masters and Slave devices with the parity option must provide a tri-state driver for the Parity line.

- Only the transmitting device (master or slave) drives the Parity line. The receiving device must sample the Parity line and all inactive devices must hold their parity line driver in the high-impedance state during the data transfer.

#### 2.4.2 Control Lines

The active bus master specifies the data transfer parameters to the selected Slave device by using the three control lines.

**2.4.2.1 Read-Not-Write (R/W).** The active bus master controls the direction of data transfer with the Read-Not-Write line. When driven Low, the active bus master transmits the data and the selected slave device receives the data. Driving the Read-Not-Write line High reverses the transfer direction.

The Read-Not-Write signal need not remain valid throughout the data transfer operation. Therefore, the Slave device must store (latch-in) the state of the Read-Not-Write signal line when the Slave device detects the leading (falling) edge of the Address Strobe (see Section 2.4.3.1).

The general Read-Not-Write signal line implementation specifications are as follows.

- Primary Masters and Secondary Masters must provide a tri-state driver for the Read-Not-Write line. Limited Primary Masters that do not share the iLBX bus with a Secondary Master can use a standard TTL driver with drive characteristics comparable to the specified tri-state driver.

- Only the active bus master drives the Read-Not-Write line. The inactive master must hold the read-not-write line-driver in the high-impedance state.

Table 2 16-Bit Data Frame

| BITS 15 - 8 | BITS 7 - 0 |

|-------------|------------|

| HIGH BYTE   | LOW BYTE   |

| wo          | RD         |

**Table 3 Element Selection**

| ELEMENT   | SIGNAL & LEVEL |      |  |  |  |

|-----------|----------------|------|--|--|--|

|           | BHEN           | ABO  |  |  |  |

| HIGH BYTE | HIGH           | HIGH |  |  |  |

| LOW BYTE  | LOW            | LOW  |  |  |  |

| RESERVED  | LOW            | нідн |  |  |  |

| WORD      | нідн           | LOW  |  |  |  |

**2.4.2.2 Data Element Select Control Line (BHEN).** The iLBX bus data transfers take place within an overall data frame that is limited by the iLBX bus configuration. Within the data frame limits, transfer of an 8-bit (byte) and 16-bit (word) data element is allowed. The particular size data element and its location within a data frame must be specified to the slave device by the active bus master. Refer to Table 2 for element size and location within a sixteen bit data frame.

The active bus master controls the type of data transfer (8-bit or 16-bit) using the Byte High Enable (BHEN) element select line and the low-order address bit (AB0). The four signal-level combinations of these two lines specify both the element size and the element location within the data frame. The signal-level combinations are shown in Table 3.

The BHEN signal is not required to remain valid throughout the data transfer operation. The Slave device must store (latch-in) the configuration of the signal line when the Slave device detects the Address Strobe signal.

The general BHEN signal line implementation specifications are as follows.

- Primary Masters and Secondary Masters must provide tri-state drivers.

Limited Primary Masters that do not share the iLBX bus with a Secondary Master can use a standard TTL driver with drive characteristics comparable to the specified tri-state driver.

- The Byte High Enable line must be implemented on all masters and Slave devices.

- Only the active bus master drives BHEN. The inactive master must hold the BHEN line driver in the high-impedance state.

#### 2.4.3 Command Lines

The active bus master and the selected Slave device use three command lines to initiate, control, and terminate a data transfer.

**2.4.3.1** Address Strobe (ASTB\*). The active bus master drives the Address Strobe line Low to initiate a data transfer cycle. The control line and address line signal levels must be valid prior to the bus master driving the Address Strobe line Low. The Slave device(s) decodes the address to determine if it is selected. The selected Slave device must store the control and address information at the leading (falling) edge of the Address Strobe signal. The selected Slave device then proceeds with the data transfer.

The general Address Strobe signal line implementation specifications are as follows.

- Primary Masters and Secondary Masters must provide a tri-state driver for the Address Strobe line. Limited Primary Masters that do not share the iLBX bus with a Secondary Master can use a standard TTL driver with drive characteristics comparable to the specified tri-state driver.

- Only the active bus master drives the Address Strobe line. The inactive master must hold its address strobe line driver in the high-impedance state.

**2.4.3.2 Data Strobe (DSTB\*).** The active bus master drives the Data Strobe line Low to set-up the actual transfer of data. The active bus master drives the Data Strobe line High after the data transfer is completed to terminate the data transfer cycle. The meaning of the Data Strobe signal varies depending on the direction of data transfer, from master to slave (write) or from slave to master (read).

During a read operation, the active bus master indicates when it is ready to accept data from the selected slave device by driving the Data Strobe line Low. The active bus master must put its data line (DB15 - DB0) tri-state drivers in the high-impedance state before driving the Data Strobe line Low. The selected slave device starts driving the required lines after detecting the leading (falling) edge of the Data Strobe signal.

During a write operation, the active bus master indicates the availability of data for the selected slave device by driving the Data Strobe line Low. The active bus master is allowed a set-up time for the data lines after it drives the Data Strobe line Low. The selected slave device samples the data after first detecting the leading (falling) edge of the Data Strobe signal plus the specified data set-up time.

The general Data Strobe signal line implementation specifications are as follows.

- Primary Masters and Secondary Masters must provide a tri-state driver for the Data Strobe line. Limited Primary Masters that do not share the iLBX bus with a Secondary Master can use standard a TTL driver with drive characteristics comparable to the specified tri-state driver.

- Only the active bus master drives the Data Strobe line. The inactive master must hold its Data Strobe line driver in the high-impedance state.

- The active bus master must hold the Data Strobe line Low for the specified minimum time after it receives the Acknowledge signal from the selected slave device.

**2.4.3.3** Acknowledge (ACK\*). The selected slave device responds to the active bus master by driving the Acknowledge line low.

The Acknowledge signal timing requirements allow flexibility. The flexibility allows overlapping the internal operation overhead of the selected master with the bus set-up time of the selected slave device. Thus during a read operation, the selected slave device can drive the Acknowledge line Low prior to completing bus set-up of the data lines. The slave device must allow sufficient time to complete bus set-up before the active bus master internally recognizes and responds to the Acknowledge signal.

During a write operation, the Slave device can drive the Acknowledge line Low any time after the leading (falling) edge of the Address strobe provided it can accept the data from the active bus master within the specified time and the active bus master meets the optimized write timing requirements. Overlapping bus set-up time with the Primary Master's internal overhead improves the data transfer performance on the iLBX bus.

The Slave device should provide a means for varying its Acknowledge response time for read operations. The variable Acknowledge timing allows optimizing the data-transfer timing. A Slave device that does not provide a means for adjusting the Acknowledge timing can not drive the Acknowledge line Low before it drives the data lines.

The Slave device should provide a means for including or excluding the Data Strobe signal state as a prerequisite for driving the Acknowledge line Low to allow for optimized or non-optimized write operation. The exclusion of the Data Strobe going Low as a prerequisite allows the close coupling and overhead overlap to optimize the write data transfer operation. A Slave device that does not provide the choice of including the Data Strobe qualification must wait for the leading edge of the Data Strobe before driving the Acknowledge line Low.

The general Acknowledge signal line implementation specifications are as follows.

- Each Slave device must provide an open collector driver for the Acknowledge line.

- When a master on the iLBX bus cannot meet the optimized timing requirements, the Slave device(s) must be configured for non-optimized operation.

- Both Primary and Secondary Masters should provide a timer to force an Acknowledge locally and avoid a system lock-up if the addressed Slave device fails to respond. The iLBX bus does not provide a means for reporting a slave response failure.

#### 2.4.4 Bus Access Lines

The Primary Master and the Secondary Master use the three bus access lines to transfer bus control between the master devices and to control alternate access to dual ported memory on a Slave device.

2.4.4.1 Lock (LOCK\*). The active bus master restricts access through the alternate port to dual port RAM memory on a Slave device by driving the Lock line Low, By locking the alternate access, the active bus master assures that shared data stored in the Slave device is not disturbed until the active bus master completes its use of the data.

The Slave device accepts the Lock signal in conjunction with a data transfer and the Slave device remains locked until Lock signal goes inactive. The Slave device must be selected by the active bus master before the Slave device accepts the state of the Lock signal. To lock a given data transfer cycle to the following data transfer cycle, the active bus master must drive the Lock signal Low before the end of the first data transfer cycle (before the trailing edge of the Data Strobe signal) and keep the Lock signal active until after the start of the last locked data transfer cycle (after the leading edge of the Address Strobe).

Dual ported iLBX Slave devices that recognize both the iLBX bus Lock and the Multibus interface present special design considerations. When alternate access to dual port memory can be locked from either port, the system can become deadlocked through access contention to the dual port memory. By limiting the lock application to the selected Slave device, the possibility of an access contention deadlock can be eliminated. However, the lock limitation allows the possibility of corrupting data if the logical memory in use crosses the physical boundary between two Slave devices. Because the logical memory space crosses the physical boundary, only part of the logical memory space is actually locked at any one time. A Slave device designed to recognize the iLBX bus Lock signal any time Lock is active avoids any risk of corrupting memory but risks system deadlock. A Slave device designed with the type of recognition optional allows the system environment to dictate which form of Lock recognition to use.

The general Lock signal line implementation specifications are as follows.

- Primary Masters and Secondary Masters must provide a tri-state driver for the Lock line. Limited Primary Masters that do not share the iLBX bus with a Secondary Master can use a standard TTL driver with drive characteristics comparable to the specified tri-state driver.

- Only the active bus master drives the Lock line. The inactive master must hold the Lock line driver in the high-impedance state.

- Slave devices with single ported memory (iLBX bus only) and Slave devices with ROM memory need not recognize Lock.

- The selected dual ported slave device must recognize the Lock signal. The selected slave device must exclude alternate access until the Lock signal is driven High.

- **2.4.4.2 Secondary Master Request (SMRQ\*).** The Secondary Master requests use of the iLBX bus from the Primary Master by driving the Secondary Master Request line low. Once the Secondary Master has control of the iLBX bus and completes its bus operation, it returns control of the iLBX bus to the Primary Master by driving the Secondary Master Request line High.

The Secondary Master must provide a TTL driver for the Secondary Master Request line and the Primary Master must provide a TTL receiver.

2.4.4.3 Secondary Master Acknowledge (SMACK\*). The Primary Master allows use of the iLBX bus by the Secondary Master by driving the Secondary Master Acknowledge line Low after the Secondary Master drives the Secondary Master Request line Low. The Primary Master must continue to drive the Secondary Master Acknowledge line Low until after the Secondary Master drives the Secondary Master Request line High. When making the bus control transfer from the Primary Master to the Secondary Master, the Primary Master first grants bus use to the Secondary Master and then must put all tri-state drivers in the high-impedance state. When making the bus control transfer from the Secondary Master to the Primary Master, the Secondary Master first puts all tri-state drivers in the high-impedance state and then returns bus use to the Primary Master. The Primary Master must provide a TTL driver for the Secondary Master Acknowledge line and the Secondary Master must provide a TTL receiver.

### 2.5 iLBX<sup>TM</sup> Bus Pin Assignments

The iLBX-bus configuration uses the form-factor of the standard 60-pin Multibus P2 connector and occupies 56 of the P2 connector pins. Table 4 lists the iLBX bus pin assignments for the 60-pin P2 edge connector. The four Multibus address extension lines (pins 55 through 58 on the P2 connector) retain the standard Multibus interface functions.

# 2.6 iLBX<sup>TM</sup> Bus Operation Protocol

The operation protocol for the iLBX bus includes the following three main operations:

- bus control access

- write data to memory

- read data from memory

The iLBX bus operations use asynchronous protocol with positive responses. Thus, specified signal level interactions must occur during an operation for the operation to proceed. Most iLBX bus timing parameters list only a minimum time or a maximum time for efficient use of the asynchronous protocol. The iLBX bus timing specifies a minimum abort time of 1 millisecond, within which a given bus transaction should be completed.

The following sections describe the different operations and the iLBX bus signal lines involved in each type of bus operation. The data-transfer operation descriptions cover the differences between 8-bit and 16-bit data transfers.

#### 2.6.1 Bus Access

The iLBX bus uses a request and acknowledgement process to pass control between the two masters. A maximum of two masters can share the iLBX bus access to memory.

The specified maximum of two masters (one Primary Master and one Secondary Master) reduces bus arbitration to a simple request and acknowledgement process. Bus control arbitration occurs asynchronously to the data transfers.

The Primary Master controls bus access on the iLBX bus. A Primary Master must monitor the Secondary Master Request line and drive the Secondary Master Acknowledge line. The Secondary Master must drive the Secondary Master Request line and monitor the Secondary Master Acknowledge line. An iLBX bus master device designed to operate as either a Primary or a Secondary Master must be exclusively configured as one or the other when implementing the iLBX bus.

The Primary Master assumes control of the iLBX bus as the default configuration for iLBX bus control. The Secondary Master must drive the Secondary Master Request line High and the Primary Master must drive the Secondary Master Acknowledge line High during system initialization to set the default control configuration.

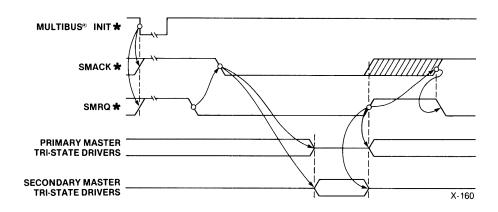

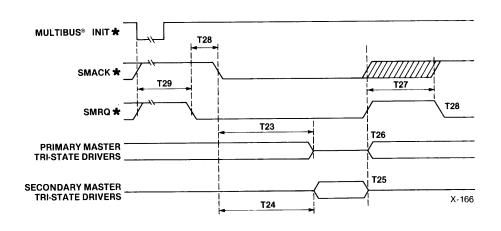

Following initialization, the Secondary Master requests control of the iLBX bus by initiating the transfer process. The bus access timing is illustrated in Figure 2. The Secondary Master drives the Secondary Master Request line Low indicating the need to control the bus. The Secondary Master can drive the request line Low anytime. The time to surrender control of the iLBX bus depends on the design implemented for the Primary Master. The time the Primary Master can retain control of the iLBX bus is not specified. Typically, the Primary Master releases control of the iLBX bus immediately if a data transfer is not in progress. When the Primary Master is actively transferring data, it retains control of the iLBX bus until completing the data transfer(s). The Primary Master relinquishes control of the iLBX bus by driving the Secondary Master Acknowledge line low. The Primary Master is allowed a maximum of 35 ns after driving the Acknowledge line Low to put its tri-state drivers in the high-impedance state. The Secondary Master must wait a minimum of 35 ns after receipt of the Acknowledge signal before enabling its tri-state drivers out of the high-impedance state.

The Secondary Master retains iLBX bus control until it completes the data transfer operation(s). The Secondary Master retains control by continuing to drive the Secondary Master Request line low. The time the Secondary Master can retain control of the iLBX bus is not specified. This allows the Secondary Master the option of making a series of data transfers without returning control of the bus to the Primary Master; however, the Secondary Master typically surrenders control of the iLBX bus after completing the data transfer(s). The Secondary Master surrenders control of the iLBX bus by driving the Secondary Master Request line High. The Secondary Master must put its tri-state drivers in the high-impedance

Table 4 iLBX<sup>TM</sup> Bus Pin Assignments, P2 Edge Connector

|     | СОМ          | PONENT SIDE                           |     | SOL          | DER SIDE                              |

|-----|--------------|---------------------------------------|-----|--------------|---------------------------------------|

| PIN | SIGNAL       | SIGNAL NAME                           | PIN | SIGNAL       | SIGNAL NAME                           |

| 1   | DB0          | DATA LINE 0                           | 2   | DB1          | DATA LINE 1                           |

| 3   | DB2          | DATA LINE 2                           | 4   | DB3          | DATA LINE 3                           |

| 5   | DB4          | DATA LINE 4                           | 6   | DB5          | DATA LINE 5                           |

| 7 9 | DB6<br>GND   | DATA LINE 6<br>GROUND                 | 8   | DB7<br>DB8   | DATA LINE 7<br>DATA LINE 8            |

| 11  | DB9          | DATA LINE 9                           | 12  | DB10         | DATA LINE 10                          |

| 13  | DB11         | DATA LINE 11                          | 14  | DB12         | DATA LINE 12                          |

| 15  | DB13         | DATA LINE 13                          | 16  | DB14         | DATA LINE 14                          |

| 17  | DB15         | DATA LINE 15                          | 18  | GND          | GROUND                                |

| 19  | ABO          | ADDRESS LINE 0                        | 20  | AB1          | ADDRESS LINE 1                        |

| 21  | AB2          | ADDRESS LINE 2                        | 22  | AB3          | ADDRESS LINE 3                        |

| 23  | AB4          | ADDRESS LINE 4                        | 24  | AB5          | ADDRESS LINE 5                        |

| 25  | AB6          | ADDRESS LINE 6                        | 26  | AB7          | ADDRESS LINE 7                        |

| 27  | GND          | GROUND                                | 28  | AB8          | ADDRESS LINE 8                        |

| 29  | AB9          | ADDRESS LINE 9                        | 30  | AB10         | ADDRESS LINE 10                       |

| 31  | AB11<br>AB13 | ADDRESS LINE 11 ADDRESS LINE 13       | 32  | AB12<br>AB14 | ADDRESS LINE 12<br>ADDRESS LINE 14    |

| 35  | AB15         | ADDRESS LINE 15                       | 36  | GND          | GROUND                                |

| 37  | AB16         | ADDRESS LINE 16                       | 38  | AB17         | ADDRESS LINE 17                       |

| 39  | AB18         | ADDRESS LINE 18                       | 40  | AB19         | ADDRESS LINE 19                       |

| 41  | AB20         | ADDRESS LINE 20                       | 42  | AB21         | ADDRESS LINE 21                       |

| 43  | AB22         | ADDRESS LINE 22                       | 44  | AB23         | ADDRESS LINE 23                       |

| 45  | GND          | GROUND                                | 46  | ACK*         | SLAVE<br>ACKNOWLEDGE                  |

| 47  | BHEN         | BYTE HIGH ENABLE                      | 48  | R/W          | READ NOT WRITE                        |

| 49  | ASTB*        | ADDRESS STROBE                        | 50  | DSTB*        | DATA STROBE                           |

| 51  | SMRQ*        | SECONDARY MASTER REQUEST              | 52  | SMACK*       | SECONDARY MASTER ACKNOWLEDGE          |

| 53  | LOCK*        | ACCESS LOCK                           | 54  | GND          | GROUND                                |

| 55  | ADR22*       | MULTIBUS ADDRESS<br>EXTENSION LINE 22 | 56  | ADR23*       | MULTIBUS ADDRESS<br>EXTENSION LINE 23 |

| 57  | ADR20*       | MULTIBUS ADDRESS EXTENSION LINE 20    | 58  | ADR21*       | MULTIBUS ADDRESS EXTENSION LINE 21    |

| 59  |              | RESERVED                              | 60  | TPAR*        | TRANSFER PARITY                       |

state before driving the request line High. The Primary Master can enable its tristate drivers out of the high-impedance state when the request signal goes High. Concurrently, the Primary Master should drive the Secondary Master Acknowledge line High. After releasing control of the iLBX bus, the Secondary Master must detect the Secondary Master Acknowledge going High before it can again drive the Secondary Master Request line Low.

#### 2.6.2 Data Transfer Operations

The data transfer operations all take place between the active bus master and the selected slave device. Because bus control-access occurs asynchronously to data transfers, it is not mentioned in the data transfer operation descriptions. Both types of data transfer operations, write and read, are similar with the main difference being the device that places the data on the iLBX bus data lines. Both write and read data transfers allow for both optimized and non-optimized operation. The optimized operation imposes additional timing requirements and considerations.

Figure 2 iLBX<sup>TM</sup> Bus Granting Timing Relationship

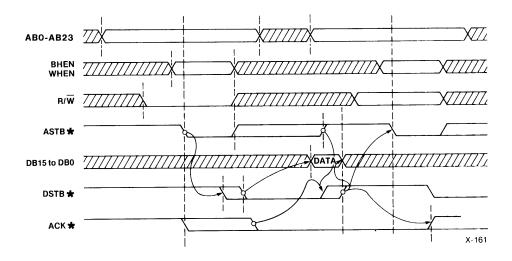

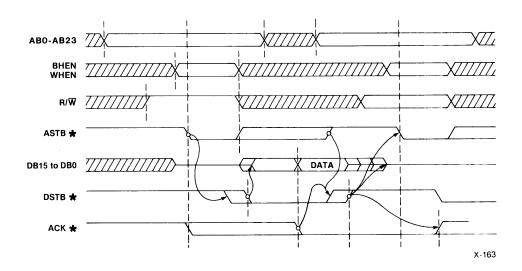

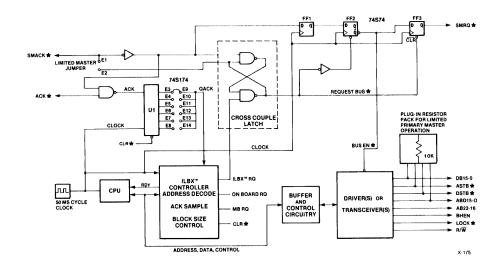

**2.6.2.1 Write Data-To-Memory.** The description of the write data-to-memory operation assumes full completion of any previous data transfer operation before the start of the write operation. The description also assumes the same master device is making another data transfer immediately following the operation described. The subsequent operation could be either read or write and is included here to show the operation to operation timing relationships. The active bus master could be either the Primary Master or the Secondary Master with the same resulting operation. Figure 3 illustrates the optimized 16-bit write data-to-memory timing relationships. The non-optimized write data-to-memory timing uses fixed signal sequences, described in the text, to assure a valid data transfer.

The active bus master initiates the write data-to-memory operation by placing the memory address on the address lines and a control configuration on the control lines. The active bus master must drive the various lines for the specified minimum set-up times before driving the Address Strobe line Low. The selected slave device stores the address information, including the data element selection information, when it detects the leading (falling) edge of the Address Strobe.

2.6.2.1.1 Optimized Operation. All devices attached to the iLBX bus must meet the additional timing requirements for optimized operation to implement optimized operation. The optimized write data-to-memory operation depends the master(s) meeting the specific maximum timing requirements from the leading edge of the Address Strobe signal. The active bus master must provide valid data a maximum of 80 ns from the leading edge of the Address Strobe signal and it must drive the Data Strobe line Low a maximum of 95 ns after the leading edge of the Address Strobe to meet the optimized operation timing requirements.

Figure 3 Write Data-To-Memory, 16-Bit Transfer Timing Relationship

Because the optimized operation timing specifies a data valid time relative to the leading edge of the Address Strobe, the Slave device can drive the Acknowledge line Low anytime after the leading edge of the Address Strobe, provided the Slave device can accept the data from the active bus master within the next 80 ns.

The master device must wait for the Acknowledge before completing the data transfer. The time coupling between the slave device and the master requires the master wait until the selected slave drives the Acknowledge line Low, and then the master must wait an additional 80 ns before driving the Data Strobe line High to complete the data transfer. If the Acknowledge is not received within 1 millisecond, the master can abort the operation by driving the Data Strobe line high.

2.6.2.1.2 Non-Optimized Operation. The non-optimized write data-to-memory operation is used when the master(s) can not meet the specific maximum timing requirements from the leading edge of the Address Strobe signal. For the nonoptimized write data-to-memory operation, the leading (falling) edge of the Data Strobe becomes the critical timing element. The active bus master must now delay driving the Data Strobe line Low until it can provide valid data within 45 ns after the leading edge of the Data Strobe. The selected Slave device is restricted from pre-acknowledging the Data Strobe, and the Slave device must wait until the leading edge of the Data Strobe before driving the Acknowledge line, ACK\*, Low. It can drive the Acknowledge line Low anytime after the leading edge of the Data Strobe provided it can accept the data from the active bus master within the next 80 ns.

**DOCUMENT NUMBER**

145695

The master device must wait for the Acknowledge before completing the data transfer. The time coupling between the slave device and the master requires the master wait until the selected slave drives the Acknowledge line Low, and then the master must wait an additional 80 ns before driving the Data Strobe line High to complete the data transfer. If the Acknowledge is not received within 1 millisecond, the master can abort the operation by driving the Data Strobe line high.

**2.6.2.1.3 Operation Completion.** The active master device completes the write data-to-memory operation by driving the Data Strobe line High.

When the write data-to-memory transfer is a single event transfer, the active master stops driving the data and address lines. The selected Slave stops driving the Acknowledge line and internally goes to the deselected state.

For sequential cycles of write data-to-memory operation, the active bus master can start address set-up for the next data transfer before driving the Data Strobe line High. The amount of data transfer overlap is limited by the minimum time of 25 ns from the rising edge of the Data Strobe to the falling edge of the next Address Strobe.

The overlap provides a potential cycle time of 105 ns per data transfer or a transfer rate of 9.5 MHz. Assuming 16-bit transfers, the resulting throughput is approximately 19 megabytes per second.

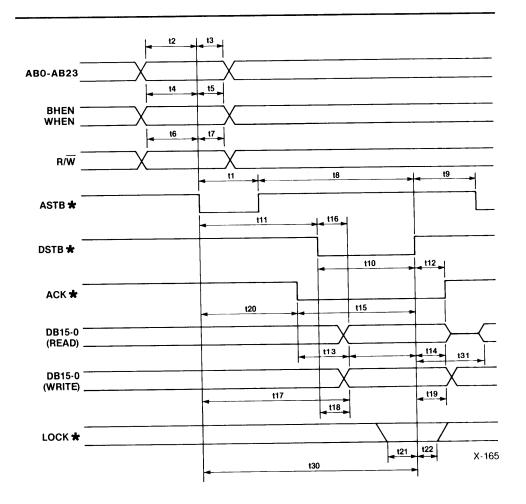

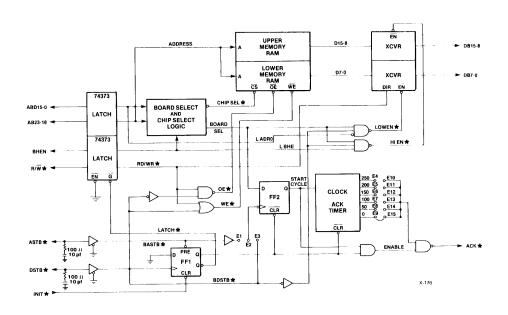

**2.6.2.2 Read Data-From-Memory.** The description of the read data-from-memory operation assumes full completion of any previous data transfer operation before the start of the read operation. The description also assumes successive data transfers by a single master device. The active bus master could be either the Primary Master or the Secondary Master with the same resulting operation. The read data-from-memory operation uses roughly the same timing relationships as the write data-to-memory. The level of the Read-Not-Write signal and the device driving the data lines constitute the main differences between the two operations.

The description of the read data-from-memory operation includes the special considerations for optimizing the data transfer rate between the active bus master and the selected slave. Because the active bus master retains control of the data lines in the write data-to-memory operation, the bus master is the key device in determining the level of data transfer performance. However, during the read data-from-memory operation, the active bus master surrenders control of the data lines to the Slave device for part of the operation. Thus, the level the cooperation between the active bus master and the selected Slave is the key element in determining the level of data transfer performance. Figure 4 illustrates the optimized 16-bit read data-from-memory timing relationships. The non-optimized read data-from-memory timing uses fixed signal sequences, described in the text, to assure a valid data transfer.

The active bus master initiates the read data-from-memory operation by placing the memory address on the address lines and a control configuration on the control lines. The active bus master must drive the various lines for the specified minimum set-up times before driving the Address Strobe line Low. The selected slave device stores the address information, including the data element selection information, when it detects the leading (falling) edge of the Address Strobe.

Figure 4 Read Data-From-Memory, 16-Bit Transfer Timing

The selected slave then drives the Acknowledge line, ACK\*, Low anytime after the leading edge of the Address Strobe signal. When the selected slave device drives the Acknowledge line Low, it must meet the timing coupling requirements of the active master device and present valid data on the data lines before the active master device samples the data lines.

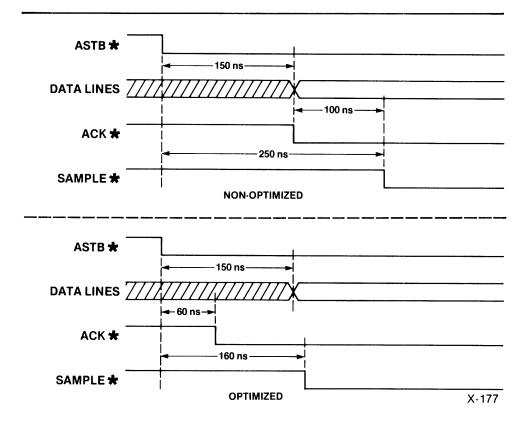

2.6.2.2.1 Non-Optimized Operation. The non-optimized read data-from-memory operation is used when a Slave device does not have variable Acknowledge to read data valid timing. For the non-optimized read data-from-memory operation, the selected Slave device must have data valid before driving the Acknowledge line Low. Because the leading edge of Data Strobe signals the selected Slave device that it can start driving the data lines, in non-optimized mode the selected Slave device must also wait for the Data Strobe before driving the Acknowledge line low.

A minimum of 80 ns after detecting the Acknowledge line Low, the active bus master completes the non-optimized read data-from-memory operation by driving the Data Strobe line High. If the Acknowledge is not received within 1 millisecond, the master can abort the operation by driving the Data Strobe line high.

2.6.2.2.2 Optimized Operation. The optimized read data-from-memory operation uses the signal overlap prohibited in the non-optimized operation. A Slave device designed for optimized operation must provide an adjustment for the length of time between when it drives the Acknowledge line Low and when it presents valid data on the data lines. The Primary Master determines the maximum allowed amount of signal overlap based on its acknowledge acceptance overhead time. The Slave device Acknowledge timing is then set to an overlap value equal to or less than the Primary Master's acknowledge acceptance overhead time. For any given Slave device, the length of time Acknowledge can precede valid data ranges from coincident (data valid at the same time the Slave device drives the Acknowledge line Low) to the maximum internal memory access time of the Slave device (immediate upon detecting the leading edge of the Address Strobe signal). Regardless of the allowed signal overlap with the optimized operation, the selected slave device must wait until the leading edge of Data Strobe before driving the data lines.

A minimum of 80 ns after detecting the Acknowledge line Low, the active bus master completes the optimized read data-from-memory operation by driving the Data Strobe line High. If the Acknowledge is not received within 1 millisecond, the master can abort the operation by driving the Data Strobe line high.

**2.6.2.2.3 Operation Completion.** The active bus master completes the read data-from-memory operation by driving the Data Strobe line High. When the read data-from-memory transfer is a single event transfer, the selected slave stops driving the data lines and the Acknowledge line and internally goes to the deselected state.

For sequential cycles of read data-from-memory, the active bus master can start address set-up for the next data transfer before driving the Data Strobe line High. The the amount of data transfer overlap is limited by the minimum time of 25 ns from the rising edge of the data strobe to the falling edge of the next Address Strobe. The signal overlapping provides a total potential cycle time of 105 ns per data transfer or a transfer rate of 9.5 MHz. Assuming 16-bit data transfers, the resulting throughput is approximately 19 megabytes per second.

#### 3. Electrical Specification

#### 3.1 Introduction

This section defines the electrical requirements of the iLBX bus. The descriptions include the types of drivers and receivers required, the method, type, and location of line termination, general signal characteristics, and electrical timing.

#### 3.2 Electrical State Relationships

The electrical state relationships used in this manual conform to the conventions used in the Multibus Specification. The iLBX bus uses commercial grade TTL components for all drivers and receivers. Table 5 relates the general industry voltage level standards for TTL components to the signal line notation conventions used in this manual. The specifications in Table 5 assume a power source of +5 Vdc, +5 percent, referenced to logic ground. The iLBX bus does not include provision for system power and the electrical specification assumes that all power is drawn from the Multibus P1 connector power lines.

Table 5 Notational Summary

| TTL                 | TTL VOLTAGE RANGE |                   |  |  |  |

|---------------------|-------------------|-------------------|--|--|--|

| ELECTRICAL<br>LEVEL | AT RECEIVER       | AT DRIVER         |  |  |  |

| H, High             | +2.0 TO +5.25 Vdc | +2.4 TO +5.25 Vdc |  |  |  |

| L, Low              | -0.5 TO +0.8 Vdc  | 0 TO +0.5 Vdc     |  |  |  |

#### 3.3 Environmental Requirements

The electrical specifications for the iLBX bus must be met under the following environmental conditions. The specifications list the ambient temperature requirements and the non-condensing requirements for humidity.

####

#### 3.4 DC Specifications

Table 6 lists the iLBX bus DC specifications for the signal line drivers and the receiver loads presented to the signal lines. The DC specifications listed assume the use of devices typically associated with the standard 16-bit implementation of the iLBX bus. Refer to Section 6, Levels of Compliance, for the driver types required with the various allowed subsets of the iLBX bus. The drive and load requirements presented in Table 6 apply regardless of the iLBX bus subset implemented.

The drive requirements include the load capacitance an output driver must drive and for tristate drivers the requirements assume four slave device loads. The load requirements include the maximum allowable input capacitance that any device can present to the signal line. The specifications assume the High drive signals are measured at  $+2.4 \, \text{Vdc}$  and the Low drive signals at  $+0.5 \, \text{Vdc}$ .

#### 3.5 Termination

DC and AC termination requirements are listed in Table 6. The DC termination for a particular line consists of a resistor connecting the line to +5VDC. The location of each resistor depends on the applicable signal line. Signal lines driven by a tristate or open collector driver (that is, DB15 - DB0, TPAR\*, ASTB\*, DSTB\*, and ACK\*. has the termination resistors located at the Primary Master. If a Primary Master is not implemented on the iLBX bus a Secondary Master, operating as a limited Primary Master, must have the capability to provide the resistors. For the signal line, SMRQ\*, the resistor is located at the Primary Master, and never at the Secondary Master.

An additional AC termination is required for lines ASTB\* and DSTB\* and is located at each slave device. Each slave device must provide a series RC network connecting the signal line to logic ground. The network should be placed in close proximity to the receiver component on the slave device.

#### 3.6 AC Specifications

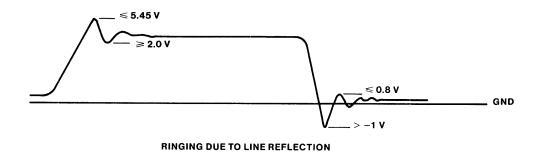

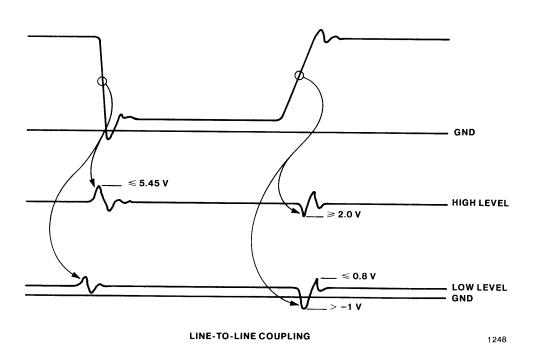

Table 7 lists the iLBX bus timing parameters for the signal lines. The table provides a reference designator for each timing parameter, a description of the timing parameter, the minimum and maximum timing requirements, and the source device where the timing parameter must be implemented. Figures 5 and 6 are timing charts that illustrate the timing relationships for the iLBX bus and the timing specifications on the timing charts use the reference designators from Table 7. Table 7 does not specify the typical transition rise and fall times for the iLBX bus drivers, however, the bus drivers should have slew rates less than 1 volt/nanosecond with less than 24 milliamps drive. Use of drivers having higher slew rates may degrade signal characteristics to an undesirable waveform. Figure 7 depicts a typical acceptable signal waveform during high-to-low and low-to-high transitions.

Table 6 DC Specifications

|                |                | DC                         |         | Minimum<br>Require |             | -       | Maximum<br>er Requir |             |

|----------------|----------------|----------------------------|---------|--------------------|-------------|---------|----------------------|-------------|

| Signal<br>Name | Driver<br>Type | Termination<br>(To +5 VDC) | High    | Low                | Load<br>Cap | High    | Low                  | Load<br>Cap |

| DB15-0         | TRI-STATE      | 10K OHMS                   | 0.6 ma  | 9 ma               | 75 pf       | 0.15 ma | 2 ma                 | 18 pf       |

| TPAR*          | TRI-STATE      | 10К ОНМЅ                   | 0.6 ma  | 9 ma               | 75 pf       | 0.15 ma | 2 ma                 | 18 pf       |

| ABD23-0        | TRI-STATE      | NONE                       | 0.4 ma  | 20 ma              | 120 pf      | 0.10 ma | 5 ma                 | 30 pf       |

| R/W            | TRI-STATE      | NONE                       | 0.2 ma  | 8 ma               | 75 pf       | 0.05 ma | 2 ma                 | 18 pf       |

| BHEN           | TRI-STATE      | NONE                       | 0.2 ma  | 8 ma               | 75 pf       | 0.05 ma | 2 ma                 | 18 pf       |

| LOCK*          | TRI-STATE      | NONE                       | 0.2 ma  | 8 ma               | 75 pf       | 0.05 ma | 2 ma                 | 18 pf       |

| SMRQ*          | TTL            | 10К ОНМЅ                   | 0.05 ma | 2 ma               | 20 pf       | 0.05 ma | 2 ma                 | 18 pf       |

| SMACK*         | TTL            | NONE                       | 0.05 ma | 2 ma               | 20 pf       | 0.05 ma | 2 ma                 | 18 pf       |

| ASTB*          | TRI-STATE      | 10K OHMS ¶                 | 0.2 ma  | 9 ma               | 75 pf       | 0.05 ma | 2 ma                 | 18 pf       |

| DSTB*          | TRI-STATE      | 10K OHMS ¶                 | 0.2 ma  | 9 ma               | 75 pf       | 0.05 ma | 2 ma                 | 18 pf       |

| ACK*           | OPEN COLL      | 330 OHMS                   | N.A.    | 20 ma              | 45 pf       | 0.05 ma | 2 ma                 | 18 pf       |

Note: ¶ = Additional AC termination for both ASTB\* and DSTB\* lines are required on each slave device. Each terminator is a series RC (100 ohm, 10 picofarad) network between the signal line and ground. The location of the termination network should be as close as possible to the receiver component input.

The following are the general and specific notes for Table 7.

#### General Notes:

- All times listed are nanoseconds unless otherwise noted

- TPAR\* timing is the same as DB15 DB0

- M refers to the current active bus master

- S refers to the currently selected slave device

- PM refers to the Primary Master

- SM refers to the Secondary Master

#### Specific Notes:

1. Board designs can implement either of two transfer rates, optimized and nonoptimized, based on the degree of close coupling desired between the master

and slave devices. Two factors determine the coupling and the degree of optimization realized when implementing the iLBX bus: the acknowledge acceptance time of the master device and the range of variability in the slave

device to pre-acknowledge the data transfer. A master device designed for

optimized operation must meet the t17 maximum time for write operation

and the t11 maximum time for read operations. When the master devices

meet the required times, the Slave device is allowed to drive the Acknowledge line Low any time after the leading edge of the Address Strobe. A

master device that does not meet the maximum write time requirements, by

default, transfers data using non-optimized timing, and the Slave device

must wait for the leading edge of the Data Strobe before driving the Acknowledge line Low. See Note 3 for the Slave device timing restrictions.

Table 7 iLBX<sup>TM</sup> Bus Timing Parameters

|     |                                                                            | TIM      | ING  | I        |      |

|-----|----------------------------------------------------------------------------|----------|------|----------|------|

| REF | PARAMETER DESCRIPTION                                                      | MIN      | мах  | SOURCE   | NOTE |

| t1  | ASTB* DURATION (WIDTH)                                                     | 25       |      | М        |      |

| t2  | ADDRESS SETUP TO LEADING EDGE OF                                           | 40       |      | М        |      |

| t3  | ASTB* ADDRESS HOLD AFTER LEADING EDGE OF ASTB*                             | 40       |      | М        |      |

| t4  | BHEN SETUP TO LEADING EDGE OF                                              | 30       |      | м        |      |

| t5  | BHEN HOLD AFTER LEADING EDGE OF ASTB*                                      | 30       |      | м        |      |

| t6  | R/W SETUP TO LEADING EDGE OF                                               | 20       |      | М        |      |

| t7  | R/W HOLD AFTER LEADING EDGE OF                                             | 25       |      | М        |      |

| t8  | TRAILING EDGE OF ASTB* TO TRAILING EDGE OF DSTB*                           | 10       |      | М        |      |

| t9  | TRAILING EDGE OF DSTB* TO LEADING                                          | 25       |      | М        |      |

| t10 | EDGE OF ASTB*<br>  DSTB* DURATION (WIDTH)                                  | 50       |      | М        |      |

| t11 | LEADING EDGE OF ASTB* TO LEADING EDGE OF DSTB*                             | 0        | 95   | М        | 1    |

| t12 | ACK * HOLD AFTER TRAILING EDGE OF DSTB *                                   | 0        | 45   | S        | 2    |

| t13 | LEADING EDGE OF ACK * TO READ DATA VALID                                   | 0        | tacc | S        | 3    |

| t14 | READ DATA HOLD TIME AFTER TRAILING EDGE OF DSTB*                           | 0        | 45   | s        | e.   |

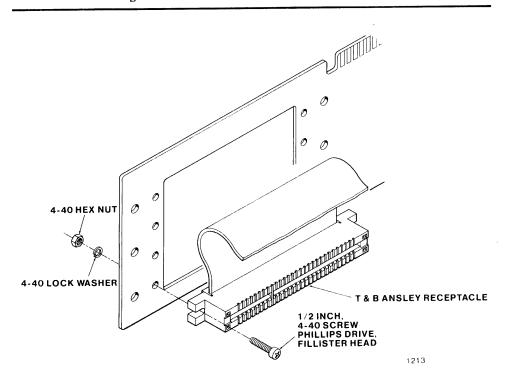

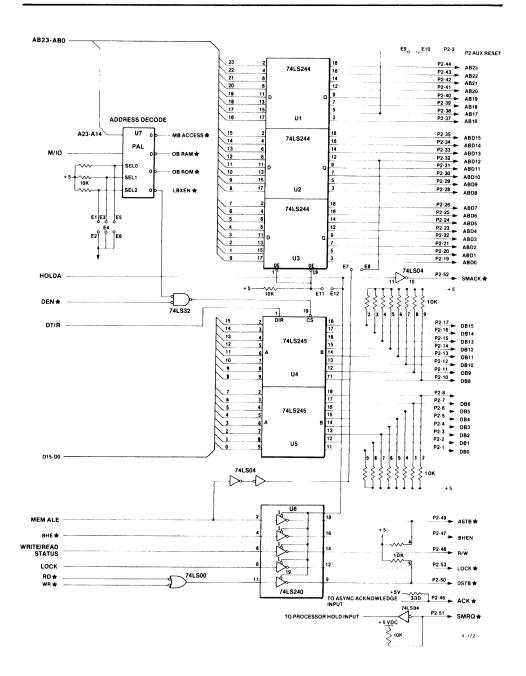

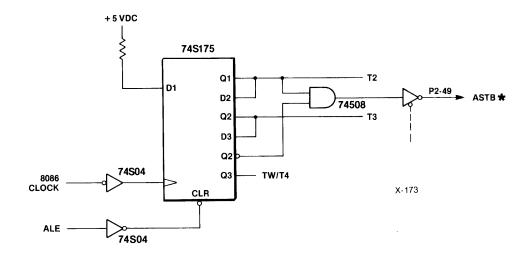

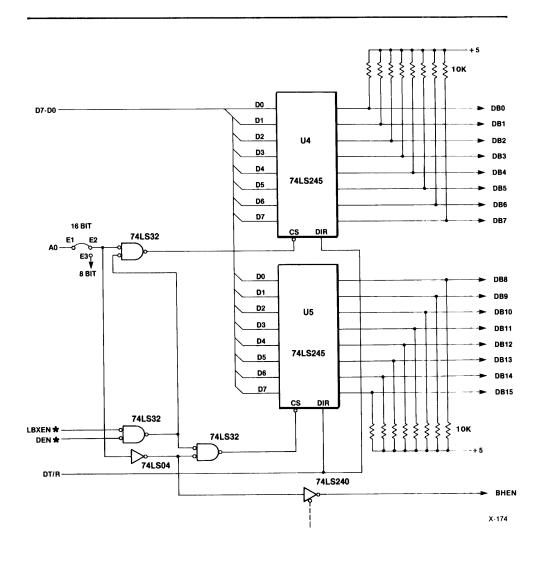

| t15 | LEADING EDGE OF ACK * TO TRAILING EDGE OF DSTB *                           | 80       |      | М        |      |