# SBC 80/20 AND SBC 80/20-4 SINGLE BOARD COMPUTERS HARDWARE REFERENCE MANUAL

Manual Order No. 9800317D

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

ICE INSITE INTEL INTELLEC LIBRARY MANAGER MCS MEGACHASSIS MICROMAP MULTIBUS PROMPT RMX UPI µSCOPE

#### PREFACE

This manual provides general information, installation, programming information, principles of operation and service information for the Intel SBC 80/20 and 80/20-4 Single Board Computers. Unless specified otherwise references to the SBC 80/20 are valid for both systems. The areas where differences occur are identified as SBC 80/20 only or SBC 80/20-4 only. Additional systems information and Component Part details are available in the following documents:

- Intel Microcomputer Systems Data Book, 98-414

- Intel 8080 Microcomputer Systems User's Manual, 98-153

|  |  | • |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

## TABLE OF CONTENTS

| Chapter |       | Title                                                                                                                      | Page                         |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 1       | INTR  | ODUCTION                                                                                                                   | 1-1                          |

| 2       | FUNC' | TIONAL/PROGRAMMING CHARACTERISTICS                                                                                         | 2-1                          |

|         | 2.1   | Functional Description                                                                                                     | 2-1                          |

|         | 2.2   | Programming Summary                                                                                                        | 2-5                          |

|         |       | 2.2.1 Memory Address Assignment                                                                                            | 2-5<br>2-6                   |

| 3       | THEO  | RY OF OPERATION                                                                                                            | 3-1                          |

|         | 3.1   | The CPU Set                                                                                                                | 3-1                          |

|         |       | 3.1.1 Instruction Timing                                                                                                   | 3-3<br>3-12<br>3-13<br>3-14  |

|         | 3.2   | System Bus Interface                                                                                                       | 3-15                         |

|         |       | 3.2.1 Bus Controller                                                                                                       | 3-15<br>3-18                 |

|         | 3.3   | Failsafe Timer                                                                                                             | 3-21                         |

|         | 3.4   | Random Access Memory (RAM)                                                                                                 | 3-21                         |

|         | 3.5   | Read Only Memory (ROM/PROM)                                                                                                | 3-26                         |

|         | 3.6   | I/O Address Decoding                                                                                                       | 3-29                         |

|         | 3.7   | Serial I/O Interface                                                                                                       | 3-31                         |

|         |       | 3.7.1 Intel®8251 Operational Summary                                                                                       | 3-34<br>3-47<br>3-49<br>3-50 |

|         | 3.8   | Parallel I/O Interface                                                                                                     | 3-51                         |

|         |       | 3.8.1 Intel® 8255 Operational Summary 3.8.2 Parallel I/O Configurations                                                    | 3-53<br>3-67                 |

|         | 3.9   | Intel® 8253 Programmable Interval Timer                                                                                    | 3-73                         |

|         |       | 3.9.1 Intel® 8253 Operational Summary                                                                                      | 3-74<br>3-84                 |

| 3       | . 10  | Intel®8259 Programmable Interrupt Controller .                                                                             | 3-87                         |

|         |       | 3.10.1 8259 Basic Functional Description 3.10.2 8259 Detailed Operational Summary 3.10.3 SBC 80/20 Interrupt Configuration | 3-87<br>3-92<br>3-106        |

# TABLE OF CONTENTS (Cont d)

| Chapter |      | <u>Title</u>                                                    | Page                 |

|---------|------|-----------------------------------------------------------------|----------------------|

|         | 3.11 | Power Fail Provisions                                           | 3-110                |

| 4       | USER | SELECTABLE OPTIONS                                              | 4-1                  |

|         | 4 1  | Memory Address Allocation                                       | 4-2                  |

|         | 4 2  | Serial I/O Options                                              | 4-3                  |

|         |      | 4.2.1 Baud Rate and Program Selectable Serial I/O Options       | 4-4<br>4-7           |

|         | 4 3  | Parallel I/O Options                                            | 4-9                  |

|         | - 0  | 4.3.1 Ports 1 and 4 (8255 Port A)                               | 4-12<br>4-24<br>4-32 |

|         | 4.4  | Interrupt Priority Options                                      | 4-45                 |

|         | 4.5  | General Options                                                 | 4-45                 |

|         |      | 4.5.1 Disable Bus Clock Signals                                 | 4-45<br>4-47<br>4-47 |

| 5       | SYST | EM INTERFACING                                                  | 5-1                  |

|         | 5.1  | Electrical Connections                                          | 5-1                  |

|         | 5.2  | SBC 80 System Bus Summary                                       | 5-7                  |

|         | 5.3  | RS232C Cabling                                                  | 5-10                 |

| 6       | COMP | ATIBLE EQUIPMENT                                                | 6-1                  |

|         | 6.1  | Master Modules                                                  | 6-1                  |

|         | 6.2  | SBC-104 and SBC-108 Combination Memory and                      |                      |

|         |      | I/O Expansion Boards                                            | 6-1                  |

|         | 6.3  | SBC-016 RAM Module                                              | 6-2                  |

|         | 6.4  | SBC-406 6K PROM Module                                          | 6-3                  |

|         | 6.5  | SBC-416 16K PROM Module                                         | 6-3                  |

|         | 6.6  | SBC-508 General Purpose I/O Module                              | 6-3                  |

|         | 6.7  | Modular Backplane and Cardcage                                  | 6-4                  |

|         | 6.8  | Intellec <sup>®</sup> Microcomputer Development System Cardcage | 6-4                  |

# TABLE OF CONTENTS (Cont d)

| Chapter |                                     | Page |

|---------|-------------------------------------|------|

| 7       | SBC 80/20 SPECIFICATIONS            | 7-1  |

|         | 7.1 DC Power Requirements           | 7-1  |

|         | 7.2 AC Characteristics              | 7-1  |

|         | 7.3 DC Characteristics              | 7-1  |

|         | 7.4 Environment                     | 7-1  |

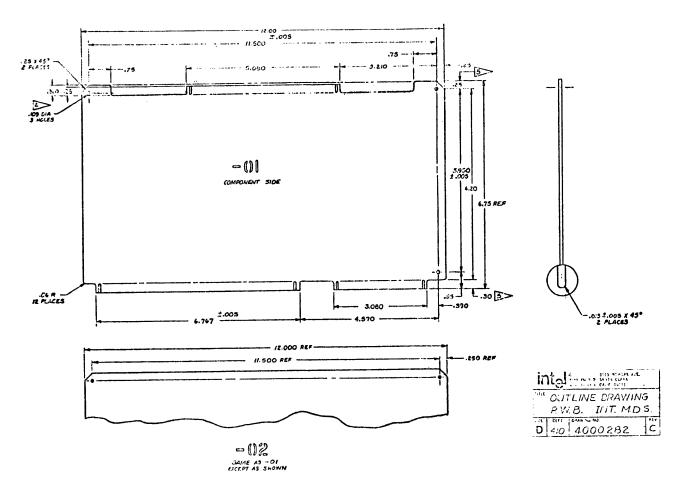

|         | 7.5 SBC 80/20 Board Outline         | 7-1  |

|         | 7.6 SBC 80/20 Compatible Connectors | 7-1  |

| APPENDI | CES                                 |      |

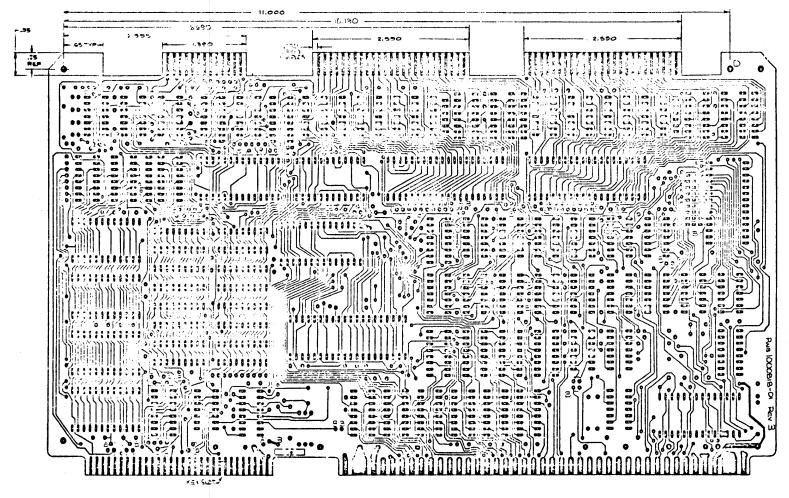

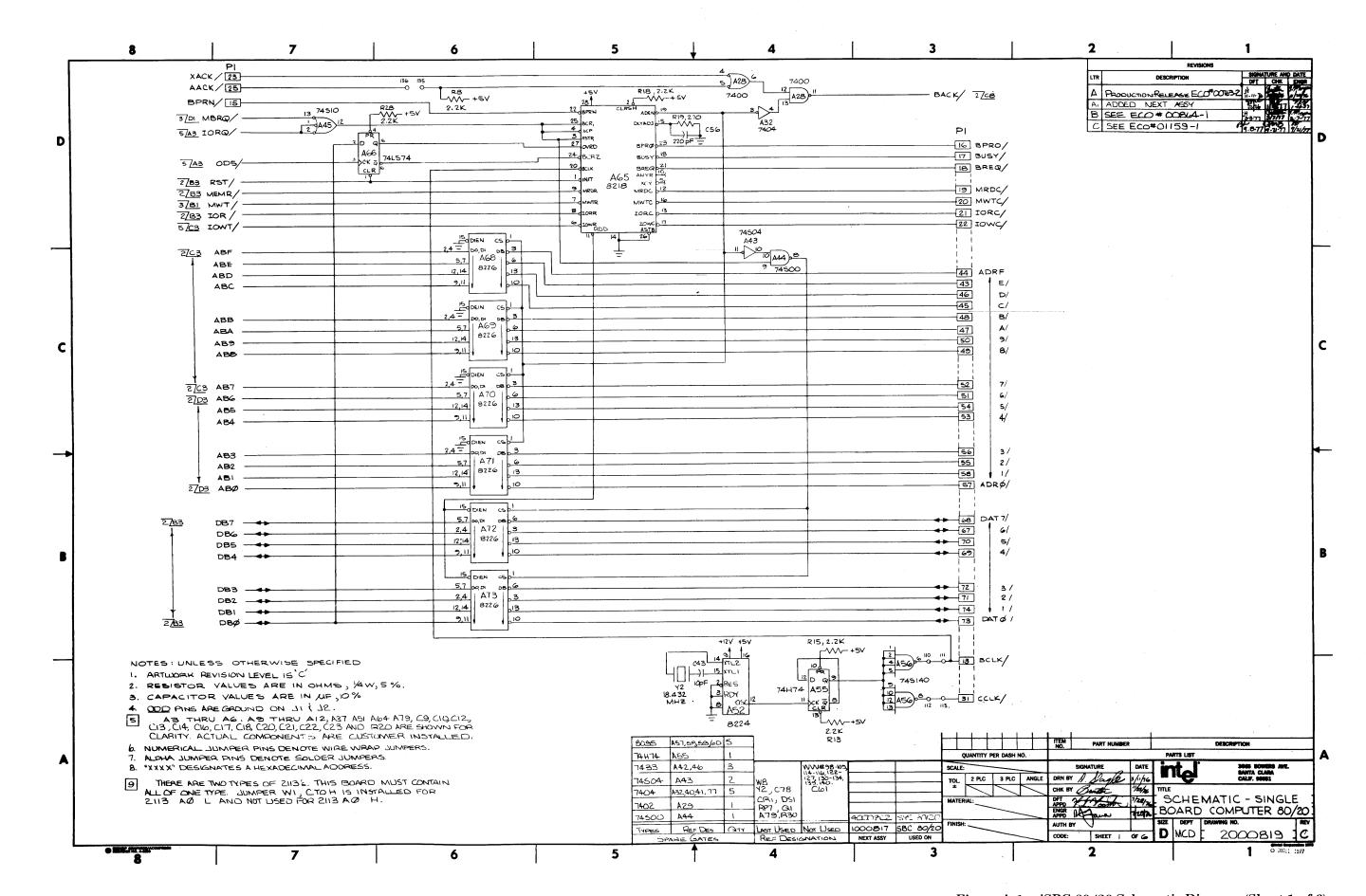

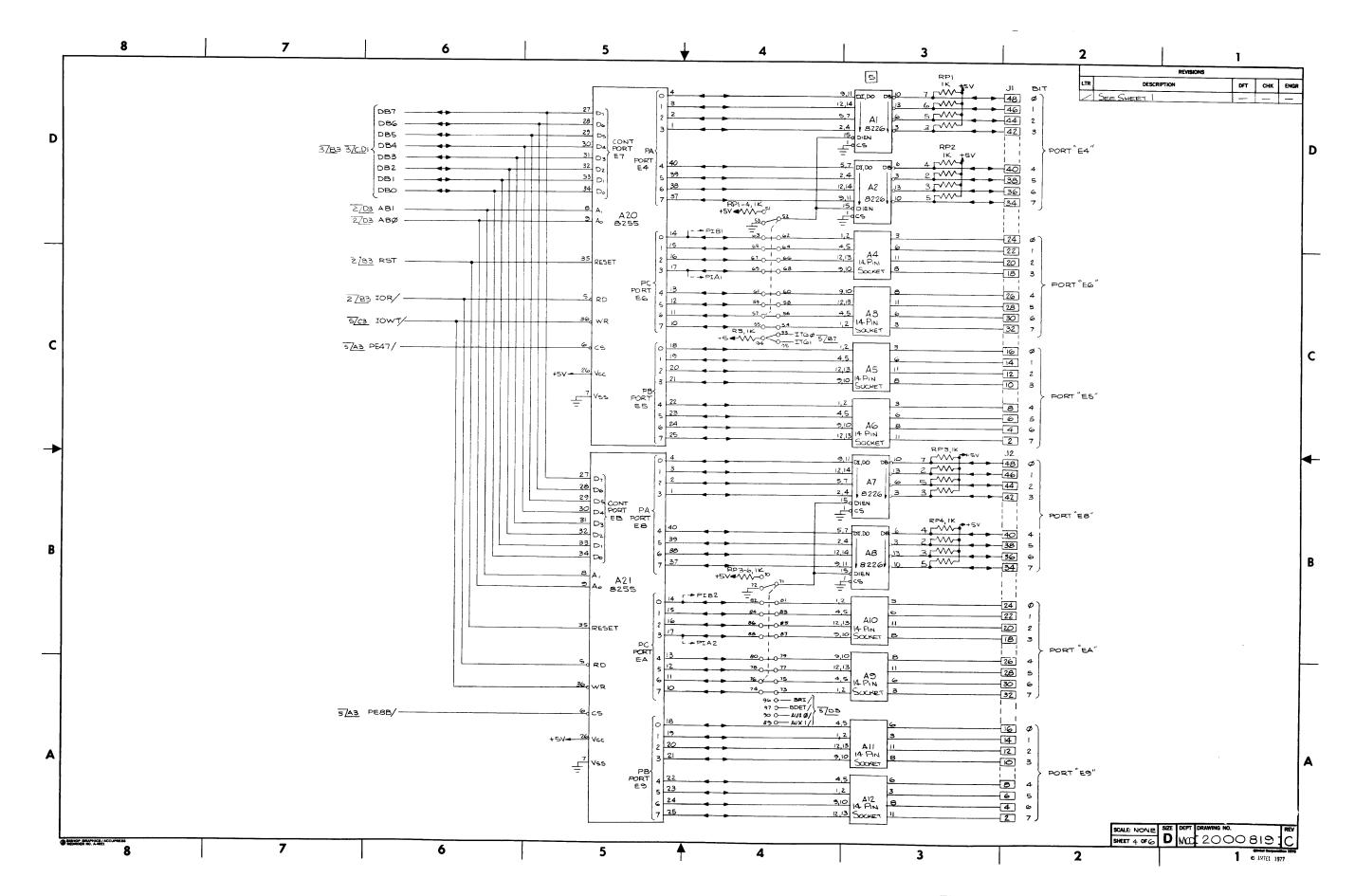

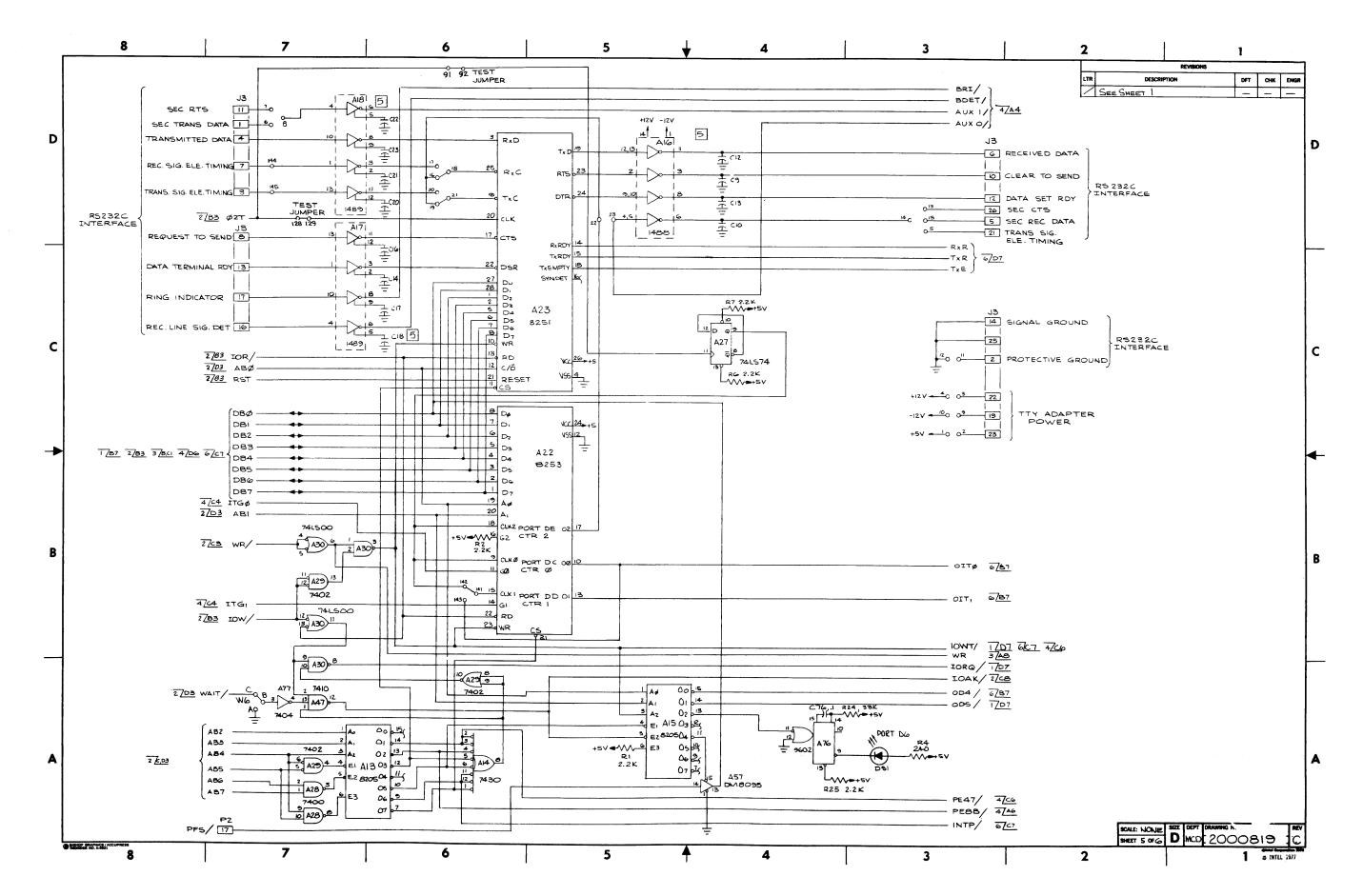

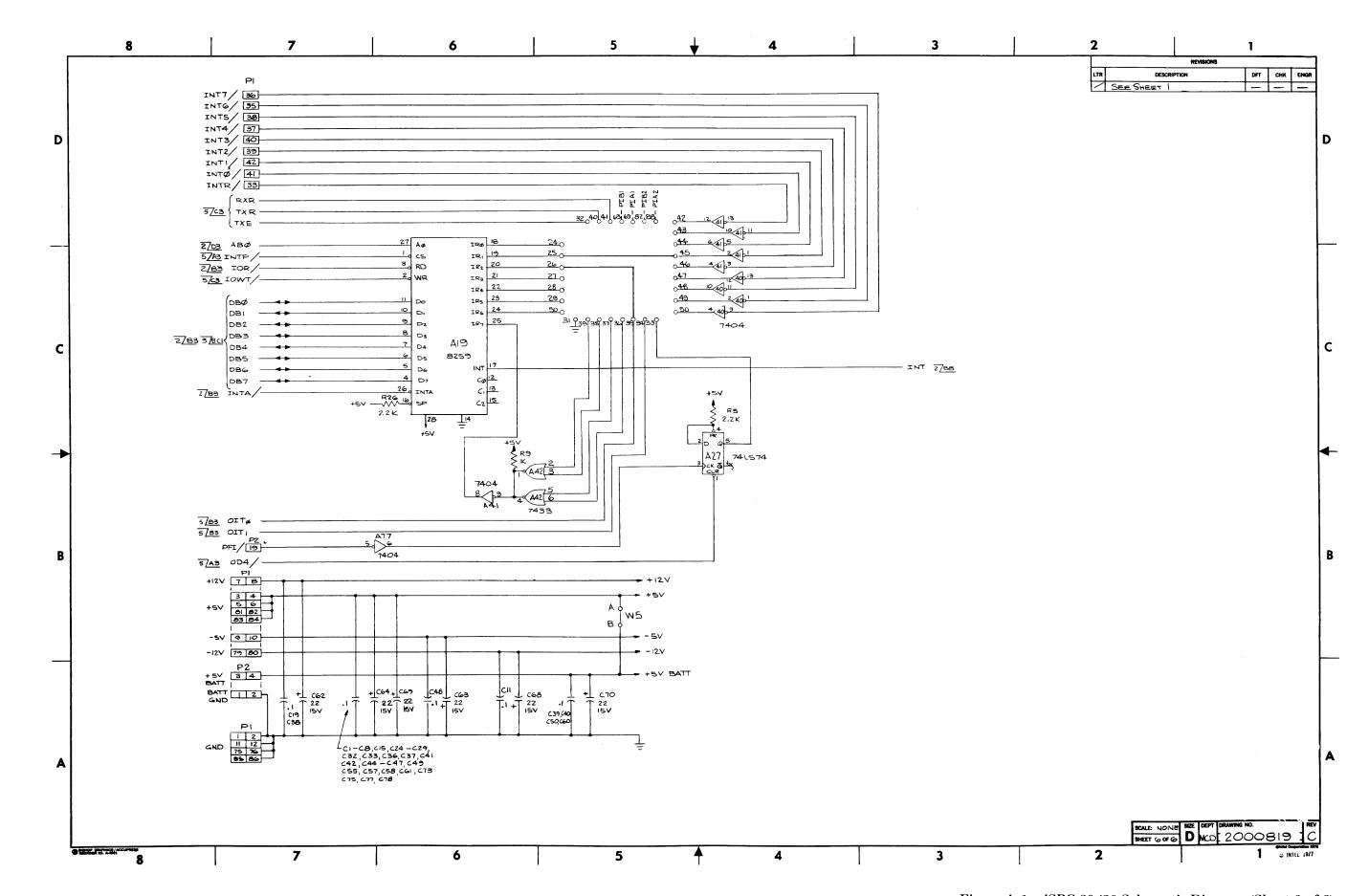

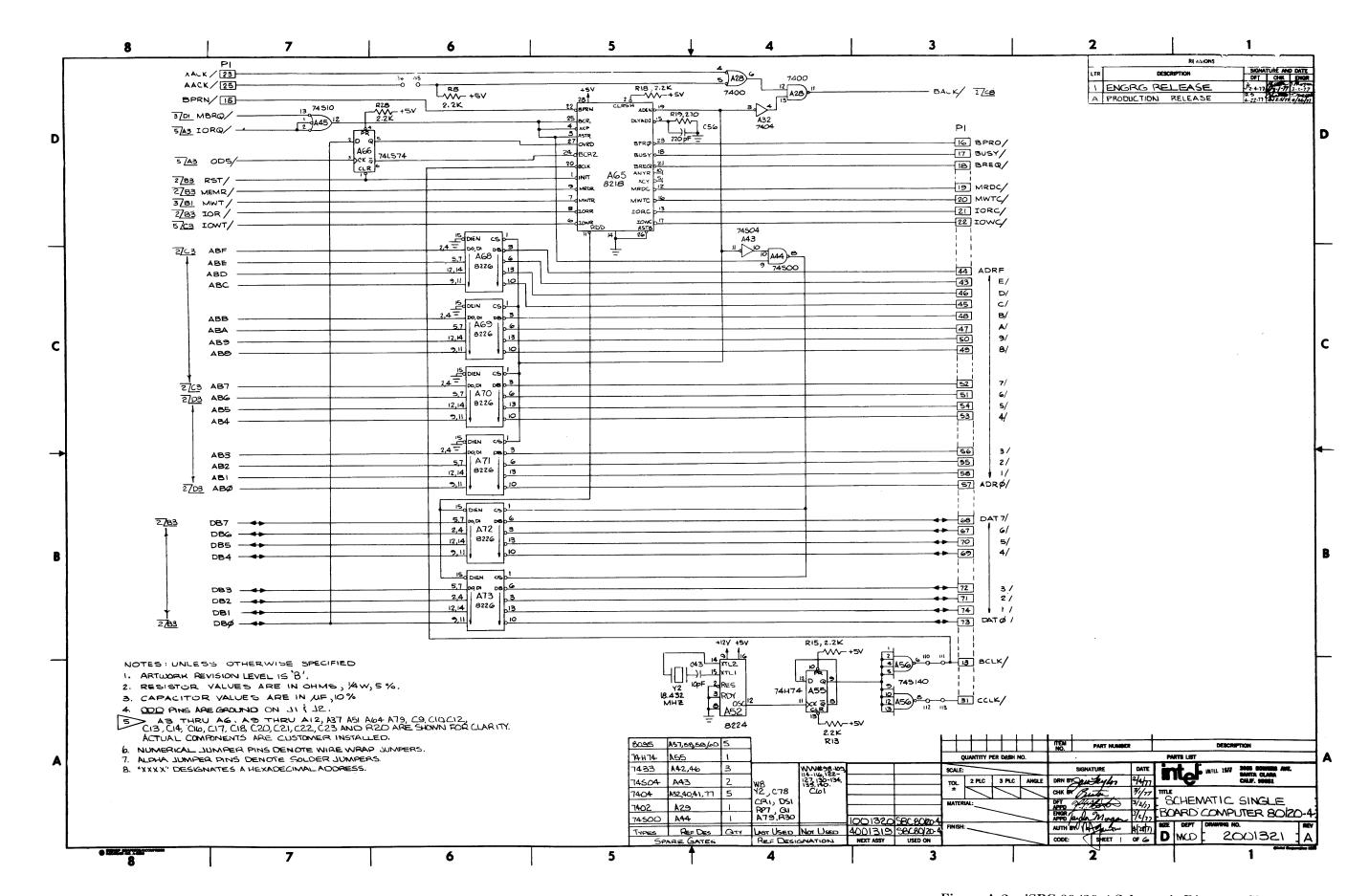

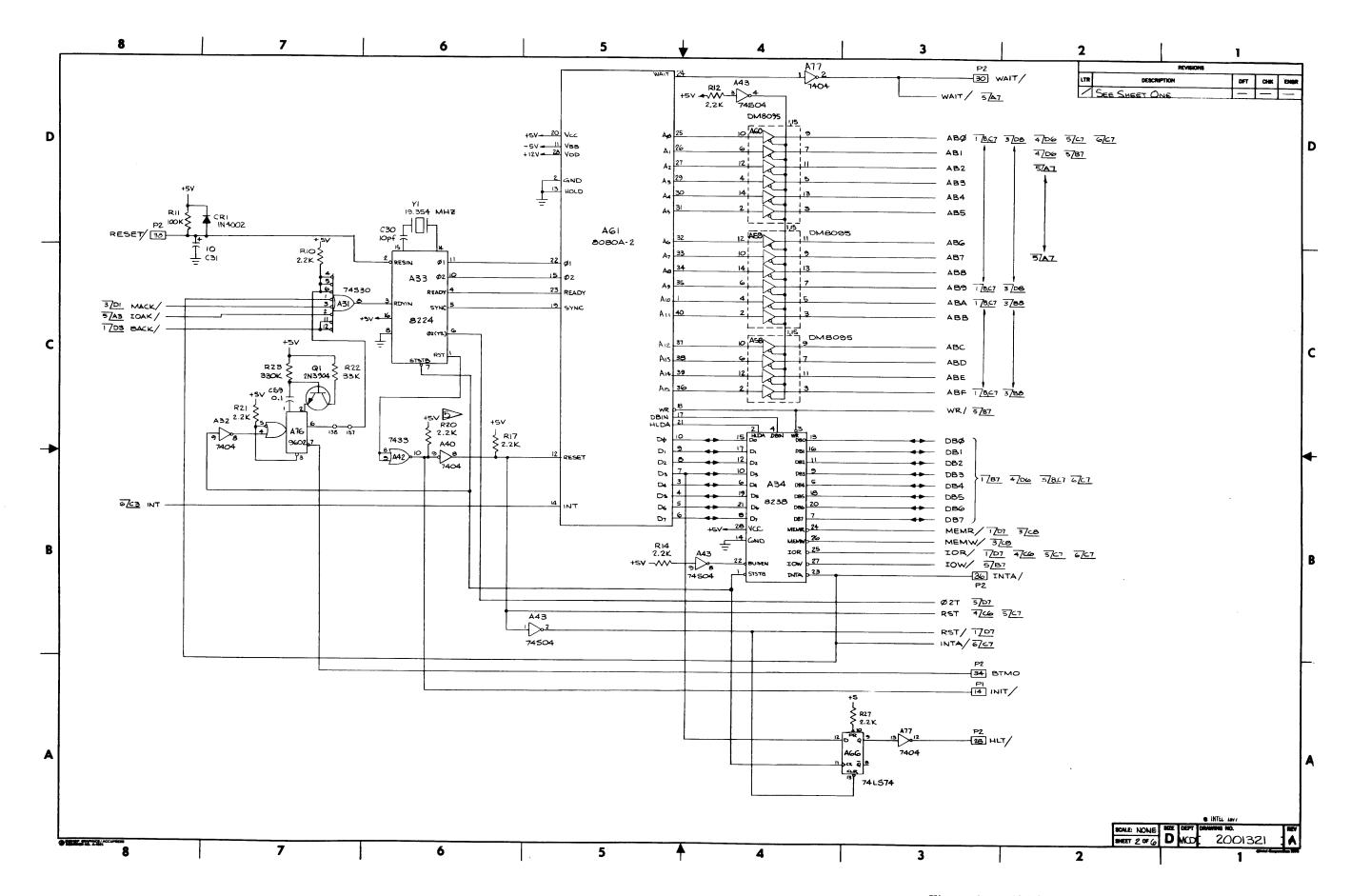

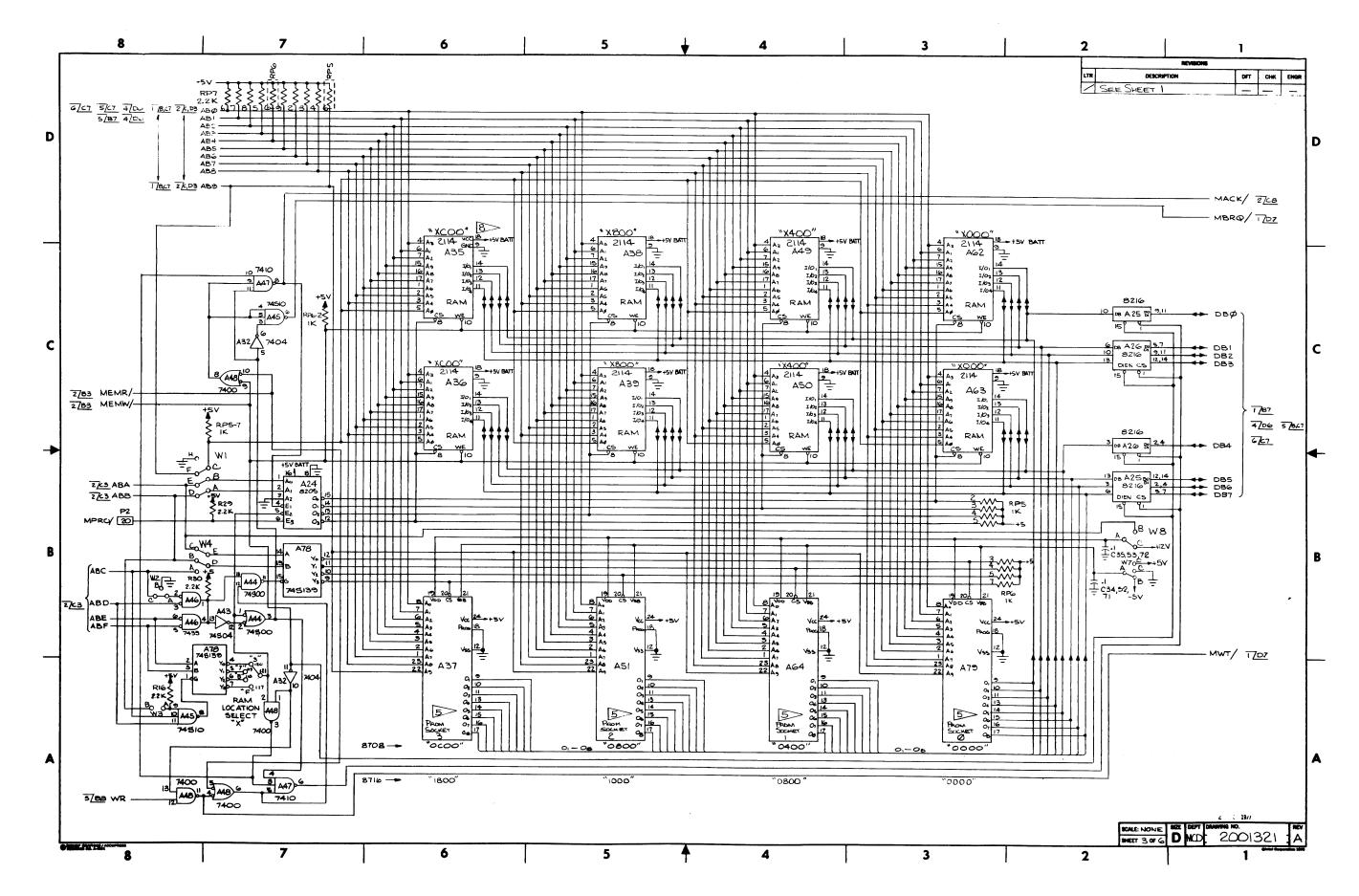

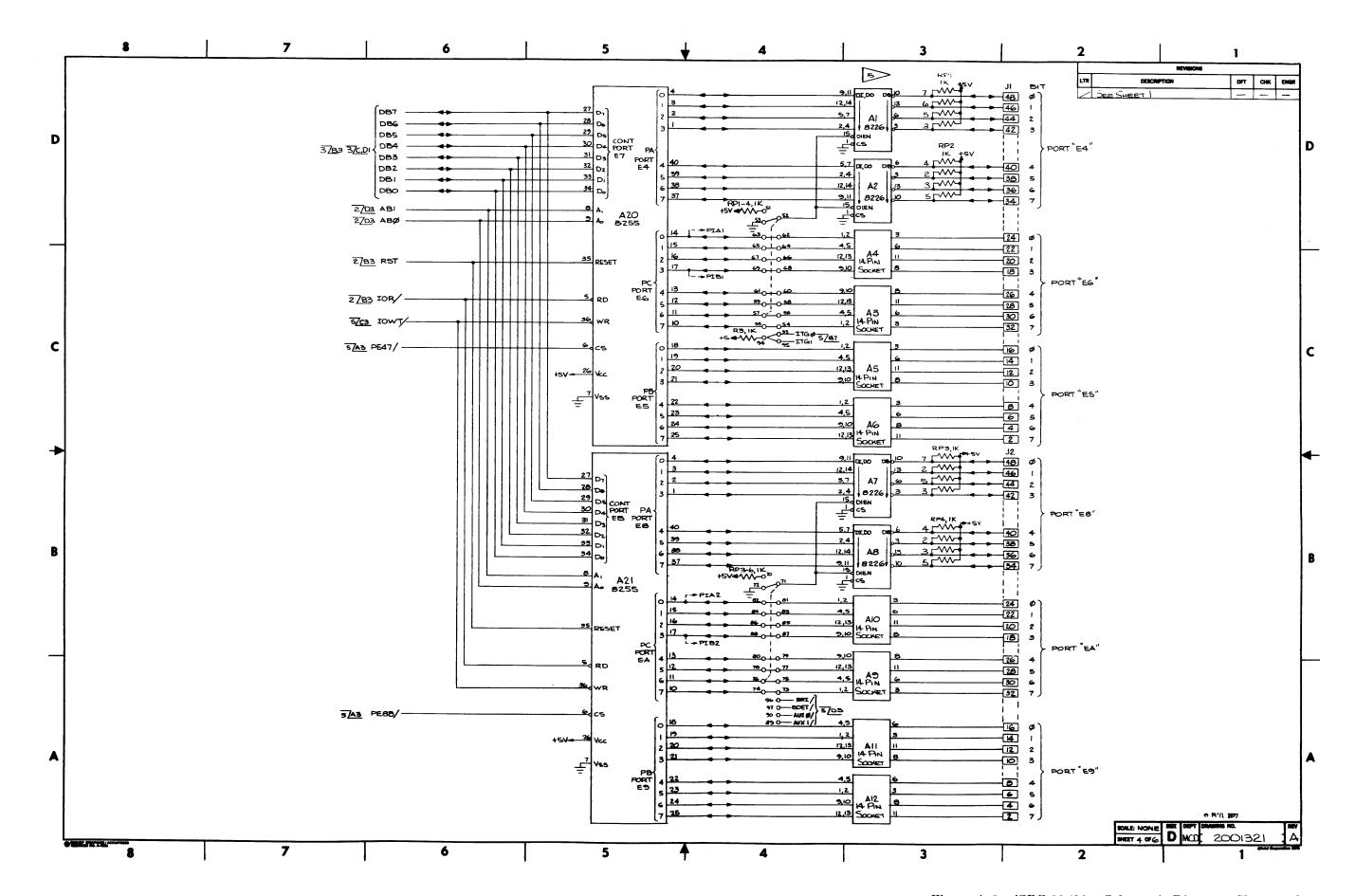

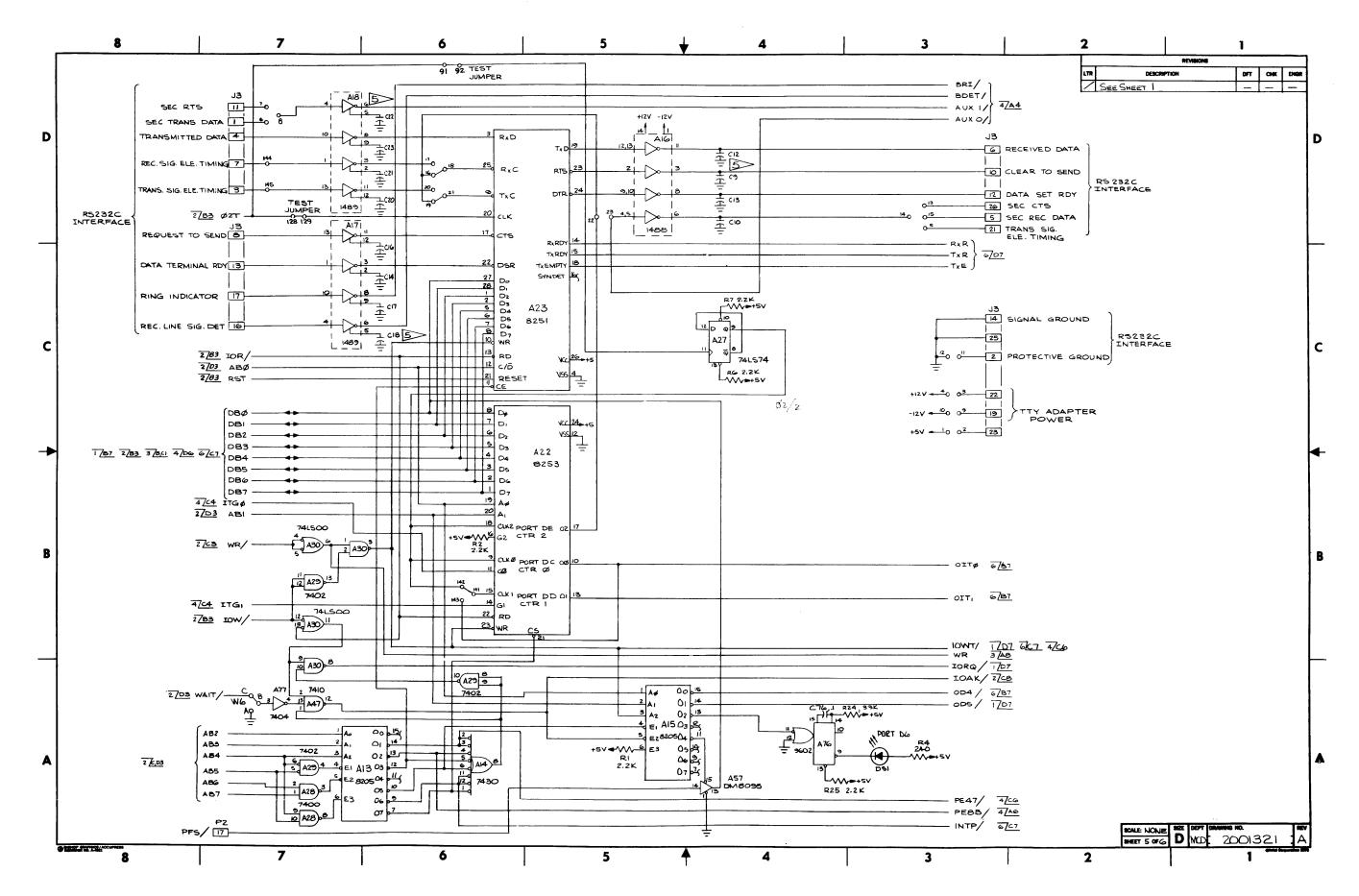

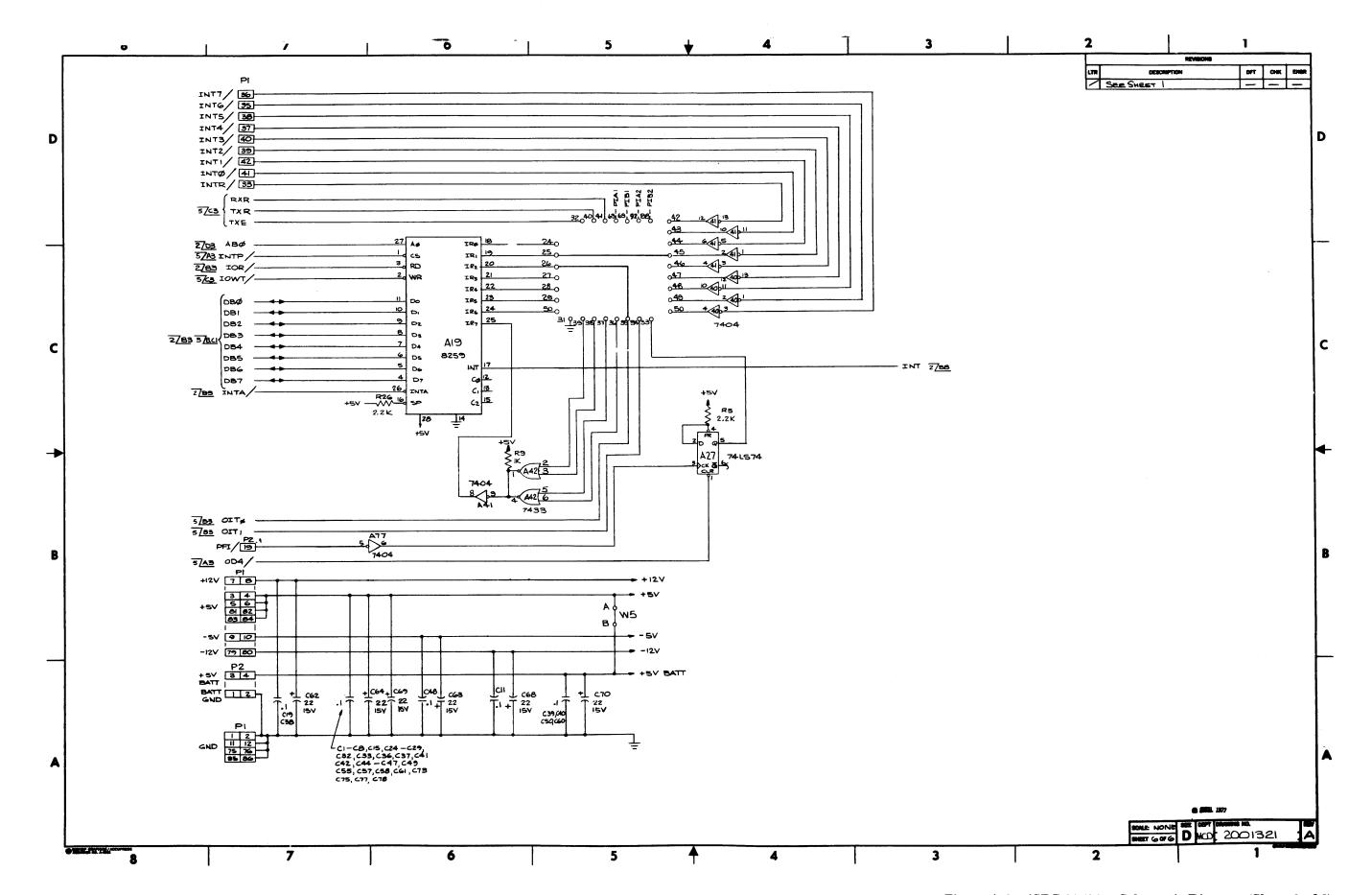

| Α       | SBC 80/20 SCHEMATICS                | A-1  |

| В       | SBC-901, SBC-902 SCHEMATICS         | B-1  |

| С       | 8080 INSTRUCTION SET SUMMARY        | C-1  |

| D       | SERIAL I/O WIRING FOR SBC 80/20     | D-1  |

| INDEX   |                                     | I-1  |

## LIST OF ILLUSTRATIONS

| Figure |                                                                   | Page |

|--------|-------------------------------------------------------------------|------|

| 2-1    | SBC 80/20 FUNCTIONAL BLOCK DIAGRAM                                | 2-2  |

| 3-1    | THE CPU SET                                                       | 3-2  |

| 3-2    | TYPICAL FETCH MACHINE CYCLE                                       | 3-6  |

| 3-3    | INPUT INSTRUCTION CYCLE                                           | 3-9  |

| 3-4    | OUTPUT INSTRUCTION CYCLE                                          | 3-10 |

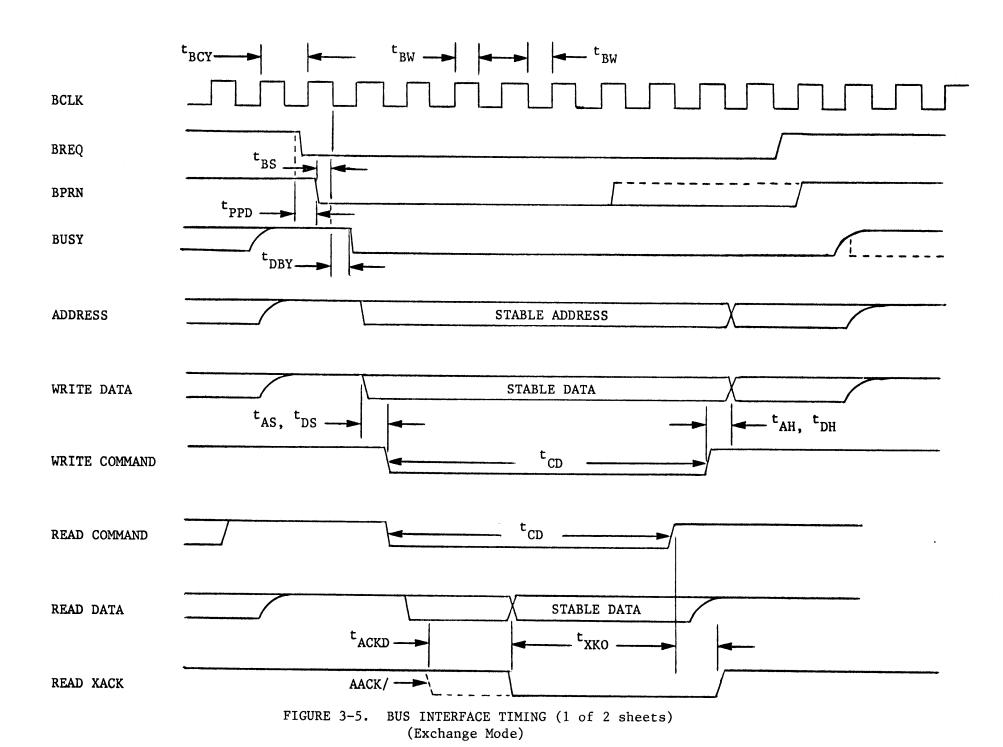

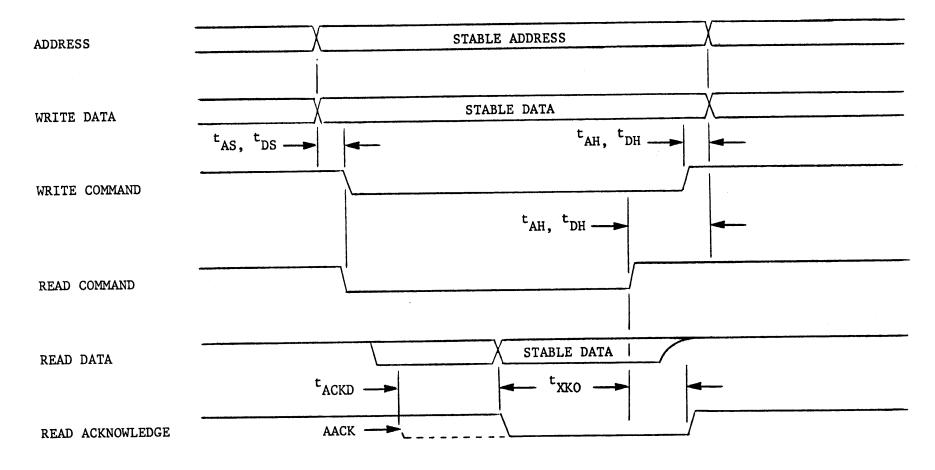

| 3-5    | BUS INTERFACE TIMING                                              | 3-19 |

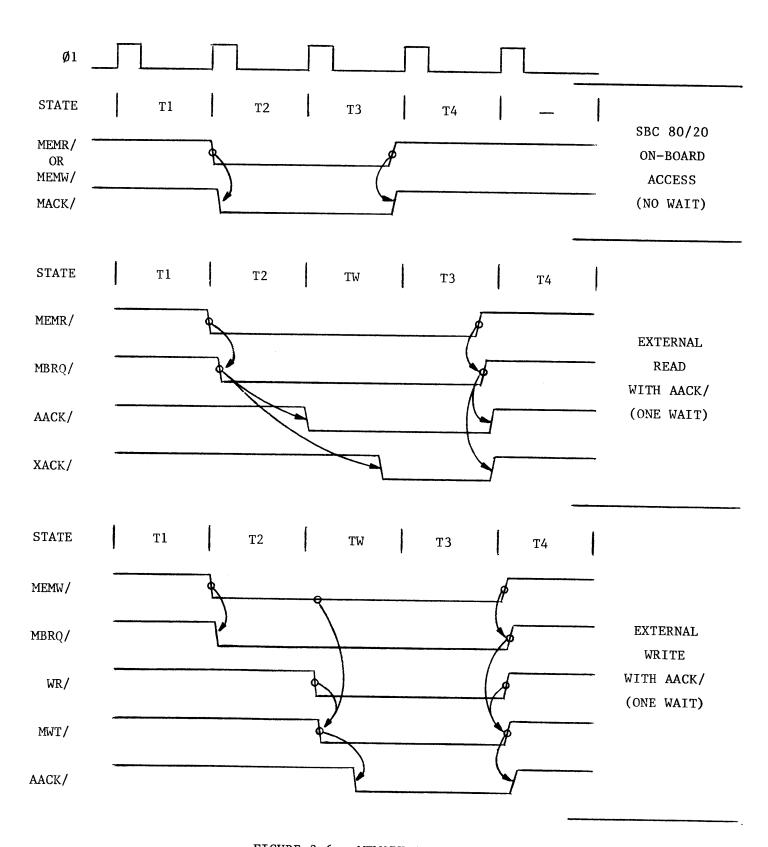

| 3-6    | MEMORY ACCESS TIMING                                              | 3-27 |

| 3-7    | SBC 80/20 ON-BOARD I/O TIMING                                     | 3-33 |

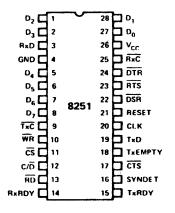

| 3-8    | 8251 PIN ASSIGNMENTS                                              | 3-36 |

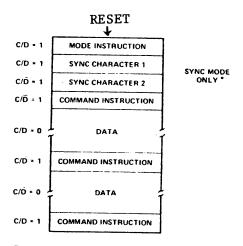

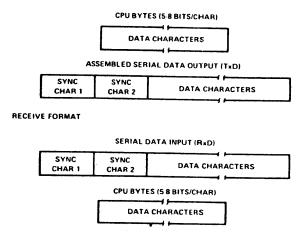

| 3-9    | TYPICAL 8251 DATA BLOCK                                           | 3-40 |

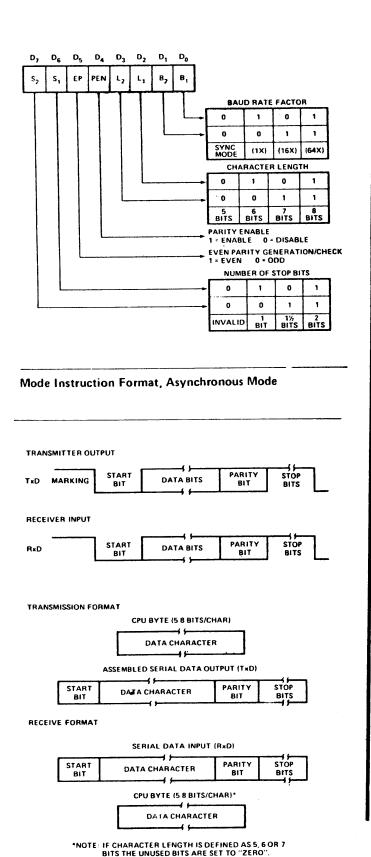

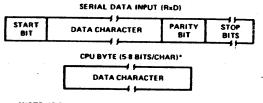

| 3-10   | ASYNCHRONOUS MODE                                                 | 3-41 |

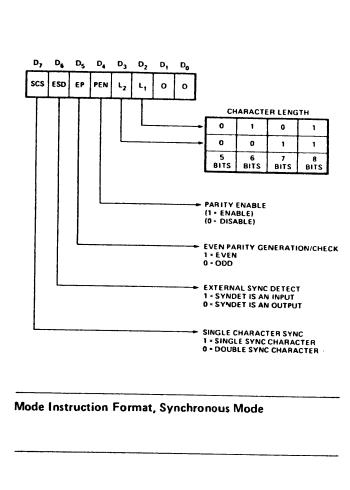

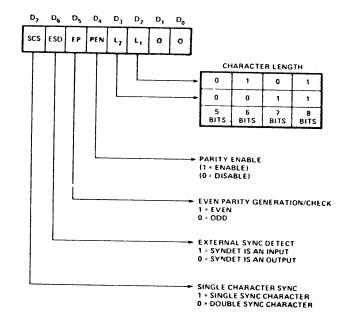

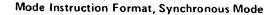

| 3-11   | SYNCHRONOUS MODE                                                  | 3-41 |

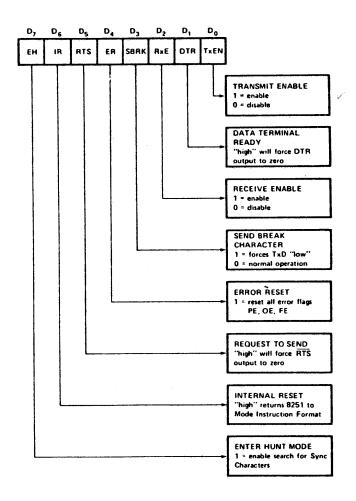

| 3-12   | COMMAND INSTRUCTION FORMAT                                        | 3-43 |

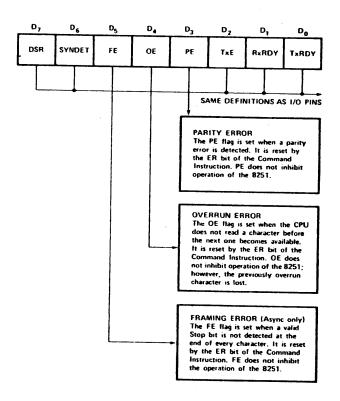

| 3-13   | STATUS READ FORMAT                                                | 3-44 |

| 3-14   | 8255 PIN ASSIGNMENTS                                              | 3-55 |

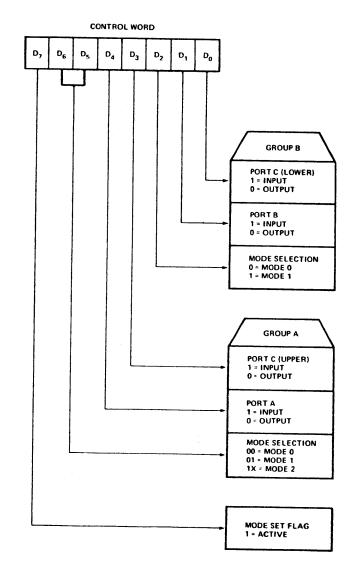

| 3-15   | MODE DEFINITION CONTROL WORD FORMAT                               | 3-55 |

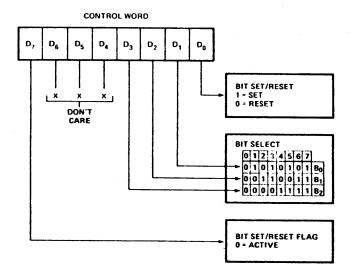

| 3-16   | BIT SET/RESET CONTROL WORD FORMAT                                 | 3-57 |

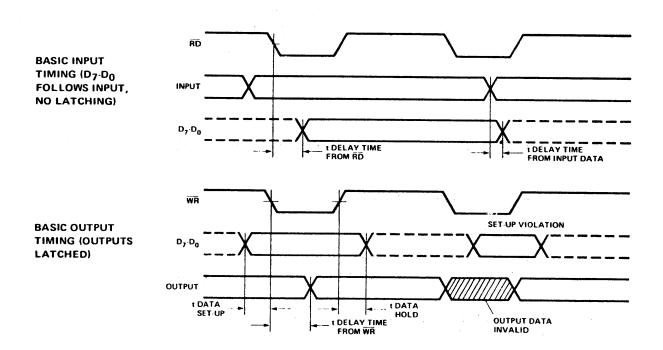

| 3-17   | 8255 MODE 0 TIMING                                                | 3-58 |

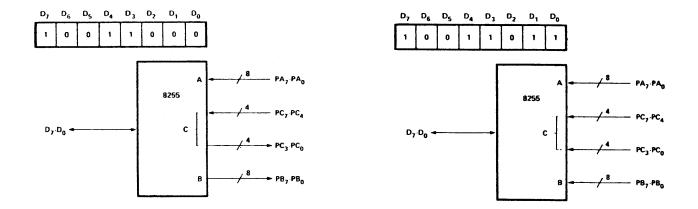

| 3-18   | EXAMPLES OF MODE 0 CONFIGURATION                                  | 3-59 |

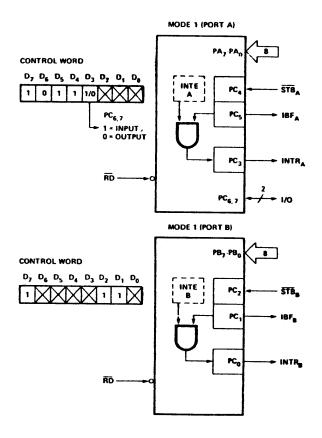

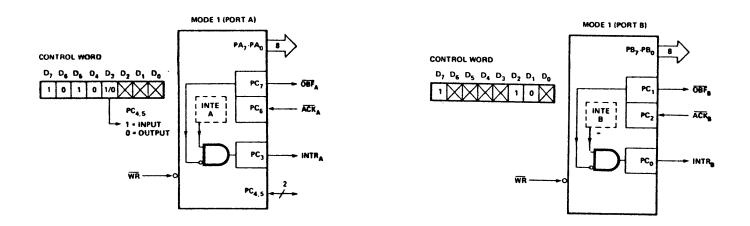

| 3-19   | MODE 1 INPUT CONFIGURATION                                        | 3-61 |

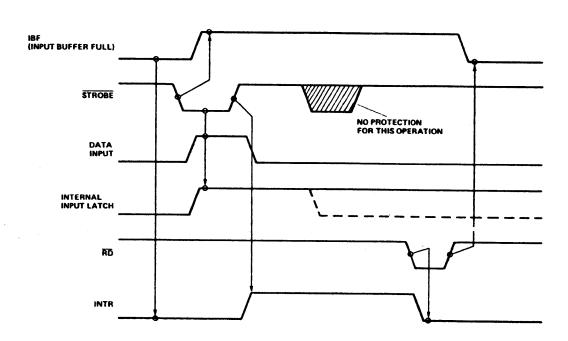

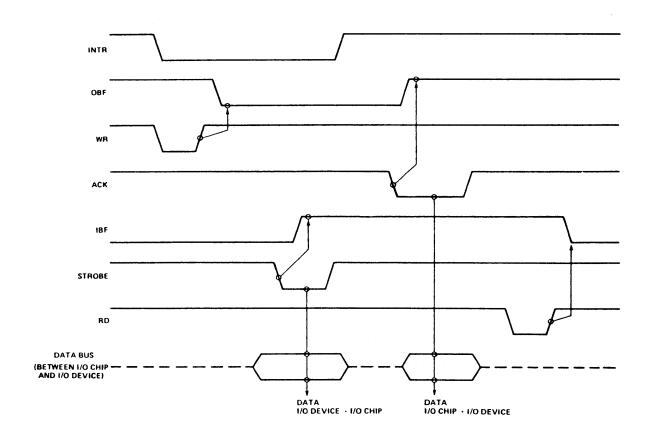

| 3-20   | 8255 MODE 1 INPUT TIMING                                          | 3-61 |

| 3-21   | MODE 1 OUTPUT CONFIGURATION                                       | 3-63 |

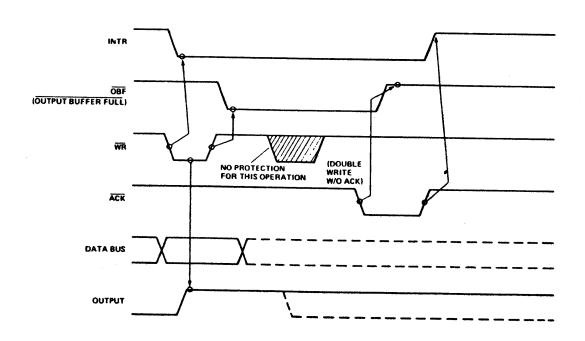

| 3-22   | MODE 1 BASIC OUTPUT TIMING                                        | 3-63 |

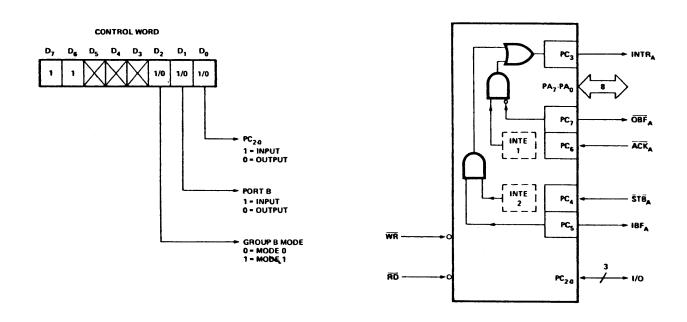

| 3-23   | MODE 2 PORT CONFIGURATION                                         | 3-65 |

| 3-24   | MODE 2 TIMING                                                     | 3-65 |

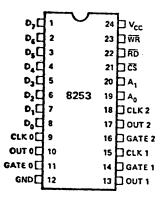

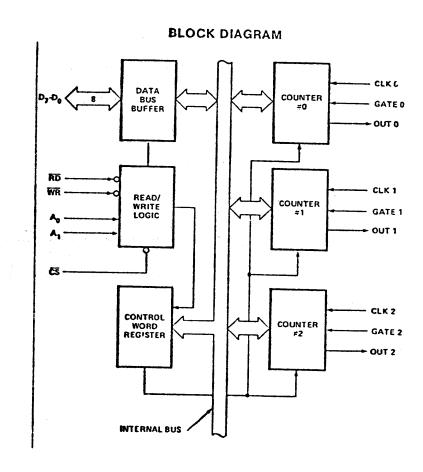

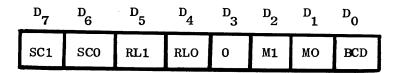

| 3-25   | 8253 FUNCTIONAL DIAGRAM                                           | 3-75 |

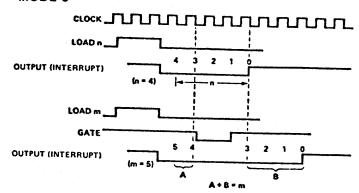

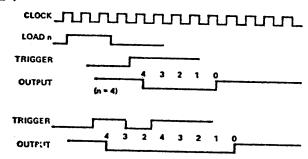

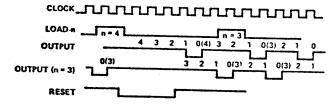

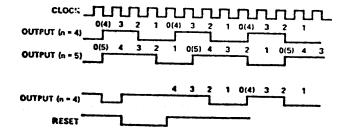

| 3-26   | 8253 TIMING DIAGRAMS                                              | 3-79 |

| 3-27   | 8253 PROGRAMMING FORMAT EXAMPLE                                   | 3-82 |

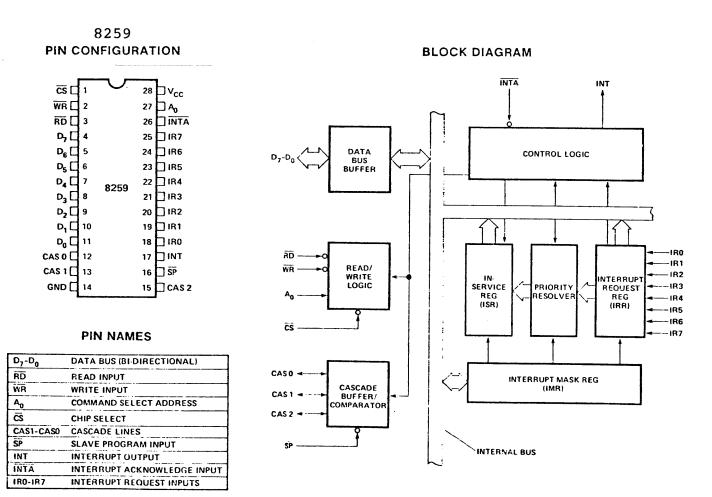

| 3-28   | 8259 INTERRUPT CONTROLLER                                         | 3-89 |

| 3-29   | INITIALIZATION SEQUENCE AS APPLICABLE TO SBC 80/20 IMPLEMENTATION | 3-96 |

| 3-30   | 8259 INITIALIZATION CONTROL WORD FORMATS                          | 3-98 |

| 3-31   | 8259 OPERATION COMMAND WORD FORMATS                               | 3-99 |

# LIST OF ILLUSTRATIONS (Cont d)

| Figure |                               | Page |

|--------|-------------------------------|------|

| 4-1    | ASYNCHRONOUS OPERATION        | 4-5  |

| 4-2    | SYNCHRONOUS OPERATION         | 4-6  |

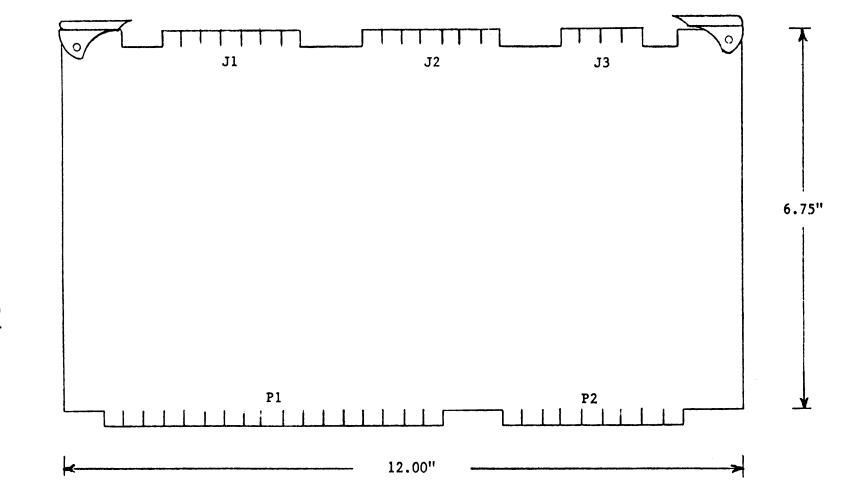

| 5-1    | SBC 80/20 EDGE CONNECTORS     | 5-4  |

| 7-1    | BUS EXCHANGE TIMING           | 7-4  |

| 7-2    | CONTINUOUS BUS CONTROL TIMING | 7-5  |

| 7-3    | SBC 80/20 BOARD OUTLINE       | 7-10 |

#### CHAPTER 1

#### INTRODUCTION

The SBC 80/20 and SBC 80/20-4 are members of Intel's complete line of OEM computer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer based solutions for OEM applications. The SBC 80/20 and SBC 80/20-4 are complete computer systems each on a single 6.75-by-12 inch printed circuit card. The CPU, system clock, read/write memory, non-volatile read-only-memory, I/O ports and drivers, serial communications interface, interval timer, interrupt controller, bus control logic and drivers all reside on the board.

Intel's powerful 8-bit n-channel MOS 8080A CPU, fabricated on a single LSI chip, is the central processor for both the SBC 80/20 and SBC 80/20-4. The 8080A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs providing both single and double precision operators. The 8080A has a 16-bit program counter which allows direct addressing of up to 64K bytes of memory. An external stack, located within any portion of memory, may be used as a last in/first out stack to store and retrieve the contents of the program counter, flags, accumulator and all of the six general purpose registers. A sixteen bit stack pointer controls the addressing of this external stack. This stack provides almost unlimited subroutine nesting. Sixteen-line address and eight-line bi-directional data busses are used to facilitate easy interface to memory and I/0.

interface on the board in conjunction with the USART provides a direct interface to RS232C compatible devices and asynchronous and synchronous modems.

The RS232C, serial data lines and signal ground lines are brought out to a 26-pin edge connector that mates with RS232C compatible flat or round cables.

A programmable timing device, Intel's 8253 Interval Timer, is also included on the board. The 8253 can be programmed to generate accurate time delays. Instead of writing inefficient timing loops into the system software, the programmer can configure the 8253 to match his requirements, initialize one of the 8253 counters with the desired quantity, and command the 8253 to begin counting out the delay. The 8253 includes three counters that can be programmed to function independently in a variety of modes. In addition to providing an interrupt on terminal count (mode 0), an 8253 counter can be configured as a programmable one-shot (mode 1), a rate generator (mode 2) or a square-wave rate generator (mode 3). One of the counters is wired to provide the baud rate frequency to the Serial I/O Interface.

An interrupt may originate from any of 27 different sources: parallel I/O interface (4), serial I/O interface (3), interval timer (2), power fail logic (1) external modules (9) or external I/O (8). Any of the 27 interrupt lines can be jumpered to one of the eight priority level inputs to an Intel 8259 Interrupt Controller. The 8259 resolves priority among all eight levels according to an algorithm which is program-selected by the user. A variety of priority

algorithms is available to the programmer so that the manner in which the interrupt requests are processed by the 8259 can be configured to match the system requirements. The priority assignments can be reconfigured dynamically at any time during the main program. The user can select any of the following modes:

- . Fully nested

- . Auto-rotating priority

- . Specific priority

- . Polled

The 8259 is programmed by the system software as an I/O peripheral.

Memory and I/O expansion may be achieved using standard Intel boards. Memory may be expanded to 65,536 bytes by adding user specified combinations of SBC-016 16K byte RAM board, SBC-406 6K byte PROM board, SBC-416 16K byte PROM board, and SBC 104/108 combination memory and I/O boards. Input/output capacity may be expanded in increments of 4 input ports and 4 output ports using SBC-508 Input/Output boards. Expandable backplanes and cardcages are available to support multi-board systems.

The development cycle of SBC 80/20 based OEM products may be significantly reduced using the Intellec Microcomputer Development System. The resident assembler, text editor, and system monitor greatly simplify the design, development, and debug of SBC 80/20 based system software. A unique In-Circuit Emulator (ICE-80) option provides the capability of executing and debugging OEM system software directly on the SBC 80/20.

Intel's high-level language, PL/M, can be used to significantly decrease the time required to develop OEM system software. PL/M is now available as a resident Intellec Microcomputer Development System option (PL/M-80).

#### CHAPTER 2

#### FUNCTIONAL/PROGRAMMING CHARACTERISTICS

This chapter briefly describes the organization of the SBC 80/20's from two points of view. The principal functions performed by the hardware are identified and the general flow is illustrated in Section 2.1. This section is intended as an introduction to the detailed information provided in Chapter 3, Theory of Operations. Section 2.2 summarizes the information needed by the programmer to initialize and access the memory and I/O facilities on the SBC 80/20.

#### 2.1 FUNCTIONAL DESCRIPTION

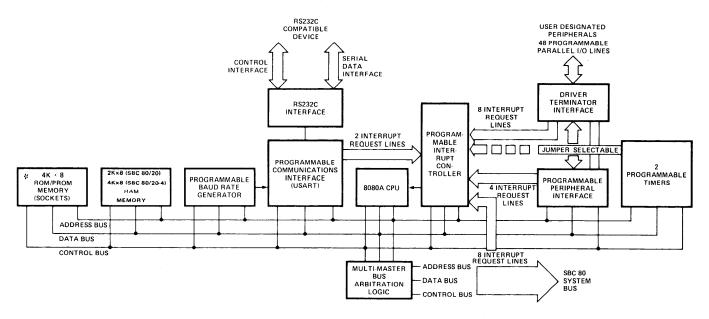

To facilitate the following description, the SBC 80/20 and SBC 80/20-4 can be divided into eight major functional blocks as shown in Figure 2-1:

- 1) CPU Set

- 2) Bus Interface (including Multi-Master Bus Control)

- 3) Random Access Memory (RAM)

- 4) Read Only Memory (ROM/PROM)

- 5) Serial I/O Interface

- 6) Parallel I/O Interface

- 7) Interval Timer

- 8) Interrupt Controller

The <u>CPU Set</u> consists of the 8080A Control Processor, the 8224 Clock Generator and the 8238 System Controller. The CPU Set is the heart of the SBC 80/20. It performs all system processing functions and provides a stable timing reference for all other circuitry

\*8 X8 ROM/EPROM available using Intel's 2716 EPROM or Intel 8316B masked ROM on either board.

FIGURE 2-1. SBC 80/20 AND SBC 80/20-4 BLOCK DIAGRAM

in the system. The CPU generates all of the address and control signals necessary to access memory and I/O ports both on the SBC 80/20 and external to the SBC 80/20. The CPU Set is capable of fetching and executing any of the 8080's instructions. The CPU Set responds to interrupt requests originating both on and off the SBC 80/20, and to WAIT requests from memory or I/O devices having an access time which is slower than that required for the SBC 80/20's 8080A cycle time.

The <u>Bus Interface</u> allows the SBC 80/20 to use a common system bus with other master devices such as other CPU's or DMA devices, thus sharing common memory and I/O resources. The Bus Interface includes an Intel Bus Controller, as well as circuits for the generation of the Bus Clock (BLCK/) signal. The Bus Controller arbitrates all SBC 80/20 requests for use of the system bus, synchronously with respect to the Bus Clock. When the SBC 80/20 acquires control of the bus, the Bus Controller generates the appropriate memory or I/O command signal, gates the address onto the system address lines and gates data on/off the system bus. Operations between the CPU and onboard resources (i.e., RAM, PROM, I/O) require no use of the system Bus.

The Random Access Memory (RAM) section provides the user with 2048 (2K) X 8-bits (SBC 80/20) or 4096 (4K) X 8-bits (SBC 80/20-4) of read/write storage, using eight Intel 2113 (SBC 80/20) or 2114 (SBC 80/20-4) static RAM devices. The 2113 or 2114 RAM requires neither refreshing nor clock inputs to operate. All operations between the CPU and on-board RAM require no WAIT states.

The Read Only Memory (ROM/EPROM) section provides the user with the necessary provisions for installing 4096 X 8-bit or 8192 X 8-bits of ROM or EPROM. Each SBC 80/20 has four 24-pin sockets that can accept either

Intel 8708 Erasable and Electrically Programmable Read Only Memory (EPROM) chips (1024 X 8-bits each) or Intel 8308 Static MOS Read Only Memory (ROM) chips (also 1024 X 8-bits each). Each SBC 80/20 also includes the option of installing four 2048 X 8-bit Intel 2716 Erasable and Electronically Programmable Read Only Memory Chips. Both boards include the necessary acknowledgement and address decoding circuitry. All CPU accesses to this on-board ROM/EPROM area require no CPU WAIT states.

The <u>Serial I/O Interface</u>, using Intel's 8251 USART device, provides a full duplex RS232 serial data communications channel that can be programmed to operate with most of the current serial data transmission protocols. Synchronous or asynchronous mode, baud rate, character length, number of stop bits and the choice of even, odd or no parity are all program selectable.

The <u>Parallel I/O Interface</u>, using two Intel 8255 Programmable Peripheral interface devices, provides 48 signal lines for the transfer and control of data to or from peripheral devices. Sixteen lines already have a bi-directional driver and termination network permanently installed. This bi-directional network allows these sixteen lines to be inputs, outputs, or bi-directional (selected via jumpers). The remaining 32 lines, however, are uncommitted. Sockets are provided for the installation of drivers or termination networks as required to meet the specific needs of the user system.

The <u>Interval Timer</u> capability is implemented with an Intel 8253 Programmable Interval Timer. The 8253 includes three 16-bit BCD or binary counters which can be programmed by the user to perform a variety of timing functions. The outputs from the first two counters can

be used as interrupt request lines, thus allowing easy implementation of such features as a real-time clock or a program monitor alarm.

The output from the third counter is applied to the Serial I/O Interface. When properly programmed, this counter can provide the desired band rate frequency for serial communications.

The SBC 80/20 also includes an Intel 8259 Interrupt Controller. The 8259 device resolves priority among eight different interrupt levels according to an algorithm that is programmed by the user. A jumper area in the interrupt section permits the user to connect any of nine external bus interrupt lines or 17 on-board interrupt requests to the eight priority level inputs to the 8259. Thus, by jumpering various interrupt lines to the appropriate priority levels and by programming the 8259 for the desired algorithm, the user can easily configure a custom interrupt structure.

#### 2.2 PROGRAMMING SUMMARY

This section summarizes the SBC 80/20 memory and I/O addressing information that is necessary for a programmer to fully utilize the system's many features.

### 2.2.1 MEMORY ADDRESS ASSIGNMENT

The SBC 80/20 and 80/20-4 RAM can be assigned (via jumpers) to any one of the four 16K address boundaries within the total 64K address space supported by the 8080A. It will always reside at the end of the selected 16K block. Table 2-1 lists the blocks of address space that can be selected for the Random Access Memory (RAM).

Memory addresses for the ROM/EPROM on the SBC 80/20 always begin at memory location zero.

TABLE 2-1. RAM ADDRESS SPACE

| JUMP       | SELECTED RAM ADDRESS SPACE (hex) |                  |  |

|------------|----------------------------------|------------------|--|

| CONNECTION | 2K (SBC 80/20)                   | 4K (SBC 80/20-4) |  |

| 120-121    | 3800-3FFF                        | 3000-3FFF        |  |

| 119-121    | 7800-7FFF                        | 7000-7FFF        |  |

| 118-121    | B800-BFFF                        | BOOO-BFFF        |  |

| 117-121    | F800-FFFF                        | F000-FFFF        |  |

#### 2.2.2 DEDICATED I/O ADDRESSES

The SBC 80/20 includes a number of I/O devices that are accessed as dedicated I/O addresses. Table 2-2 summarizes the dedicated I/O port addresses, the I/O devices, the sections within the manual where each I/O device is described and the specific function which is accessed by an input or output instruction to a particular I/O address.

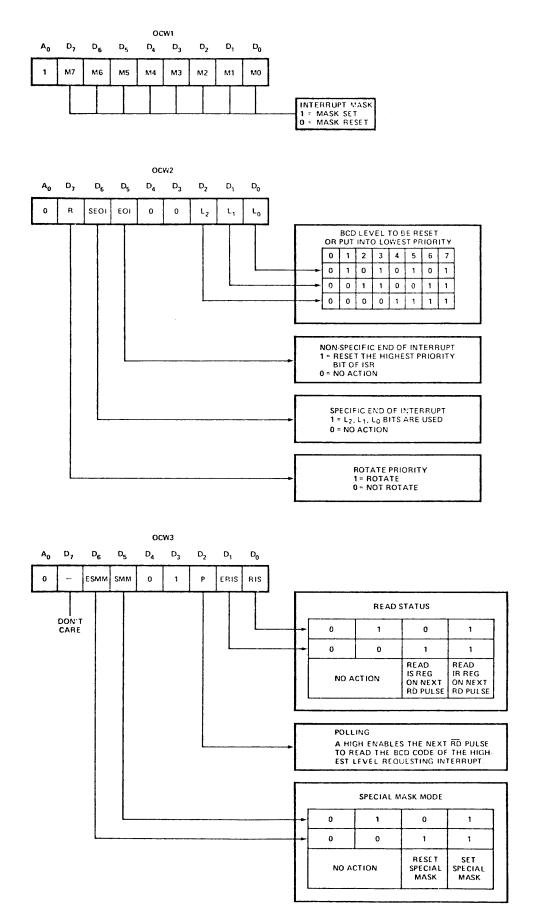

The Initialization Control Word (ICW1, ICW2 and ICW3) registers and the Operation Control Word (OCW1, OCW2 and OCW3) registers in the 8259 Interrupt Controller share several I/O addresses and are loaded in a particular sequence (indicated by various data bits in the control word). The 8259's Interrupt Requests Register (IRR) and In Service Register (ISR) also share an I/O address; the current contents of OCW3 dictate which can be read or whether the current interrupt level is read (See Section 3.10). Because this information could not be summarized within the format of Table 2-2, we have provided Table 2-3 as a summary of the 8259's basic operation.

TABLE 2-2. I/O PORT ADDRESSING

|                                | ·                                         |                                                       |                                                           |

|--------------------------------|-------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|

| I/O PORT ADDRESS (hexadecimal) | I/O<br>DEVICE<br>(reference<br>section)   | INPUT FUNCTION                                        | OUTPUT FUNCTION                                           |

| D4                             | Power Fail<br>(3.11)                      | Read Power Fail Status                                | Reset Power Fail latch.                                   |

| D5                             | System Bus<br>Override<br>(3.2)           | Not used                                              | Set or reset override control (using data bus line 0).    |

| D6                             | LED Diagnostic<br>Indicator<br>(3.6)      | ♪ Not used                                            | Flash LED for 1<br>millisecond                            |

| D7                             | Not used                                  | -                                                     | _                                                         |

| D8 or DA D9 or DB              | 8259<br>Interrupt<br>Controller<br>(3.10) | Various read functions (see Table 2-3)                | Various write functions<br>(see Table 2-3)                |

| DC<br>DD<br>DE<br>DF           | 8253<br>Interval<br>Timer<br>(3.9)        | Read counter 0 Read counter 1 Read counter 2 Not used | Load counter 0 Load counter 1 Load counter 2 Mode control |

| E4<br>E5<br>E6<br>E7           | 8255 #1 (3.8)                             | Read port A<br>Read port B<br>Read port C             | Write port A Write port B Write port C Control            |

| E8<br>E9<br>EA<br>EB           | 8255 #2 (3.8)                             | Read port A<br>Read port B<br>Read port C             | Write port A Write port B Write port C Control            |

| EC or EE ED or EF              | 8251<br>USART<br>(3.7)                    | Data in<br>Read Status                                | Data out<br>Control                                       |

Either port address may be used.

Though these port addresses are not used by the SBC 80/20, they are not available for use by external I/O devices.

Raud Rate Generator Counter

TABLE 2-3. 8259 OPERATION SUMMARY

| I/O PORT         | DATA BITS |    | INPUT OPERATION                                                          |  |

|------------------|-----------|----|--------------------------------------------------------------------------|--|

| ADDRESS<br>(hex) | D4        | D3 |                                                                          |  |

| D8 or DA         | -         | -  | Read IRR, ISR or current interrupt level (depending on contents of OCW3) |  |

| D9 or DB         | -         | -  | Read Interrupt Mask Register (IMR)                                       |  |

|                  |           |    | OUTPUT OPERATION                                                         |  |

| D8 or DA         | 0         | 0  | Load OCW2                                                                |  |

| D8 or DA         | 0         | 1  | Load OCW3                                                                |  |

| D8 or DA         | 1         | Х  | Load ICW1                                                                |  |

| D9 or DB         | Х         | X  | Load OCW1, ICW2 or ICW3<br>(depending on sequence)                       |  |

#### CHAPTER 3

#### THEORY OF OPERATION

In the preceding chapter we introduced and briefly defined each of the SBC 80/20 functional blocks. In this chapter we shall describe how each block performs its particular function(s). The text will constantly refer to the SBC 80/20 schematics, provided in Appendix A.

Note: Both active-high (positive true) and active-low (negative true) signals appear on the SBC 80/20 schematics. To eliminate any confusion when reading this chapter, the following convention will be adhered to: whenever a signal is active-low, its mnemonic is followed by a slash; for example, MRDC/ means that the level on that line will be low when the memory read command is true (active). If the signal is subsequently inverted, thus making it active-high, the slash is omitted; for example, MRDC means that the level on that line will be high when the memory read command is true.

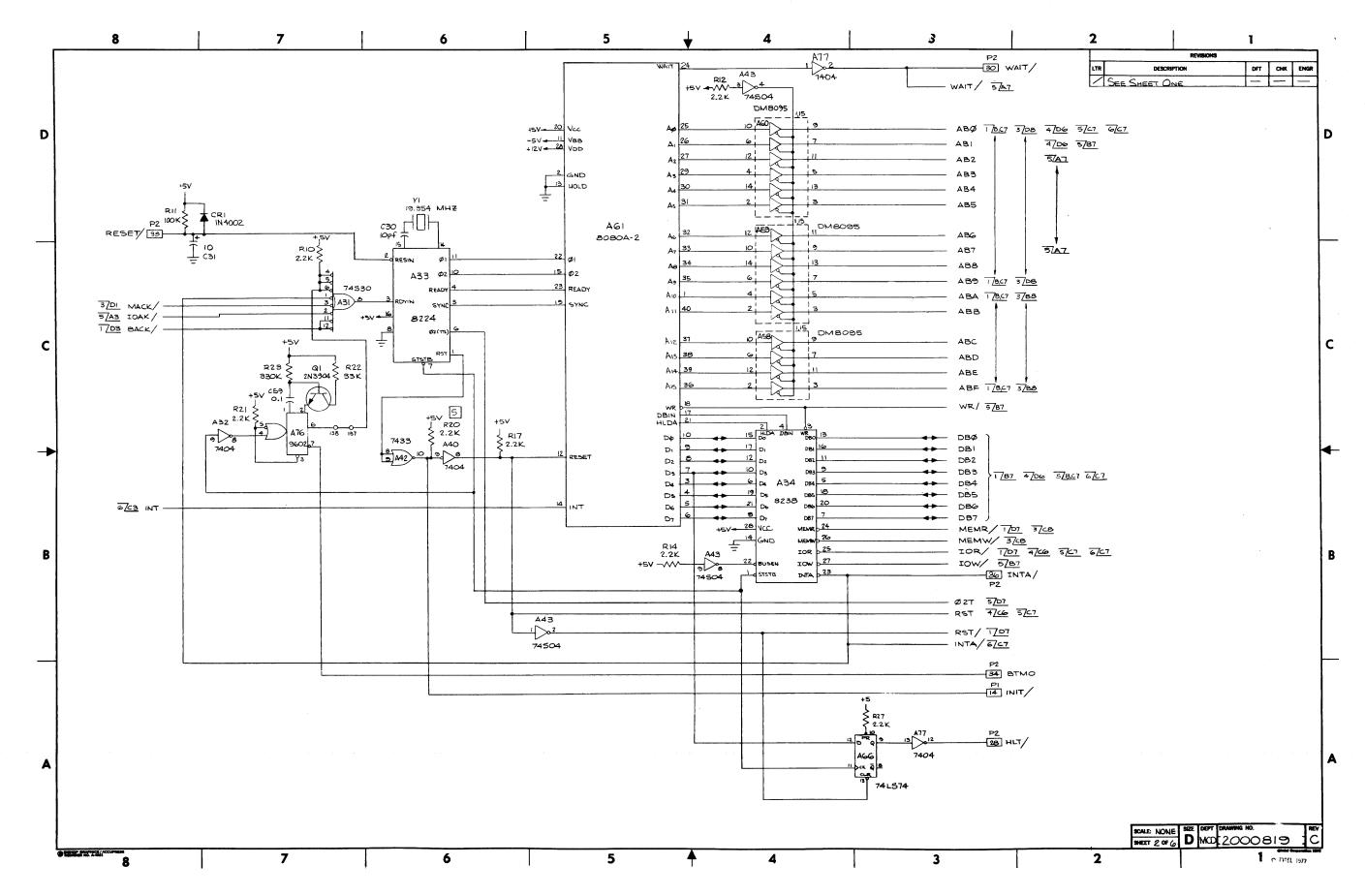

#### 3.1 THE CPU SET

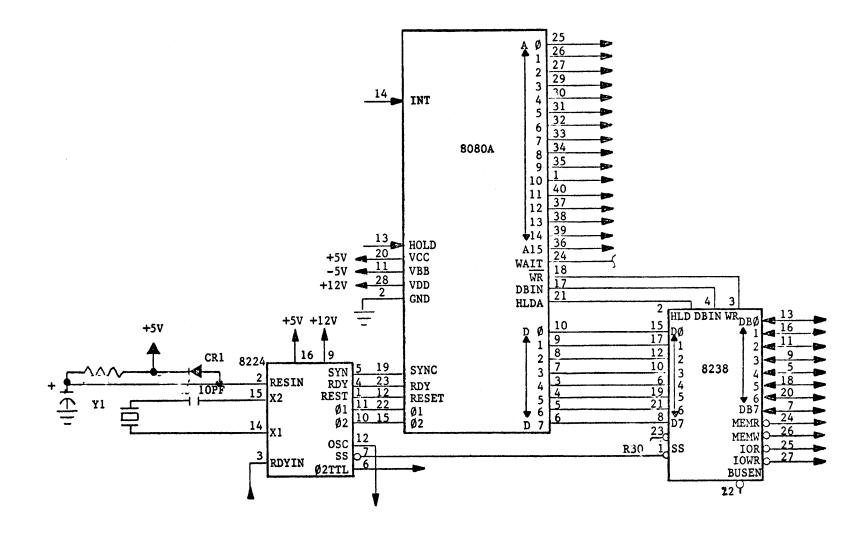

The CPU Set consists of three Intel® integrated circuit devices:

- \* 8080A Central Processor Unit

- \* 8224 Clock Generator

- \* 8238 System Controller

and a 19.354 MHz crystal that establishes the frequency of oscillation for the 8224 device via a 10pF capacitor, as shown in Figure 3-1. Together, the elements in the CPU Set perform all central processing functions. The following paragraphs describe how the elements within the CPU Set interact with all other logic on the SBC 80/20. The interaction between IC's within the CPU Set, however, is not described. Instead, the reader is referred to the Intel® "8080 Microcomputer Systems User's Manual" for a detailed

FIGURE 3-1. THE CPU SET

description of the 8080, 8224 and 8238 devices.

The CPU Set is shown on sheet 2 of the SBC 80/20 schematic (Appendix A).

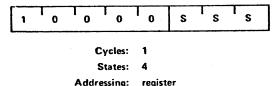

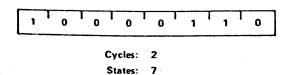

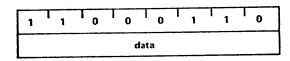

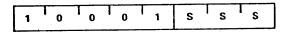

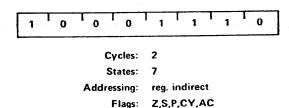

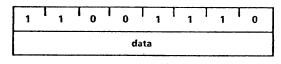

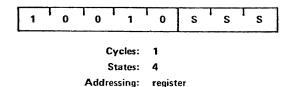

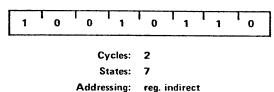

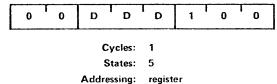

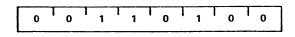

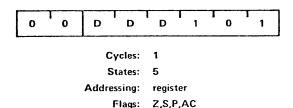

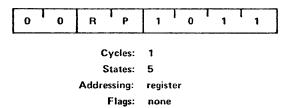

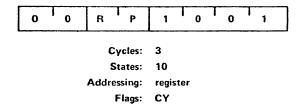

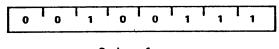

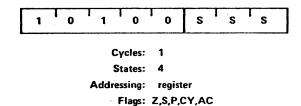

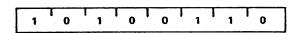

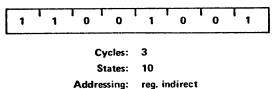

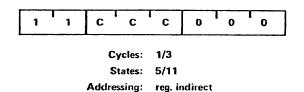

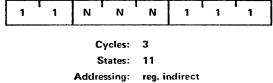

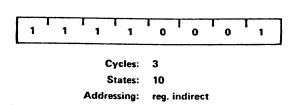

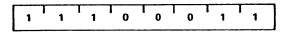

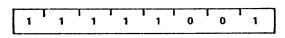

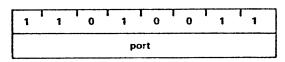

#### 3.1.1 INSTRUCTION TIMING

The activities of the CPU Set are cyclical. The CPU fetches an instruction, performs the operations required, fetches the next instruction, and so on. This orderly sequence of events requires precise timing. The 8224 Clock Generator, provides the primary timing reference for the CPU Set. The crystal in conjunction with a 10pF capacitor tunes an oscillator within the 8224 to precisely 19.354 MHz. The 8224 "divides" the oscillations by nine to produce two-phase timing inputs ( $\emptyset$ 1 and  $\emptyset$ 2) for the 8080. The  $\emptyset$ 1 and  $\emptyset$ 2 signals define a cycle of approximately 465 ns. duration. A TTL level phase 2 ( $\emptyset$ 2T) signal is also derived and made available to external logic. All processing activities of the CPU Set are referred to the period of the  $\emptyset$ 1 and  $\emptyset$ 2 clock signals.

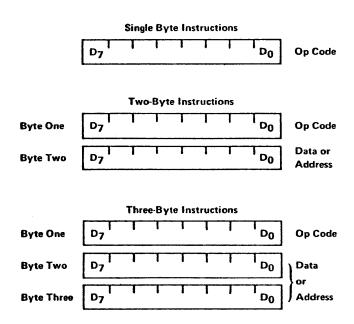

Within the 8080 CPU Set, an <u>instruction cycle</u> is defined as the time required to fetch and execute an instruction. During the fetch, a selected instruction (one, two or three bytes) is extracted from memory and deposited in the CPU's operating registers. During the execution part, the instruction is decoded and translated into specific processing activities.

Every instruction cycle consists of one, two, three, four or five machine cycles. A <u>machine cycle</u> is required each time the CPU accesses memory or an I/O port. The fetch portion of an instruction

cycle requires one machine cycle for each byte to be fetched. The duration of the execution portion of the instruction cycle depends on the kind of instruction that has been fetched. Some instructions do not require any machine cycles other than those necessary to fetch the instruction; other instructions, however, require additional machine cycles to write or read data to/from memory or I/O devices.

Each machine cycle consists of three, four or five states. A <u>state</u> is the smallest unit of processing activity and is defined as the interval between two successive positive-going transitions of the  $\emptyset 1$  clock pulse.

There are three exceptions to the defined duration of a state. They are the WAIT state, the hold (HLDA) state and the halt (HLTA) state. Because the WAIT, the HLDA, and the HLTA states depend upon external events, they are by their nature of indeterminate length. Even these exceptional states, however, must be synchronized with the pulses of the driving clock. Thus the duration of all states, including these, are integral multiples of the clock pulse.

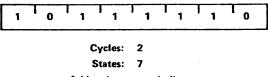

To summarize, then, each <u>clock period</u> marks a <u>state</u>; three to five <u>states</u> summarize a <u>machine cycle</u>; and one to five <u>machine cycles</u> comprise an <u>instruction cycle</u>. A full instruction cycle requires anywhere from four to seventeen states for its completion, depending on the kind of instruction involved.

There is just one consideration that determines how many machine cycles are required in any given instruction cycle: the number of times that the processor must reference a memory address or an I/O

address, in order to fetch and execute the instruction. Like many processors, the 8080 is so constructed that it transmits one address per machine cycle. Thus, if the fetching and execution of an instruction requires two memory references, then the instruction cycle associated with that instruction consists of two machine cycles. If five such references are called for, then the instruction cycle contains five machine cycles.

Every instruction cycle has at least one reference to memory, during which the instruction is fetched. An instruction cycle must always have a fetch, even if the execution of instruction requires no further references to memory. The first machine cycle in every instruction cycle is therefore a FETCH. Beyond that, there are no fast rules. It depends on the kind of instruction. The input (INP) and the output (OUT), instructions each require three machine cycles: a FETCH, to obtain the instruction; a MEMORY READ, to obtain the address of the object peripheral; and an INPUT or an OUTPUT machine cycle, to complete the transfer.

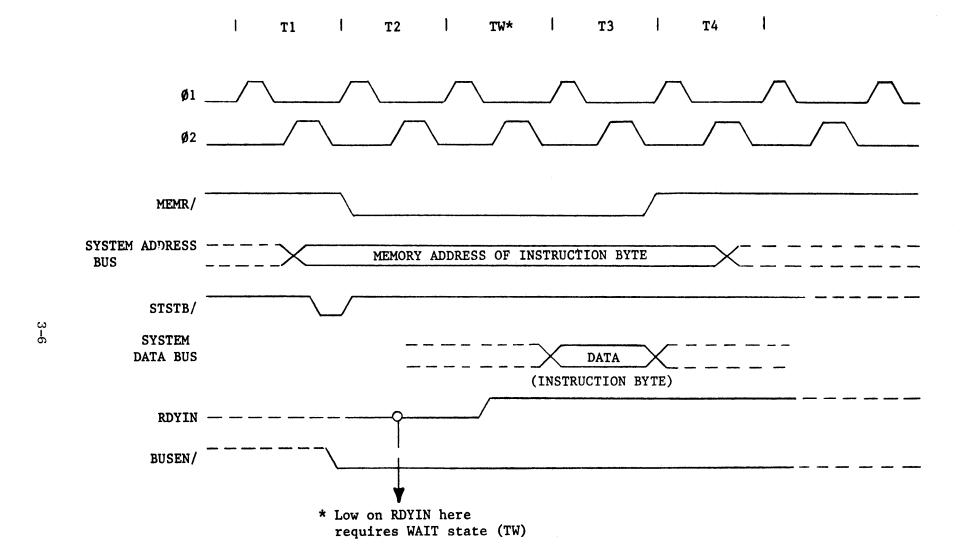

Every machine cycle within an instruction cycle consists of three to five active states (referred to as T1, T2, T3, T4, and T5). The actual number of states depends upon the instruction being executed, and on the particular machine cycle within the greater instruction cycle. Figure 3-2 shows the timing relationships in a typical FETCH machine cycle. Events that occur in each state are referred to transitions of the Ø1 and Ø2 clock pulses.

At the beginning of each machine cycle (in state T1), the 8080 activates its SYNC output and issues status information on its data

FIGURE 3-2. TYPICAL FETCH MACHINE CYCLE

bus. The 8224 accepts SYNC and generates an active-low status strobe (STSTB/) as soon as the status data is stable on the data bus. The status information indicates the type of machine cycle in progress. The 8238 System Controller accepts the status bits from the 8080 and STSTB/ from the 8224, and uses them to generate the appropriate control signals (MEMR/, MEMW/, IOR/ and IOW/) for the current machine cycle.

The rising edge of  $\emptyset$ 2 during T1 loads the processor's address lines (ABO-ABF). These lines become stable within a brief delay of the  $\emptyset$ 2 clocking pulse, and they remain stable until the first  $\emptyset$ 2 pulse after state T3. This gives the processor ample time to read the data returned from memory.

Once the processor has sent an address to memory, there is an opportunity for the memory to request a WAIT. This it does by pulling the 8224°s RDYIN line low. As long as the RDYIN line remains low, the CPU Set will idle, giving the memory time to respond to the addressed data request. The 8224 synchronizes RDYIN with internal processor timing and applies the result to the 8080°s READY input. The processor responds to a wait request by entering an alternative state (TW) at the end of T2, rather than proceeding directly to the T3 state. A wait period may be of indefinite duration. The 8080 remains in the waiting condition until its READY line again goes high. The cycle may then proceed, beginning with the rising edge of the next Ø1 clock. A WAIT interval will therefore consist of an integral number of TW states and will always be a multiple of the clock period.

The events that take place during the T3 state are determined by the kind of machine cycle in progress. In a FETCH machine cycle, the CPU Set interprets the data on its data bus as an instruction. During a MEMORY READ, signals on the same bus are interpreted as a data word. The CPU Set itself outputs data on this bus during a MEMORY WRITE machine cycle. And during I/O operations, the CPU Set may either transmit or receive data, depending on whether an INPUT or an OUTPUT operation is involved. Consider the following two examples.

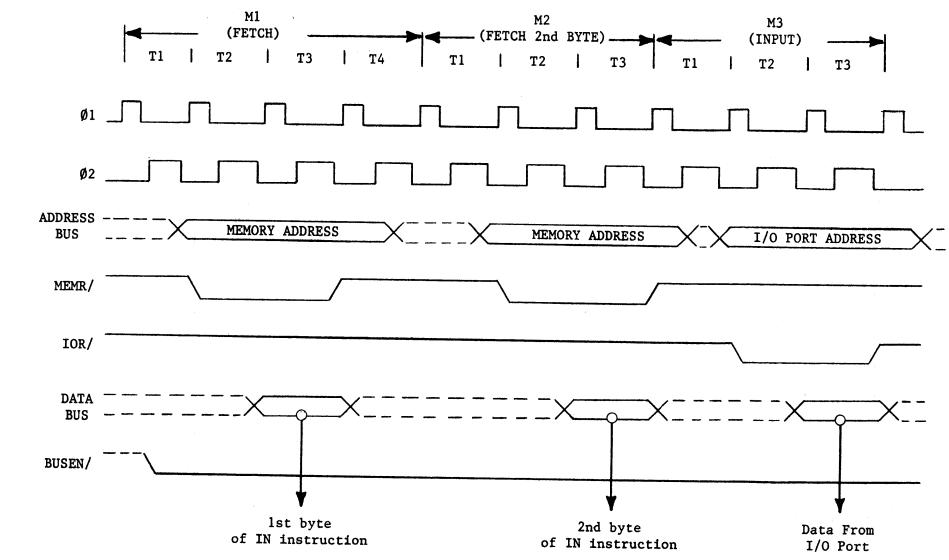

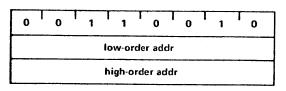

Figure 3-3 illustrates the timing that is characteristic of an input instruction cycle. During the first machine cycle (M1), the first byte of the two-byte IN instruction is fetched from memory. The 8080 places the 16-bit memory address on the system bus near the end of state T1. The 8238 activates the memory read control signal (MEMR/) during states T2 and T3 (and any intervening wait states, if required). During the next machine cycle (M2), the second byte of the instruction is fetched. During the third machine cycle (M3), the IN instruction is executed. The 8080 duplicates the 8-bit I/O address on address lines ABO-7 and AB8-F. The 8238 activates the I/O read control signal (IOR/) during states T2 and T3 of this cycle. The system bus enable input (BUSEN/) to the 8238 is always held low to allow for normal operation of the data bus buffers and the read/ write control signals. If BUSEN/ goes high the data bus output buffers and control signal buffers are forced into a high-impedance state.

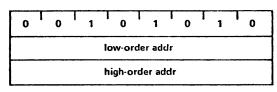

Figure 3-4 illustrates an instruction cycle during which the

FIGURE 3-3. INPUT INSTRUCTION CYCLE

FIGURE 3-4. OUTPUT INSTRUCTION CYCLE

CPU Set outputs data. During the first two machine cycles (M1 and M2), the CPU Set fetches the two-byte OUT instruction. During the third machine cycle (M3), the OUT instruction is executed. The 8080 duplicates the 8-bit I/O address on lines ABO-7 and AB8-F. The 8238 activates the I/O write control signal (IOW/) at the beginning of state T2 of this cycle. The 8238 outputs the data onto the system bus at the end of state T2. Data on the bus remains stable throughout the remainder of the machine cycle.

Observe that a RDYIN signal is necessary for completion of an output machine cycle. Unless such an indication is present, the processor enters the TW state, following the T2 state. Data on the output lines remains stable in the interim, and the processing cycle will not proceed until the RDYIN line again goes high.

Note: The 8238 System Controller generates a write control signal (IOW/ or MEMW/) at the beginning of all write cycles. The IOW/ or MEMW/ signal occurs earlier than the 8080's WR/ output. IOW/ and MEMW/ are advanced write commands that can allow a ready indication to be returned to the CPU Set early enough to avoid an unnecessary wait state. The advanced write command (IOW/ or MEMW/) is subsequently synchronized with the 8080's WR/ output to produce a system write command (MWT/ or IOWT/) that causes the I/O or memory device to actually write the data, later in the cycle.

The negative-going leading edge of WR/ is referred to the rising edge of the first  $\emptyset 1$  clock pulse following T2. Thus, WR/ coincides with the appearance of stable data on the system bus. WR/ remains low until re-triggered by the leading edge of  $\emptyset 2$ , during the state following T3. Note that any TW states intervening between T2 and T3 of the output machine cycle will necessarily extend WR/.

All processor machine cycles consist of at least three states: T1, T2, and T3 as just described. If the CPU Set has to wait for a RDYIN response, then the machine cycle may also contain one or more TW states. During the three basic states, data is transferred to or from the CPU Set.

After the T3 state, however, it becomes difficult to generalize. T4 and T5 states are available, if the execution of a particular instruction requires them. But not all machine cycles make use of these states. It depends upon the kind of instruction being executed, and on the particular machine cycle within the instruction cycle. The processor will terminate any machine cycle as soon as its processing activities are completed, rather than proceeding through the T4 and T5 states every time. Thus the 8080 may exit a machine cycle following the T3, the T4, or the T5 state and proceed directly to the T1 state of the next machine cycle.

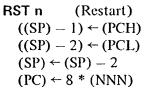

#### 3.1.2 INTERRUPT SEQUENCES

The 8080 has the built-in capacity to handle external interrupt requests. Peripheral logic can initiate an interrupt simply by driving the processor's interrupt (INT) line high. The interrupt (INT) input is asynchronous, and a request may therefore originate at any time during any instruction cycle. Internal logic re-clocks the external request, so that a proper correspondence with the driving clock is established. An interrupt request (INT) acts in coincidence with the \$\phi 2\$ clock to set the internal interrupt latch. This event takes place during the last state of the instruction cycle in

which the request occurs, thus ensuring that any instruction in progress is completed before the interrupt can be processed.

enabled interrupt request resembles an ordinary FETCH machine cycle in most respects. The contents of the program counter are latched onto the address lines during T1, but the counter itself is not incremented during the INTERRUPT machine cycle, as it otherwise would be. In this way, the pre-interrupt status of the program counter is preserved, so that data in the counter may be saved in the stack. This in turn permits an orderly return to the interrupted program after the interrupt request has been processed.

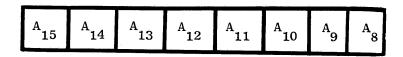

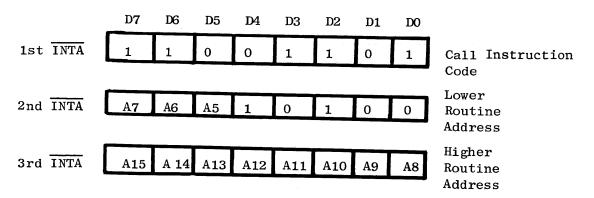

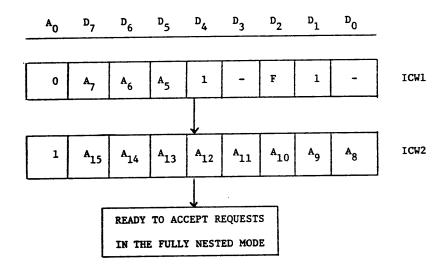

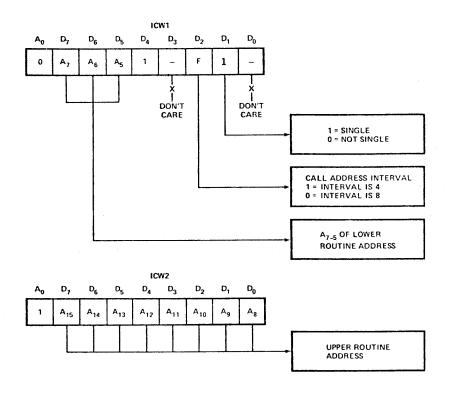

The 8238's INTA/ output (to connector pin P2-40) is normally used to gate an "interrupt instruction" onto the system data bus during state T3. The interrupt instruction is usually a one-byte RST but on the SBC 80/20 it is a three-byte CALL instruction which causes program control to branch to an interrupt routine. When the CALL interrupt instruction is supplied by the 8259 Interrupt controller, the 8238 generates an INTA/ pulse for each of the three bytes. INTA/ also acknowledges the arrival of the interrupt instruction at the RDYIN input on the 8224.

#### 3.1.3 HALT SEQUENCES

When a halt instruction (HLT) is executed, the 8080 enters the halt state after state T2 of the next machine cycle. There are two ways in which the 8080 can exit the halt state:

- . A high on the 8224 reset input (RESIN/) will always reset the 8080 to state T1; reset also clears the program counter.

- . An interrupt (i.e., INT goes high while INTE is enabled) will cause the 8080 to exit the halt state and enter state T1 on the rising edge of the next  $\emptyset$ 1 clock pulse.

Note: The interrupt enable (INTE) flag must be set when the halt state is entered; otherswise, the 8080 will only be able to exit via a reset signal.

#### 3.1.4 START-UP SEQUENCE

When power is applied initially to the 8080, the processor begins operating immediately. The contents of its program counter, stack pointer, and the other working registers are naturally subject to random factors and cannot be specified. For this reason, the CPU Set power-up sequence begins with a reset. An external RC network is connected to the 8224°s RESIN/input. The slow transition of the power supply rise is sensed by an internal Schmitt Trigger which converts the slow transition into a clean, fast edge on the RESIN/line when the input level reaches a predetermined value.

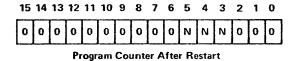

An active RESIN/ input to the 8224 produces a synchronized RESET signal which restores the processor's internal program counter to zero. Program execution thus begins with memory location zero, following a reset.

Systems which require the processor to wait for an explicit start-up signal will store an enable interrupt instruction (EI) and a halt instruction (HLT) in these locations. A manual or an automatic INTERRUPT will be used

for starting. In other systems, the processor may begin executing its stored program immediately. Note, however, that the reset has no effect on status flags, or on any of the processor's working registers (accumulator, registers, or stack pointer). The contents of these registers remain indeterminate, until initialized explicitly by the program.

In addition to generating a RESET signal, the RESIN/ input causes the 8224's status strobe (STSTB/) output to remain true (low). This allows both the 8080 and 8238 to be reset by a power-up sequence or an externally generated RESET/ condition (input via connector pin P2-38).

#### 3.2 SYSTEM BUS INTERFACE

The System Bus Interface allows the SBC 80/20 to use a common system bus with other master devices such as other CPU's, DMA devices or Peripheral Controllers, thus sharing memory and I/O resources. The System Bus Interface consists of a Bus Controller, a 74LS74 Override flip flop, six 8226 Bidirectional Bus Drivers, as well as an 8224 clock generator and a 74H74 D-type flip flop for generation of the Bus Clock and Constant Clock signals, as shown on sheet 1 of the SBC 80/20 schematic (Appendix A).

## 3.2.1 Bus Controller

The Bus Controller arbitrates all SBC 80/20 requests for use of the sytem bus, synchronously with respect to the Bus Clock (BCLK/). When the SBC 80/20 acquires control of the bus,

the Bus Controller generates the appropriate memory or I/O command signal, gates the address onto the address lines, and gates data on/off the bus, at the appropriate times. An external RC network connected to the Bus Controller's Delay-Adjust (DLYADJ/) input guarantees the required setup and hold time relationships between the address/data lines and the control signals.

The negative-going edge of the Bus Clock (BCLK/) signal provides a timing reference for the Controller's bus arbitration logic. BCLK/ can be externally generated (and received at connector pin P1-13), or can be generated on the SBC 80/20 board (if jumper pair 110-111 is connected). An 18.432 MHz OSC output from the 8224 is applied to the clock input of a 74H74 D-type flip. The  $\overline{Q}$  output from this latch is tied to its own D input. Consequently, the Q output exhibits half the frequency of the OSC input. If jumper pairs 112-113 and 110-111 are connected, this 9.216 MHz output is buffered and made available to external modules on the Constant Clock (CCLK/) line (via connector P1-31) and the Bus Clock (BCLK/) line (via connector P1-13), as well as the Bus Controller.

Bus arbitration activity begins when an external memory or I/O request (MBRQ/ or IORQ/) signal is generated and applied to the Bus request (BCR1) and Transfer Start Request (XSTR) inputs. The request is strobed in by RSTB/ (which is always enabled on the SBC 80/20). Following the next rising and falling edge of BCLK/ the Bus Controller outputs Bus Request, BREQ/ (connector pin P1-18) and forces Bus Priority Out, BPRO/ (connector pin P1-16) inactive (high). BREQ/ is used to request the system bus when

priority is decided by a parallel priority resolution circuit such as an 8214 or a 3003 device. BPRO/ is used to allow lower priority masters to gain control of the bus when a serial priority resolution structure is used. BPRO/ would go to the Bus Priority In (BPRN/) input of the next lower priority master.

When control of the bus is granted to the SBC 80/20, a low level appears on its Bus Priority In (BPRN/) input. The Bus Controller activates its BUSY/ (connector pin P1-17) and Address and Data Enable (ADEN/) outputs. BUSY/ "locks" the SBC 80/20 onto the bus by prohibiting any other master from acquiring control of the bus. ADEN/ enables the 8226 devices which drive the system address (ADRO/-ADRF/) and data busses (DATO/-DAT7/). ADEN/ also enables the bus acknowledge gate at A28-13. When the external acknowledge signal (XACK/ or AACK/) is received it will be gated to the CPU section's RDYIN pin.

When one of the SBC 80/20 external access request lines (MBRQ/ or IORQ/) activates the Transfer Start Request input (XSTR) and ADEN/ is activated, the Bus Controller's timing logic starts the internal sequence which ultimately (depending on the RC network at DLYADJ/) generates the appropriate memory/IO read/write control output (MRDC/, MWTC/, IORC/, or IOWC/) based on the active command request input (MEMR/, MWT/, IOR/ or IOWT/) from the CPU section or Address Decoding logic.

The Bus Controller also provides two other outputs during external access operations. The Any Request output (ANYR) goes high (active) whenever one of the command request inputs (e.g., MWT) is

active. The Read Data output (RDD) is always low (indicating write mode) except for read intervals that begin with the arrival of an active read command request (MEMR/ or IOR/) and end three gate delays after the read control output (MRDC/ or IORC/) goes inactive. RDD controls the direction of the two 8226 bidirectional devices which drive the System Data Bus (DATO/-DAT7/).

The SBC 80/20 can only lose control of the system bus if its BPRN/ input goes high or the bus request inputs (MBRQ/ and IORQ/) go inactive causing the Transfer Complete input (XCP/) to be activated. In either case, the SBC 80/20 will only lose the bus if it is not in the middle of a transfer and its override flip flop is not set (see below).

A low level on the Bus Controller's INIT/ input will initialze the device.

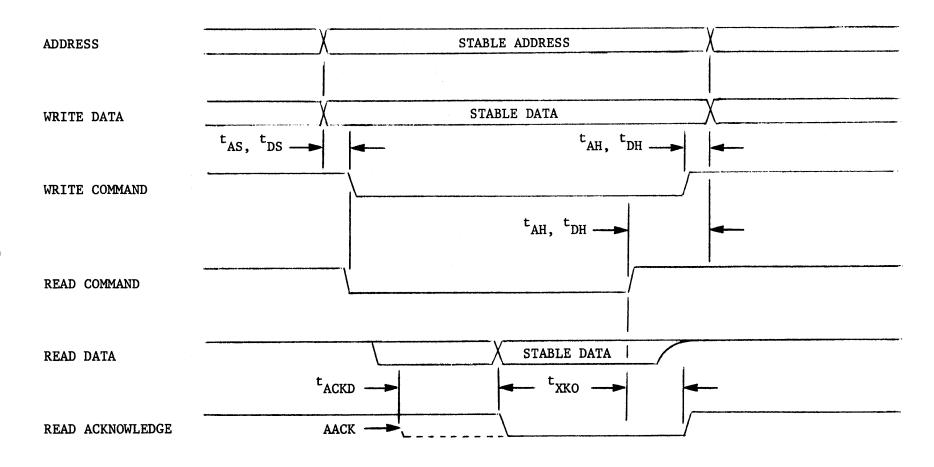

Bus Interface timing is illustrated in Figure 3-5.

#### 3.2.2 SYSTEM BUS OVERRIDE FEATURE

If it is necessary to guarantee that the SBC 80/20 not lose control of the system bus, the override function can be invoked by executing an OUTPUT instruction to address D5 (hexadecimal).

If data bit 0 is a "1" when this output instruction is executed, the Override flip flop (at A27) is set. While this flip flop is set, the SBC 80/20 cannot relinquish control of the system bus.

If data bit 0 is "0" when the output instruction to address D5 is executed or if the Reset signal (RST/) is activated, the Override flip flop is reset. The SBC 80/20 must clear the Override capability

FIGURE 3-5. BUS INTERFACE TIMING (2 of 2 sheets) (Override Mode)

when it is finished with exclusive use of the bus. This function is also useful in those cases where the SBC 80/20 is the only master in the system. In these applications, the SBC 80/20 can save an additional 216 nsec to get a command on the bus.

#### 3.3 FAILSAFE TIMER

If the CPU section tries to access a memory or I/O device but that device, for whatever reason, does not return an acknowledgement (ready) indication, the 8080 remains in a wait state until ready is received. The Failsafe Timer is designed to prevent hanging the system up in this way. A 9602 one-shot (sheet 2 of schematic - Appendix A) is triggered by Status Strobe (STSTB), from the CPU 8224 Clock generator, at the beginning of each machine cycle. If the one-shot is not re-triggered (i.e., if another cycle does not begin) within approximately 10 m.s., the 9602 times out and its output is gated through to the RDYIN pin on the 8224, thus allowing the 8080 to exit the wait state. This feature can be very helpful during system debugging. The SBC 80/20 is shipped with the Failsafe enabled. To disable the Failsafe Timer remove jumper pair 137-138.

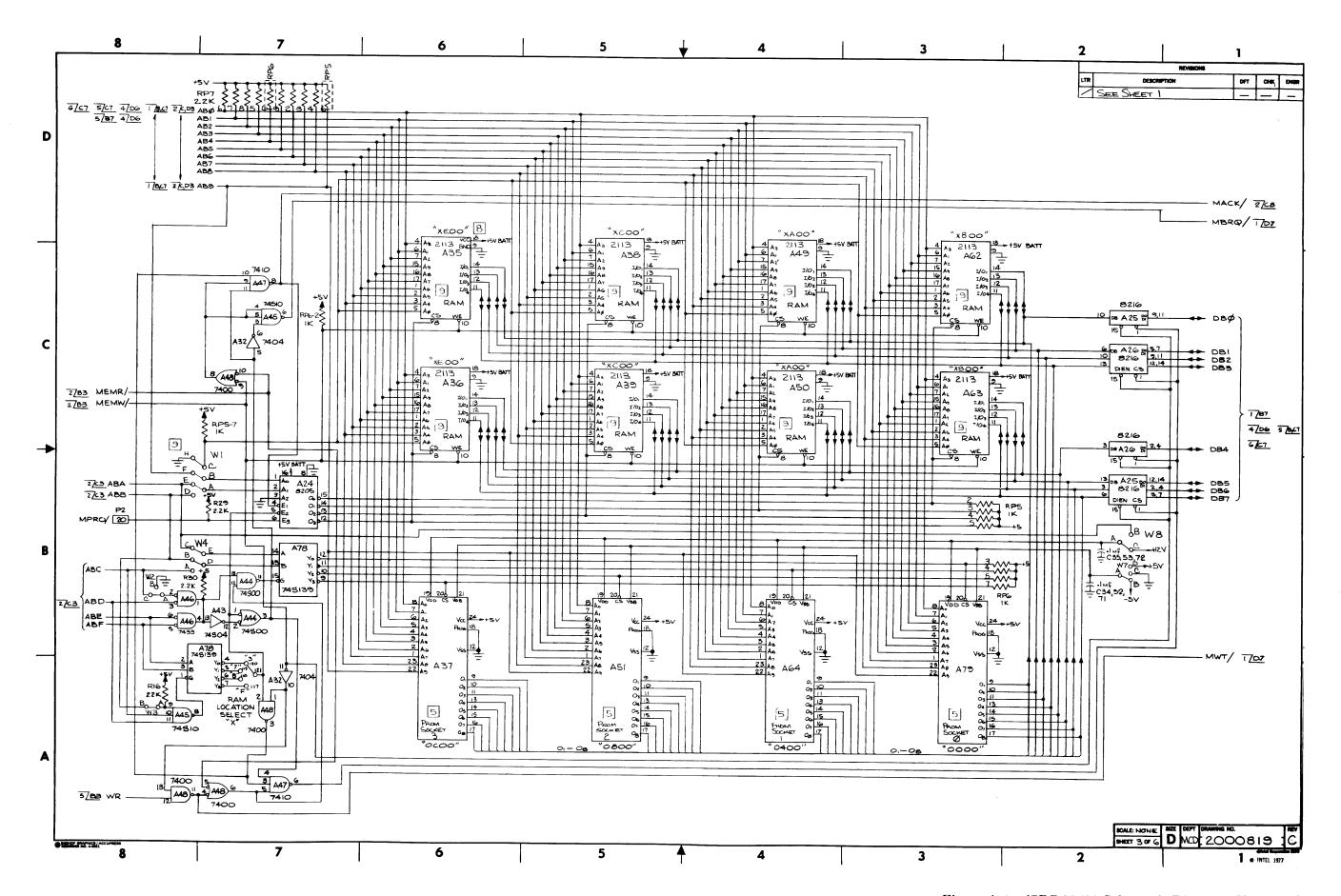

## 3.4 RANDOM ACCESS MEMORY (RAM)

The Random Access Memory (RAM section provides the SBC 80/20 or SBC 80/20-4 user with 2048 (2K) X 8-bits or 4096 (4K) X 8-bits of read/write storage respectively, using eight Intel 2113 (SBC

80-20) or eight Intel 2114 (SBC 80/20-4) static RAM devices. The 2113 or 2114 RAMs require neither refreshing nor clock inputs to operate. The RAM logic includes two 8216 four-bit bidirectional bus drivers, an 8205 one-of-eight decoder and a 74S139 one-of-four decoder (for address block and chip selection), as well as assorted gates and jumper pads as shown on sheet 3 of the schematic (Appendix A).

Each 2113 RAM device, on the SBC 80/20, stores 512 X 4-bits of data. Each 2114 RAM device, on the SBC 80/20-4, stores 1024 X 4-bits of data. Each chip has 10 address inputs (A0-A9) and four common data input/output pins  $(I/0_1-I/0_4)$ , as well as active-low chip select (CS/) and write enable (WE/) inputs. Power inputs (+5V and ground) are also present. In the event of a power failure, power can be provided to the RAMs by a back-up battery input, thus ensuring that no memory data is lost.

The data input/output pins (I/O<sub>1</sub>-I/O<sub>4</sub>) are connected to the SBC 80/20 bus (DBO-DB7) through 8216 bidirectional bus drivers (at A25 and A26). During SBC 80/20 memory write cycles, the Memory Write control signal (MEMW/) causes the 8216 devices to accept data from the SBC 80/20 bus and make it available to the RAM devices. MEMW/ is also applied to the RAM write enable (WE/) inputs, permitting two selected RAM devices each to accept four bits of data and write them into the addressed location. During memory read cycles, the absence of a low level on MEMW/ causes the selected RAM's to output data from the addressed location. Likewise, the

8216 bidirectional bus drivers pass data from the RAM $^{\circ}$ s onto the SBC 80/20 bus (DB $\emptyset$ -DB7).

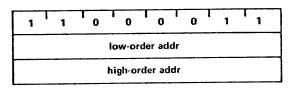

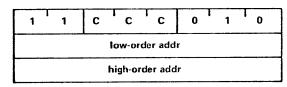

When the on-board RAM is accessed, the nine least significant bits, ABO-AB8, of the 16-bit SBC 80/20 address bus specify the 4-bit segment to be accessed on the selected RAM\*s. Address bits AB9 and ABA specify which pair of RAM devices are to be selected. The next three address bits ABA, ABC, and ABD, must be high to allow the SBC 80/20 on-board RAM to be accessed.

The two most significant address bits, ABE and ABF, select one of the four 16K blocks within the total 64K memory address space that can be accessed by an 8080 microcomputer. Thus, SBC 80/20 RAM can be assigned to any one of the four 16K blocks of address space but it will always reside at the end of the selected 16K block.

The two most significant address lines, ABE and ABF, are applied to the address inputs on the 74S139 one-of-four decoder (at A78 pins 2 and 3). This decoder is enabled by the output from NAND gate at A45-8. Therefore address lines ABB, ABC and ABD must all be high to enable the 74S139 decoder. When enabled, the levels on ABE and ABF cause one of the four decoder outputs to go low. Each decoder output is tied to one half of a jumper pair, labeled "3", "7", "B" or "F" to represent the high order hexadecimal digit of the selected RAM address space. Table 3-1 correlates the four jumper connections with the selected RAM address space.

TABLE 3-1. RAM ADDRESS SELECTION JUMPERS

| JUMPER     | SELECTED RAM ADDRESS SPACE (hex) |                  |  |

|------------|----------------------------------|------------------|--|

| CONNECTION | 2K (SBC 80/20)                   | 4K (SBC) 80/20-4 |  |

| 120-121    | 3800-3FFF                        | 3000-3FFF        |  |

| 119-121    | 7800-7FFF                        | 7000-7FFF        |  |

| 118-121    | B800-BFFF                        | BOOO-BFFF        |  |

| 117-121    | F800-FFFF                        | F000-FFFF        |  |

|            |                                  |                  |  |

When the jumper-selected decoder output is activated it allows the Memory Acknowledge signal (MACK/) to be generated (discussed below) and permits the 8216 bus drivers to be enabled. The active decoder output also enables the 8205 decoder at A24.

If the Memory Protect line, MPRO/ (connector pin P2-20), is inactive (high) and a memory read or write (MEMR/ or MEMW/) is indicated, the 8205 decoder will determine the two RAM chips to be selected. The low order four decoder outputs are each connected to the chip select (CS/) inputs on a pair of RAM devices. Thus, the active decoder output selects the two RAM chips to be accessed (A35 & A36, A38 & A39, A49 & A50 or A62 & A63). The least significant address bits (ABO-AB9) then specify the 4-bit segment to be accessed on each of the two selected RAM's.

The memory logic also includes several gates that are used to generate the following memory control signals: Memory Acknow-ledge (MACK/), Memory Bus Request (MBRQ) and Memory Write (MWT/).

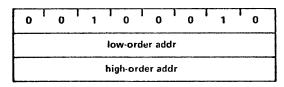

During RAM access cycles, the Memory acknowledge signal (MACK/) is generated by the 7410 NAND gate at A47-8 when Memory read (MEMR/) or write (MEMW/) is true and the on-board RAM address space is selected (as described above). MACK/ is applied to the RDYIN input on the CPU Section and allows the 8080 to proceed with the access cycle without any wait states. When memory which is external to the SBC 80/20 is accessed, the external memory module must return a Transfer Acknowledge, XACK/ (connector pin P1-23). XACK/ and MACK/ indicate that data is available on the data bus during memory read cycles, or that data has been accepted from the data bus during memory write cycles. When a memory read command is issued for an external memory module, that module can return an advanced acknowledge AACK/ (connector pin P1-25), that will allow the data to be read without requiring any wait state. To summarize memory access acknowledgements: All SBC 80/20 on-board memory accesses (read and write) return MACK/ to the CPU Section and proceed without any wait states. All external memory accesses return XACK/ to the SBC 80/20 (even if AACK/ is also returned). During external memory read cycles, AACK/ can be returned before the data is actually read, allowing the read cycle to proceed with a minimum of one

wait state. Otherwise, external accesses could require more than one wait state, as shown in Figure 3-6.

If MEMR/ or MEMW/ is true but the SBC 80/20 on-board memory is not selected, the System Memory Bus Request signal (MBRQ/) is generated (at A45-6). MBRQ/ is applied to the System Bus Interface and indicates that external memory is to be accessed.

The System Memory Write signal (MWT/) is also applied to the System Bus Interface. MWT/ is the result of NANDing the memory Write signal (MEMW/) from the 8238 System Controller with the Write pulse (WR/) from the 8080. Recall that MEMW/ is generated at the beginning of all memory write cycles (state T2). MEMW/ occurs earlier than WR/ and allows the memory acknowledge (MACK/) for on-board accesses to be returned early enough to avoid an unnecessary wait state. Thus, MEMW/ is synchronized with WR/ to produce MWT/. The MWT/ signal causes the data to be written into an external memory location, during state T3 of the memory cycle. Thus, all external writes will require at least one wait state.

Memory access timing is illustrated in Figure 3-6.

#### 3.5 READ ONLY MEMORY (ROM/PROM)

The SBC 80/20 and SBC 80/20-4 have provision for installing 4096 (4K) X 8-bit words of read only memory in sockets on the PC board.

Four Intel 8708 1K X 8-bit Erasable and Electronically Programmable Read Only Memory (EPROM) chips or four 8308 1K X 8-bit static MOS mask Read Only Memory (ROM) chips can be installed in the four 24-pin sockets. The SBC 80/20 and SBC 80/20-4 also have provisions

FIGURE 3-6. MEMORY ACCESS TIMING

for installing 8192 (8K) X 8-bit words of memory by using Intel 2716 2K X 8-bit Erasable and Electronically Programmable Read Only Memory or 8316B Masked ROM chips instead of 8708 or 8308 chips.

In addition to the four 24-pin sockets, the ROM/EPROM logic includes a 74S139 one-of-four decoder for chip selection and assorted gates as shown on sheet 3 of the schematic (Appendix A).

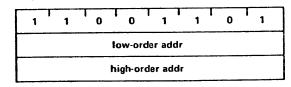

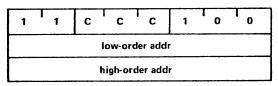

The ten least significant address lines, ABO-AB9 are applied to the address pins (AO-9) at each of the four sockets. Address lines ABA and ABB are applied to the two inputs of the 74S139 decoder at A78, pins 13 and 14. Unless the decoder is disabled by the line which specifies RAM selection (as described in the previous section) or the memory read signal (MEMR/) is inactive, the levels on ABA and ABB will cause one of the four decoder outputs to go low and enable one of the four ROM/EPROM chips in sockets A37, A51, A64 or A79.

The four most significant address lines, ABC-ABF, are gated together (all four must be low) and ORed with the RAM selection line to form the signal which indicates that an SBC 80/20 on-board memory access is to occur. Thus, the SBC 80/20 ROM/EPROM will always begin at memory address zero.

During on-board ROM/EPROM read cycles, the selection line is NANDed with Memory Read (MEMR/) to generate the Memory Acknowledge signal, MACK/ (at A47-8), as well as the signal (at A47-6) which enables the 8216 bidirectional bus drivers. The bus drivers gate

data read from a ROM/EPROM chip onto the SBC 80/20 data bus (DBO-DB7). Notice on the schematic that the output from the NAND gate at A48-3 prevents MACK/ and the bus driver enable signal from being generated during memory write cycles addressed to the ROM/EPROM address space.

If neither SBC 80-20 on-board RAM nor ROM/EPROM is selected, the System Memory Bus Request signal (MBRQ/) is generated as described in the previous section.

ROM/EPROM read timing is as shown in Figure 3-6(A). All SBC 80/20 on-board ROM/EPROM reads proceed without any wait states.

#### 3.6 I/O ADDRESS DECODING

The SBC 80/20 includes the following programmable devices which are accessed by I/O commands directed to particular addresses:

- . Two 8255 Programmable Peripheral Interfaces

- . 8251 USART Serial I/O Interface

- . 8259 Interrupt Controller

- . 8253 Interval Timer

- . Power Fail Status/Interrupt latch

- System Bus override flip flop

- . LED Diagnostic Indicator

The I/O Address Decoding logic accepts address lines AB2 through AB7 and generates the appropriate chip select/enable signal

for the addressed device. This logic consists of two 8205 one-of-eight decoders and assorted gates as shown on sheet 5 of the schematic (Appendix A).

Address lines AB2-AB4 are applied to the address inputs of the first decoder (at A13). Address lines AB4-AB7 are gated through to the decoder enable inputs such that only I/O addresses between DO and EF (hexadecimal) will enable the decoder. Decoder output O is not used. Decoder output 1 is true (low) when the address lies between E4 and E7. This line is labeled PE47/, and is made available to the 8255 parallel I/O interface chip select input at A20-6, Decoder output 2 is true when the address lies between E8 and EB. This line is labeled PE8B/, and is made available to the other 8255 device chip select input at A21-6. Decoder output 3 is true when the address lies between EC and EF. This line is applied to the chip select input on the 8251 USART. Decoder output 4 is not used. Decoder output 5 is true when the address lies between D4 and D7. This line enables the second 8205 decoder (at A15) as described below. Decoder output 6 is true when the address lies between D8 and DB. This line enables the 8253 Interval Timer. Decoder output 7 is true when the address lies between DC and DF. This line, labeled INTP/, enables the 8259 Interrupt Controller.

The second 8205 decoder (at A15) further decodes I/O addresses between D4 and D7 (after one wait state, unless jumper pair 115-116 is disconnected) if one of the I/O control signals (IOR/orIOW/) is true. Address lines ABO and AB1 are applied to decoder inputs AO and A1. IOW/ and WR/ are NANDed together at A30-3 and the result

is applied to decoder input A3. Consequently output O from this decoder (OD4/) is true near the end of an I/O write to port D4 instruction. OD4/ resets the Power Fail status latch at A27-1. Decoder output 1 (OD5/) is true for an output to port D5. OD5/ clocks the System Bus override flip flop. Decoder output 2 is true for an output to port D6 which triggers a lms one-shot that flashes the light emitting diode (LED) at DS1. Decoder output 4 is true when I/O read to port 4 is executed. This line enables the Power Fail Status signal (PFS/) from connector pin P2-17 to data bus line 0 (DBO). None of the other outputs on the second decoder are used.

Table 3-2 summarizes I/O addressing for the SBC 80/20.

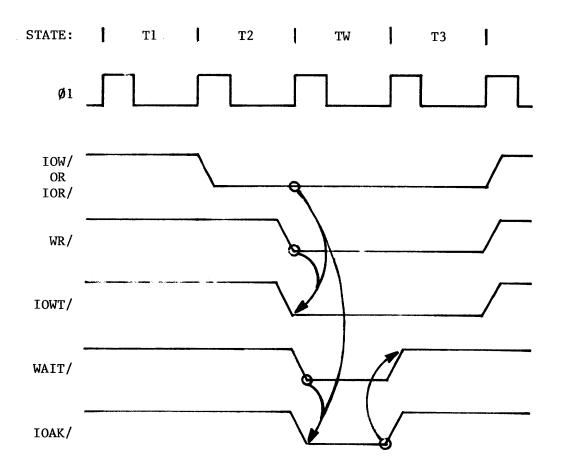

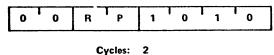

Whenever I/O Read (IOR/) or I/O Write (IOW/) is true and the address on the bus represents a value between D4-DF or E4-EF, the I/O Acknowledge signal (IOAK/) is generated when the 8080's WAIT/ output goes low, thus requiring one wait state during all SBC 80/20 on-board I/O cycles, as shown in Figure 3-7.

If IOR/ or IOW/ is true but the I/O address refers to an external port, the I/O Request signal (IORQ/) is generated and applied to System Bus Interface which will attempt to acquire control of the System Bus in order to execute the I/O instruction. The external I/O device must return a Transfer Acknowledge signal (XACK/) to complete the I/O cycle.

## 3.7 SERIAL I/O INTERFACE

The Serial I/O Interface logic provides the SBC 80/20 with a serial data communications channel that can be programmed to operate

TABLE 3-2. I/O PORT ADDRESSING

| I/O PORT<br>ADDRESS<br>(hexadecimal) | I/O<br>DEVICE                   | INPUT<br>FUNCTION                                      | OUT PUT<br>FUNCT I ON                                             |

|--------------------------------------|---------------------------------|--------------------------------------------------------|-------------------------------------------------------------------|

| D4                                   | Power Fail                      | Read Power Fail Status                                 | Reset Power Fail<br>latch                                         |

| D5                                   | System Bus<br>Override          | *Not used                                              | Set or reset over-<br>ride control<br>(using data bus<br>line O), |

| D6                                   | LED Diagnostic<br>Indicator     | *Not used                                              | Flash LED.                                                        |

| D7                                   | *Not used                       |                                                        |                                                                   |

| **D8 or DA<br>**D9 or DB             | 8259<br>Interrupt<br>Controller | Various read func-<br>tions. (See Section<br>3.10)     | Various write<br>functions. (See<br>Section 3.10)                 |

| DC<br>DD<br>DE<br>DF                 | 8253<br>Interval<br>Timer       | Read counter 0 Read counter 1 Read counter 2 *Not used | Load Counter 0 Load counter 1 Load counter 2 Mode control         |

| E4<br>E5<br>E6<br>E7                 | 8255<br>PPI<br>#1               | Read port A<br>Read port B<br>Read port C<br>          | Write port A<br>Write port B<br>Write port C<br>Control           |

| E8<br>E9<br>EA<br>EB                 | 8255<br>PPI<br>#2               | Read port A<br>Read port B<br>Read port C<br>          | Write port A<br>Write port B<br>Write port C<br>Control           |

| **EC or EE<br>**ED or EF             | 8251<br>USART                   | Data in<br>Read Status                                 | Data out<br>Control                                               |

<sup>\*\*</sup>Either port address may be used.

<sup>\*</sup>Though these port addresses are not used by the SBC 80/20, they are not available for use by external I/O devices.

FIGURE 3-7. SBC 80/20 ON-BOARD I/O TIMING

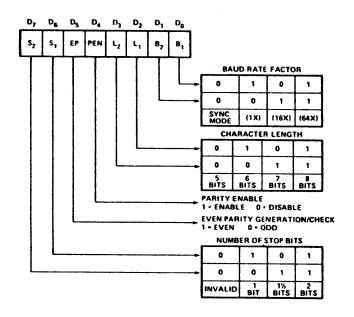

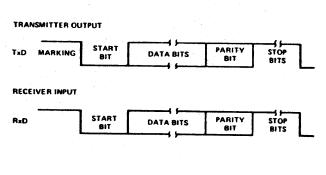

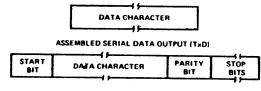

with most of the current serial data transmission protocols, synchronous or asynchronous. Baud rate, character length, number of stop bits and even/odd parity are program selectable.

The Serial I/O Interface logic consists primarily of an Intel 8251 USART device and several driver/receiver circuits as shown on sheet 5 of the SBC 80/20 schematic (Appendix A). Before describing the specific operation of the Serial I/O logic however, we will summarize the general operational characteristics of the 8251 USART, because it essentially defines the character of the serial I/O Interface.

#### 3.7.1 INTEL®8251 OPERATIONAL SUMMARY

The 8251 is a Universal Synchronous/Asynchronous Receiver/

Transmitter designed specifically for the 8080 Micro-computer System. Like other I/O devices in the 8080 Micro-computer System its functional configuration is programmed by the systems software for maximum flexibility. The 8251 can support virtually any serial data technique currently in use (including IBM "Bi-Sync").

#### Modem Control

The 8251 has a set of control inputs and outputs that can be used to simplify the interface to almost any Modem. The Modem control signals are general purpose in nature and can be used for functions other than Modem control, if necessary.

# DSR (Data Set Ready)

The  $\overline{\rm DSR}$  input signal is general purpose in nature. Its condition can be tested by the CPU using a Status Read Operation. The  $\overline{\rm DSR}$  input is normally used to test Modem conditions such as Data Set Ready.

# DTR (Data Terminal Ready)

The  $\overline{\text{DTR}}$  output signal is general purpose in nature. It can be set "low" by programming the appropriate bit in the Command Instruction word. The  $\overline{\text{DTR}}$  output signal is normally used for Modem control such as Data Terminal Ready or Rate Select.

## RTS (Request to Send)

The  $\overline{\text{RTS}}$  output signal is general purpose in nature. It can be set "low" by programming the appropriate bit in the Command Instruction word. The  $\overline{\text{RTS}}$  output signal is normally used for Modem control such as Request to Send.

## CTS (Clear to Send)

A "low" on this input enables the 8251 to transmit data (serial) if the TxEN bit in the Command byte is set to a "one". This is very important to remember:

## TXRDY (Transmitter Ready)

This output signals the CPU that the transmitter is ready to accept a data character. It can be used as an interrupt to the system or for polled operation when the CPU can check TXRDY using a status read operation. TXRDY is active only when CTS is enabled.

# USART PIN CONFIGURATION

| Pin Name | Pin Function                                  |

|----------|-----------------------------------------------|

| D7 D0    | Data Bus (8 bits)                             |

| C/D      | Control or Data is to be Written or Read      |

| RO       | Read Data Command                             |

| WR       | Write Data or Control Command                 |

| cs       | Chip Enable                                   |

| CLK      | Clock Pulse (TTL)                             |

| RESET    | Reset                                         |

| TxC      | Transmitter Clock                             |

| TxD      | Transmitter Data                              |

| RxC      | Receiver Clock                                |

| RxD      | Receiver Data                                 |

| RxRDY    | Receiver Ready (has character for 8080)       |

| TxRDY    | Transmitter Ready (ready for char. from 8080) |

| Pin Name | Pin Function         |

|----------|----------------------|

| DSR      | Data Set Ready       |

| DTR      | Data Terminal Ready  |

| SYNDET   | Sync Detect          |

| RTS      | Request to Send Data |

| CTS      | Clear to Send Data   |

| TxE      | Transmitter Empty    |

| Vcc      | +5 Volt Supply       |

| GND      | Ground               |

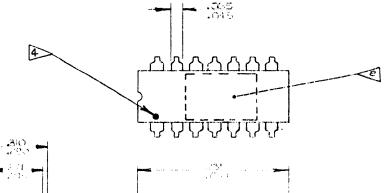

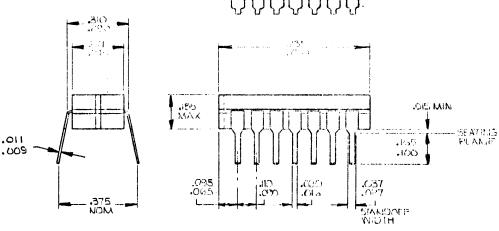

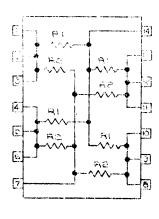

FIGURE 3-8. 8251 PIN ASSIGNMENTS

TXRDY is automatically reset when a character is loaded from the CPU.

#### TXE (Transmitter Empty)

When the 8251 has no characters to transmit, the TXE output will go "high". It resets automatically upon receiving a charater from the CPU. TXE can be used to indicate the end of a transmission mode, so that the CPU "knows" when to "turn the line around" in the half-duplexed operational mode.

In SYNChronous mode, a "high" on this output indicates that a character has not been loaded and the SYNC character or characters are about to be transmitted automatically as "fillers".

#### TXC (Transmitter Clock)

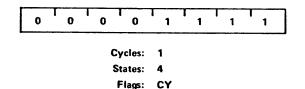

The Transmitter Clock controls the rate at which the character is to be transmitted. In the Synchronous transmission mode, the frequency of TXC is equal to the actual Baud Rate (1X). In Asyn-

chronous transmission mode, the frequency of TXC is a multiple of the actual Baud Rate. A portion of the mode instruction selects the value of the multiplier; it can be 1X, 16X or 64X the Baud Rate.

#### For Example:

If Baud Rate equals 110 Baud,

TXC equals 110 Hz (1X)

TXC equals 1.76 kHz (16X)

TXC equals 7.04 kHz (64X).

If Baud Rate equals 9600 Baud,

TXC equals 153.6 kHz (16X).

The falling edge of  $\overline{\text{TXC}}$  shifts the serial data out of the 8251.

#### RXRDY (Receiver Ready)

This output indicates that the 8251 contains a character that is ready to be input to the CPU. RXRDY can be connected to the interrupt structure of the CPU or for polled operation the CPU can check the condition of RXRDY using a status read operation. RXRDY is automatically reset when the character is read by the CPU.

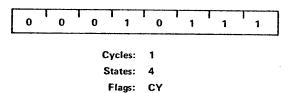

## RXC (Receiver Clock)

The Receiver Clock controls the rate at which the character is to be received. In Synchronous Mode, the frequency of  $\overline{\text{RXC}}$  is equal to the actual Baud Rate (1X). In Asynchronous Mode, the frequency of  $\overline{\text{RXC}}$  is a multiple of the actual Baud Rate. A portion of the mode instruction selects the value of the multiplier; it can be 1X, 16X or 64X the Baud Rate.

## For Example:

If Baud Rate equals 300 Baud,

RXC equals 300 Hx (1X)

RXC equals 4800 Hz (16X)

RXC equals 19.2 kHz (64X).

If Baud Rate equals 2400 Baud,

RXC equals 2400 Hz (1X)

RXC equals 38.4 kHz (16X)

RXC equals 153.6 kHz (64X).

Data is sampled into the 8251 on the rising edge of  $\overline{\text{RXC}}$ .

Note: In most communications systems, the 8251 will be handling both the transmission and reception operations of a single link. Consequently, the Receive and Transmit Baud Rates will be the same. Both TXC and RXC will require identical frequencies for this operation and can be tied together and connected to a single frequency source (Baud Rate Generator) to simplify the interface.

#### SYNDET (SYNC Detect)

This pin is used in SYNChronous Mode only. It is used as either input or output, programmable through the Control Word. It is reset to "low" upon RESET. When used as an output (internal Sync mode), the SYNDET pin will go "high" to indicate that the 8251 has located the SYNC character in the Receive mode. If the 8251 is programmed to use double Sync characters, then SYNDET will go "high" in the middle of the last bit of the second Sync character. SYNDET is automatically reset upon a Status Read operation.

When used as an input, (external SYNC detect mode), a positive going signal will cause the 8251 to start assembling data

characters on the falling edge of the next  $\overline{\text{RXC}}$ . Once in SYNC, the "high" input signal can be removed. The duration of the high signal should be at least equal to the period of  $\overline{\text{RXC}}$ .

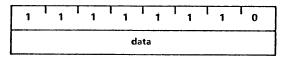

### Programming the 8251

Prior to starting data transmission or reception, the 8251 must be loaded with a set of control words generated by the CPU. These control signals define the complete functional definition of the 8251 and must immediately follow a System Reset operation (internal or external).

The control words are split into two formats:

- 1. Mode Instruction,

- 2. Command Instruction.

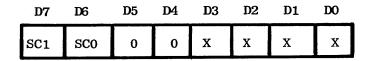

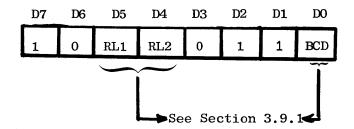

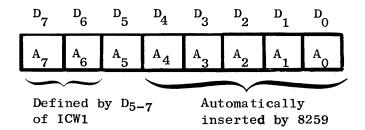

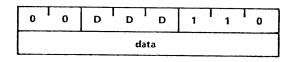

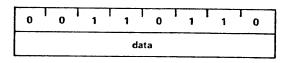

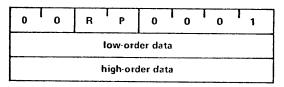

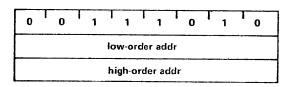

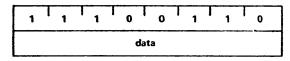

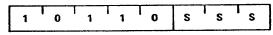

Both the Mode and Command instructions must conform to a specified sequence for proper device operation. The Mode Instruction must be inserted immediately following a Reset operation, prior to using the 8251 for data communication.