# SBC 202 DOUBLE DENSITY DISKETTE CONTROLLER HARDWARE REFERENCE MANUAL

Order Number: 9800420A

# SBC 202 DOUBLE DENSITY DISKETTE CONTROLLER HARDWARE REFERENCE MANUAL

Order Number: 9800420A

Copyright © 1977 Intel Corporation

Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051

#### **PREFACE**

This manual provides general information, preparation for use, principles of operation, and service information for the Intel SBC 202 Double Density Diskette Controller. The information presented herein is adequate to support normal installation and programming needs. Additional system information is available in the following documents.

- Intel SBC 80 Single Board Computer Hardware Reference Manual.

- Intel System 80 Microcomputer Hardware Reference Manual.

- Intel Series 3000 Microprogramming Manual, Part No. 98-210A.

- Intel Series 3000 Reference Manual, Part No. 98-221A.

The information in this manual is subject to change without notice. Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this manual. Intel Corporation makes no commitment to update nor to keep current the information contained in this manual.

No part of this manual may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation. The following are trademarks of Intel Corporation and may be used only to describe Intel products:

| ICE-30          | MCS         |

|-----------------|-------------|

| ICE-80          | MEGACHASSIS |

| INSITE          | MICROMAP    |

| INTEL           | MULTIBUS    |

| INTELLEC        | PROMPT      |

| LIBRARY MANAGER | UPI         |

## **CONTENTS**

| CHAPTER 1                        |      | CHAPTER 4                         |      |

|----------------------------------|------|-----------------------------------|------|

| GENERAL INFORMATION              | Page | PRINCIPLES OF OPERATION           |      |

| Introduction                     | 1-1  | Introduction                      |      |

| Description                      | 1-2  | Functional Description            | 4-1  |

| Channel Board                    | 1-2  | Channel Board                     | 4-1  |

| Interface Board                  | 1-2  | Channel Command Block             | 4-3  |

| Specifications                   | 1-2  | Microprogram Control Unit         | 4-4  |

| Terminology                      |      | Microprogram Memory Block         | 4-6  |

|                                  |      | Central Processing Element        | 4-6  |

|                                  |      | Data Clock Shift Register         |      |

| CHAPTER 2                        |      | Data Flow Control                 |      |

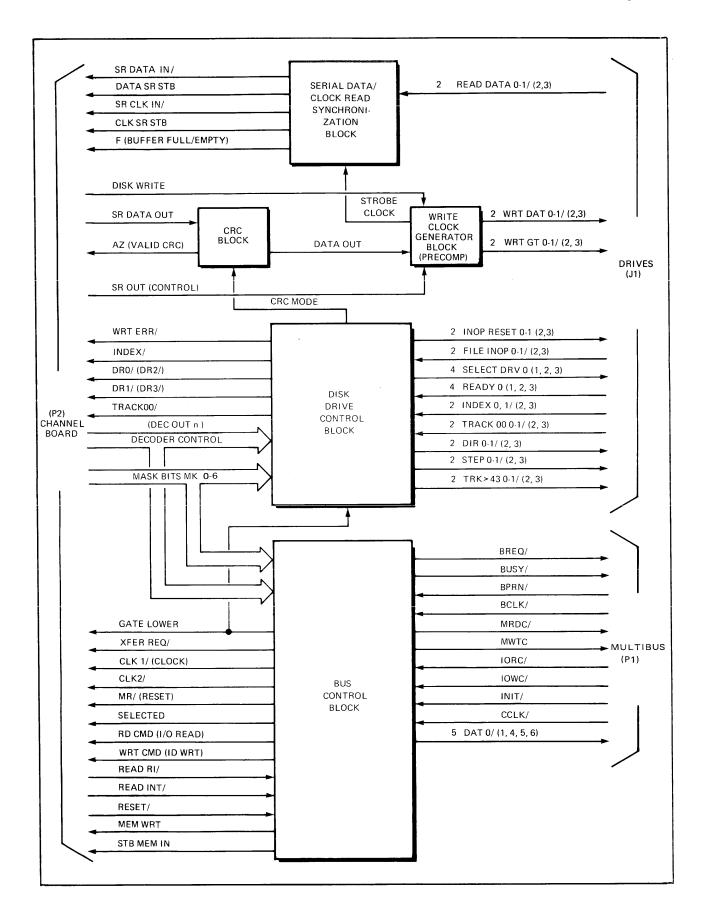

| PREPARATION FOR USE              |      | Interface Board                   | 4-14 |

| Introduction                     | 2-1  | Disk Drive Control                | 4-14 |

| Unpacking and Inspection         | 2-1  | Write Data Generator              |      |

| Installation Considerations      |      | Serial Data/Clock Synchronization | 4-21 |

| Power Requirements               | 2-1  | Cyclic Redundancy Check           |      |

| Cooling Requirements             |      | Bus Control                       | 4-22 |

| Physical Dimensions              |      | Recording Format                  | 4-25 |

| Interface Requirements           | 2-1  | Physical Data Format              | 4-25 |

| Operating Characteristics        |      | Track Format                      | 4-26 |

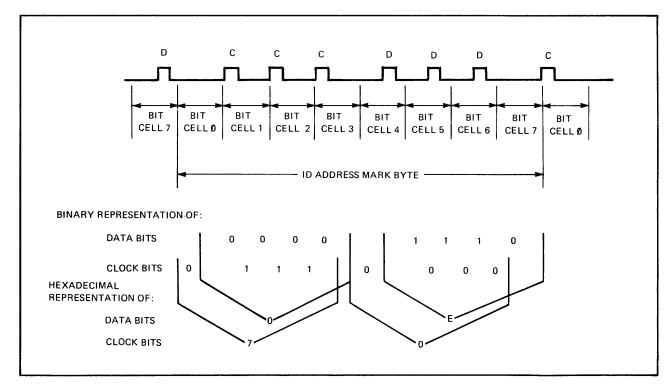

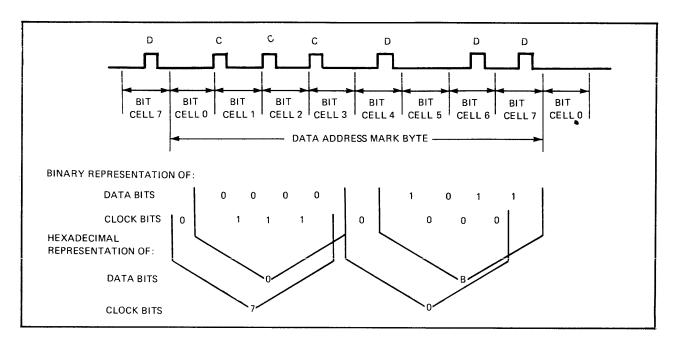

| Switch and Jumper Configurations |      | Address Marks                     | 4-26 |

| I/O Base Address Selection       | 2-20 | CRC Bytes                         | 4-29 |

| Interrupt Level Selection        | 2-20 |                                   |      |

| CHAPTER 3                        |      |                                   |      |

| PROGRAMMING INFORMATION          | 2.1  | CHAPTED 5                         |      |

| Introduction                     |      | CHAPTER 5                         |      |

| Channel Commands                 |      | SERVICE INFORMATION               | . ج  |

| Diskette Operations              |      | Introduction                      |      |

| I/O Parameter Block              |      | Service Diagrams                  |      |

| Error Indications                | 3-9  | Reshipment                        | 5-1  |

## **TABLES**

| Table Title                                     | Page   | Table Title                            | Page   |

|-------------------------------------------------|--------|----------------------------------------|--------|

| Specifications                                  | . 1-3  | I/O Parameter Block (IOPB) Format      | . 3-8  |

| Channel Board P1 Connector Pin Assignments      |        | Interrupt Control Bits                 | . 3-8  |

| Channel Board P2 Connector Pin Assignments      |        | ACO Input Selection                    |        |

| Interface Board P1 Connector Pin Assignments    |        | Microinstruction Bit Assignment        |        |

| Interface Board P2 Connector Pin Assignments    |        | Control Pulses and Levels Generated by |        |

| Interface Board J1 Connector Pin Assignments    |        | Microprogram                           | . 4-8  |

| Diskette Controller/Multibus AC Characteristics |        | Control Function Definitions           |        |

| Diskette Controller/Drive Interface AC          |        | I-Bus Selection by Mask Field Bits     | . 4-10 |

| Characteristics                                 | . 2-13 | K-Bus Input Selection                  |        |

| Diskette Controller/Multibus DC Characteristics | . 2-14 |                                        |        |

| Diskette Controller/Drive Interface DC          |        |                                        |        |

| Characteristics                                 | . 2-16 |                                        |        |

### **ILLUSTRATIONS**

| Figure Title                             | Page | Figure Title                      | Page |

|------------------------------------------|------|-----------------------------------|------|

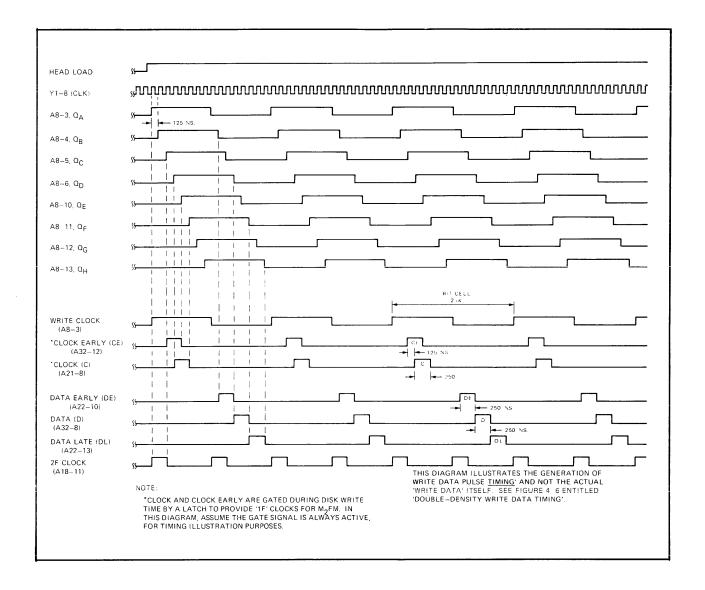

| Typical System Block Diagram             | 1-1  | Precompensation Timing            | 4-19 |

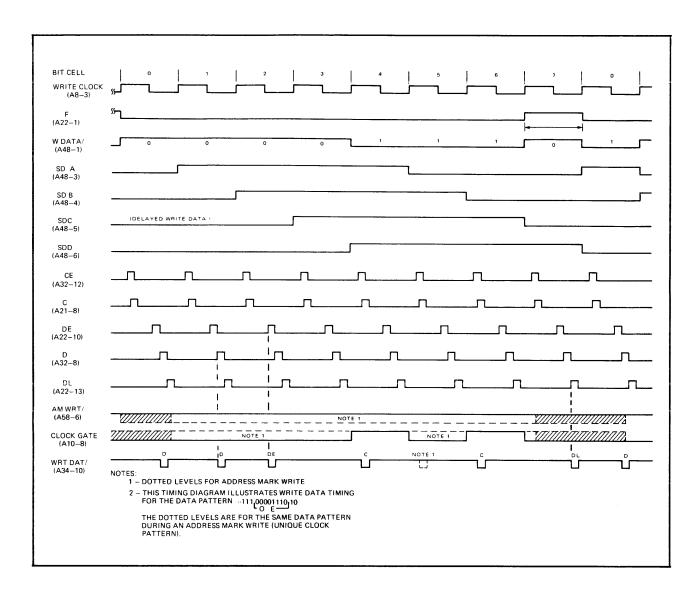

| Channel and Interface Board Connectors   | 2-2  | Write Data Timing                 | 4-20 |

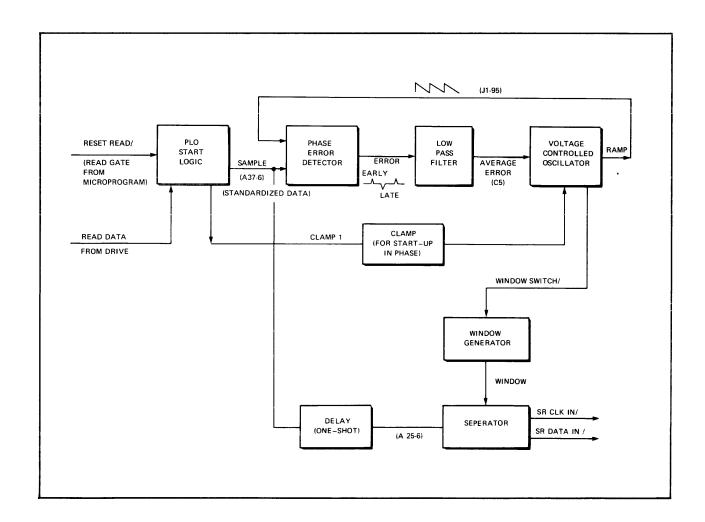

| Slave Command Timing                     |      | Pulse Locked Oscillator           |      |

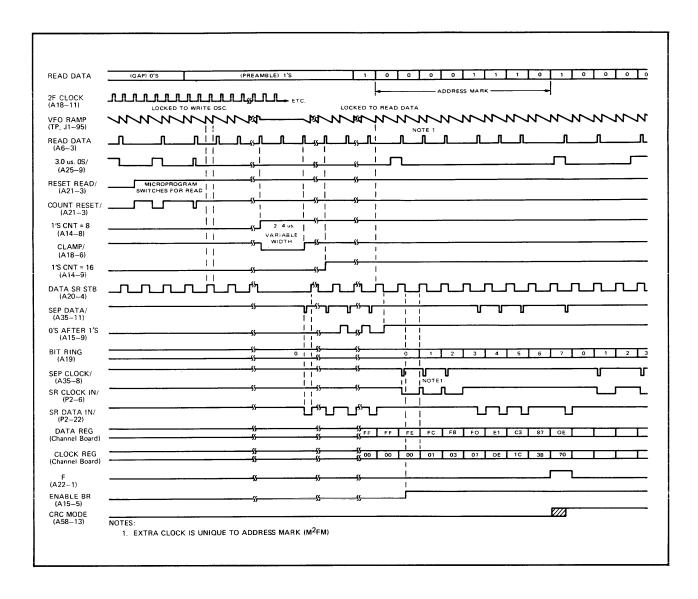

| Bus Exchange Timing                      |      | Read Synchronization Timing       | 4-23 |

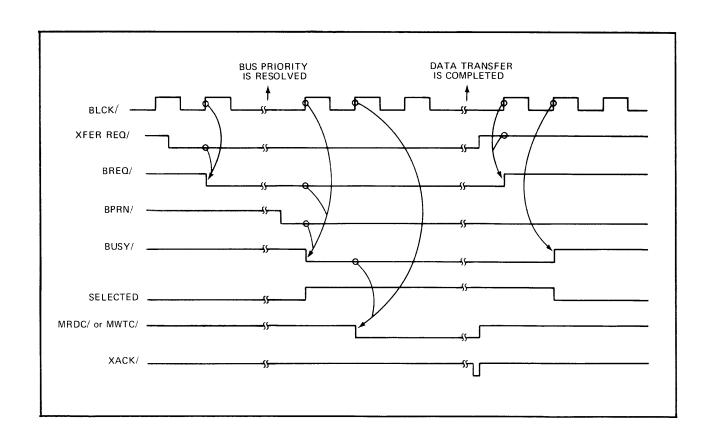

| Master Command Timing                    |      | Bus Control Timing                | 4-24 |

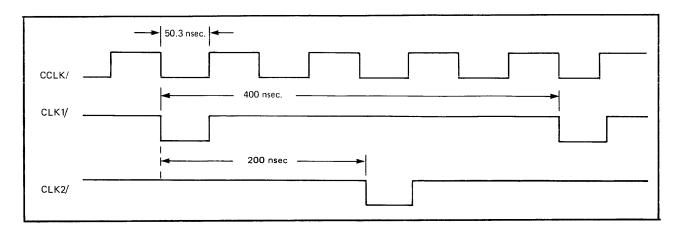

| Step/Settling Timings                    | 2-18 | CLK 1/ and CLK 2/ Timing          | 4-25 |

| Read Timing                              |      | Physical Data Format              | 4-25 |

| Write Timing                             | 2-19 | Byte Representation               | 4-26 |

| Index Timing                             |      | Data Bytes                        | 4-27 |

| Write Fault Reset Timing                 |      | Data Bits                         | 4-27 |

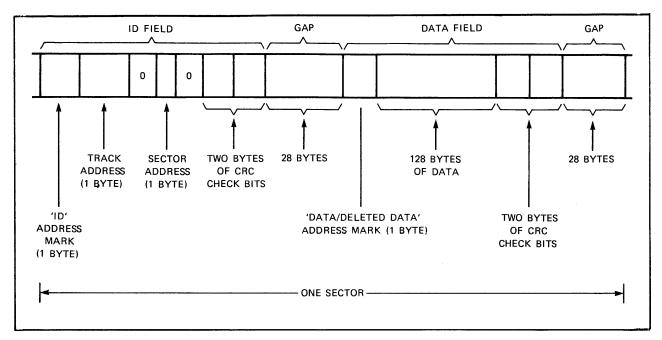

| Sector Format                            |      | Bit Cell                          | 4-27 |

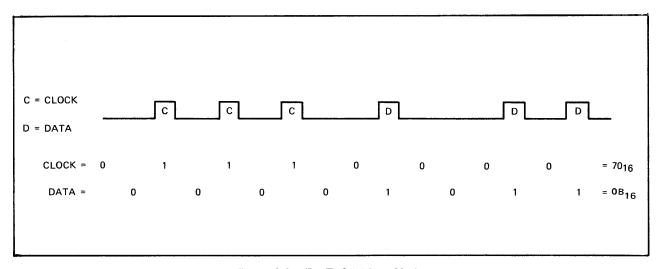

| "Data" Address Mark                      |      | Track Format                      | 4-28 |

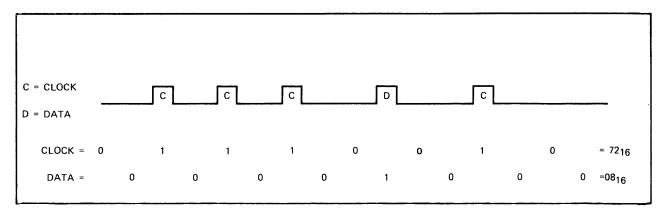

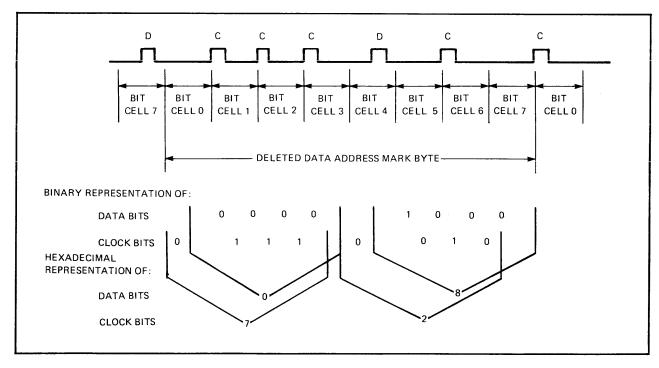

| "Delete Data" Address Mark               |      | Index Address Mark                | 4-30 |

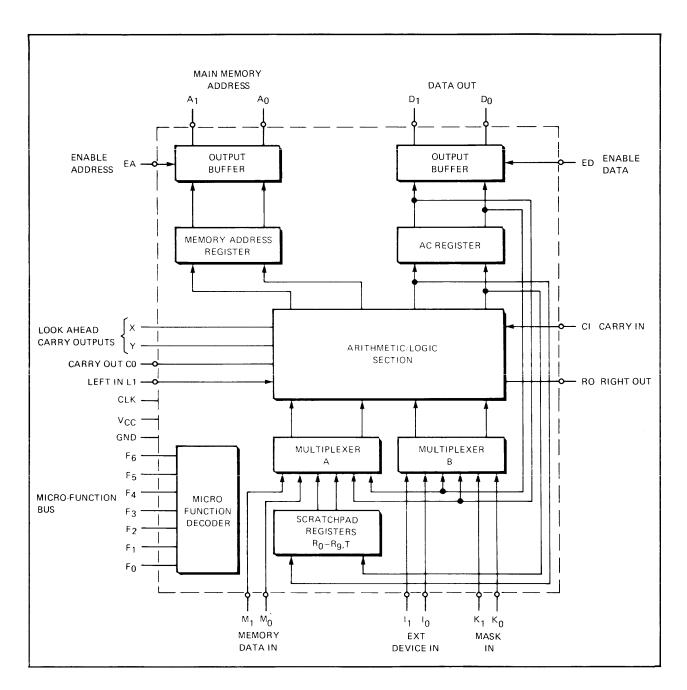

| Channel Board Functional Block Diagram   |      | ID Address Mark                   | 4-30 |

| Microprogram Control Unit Functional     |      | Data Address Mark                 | 4-31 |

| Block Diagram                            | 4-4  | Delete Data Address Mark          | 4-31 |

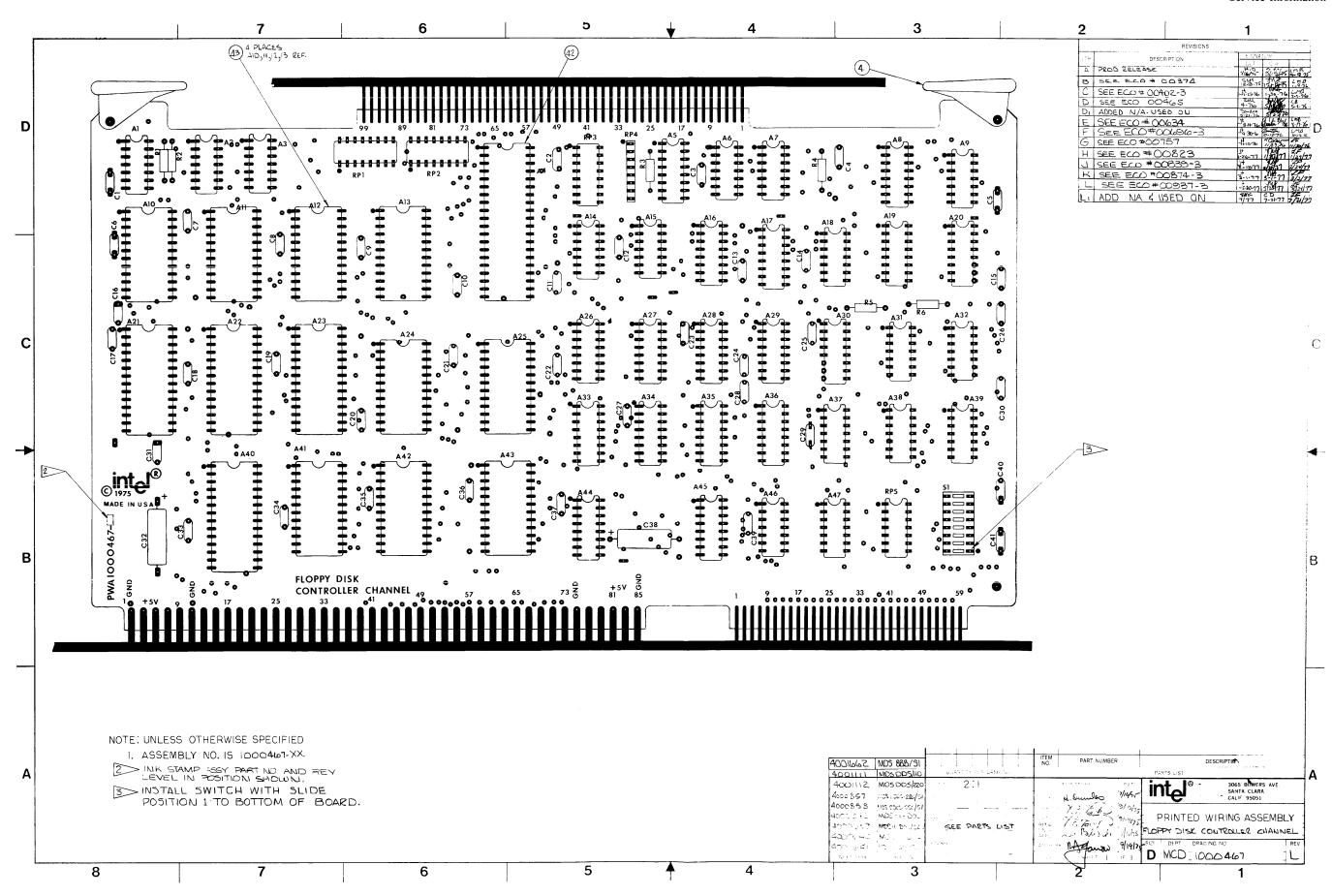

| Central Processing Element Functional    |      | Parts Location: Channel Board     | 5-3  |

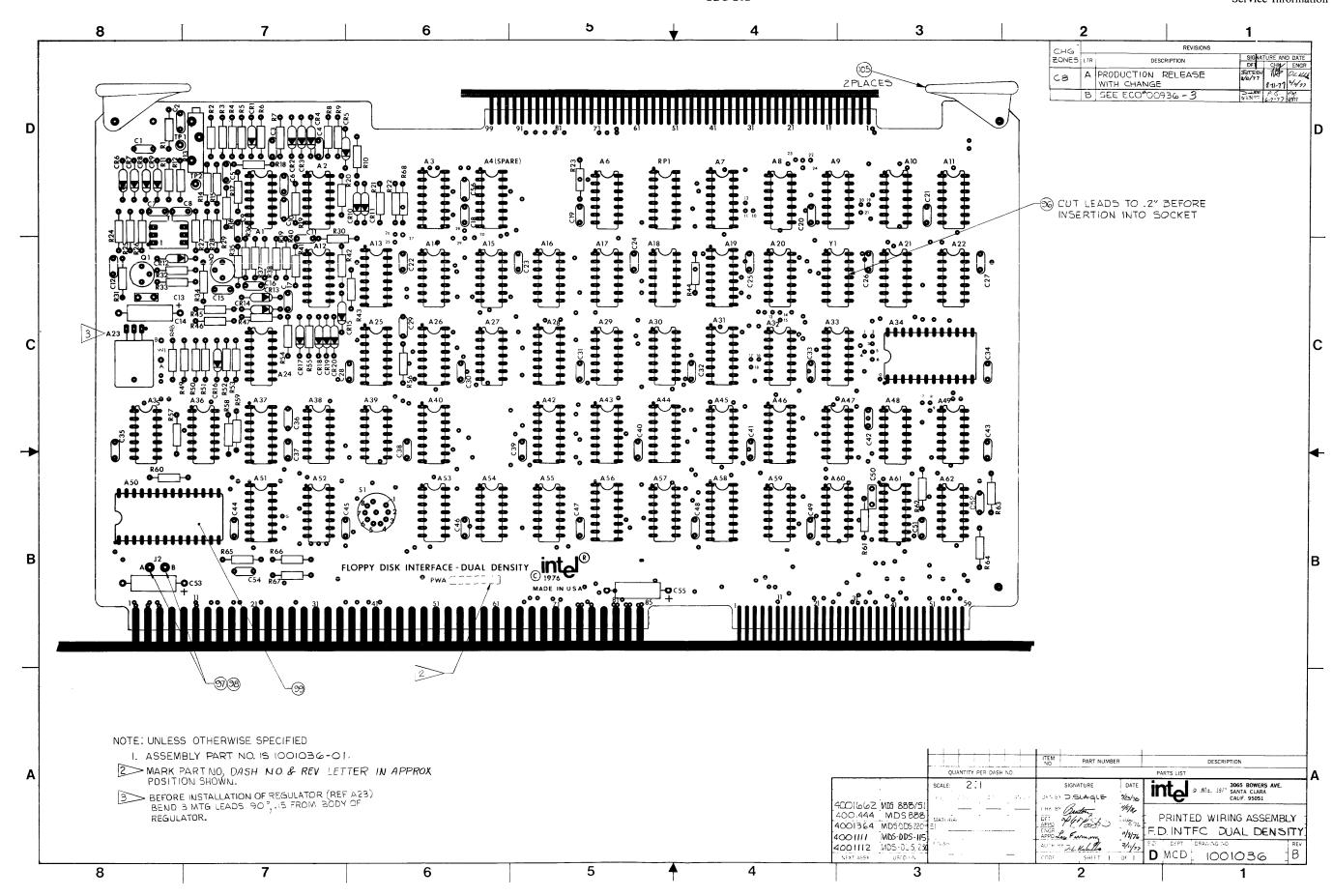

| Block Diagram                            | 4-11 | Parts Location: Interface Board   | 5-5  |

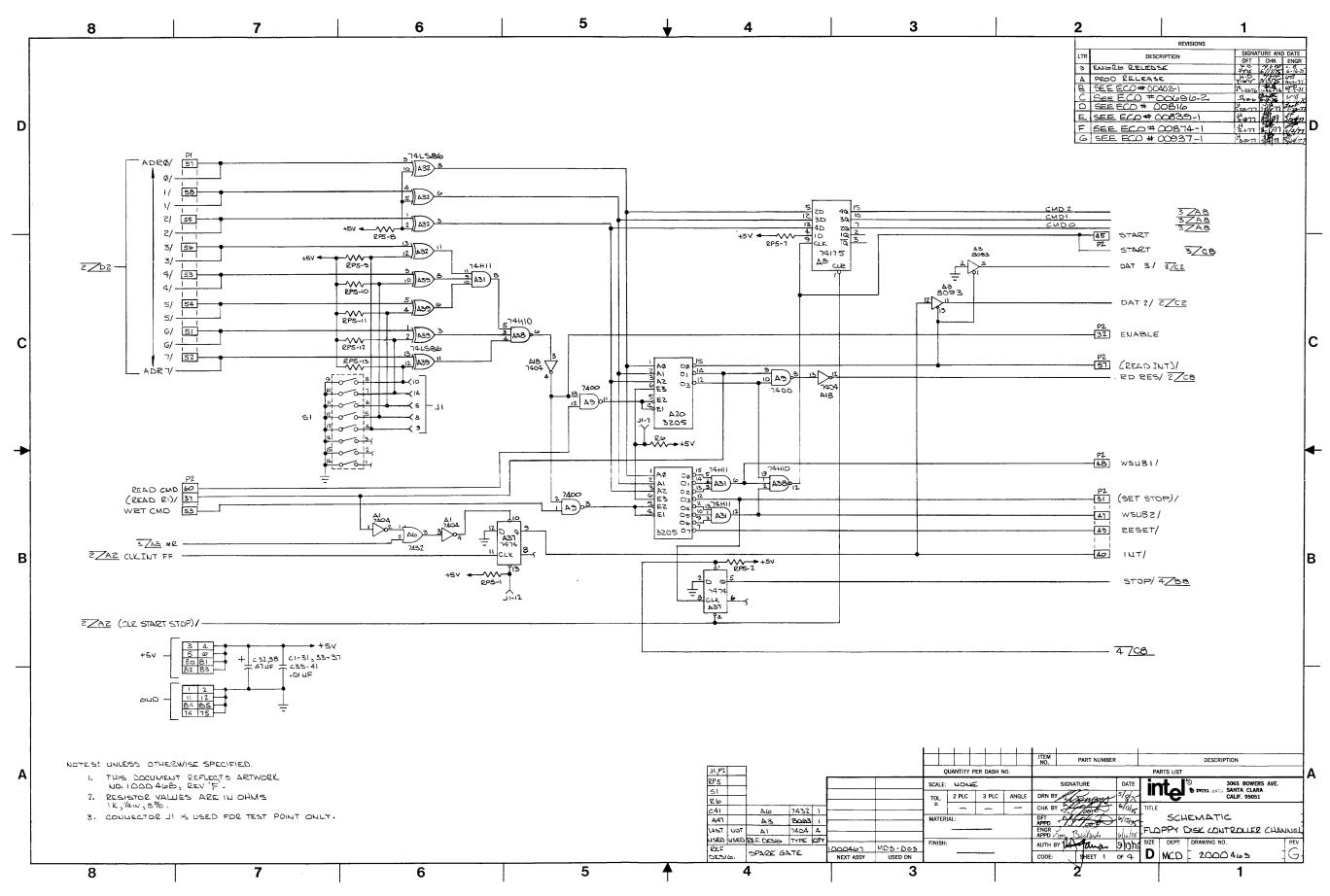

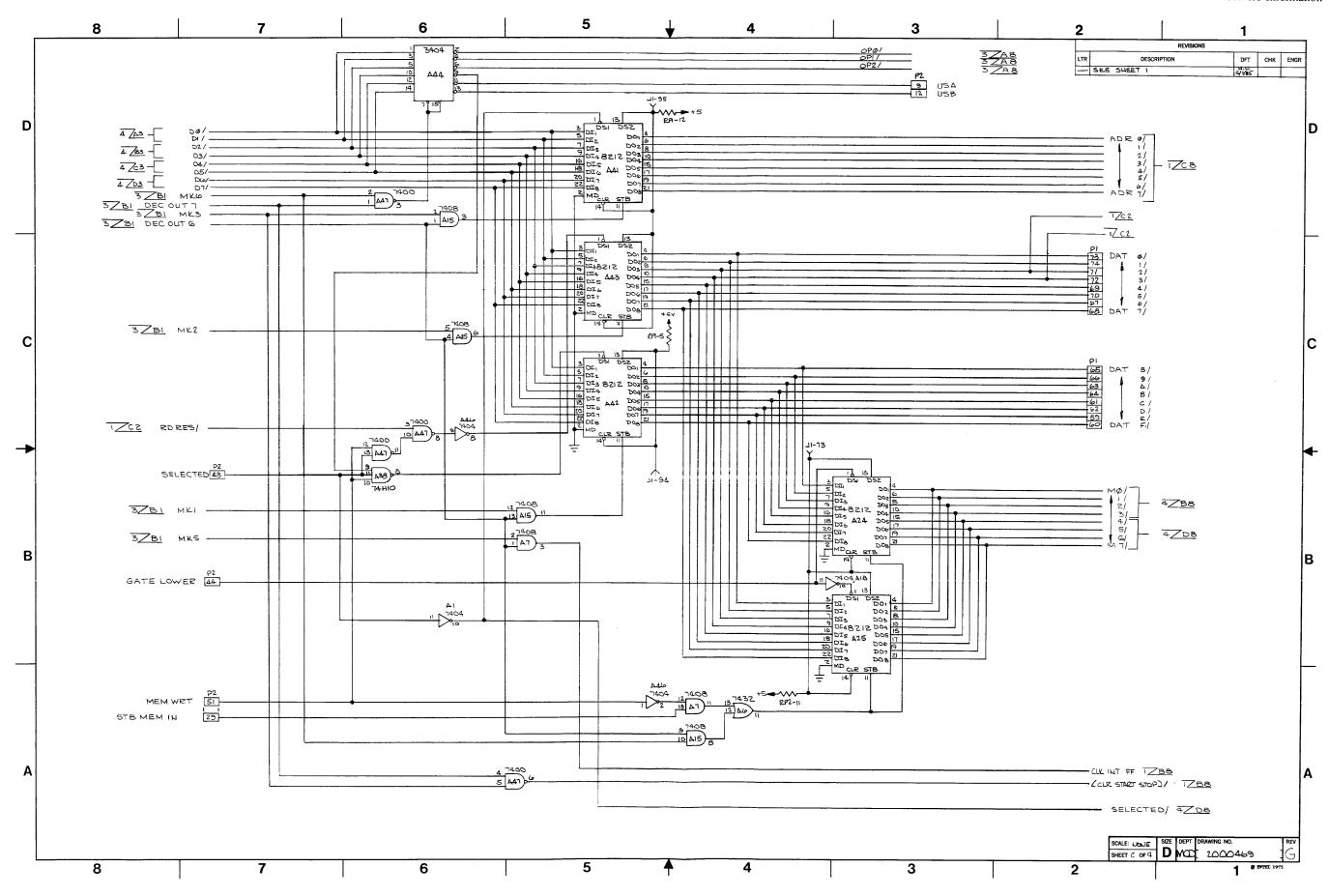

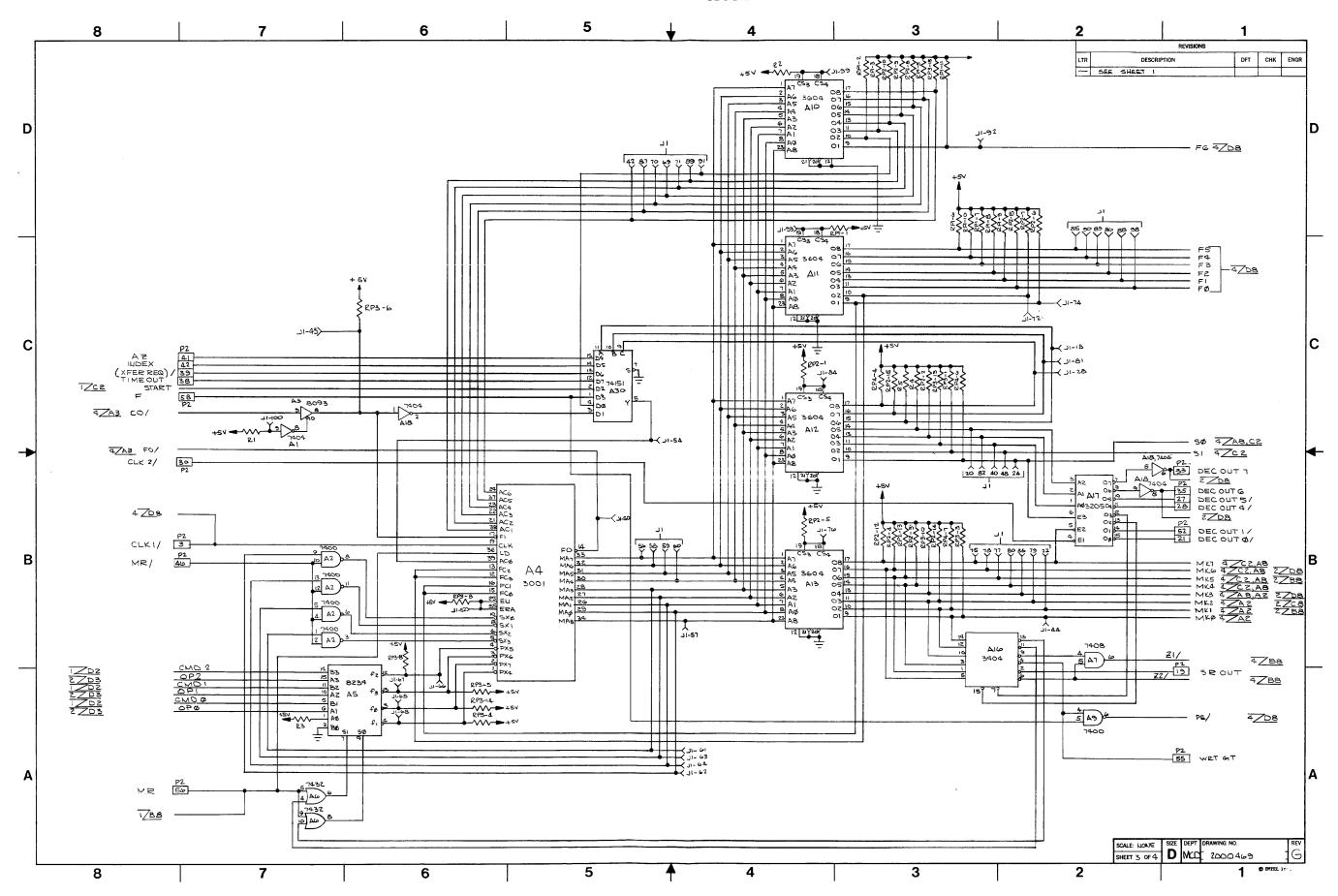

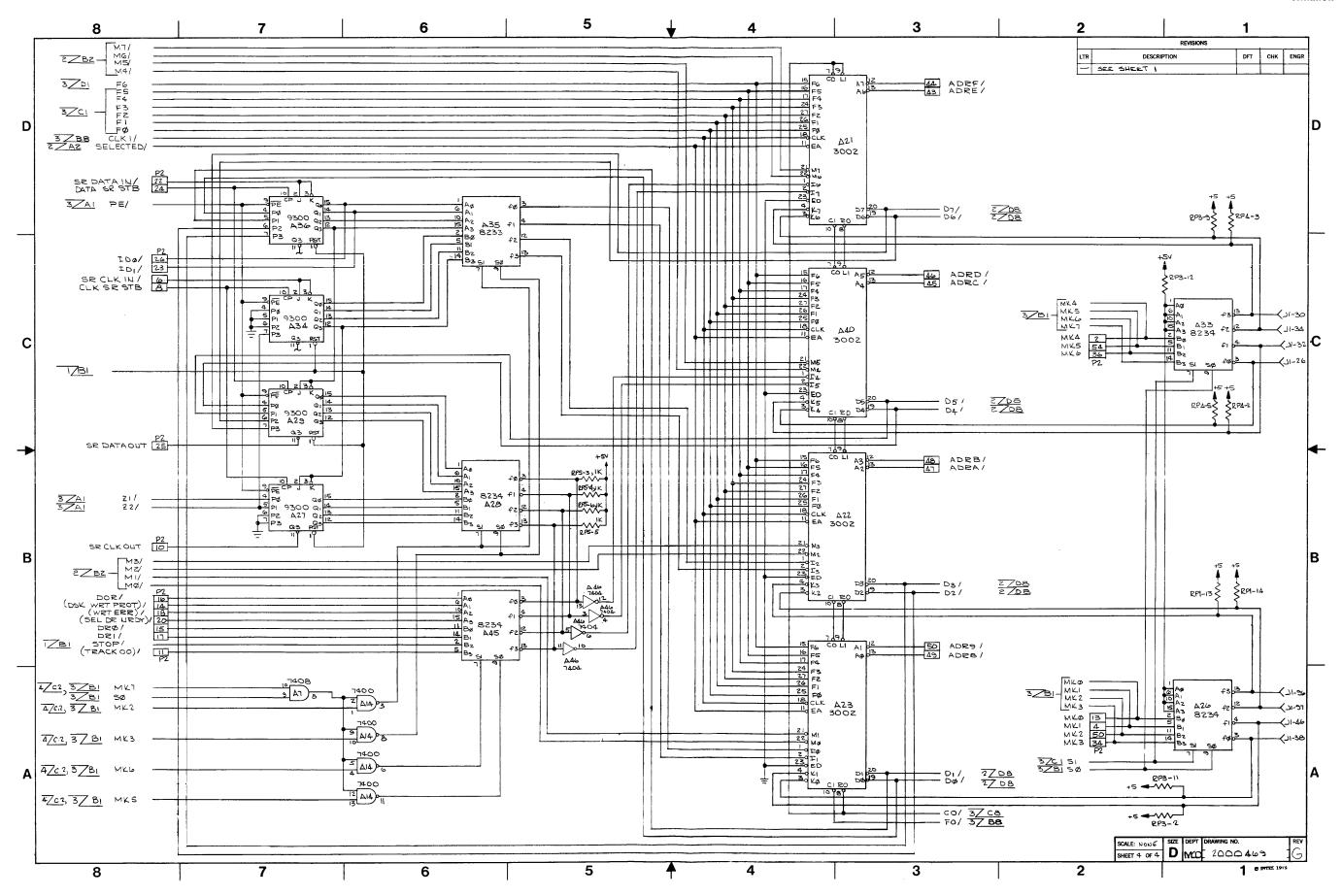

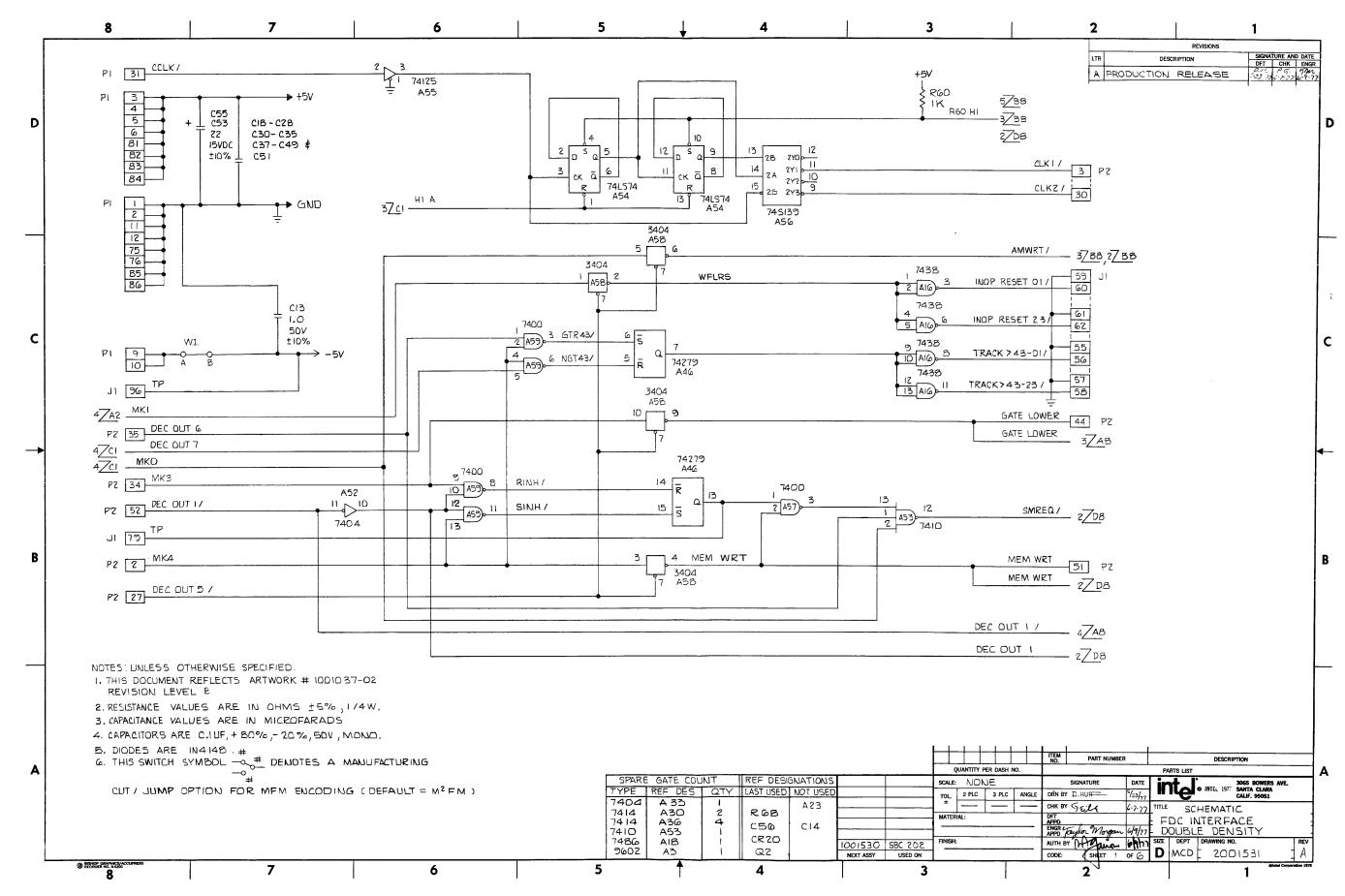

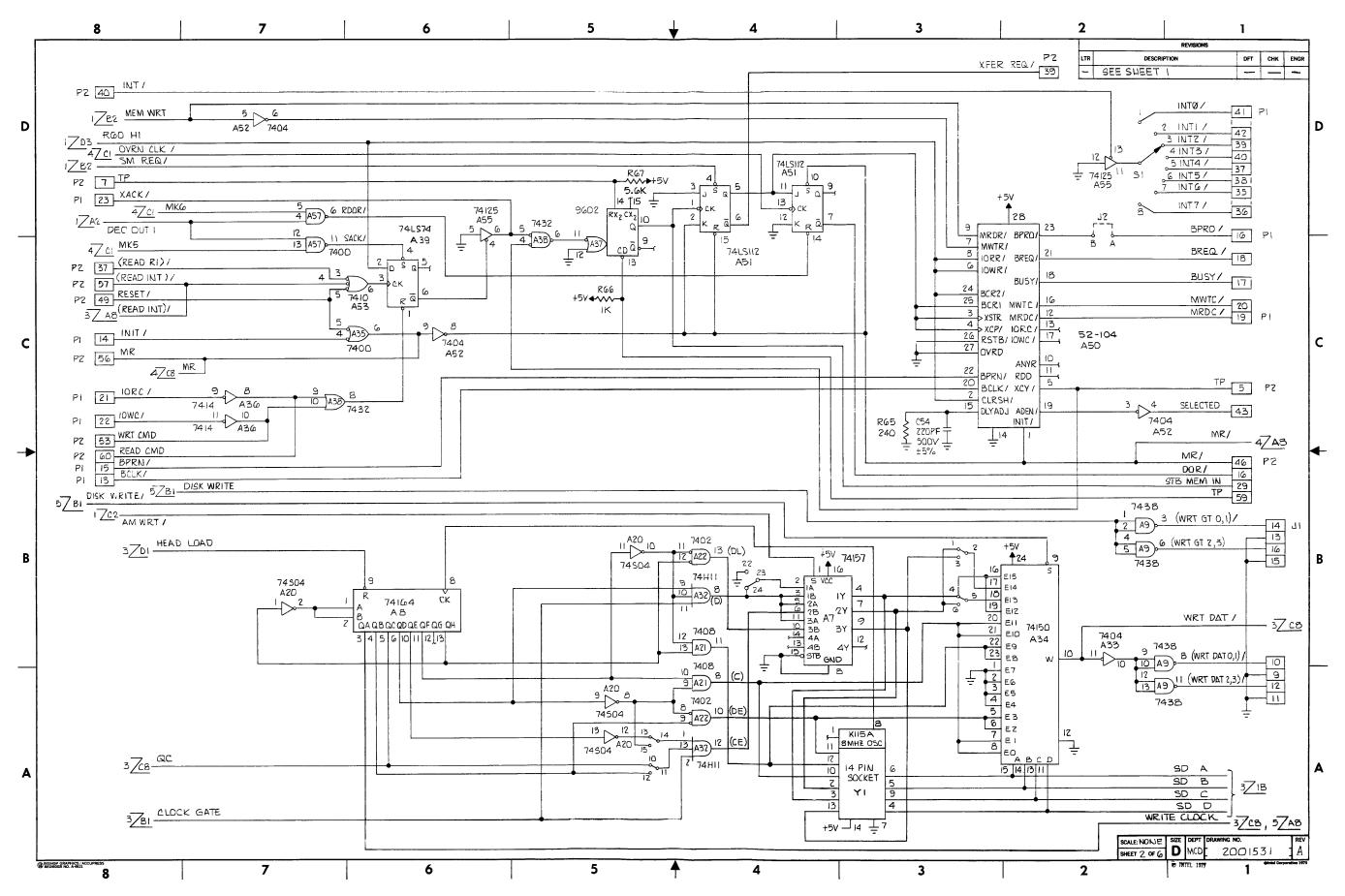

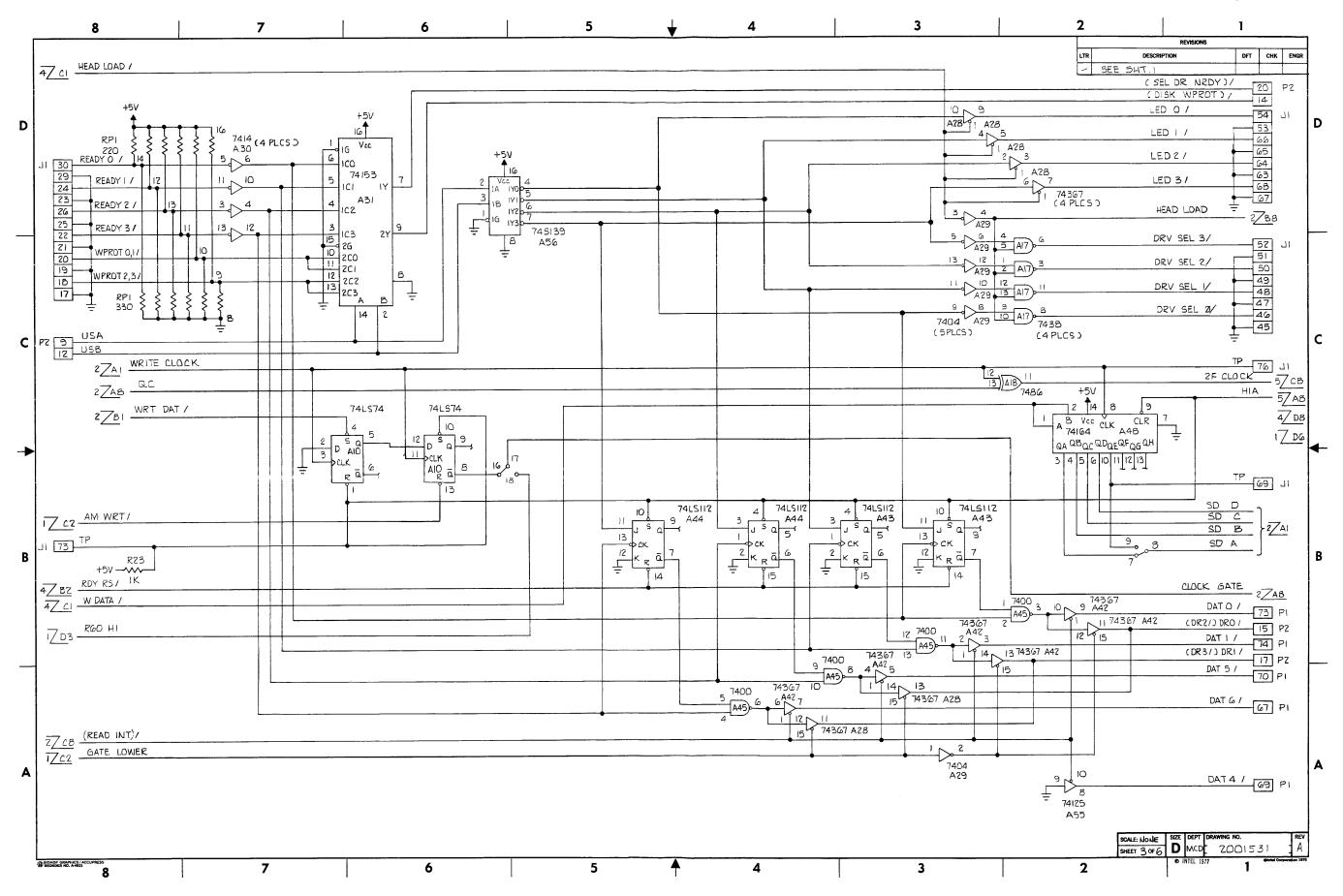

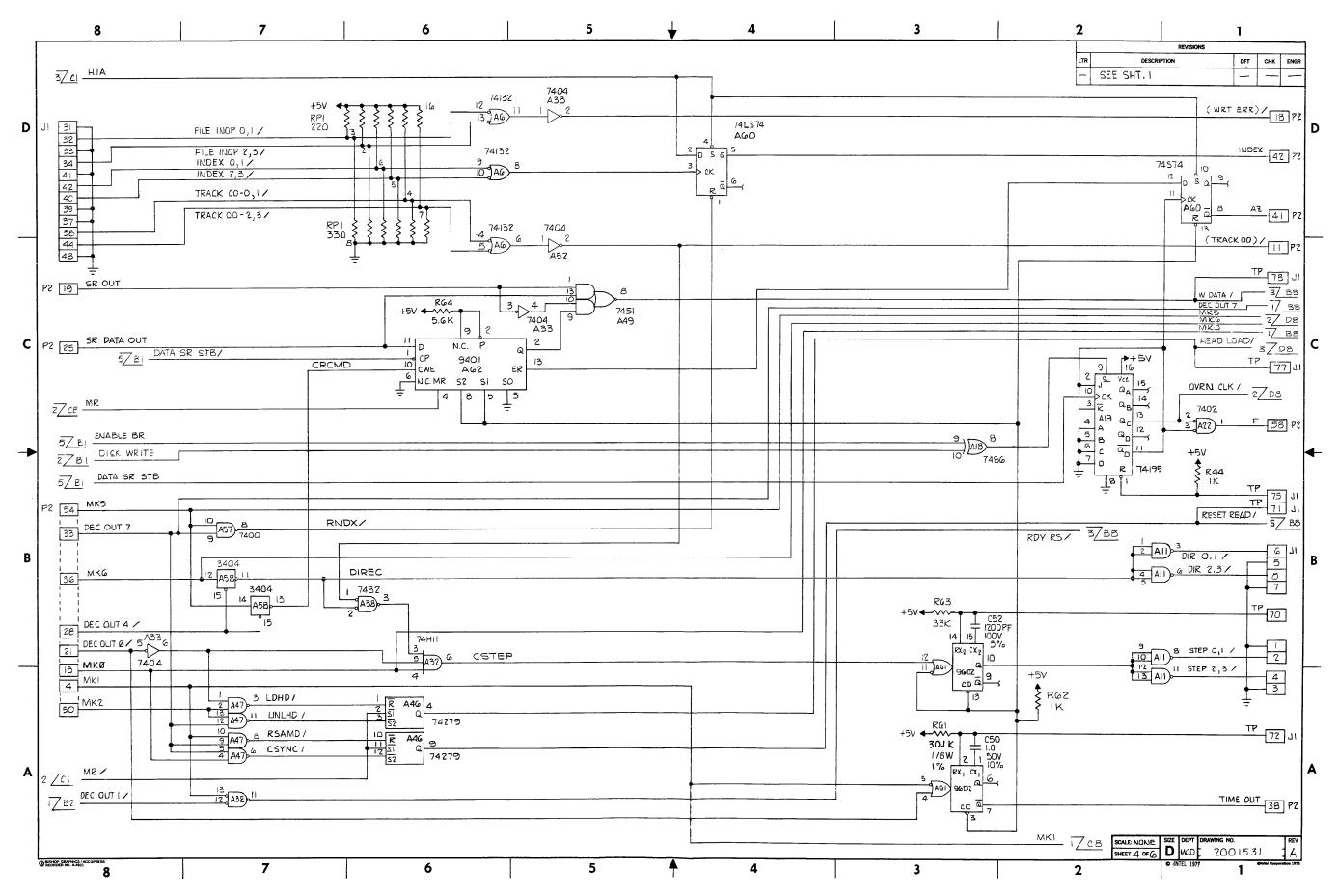

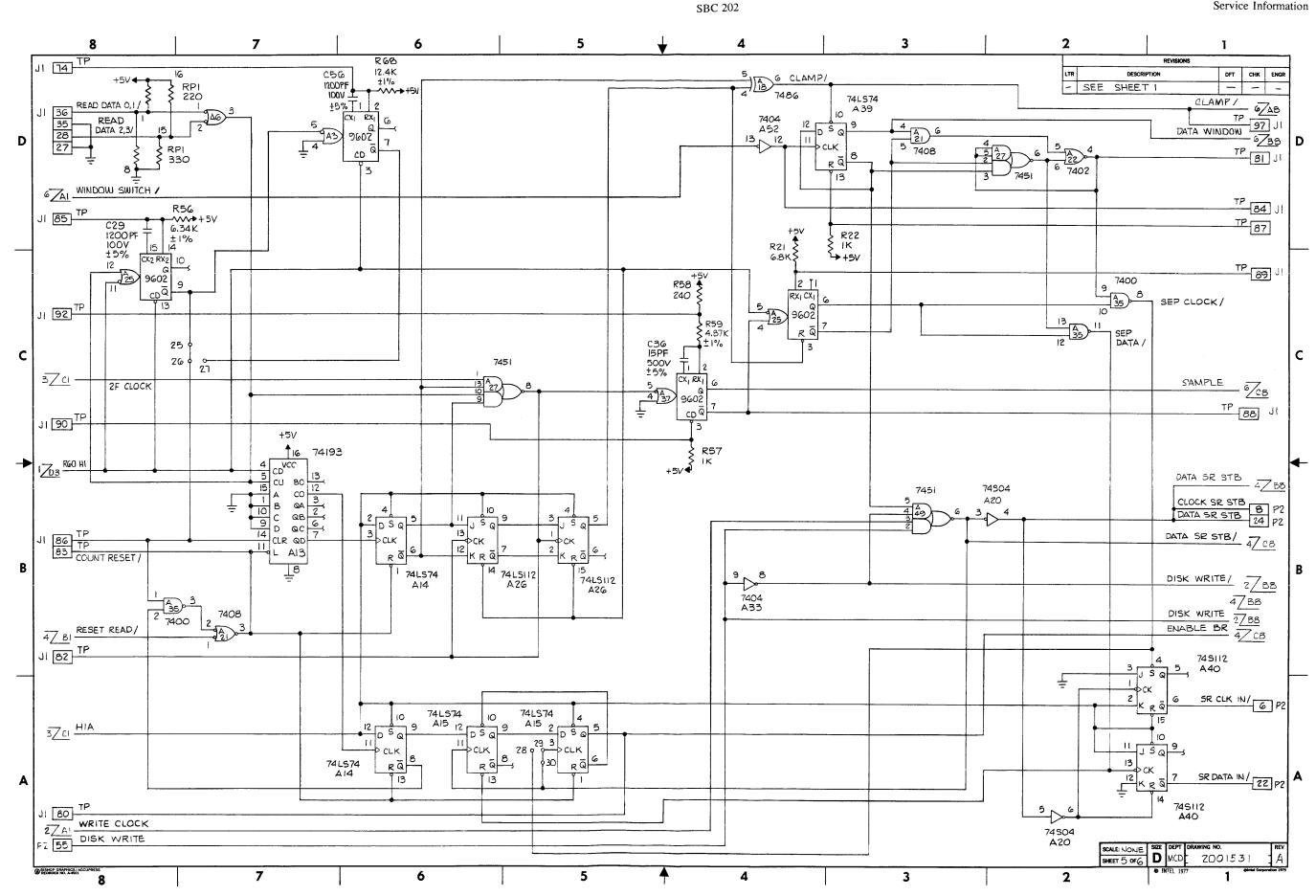

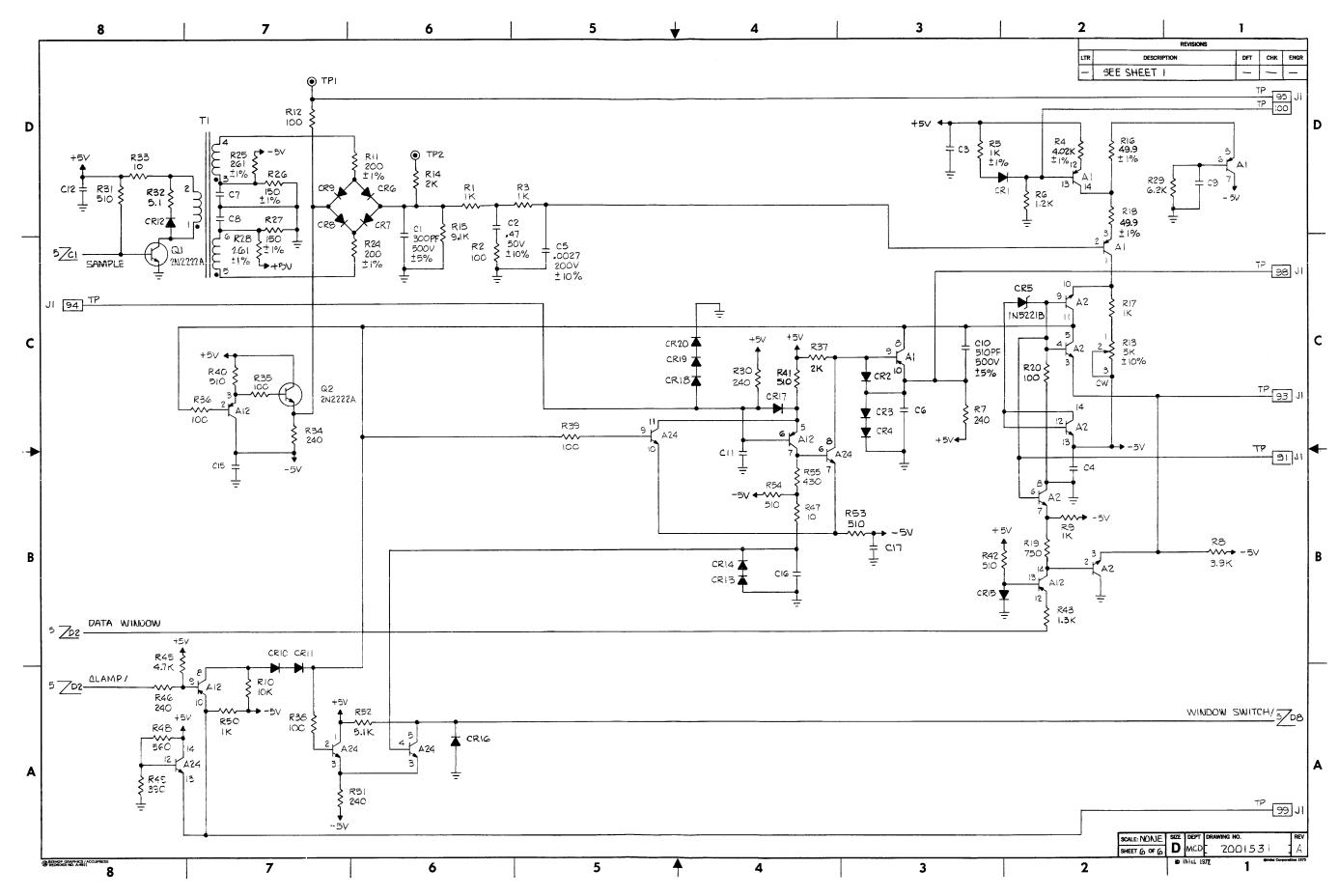

| Interface Board Functional Block Diagram |      | Channel Board Schematic Diagram   | 5-7  |

| Head Movement Control Timing             |      | Interface Board Schematic Diagram | 5-15 |

| Read Initiate Timing                     |      |                                   |      |

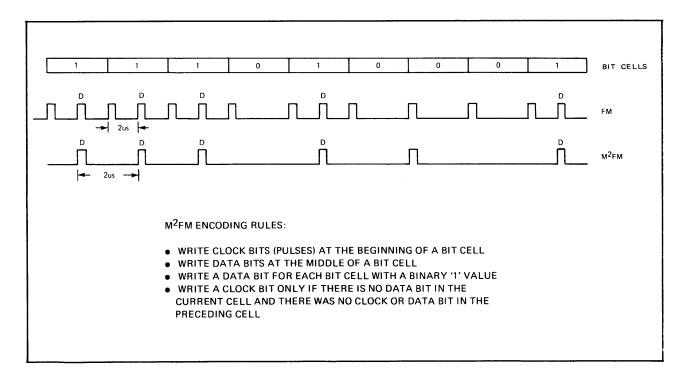

| M2FM Data Encoding                       |      |                                   |      |

# CHAPTER 1 GENERAL INFORMATION

#### 1-1. INTRODUCTION

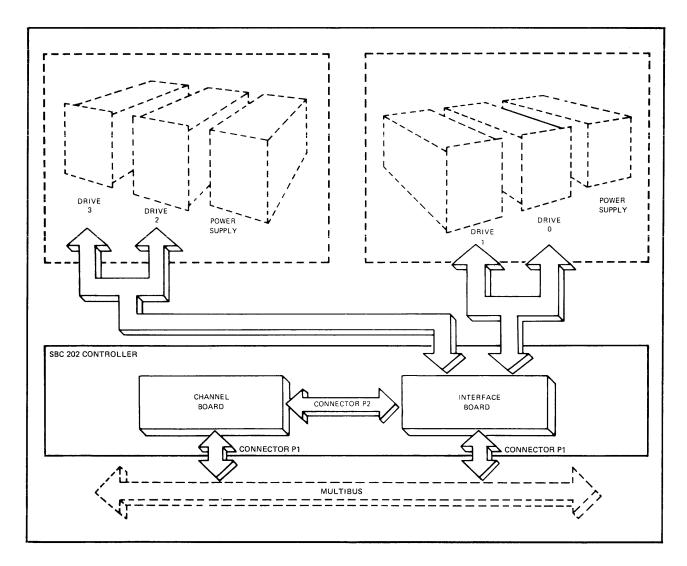

The Intel SBC 202 Double Density Diskette Controller provides control for interfacing up to four flexible diskette drives to any Intel SBC 80 Single Board Computer or System 80. The controller has been implemented with Intel's Series 3000 Bipolar Computing Elements. The SBC 202 provides a high-speed, efficient, and easy to use high capacity random access bulk storage interface. All DMA logic is provided so that no additional board or circuitry are required. Figure 1-1 is a block diagram of a typical system with an SB 202.

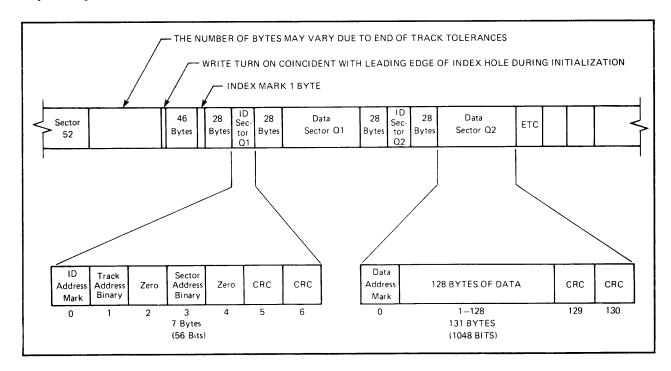

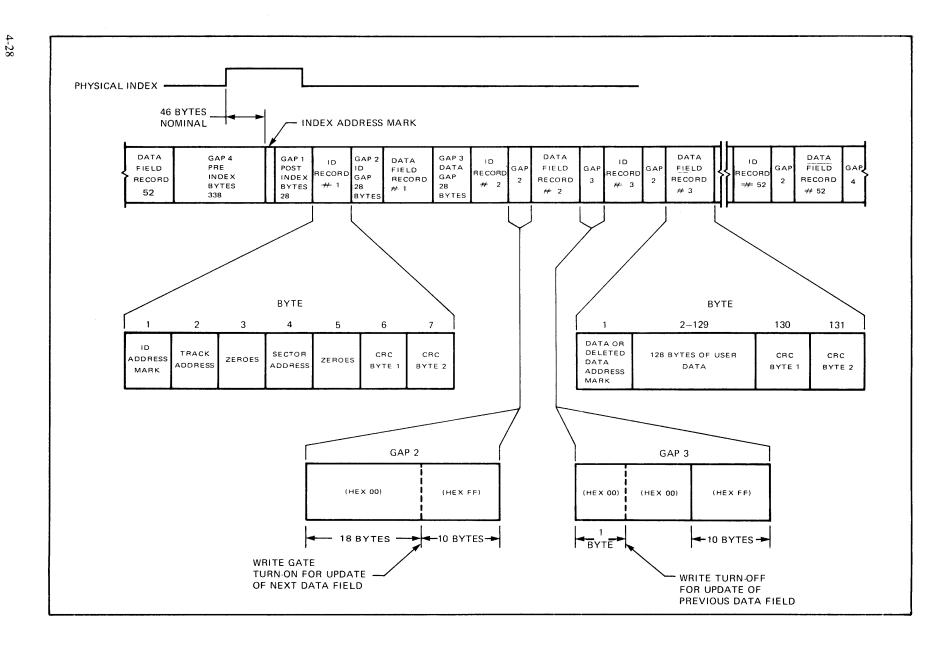

The SBC 202 has been designed to be compatible with most double density specified flexible diskette drives. The controller facilitates recording all data in soft-sector format. The microprogrammed track format consists of 52 records with 128 bytes/record. The Shugart SA 800-1 Drive is fully compatible with this dense track format due to its "straddle-erase" magnetic head. Use of other manufacturers' flexible disk drives is also accommodated, with the limitation that after any "write data" operation, the CPV must delay 500 microseconds before issuing another read or write command. Therefore, use of multi-sector "write data" commands is only possible with the SA 800-1.

Figure 1-1. Typical System Block Diagram

General Information SBC 202

#### 1-2. DESCRIPTION

The SBC 202 Controller consist of two boards—the Channel Board and Interface Board. These boards may reside in the System 80 chassis, the SBC 604 or 614 Module Cardcage, or in the customer's own custom designed SBC 80 bus-compatible backplane. The Channel Board and the Interface Board are discussed in detail below.

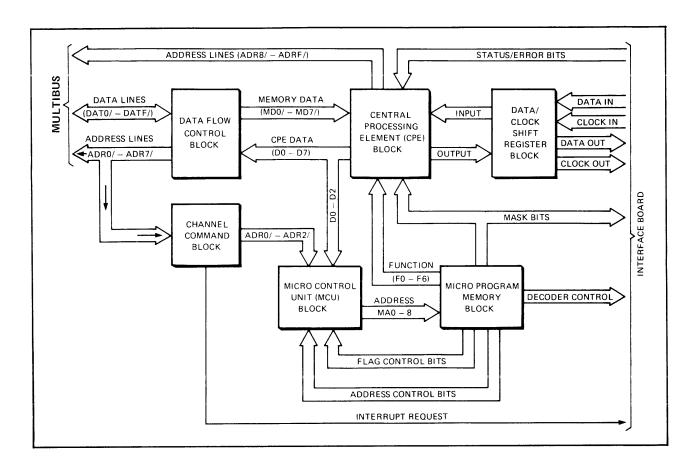

#### 1-3. CHANNEL BOARD

The Channel Board is the primary control module within the diskette controller. It receives, decodes, and responds to channel commands from the Central Processor Unit (CPU) on the Intel SBC 80 Single Board Computer. The Channel Board can access a block of system memory to determine the particular diskette operations to be performed and fetch the parameters required for the successful completion of the specified operation.

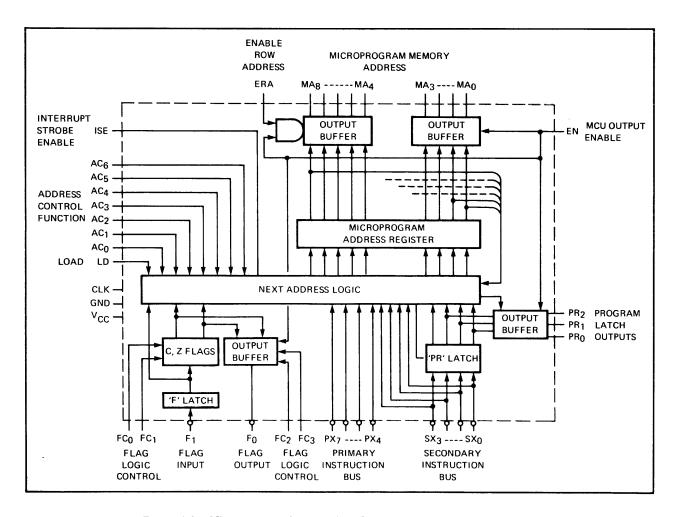

The control functions of the Channel Board have been achieved with an 8-bit microprogrammed processor, designed with Intel's Series 3000 Bipolar Microcomputer Set. This 8-bit processor includes four 3002 Central Processing Elements (2-bit slice per CPE), a 3001 Microprogram Control Unit, and 512 × 32 bits of 3604 programmable read-only memory (PROM) which stores the microprogram. It is the execution of the microprogram by the microcomputer set which actually effects the control capability of the Channel Board.

#### 1-4. INTERFACE BOARD

The Interface Board provides the SBC 202 Double Density Diskette Controller with a means of communication with the diskette drives, as well as with the Intel SBC 80 Multibus.

Under control of the mieroprogram being executed on the Channel Board, the Interface Board generates those signals which cause the read/write head on the selected drive to be loaded (i.e., to come in contact with the diskette platter), cause the head to move to the proper track, and verify successful operation. The Interface Board accepts the data being read off the diskette, interprets synchronizing bit patterns, checks the validity of the data using a cyclic redundancy check (CRC) polynomial, and then transfers the data to the Channel Board.

During write operations, the Interface Board outputs the data and clock bits to the selected drive at the proper times, and generates the CRC characters which are then appended to the data

When the diskette controller requires access to the system memory, the Interface Board requests and maintains DMA transfer control of the system bus, and generates the appropriate memory command. The Interface Board also acknowledges I/O commands as required by the Intel SBC 80 Multibus.

The diskette controller is capable of performing seven different operations: recalibrate, seek, format track, write data, write deleted data, read data, and verify CRC.

#### 1-5. SPECIFICATIONS

Table 1-1 lists the physical and performance characteristics of the SBC 202.

#### 1-6. TERMINOLOGY

Whenever a signal is active-low, its mnemonic is followed by a slash; for example MRDC/ means that the level on that line will be low when the memory read command is true (active). If the signal is subsequently inverted, thus making it active-high, the slash is omitted; for example, MRDC means that the level on that line will be high when the memory command is true.

#### Table 1-1. Specifications

MEDIA (Flexible Diskette)

Recording Surface: One Tracks/Diskette: 77

Sectors/Track: 52

Bytes/Sector: 128

PHYSICAL CHARACTERISTICS

Mounting: Occupies two slots of System 80 Chassis or

SBC 604/614 Cardcage.

Dimensions (each board);

Height: 6.75 in. (17.15 mm)

Width: 12.00 in. (30.48 mm)

Depth: 0.50 in. (1.27 mm)

**ELECTRICAL CHARACTERISTICS**

DC Power Requirements:

Channel Board: 5V @ 3.75A (typ), 5A (max) Interface Board: 5V @ 1.5A (typ), 2.5A (max)

-5V @ 0.1A (typ), 0.2A (max)

**ENVIRONMENTAL CHARACTERISTICS**

Temperature

Operating:  $0^{\circ}\text{C to }55^{\circ}\text{C}$ Non-Operating:  $-55^{\circ}\text{C to }+85^{\circ}\text{C}$

Humidity:

Operating: Up to 90% relative humidity without

condensation.

Non-Operating: All conditions without condensation

of water or frost.

# CHAPTER 2 PREPARATION FOR USE

#### 2-1. INTRODUCTION

This chapter provides instructions for installing the SBC 202 Double Density Diskette Controller. The instructions include unpacking and inspection; installation considerations such as power and cooling requirements, physical dimensions, bus interface requirements, ac and dc signal characteristics, and switch and jumper configurations.

#### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, contact the Intel Technical Support Center (see paragraph 5-3) to obtain a Return Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

#### 2-3. INSTALLATION CONSIDERATIONS

The Diskette Controller is designed to interface an Intel SBC 80 Single Board Computer System 80 based product with a Double Density Diskette such as the Shugart SA 800-1 Drive. Important interfacing criteria are presented in the following paragraphs.

#### 2-4. POWER REQUIREMENTS

The Diskette Controller requires  $+5V~(\pm0.25V)$  at 7.5A maximum and -5V ( $\pm0.25V$ ) at 0.2A maximum. For installation in an SBC 80 Single Board Computer based system

ensure that the system power supply has sufficient current overhead to accommodate the additional requirements.

#### 2-5. COOLING REQUIREMENT

The Diskette Controller dissipates 522 kilogram-calories/hour (131.5 BTU/hour) and adequate circulation of air must be provided to prevent a temperature rise above 55°C (131°F).

Exercise caution in locating the Diskette Drives. The SA 800-1 dissipates 1046 kilogram-calories/hour (314 BTU/hour) for each drive. Provide adequate ventilation to permit the convective dissipation of heat from the system components.

#### 2-6. PHYSICAL DIMENSIONS

Physical dimensions of the Diskette Controller are specified in table 1-1.

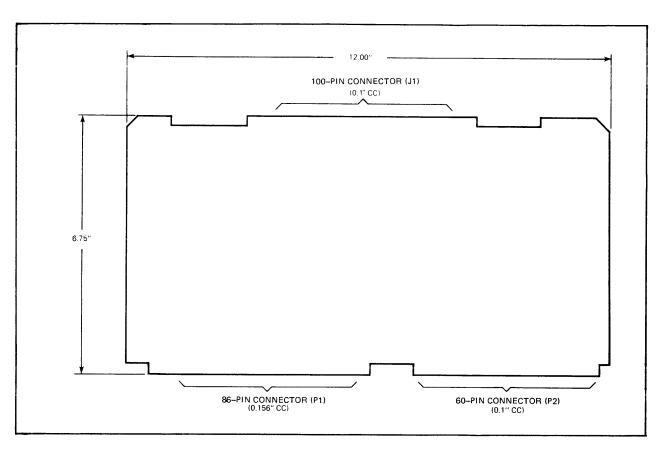

#### 2-7. INTERFACE REQUIREMENTS

The Channel and Interface Boards each communicate with the Multibus through a standard 86-pin double-sided PC edge connector (P1), 0.156" contact centers (see figure 2-1). CON-TROL DATA CORPORATION'S VPB01E43A00A1 is one suitable type of connector for P1. The two controller boards communicate with each other via a 60-pin, double-sided PC edge connector, 0.1" contact centers (see figure 2-1). CDC97169001 is one suitable type of connector for P2. Both boards also include a 100-pin, double-sided PC edge connector (J1), 0.1" contact centers (see figure 2-1). VIKING 3VH50/1JN5 is one suitable type of connector for J1. The Channel Board only uses its J1 connector as a means of accessing various test points on the board. The Interface Board, however, communicates with the diskette drives(s) via its J1 connector. The Interface Board's J1 connector also allows access to various test points. Pin allocations for each of the connectors on the Channel Board are provided in tables 2-1 and 2-2. The same information for the Interface Board is provided in tables 2-3 thru 2-5.

Figure 2-1. Channel and Interface Board Connectors

Table 2-1. Channel Board P1 Connector Pin Assignments

| PIN                                       | SIGNAL                | FUNCTION |

|-------------------------------------------|-----------------------|----------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | GND +5V NO CONNECTION | Power    |

| 11<br>12                                  | GND                   |          |

| 13                                        | <b>^</b>              |          |

| THRU                                      | NO CONNECTION         |          |

| 42                                        | •                     |          |

Table 2-1. Channel Board P1 Connector Pin Assignments (Continued)

| PIN      | SIGNAL         | FUNCTION      |

|----------|----------------|---------------|

| 43       | ADRE/          |               |

| 44       | ADRF/          |               |

| 45       | ADRC/          |               |

| 46       | ADRD/          |               |

| 47       | ADRA/          |               |

| 48       | ADRB/          |               |

| 49       | ADR8/          |               |

| 50       | ADR9/          |               |

| 51       | ADR6/          | ADDRESS lines |

| 52       | ADR7/          |               |

| 53       | ADR4/          |               |

| 54       | ADR5/          |               |

| 55       | ADR2/          |               |

| 56       | ADR3/          |               |

| 57       | ADRO/          |               |

| 58       | ADR1/          |               |

| 59       | DATE/          |               |

| 60       | DATF/          |               |

| 61       | DATC/          |               |

| 62<br>63 | DATD/<br>DATA/ |               |

| 64       | DATA/<br>DATB/ |               |

| 65       | DATB/          |               |

| 66       | DAT9/          | DATA lines    |

| 67       | DAT6/          | DATA lines    |

| 68       | DAT7/          |               |

| 69       | DAT4/          |               |

| 70       | DAT5/          |               |

| 71       | DAT2/          |               |

| 72       | DAT3/          |               |

| 73       | DATO/          |               |

| 74       | DAT1/          |               |

| 75       | } GND          |               |

| 76       | j GIND         |               |

| 77       | )              |               |

| 78       | NO CONNECTION  |               |

| 79       | INO CONNECTION |               |

| 80       | !              |               |

| 81       |                | Power         |

| 82       | } +5V          |               |

| 83       |                |               |

| 84       | !              |               |

| 85<br>86 | GND            |               |

Table 2-2. Channel Board P2 Connector Pin Assignments

| <del></del> 1 |               |                                      |  |

|---------------|---------------|--------------------------------------|--|

| PIN           | SIGNAL        | FUNCTION                             |  |

| 1             | _             | _                                    |  |

| 2             | MK4           | Mask bit 4                           |  |

| 3             | CLK1/         | Diskette controller clock 1          |  |

| 4             | MK1           | Mask bit 1                           |  |

| 5             | _             | _                                    |  |

| 6             | SR CLK IN 1   | Serial clock input line              |  |

| 7             | -             | <del>-</del>                         |  |

| 8             | CLK SR STB    | Serial clock strobe                  |  |

| 9             | USA           | Unit select bit A                    |  |

| 10            | SR CLK OUT    | Serial clock out line                |  |

| 11            | TRACK 00/     | Track 00 detected                    |  |

| 12            | USB           | Unit select bit B                    |  |

| 13            | MKØ           | Mask bit 0                           |  |

| 14            | DSK WRT PROT/ | Disk write protected                 |  |

| 15            | DR0/          | Drive 0 ready                        |  |

| 16            | DOR/          | Data overrun error                   |  |

| 17            | DR1/          | Drive 1 ready                        |  |

| 18            | WRT ERR/      | Write error                          |  |

| 19            | SR OUT        | Write data multiplexer control level |  |

| 20            | SEL DR NRDY/  | Selected drive not ready             |  |

| 21            | DEC OUT 0/    | Control decoder output 0             |  |

| 22            | SR DATA IN/   | Serial data in line                  |  |

| 23            | ID1/          | Input data bit 1                     |  |

| 24            | DATA SR STB   | Serial data strobe                   |  |

| 25            | SR DATA OUT   | Serial data out line                 |  |

| 26            | ID0/          | Input data bit 0                     |  |

| 27            | DEC OUT 5/    | Control decoder 5 output             |  |

| 28            | DEC OUT 4/    | Control decoder 4 output             |  |

| 29            | STB MEM IN    | Strobe memory data in                |  |

| 30            | CLK2/         | Diskette controller clock 2          |  |

| 31            | SET STOP/     | 'Stop diskette' channel command      |  |

| 32            | ENABLE        | Diskette controller addressed        |  |

| 33            | DEC OUT 7     | Control decoder output 7             |  |

| 34            | MK3           | Mask bit 3                           |  |

| 35            | DEC OUT 6     | Control decoder output 6             |  |

| 36            | MK6           | Mask bit 6                           |  |

| 37            | RD RI/        | 'Read result type' channel command   |  |

| 38            | TIME OUT      | 10 msec. timing pulse                |  |

| 39            | XFER REQ/     | Controller requests Multibus         |  |

| 40            | INT/          | Interrupt line                       |  |

| 41            | AZ            | All zeros, valid CRC check           |  |

| 42            | INDEX         | Index mark detected                  |  |

Preparation for Use

Table 2-2. Channel Board P2 Channel Pin Assignments (Continued)

| PIN | SIGNAL     | FUNCTION                                   |

|-----|------------|--------------------------------------------|

| 43  | SELECTED   | Controller has control of Multibus         |

| 44  | GATE LOWER | Input low-order data byte                  |

| 45  | BUSY START | Microprogram responding to channel command |

| 46  | MR/        | Master reset                               |

| 47  | WSUB2/     | Not used at present                        |

| 48  | WSUB1/     | Not used at present                        |

| 49  | RESET/     | 'Reset' channel command                    |

| 50  | MK2        | Mask bit 2                                 |

| 51  | MEM WRT    | Write data to Multibus memory              |

| 52  | DEC OUT 1/ | Control decoder output 1                   |

| 53  | WRT CMD    | I/O write command                          |

| 54  | MK5        | Mask bit 5                                 |

| 55  | WRT GT     | Write gate control level                   |

| 56  | MR         | Master reset                               |

| 57  | RD INT/    | 'Read subsystem status' command            |

| 58  | F          | Shift registers are full or empty          |

| 59  | <u> </u>   | _                                          |

| 60  | RD CMD     | I/O read command                           |

Table 2-3. Interface Board P1 Connector Pin Assignments

| PIN      | SIGNAL         | FUNCTION                         |

|----------|----------------|----------------------------------|

|          |                |                                  |

| 1        | GND            |                                  |

| 2        |                |                                  |

| 3        |                |                                  |

| 4        | } +5 V         |                                  |

| 5        |                | Power                            |

| 6        | {              | 1 OWEI                           |

| 7        | NO CONNECTION  |                                  |

| 8        | {              |                                  |

| 9<br>10  | } -5V          |                                  |

| 11       | 1 !            |                                  |

| 12       | } GND          |                                  |

| 13       | BCLK/          | Bus clock (9.803 MHz)            |

| 14       | INIT/          | System initialization            |

| 15       | BPRN/          | Bus priority in                  |

| 16       | BPRO/          | Bus priority out                 |

| 17       | BUSY/          | Bus busy                         |

| 18       | BREQ/          | Bus request                      |

| 19       | MRDC/          | Memory read command              |

| 20       | MWTC/          | Memory write command             |

| 21       | IORC/          | I/O read command                 |

| 22       | IOWC/          | I/O write command                |

| 23       | XACK/          | Transfer acknowledge             |

| 24       | <b>A</b>       |                                  |

| 25       |                |                                  |

| 26       |                |                                  |

| 27       | NO CONNECTION  |                                  |

| 28       |                |                                  |

| 29       |                |                                  |

| 30       | <b>*</b>       |                                  |

| 31       | CCLK/          | Common clock (9.803 MHz)         |

| 32       | A              |                                  |

| 33       | NO CONNECTION  |                                  |

| 34       | INTO!          |                                  |

| 35       | INT6/          |                                  |

| 36       | INT7/          |                                  |

| 37<br>38 | INT4/<br>INT5/ | Priority interrupt request lines |

| 38       | INT2/          | Friority interrupt request lines |

| 40       | INT3/          |                                  |

| 41       | INTO/          |                                  |

| 42       | INTO/          |                                  |

| 43       |                |                                  |

| 44       | T              |                                  |

| 45       | NO CONNECTION  |                                  |

| 46       | NO CONNECTION  |                                  |

| 47       |                |                                  |

| 48       |                |                                  |

|          | I              |                                  |

Table 2-3. Interface Board P1 Connector Pin Assignments (Continued)

| PIN      | SIGNAL        | FUNCTION |

|----------|---------------|----------|

| 49       | <b>^</b>      |          |

| 50       |               |          |

| 51       |               |          |

| 52       |               |          |

| 53       |               |          |

| 54       |               |          |

| 55       |               |          |

| 56       | j             |          |

| 57       |               |          |

| 58       |               |          |

| 59       |               |          |

| 60       |               |          |

| 61       |               | ·        |

| 62       |               |          |

| 63       |               |          |

| 64       |               |          |

| 65       | NO CONNECTION |          |

| 66       |               |          |

| 67<br>68 |               |          |

| 69       |               |          |

| 70       |               |          |

| 71       |               |          |

| 72       |               | ,        |

| 73       |               |          |

| 74       |               |          |

| 75       |               |          |

| 76       | GND           |          |

| 77       | )             |          |

| 78       | NO CONNECTION |          |

| 79       | ]             |          |

| 80       | )             | Power    |

| 81       |               | · Oveci  |

| 82       | } +5 V        |          |

| 83       |               |          |

| 84       | 1             |          |

| 85       | } GND         |          |

| 86       | ] ] [         |          |

Table 2-4. Interface Board P2 Connector Pin Assignments

| PIN | SIGNAL       | FUNCTION                               |

|-----|--------------|----------------------------------------|

|     |              |                                        |

| 1 2 | —<br>MK4     | —<br>Mask bit 4                        |

| 3   | CLK1/        | Diskette controller clock 1            |

| 4   | MK1          | Mask bit 1                             |

| 5   | TP           | Test point                             |

| 6   | SR CLK IN/   | Serial clock in line                   |

| 7   | TP T         | Test point                             |

| 8   | CLK SR STB   | Serial clock strobe                    |

| 9   | USA          | Unit select bit A                      |

| 10  | _            | —                                      |

| 11  | TRACK00/     | Track 00 detected                      |

| 12  | USB          | Unit select bit B                      |

| 13  | MKO          | Mask bit 0                             |

| 14  | DISK WPROT/  | Disk write protected                   |

| 15  | DR0/ (DR2/)  | Drive 0 ready or Drive 2 ready         |

| 16  | DOR/         | Data overrun error                     |

| 17  | DR1/ (DR3/)  | Drive 1 ready or drive 3 ready         |

| 18  | WRT ERR/     | Write error                            |

| 19  | SR OUT       | Shift register out control level       |

| 20  | SEL DR NRDY/ | Selected drive not ready               |

| 21  | DEC OUT 0/   | Control decoder output 0               |

| 22  | SR DATA IN/  | Serial data in line                    |

| 23  | _            |                                        |

| 24  | DATA SR STB/ | Serial data strobe                     |

| 25  | SR DATA OUT  | Serial data out line                   |

| 26  | _            | —————————————————————————————————————— |

| 27  | DEC OUT 5/   | Control decoder 5 output               |

| 28  | DEC OUT 4/   | Control decoder 4 output               |

| 29  | STB MEM IN   | Strobe memory data in                  |

| 30  | CLK2/        | Diskette controller clock 2            |

| 31  | _            | _                                      |

| 32  |              | _                                      |

| 33  | DEC OUT 7    | Control decoder output 7               |

| 34  | MK3          | Mask bit 3                             |

| 35  | DEC OUT 6    | Control decoder output 6               |

| 36  | MK6          | Mask bit 6                             |

| 37  | RD RI/       | 'Read result type' channel command     |

| 38  | TIME OUT     | 10 msec. timing pulse                  |

| 39  | XFER REQ/    | Controller requests Multibus           |

| 40  | INT/         | Interrupt line                         |

| 41  | AZ           | All zeros, valid CRC check             |

| 42  | INDEX        | Index mark detected                    |

| 43  | SELECTED     | Controller has control of Multibus     |

| 44  | GATE LOWER   | Input low order data byte              |

| 45  | _            |                                        |

| 46  | MR/          | Master reset                           |

| 47  |              | _                                      |

| 48  | _            | _                                      |

Table 2-4. Interface Board P2 Connector Pin Assignments (Continued)

| PIN | SIGNAL     | FUNCTION                                |

|-----|------------|-----------------------------------------|

| 49  | RESET/     | 'Reset' channel command                 |

| 50  | MK2        | Mask bit 2                              |

| 51  | MEM WRT    | Write data to System memory             |

| 52  | DEC OUT 1/ | Control decoder output 1                |

| 53  | WRT CMD    | I/O write command                       |

| 54  | MK5        | Mask bit 5                              |

| 55  | WRTGT      | Write gate control level                |

| 56  | MR         | Master reset                            |

| 57  | RD INT/    | 'Read subsystem status' channel command |

| 58  | F          | Shift registers full or empty           |

| 59  | TP         | Test point                              |

| 60  | RD CMD     | I/O read command                        |

Table 2-5. Interface Board J1 Connector Pin Assignments

| PIN | SIGNAL          | FUNCTION                                        |

|-----|-----------------|-------------------------------------------------|

| 1   | GND             | Ground                                          |

| 2   | STEP 0, 1/      | Steps head one track (drive 0, 1)               |

| 3   | GND             | Ground                                          |

| 4   | STEP 2, 3/      | Steps head one track (drive 2, 3)               |

| 5   | GND             | Ground                                          |

| 6   | DIR 0, 1/       | Step direction indicator (drive 0, 1)           |

| 7   | GND             | Ground                                          |

| 8   | DIR 2, 3/       | Step direction indicator (drive 2, 3)           |

| 9   | GND             | Ground                                          |

| 10  | WRT DAT 0, 1/   | Write data (drive 0, 1)                         |

| 11  | GND             | Ground                                          |

| 12  | WRT DAT 2, 3/   | Write data (drive 2, 3)                         |

| 13  | GND             | Ground                                          |

| 14  | WRT GT 0, 1/    | Write gate (drive 0, 1)                         |

| 15  | GND             | Ground                                          |

| 16  | WRT GT 2, 3/    | Write gate (drive 2, 3)                         |

| 17  | GND             | Ground                                          |

| 18  | WPROT 2, 3/     | Diskette write protected indicator (drive 0, 1) |

| 19  | GND             | Ground                                          |

| 20  | WPROT 0, 1/     | Diskette write protected indicator (drive 2, 3) |

| 21  | GND             | Ground                                          |

| 22  | READY 3/        | Ready indicator from drive 3                    |

| 23  | GND             | Ground                                          |

| 24  | READY 1/        | Ready indicator from drive 1                    |

| 25  | GND             | Ground                                          |

| 26  | READY 2/        | Ready indicator from drive 2                    |

| 27  | GND             | Ground                                          |

| 28  | READ DATA 2, 3/ | Read data, unseparated (drive 2, 3)             |

Table 2-5. Interface Board J1 Connector Pin Assignments (Continued)

| PIN | SIGNAL               | FUNCTION                                              |

|-----|----------------------|-------------------------------------------------------|

| 29  | GND                  | Ground                                                |

| 30  | READY 0/             | Ready indicator from drive 0                          |

| 31  | GND                  | Ground                                                |

| 32  | FILE INOP 0, 1/      | Drive inoperable, write fault (drive 0, 1)            |

| 33  | GND                  | Ground                                                |

| 34  | FILE INOP 2, 3/      | Drive inoperable, write fault (drive 2, 3)            |

| 35  | GND                  | Ground                                                |

| 36  | READ DATA 0, 1/      | Read data, unseparated (drive 0, 1)                   |

| 37  | GND                  | Ground                                                |

| 38  | TRACK00 - 0, 1/      | Track 0 indicator (drive 0, 1)                        |

| 39  | GND                  | Ground                                                |

| 40  | INDEX 2, 3/          | Index indicator (drive 2, 3)                          |

| 41  | GND                  | Ground                                                |

| 42  | INDEX 0, 1/          | Index indicator (drive 0, 1)                          |

| 43  | GND                  | Ground                                                |

| 44  | TRACK00 - 2, 3/      | Track Ø indicator (drive 2, 3)                        |

| 45  | GND                  | Ground                                                |

| 46  | DRV SEL 0/           | Select/load head drive Ø                              |

| 47  | GND                  | Ground                                                |

| 48  | DRV SEL 1/           | Select/load head drive 1                              |

| 49  | GND                  | Ground                                                |

| 50  | DRV SEL 2/           | Select/load head drive 2                              |

| 51  | GND                  | Ground                                                |

| 52  | DRV SEL 3/           | Select/load head drive 3                              |

| 53  | GND                  | Ground                                                |

| 54  | LED 0/               | Drive 0 selected indicator                            |

| 55  | GND                  | Ground                                                |

| 56  | TRACK $> 43 - 0, 1/$ | Track greater than 43, low write current (drive 0, 1) |

| 57  | GND                  | Ground                                                |

| 58  | TRACK $> 43 - 2, 3/$ | Track greater than 43, low write current (drive 2, 3) |

| 59  | GND                  | Ground                                                |

| 60  | INOP RESET 0, 1/     | File inoperable reset (drive 0, 1)                    |

| 61  | GND                  | Ground                                                |

| 62  | INOP RESET 2, 3/     | File inoperable reset (drive 2, 3)                    |

| 63  | GND                  | Ground                                                |

| 64  | LED 2/               | Drive 2 selected indicator                            |

| 65  | GND                  | Ground                                                |

| 66  | LED 1/               | Drive 1 selected indicator                            |

| 67  | GND                  | Ground                                                |

| 68  | LED 3/               | Drive 3 selected indicator                            |

| 69  | TP                   | Test Point                                            |

| 70  | TP                   | <b>^</b>                                              |

| 71  | TP                   |                                                       |

| 72  | TP                   |                                                       |

| 73  | TP                   |                                                       |

| 74  | TP                   |                                                       |

| 75  | TP                   | <b>↓</b>                                              |

| 76  | TP                   | Test Point                                            |

Table 2-5. Interface Board J1 Connector Pin Assignment (Continued)

| PIN | SIGNAL | FUNCTION   |

|-----|--------|------------|

| 77  | TP     | Test Point |

| 78  | TP     | <b>A</b>   |

| 79  | TP     |            |

| 80  | TP     |            |

| 81  | TP     |            |

| 82  | TP     |            |

| 83  | TP     |            |

| 84  | TP     |            |

| 85  | TP     |            |

| 86  | TP     |            |

| 87  | TP     |            |

| 88  | TP     |            |

| 89  | TP     |            |

| 90  | TP     |            |

| 91  | TP     |            |

| 92  | TP     |            |

| 93  | TP     |            |

| 94  | TP     |            |

| 95  | TP     |            |

| 96  | TP     |            |

| 97  | TP     |            |

| 98  | TP     |            |

| 99  | TP     |            |

| 100 | TP     | Test Point |

Preparation for Use SBC 202

#### 2-8. OPERATING CHARACTERISTICS

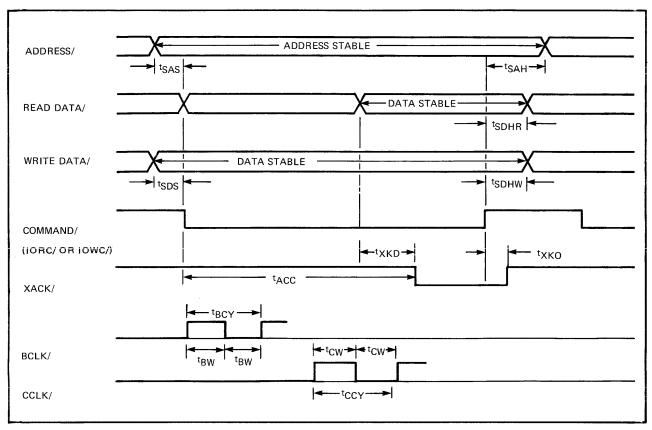

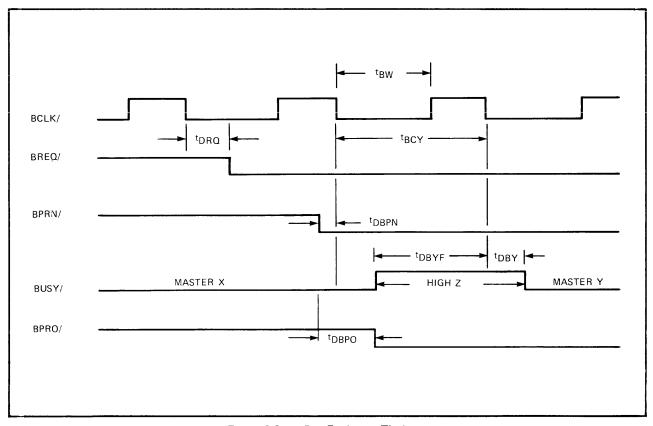

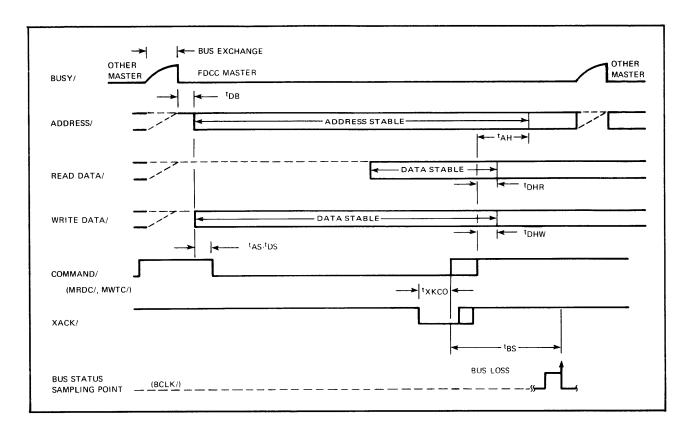

AC characteristics of the Diskette Controller are presented in tables 2-6 and 2-7, and figures 2-2 through 2-9. DC characteristics are specified in tables 2-8 and 2-9.

Table 2-6. Diskette Controller/Multibus AC Characteristics

| PARAMETER          | MINIMUM<br>(nsec) | MAXIMUM<br>(nsec) | DESCRIPTION                             | REMARKS                                       |

|--------------------|-------------------|-------------------|-----------------------------------------|-----------------------------------------------|

| <sup>t</sup> SAS   | 50                |                   | Address Setup Time to I/O<br>Command    | Provided by Host CPU                          |

| tSDS               | 0                 |                   | Data Setup Time to I/O Command          | Provided by Host CPU                          |

| <sup>t</sup> SAH   | 0                 |                   | Address Hold Time from I/O<br>Command   | Provided by Host CPU                          |

| <sup>t</sup> SDHW  | 0                 |                   | Data Hold Time from I/O<br>Command      | Provided by Host CPU                          |

| <sup>t</sup> \$DHR | 25                |                   | Read Data Hold Time from I/O<br>Command | Provided by Flexible Disc<br>Controller (FDC) |

| <sup>t</sup> ACC   | Bus <sup>-</sup>  | l<br>Timeout      | I/O Access Time                         | Provided by FDC                               |

| <sup>t</sup> XKD   | 7                 |                   | XACK Delay from Read Data               | Provided by FDC                               |

| <sup>t</sup> XKO   | 30                |                   | XACK Hold Time from I/O<br>Command      | Provided by FDC                               |

| <sup>t</sup> BCY   | 100               |                   | Bus Clock Cycle Time                    | Provided by CPU                               |

| t <sub>BW</sub>    | 25                |                   | Bus Clock Low and High Periods          | Provided by CPU                               |

| TCCY               | 100               |                   | Common Clock Cycle Time                 | Provided by CPU                               |

| <sup>t</sup> CW    | 25                |                   | Common Clock Low and High<br>Periods    | Provided by CPU                               |

| <sup>t</sup> DRQ   |                   | 35                | Bus Request Delay                       |                                               |

| tDBY               |                   | 65                | Bus Busy Turn on Delay                  |                                               |

| <sup>t</sup> DBYF  |                   | 40                | Bus Busy Turn off Delay                 |                                               |

| <sup>t</sup> DBPN  | 30                |                   | Priority Input Setup Time               |                                               |

| <sup>t</sup> DBPO  |                   | 20                | BPRO/ Serial Delay from BPRN/           |                                               |

| t <sub>DB</sub>    | 50                |                   | Busy to Address/Data Delay              |                                               |

Table 2-6. Diskette Controller/Multibus AC Characteristics (Continued)

| PARAMETER           | MINIMUM<br>(nsec) | MAXIMUM<br>(nsec) | DESCRIPTION                   | REMARKS                              |

|---------------------|-------------------|-------------------|-------------------------------|--------------------------------------|

| <sup>t</sup> AS, DS | 60                |                   | Address/Data Setup to Command |                                      |

| <sup>t</sup> XKCO   | 35                | 125               | XACK to Command Turn Off      |                                      |

| <sup>t</sup> AH     | 115               |                   | Address Hold Time             |                                      |

| <sup>t</sup> DHW    | 125               |                   | Data Hold Time                |                                      |

| <sup>t</sup> DHR    | 0                 |                   | Read Data Hold Time           | Provided by Memory<br>Module (Slave) |

| <sup>†</sup> BS     | 200               |                   | Bus Sample Delay Time         | Wodale (Glave)                       |

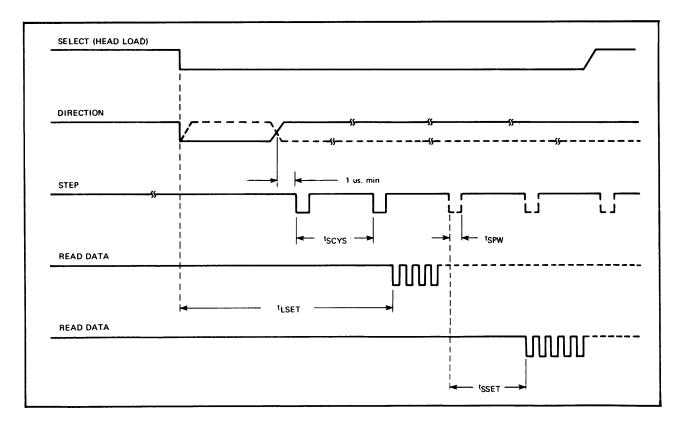

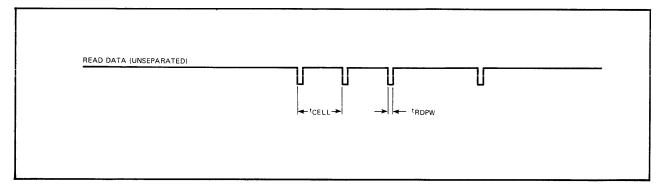

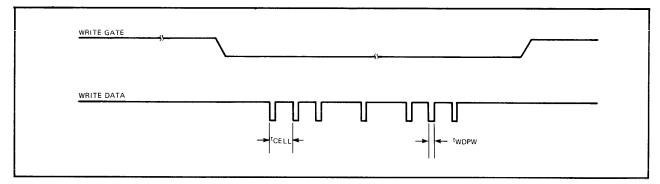

Table 2-7. Diskette Controller/Drive Interface AC Characteristics

| PARAMETER         | MINIMUM  | TYPICAL    | MAXIMUM  | DESCRIPTION                    |

|-------------------|----------|------------|----------|--------------------------------|

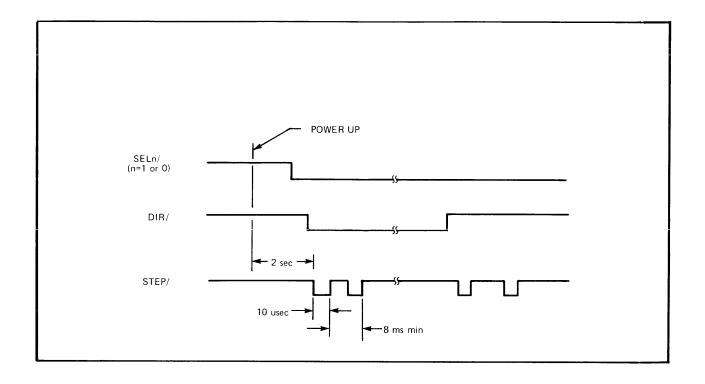

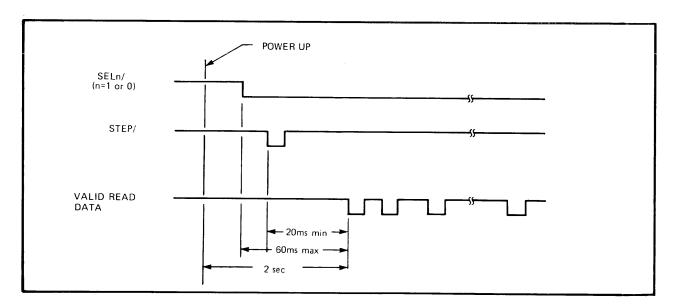

| <sup>t</sup> SCYS | 8 msec   | 10 msec    | 12 msec  | Step Cycle Time                |

| <sup>t</sup> SPW  |          | 10 usec    |          | Step Pulse Width               |

| <sup>t</sup> LSET |          | 60 msec    |          | Settling Time — Select to Data |

| <sup>t</sup> SSET |          | 20 msec    |          | Settling Time — Step to Data   |

| <sup>t</sup> RDPW | 200 nsec | 250 nsec   | 300 nsec | Read Data Pulse Width (Rd)     |

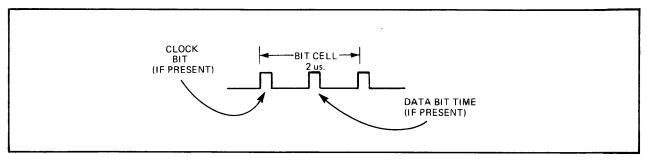

| †CELL             |          | 2 usec     |          | Bit Cell Time                  |

| <sup>t</sup> WDPW |          | 250 nsec   |          | Write Data Pulse Width (Wt)    |

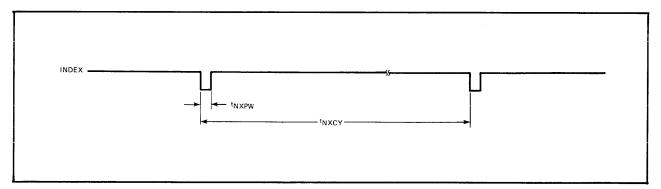

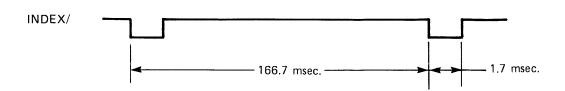

| <sup>t</sup> NXPW |          | 1.5 msec   |          | Multibus Pulse Width           |

| tNXCY             |          | 166.7 msec |          | Index Cycle Time               |

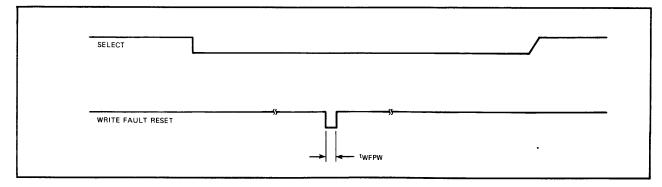

| t <sub>WFPW</sub> | 2 usec   |            | 2.8 usec | Write Fault Reset Pulse Width  |

Preparation for Use SBC 202

Table 2-8. Diskette Controller/Multibus DC Characteristics

|               |                                    | PARAMETER                        | TEST                                           | P    | ARAMETI     | R     |

|---------------|------------------------------------|----------------------------------|------------------------------------------------|------|-------------|-------|

| SIGNAL        | SYMBOL                             | DESCRIPTION                      | CONDITION                                      | MIN  | MAX         | UNITS |

| ADRF/-ADR8/   | VOL                                | Output Low Voltage               | I <sub>OI</sub> =10mA                          |      | .45         | v     |

|               | v <sub>OH</sub>                    | Output High Voltage              | I <sub>OH</sub> =-1mA                          | 2.4  |             | v     |

|               | *c                                 | Capacitive Load                  | OII                                            |      | 15          | pf    |

|               |                                    |                                  |                                                |      |             | μ,    |

| ADR7/ ADRØ/   | VOL                                | Output Low Voltage               | I <sub>OL</sub> =15mA                          |      | .45         | V     |

|               | V <sub>ОН</sub>                    | Output High Voltage              | I <sub>OH</sub> =-1mA                          | 3.65 |             | V     |

|               | VIL                                | Input Low Voltage                |                                                |      | .8          | V     |

|               | VIH                                | Input High Voltage               |                                                | 2    |             | V     |

|               | l <sub>IL</sub>                    | Input Current at V <sub>IL</sub> | V <sub>IL</sub> = .4V                          |      | -1.6        | mA    |

|               | 'ін                                | Input Current at V <sub>IH</sub> | V <sub>IH</sub> =2.4V                          |      | 40          | uA    |

|               | *C                                 | Capacitive Load                  |                                                |      | 15          | pf    |

| DATF/ – DAT4/ | Voi                                | Output Low Voltage               | 115mA                                          |      | 45          |       |

| DAITY DAITY   | V <sub>OL</sub><br>V <sub>OH</sub> | Output High Voltage              | I <sub>OL</sub> =15mA<br>I <sub>OH</sub> =-1mA | 3.65 | .45         | V     |

|               | VIL                                | Input Low Voltage                | 10H1111A                                       | 3.05 | .85         | V     |

|               | VIH                                | Input High Voltage               |                                                | 2    | .65         | V     |

|               | l lil                              | Input Current at VII             | V <sub>IL</sub> = .45V                         |      | <b>–.25</b> | mA    |

|               | IIH                                | Input Current at V <sub>IH</sub> | V <sub>IH</sub> =5.25V                         |      | 10          | uA    |

|               | *c                                 | Capacitive Load                  | III                                            |      | 15          | pf    |

|               |                                    |                                  |                                                |      |             | '     |

| DAT3/ - DATØ/ | VOL                                | Output Low Voltage               | I <sub>OL</sub> =15mA                          |      | .45         | V     |

|               | V <sub>ОН</sub>                    | Output High Voltage              | I <sub>OH</sub> =-1mA                          | 3.65 |             | V     |

|               | VIL                                | Input Low Voltage                |                                                |      | .85         | V     |

|               | V <sub>IH</sub>                    | Input High Voltage               |                                                | 2    | 0.5         | V     |

|               | IL.                                | Input Current at VIL             | V <sub>IL</sub> = .45V                         |      | 25          | mA    |

|               | I <sub>IH</sub>                    | Input Current at V <sub>IH</sub> | V <sub>IH</sub> =5.25V                         |      | 10          | uA    |

|               |                                    | Capacitive Load                  |                                                |      | 15          | pf    |

| DCI K/        | VIL                                | Input Low Voltage                |                                                |      | .8          | V     |

| BCLK/         | V <sub>IH</sub>                    | Input High Voltage               |                                                | 2    |             | V     |

| CCER          | IIL                                | Input Current at VII             | V <sub>1L</sub> = .4V                          |      | -2          | mA    |

|               | I <sub>IH</sub>                    | Input Current at VIH             | V <sub>IH</sub> =2.4V                          |      | 50          | uA    |

|               | *c                                 | Capacitive Load                  | '''                                            |      | 15          | pf    |

|               |                                    |                                  |                                                |      |             |       |

| BPRN/         | VIL                                | Input Low Voltage                |                                                |      | .8          | V     |

|               | V <sub>IH</sub>                    | Input High Voltage               |                                                | 2    |             | V     |

|               | I <sub>I</sub> L                   | Input Current at V <sub>IL</sub> | V <sub>IL</sub> = .4V                          |      | -3.2        | mA    |

|               | ЧН                                 | Input Current at V <sub>IH</sub> | V <sub>IH</sub> =2.4V                          |      | 80          | uA    |

|               | *C                                 | Capacitive Load                  |                                                |      | 15          | pf    |

| IORC/, IOWC/  | VIL                                | Input Low Voltage                |                                                |      | .8          | V     |

| INIT/         | V <sub>IH</sub>                    | Input High Voltage               |                                                | 2    | ]           | V     |

|               | 11L                                | Input Current at V <sub>IL</sub> | V <sub>1L</sub> = .4V                          | ļ    | -1.6        | mA    |

|               | ЧН                                 | Input Current at V <sub>IH</sub> | V <sub>IH</sub> =2.4V                          |      | 40          | uA    |

Table 2-8. Diskette Controller/Multibus DC Characteristics (Continued)

|               |                  | PARAMETER                        | TEST                        | PARAMETER |      |       |

|---------------|------------------|----------------------------------|-----------------------------|-----------|------|-------|

| SIGNAL        | SYMBOL           | DESCRIPTION                      | CONDITION                   | MIN       | MAX  | UNITS |

|               | *C               | Capacitive Load                  |                             |           | 15   | pf    |

| XACK/         | v <sub>OL</sub>  | Output Low Voltage               | I <sub>OL</sub> =16mA       |           | .4   | V     |

|               | V <sub>OH</sub>  | Output High Voltage              | I <sub>OH</sub> =-5.2mA     | 2.4       |      | V     |

|               | VIL              | Input Low Voltage                |                             |           | .8   | V     |

|               | VIH              | Input High Voltage               |                             | 2         |      | V     |

|               | I <sub>I</sub> L | Input Current at V <sub>IL</sub> | V <sub>IL</sub> = .4V       |           | -1.6 | mA    |

|               | ЧН               | Input Current at V <sub>IH</sub> | V <sub>IH</sub> =2.4V       |           | 40   | uA    |

|               | 'LL              | Input Leakage Low                | High Z V <sub>o</sub> =2.4  | V         | -40  | uA    |

|               | 'LH              | Input Leakage High               | High Z V <sub>0</sub> = .4\ | <b>/</b>  | 40   | uA    |

|               | *C               | Capacitive Load                  |                             |           | 15   | pf    |

| BPRO/         | v <sub>OL</sub>  | Output Low Voltage               | f <sub>OL</sub> =3.2mA      |           | .45  | V     |

|               | Voн              | Output High Voltage              | I <sub>OH</sub> =400uA      | 2.4       | 1    | V     |

| •             | *c               | Capacitive Load                  |                             |           | 15   | pf    |

| BREQ          | v <sub>OL</sub>  | Output Low Voltage               | I <sub>OL</sub> =20mA       |           | .45  | V     |

|               | v <sub>oh</sub>  | Output High Voltage              | I <sub>OH</sub> =400uA      | 2.4       |      | \ \   |

|               | *c               | Capacitive Load                  |                             |           | 15   | pf    |

| MRDC/, MWTC/  | VOL              | Output Low Voltage               | I <sub>OL</sub> =32mA       |           | .4   | V     |

|               | VOH              | Output High Voltage              | i <sub>OH</sub> =-2mA       | 2.4       |      | V     |

|               | *C               | Capacitive Load                  | On 2,                       |           | 15   | pf    |

| BUSY/         | v <sub>OL</sub>  | Output Low Voltage               | I <sub>OL</sub> =20mA       |           | 45   | v     |

|               | v <sub>OH</sub>  | Output High Voltage              | Open Collector              |           | İ    |       |

|               | *C               | Capacitive Load                  |                             |           | 15   | pf    |

| INT7/ — INTØ/ | VOL              | Output Low Voltage               | I <sub>OL</sub> =16mA       |           | .4   | V     |

|               | ГОН              | Output High Leakage              | Open Collector              |           |      |       |

|               |                  |                                  | Off                         |           | 250  | uA    |

|               | *c               | Capacitive Load                  | V <sub>OH</sub> =5.5V       |           | 15   | pf    |

|               |                  |                                  |                             |           |      |       |

Table 2-9. Diskette Controller/Drive Interface DC Characteristics

| CIONAL       | 0)/44001        | PARAMETER                        | TEST                      | P   | ARAME | TER    |

|--------------|-----------------|----------------------------------|---------------------------|-----|-------|--------|

| SIGNAL       | SYMBOL          | DESCRIPTION                      | CONDITION                 | MIN | MAX   | UNITS  |

| SELØ/, SEL1/ | V <sub>OL</sub> | Output Low Voltage               | I <sub>OL</sub> =48mA     |     | .4    | V      |

| SEL2/, SEL3/ | I <sub>ОН</sub> | Output High Leakage              | Open Collector            |     |       |        |

|              |                 | '                                | Off V <sub>OH</sub> =5.5V |     | 250   | uA     |

| WRT DAT/     | *C              | Capacitive Load                  |                           |     | 15    | pf     |

| WRT GT/      |                 |                                  |                           |     |       |        |

| STEP/        |                 |                                  |                           |     |       |        |

| DIR/         |                 |                                  |                           |     |       |        |

| WRT FLT      |                 |                                  |                           |     |       |        |

| RESET/       |                 |                                  |                           |     |       |        |

| TRACK GT     |                 |                                  |                           |     | ļ     |        |

| 43/          |                 |                                  |                           |     |       |        |

| READY Ø/     | VIL             | Input Low Voltage                |                           |     | .8    | V      |

| READY 1/     | VIH             | Input High Voltage               |                           | 3.0 |       | V      |

| SEP DATA/    | IL              | Input Current at V <sub>IL</sub> | V <sub>IL</sub> = .8      |     | -26   | mA (2) |

| SEP CLOCK/   | Iн              | Input Current at V <sub>IH</sub> | V <sub>IH</sub> =3.0      |     | 10    | mA (1) |

| TRACK Ø/     | *C              | Capacitive Load                  |                           |     | 15    | pf     |

| INDEX/       |                 |                                  |                           |     |       |        |

| WRT FLT/     |                 |                                  |                           |     |       |        |

| WPROT/       |                 |                                  |                           |     | ļ     |        |

| LEDØ/        | VOL             | Output Low Voltage               | I <sub>OL</sub> =16mA     |     | .4    | ٧      |

| LED1/        | Voн             | Output High Voltage              | I <sub>OH</sub> =400ua    | 2.4 | }     | ٧      |

|              | *C              | Capacitive Load                  |                           |     | 15    | pf     |

Includes 9.1mA due to 220/330 $\Omega$  pull-up/pull-down. Includes 25mA due to 220/330 $\Omega$  pull-up/pull-down.

<sup>\*</sup> Capacitance values are approximations.

Figure 2-2. Slave Command Timing

Figure 2-3. Bus Exchange Timing

Preparation for Use SBC 202

Figure 2-4. Master Command Timing

Figure 2-5. Step/Settling Timings

Figure 2-6. Read Timing

Figure 2-7. Write Timing

Figure 2-8. Index Timing

Figure 2-9. Write Fault Reset Timing

Preparation for Use SBC 202

## 2-9. SWITCH AND JUMPER CONFIGURATIONS

The following paragraphs provide instructions for configuring the I/O Base Address switch and the Interrupt Level Select switch. The memory base address, which is under program control, is described in paragraph 4-4.

#### 2-10. I/O BASE ADDRESS SELECTION

The user must assign a base address to the Diskette Channel. The base address is defined by the five most significant bits of the eight-bit I/O port address. The three least significant bits, then, can be used to differentiate between eight input or eight output channel commands. When the CPU accesses the Diskette Channel by executing an I/O instruction the base address (BASE) is used to select the Diskette Channel, while the three low-order address bits select one of the channel commands, as described in Chapter 3.

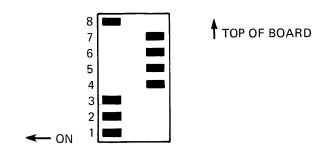

A base address is assigned by opening or closing the five most significant switch positions of the S1 switch (S1-4, 5, 6, 7, 8) on the Channel Board (see sheet 1 of the Channel Board schematic in Chapter 5). When a switch position is closed (on) (tied to ground) it represents the assignment of a logical 0 address bit. When a position is open (off) (+5V), it represents a logical 1 selection.

The following sketch represents a base address selection of 78<sub>16</sub>.

#### 2-11. INTERRUPT LEVEL SELECTION

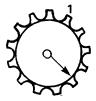

The user can assign the Diskette Channel's interrupt request line to any one of eight interrupt priority levels (INTO/-INT7/) by moving the interrupt level select switch (S1) on the Interface Board to the desired position. This eight position rotary switch is shown on sheet 3 of the Interface Board schematic in Chapter 5. The eight switch positions are associated with the following priority levels:

| SWITCH POSITION | INTERRUPT<br>PRIORITY LINE | RELATIVE PRIORITY<br>(INTELLEC MDS SYSTEM) |

|-----------------|----------------------------|--------------------------------------------|

| 1               | INTO/                      | HIGHEST                                    |

| 2               | INT1/                      |                                            |

| 3               | INT2/                      |                                            |

| 4               | INT3/                      |                                            |

| 5               | INT4/                      |                                            |

| 6               | INT5/                      |                                            |

| 7               | INT6/                      | ♥                                          |

| 8               | INT7/                      | LOWEST                                     |

The following sketch shows the switch settting 3 corresponding to priority line INT2/.

# \_int<sub>e</sub>L

# CHAPTER 3 PROGRAMMING INFORMATION

#### 3-1. INTRODUCTION

All operations must be initiated by the Central Processor Unit (CPU). Once initiated the controller completes the specified operation without further intervention on the part of the CPU. From the CPU's point of view, there are only three general steps required to complete any diskette operation.

- The CPU must prepare and store in system memory an I/O Parameter Block (IOPB) for each operation to be performed. An IOPB (seven bytes) specifies a particular diskette opertion and provides all of the parameters required for execution of that operation.

- The CPU must then pass the memory address of the IOPB to the Controller Channel.

- The CPU must process the result information from the Controller Channel upon completion of the operation(s).

The following paragraphs define the system operation.

The 7-byte parameter block (IDPB) must adapt the following format:

Byte 1 Channel Command

- 2 Diskette Instruction

- 3 Number of Records

- 4 Track Address

- 5 Sector Address

- 6 Buffer Address (Lower)

- 7 Buffer Address (Upper)

The preparation of the IOPB by the CPU, in itself, requires no interaction with the Controller Diskette Channel. The passing of the memory address for the IOPB and the result processing, however, do require interaction. Six channel commands have been defined to allow the CPU to perform these interactive steps. Three of the channel commands are the result of the CPU executing an output instruction to a dedicated I/O port address, while the other three commands are the result of input instructions to dedicated ports. The six channel commands are:

- (1) Write memory address lower (output)

- (2) Write memory address upper and start the diskette operation (output)

- (3) Reset the channel (output)

- (4) Read subsystem status (input)

- (5) Read result type (input)

- (6) Read result byte (input)

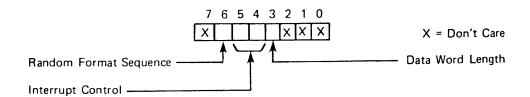

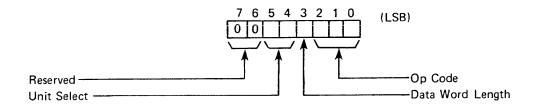

The channel command provides the Controller with information which:

- (1) Determines the method of assigning logical sector addresses.

- (2) Enables or disables a series of possible diskette interrupts.

- (3) Determines the length of the data word to be transferred.

The CPU outputs the memory address of the IOPB by executing channel commands 1 and 2. Upon execution of channel command 2, the Controller Channel will request master control of the Multibus, fetch the diskette instruction and associated parameters from the IOPB, and proceed to perform the specified diskette operation. The diskette instruction byte in the IOPB can specify any one of seven diskette operations:

- (1) Recalibrate (seek track 00)

- (2) Seek

- (3) Format a track

- (4) Write data (with data address marks)

- (5) Write data (with deleted address marks)

- (6) Read data

- (7) Verify CRC

The Controller Channel can interrupt the CPU when the operation is completed or when the diskette ready status changes. The host system software can implement its CPU interrupt mechanism via this direct interrupt feature or it can "poll" the Controller Channel by executing channel command 4 (read subsystem status). When the CPU determines that the operation sequence has been completed (either by receiving an interrupt request or by reading the interrupt status), the CPU should execute channel commands 5 and 6 (read result type and read result byte) to determine whether the diskette operations were successfully completed, and if not which type of error occurred.

Thus, in summary, we see that certain channel commands are executed by the CPU to point the Controller Channel to an IOPB in system memory, and initiate the operation sequence. The Controller Channel, then, accesses the IOPB to perform the diskette operation specified by the instruction byte of the IOPB. The Controller Channel will, if enabled by the IOPB, generate an I/O complete interrupt request upon completion of each diskette operation or detection of an error. The CPU, then, executes other channel commands to determine the result of the diskette operation.

Programming Information SBC 202

#### 3-2. CHANNEL COMMANDS

There are six channel commands to which the Controller Channel will respond. Three of the channel commands are issued when a CPU in the system executes output (I/O write) instructions with the appropriate eight-bit I/O addresses. The other three commands are issued when the CPU executes input (I/O read) instructions with the appropriate I/O addresses.

When the CPU executes one of the output channel commands, it activates the I/O write (IOWC/) line and duplicates the appropriate 8-bit I/O address on address lines ADR0/-ADR7/ and ADR8/- ADRF/ of the System bus. Depending on the particular channel command, the CPU may also place relevant data on data lines DAT0/-DAT7/ of the System bus. The CPU maintains the data lines until the Controller Channel returns the transfer acknowledge (XACK/) signal.

When the CPU executes one of the input channel commands, it activates the I/O read (IORC/) line and duplicates the appropriate I/O address on both halves of the System bus. The CPU expects the Controller Channel to activate the transfer knowledge (XACK/) line when it has placed the requested data on data lines DATO/-DAT7/.

The Controller Channel differentiates between the different channel commands by interrogating the I/O read (IOCR/) and I/O write (IOWC/) lines and the three least significant address lines (ADR0/ - ADR2/). The five most significant I/O address lines (ADR3/ - ADR7/) define the switch-selectable BASE address for the Controller Channel.

If the Controller Channel is not busy, it will respond to an output channel command within 3 microseconds. It is is busy, the "write MA lower" and "write MA upper" commands are ignored; no acknowledge is returned. (Note: Because no acknowledge is returned in this case, it could be possible to "hang up" the host system if the system does not include a Fail Safe time-out provision, as is provided on the Front Panel Control Module in the system). The "reset" command, however, is acknowledged even if the Controller Channel is busy. "Reset" is executed immediately (if issued during a data write operation, garbled data will be written).

The Diskette Controller responds to "read subsystem status" and "read result type" input channel commands within 1 microsecond. The information returned in response to a "read subsystem status" command is always valid. The eight bits of data returned in response to a "read result type" command, however, are only valid if the Controller Channel had previously issued an interrupt request to the CPU. The Controller Channel will, if not busy, respond to a "read result byte" input command within 3 microseconds. If the Controller Channel is busy, however, it ignores the "read result byte" command (i.e., no acknowledge is returned). The "read result type" and "read result byte" commands must be executed sequentially ("read result type" first), and should be executed only in response to an interrupt request from the Controller Channel; execution at other times could produce erroneous result data.

The use and format of each of the six channel commands is described below:

#### WRITE MEMORY ADDRESS LOWER (OUTPUT)

This channel command outputs the low order byte of the 16-bit memory address that points to byte 1 ("channel word") of the IOPB.

System address bus: BASE + 1

System data bus: Eight least significant bits of the 16-

bit memory address that points to

the first IOPB.

### WRITE MEMORY ADDRESS UPPER AND START THE DISKETTE OPERATION (OUTPUT)

This channel command outputs the high order byte of the 16-bit memory address that points to byte 1 of the IOPB. This command also causes the Controller Channel to begin executing the diskette operation specified in byte 2 (instruction byte) of the addressed IOPB.

System address bus BASE + 2

System data bus: Eight most significant bits of the 16-

bit memory address

#### RESET DISKETTE SYSTEM (OUTPUT)

This output channel command causes all control logic in the Controller Channel to be reset in an initialized state. If this command is issued while a "write data" diskette operation is in progress, the data in the sector currently being written will be garbled. This command is intended to clear a "hang up" in the Controller Channel.

System address bus: BASE + 7

System data bus: Not used.

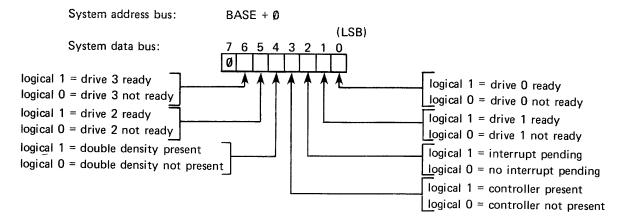

#### READ SUBSYSTEM STATUS (INPUT)

This input channel command causes the Controller Channel to return.

bit 0 — ready status of drive 0

bit 1 — ready status of drive 1

bit 2 - state of the channel's interrupt flip-flop

bit 3 — controller presence indicator

bit 4 — double density controller presence indicator

bit 5 — ready status of drive 2

bit 6 — ready status of drive 3

These indications allow the operating system to monitor the operation of the Controller Channel.

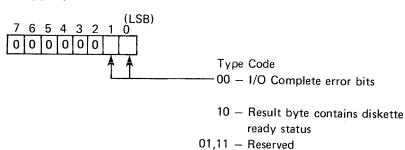

#### **READ RESULT TYPE (INPUT)**

This input channel command causes the Controller Channel to return eight bits of information to the CPU. The two least sig-

nificant bits specify one of four different types of result byte (see next paragraph) associated with diskette operations.

System address bus:

BASE + 1

System data bus:

#### **READ RESULT BYTE (INPUT)**

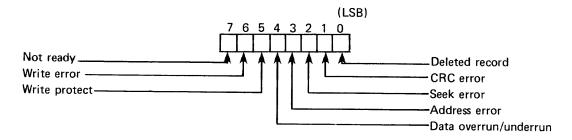

This input channel command causes the Controller Channel to return eight bits of information to the CPU. The interpretation of these bits is dependent upon the type code returned in the result type word (see previous paragraph). The "read result byte" channel command should only be executed after a "read result type" command has been executed.

System address bus:

BASE + 3

System data bus:

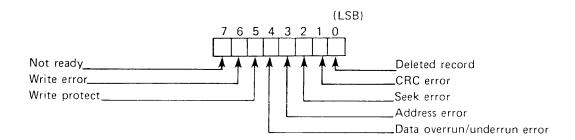

If the type code in the result type word = 00, the result byte, input on the data bus, will contain error bits (see Paragraph 3-5 for error explanations) and will be formatted as follows:

Programming Information SBC 202

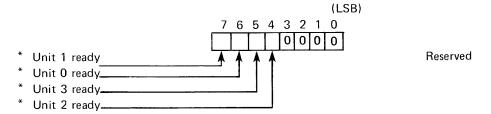

If the type code = 10, the controller has detected a change in the ready status of a drive and the contents of the result byte will indicate the current ready status of the diskette drives: