# intel<sup>®</sup> OEM COMPUTERS

## SBC 80/10 SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

## SBC-80/10

## HARDWARE REFERENCE MANUAL

Copyright © 1976

Intel Corporation

3065 Bowers Avenue

Santa Clara, California 95050

#### SBC-80/10

#### HARDWARE REFERENCE MANUAL

Copyright © 1976 by Intel Corporation. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Intel Corporation.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

#### TABLE OF CONTENTS

| Chapter |       |                             |           |     |     | P | age No       |

|---------|-------|-----------------------------|-----------|-----|-----|---|--------------|

| 1       | INTRO | DUCTION                     |           | •   |     |   | 1-1          |

| 2       | FUNC  | IONAL DESCRIPTION           |           |     |     | • | 2-1          |

| 3       | THEO  | Y OF OPERATION              |           |     |     | • | 3-1          |

|         | 3.1   | CPU SET                     |           |     |     |   | 3-1          |

|         |       | 3.1.1 INSTRUCTION TIMING    |           |     |     |   | 3-3          |

|         |       | 3.1.2 INTERRUPT SEQUENCES   | s         |     |     | • | 3-12         |

|         |       | 3.1.3 HOLD SEQUENCES        |           |     |     |   | 3-13         |

|         |       | 3.1.4 HALT SEQUENCES        |           |     |     |   |              |

|         |       | 3.1.5 START-UP SEQUENCE     |           |     |     |   |              |

|         | 3.2   | SYSTEM BUS INTERFACE LOGI   |           |     |     |   |              |

|         |       | 3.2.1 SYSTEM CONTROL SIG    |           |     |     |   |              |

|         |       | 3.2.2 SYSTEM BUS DRIVERS    |           |     |     |   |              |

|         |       | 3.2.3 FAILSAFE TIMER        |           |     |     | • | 3-20         |

|         | 3.3   | RANDOM ACCESS MEMORY (RAM   |           |     |     |   |              |

|         |       | READ ONLY MEMORY (ROM/PRO   |           |     |     |   |              |

|         |       | SERIAL I/O INTERFACE        |           |     |     |   |              |

|         |       | 3.5.1 INTEL® 8251 OPERAT    |           |     |     |   |              |

|         |       | 3.5.2 SERIAL I/O CONFIGU    |           |     |     |   |              |

|         |       | 3.5.3 BAUD RATE CLOCK GE    |           |     |     |   |              |

|         |       | 3.5.4 SERIAL I/O INTERRU    |           |     |     |   |              |

|         | 3.6   | PARALLEL I/O INTERFACE .    |           |     |     |   |              |

|         | 0.0   | 3.6.1 INTEL® 8255 OPERATION | ONAL SUMM | ARY |     |   | 3-43         |

|         |       | 3.6.2 PARALLEL I/O CONFI    |           |     |     |   |              |

| 4       | USER  | SELECTABLE OPTIONS          |           |     |     |   | 4-1          |

|         | 4.1   | SERIAL I/O INTERFACE OPTI   | ONS       |     |     |   | 4-2          |

|         | 4.1   | 4.1.1 INTERFACE TYPE .      |           |     |     |   | 4-2          |

|         |       | 4.1.2 BAUD RATE AND PROG    |           |     |     | • |              |

|         |       | SERIAL I/O OPTIONS          |           |     |     |   | 4 2          |

|         | 1 2   | PARALLEL I/O OPTIONS        |           |     |     |   | 4-8          |

|         | 4.4   | 4.2.1 PORT 1 (GROUP 1 PO    |           |     |     |   | 4-8<br>4-9   |

|         |       | 4.2.2 PORT 2 (GROUP 1 PO    | KIA) · ·  | •   | • • | • | 4-9<br>4-14  |

|         |       |                             |           |     |     |   |              |

|         |       | 4.2.3 PORT 3 (GROUP 1 PO    |           |     |     |   | 4-16<br>4-17 |

|         |       | 4.2.4 PORTS 4 AND 5 (GRO    |           |     |     |   |              |

|         | 4.0   | 4.2.5 PORT 6 (GROUP 2 PO    |           |     |     |   | 4-20         |

|         | 4.3   |                             | · · · · · |     |     |   | 4-24         |

|         |       | 4.3.1 SYSTEM RESET OUTPU    |           |     |     | - | 4-24         |

|         |       | 4.3.2 DISABLE BUS CLOCK     | SIGNALS   |     |     |   | 4-24<br>4-24 |

|         |       |                             |           |     |     |   | 4-24<br>4-28 |

|         | , ,   | 4.3.4 INTERRUPT SOURCES     |           | • • | • • | • | 4-28         |

|         | 4 4   | DEFAULT OPTIONS             |           |     |     |   | 4-20         |

## TABLE OF CONTENTS (Continued)

| Chapter |        |                                      |     |       | P | age No |

|---------|--------|--------------------------------------|-----|-------|---|--------|

| 5       | SYST   | EM INTERFACING                       | •   | <br>• |   | 5-1    |

|         | 5.1    | ELECTRICAL CONNECTIONS               | • • |       |   | 5-1    |

|         | 5.2    | EXTERNAL SBC 80/10 SYSTEM BUS SUMMAR | Υ.  |       | • | 5-7    |

|         |        | RS232C CABLING                       |     |       |   |        |

|         | 5.4    | TELETYPE MODIFICATIONS               | •   | <br>• | • | 5-13   |

| 6       | COMP   | ATIBLE EQUIPMENT                     |     | <br>• | • | 6-1    |

|         | 6.1    | SBC-104 COMBINATION MEMORY AND I/O   |     |       |   |        |

|         | EXPA   | NSION BOARD                          | • ( |       |   | 6-1    |

|         |        | MASTER MODULES                       |     |       |   |        |

|         | 6.3    | SBC-016 16K RAM MODULE               |     |       | • | 6-2    |

|         |        | SBC-406 6K PROM MODULE               |     |       |   |        |

|         | 6.5    | SBC-416 16K PROM MODULE              |     |       |   | 6-4    |

|         | 6.6    | SBC-508 GENERAL PURPOSE I/O MODULE   |     |       |   | 6-5    |

|         | 6.7    | MODULAR BACKPLANE AND CARDCAGE       |     |       |   | 6-5    |

|         |        | INTELLEC® MDS CARDCAGE               |     |       |   |        |

| 7       | SBC-   | 30/10 SPECIFICATIONS                 |     | <br>• | • | 7-1    |

|         | 7.1    | POWER REQUIREMENTS                   |     |       |   | 7-1    |

|         | 7.2    | DC CHARACTERISTICS                   |     |       |   | 7-1    |

|         | 7.3    | AC CHARACTERISTICS                   |     |       |   | 7-1    |

|         | 7.4    | ENVIRONMENTAL LIMITATIONS            |     | <br>• |   | 7-1    |

|         | 7.5    | PHYSICAL CHARACTERISTICS             |     |       |   | 7-1    |

|         | 7.6    | SBC 80/10 COMPATIBLE CONNECTORS      |     |       | • | 7-1    |

| APPENI  | OIX A. | SBC-80/10 SCHEMATICS                 |     |       | • | A-1    |

| APPENI  | OIX B. | 8080 INSTRUCTION SET SUMMARY         |     | <br>• | • | B-1    |

| ΔΡΡΕΝΙ  | OTX C. | SBC-901 SBC-902 SCHEMATICS           |     |       |   | C-1    |

## LIST OF FIGURES

| Figure       |                                     | Page |

|--------------|-------------------------------------|------|

| 2-1          | SBC-80/10 FUNCTIONAL BLOCK DIAGRAM  | 2-2  |

| 3-0          | THE CPU SET                         |      |

| 3-1          | TYPICAL FETCH MACHINE CYCLE         | 3-6  |

| 3-2          | INPUT INSTRUCTION CYCLE             |      |

| 3-3          | OUTPUT INSTRUCTION CYCLE            | 3-10 |

| 3-4          | READY TIMING                        | 3-19 |

| 3-5          | RAM ACCESS TIMING                   | 3-24 |

| 3-6          | 8251 PIN ASSIGNMENTS                |      |

| 3-7          | TYPICAL 8251 DATA BLOCK             | 3-31 |

| 3-8          | ASYNCHRONOUS MODE                   | 3-33 |

| 3-9          | SYNCHRONOUS MODE                    |      |

| 3-10         | COMMAND INSTRUCTION FORMAT          | 3-34 |

| 3-11         | STATUS READ FORMAT                  | 3-35 |

| 3-12         | 8255 PIN ASSIGNMENTS                |      |

| 3-13         | MODE DEFINITION CONTROL WORD FORMAT |      |

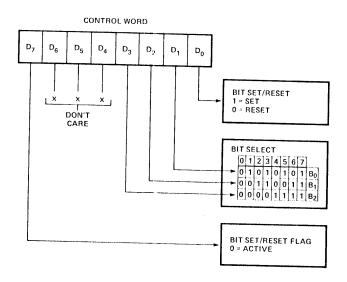

| 3-14         | BIT SET/RESET CONTROL WORD FORMAT   | 3-47 |

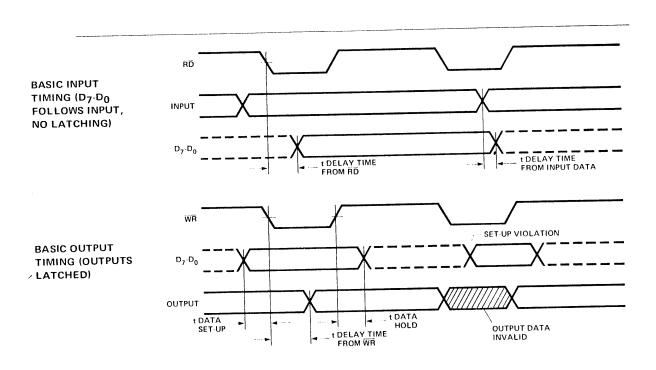

| 3-15         | 8255 MODE 0 TIMING                  | 3-48 |

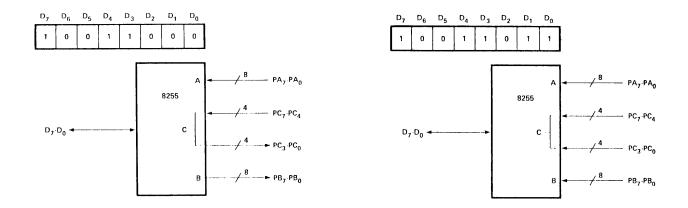

| 3-16         | EXAMPLES OF MODE 0 CONFIGURATION    | 3-48 |

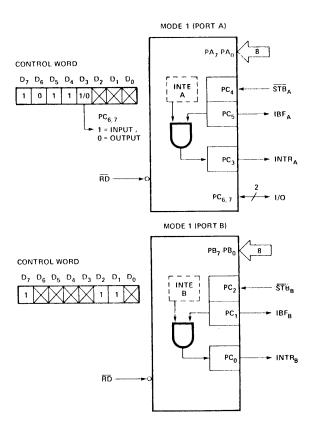

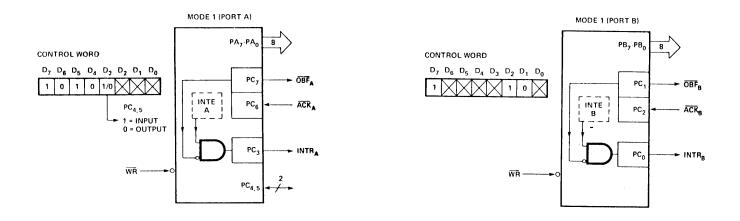

| 3-17         | MODE 1 INPUT CONFIGURATION          | 3-51 |

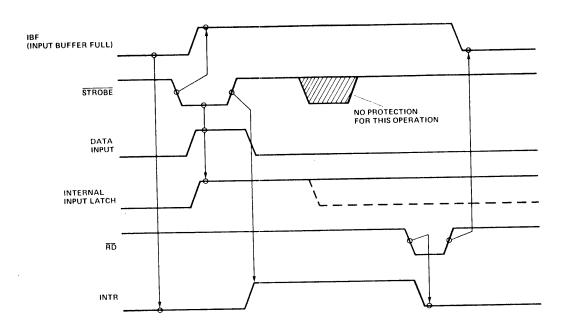

| 3-18         | 8255 MODE 1 INPUT TIMING            | 3-51 |

| 3-19         | MODE 1 OUTPUT CONFIGURATION         | 3-52 |

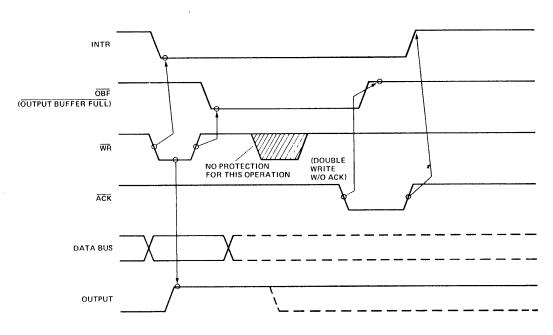

| 3-20         | MODE 1 BASIC OUTPUT TIMING          | 3-52 |

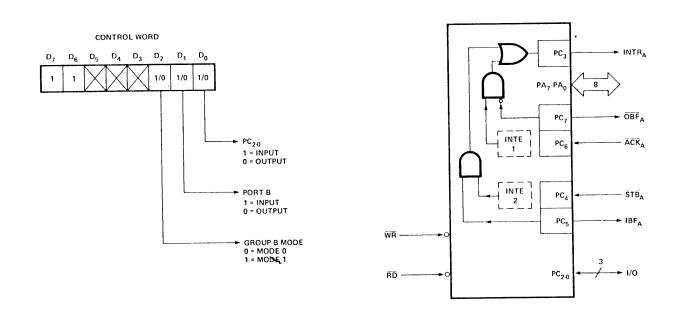

| 3-21         | MODE 2 PORT CONFIGURATION           | 3-54 |

| 3-22         | MODE 2 TIMING                       | 3-55 |

| 4-1          | ASYNCHRONOUS OPERATION              | 4-6  |

| 4-2          | SYNCHRONOUS OPERATION               | 4-7  |

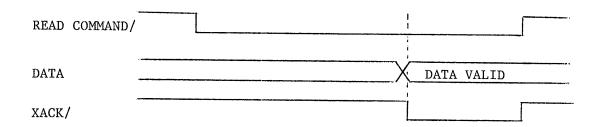

| 4-3          | READ COMMAND WITH XACK/             | 4-25 |

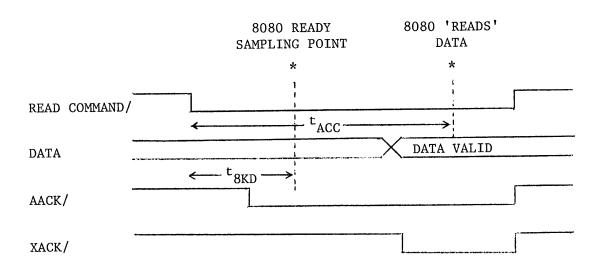

| 4-4          | READ COMMAND WITH AACK/             | 4-26 |

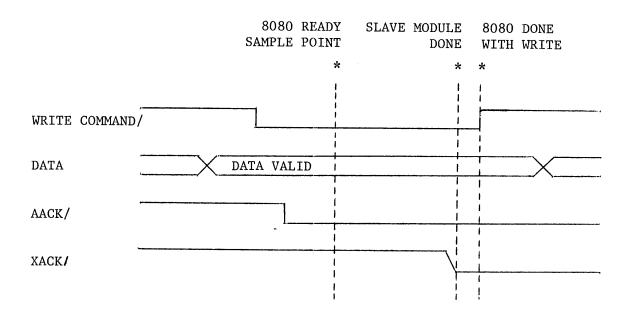

| 4-5          | WRITE COMMAND WITH AACK/            | 4-27 |

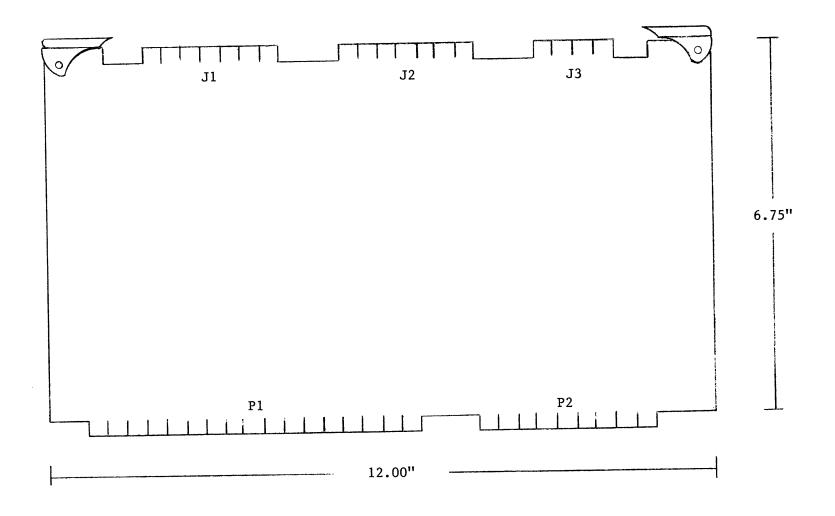

| 5-1          | SBC-80/10 EDGE CONNECTORS           | 5-4  |

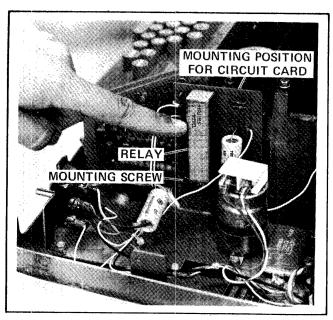

| 5-3          | RELAY CIRCUIT (ALTERNATE)           | 5-15 |

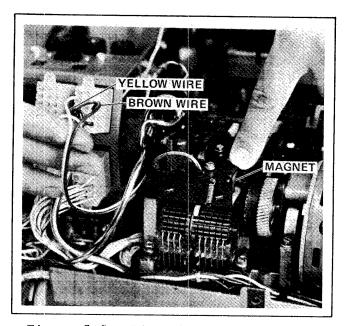

| 5-4          | DISTRIBUTOR TRIP MAGNET             | 5-15 |

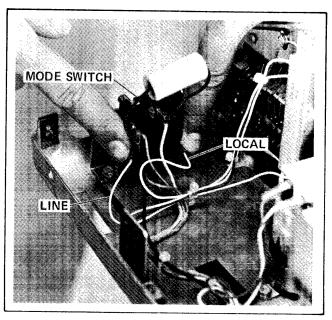

| 5-5          | MODE SWITCH                         | 5-15 |

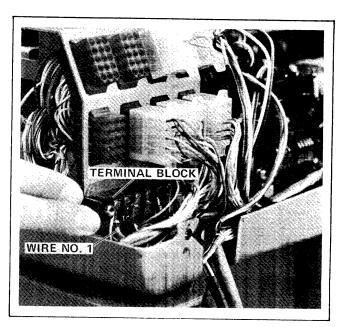

| 5-6          | TERMINAL BLOCK                      |      |

| 5 <b>-</b> 7 | CURRENT SOURCE RESISTOR             |      |

| 5-8          | TELETYPE LAYOUT                     | 5-16 |

| 5-9          | TELETYPE MODIFICATION               | 5-17 |

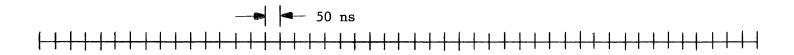

| 7 <b>-</b> 3 | BUS EXCHANGE (WRITE)                | 7-10 |

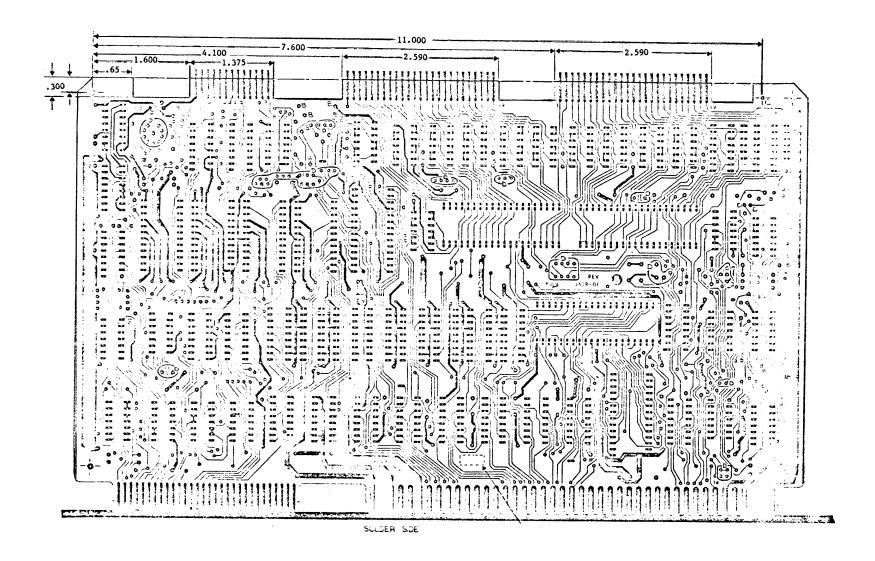

| 7-4          | SBC 80/10 DIMENSION DRAWING         |      |

## LIST OF TABLES

| Number       |                                                    | Page       |

|--------------|----------------------------------------------------|------------|

| 3-0          | SERIAL COMMUNICATION (3251) ADDRESS ASSIGNMENTS    | 3-39       |

| 3-1          | 8255 MODE DEFINITION SUMMARY                       | 3-56       |

| 3-2          | 8255 BASIC OPERATION                               | 3-58       |

| 3-3          | PARALLEL I/O PORT ADDRESSES                        | 3-58       |

| 3-4          | GROUP 2 PORT C I/O CONFIGURATIONS                  | 3-63       |

| 4-1          | 20 mA CURRENT LOOP SERIAL I/O INTERFACE            | 4-3        |

| 4-2a         | RS232C INTERFACE, "DATA SET" ROLE                  | 4-4        |

| 4-2b         | RS232C INTERFACE, "DATA PROCESSING TERMINAL" ROLE  | 4-4        |

| 4-3          |                                                    |            |

| 4-4          | PORT 1, MODE 0 INPUT CONFIGURATION                 | 4-10       |

| 4-5          | PORT 1, MODE O LATCHED OUTPUT CONFIGURATION        | 4-10       |

| 4-6          | PORT 1, MODE 1 STROBED INPUT CONFIGURATION         | 4-11       |

| 4-7          | PORT 1, MODE 1 LATCHED OUTPUT CONFIGURATION        | 4-12       |

| 4-8          | PORT 1, MODE 2 BI-DIRECTIONAL CONFIGURATION        |            |

| 4-9          | · · · · · · · · · · · · · · · · · · ·              |            |

| 4-10         |                                                    |            |

| 4-11         | PORT 2, MODE 1 STROBED INPUT CONFIGURATION         |            |

| 4-12         | PORT 2, MODE 1 LATCHED OUTPUT CONFIGURATION        |            |

| 4-13         |                                                    |            |

| 4-14         |                                                    |            |

| 4-15         | PORT 4, MODE 0, INPUT CONFIGURATION                |            |

| 4-16         | PORT 4, MODE O LATCHED OUTPUT CONFIGURATION        |            |

| 4-17         | PORT 5, MODE O INPUT CONFIGURATION                 |            |

| 4-18         | PORT 5, MODE O LATCHED OUTPUT CONFIGURATION        |            |

| 4-19         | PORT 6, MODE 0, 8-BIT INPUT CONFIGURATION          |            |

| 4-20         | PORT 6, MODE 0, 8-BIT LATCHED OUTPUT CONFIGURATION |            |

| 4-21         | PORT 6, MODE O UPPER 4-BIT INPUT/LOWER 4-BIT       | ,          |

| 7 2+         | LATCHED OUTPUT CONFIGURATION                       | 4-22       |

| 4-22         |                                                    | 7 22       |

| -T 4 4       | 4-BIT INPUT CONFIGURATION                          | 4-22       |

| 4-23         |                                                    |            |

| 4-24         | DEFAULT OPTION ON THE SBC 80/10                    |            |

| 5-1          |                                                    |            |

| 5-2          |                                                    |            |

|              | PIN ASSIGNMENTS FOR CONNECTOR J3                   |            |

| 5 <b>-</b> 4 | PIN ASSIGNMENTS FOR CONNECTOR P2                   |            |

| 5-5          | PIN ASSIGNMENTS FOR CONNECTOR P1                   | 5-10       |

| 5-6          | J3/RS232C CONNECTOR PIN CORRESPONDENCE             | 5-12       |

| 6-1          | SBC 80/10 INTER-MODULE ACCESS CHARACTERISTICS      | 6-3        |

| 7-1          | DC POWER REQUIREMENTS                              | 7-2        |

| 7-1<br>7-2   | SBC 80/10 AC CHARACTERISTICS                       | 7-2<br>7-3 |

| 7-2<br>7-3   | SBC 80/10 AC CHARACTERISTICS                       | 7-3<br>7-4 |

| 7-3<br>7-4   | SBC 80/10 DC CHARACTERISTICS                       | 7-4<br>7-5 |

| 7-4<br>7-5   | SBC 80/10 COMPATIBLE CONNECTOR HARDWARE            | 7-7        |

| , – ,        | SEC COLIC CONTAILED COMMECTOR HARDWARE             | ,-,        |

#### CHAPTER 1

#### INTRODUCTION

The SBC-80/10 is a member of Intel's complete line of OEM computer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer based solutions for OEM applications. The SBC-80/10 is a complete computer system on a single 6.75-by-12 inch printed circuit card. The CPU, system clock, read/write memory, non-volatile read-only-memory, I/O ports and drivers, serial communications interface, bus control logic and drivers all reside on the board.

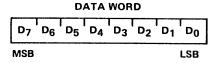

Intel's powerful 8-bit n-channel MOS 8080A CPU, fabricated on a single LSI chip, is the central processor for the SBC-80/10. The 8080A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs providing both single and double precision operators. The 8080A has a 16-bit program counter which allows direct addressing of up to 64K bytes of memory. An external stack, located within any portion of memory, may be used as a last in/first out stack to store and retrieve the contents of the program counter, flags, accumulator and all of the six general purpose registers. A sixteen bit stack pointer controls the addressing of this external stack. This stack provides almost unlimited subroutine nesting. Sixteen-line address and eightline bi-directional data busses are used to facilitate easy interface to memory and I/O.

The powerful 8080A instruction set allows the user to write

efficient programs in a minimum amount of time. The accumulator group instructions include arithmetic and logical operators with direct, register indirect, and immediate addressing modes. Move, load, and store instruction groups provide the ability to move either 8 or 16 bits of data between memory, the six working registers and the accumulator using all addressing modes. The ability to branch to different portions of a program is provided with jump, jump conditional, and computed jumps. The ability to conditionally and unconditionally call to and return from subroutines is provided. The RESTART (or single byte call instruction) is used for interrupt operation. Double precision operators such as stack manipulation and double add instructions extend both the arithmetic and interrupt handling capability of the 8080A. The ability to increment and decrement memory, the six general registers and the accumulator is provided as well as extended increment and decrement instructions to operate on the register pairs and stack pointer.

The SBC-80/10 contains 1K 8-bit words of read/write memory using Intel's 8111 low power static RAMs. Sockets for up to 4K 8-bit words of non-volatile read-only memory are provided on the board. Read-only memory may be added in 1K byte increments by using Intel's 8708 erasable and electrically reprogrammable ROMs (EPROMs) or Intel® 8308 metal mask ROMs. The 8080A performs read and write operations at maximum speed when accessing all on-board memory.

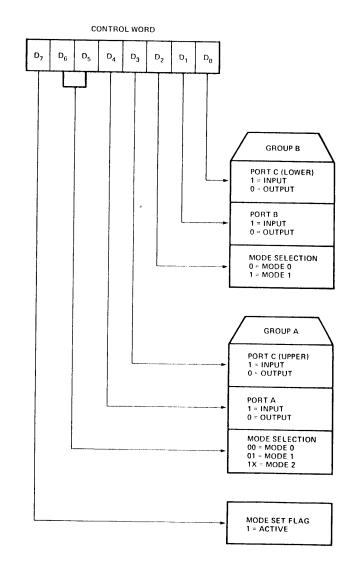

The SBC-80/10 contains 48 programmable parallel I/O lines implemented using two Intel® 8255 Programmable Peripheral Interface devices.

The software is used to configure the I/O lines in combinations of unidirectional input/output, and bidirectional ports. Therefore, the I/O interface may be customized to meet specified peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate optional line drivers and terminators for each application.

A programmable serial communications interface using Intel's 8251 Universal Synchronous/Asynchronous Receiver/Transmitter (USART) is contained on the board. The USART can be programmed by the systems software to provide virtually any serial data transmission technique presently in use (including IBM Bi-Sync). The mode of operation (i.e., synchronous or asynchronous), data format, control character format, parity, and asynchronous serial transmission rate (within limitations given later) are all under program control. The 8251 provides full duplex, double buffered transmission and receive capability. Parity, overrun, and framing error detection are all incorporated in the USART. The inclusion of jumper selectable teletype, or RS232C compatible interfaces on the board in conjunction with the USART provide a direct interface to a teletype, CRT, RS232C compatible devices, and asynchronous and synchronous modems.

A single-level interrupt may originate from any one of six sources including the USART, Programmable I/O interface, and two user designated interrupt request lines. When an interrupt request is recognized, a RESTART 7 instruction is generated. The processor responds by suspending program execution and executing a user defined interrupt service

routine originating at location 38<sub>16</sub>.

Memory and I/O expansion may be achieved using standard Intel boards. Memory may be expanded to 65,536 bytes by adding user specified combinations of SBC-016 16K byte RAM board, SBC-406 6K byte and SBC-416 16K byte PROM boards. Input/output capacity may be expanded in increments of 4 input ports and 4 output ports using SBC-508 Input/Output boards. Expandable backplanes and cardcages are available to support multi-board systems.

The development cycle of SBC-80/10 based OEM products may be significantly reduced using the Intellec MDS<sup>T.M</sup>Microcomputer Development System. The resident assembler, text editor, and system monitor greatly simplify the design, development, and debug of SBC-80/10 based system software. A unique In-Circuit Emulator (ICE-80) MDS option provides the capability of executing and debugging OEM system software directly on the SBC-80/10.

Intel's high-level language, PL/M, can be used to significantly decrease the time required to develop OEM system software.

#### CHAPTER 2

#### FUNCTIONAL DESCRIPTION

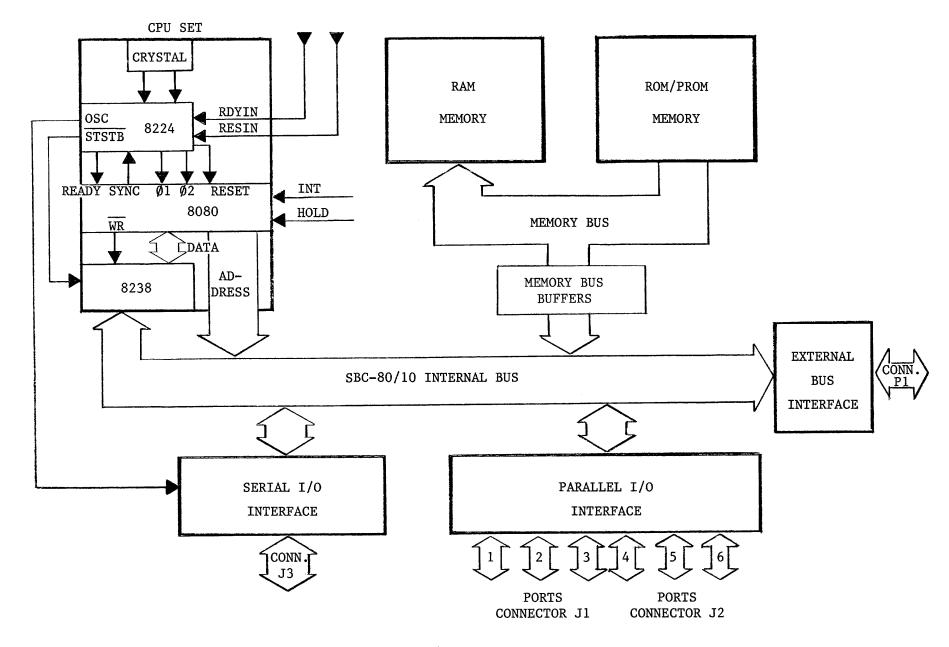

For descriptive purposes, the circuitry on the SBC-80/10 can be divided into six functional blocks:

- 1) CPU Set

- 2) System Bus Interface

- 3) Random Access Memory (RAM)

- 4) Read Only Memory (ROM/PROM) Logic

- 5) Serial I/O Interface

- 6) Parallel I/O Interface

as shown in Figure 2-1.

The <u>CPU Set</u> consists of the 8080A Control Processor, the 8224 Clock Generator and the 8238 System Controller. The CPU Set is the heart of the SBC-80/10. It performs all system processing functions and provides a stable timing reference for all other circuitry in the system. The CPU Set generates all of the address and control signals necessary to access memory and I/O ports both on the SBC-80/10 and external to the SBC-80/10. The CPU Set is capable of fetching and executing any of the 8080's seventy-eight instructions. The CPU Set responds to interrupt requests originating both on and off the SBC-80/10, to HOLD requests from modules wishing to acquire control of the system bus, and to WAIT requests from memory or I/O devices having an access time which is slower than the 8080's cycle time.

The <u>System Bus Interface</u> includes an assortment of circuitry which gates interrupt requests, HOLD requests, READY (no wait inputs and the system reset input to the appropriate pins of the CPU Set. Other circuits drive the various external system control signals. The

FIGURE 2-1. SBC-80/10 FUNCTIONAL BLOCK DIAGRAM

System Bus Interface also includes two 8216 bi-directional bus drivers which drive the memory data bus on the SBC-80/10. Six 8226 devices drive the external system data and address busses.

The Random Access Memory (RAM) section provides the SBC-80/10 user with  $1024 \times 8$ -bits of on-board read/write storage. Eight Intel® 8111 Static MOS RAM chips ( $256 \times 4$ -bits each) are mounted on the SBC-80/10, along with all of the necessary acknowledgment and memory address decoding logic.

The Read Only Memory (ROM/PROM) section provides the user with the necessary provisions for installing  $4096 \times 8$ -bits of ROM or PROM. The SBC-80/10 has four 24-pin sockets that can accept either Intel's 8708 Erasable and Electrically Programmable Read Only Memory chips (1024  $\times$  8-bits each) or Intel's 8308 Static MOS Read Only Memory chips (also  $1024 \times 8$ -bits each). The ROM/PROM logic also includes the necessary acknowledgment and memory address decoding circuitry.

The <u>Serial I/O Interface</u>, using Intel's 8251 USART device, provides a bi-directional serial data communications channel that can be programmed to operate with most of the current serial data transmission protocols. Synchronous or asynchronous mode, baud rate, character length, number of stop bits and the choice of even, odd or no parity are all program selectable. The user also has the option of configuring the Serial I/O Interface as an EIA RS232 interface or as a Teletype-compatible current loop interface.

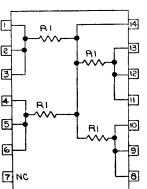

The <u>Parallel I/O Interface</u>, using two Intel® 8255 Programmable Peripheral interface devices, provides 48 signal lines for the transfer and

control of data to or from peripheral devices. Eight lines already have a bidirectional driver and termination network permanently installed. This bidirectional network allows these eight lines to be inputs, outputs, or bidirectional (selected via jumpers). The remaining 40 lines, however, are uncommitted. Sockets are provided for the installation of drivers or termination networks as required to meet the specific needs of the user system.

#### CHAPTER 3

#### THEORY OF OPERATION

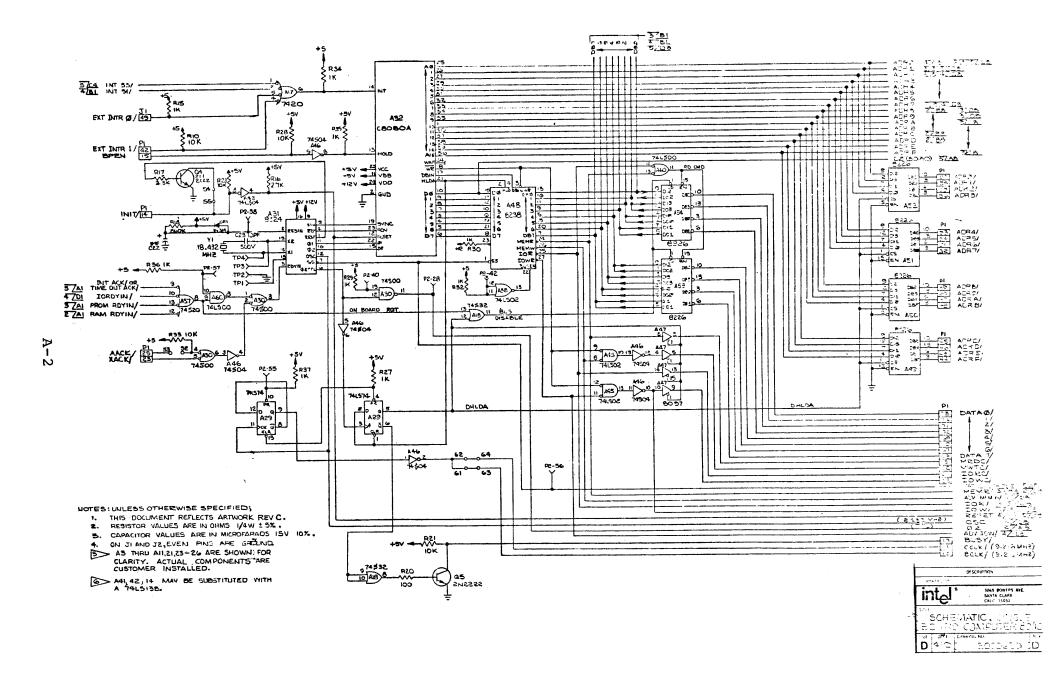

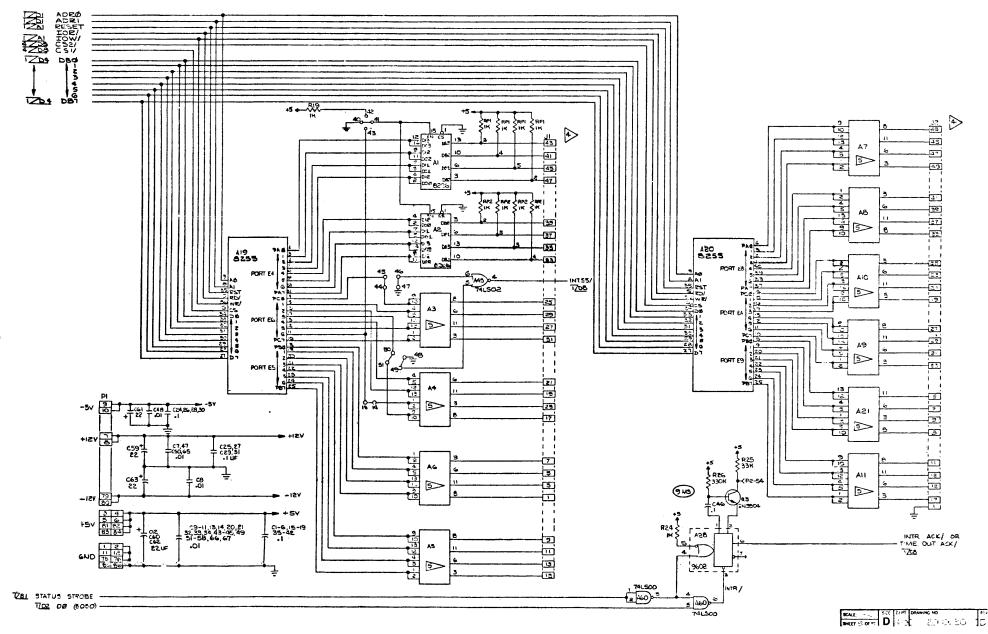

In the preceding chapter we introduced each of the SBC-80/10 functional blocks and defined what each block was capable of doing. In this chapter we shall go one step further and describe how each block performs its particular function(s). The text will constantly refer to the SBC-80/10 schematics, provided in Appendix A.

Note: Both active-high (positive true) and active-low (negative true) signals appear on the SBC-80/10 schematics. To eliminate any confusion when reading this chapter, the following convention will be adhered to: whenever a signal is active-low, its mnemonic is followed by a slash; for example, MRDC/ means that the level on that line will be low when the memory read command is true (active). If the signal is subsequently inverted, thus making it active-high, the slash is omitted; for example, MRDC means that the level on that line will be high when the memory read command is true.

#### 3.1 THE CPU SET

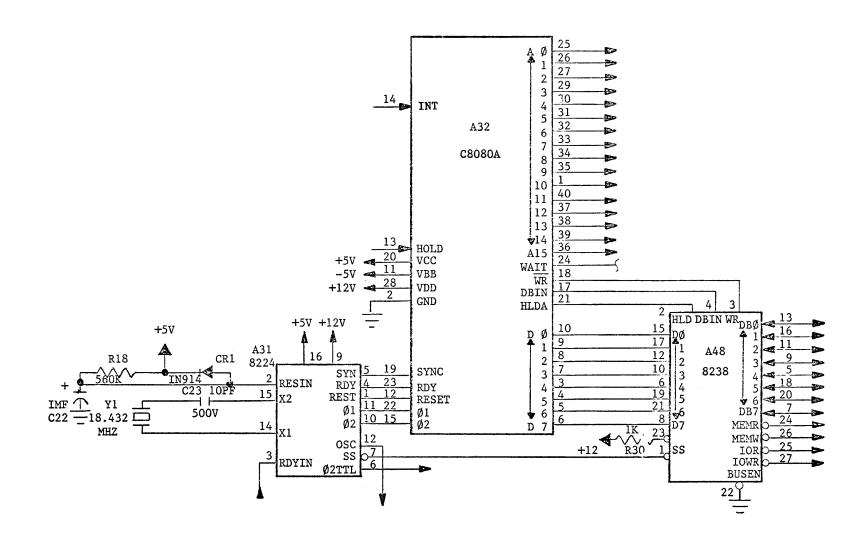

The CPU Set consists of three Intel® integrated circuit devices:

- \* 8080A Central Processor Unit

- \* 8224 Clock Generator

- \* 8238 System Controller

and an 18.432 MHz crystal that establishes the frequency of oscillation for the 8224 device via a 10pF capacitor, as shown in Figure 3-0. Together, the elements in the CPU Set perform all central processing functions. The following paragraphs describe how the elements within the CPU Set interact with all other logic on the SBC-80/10. The interaction between the IC's within the CPU Set, however, is not described. Instead, the reader is referred to the Intel® "8080 Microcomputer Systems User's Manual" for a detailed description of the 8080, 8224 and 8238 devices.

FIGURE 3-0. THE CPU SET

The CPU Set is shown on sheet 1 of the SBC-80/10 schematic (Appendix A).

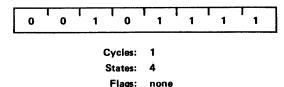

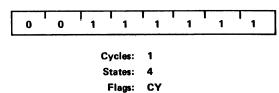

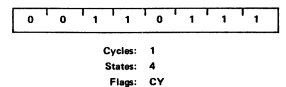

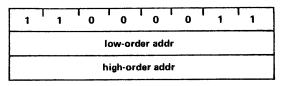

#### 3.1.1 INSTRUCTION TIMING

The activities of the CPU Set are cyclical. The CPU fetches an instruction, performs the operations required, fetches the next instruction, and so on. This orderly sequence of events requires precise timing. The 8224 Clock Generator, provides the primary timing reference for the CPU Set. The crystal in conjunction with a 10pF capacitor tunes an oscillator within the 8224 to precisely 18.432 MHz. The 8224 "divides" the oscillations by nine to produce two-phase timing inputs ( $\phi$ 1 and  $\phi$ 2) for the 8080. The  $\phi$ 1 and  $\phi$ 2 signals define a cycle of approximately 488 ns. duration. A TTL level phase 2 ( $\phi$ 2TTL) signal is also derived and made available to external logic. In addition, the output of the oscillator is buffered and brought out on OSC so that other system timing signals can be derived from this stable, crystal controlled source (e.g., the serial I/O baud rate is derived from OSC). All processing activities of the CPU Set are referred to the period of the  $\phi$ 1 and  $\phi$ 2 clock signals.

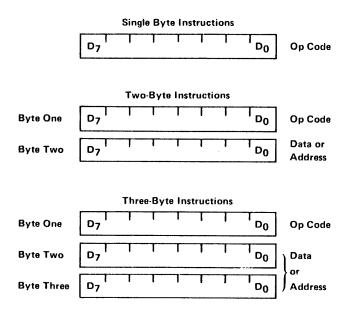

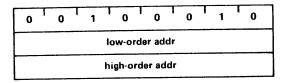

Within the 8080 CPU Set, an <u>instruction cycle</u> is defined as the time required to fetch and execute an instruction. During the fetch, a selected instruction (one, two or three bytes) is extracted from memory and deposited in the CPU's operating registers. During the execution part, the instruction is decoded and translated into specific processing activities.

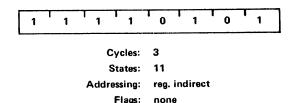

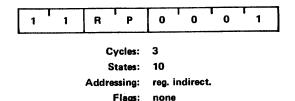

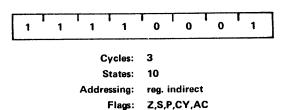

Every instruction cycle consists of one, two, three, four or five machine cycles. A machine cycle is required each time the CPU accesses

memory or an I/O port. The fetch portion of an instruction cycle requires one machine cycle for each byte to be fetched. The duration of the execution portion of the instruction cycle depends on the kind of instruction that has been fetched. Some instructions do not require any machine cycles other than those necessary to fetch the instruction; other instructions, however, require additional machine cycles to write or read data to/from memory or I/O devices.

Each machine cycle consists of three, four or five states. A

state is the smallest unit or processing activity and is defined as

the interval between two successive positive-going transitions of the

\$\psi\$1 clock pulse.

There are three exceptions to the defined duration of a state.

They are the WAIT state, the hold (HLDA) state and the halt (HLTA)

state. Because the WAIT, the HLDA, and the HLTA states depend upon external events, they are by their nature of indeterminate length.

Even these exceptional states, however, must be synchronized with the pulses of the driving clock. Thus the duration of all states, including these, are integral multiples of the clock pulse.

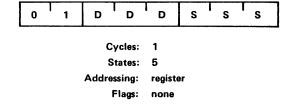

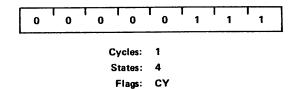

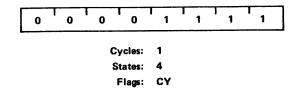

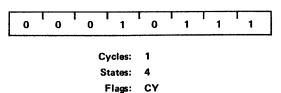

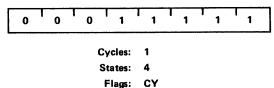

To summarize, then, each <u>clock period</u> marks a <u>state</u>; three to five <u>states</u> summarize a <u>machine cycle</u>; and one to five <u>machine cycles</u> comprise an <u>instruction cycle</u>. A full instruction cycle requires anywhere from four to seventeen states for its completion, depending on the kind of instruction involved.

There is just one consideration that determines how many machine cycles are required in any given instruction cycle: the number of times that the processor must reference a memory address or an I/O address, in order to fetch and execute the instruction. Like many processors, the 8080 is so constructed that

it transmits one address per machine cycle. Thus, if the fetching and execution of an instruction requires two memory references, then the instruction cycle associated with that instruction consists of two machine cycles. If five such references are called for, then the instruction cycle contains five machine cycles.

Every instruction cycle has at least one reference to memory, during which the instruction is fetched. An instruction cycle must always have a fetch, even if the execution of instruction requires no further references to memory. The first machine cycle in every instruction cycle is therefore a FETCH. Beyond that, there are no fast rules. It depends on the kind of instruction. The input (INP) and the output (OUT), instructions each require three machine cycles: a FETCH, to obtain the instruction; a MEMORY READ, to obtain the address of the object peripheral; and an INPUT or an OUTPUT machine cycle, to complete the transfer.

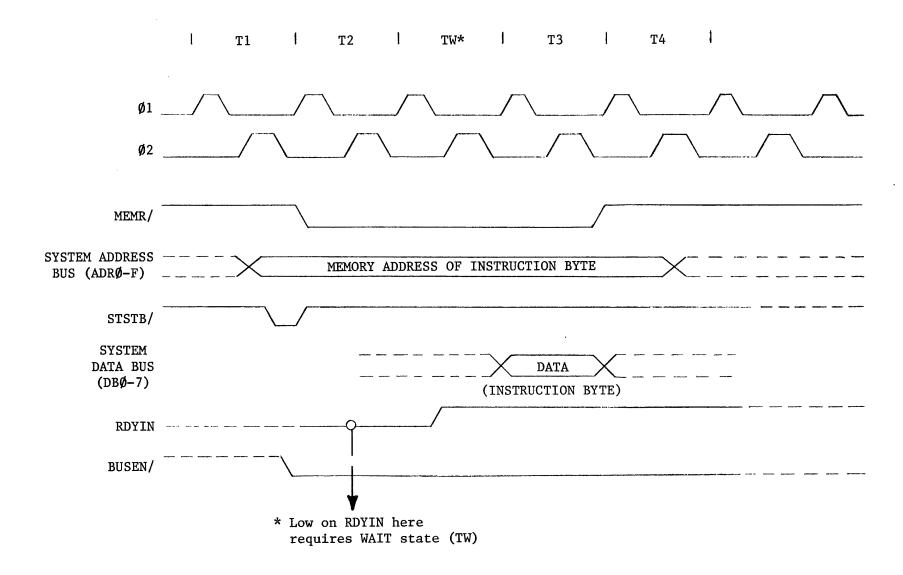

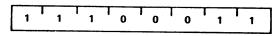

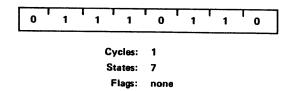

Every machine cycle within an instruction cycle consists of three to five active states (referred to as T1, T2, T3, T4, and T5). The actual number of states depends upon the instruction being executed, and on the particular machine cycle within the greater instruction cycle. Figure 3-1 shows the timing relationships in a typical FETCH machine cycle. Events that occur in each state are referred to transitions of the  $\emptyset 1$  and  $\emptyset 2$  clock pulses.

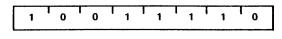

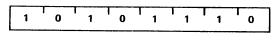

At the beginning of each machine cycle (in state T1), the 8080 activates its SYNC output and issues status information on its data bus. The 8224 accepts SYNC and generates an active-low status strobe (STSTB/) as soon as the status data is stable on the data bus. The status information indicates the type of machine cycle in progress.

FIGURE 3-1. TYPICAL FETCH MACHINE CYCLE

The 8238 System Controller accepts the status bits from the 8080 and STSTB/ from the 8224, and uses them to generate the appropriate control signals (MEMR/, MEMW/, IOR/ and IOWR/) for the current machine cycle.

The rising edge of  $\emptyset 2$  during T1 loads the processor's address lines (A0 - A15). These lines become stable within a brief delay of the  $\emptyset 2$  clocking pulse, and they remain stable until the first  $\emptyset 2$  pulse after state T3. This gives the processor ample time to read the data returned from memory.

Once the processor has sent an address to memory, there is an opportunity for the memory to request a WAIT. This it does by pulling the \$224's RDYIN line low. As long as the RDYIN line remains low, the CPU Set will idle, giving the memory time to respond to the addressed data request. The 8224 synchronizes RDYIN with internal processor timing and applies the result to the 8080's READY input. The processor responds to a wait request by entering an alternative state (TW) at the end of T2, rather than proceeding directly to the T3 state. A wait period may be of indefinite duration. The 8080 remains in the waiting condition until its READY line again goes high. The cycle may then proceed, beginning with the rising edge of the next Ø1 clock. A WAIT interval will therefore consist of an integral number of TW states and will always be a multiple of the clock period.

The events that take place during the T3 state are determined by the kind of machine cycle in progress. In a FETCH machine cycle, the CPU Set interprets the data on its data bus as an instruction. During a MEMORY READ, signals on the same bus are interpreted as a data word.

The CPU Set itself outputs data on this bus during a MEMORY WRITE machine cycle. And during I/O operations, the CPU Set may either transmit or receive data, depending on whether an INPUT or an OUTPUT operation is involved. Consider the following two examples.

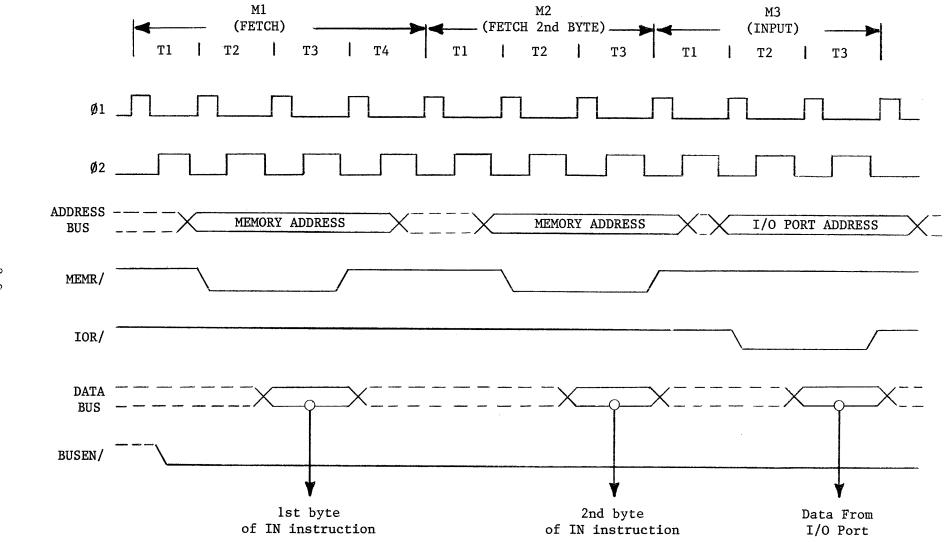

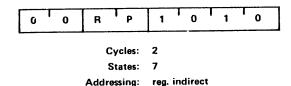

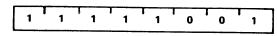

Figure 3-2 illustrates the timing that is characteristic of an input instruction cycle. During the first machine cycle (M1), the first byte of the two-byte IN instruction is fetched from memory. The 8080 places the 16-bit memory address on the system bus near the end of state T1. The 8238 activates the memory read control signal (MEMR/) during states T2 and T3 (and any intervening wait states, if required). During the next machine cycle (M2), the second byte of the instruction is fetched. During the third machine cycle (M3), the IN instruction is executed. The 8080 duplicates the 8-bit I/O address on address lines ADRO-7 and ADR8-F. The 8238 activates the I/O read control signal (IOR/) during states T2 and T3 of this cycle. In all cases the system bus enable input (BUSEN/) to the 8238 allows for normal operation of the data bus buffers and the read/write control signals. If BUSEN/ goes high the data bus output buffers and control signal buffers are forced into a high-impedance state.

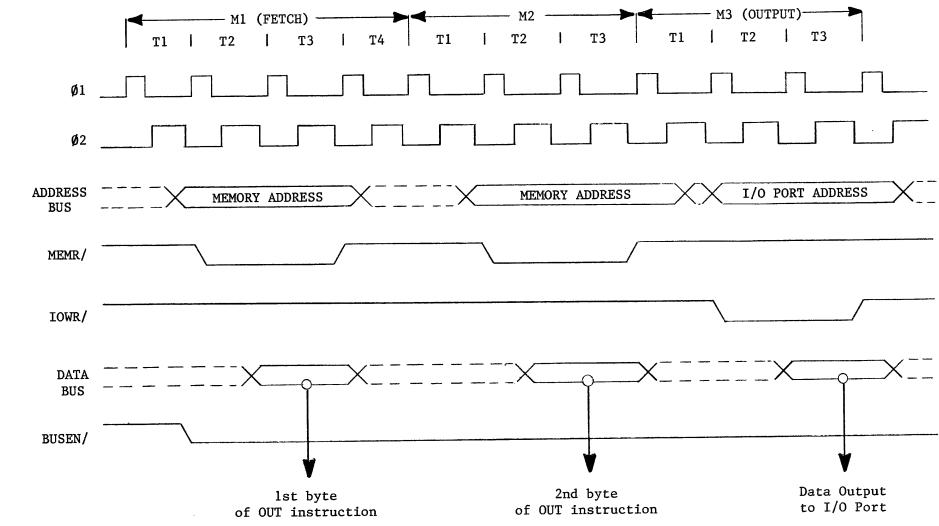

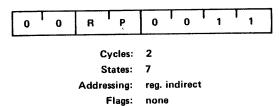

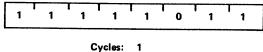

Figure 3-3 illustrates an instruction cycle during which the CPU Set outputs data. During the first two machine cycles (M1 and M2), the CPU Set fetches the two-byte OUT instruction. During the third machine cycle (M3), the OUT instruction is executed. The 8080 duplicates the 8-bit I/O address on lines ADRO-7 and ADR8-F. The 8238 activates an advanced I/O write control signal (IOWR/) at the beginning of state T2 of this cycle. The nature and implications of the 8238 timing

FIGURE 3-2. INPUT INSTRUCTION CYCLE

FIGURE 3-3. OUTPUT INSTRUCTION CYCLE

will be explained later (p. 3-17). The 8238 outputs the data onto the system bus at the end of state T2. Data on the bus remains stable throughout the remainder of the machine cycle. BUSEN/ must be low to prevent the output and control buffers from being forced into the high-impedance state.

Observe that a RDYIN signal is necessary for completion of an output machine cycle. Unless such an indication is present, the processor enters the TW state, following the T2 state. Data on the output lines remains stable in the interim, and the processing cycle will not proceed until the RDYIN line again goes high.

The 8080 generates a WR/ output for qualification of the advanced I/O write (IOWR/) and memory write (MEMW/) control signals from the 8238, during those machine cycles in which the CPU Set outputs data. The negative-going leading edge of WR/ is referred to the rising edge of the first Ø1 clock pulse following T2. WR/ remains low until re-triggered by the leading edge of Ø2, during the state following T3. Note that any TW states intervening between T2 and T3 of the output machine cycle will necessarily extend WR/.

All processor machine cycles consist of at least three states: T1, T2, and T3 as just described. If the CPU Set has to wait for a RDYIN response, then the machine cycle may also contain one or more TW states. During the three basic states, data is transferred to or from the CPU Set.

After the T3 state, however, it becomes difficult to generalize.

T4 and T5 states are available, if the execution of a particular instruction requires them. But not all machine cycles make use of these states. It depends upon the kind of instruction being executed, and

on the particular machine cycle within the instruction cycle. The processor will terminate any machine cycle as soon as its processing activities are completed, rather than proceeding through the T4 and T5 states every time. Thus the 8080 may exit a machine cycle following the T3, the T4, or the T5 state and proceed directly to the T1 state of the next machine cycle.

#### 3.1.2 INTERRUPT SEQUENCES

The 8080 has the built-in capacity to handle external interrupt requests. Peripheral logic can initiate an interrupt simply by driving the processor's interrupt (INT) line high. The interrupt (INT) input is asynchronous, and a request may therefore originate at any time during any instruction cycle. Internal logic re-clocks the external request, so that a proper correspondence with the driving clock is established. An interrupt request (INT) arriving during the time that the interrupt enable line (INTE) is high, acts in coincidence with the Ø2 clock to set the internal interrupt latch. This event takes place during the last state of the instruction cycle in which the request occurs, thus ensuring that any instruction in progress is completed before the interrupt can be processed.

The INTERRUPT machine cycle which follows the arrival of an enabled interrupt request resembles an ordinary FETCH machine cycle in most respects. The contents of the program counter are latched onto the address lines during T1, but the counter itself is not incremented during the INTERRUPT machine cycle, as it otherwise would be. In this way, the pre-interrupt status of the program counter is preserved, so that data in the counter may be saved in the stack.

This in turn permits an orderly return to the interrupted program after the interrupt request has been processed.

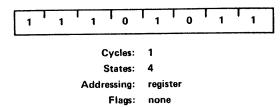

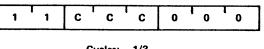

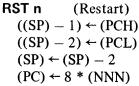

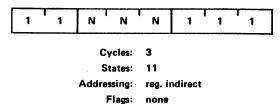

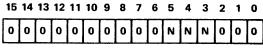

Because the 8238's INTA/ output (pin 23) is tied to +12 volts, the 8238 blocks incoming data and automatically inserts a Restart (RST 7) instruction onto the 8080 data bus during state T3, when the interrupt is acknowledged by the 8080. RST is a special one-byte call instruction that facilitates the processing of interrupts (the ordinary program call instruction is three bytes long). The RST 7 instruction causes the 8080 to branch program control to the instruction being stored in memory location 38<sub>16</sub>.

#### 3.1.3 HOLD SEQUENCES

By activating the 8080's HOLD input, an external device can cause the CPU Set to suspend its normal operations and relinquish control of the address and data busses. The CPU Set responds to a request of this kind by floating its address and data outputs, so that these exhibit a high impedance to other devices sharing the busses. At the same time, the processor acknowledges the HOLD by placing a high on on its HLDA output pin. During an acknowledged HOLD, the address and data busses are under control of the peripheral which originated the request, enabling it to conduct memory transfers without processor intervention.

#### 3.1.4 HALT SEQUENCES

When a halt instruction (HLT) is executed, the 8080 enters the halt state after state T2 of the next machine cycle. There are only three ways in which the 8080 can exit the halt state:

- · A high on the 8224 reset input (RESIN/) will always reset the 8080 to state T1; reset also clears the program counter.

- A HOLD input will cause the 8080 to enter the hold state, as previously described. When the HOLD line goes low, the 8080 re-enters the halt state on the rising edge of the next Ø1 clock pulse.

- An interrupt (i.e., INT goes high while INTE is enabled) will cause the 8080 to exit the halt state and enter state

T1 on the rising edge of the next Ø1 clock pulse. NOTE: The interrupt enable (INTE) flag must be set when the halt state is entered; otherwise, the 8080 will only be able to exit via a reset signal.

#### 3.1.5 START-UP SEQUENCE

When power is applied initially to the 8080, the processor begins operating immediately. The contents of its program counter, stack pointer, and the other working registers are naturally subject to random factors and cannot be specified. For this reason, the CPU Set power-up sequence begins with a reset. An external RC network is connected to the 8224's RESIN/ input. The slow transition of the power supply rise is sensed by an internal Schmitt Trigger which converts the slow transition into a clean, fast edge on the RESIN/ line when the input level reaches a predetermined value.

An active RESIN/ input to the 8224 produces a synchronized RESET signal which restores the processor's internal program counter to zero. Program execution thus begins with memory location zero, following

a reset. Systems which require the processor to wait for an explicit start-up signal will store a halt instruction (HLT) in this location. A manual or an automatic INTERRUPT will be used for starting. In other systems, the processor may begin executing its stored program immediately. Note, however, that the reset has no effect on status flags, or on any of the processor's working registers (accumulator, indices, or stack pointer). The contents of these registers remain indeterminate, until initialized explicitly by the program.

In addition to generating a RESET signal, the RESIN/ input causes the 8224's status strobe (STSTB/) output to remain true (low). This allows both the 8080 and 8238 to be reset by a power-up sequence or an externally generated RESIN/ condition.

#### 3.2 SYSTEM BUS INTERFACE LOGIC

The System Bus Interface logic consists of three general groups of circuitry:

- 1) assorted gates that accept the various bus control signals, the interrupt request lines, the ready indications and then applies these signals to the CPU Set.

- 2) the system bus drivers, and

- 3) the Failsafe circuitry which generates an acknowledgment during interrupt sequences and during those cycles in which an acknowledgment is not returned because a non-existent device was inadvertently addressed.

Each group is described in the following paragraphs.

## 3.2.1 SYSTEM CONTROL SIGNAL LOGIC

#### Interrupt Requests:

Four interrupt request lines are ORed together at A17-6 (ref. Appendix A) and applied to the 8080's INT input. Two of the interrupt request lines are from external sources: EXT INTR 1/ which enters the SBC-80/10

at connector J1 pin 49 and EXT INTR 2/ which enters the SBC-80/10 at P1-42. The other two interrupt requests originate on the SBC-80/10: INT 55/ is an interrupt request from ports 1 or 2 in the Parallel I/O Interface (see Section 3.6.2); and INT 51/ is an interrupt request from the 8251 USART in the Serial I/O Interface (see Section 3.5.4).

#### Hold Requests:

If the SBC-80/10 is operating in a system with other modules sharing a common external bus, another module can acquire control of the external bus by activating the 8080's HOLD/ input (connector pin P1-15). HOLD/ is inverted and applied to the 8080's HOLD pin. As described in Section 3.1.3, the 8080 will subsequently activate its hold acknowledge (HLDA) output. HLDA is, in turn, latched by a 74LS74 flip flop (at A29). The Q output from the D-type latch (DHLDA) disables the 8097 circuits (A47) that drive the external read/ write control outputs: MRDC/, MWTC/, IORC/ and IOWC/. DHLDA also disables the external system address and data bus drivers by asserting a high at their active-low chip select (CS/) input pins. As a result of DHLDA, all of the above-mentioned drivers enter the high-impedance state. The Q output from the DHLDA output informs other modules of this condition via the BUSY/ output (connector pin P1-17).

#### System Reset:

Connector pin P1-14 on the SBC-80/10 can be used to accept an externally generated SYSTEM RESET signal and to transfer a SBC-80/10

generated RESET signal to other modules in the system. If jumper pair 54-55 is connected, a RESET from the 8224 will be gated through the Q4 transistor to connector pin P1-14, thus resetting other modules in the system during power-up sequences. An externally generated SYSTEM RESET is accepted at P1-14, buffered, applied to the 8080's RESET input and made available to other logic on the SBC-80/10.

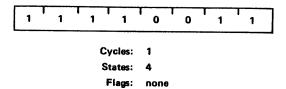

#### I/O Ready Generation

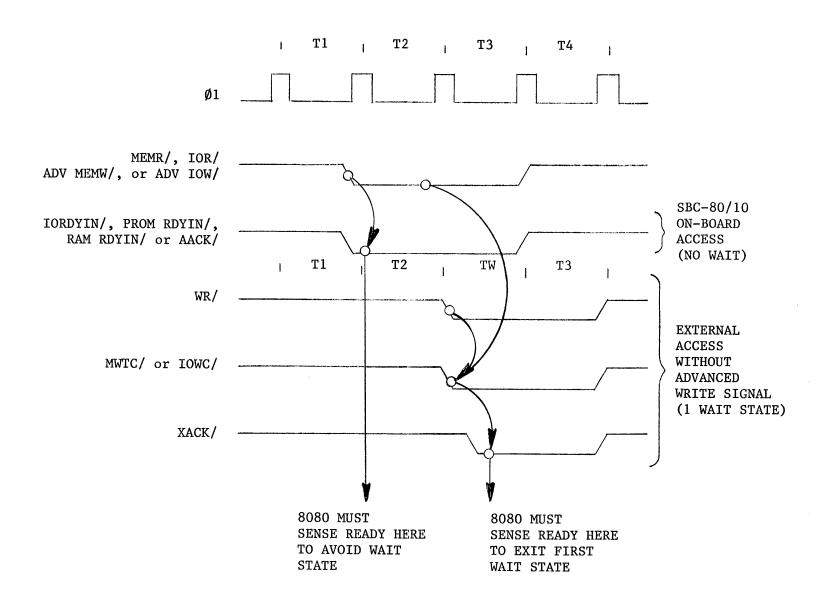

During each serial or parallel I/O cycle, a "ready" indication (IORDYIN/) is returned to the CPU Set. The three chip select lines for the 8251 and the two 8255 devices are ORed together (at A17-8 on sheet 3 of the schematic). The resultant output is then NANDed (at A44-11) with the I/O read (IOR) or the advanced I/O write (ADVIOW) signal to produce IORDYIN/. Recall from Section 3.1 that the 8238 System Controller (in the CPU Set) generates the I/O write control output at the beginning of all I/O write cycles. The IOW/ signal occurs earlier than the 8080's WR/ output. The 8238's IOW/ signal, alone, is labeled ADV IOW/. IOW/ is also synchronized with the 8080's WR/ output to produce the system write command IOWC/. ADV IOW/ allows the ready indication to be returned early enough to avoid an unnecessary wait state (see Figure 3-4). The IOWC/ signal causes an I/O device to actually write the data, later in the I/O cycle.

#### Ready Inputs:

Recall from Section 3.1.1 that the CPU Set must see a ready indication before proceeding to internal state T3 during all machine cycles. The 74S20 section at A57 on sheet 1 of the schematic OR's

the following ready indications:

- 1) INT ACK/ or TIME OUT ACK/ from the Failsafe logic (see Section 3.2.3),

- 2) IORDYIN/ from the Serial and Parallel I/O Interfaces,

- 3) PROM RDYIN/ from the ROM/PROM logic (see Section 3.4), and

- 4) RAM RDYIN/ from the RAM section (see Section 3.3).

The resultant output indicates an on-board memory or I/O access and is used to disable the external data bus drivers at A53 and A54. This output from A57-8 is also ORed (at A30-3) with the externally generated AACK/ (connector pin P1-25) and XACK/ (connector pin P1-23) inputs. The output from A30-3 is then applied to the CPU Set's RDYIN input (pin 3 on the 8224). When the SBC-80/10 CPU Set accesses an external module, the AACK/ or XACK/ input informs the CPU Set that the external device is ready. AACK/ is an advanced acknowledge that allows certain OEM modules to be accessed faster.

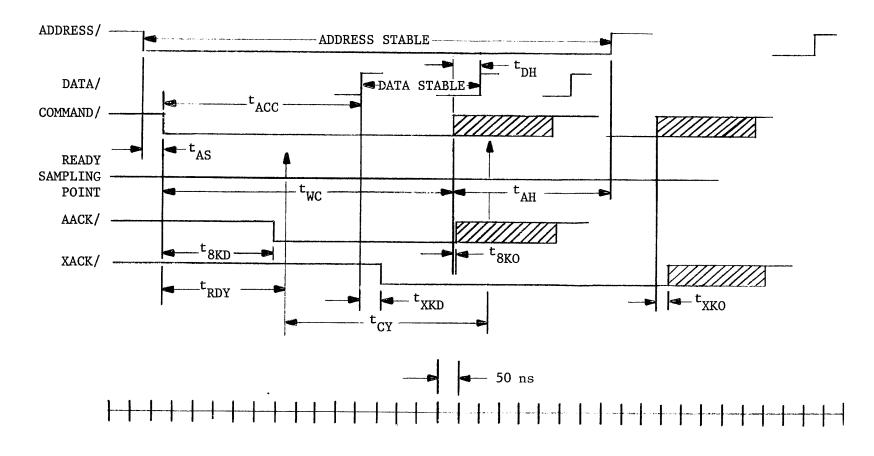

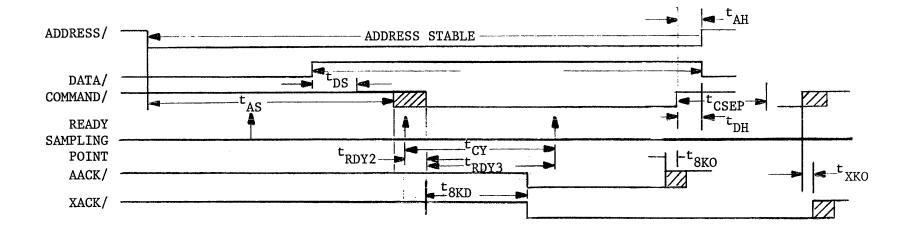

Figure 3-4 illustrates basic timing for the ready indications.

Bus Clock Generation:

The OSC output from the CPU Set (18.432 MHz frequency) is applied to the clock input of a 74LS74 D-type flip flop (at A29-11 on sheet 1 of the schematic). The  $\overline{Q}$  output from this latch is tied to its own D input. Consequently, the Q output exhibits half the frequency of the OSC input. This 9.216 MHz output is buffered and made available to external modules on the common clock (CCLK/) line (via connector pin P1-31) and the bus clock (BCLK/) line (via connector pin P1-13).

#### 3.2.2 SYSTEM BUS DRIVERS

The SBC-80/10 internal memory data bus (DMO-DM7) is driven by

FIGURE 3-4. READY TIMING

two 8216 bidirectional bus drivers, shown at A55 and A56 on sheet 3 of the schematic. All data being transferred to/from the RAM memory (see Section 3.3) or ROM/PROM memory (see Section 3.4) is routed through these two devices. The chip select (CS/) input is provided by the MEM CMD/ signal which is the result of ORing RAM RDYIN/ and PROM RDYIN/. The direction enable (DIEN) input to the 8216's is provided by the memory read (MEMR) signal.

When the SBC-80/10 communicates with an external module, the data is driven by two 8226 bidirectional data bus drivers at A53 and A54 on sheet 1 of the schematic. The direction input to the 8226's is provided by the OR of memory read (MEMR) and I/O read (IOR). The 8226 devices will be disabled during 8080 HOLD sequences. The eight data bus lines to the 8226 bus drivers enter/leave the SBC-80/10 via the P1 edge connector.

The external 16-bit system address bus is driven by four 8226 bidirectional bus drivers. However, because the direction enable pin (EN/) on these 8226 devices is tied to ground, they can only be used to transmit addresses to external modules; they will not receive addresses from external modules. Consequently, the SBC-80/10 can access other modules, but other modules cannot access the memory or I/O controllers on the SBC-80/10. Like the data bus drivers, these 8226 devices are disabled during 8080 HOLD sequences.

#### 3.2.3 FAILSAFE TIMER

When the 8080 acknowledges an interrupt request, the 8238 System Controller "forces" an RST 7 instruction onto the 8080's data bus

(see Section 3.1.2). In order to read this RST 7 instruction, however, the 8080 must sense a ready indication. The 8080 acknowledges

an interrupt by setting status bit 0 (DO) during the status output

portion of each machine cycle (i.e., when STATUS STROBE is true).

When this occurs, the 9602 one-shot (shown at A28 on sheet 5 of the

schematc) is reset causing a low signal on its output (INTR ACK/).

This output is then gated through to the RDYIN pin on the 8224 as described in Section 3.2.1.

The Failsafe timer also performs another function. If the CPU Set tries to access a memory or I/O device but that device, for some reason, does not return a ready indication, then the 8080 remains in a wait state until ready is received. The Failsafe timer is designed to prevent hanging the system up in this way. The 9602 one-shot is triggered by STATUS STROBE at the beginning of each machine cycle. If the one-shot is not re-triggered (i.e., if another cycle does not begin) within 9 ms., then the 9602 times out and its output (also labeled TIME OUT ACK/) is gated through to the RDYIN pin on the 8224, thus allowing the 8080 to exit the wait state. This can be very helpful during system debugging.

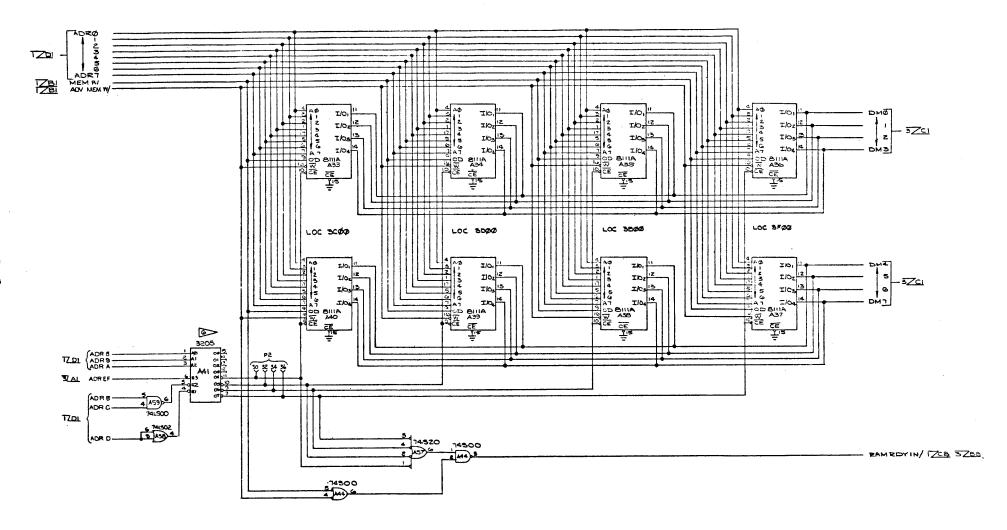

### 3.3 RANDOM ACCESS MEMORY (RAM)

The Random Access Memory (RAM) provides the SBC-80/10 user with 1024 (1k)  $\times$  8-bits of read/write storage that requires no clocks or refreshing to operate. The RAM logic consists of eight Intel 8111  $256 \times 4$  -bit Static MOS RAM chips, an Intel 3205 three-to-eight decoder for chip selection and assorted gates as shown on sheet 2 of the SBC-80/10 schematic (Appendix A).

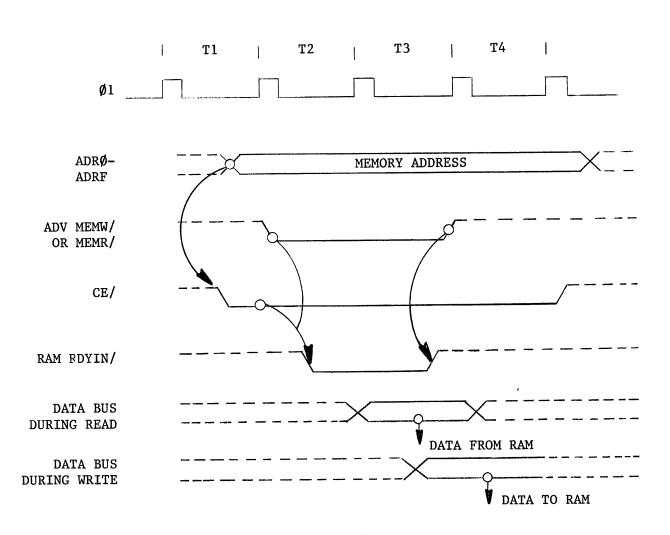

The 8111 RAM devices used on the SBC 80/10 have a maximum access time of 500 nsec. Each chip has might address inputs (A0-A7) that select one of the 256 four-bit segments, active-low write (W/) and chip enable (CE/) inputs and an output disable (OD) input. Each chip also has four common data input/output pins (I/O1-I/O4). A high on the OD input disables output and allows the I/O pins to be used for input. During memory read accesses, the data is read out nondestructively and has the same polarity as the input data.

The least significant system address lines (ADRO-ADR7) are applied to the eight address input pins on each 8111 RAM. The most significant eight system address lines (ADR8-ADRF) feed a 3205 decoder. Each of the four most significant decoder outputs are applied to the chip enable (CE/) inputs on two RAM chips. One RAM in each pair reads or writes data bits 0 to 3 (DMO-DM3) while the other RAM reads or writes data bits 4 to 7 (DM4-DM7) for each RAM access. One of the decoder outputs will be activated (low) whenever the value on the system address bus is within the range 3COO-3FFF (hexadecimal).

During memory write cycles, the advanced memory write signal (ADV MEMW/) is applied to the write input (W/) on each RAM. A high on the active-low memory read line (MEMR/) allows the selected RAM's I/O pins to be used to accept the data which is to be written into the addressed location. During memory read cycles, the level on ADV MEMW/ is high but is low on MEMR/ thus allowing the addressed data to be read out and onto the data bus.

During all RAM access cycles, the active decoder output is NANDed with ADV MEMW or MEMR (at A44-3) to produce a ready indication

for the CPU Set (RAM RDYIN/). The 8238 System Controller (see Section 3.1) generates ADV MEMW or MEMR early enough in the memory cycle to allow RAM RDYIN/ to appear at the CPU Set in time to prevent the occurrence of any wait states. Figure 3-5 illustrates RAM access timing.

Whenever SBC-80/10 RAM is accessed, the data is transferred to/ from the RAM chips on the memory data bus (DMO-DM7). Lines DMO-DM7 are interfaced to the system data bus through two Intel 8216 bidirectional bus drivers (shown at A55 and A56 on sheet 3 of the schematic) as described in Section 3.2.

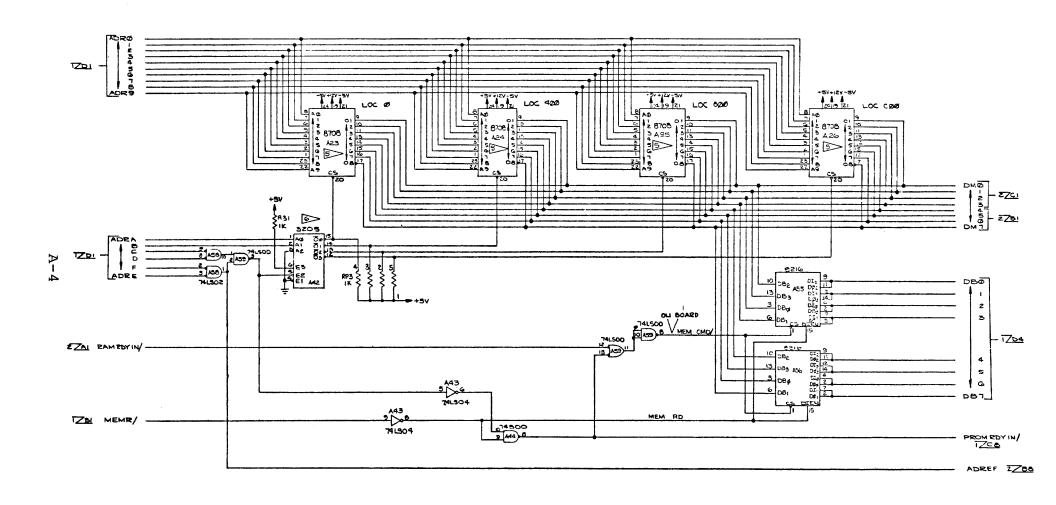

### 3.4 READ ONLY MEMORY (ROM/PROM)

The SBC-80/10 has provision for installing 4096 (4K)  $\times$  8-bit words of read only memory in sockets already on the PC board. Four Intel 8708 1K  $\times$  8-bit Erasable and Electrically Programmable Read Only Memory (PROM) chips or four 8308 1K  $\times$  8-bit static MOS mask Read Only Memory (ROM) chips can be installed in the four 24-pin sockets shown on sheet 3 of the SBC-80/10 schematic (Appendix A).

In addition to the four 24-pin sockets, the ROM/PROM logic includes an Intel 3205 decoder for address decoding and several assorted gates used in generating the ready indication.

Address lines ADRO-ADR9 are applied to the address pins AO-A9 at each of the four sockets. The remaining address lines, ADRA-ADRF are decoded by the 3205 device at A42. Each of the four least significant decoder outputs are applied to the chip select (CS/) pin at one of four sockets. One chip select line will be activated whenever the value on the system address bus is between 0000 and OFFF (hexadecimal).

FIGURE 3-5. RAM ACCESS TIMING

In addition, when the four most significant address lines are low (i.e., the address is less than OFFF) during a memory read cycle, the output from the 74LSOO section at A39-3 is NANDed with MEMR to produce a ready indication (PROM RDYIN/) for the CPU Set. PROM RDYIN/ is thus generated in time to allow all ROM/PROM reads to occur without any wait states. PROM RDYIN/ has the same timing as RAM RDYIN/, as shown in Figure 3-5.

Whenever one of the ROM/PROM devices are read, the data from the chips output pins (01-08) is placed on the memory data bus (DMO-DM7) which is interfaced to the system bus via two Intel 8216 bidirectional bus drivers (at A55 and A56), as described in Section 3.2.

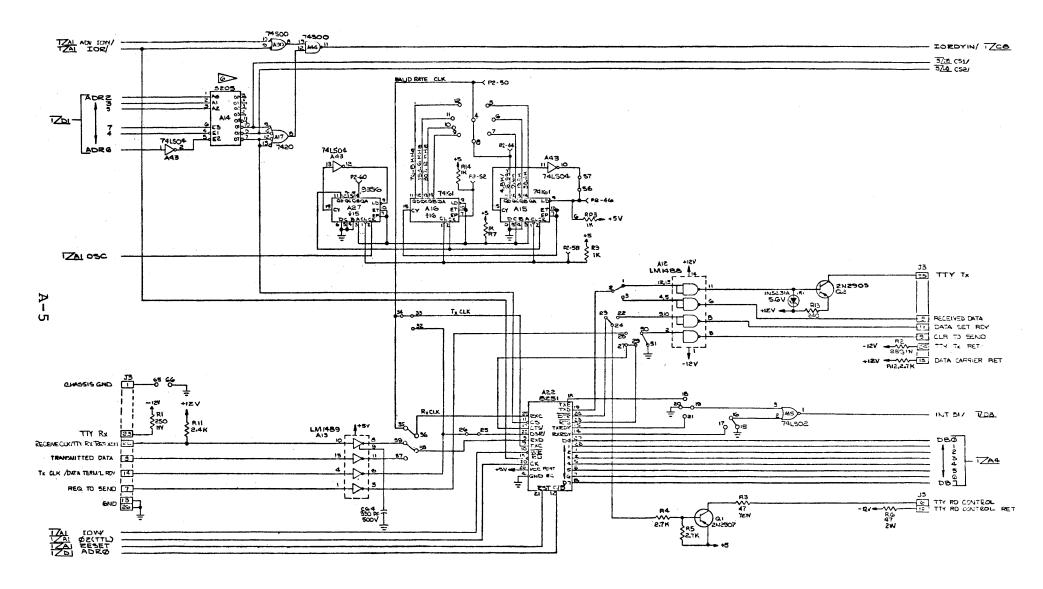

#### 3.5 SERIAL I/O INTERFACE

The Serial I/O Interface logic provides the SBC-80/10 with a serial data communications channel that can be programmed to operate with most of the current serial data transmission protocols, synchronous or asynchronous. Baud rate, character length, number of stop bits and even/odd parity are program selectable. In addition, the serial I/O Interface can be configured (through jumper connections) as an EIA RS232Cinterface or as a Teletype-compatible current loop interface.

The Serial I/O Interface logic consists primarily of an Intel 8251 USART device and a counting network for baud rate selection, as shown on sheet 4 of the SBC-80/10 schematic (Appendix A). Before describing the specific operation of the Serial I/O logic however, we will summarize the general operational characteristics of the 8251

USART, because it essentially defines the character of the Serial I/O Interface.

#### 3.5.1 INTEL 8251 OPERATIONAL SUMMARY

The 8251 is a Universal Synchronous/Asynchronous Receiver/Transmitter designed specifically for the 8080 Micro-computer System. Like other I/O devices in the 8080 Micro-computer System its functional configuration is programmed by the systems software for maximum flexibility. The 8251 can support virtually any serial data technique currently in use (including IBM "Bi-Sync").

#### Modem Control

The 8251 has a set of control inputs and outputs that can be used to simplify the interface to almost any Modem. The modem control signals are general purpose in nature and can be used for functions other than Modem control, if necessary.

### DSR (Data Set Ready)

The  $\overline{\text{DSR}}$  input signal is general purpose in nature. Its condition can be tested by the CPU using a Status Read operation. The  $\overline{\text{DSR}}$  input is normally used to test Modem conditions such as Data Set Ready.

#### DTR (Data Terminal Ready)

The  $\overline{DTR}$  output signal is general purpose in nature. It can be set "low" by programming the appropriate bit in the Command Instruction word. The  $\overline{DTR}$  output signal is normally used for Modem control such as Data Terminal Ready or Rate Select.

## RTS (Request to Send)

The  $\overline{\text{RTS}}$  output signal is general purpose in nature. It can be set "low" by programming the appropriate bit in the Command Instruction word. The  $\overline{\text{RTS}}$  output signal is normally used for Modem control such as Request to Send.

## CTS (Clear to Send)

A "low" on this input enables the 8251 to transmit data (serial) if the TxEN bit in the Command byte is set to a "one". This is very important to remember!

USART PIN CONFIGURATION

| _                |    |      |    |                   |

|------------------|----|------|----|-------------------|

| D <sub>2</sub>   | 1  |      | 28 | <b>⊐</b> □,       |

| ₽3 🗖             | 2  |      | 27 | <b>⊐</b> ₽₀       |

| RxD 🗀            | 3  |      | 26 | □ v <sub>cc</sub> |

| GND 🗖            | 4  | 8251 | 25 | RxC               |

| D, 🗀             | 5  |      | 24 | DTR               |

|                  | 6  |      | 23 | RTS               |

| D <sub>6</sub> 🗀 | 7  |      | 22 | DSR               |

| D, 🗀             | 8  |      | 21 | RESET             |

| TxC _            | 9  |      | 20 | CLK CLK           |

| WR 🗀             | 10 |      | 19 | TxD               |

| cs 🗖             | 11 |      | 18 | TXEMPTY           |

| c/ō 🗖            | 12 |      | 17 | CTS               |

| RD 🗀             | 13 |      | 16 | SYNDET            |

| RxRDY [          | 14 |      | 15 | TxRDY             |

| Pin Name                      | Pin Function                                 |

|-------------------------------|----------------------------------------------|

| D <sub>7</sub> D <sub>0</sub> | Data Bus (8 bits)                            |

| C/D                           | Control or Data is to be Written or Read     |

| RD                            | Read Data Command                            |

| WR                            | Write Data or Control Command                |

| ĊS                            | Chip Enable                                  |

| CLK                           | Clock Pulse (TTL)                            |

| RESET                         | Reset                                        |

| T×C                           | Transmitter Clock                            |

| TxD                           | Transmitter Data                             |

| RxC                           | Receiver Clock                               |

| RxD                           | Receiver Data                                |

| RxRDY                         | Receiver Ready (has character for 8080)      |

| TxRDY                         | Transmitter Ready (ready for char, from 8080 |

| i | Pin Name | Pin Function         |

|---|----------|----------------------|

|   | DSR      | Data Set Ready       |

|   | DTR      | Data Terminal Ready  |

|   | SYNDET   | Sync Detect          |

|   | RTS      | Request to Send Data |

|   | CTS      | Clear to Send Data   |

|   | TxE      | Transmitter Empty    |

|   | Vcc      | +5 Volt Supply       |

|   | GND      | Ground               |

FIGURE 3-6. 8251 PIN ASSIGNMENTS

## TXRDY (Transmitter Ready)

This output signals the CPU that the transmitter is ready to accept a data character. It can be used as an interrupt to the system or for polled operation when the CPU can check TXRDY using a status read operation.  $\overline{\text{TXRDY}}$  is active only when  $\overline{\text{CTS}}$  is enabled.  $\overline{\text{TXRDY}}$  is automatically reset when a character is loaded from the CPU.

#### TXE (Transmitter Empty)

When the 8251 has no characters to transmit, the TxE output will go "high". It resets automatically upon receiving a character from the CPU. TXE can be used to indicate the end of a transmission mode, so that the CPU "knows" when to "turn the line around" in the half-duplexed operational mode.

In SYNChronous mode, a "high" on this output indicates that a character has not been loaded and the SYNC character or characters are about to be transmitted automatically as "fillers".

#### TXC (Transmitter Clock)

The Transmitter Clock controls the rate at which the character is to be transmitted. In the Synchronous transmission mode, the frequency of  $\overline{\text{TXC}}$  is equal to the actual Baud Rate (1X). In Asynchronous transmission mode, the frequency of  $\overline{\text{TXC}}$  is a multiple of the actual Baud Rate. A portion of the mode instruction selects the value of the multiplier; it can be 1X, 16X or 64X the Baud Rate.

#### For Example:

If Baud Rate equals 110 Baud,

TXC equals 110 Hz (1X)

TXC equals 1.76 kHz (16X)

$\overline{\text{TXC}}$  equals 7.04 kHz (64X).

If Baud Rate equals 9600 Baud,

TXC equals 614.4 kHz (64X).

The falling edge of  $\overline{\text{TXC}}$  shifts the serial data out of the 8251.

### RXRDY (Receiver Ready)

This output indicates that the 8251 contains a character that is ready to be input to the CPU. RXRDY can be connected to the interrupt structure of the CPU or for polled operation the CPU can check the condition of RXRDY using a status read operation. RXRDY is automatically reset when the character is read by the CPU.

### RXC (Receiver Clock)

The Receiver Clock controls the rate at which the character is to be received. In Synchronous Mode, the frequency of  $\overline{\text{RXC}}$  is equal to the actual Baud Rate (1X). In Asynchronous Mode, the frequency of  $\overline{\text{RXC}}$  is a multiple of the actual Baud Rate. A portion of the mode instruction selects the value of the multiplier; it can be 1X, 16X or 64X the Baud Rate.

### For Example:

If Baud Rate equals 300 Baud,

RXC equals 300 Hx (1X)

RXC equals 4800 Hz (16X)

RXC equals 19.2 kHz (64X).

If Baud Rate equals 2400 Baud,

RXC equals 2400 Hz (1X)

RXC equals 38.4 kHz (16X)

RXC equals 153.6 kHz (64X).

Data is sampled into the 8251 on the rising edge of  $\overline{\text{RXC}}$ .

Note: In most communications systems, the 8251 will be handling both the transmission and reception operations of a single link.

Consequently, the Receive and Transmit Baud Rates will be the Same. Both TXC and RXC will require identical frequencies for this operation and can be tied together and connected to a single frequency source (Baud Rate Generator) to simplify the interface.

### SYNDET (SYNC Detect)

This pin is used in SYNCHronous Mode only. It is used as either input or output, programmable through the Control Word. It is reset to "low" upon RESET. When used as an output (internal Sync mode), the SYNDET pin will go "high" to indicate that the 8251 has located the SYNC character in the Receive mode. If the 8251 is programmed to use double Sync characters, then SYNDET will go "high" in the middle of the last bit of the second Sync character. SYNDET is automatically reset upon a Status Read operation.

When used as an input, (external SYNC detect mode), a positive going signal will cause the 8251 to start assembling data characters on the falling edge of the next  $\overline{\text{RXC}}$ . Once in SYNC, the "high" input signal can be removed. The duration of the high signal should be at least equal to the period of  $\overline{\text{RXC}}$ .

### Programming the 8251

Prior to starting data transmission or reception, the 8251 must be loaded with a set of control words generated by the CPU. These control signals define the complete functional definition of the 8251 and must immediately follow a Reset operation (internal or external).

The control words are split into two formats:

- 1. Mode Instruction,

- 2. Command Instruction.

Both the Mode and Command instructions must conform to a specified sequence for proper device operation. The Mode Instruction must be inserted immediately following a Reset operation, prior to using the 8251 for data communication.

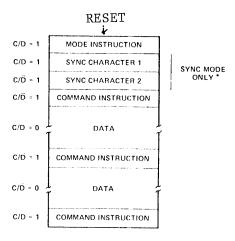

All control words written into the 8251 after the Mode Instruction will load the Command Instruction. Command Instructions can be written into the 8251 at any time in the data block during the operation of the 8251. To return to the Mode Instruction format a bit in the Command Instruction word can be set to initiate an internal Reset operation which automatically places the 8251 back into the Mode Instruction format. Command Instructions must follow the Mode Instructions or Sync characters (see Figure 3-7).

\*The second SYNC character is skipped if MODE instruction has programmed the 8251 to single character Internal SYNC Mode. Both SYNC characters are skipped if MODE instruction has programmed the 8251 to ASYNC mode.

FIGURE 3-7. TYPICAL 8251 DATA BLOCK

#### Mode Instruction:

This format defines the general operational characteristics of the 8251. It must follow a Reset operation (internal or external). Once the Mode instruction has been written into the 8251 by the CPU, SYNC characters or Command instructions may be inserted.

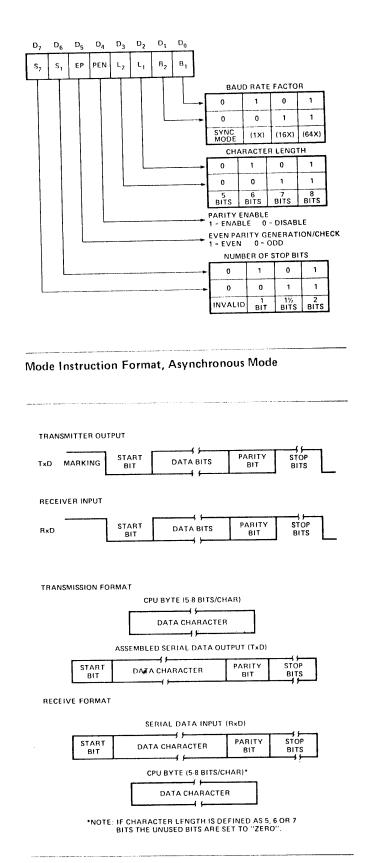

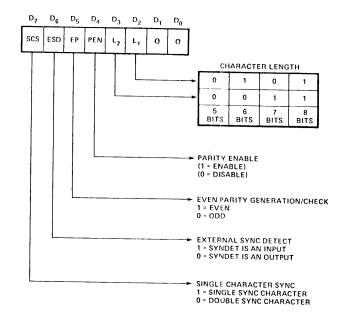

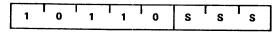

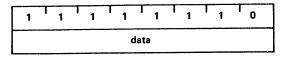

The 8251 can be used for either synchronous or asynchronous

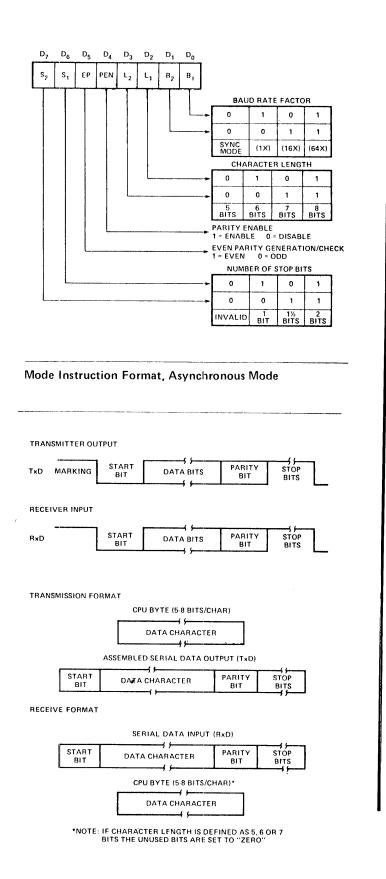

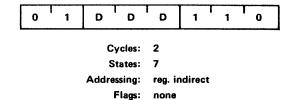

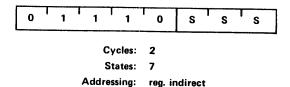

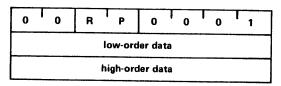

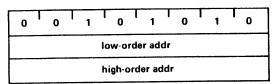

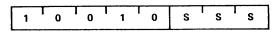

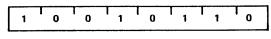

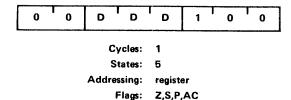

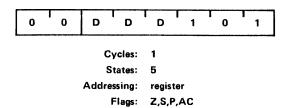

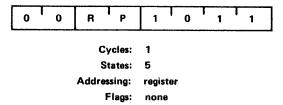

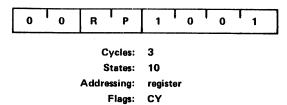

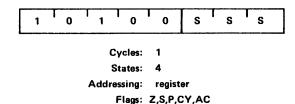

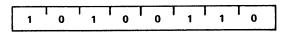

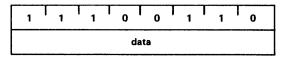

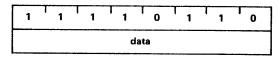

data communications. The two least significant bits of the Mode Instruction control word specify synchronous or asynchronous operation. The format for the remaining bits in the control word depends on the mode chosen by bits 0 and 1. Figure 3-8 shows the control word format for the asynchronous mode, while Figure 3-9 illustrates the control word format for the synchronous mode.

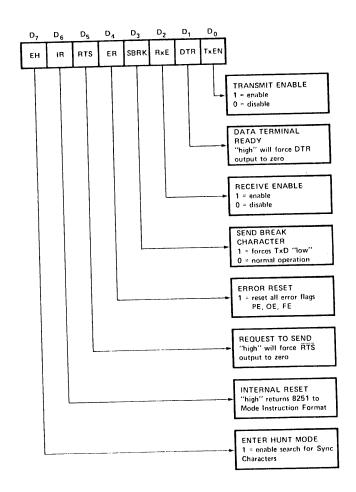

#### Command Instruction:

Once the functional definition of the 8251 has been programmed by the Mode Instruction and the Sync Characters are loaded (if in Sync Mode) then the device is ready to be used for data communication. The Command Instruction controls the actual operation of the selected format. Functions such as: Enable Transmit/Receive, Error Reset and Modem Controls are provided by the Command Instruction.

Once the Mode instruction has been written into the 8251 and Sync characters inserted, if necessary, then all further "control writes" ( $C/\overline{D}=1$ ) will load the Command Instruction. A Reset operation (internal or external) will return the 8251 to the Mode Instruction Format.

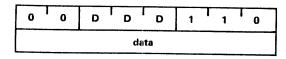

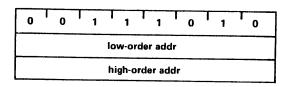

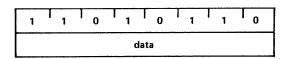

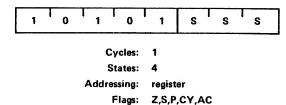

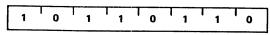

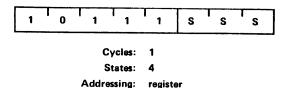

Figure 3-10 illustrate the format of a Command Instruction control word.  $\dot{}$

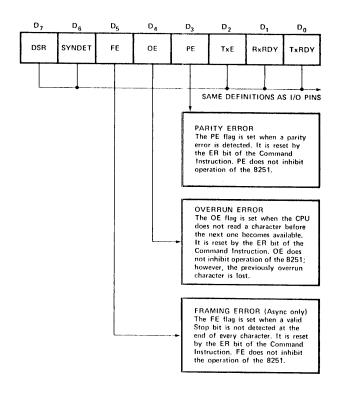

#### Status Read Definition

In data communication systems it is often necessary to examine the "status" of the active device to ascertain if errors have occurred or other conditions that require the processor's attention. The 8251 has facilities that allow the programmer to "read" the status of the device at any time during the functional operation.

FIGURE 3-8. ASYNCHRONOUS MODE.

FIGURE 3-9. SYNCHRONOUS MODE.

FIGURE 3-10. COMMAND INSTRUCTION FORMAT

A normal "read" command is issued by the CPU with the  $\mbox{C}/\overline{\mbox{D}}$  input at one to accomplish this function.

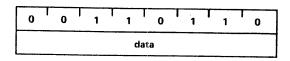

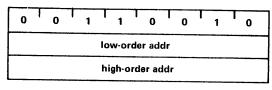

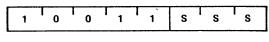

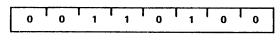

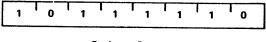

Some of the bits in the Status Read Format have identical meanings to external output pins so that the 8251 can be used in a completely Polled environment or in an interrupt driven environment (refer to Figure 3-11).

FIGURE 3-11. STATUS READ FORMAT

## 8251 DATA TRANSFERS

Once programmed, the 8251 is ready to perform its communication functions. The TXRDY output is raised "high" to signal the CPU that the 8251 is ready to receive a character. This output (TXRDY) is reset automatically when the CPU writes a character into the 8251. On the other hand, the 8251 receives serial data from the MODEM or

I/O device; upon receiving an entire character the RXRDY output is raised "high" to signal the CPU that the 8251 has a complete character ready for the CPU to fetch. RXRDY is reset automatically upon the CPU read operation.

The 8251 cannot begin transmission until the TXEN (Transmitter Enable) bit is set in the Command Instruction and it has received a Clear To Send (CTS) input. The TXD output will be held in the marking state upon Reset.

### Asynchronous Mode (Transmission):

Whenever a data character is sent by the CPU the 8251 automatically adds a Start bit (low level) and the programmed number of Stop bits to each character. Also, an even or odd Parity bit is inserted prior to the Stop bit(s), as defined by the Mode Instruction. The character is then transmitted as a serial data stream on the TXD output. The serial data is shifted out on the falling edge of  $\overline{\text{TXC}}$  at a rate equal to 1/16 or 1/64 that of the  $\overline{\text{TXC}}$ , as defined by the Mode Instruction. BREAK characters can be continuously sent to the TXD if commanded to do so.

When no data characters have been loaded into the 8251 the TXD output remains "high" (marking) unless a Break (continuously low) has been programmed.

### Asynchronous Mode (Receive):

The RXD line is normally high. A falling edge on this line triggers the beginning of a START bit. The validity of this START bit is checked by again strobing this bit at its nominal center.

If a low is detected again, it is a valid START bit, and the bit

counter will start counting. The bit counter locates the center of the data bits, the parity bit (if it exists) and the stop bits. If parity error occurs, the parity error flag is set. Data and parity bits are sampled on the RXD pin with the rising edge of RXC. If a low level is detected as the STOP bit, the Framing Error flag will be set. The STOP bit signals the end of a character. This character is then loaded into the parallel I/O buffer of the 8251. The RXRDY pin is raised to signal the CPU that a character is ready to be fetched. If a previous character has not been fetched by the CPU, the present character replaces it in the I/O buffer, and the OVERRUN flag is raised (thus the previous character is lost). All of the error flags can be reset by a command instruction. The occurrence of any of these errors will not stop the operation of the 8251.

#### Synchronous Mode (Transmission):

The TXD output is continuously high until the CPU sends its first character to the 8251 which usually is a SYNC character. When the  $\overline{\text{CTS}}$  line goes low, the first character is serially transmitted out. All characters are shifted out on the falling edge of  $\overline{\text{TXC}}$ . Data is shifted out at the same rate as the  $\overline{\text{TXC}}$ .

Once transmission has started, the data stream at TXD output must continue at the TXC rate. If the CPU does not provide the 8251 with a character before the 8251 becomes empty, the SYNC characters (or character if in single SYNC word mode) will be automatically inserted in the TXC data stream. In this case, the TXEMPTY pin will momentarily go high to signal that the 8251 is empty and SYNC characters are being sent out. The TXEMPTY pin is internally reset by the next character being written into the 8251.

Synchronous Mode (Receive):

In this mode, character synchronization can be internally or externally achieved. If the internal SYNC mode has been programmed, the receiver starts in a HUNT mode. Data on the RXD pin is then sampled in on the rising edge of RXC. The content of the RX buffer is continuously compared with the first SYNC character until a match occurs. If the 8251 has been programmed for two SYNC characters, the subsequent received character is also compared. When both SYNC characters have been detected, the USART ends the HUNT mode and is in character synchronization. The SYNDET pin is then set high, and is reset automatically by a STATUS READ.

In the external SYNC mode, synchronization is achieved by applying a high level on the SYNDET pin. The high level can be removed after one  $\overline{\text{RXC}}$  cycle.

Parity error and overrun error are both checked in the same way as in the Asynchronous receive mode.

The CPU can command the receiver to enter the HUNT mode if synchronization is lost.

#### 3.5.2 Serial I/O Configurations

The 8251 USART presents a parallel, eight-bit interface to the CPU Set via the system data bus (DBO-DB7) and presents a EIA RS232C \* or TTY current loop\* interface to an external device (via edge connector J3). The 8251's interface with the CPU Set is enabled by a low

\* Electrical interfaces provided on SBC 80/10

level on its chip select (CS/) pin. CS/ is low when the I/O address on the system address bus is between EC and EF (hexadecimal). Address bits 2 through 7 are decoded (at A14) to produce the CS/ input. The

TABLE 3-0. SERIAL COMMUNICATION (8251) ADDRESS ASSIGNMENTS

| I/O ADDRESS<br>(BASE 16) | COMMAND | FUNCTION     |  |

|--------------------------|---------|--------------|--|

| ED OR EF                 | OUTPUT  | CONTROL WORD |  |

| EC OR EE                 | OUTPUT  | DATA         |  |

| ED OR EF                 | INPUT   | STATUS       |  |

| EC OR EE                 | INPUT   | DATA         |  |

least significant address bit, ADRO, is applied to the 8251's  $C/\overline{D}$  input (pin 12) thus indicating a control (if set) or data (if reset) byte on the data bus.

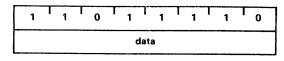

An output instruction (IOW/ is true) to port ED or EF (CS/ is low and ADRO is high) causes the 8251 to accept a control byte through its data bus pins. The control byte can be either a mode instruction or a command instruction, depending on the sequence in which it is sent. The various bits in the mode control word specify the baud rate multiplexer, character length, parity and the number of stop bits as described in Section 3.5.1. Note that the actual baud rate selected is dependent on the configuration of the baud rate jumper network (refer to Section 3.5.3). The various bits in the command control word instruct the USART to enable/disable the receiver and transmitter, to reset errors, to reset internal control and return to the mode control cycle, and to set/clear the Data Terminal Ready output.

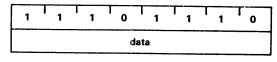

An output instruction to portEC or EE (CS/ and ADRO are low) causes the 8251 USART to accept a data byte through its data bus pins. Bit 0 is the least significant bit and bit 7 is the most significant bit. The 8251 will subsequently transmit the data byte (if the transmitter is enabled), in serial fashion, to the external device as described in Section 3.5.1.

An input instruction (IOR/ is true) to port ED or EF (CS/ is low and ADRO is high) causes the 8251 USART to place a status byte onto the system bus. The status bits are the result of status and error checking functions performed within the USART (see Section 3.5.1).

An input instruction (IOR/ is true) to port EC or EE (CS/ and ADRO are low) causes the USART to output a data byte (previously

received from the external device) from its data bus pins. Bit 0 is the least significant bit and bit 7 is the most significant bit.

Timing for the USART's internal function is provided by the  $\phi$ 2TTL signal (see Section 3.1.1). The USART is reset by the occurrence of a high level on the RESET line.

The 8251 USART transmits and receives serial data, synchronously or asynchronously, as described in Section 3.5.1. By jumper-connecting the 8251 pins to different external lines, the Serial I/O logic can present either a Teletype-compatible current loop interface or an EIA RS232C interface to an external device. If the TTY-compatible current loop interface is used, the connections listed in Table 4-1 are required (see Section 4.1).

If the EIARS232C interface is used, the connections listed in Table 4-2 are required (see Section 4.1).

### 3.5.3 BAUD RATE CLOCK GENERATION

The baud rate clock network consists of a 93S16 'divide-by-15' counter, two 74161 'divide-by-16' counters and wire-wrap jumpers for baud rate clock selection. The 93S16 counter is driven by the oscillator output (OSC) from the CPU Set. The QD output from this counter, in turn, drives the two 74161 counters. The outputs from these counters, each providing a different clock frequency, are tied to jumper pins that can be connected to the BAUD RATE CLK line. The available frequencies are listed in Table 4-3 (located in Section 4.2). Recall that the effective baud rate of the 8251 USART is also dependent on the state of the 8251's internal frequency divider and the mode of operation (refer to Section 3.5.1). The 8251 is capable of dividing the baud rate clock by 1, 16 or 64.

#### 3.5.4 SERIAL I/O INTERRUPTS

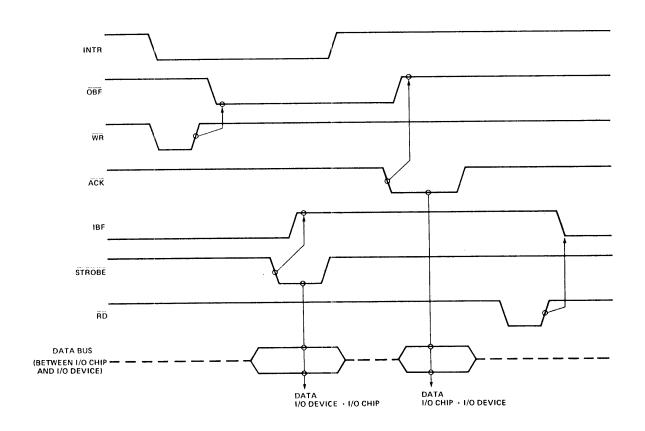

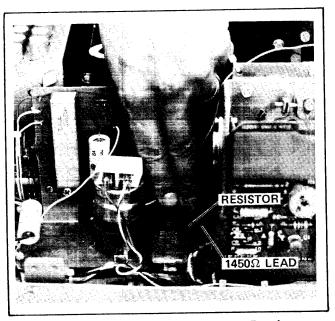

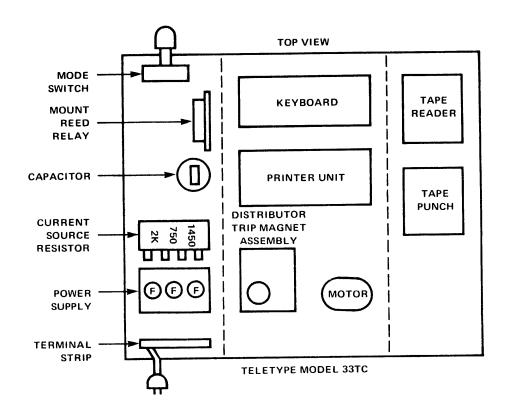

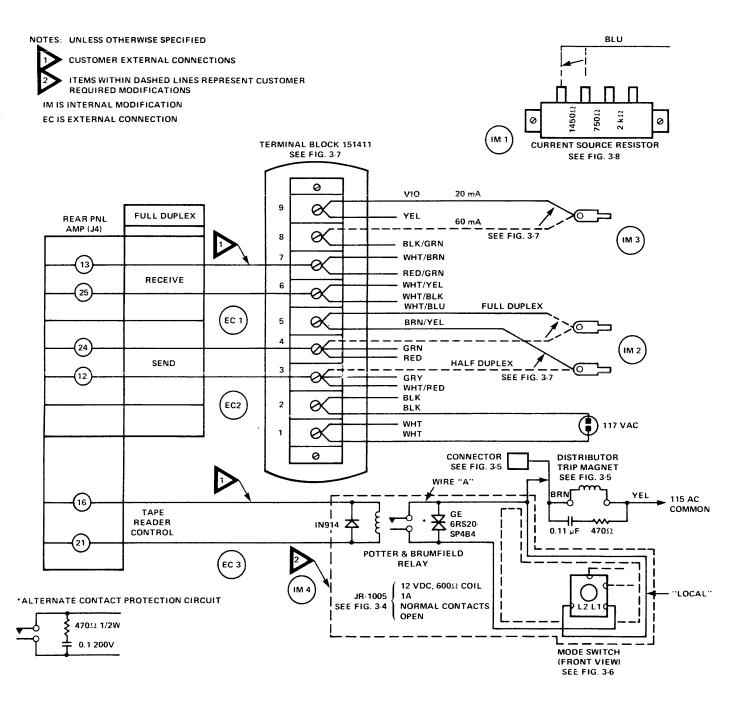

The Serial I/O logic can be configured with different forms of an interrupt request mechanism. By connecting jumper pair 16-17 and disconnecting 15-16, the user can allow the 8251's Receiver Ready (RXRDY) output (pin 14) to generate an interrupt request (INT51/) to the CPU Set. RXRDY goes high whenever the receiver enable bit of the command word has been set and the 8251 contains a character that is ready to be input to the CPU Set. The user can also choose to have the 8251's Transmitter Ready (TXRDY) or the Transmitter Empty (TXE) output activate the INT51/ interrupt request. If jumper pair 19-21 is connected, a high on TXRDY (pin 15) will activate INT51/. If jumper pair 18-19 is connected instead, an active TXE (pin 18) output will generate INT51/. TXE goes high when the 8251 has no characters to transmit. TXRDY is high when the 8251 is ready to accept a character from the CPU Set. Both TXE and TXRDY are enabled by setting the transmit enable bit of the command word. Notice on the schematic that, if jumper pairs 19-20 and 15-16 are connected, Serial I/O interrupts are inhibited.