# SBC 211/212 DISKETTE HARDWARE SYSTEM HARDWARE REFERENCE MANUAL

Manual Order Number: 98-349B

# SBC 211/212 DISKETTE HARDWARE SYSTEM HARDWARE REFERENCE MANUAL

Manual Order Number: 98-349B

Copyright © 1976, 1977 Intel Corporation

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

ICE-30 ICE-80 INSITE INTEL INTELLEC LIBRARY MANAGER MCS

MEGACHASSIS MICROMAP MULTIBUS PROMPT RMX-80 UPI

#### PREFACE

This reference manual is intended as the primary source of information on the Intel Diskette Hardware System. We have tried to explain, in an easy to follow format, how to incorporate the diskette system into an Intel OEM computer system, how it communicates with the other SBC products and what internal operations take place.

Refer to the SBC 915 User's Guide for a description of the optional Go/No Go Diagnostic and Monitor Program for SBC 80/10 and System 80/10, and to the SBC 925 User's Guide for a description of the optional Go/No Go Diagnostic and Monitor Program for SBC 80/20 and System 80/20.

# TABLE OF CONTENTS

| CHAPTER | TITLE                                                                                                                                                                                                                                                                                                                                                | PAGE NO                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                         | 1-1                                               |

|         | 1.1 SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                  | 1-1<br>1-6                                        |

| 2       | OPERATIONAL SUMMARY AND PROGRAMMING CONSIDERATIONS                                                                                                                                                                                                                                                                                                   | 2-1                                               |

|         | 2.1 CHANNEL COMMANDS 2.2 DISKETTE OPERATIONS 2.3 I/O PARAMETER BLOCK 2.4 ERROR INDICATIONS                                                                                                                                                                                                                                                           | 2-10<br>2-17                                      |

| 3       | THE CHANNEL BOARD                                                                                                                                                                                                                                                                                                                                    | 3-1                                               |

|         | 3.1 FUNCTIONAL ORGANIZATION OF THE CHANNEL BOARD  3.2 THEORY OF OPERATION: CHANNEL BOARD 3.2.1 CHANNEL COMMAND BLOCK 3.2.2 MICRO CONTROL UNIT (MCU) BLOCK 3.2.3 MICROPROGRAM MEMORY BLOCK 3.2.4 CENTRAL PROCESSING ELEMENT (CPE) BLOCK 3.2.5 DATA/CLOCK SHIFT REGISTER BLOCK 3.2.6 DATA FLOW CONTROL BLOCK 3.3.3 SCHEMATICS/PIN LISTS: CHANNEL BOARD | 3-6<br>3-6<br>3-9<br>3-14<br>3-21<br>3-26<br>3-28 |

| 4       | THE INTERFACE BOARD                                                                                                                                                                                                                                                                                                                                  | 4-1                                               |

|         | 4.1 FUNCTIONAL ORGANIZATION OF THE INTERFACE BOARD  4.2 THEORY OF OPERATION: INTERFACE BOARD 4.2.1 DISK DRIVE CONTROL 4.2.2 SERIAL DATA/CLOCK SYNCHRONIZATION 4.2.3 WRITE CLOCK GENERATOR 4.2.4 CYCLIC REDUNDANCY CHECK (CRC) 4.2.5 BUS CONTROL                                                                                                      | 4-5<br>4-5<br>4-9<br>4-15<br>4-19                 |

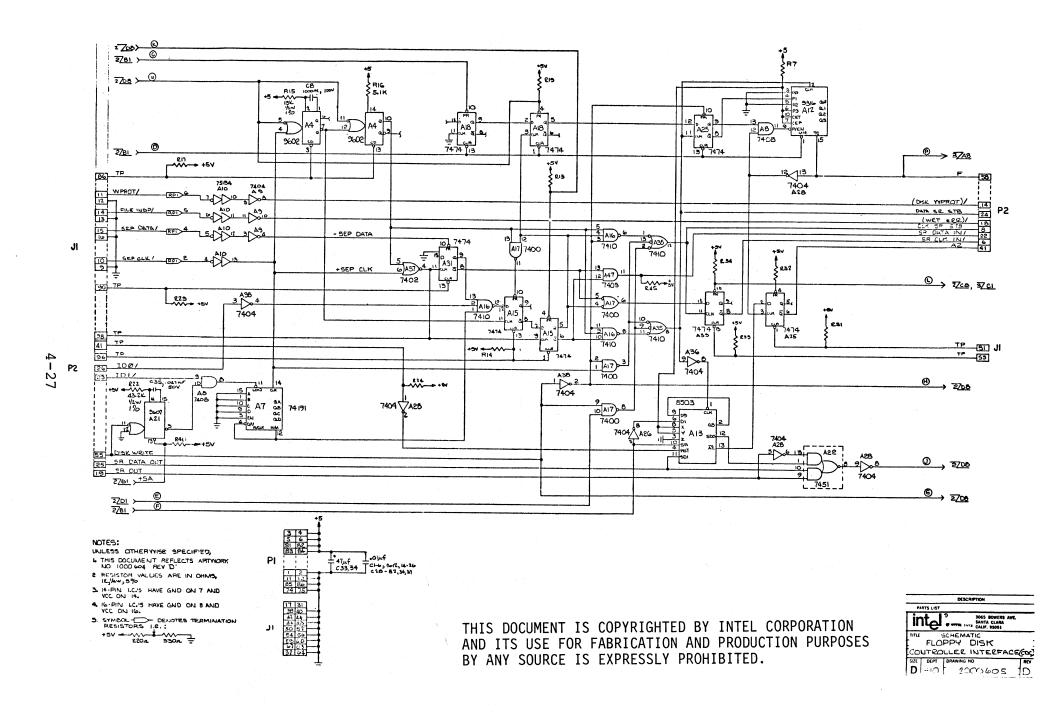

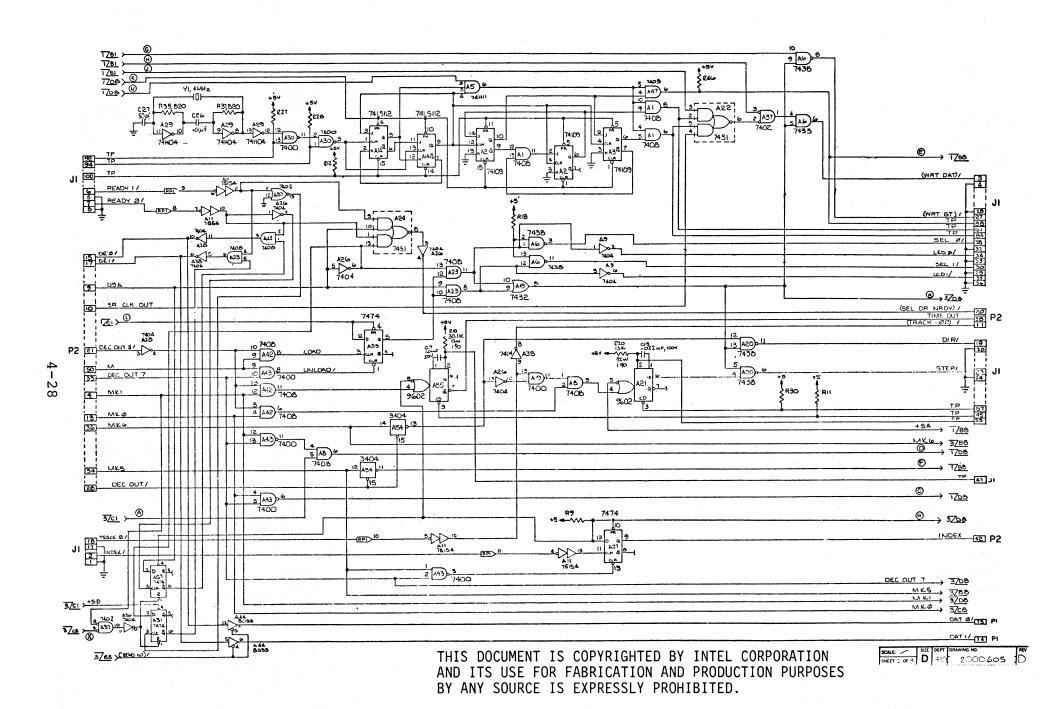

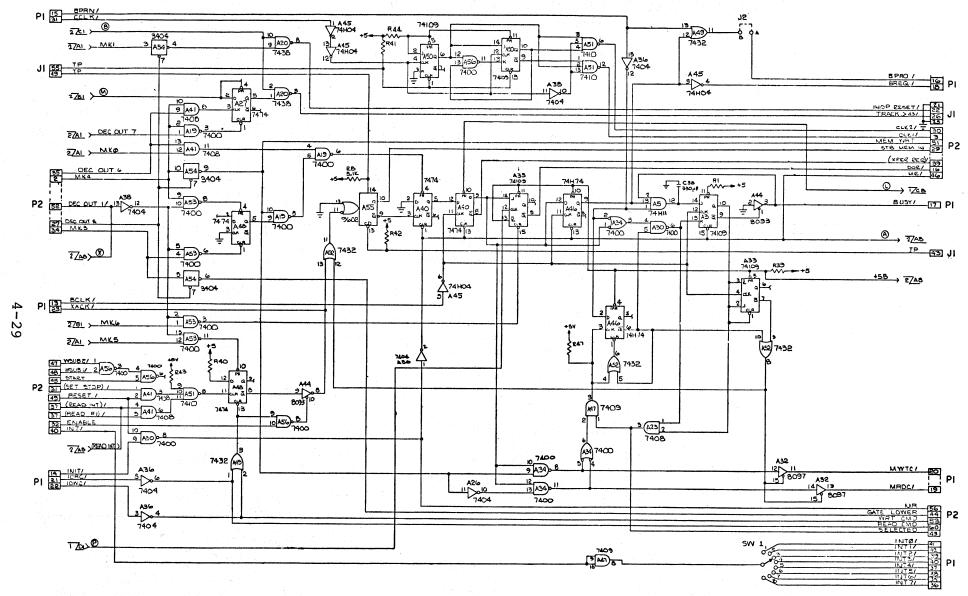

|         | 4.3 SCHEMATICS/PIN LISTS: INTERFACE BOARD                                                                                                                                                                                                                                                                                                            | 4-26                                              |

# TABLE OF CONTENTS - (Continued)

| CHAPTER | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PAGE NO.                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|         | THE DISKETTE DRIVES                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-1                                                                                 |

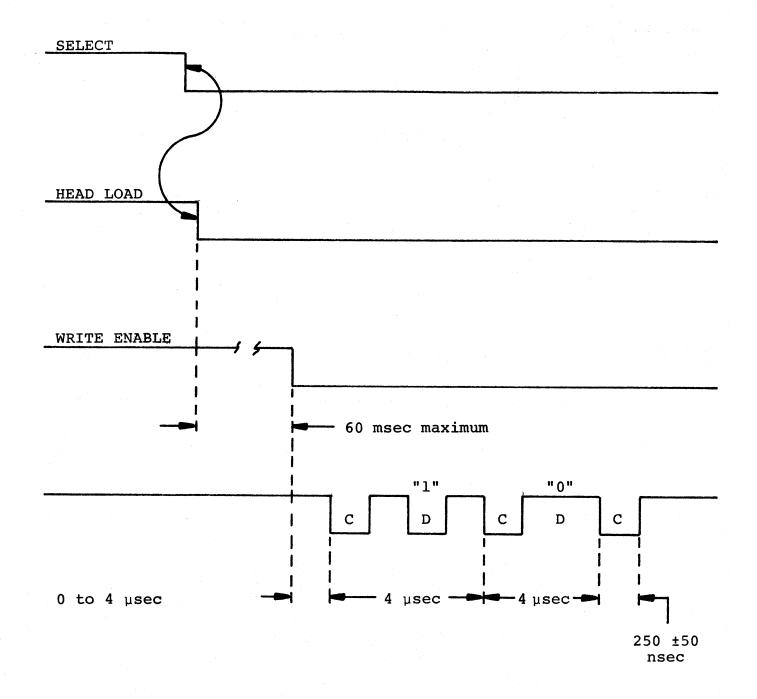

|         | 5.1 FUNCTIONAL DESCRIPTION 5.2 PERFORMANCE CHARACTERISTICS 5.2.1 RECORDING CHARACTERISTICS 5.2.2 BIT TRANSFER RATE 5.2.3 DATA CAPACITY 5.2.4 LATENCY TIME 5.2.5 POSITIONING CHARACTERISTICS 5.2.6 FDD START AND STOP TIME 5.2.7 ERROR RECOVERY 5.2.8 ENVIRONMENTAL LIMITS 5.2.9 WRITE PROTECT 5.3 INTERFACE SPECIFICATION 5.4 DISK CARTRIDGE STORAGE AND HANDLING 5.5 ADDITIONAL INFORMATION 5.5.1 CDC DRIVES 5.5.1.1 HEAD LOAD 5.5.1.2 DRIVE SELECT/READY | 5-3<br>5-4<br>5-4<br>5-4<br>5-5<br>5-5<br>5-6<br>5-6<br>5-7<br>5-17<br>5-18<br>5-18 |

|         | 5.5.1.3 "DAISY CHAIN" TERMINATION 5.5.2 SHUGART DRIVES                                                                                                                                                                                                                                                                                                                                                                                                     | 5-18<br>5-19<br>5-19<br>5-19<br>5-19                                                |

| 6       | 6.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 6-1                                                                               |

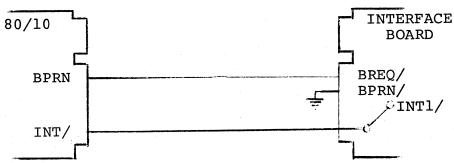

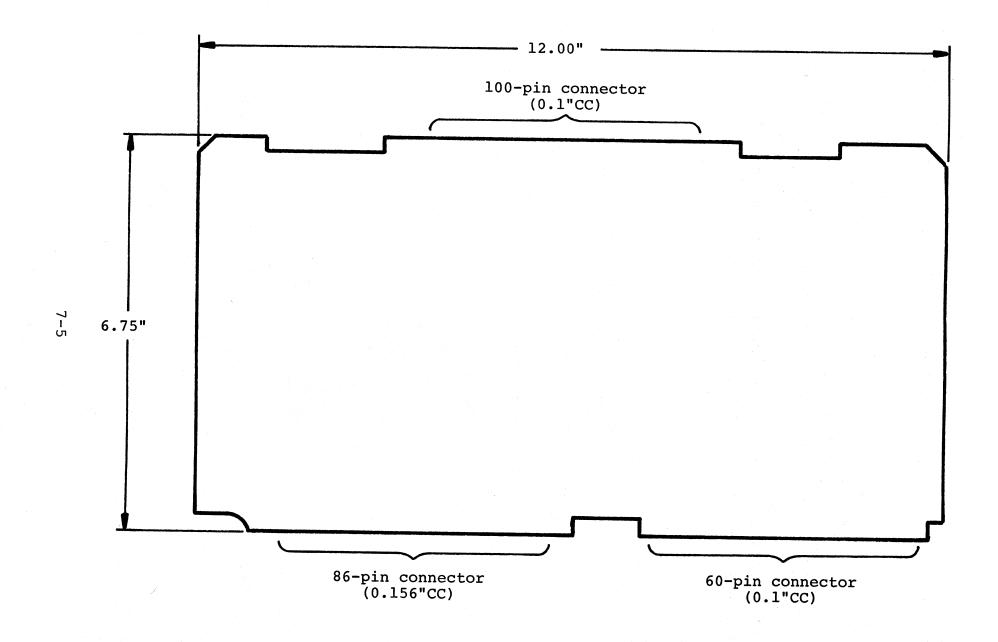

| 7       | UTILIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 7-1<br>. 7-2<br>. 7-3<br>. 7-6                                                    |

| 8       | OPERATING CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 8-1                                                                               |

# APPENDICES

| APPENDIX | TITLE                                       | PAGE NO.     |

|----------|---------------------------------------------|--------------|

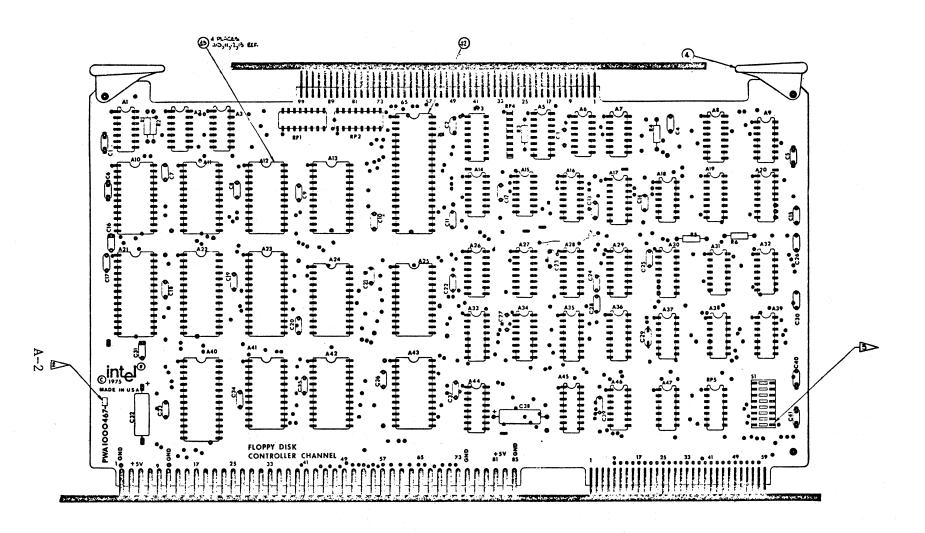

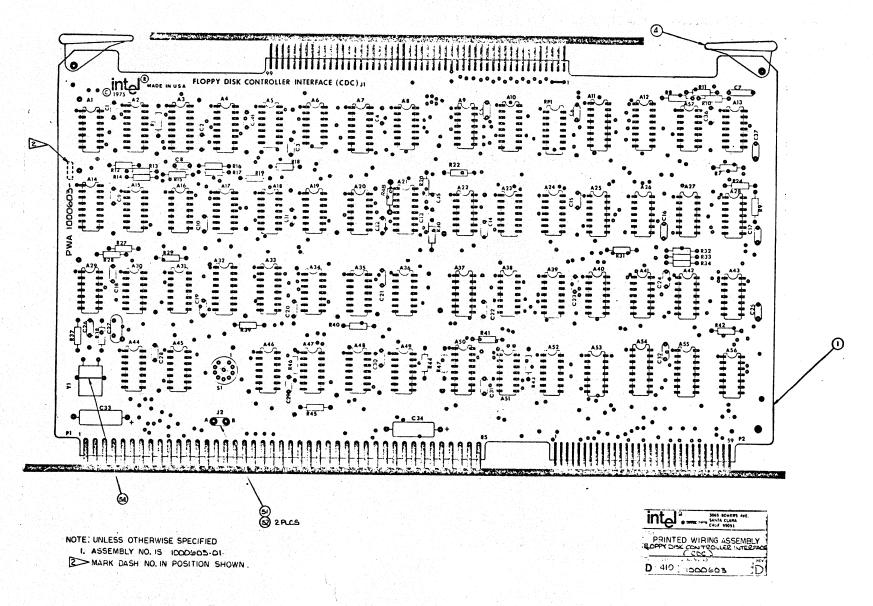

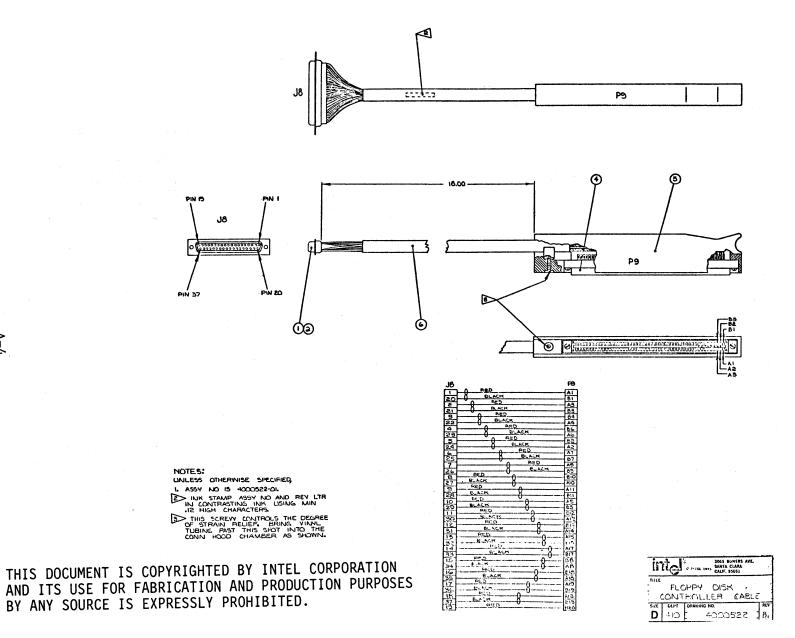

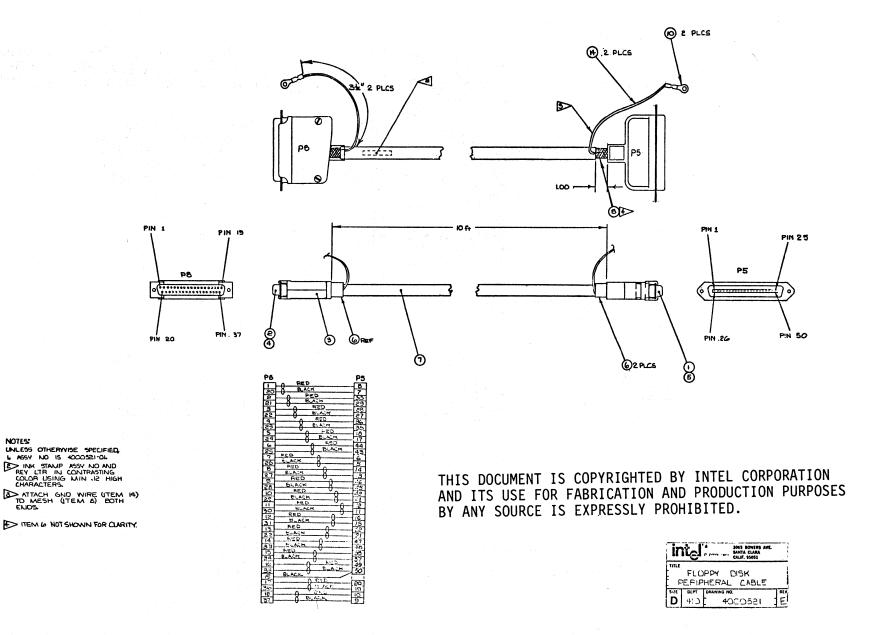

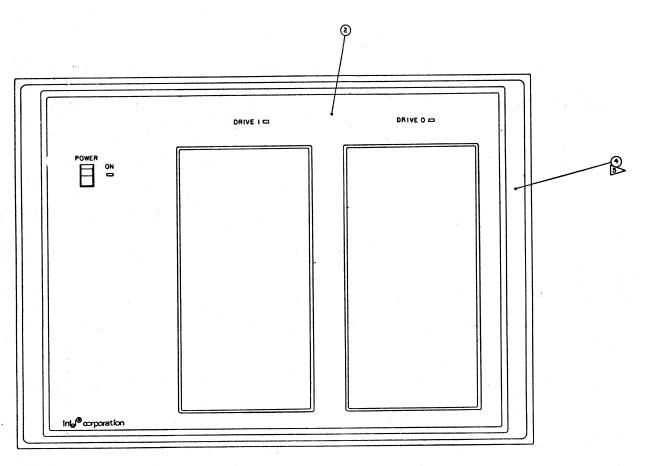

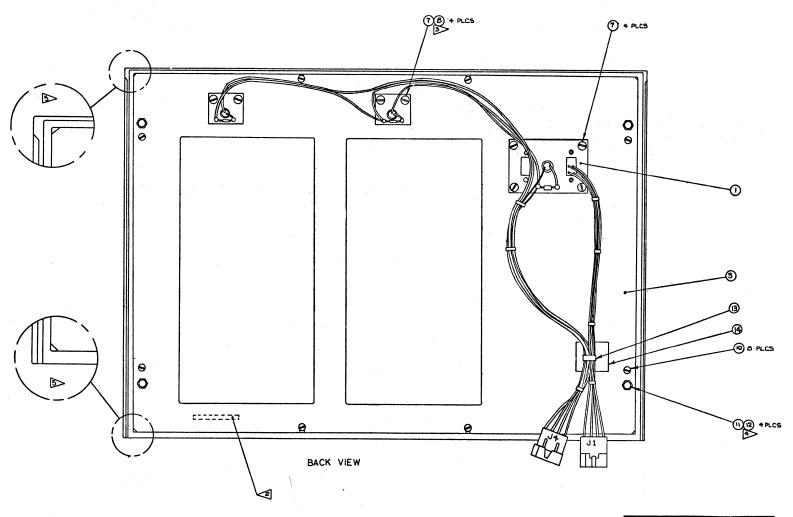

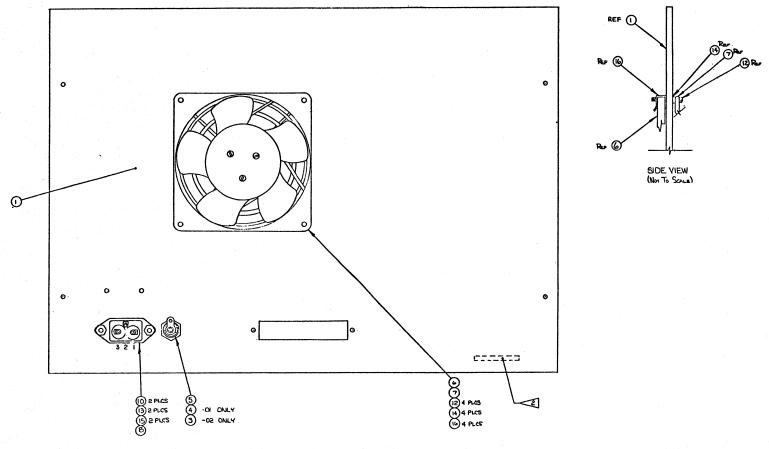

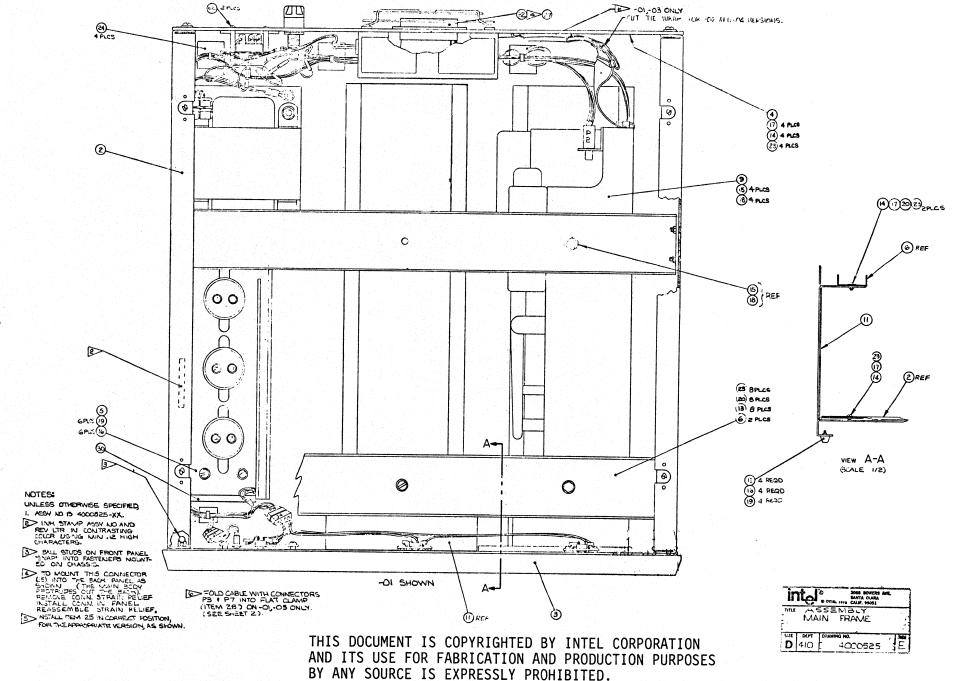

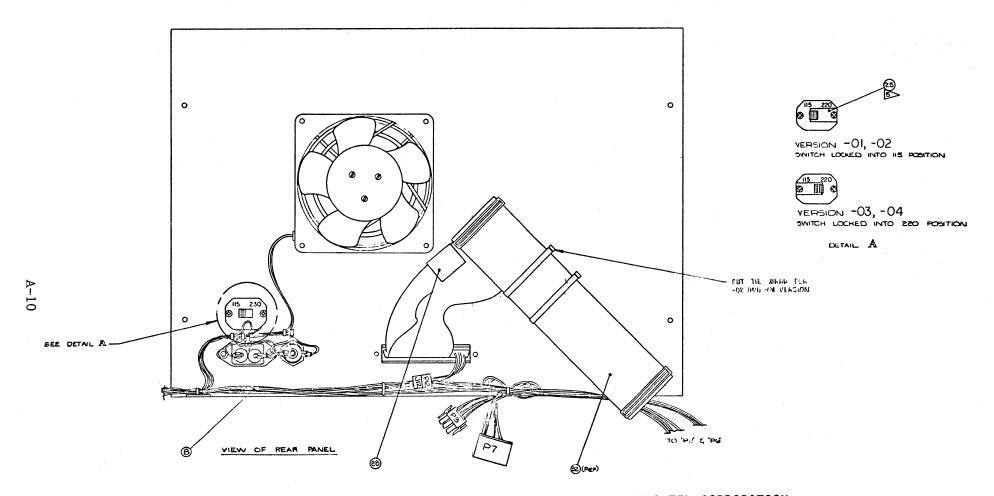

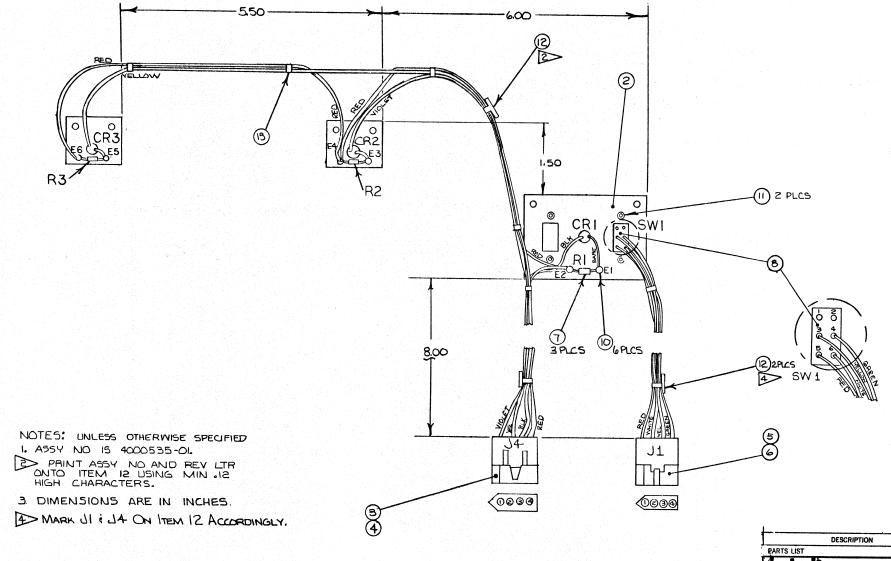

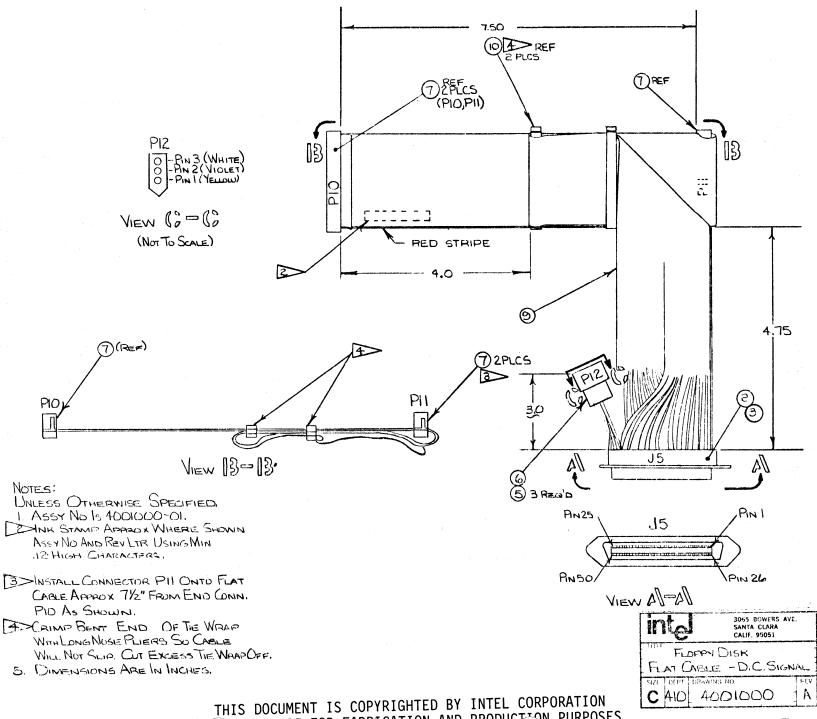

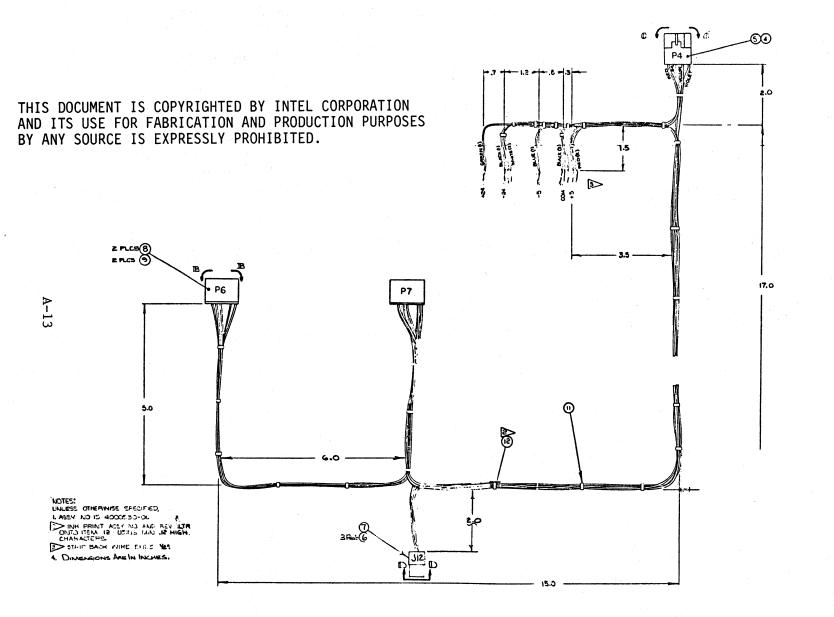

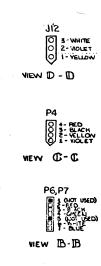

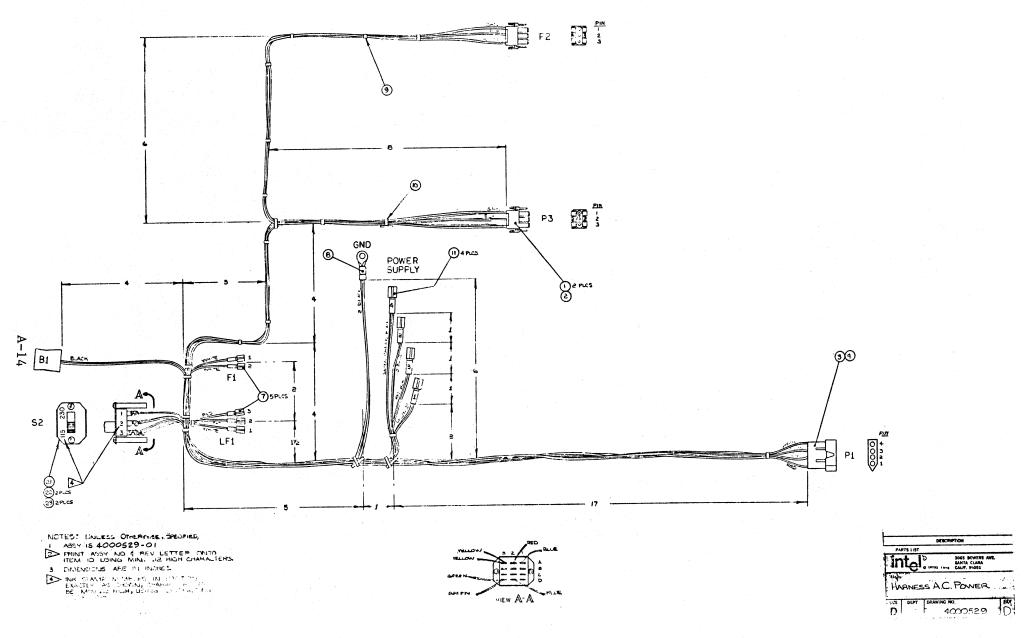

| A        | SBC 201, SBC 211, SBC 212 ASSEMBLY DRAWINGS | A-1          |

|          | CHANNEL BOARD ASSEMBLY DRAWING              | A-3<br>, A-5 |

| В        | FLEXIBLE DISKETTE CONTROLLER DRIVER EXAMPLE | B-1          |

# LIST OF ILLUSTRATIONS

| FIGURE | TITLE                                             | PAGE NO. |

|--------|---------------------------------------------------|----------|

| 1-1    | SBC DISKETTE SYSTEM BLOCK DIAGRAM                 |          |

| 1-2    | PHYSICAL DATA FORMAT                              |          |

| 1-3    | BYTE REPRESENTATION                               |          |

| 1-4    | DATA BYTES                                        |          |

| 1-5    | DATA BIT                                          |          |

| 1-6    | BIT CELL                                          |          |

| 1-7    | TRACK FORMAT                                      |          |

| 1-8    | INDEX ADDRESS MARK                                |          |

| 1-9    | ID ADDRESS MARK                                   |          |

| 1-10   | DATA ADDRESS MARK                                 |          |

| 1-11   | DELETED DATA ADDRESS MARK                         | . 1-15   |

| 2-1    | SECTOR FORMAT                                     |          |

| 2-2    | "DATA" ADDRESS MARK                               |          |

| 2-3    | "DELETED DATA" ADDRESS MARK                       |          |

| 2-4    | I/O PARAMETER BLOCK (IOPB) FORMAT                 | . 2-18   |

| 3-1    | CHANNEL BOARD: FUNCTIONAL BLOCK DIAGRAM           | 3-3      |

| 3-2    | 3001 MICROPROGRAM CONTROL UNIT: FUNCTIONAL BLOCK  |          |

|        | DIAGRAM                                           | 3-10     |

| 3-3    | 3002 CENTRAL PROCESSING ELEMENT: FUNCTIONAL BLOCK | ζ        |

|        | DIAGRAM                                           |          |

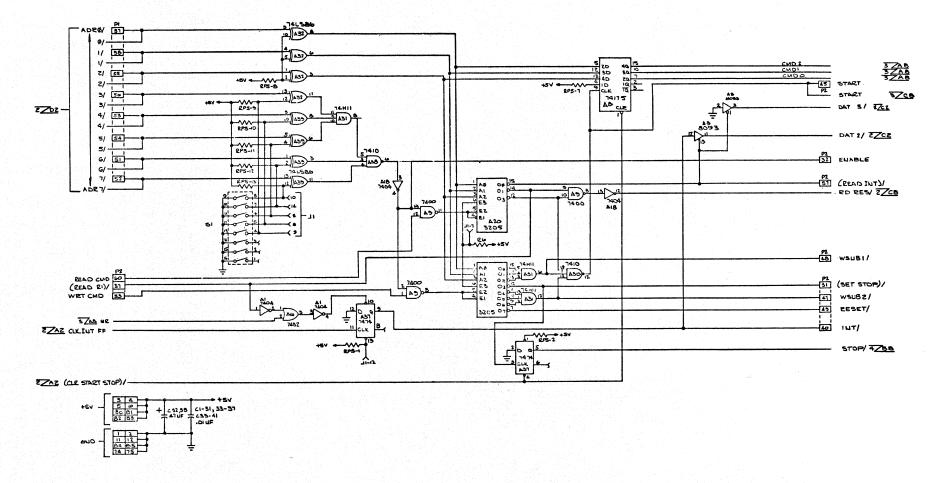

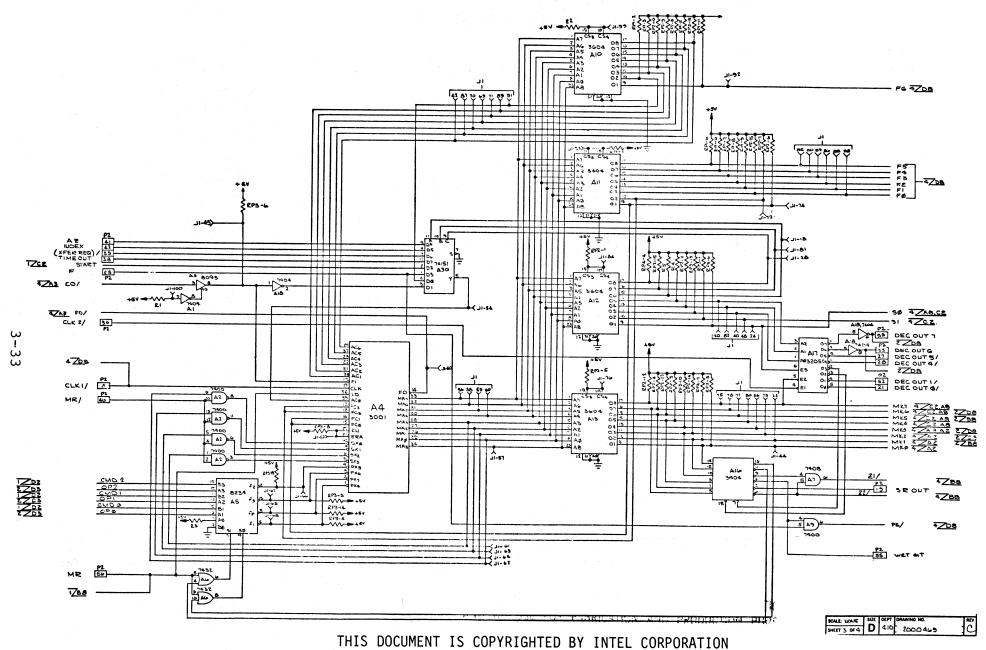

| 3-4    | SCHEMATIC DRAWING: CHANNEL BOARD                  | 3-31     |

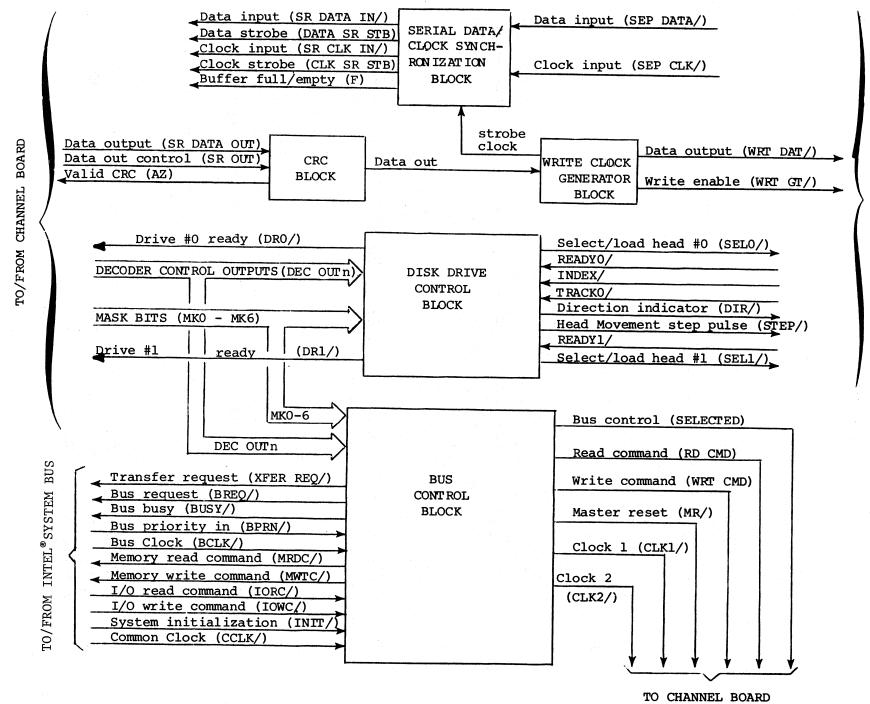

| 4-1    | INTERFACE BOARD: FUNCTIONAL BLOCK DIAGRAM         | 4-3      |

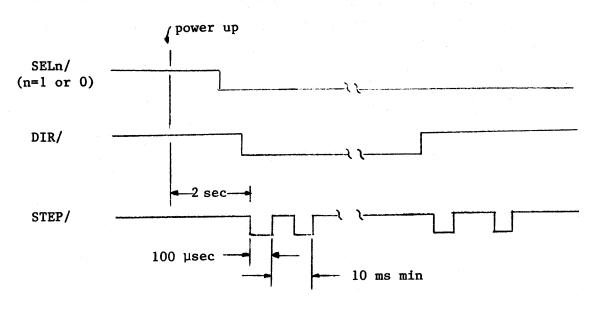

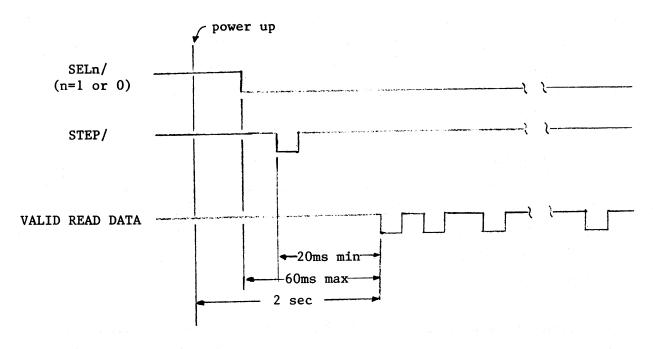

| 4-2    | HEAD MOVEMENT CONTROL TIMING                      |          |

| 4-3    | READ INITIATE TIMING                              |          |

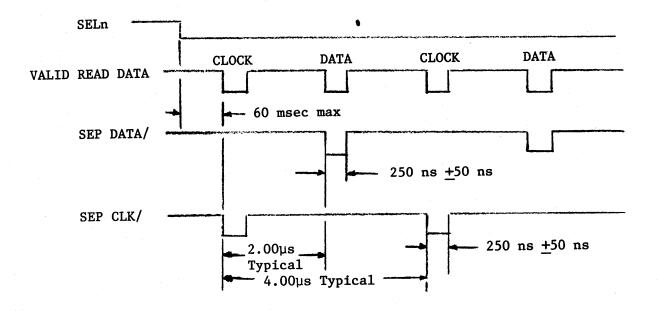

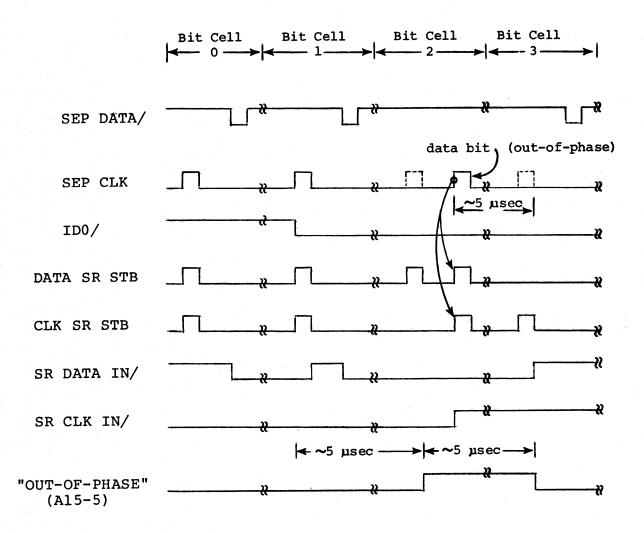

| 4-4    | READ SIGNAL TIMING                                |          |

| 4-5    | TIMING FOR ADDRESS MARK DETECTION                 |          |

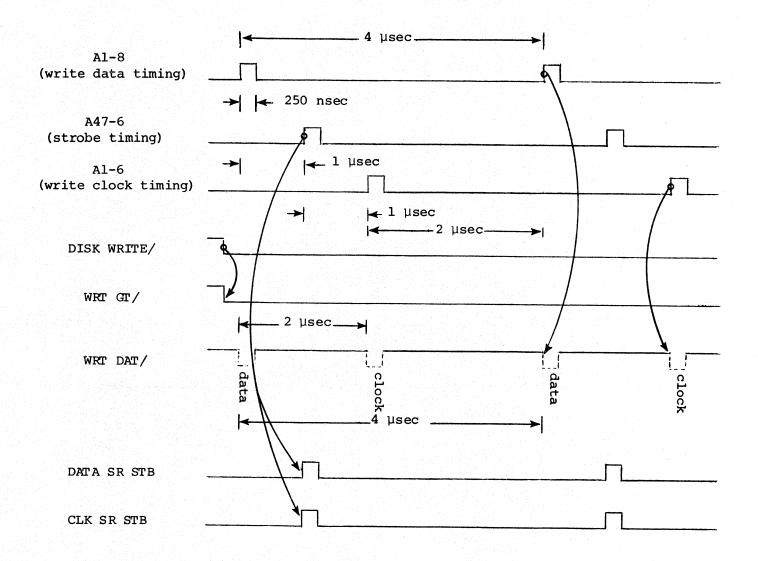

| 4-6    | WRITE CLOCK TIMING                                |          |

| 4-7    | WRITE INITIATE TIMING                             |          |

| 4-8    | BUS CONTROL TIMING                                |          |

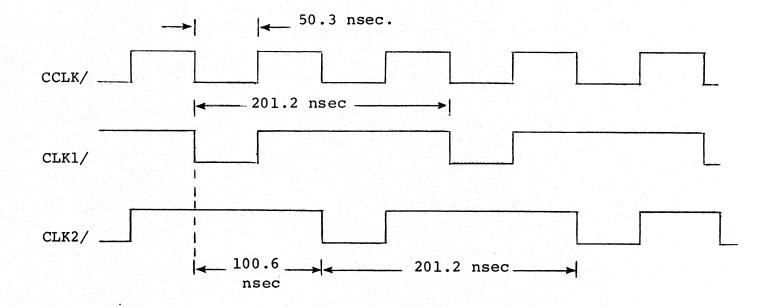

| 4-9    | CLK1/ AND CLK2/TIMING                             |          |

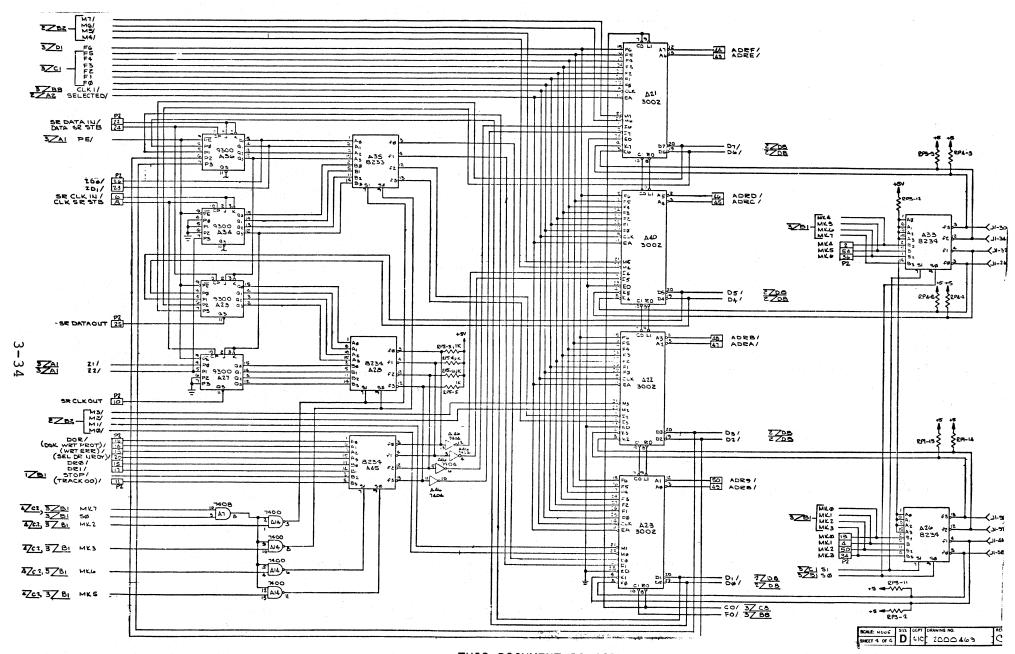

| 4-10   | SCHEMATIC DRAWING: INTERFACE BOARD                |          |

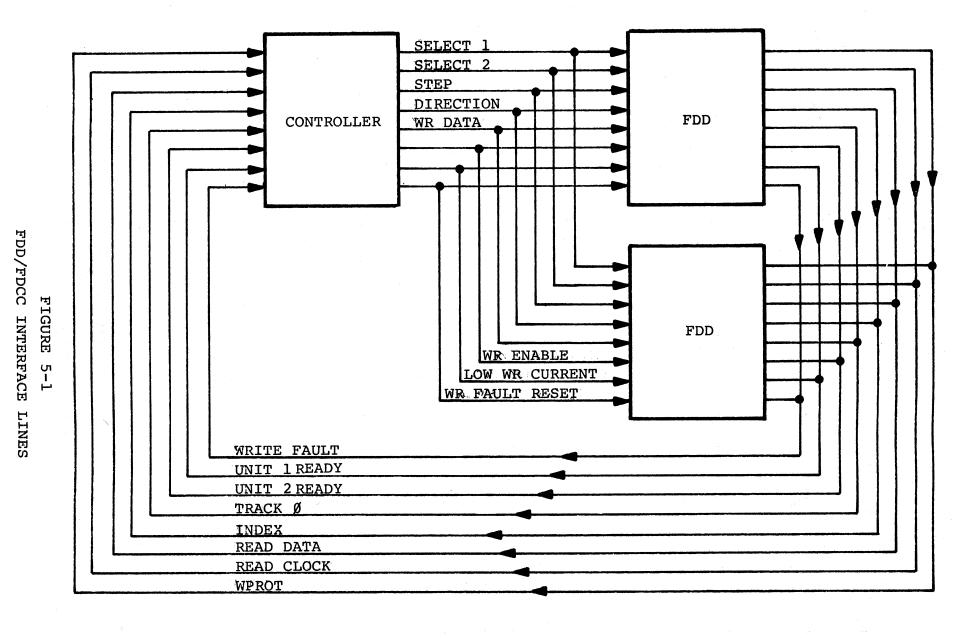

| 5-1    | FDD/FDCC INTERFACE LINES                          | 5-8      |

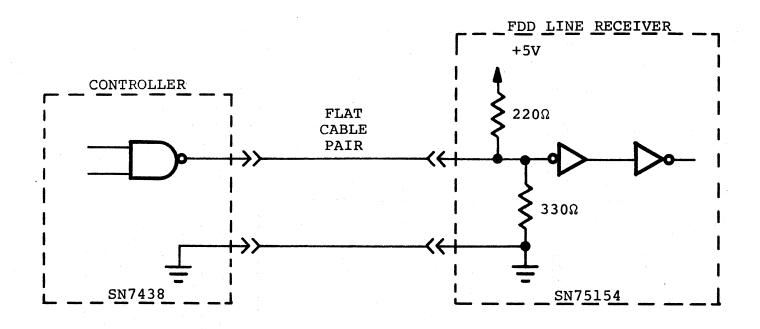

| 5-2    | FDD DRIVER/RECEIVER CIRCUITS                      | 5-9      |

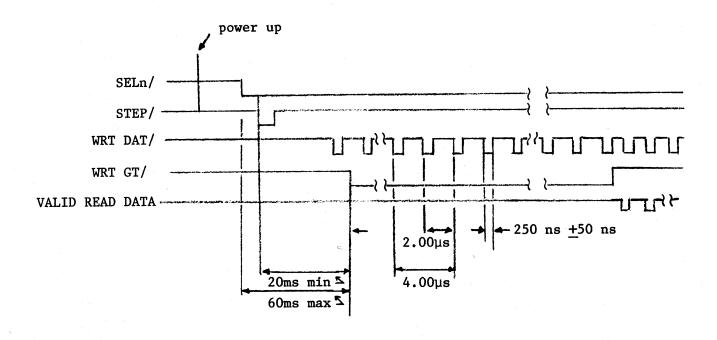

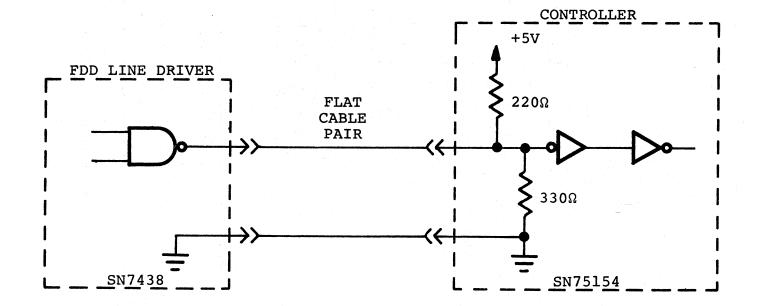

| 5-3    | WRITE DATA TIMING                                 | 5-12     |

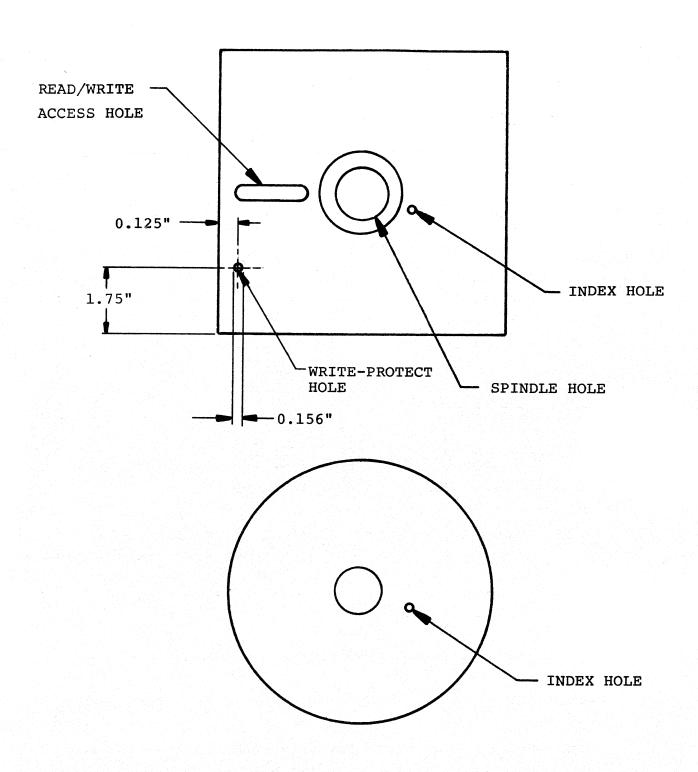

| 5-4    | FLEXIBLE DISK CARTRIDGE                           | 5-13     |

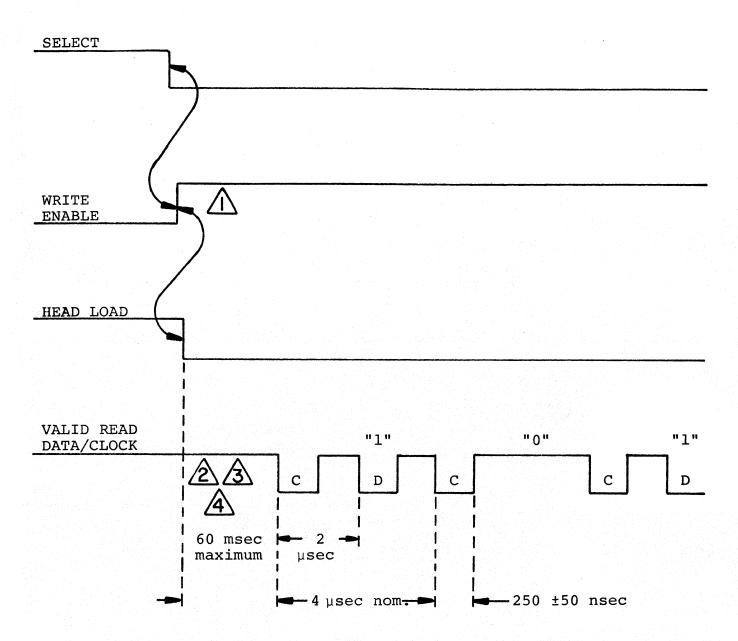

| 5-5    | READ DATA TIMING                                  |          |

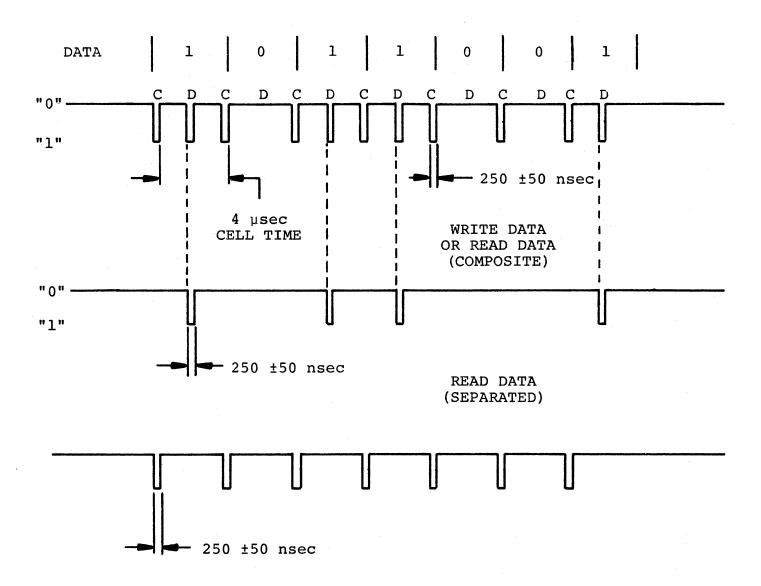

| 5-6    | SINGLE DENSITY DATA TIMING                        | 5-16     |

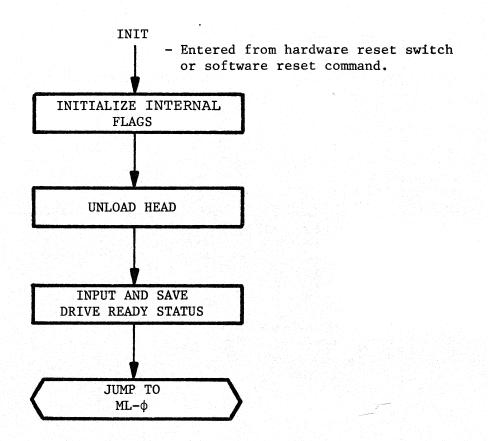

| 6-1    | INITIALIZATION                                    | 6-3      |

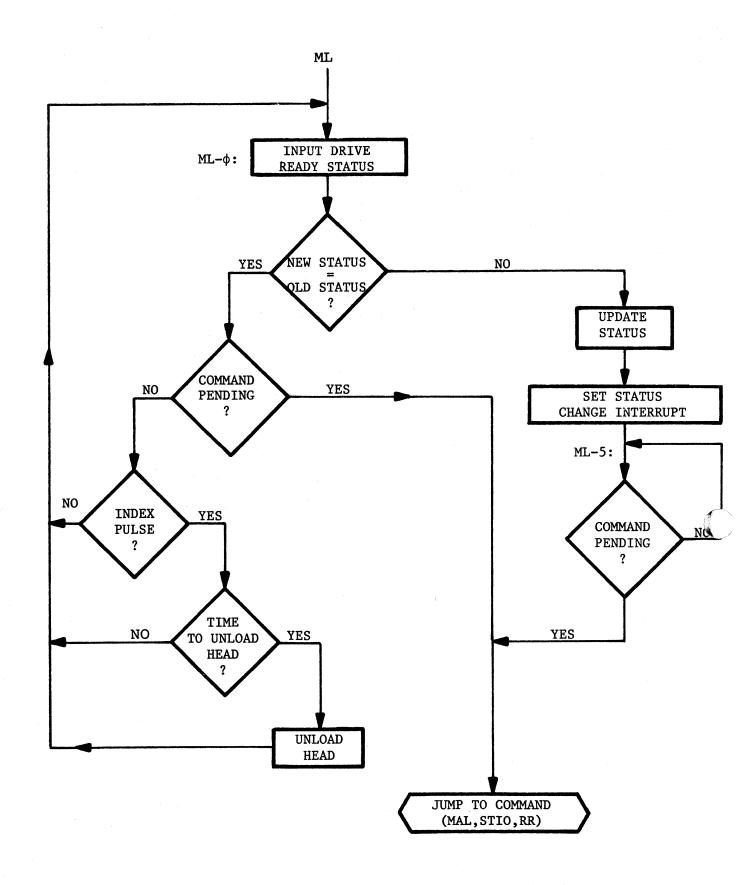

| 6-2    | MAINLINE                                          | 6-4      |

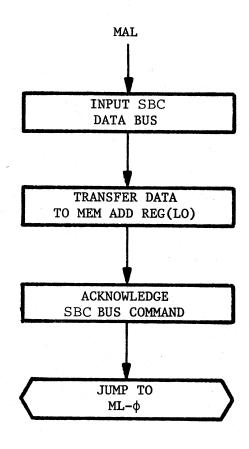

| 6-3    | LOAD MA LOWER                                     |          |

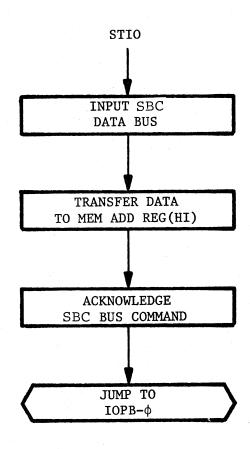

| 6-4    | LOAD MA UPPER AND START I/O                       |          |

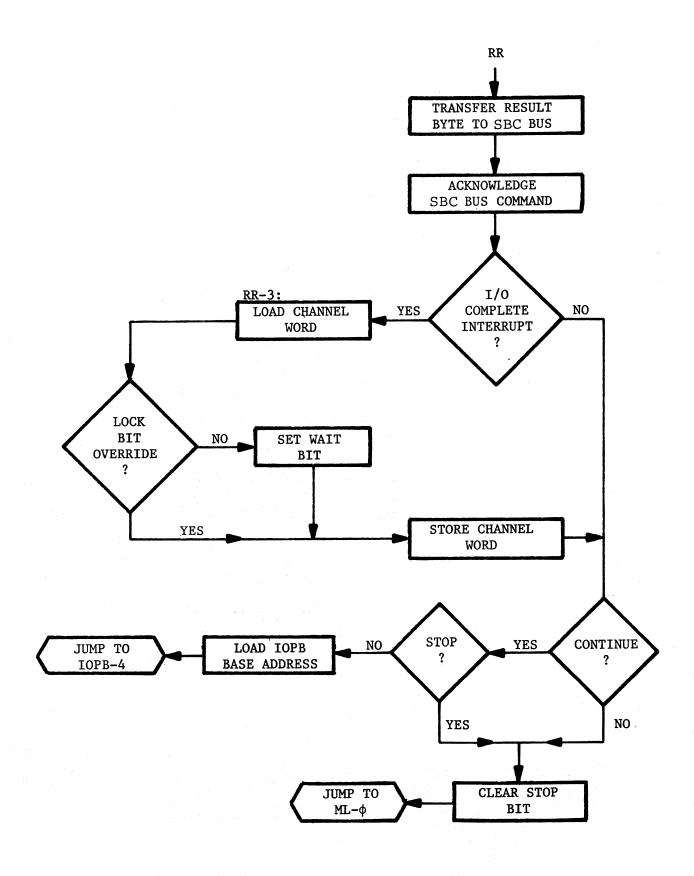

| 6-5    | READ RESULT BYTE                                  |          |

# LIST OF ILLUSTRATIONS - (Continued)

| FIGURE       | TITLE                                          | PAGE NO. |

|--------------|------------------------------------------------|----------|

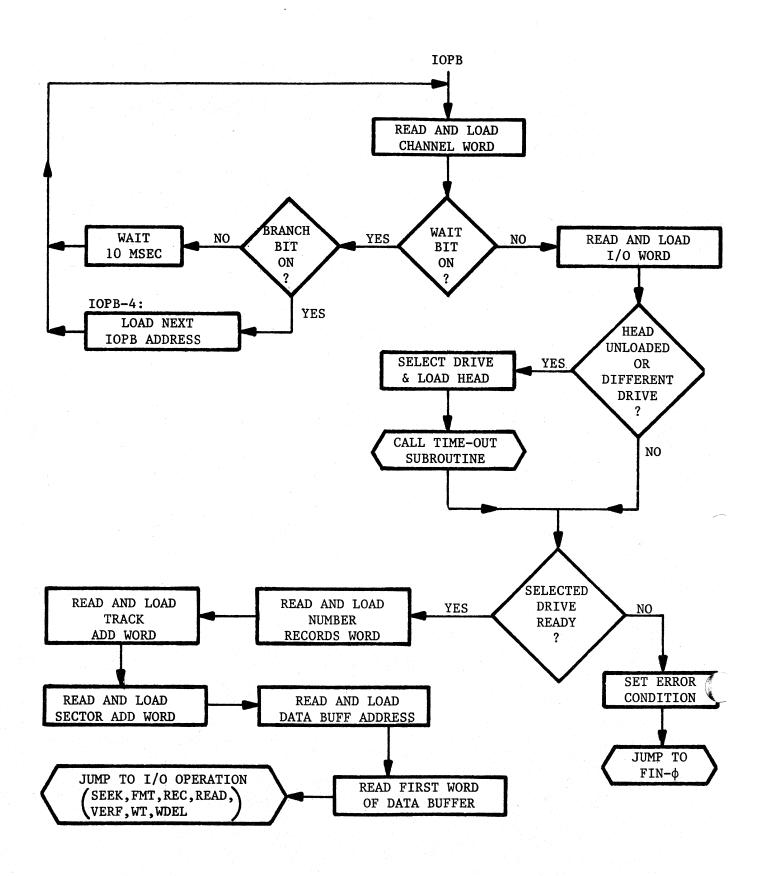

| 6-6<br>6-7   | IOPB LOADER/OP DECODE                          | 6-8      |

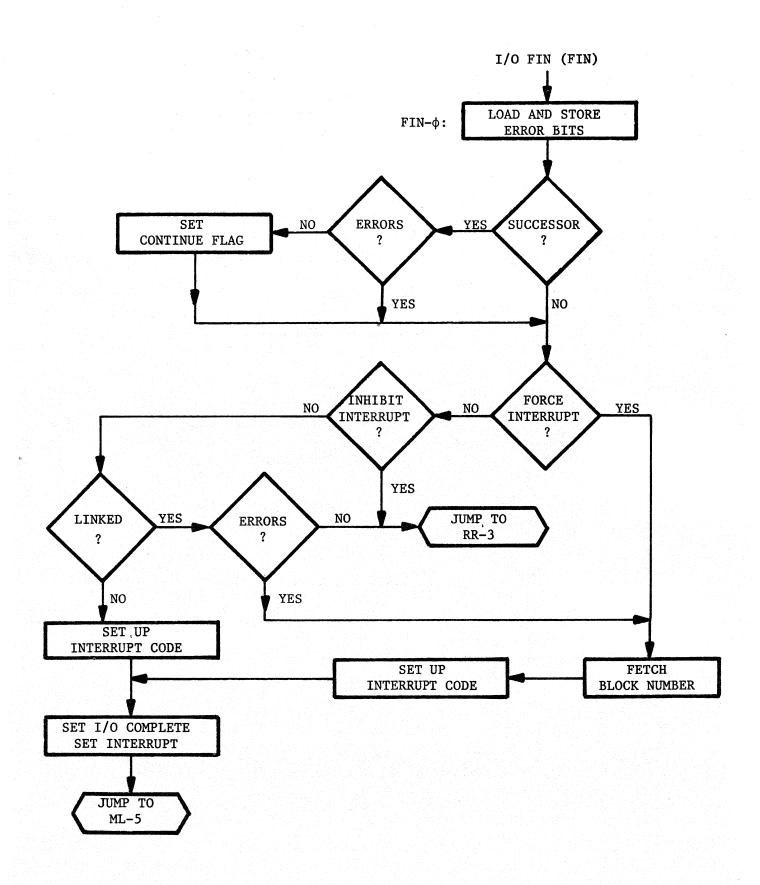

| 6-8          | I/O FINISH                                     | 6-9      |

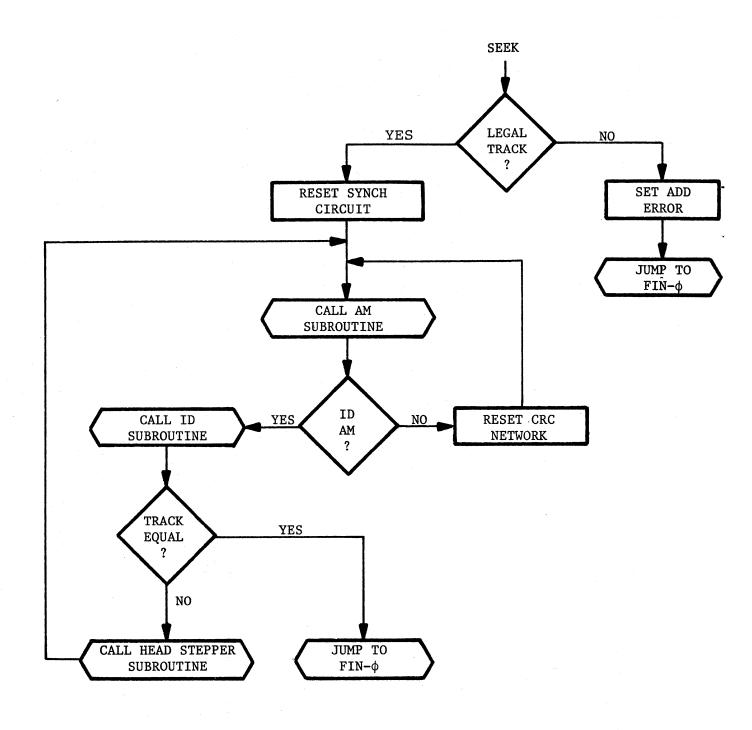

| 6-8<br>6-9   | SEEK                                           | 6-10     |

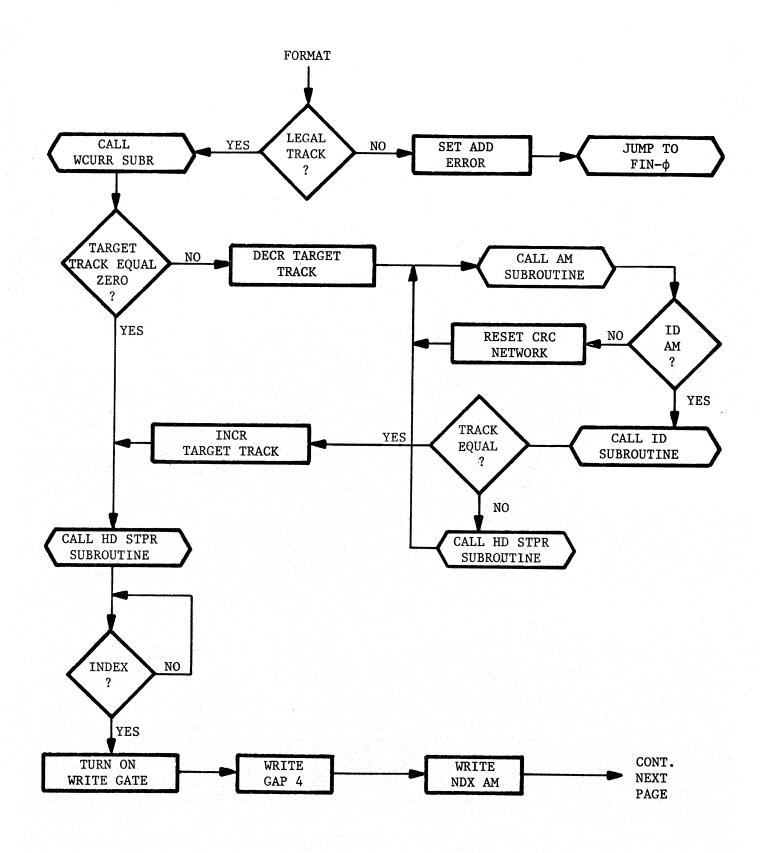

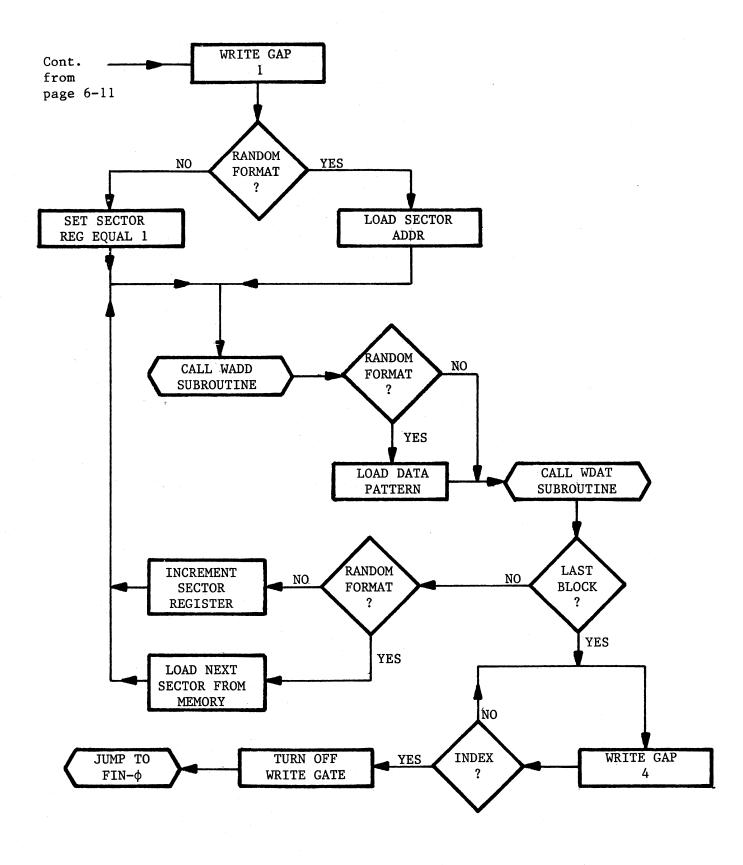

| 6-10         | FORMAT                                         | 6-11     |

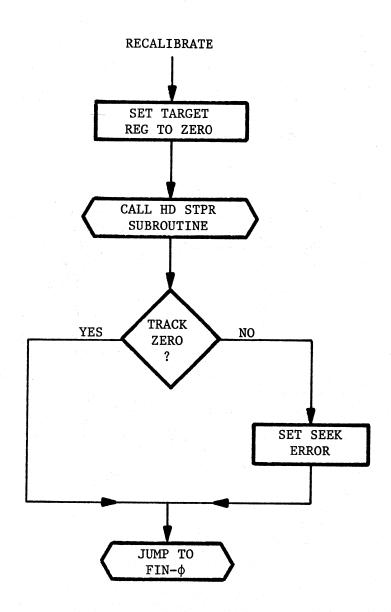

| 6-11         | RECALIBRATE                                    | 6-13     |

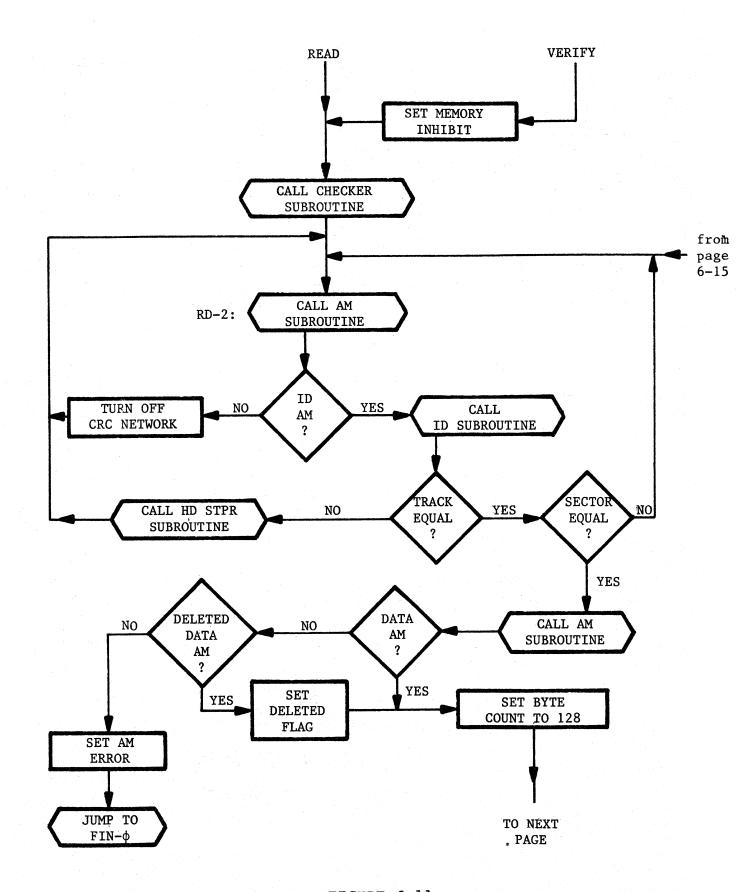

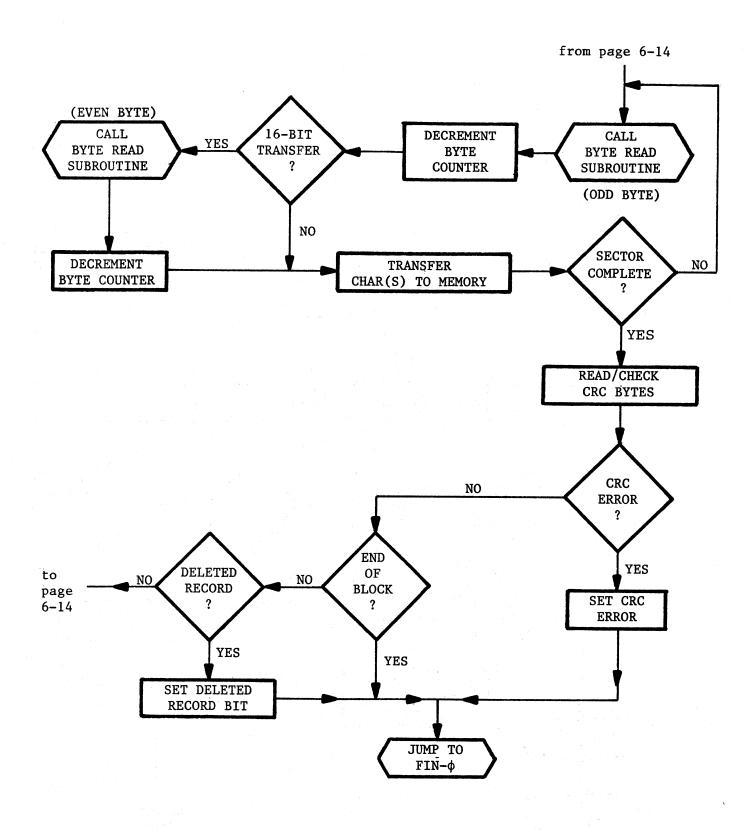

| 6-12         | VERIFY/READ                                    | 6-14     |

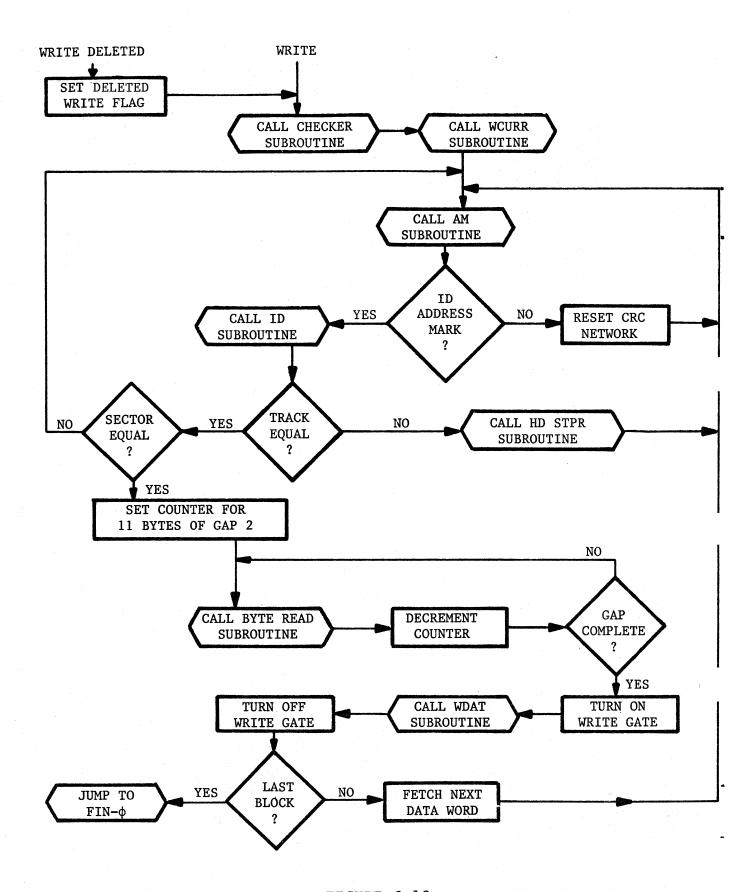

| 6-13         | WRITE DELETED/WRITE                            |          |

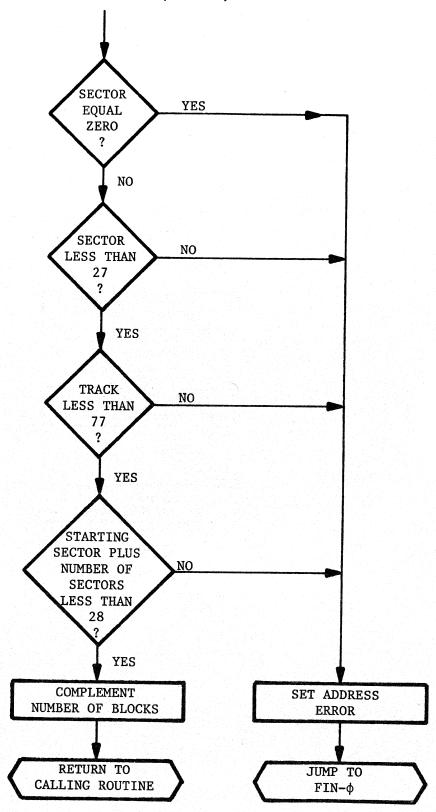

| 6-14         | ADDRESS PARAMETER CHECKER                      |          |

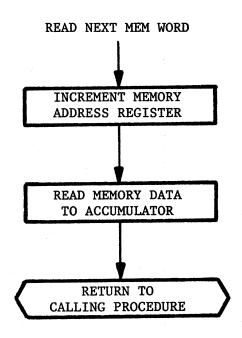

| 6-14<br>6-15 | READ NEXT MEMORY WORD                          |          |

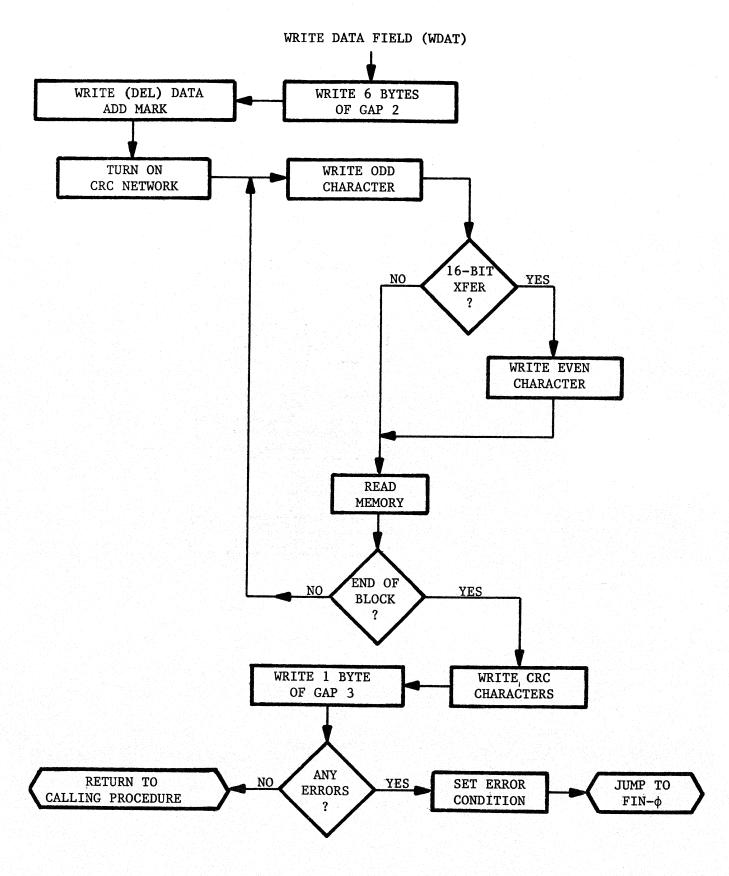

| 6-16         | WRITE DATA FIELD                               |          |

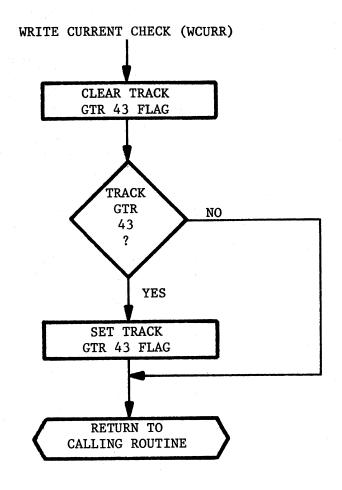

| 6-17         | WRITE CURRENT CHECK                            |          |

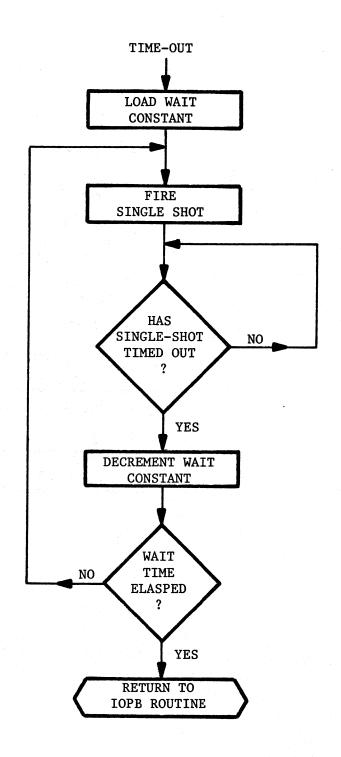

| 6-17<br>6-18 |                                                |          |

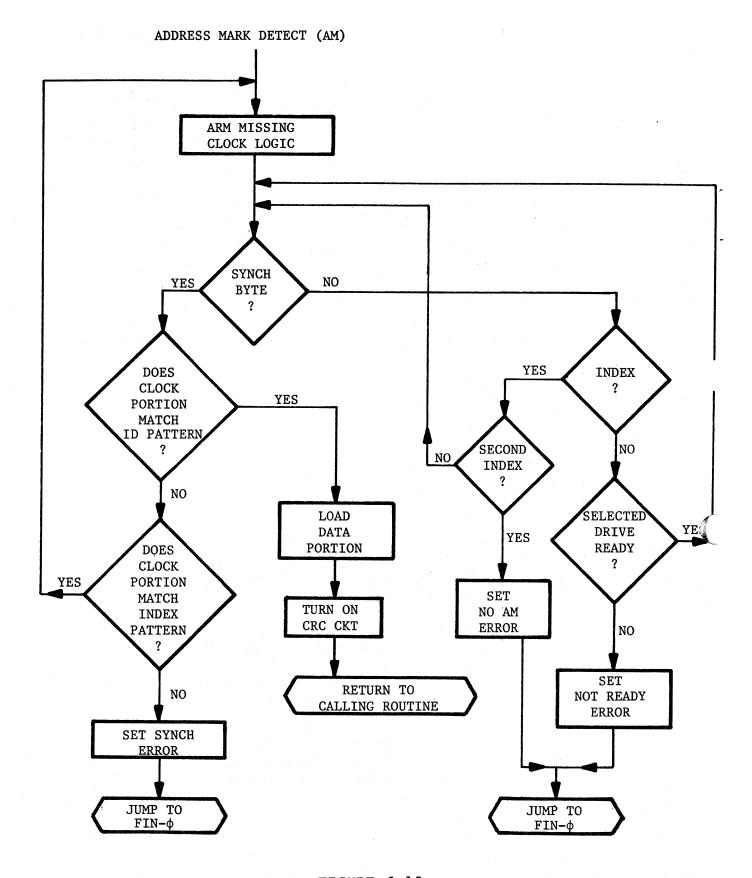

| 6-19         | ADDRESS MARK DETECT                            |          |

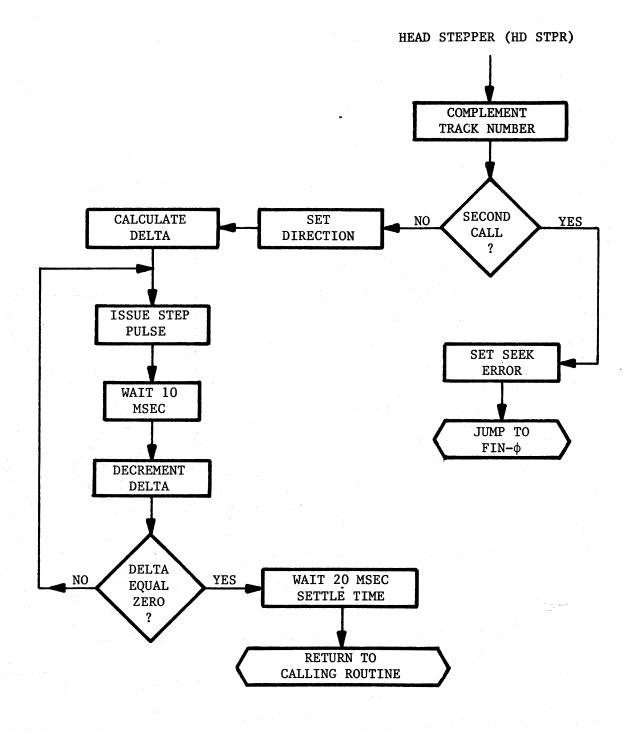

| 6-20         | HEAD STEPPER                                   |          |

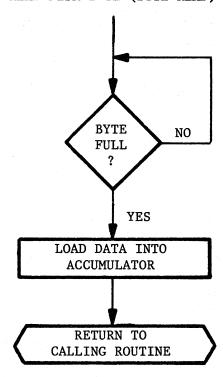

| 6-21         | READ DISK BYTE                                 |          |

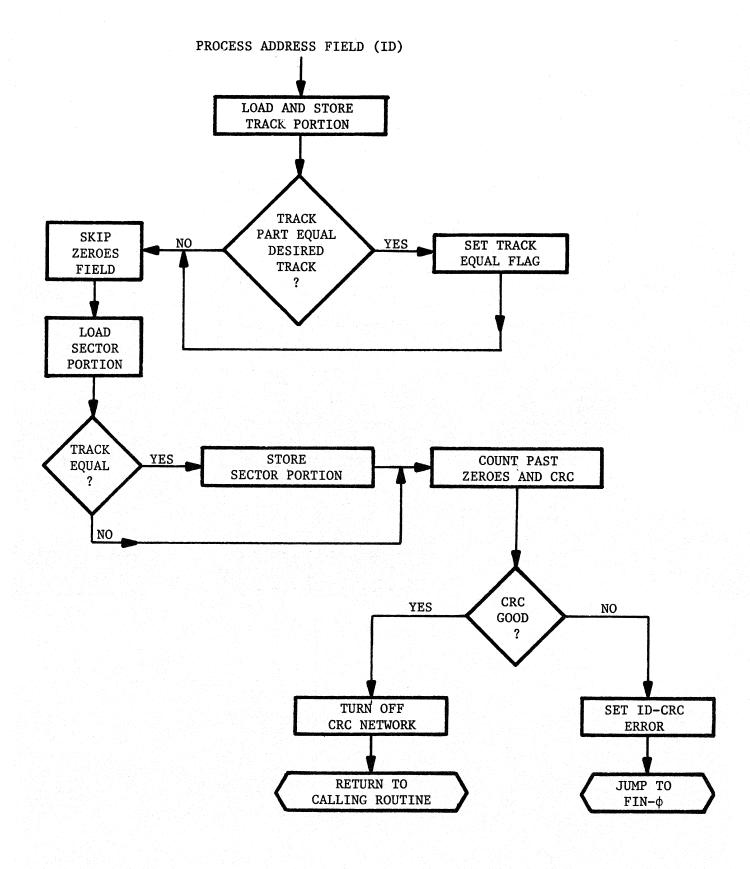

| 6-22         | PROCESS ADDRESS FIELD                          |          |

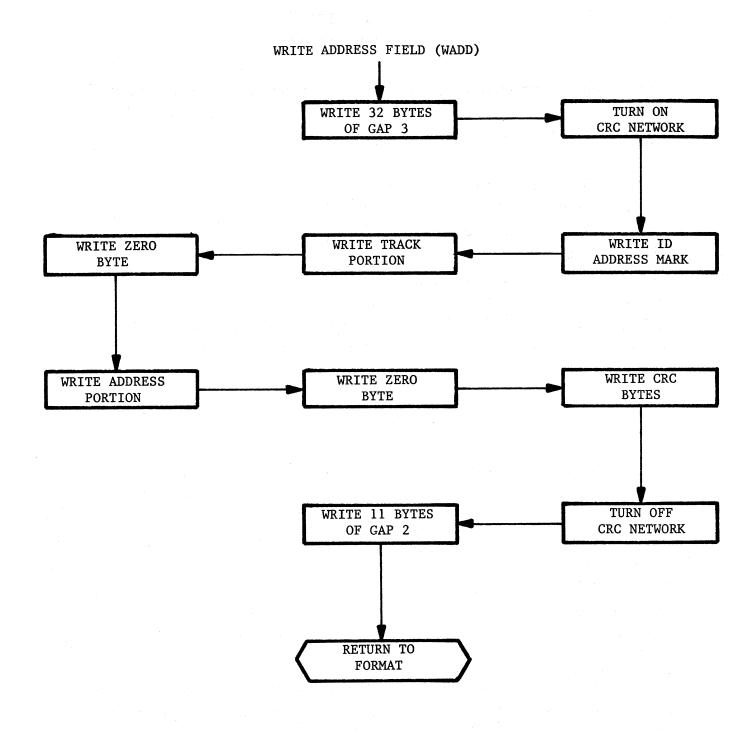

| 0-22         | WRITE ADDRESS FIELD                            | 6-26     |

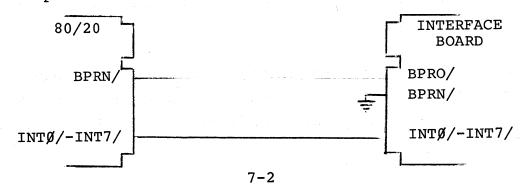

| 7-1          | CONNECTORS ON THE CHANNEL AND INTERFACE BOARDS | 7-5      |

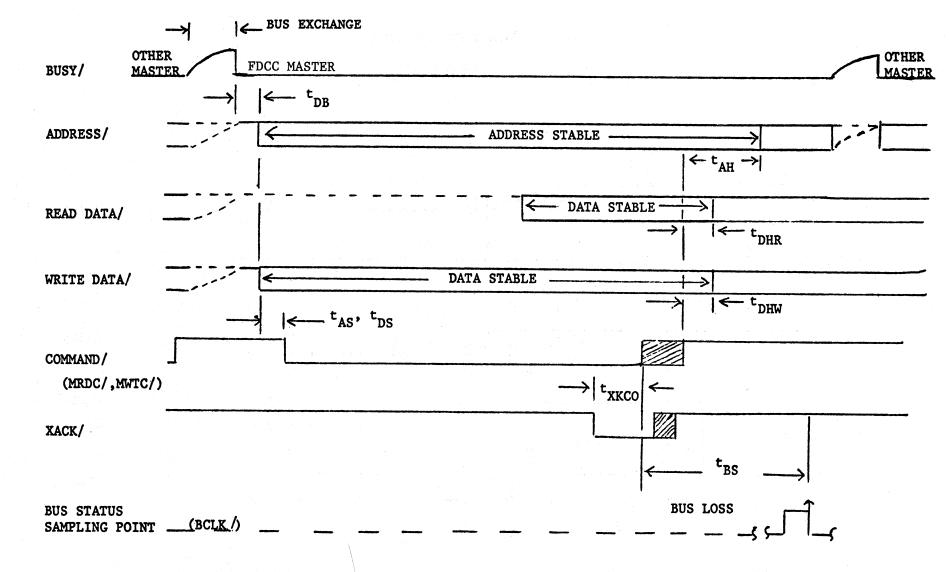

| 8-1          | SLAVE COMMAND TIMING - FDCC                    | 8-3      |

| 8-2          | BUS EXCHANGE TIMING                            | 8-4      |

| 8-3          | MASTER COMMAND TIMING                          | 8-5      |

| 8-4          | TIMING DIAGRAM: STEP PULSE AND SETTLING TIME   | 8-7      |

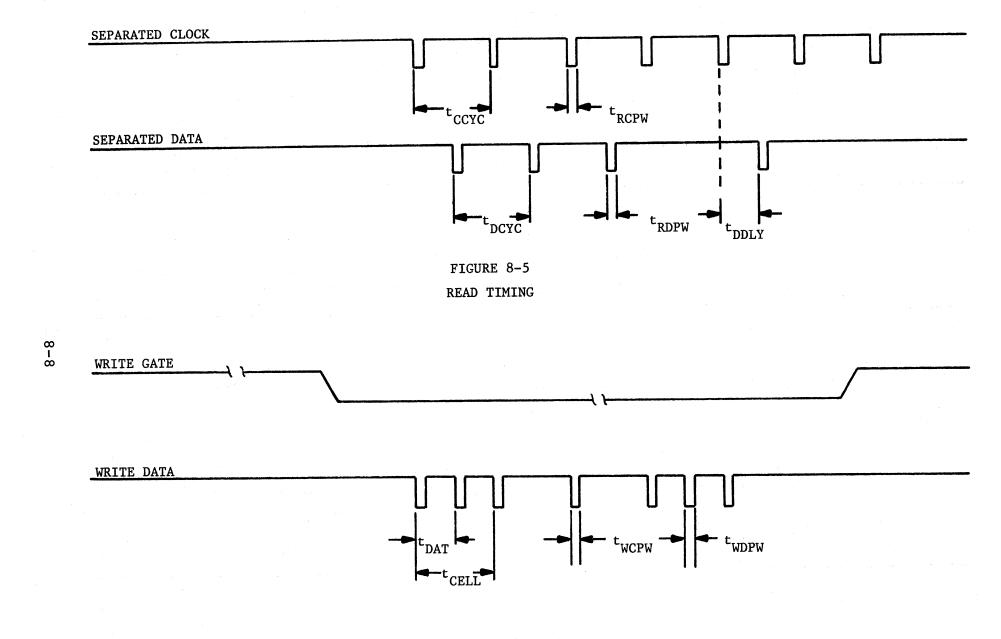

| 8-5          | READ TIMING                                    |          |

| 8-6          | WRITE TIMING                                   |          |

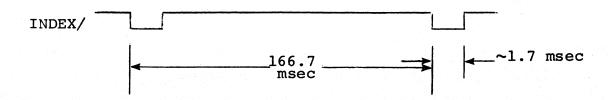

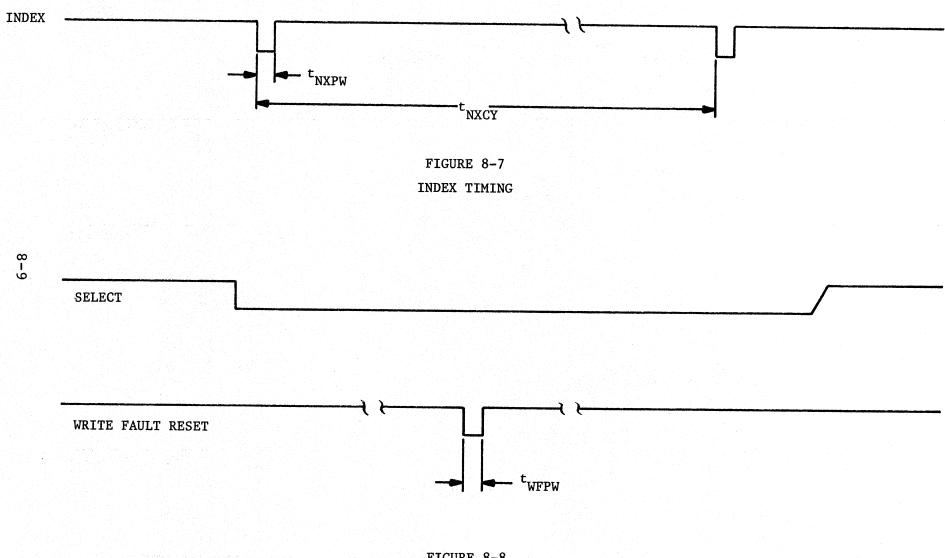

| 8-7          | INDEX TIMING                                   | 8-9      |

| 8-8          | WRITE FAULT RESET TIMING                       |          |

|              |                                                |          |

# LIST OF TABLES

| TABLE      | TITLE                                                            | PAGE NO.     |

|------------|------------------------------------------------------------------|--------------|

| 1-1        | DISKETTE DRIVE PERFORMANCE SPECIFICATIONS                        | 1-4          |

| 2-1        | INTERRUPT CONTROL BITS                                           | 2-19         |

| 3-1<br>3-2 | ACO INPUT SELECTION                                              |              |

| 3-3        | CONTROL PULSES AND LEVELS GENERATED BY MICROPROGRAM              |              |

| 3-5        | I-BUS SELECTION BY MASK FIELD BITS                               | 3-22         |

|            | PIN LIST: P1 BUS CONNECTOR                                       |              |

| 4-1<br>4-2 | PIN LIST: P1 BUS CONNECTOR                                       | 4-30<br>4-31 |

| 4-3        | J1 DRIVE CONNECTOR                                               |              |

| 8-1        | DISKETTE CONTROLLER SBC BUS AC CHARACTERISTICS                   | 8-2          |

| 8-2        | DISKETTE CONTROLLER DRIVE INTERFACE AC CHARACTERISTICS           | 8-6          |

| 8-3        | DISKETTE CONTROLLER DC CHARACTERISTICS (SBC)                     | 8-11         |

| 8-4        | DISKETTE CONTROLLER DC CHARACTERISTICS (DRIVE/DISPLAY INTERFACE) | 8-14         |

|            |                                                                  |              |

# CHAPTER 1 INTRODUCTION

The SBC 211/212 Diskette Hardware System provides a bulk storage capability for Intel's OEM computer systems. The SBC 211 and 212 systems include an intelligent controller (the SBC 201) and up to two diskette drives (refer to Section 1.1). Each drive provides 2,050,048 user-accessible data bits of storage with a data transfer rate of 250,000 bits/second. The controller has been implemented with Intel's powerful Series 3000 Bipolar Computing Elements. The controller provides an interface to the Intel System bus (Multibus) as well as supporting the two diskette drives. The controller records all data in the IBM soft-sectored format, described in Section 1.2.

#### 1.1 SYSTEM OVERVIEW

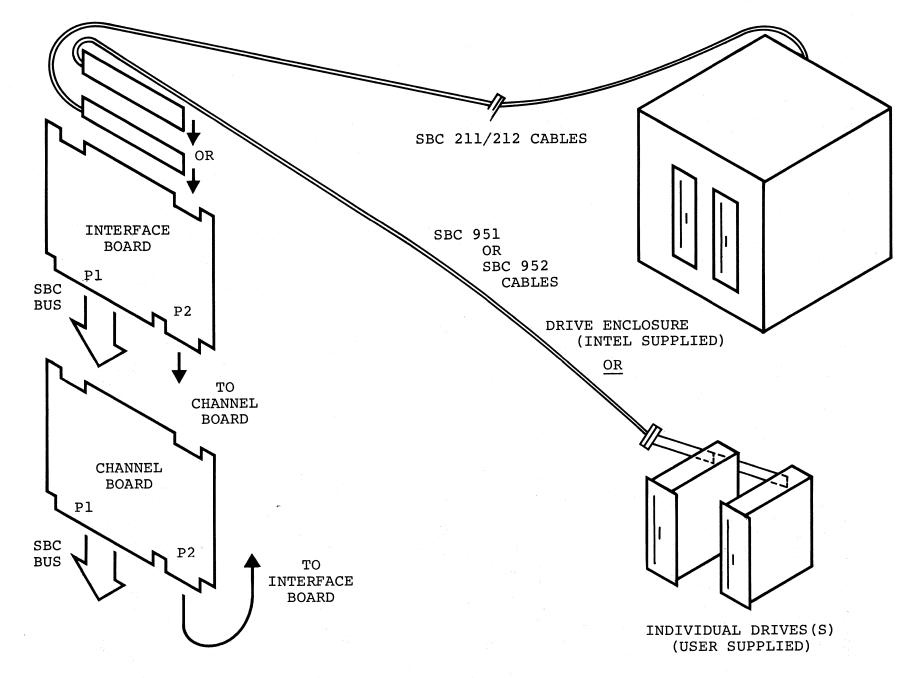

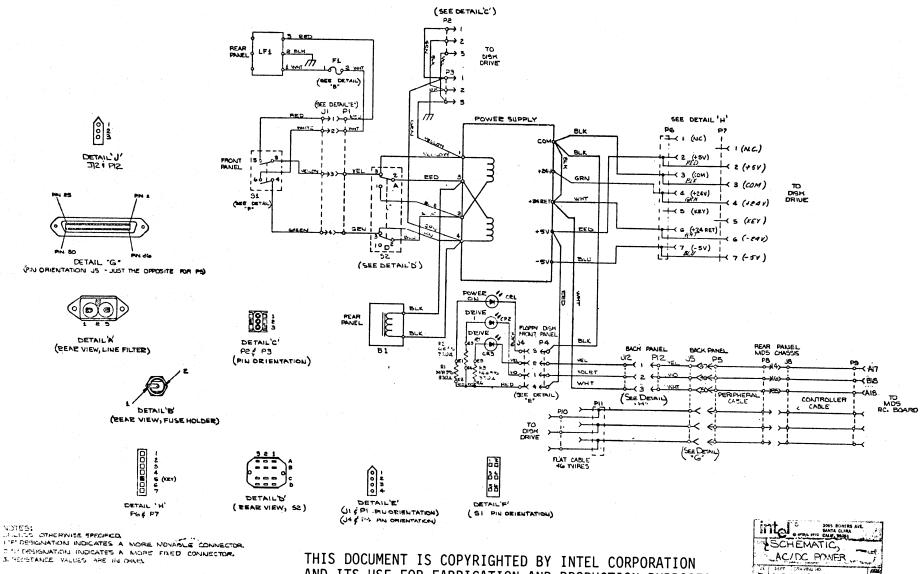

In addition to one or two diskette drives, their enclosure and power supplies, the Diskette System includes the Channel Board and the Interface Board. These two printed circuit boards constitute what we refer to as the SBC 201 Diskette Controller. The controller plugs into our standard cardcage or your custom backplane. Each of the system components is shown in Figure 1-1, and described in the following paragraphs:

The Channel Board is the primary control module within the Diskette System. The Channel Board receives, decodes and responds to channel commands from a Central Processor Unit (CPU) in the computer system. The Channel Board can access common system memory to determine the particular diskette operations to be performed and to fetch the parameters required for the successful completion of the specified operations. The Channel Board also monitors Diskette System status and error conditions, and organizes these indications into "result type" and "result byte" words that can be read by the OEM computer.

FIGURE 1-1

SBC DISKETTE SYSTEM BLOCK DIAGRAM

The control functions of the Channel and Interface Boards are provided by an 8-bit microprogrammed processor, implemented with Intel's Series 3000 Bipolar Computing Elements. The 8-bit controller includes four 3002 Central Processing Elements (2-bit slice per CPE), a 3001 Microprogram Control Unit and 512 x 32 bits of 3604 programmable-read-only-memory (PROM) which stores the microprogram. The processing and control capabilities of the Diskette system are achieved by execution of the microprogram.

The <u>Interface Board</u> provides the diskette controller with a means of communicating with the diskette drives, as well as with the system bus. Under control of the microprogram executed from the Channel Board, the Interface Board generates those signals which cause the read/write head on the selected drive to be loaded (i.e., to come in contact with the diskette platter), then cause the head to move to the proper track. The Interface Board accepts the data being read off the diskette, interprets certain synchronizing bit patterns, checks the validity of the data using a cyclic redundancy check (CRC) polynomial, and passes the data to the Channel Board.

During write operations, the Interface Board outputs the data and clock bits to the selected drive at the proper times. It also generates CRC characters which are appended to the data; this allows the data to be verified when it is subsequently read.

When the diskette controller requires access to the common system memory, the Interface Board requests and maintains master control of the system bus, and generates the appropriate memory command.

When a CPU in the Intel®OEM computer system issues a channel command to the Diskette System, the Interface Board acknowledges the command as required by system bus protocol.

Each <u>diskette drive</u> consists of read/write and control electronics (on a single printed circuit board), drive mechanism, read/write head, track positioning mechanism and the removable diskette platter. These components interact to perform the following functions:

- Interpret and generate control signals.

- Move read/write head to selected track.

- Read and write data

Table 1-1 lists the performance characteristics for each diskette drive.

TABLE 1-1

DISKETTE DRIVE PERFORMANCE SPECIFICATIONS

| Capacity (formatted) | Per Disk - 256,256 bytes |

|----------------------|--------------------------|

|                      | Per Track - 3,328 bytes  |

| Data Transfer Rate:  | 250 kilobits/second      |

| Access Time:         | Track to Track - 10 ms   |

|                      | Settling Time - 10 ms    |

| Average Access Time: | 260 ms                   |

| Rotational Speed:    | 360 RPM                  |

| Average Latency:     | 83 ms                    |

| Recording Mode:      | Frequency Modulation     |

|                      | Trequency Modulatio      |

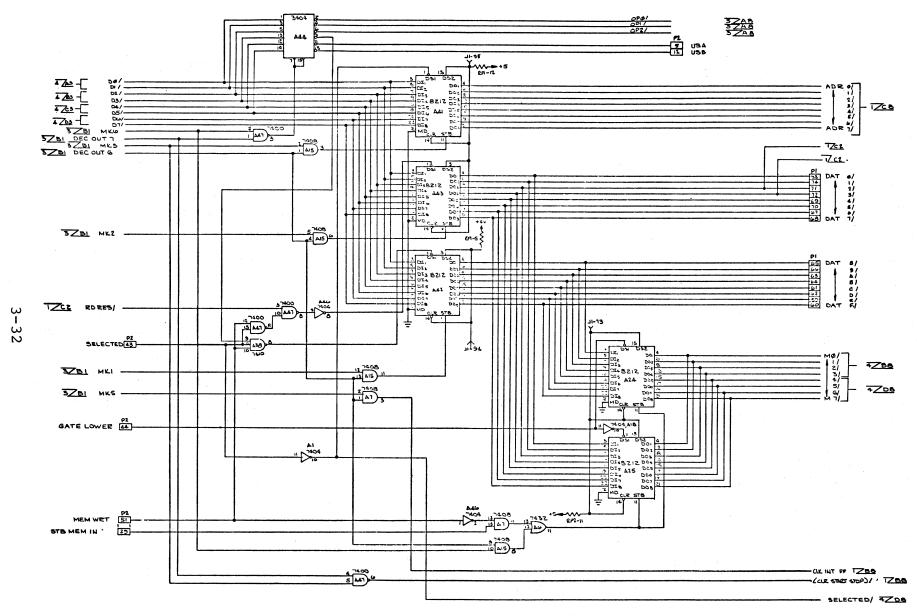

The remaining chapters of the manual deal with each of the system elements in detail. Chapter 2 describes the range of operations that can be performed by the Diskette System, and also provides specific information on how to program the system to execute each of the possible operations. Chapters 3 and 4 provide detailed information on the theory of operation for the Channel Board and the Interface Board, respectively. The final section in each of

these chapters provides a complete schematic drawing of the board as well as a detailed pin list. The reader should continually refer to these schematic drawings in the course of reading the theory of operation sections.

NOTE: To avoid any confusion when referring to the schematics for the Channel and Interface Boards, or when reading the corresponding circuit descriptions, the following notation, concerning the active level of a signal, will apply:

Whenever a signal is active-low, its mnemonic is followed by a slash; for example, MRDC/ means that the level on that line will be low when the memory read command is true (active). If the signal is subsequently inverted, thus making it active-high, the slash is omitted; for example, MRDC means that the level on that line will be high when the memory command is true.

Chapter 5 lists the manufacturer's information on the diskette drives. Chapter 6 provides the major state flow charts for the microprogram which is executed by the Series 3000 Bipolar Microcomputer Set (on the Channel Board), and which essentially controls operation of the Diskette System. Chapter 7 provides basic information on the installation and use of the Diskette System. Finally, Chapter 8 summarizes the AC and DC operating characteristics for the Diskette System.

Before proceeding to Chapter 2, however, we first provide a comprehensive review of the IBM soft-sectored recording format which is used by the Diskette System.

#### 1.2 RECORDING FORMAT

This section summarizes the specifications for the IBM softsectored recording format used by the Diskette System.

# Physical Data Format:

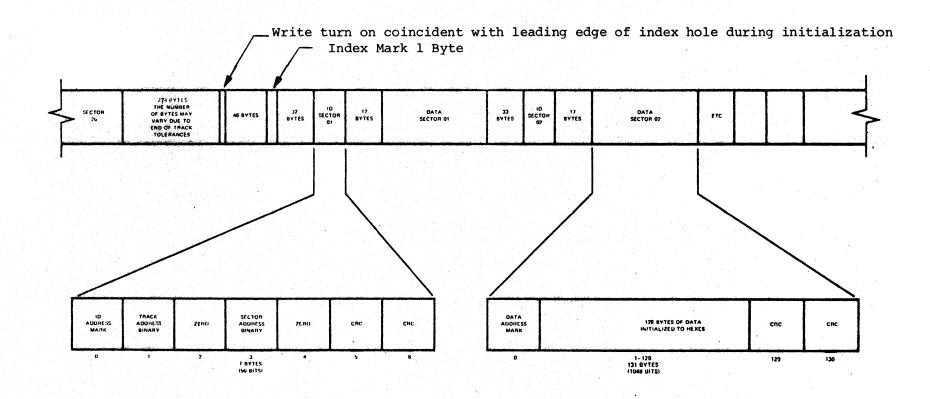

The physical data format is the format with which the diskette controller circuitry must interact. The elements of the physical data format are the hard index hole, index mark, sector address marks, sector headers, and data sectors. The index mark and sector address marks are recorded with unique clock patterns requiring the controller circuitry to accumulate the unique clock patterns for index and sector address mark identification. Figure 1-2 illustrates the general physical data format.

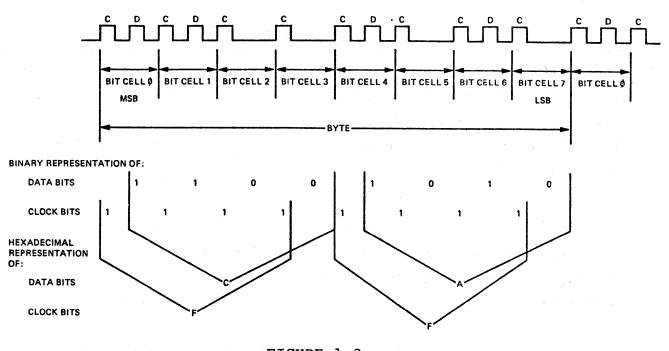

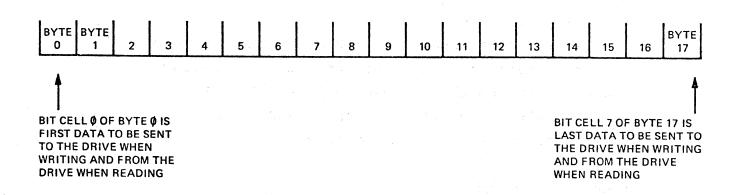

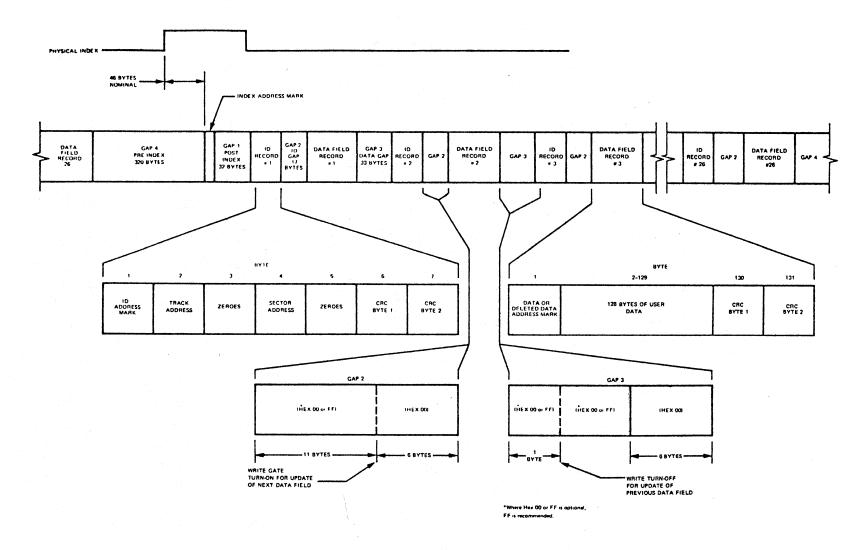

A "byte", when referring to serial data (being written to or read from the diskette drive), is defined as eight (8) consecutive bit cells. By definition, a bit cell is the period between the leading edge of one clock bit and the leading edge of the next clock bit. The most significant bit cell is defined as bit cell 0 and the least significant bit cell is defined as bit cell 7. When reference is made to a specific data bit (i.e., data bit 3), it is with respect to the corresponding bit cell (bit cell 3).

During a write operation bit cell 0 of each byte is transferred to the drive first with bit cell 7 being transferred last. Correspondingly, the most significant byte of data is transferred to the diskette first and the least significant byte is transferred last.

When data is being read back from the drive, bit cell 0 of each byte will be transferred first with bit cell 7 last. As with reading, the most significant byte will be transferred first from the drive to the user.

FIGURE 1-2

Physical Data Format

FIGURE 1-3

BYTE REPRESENTATION

FIGURE 1-4

DATA BYTES

Figure 1-3 illustrates the relationship of the bits within a byte and Figure 1-4 illustrates the relationship of the bytes for read and write data.

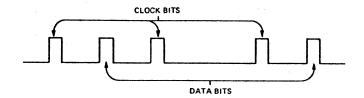

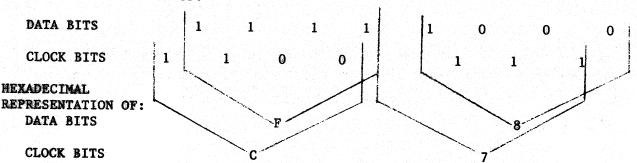

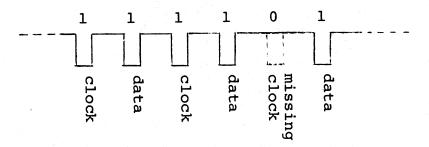

Data is recorded on the diskette using frequency modulation as the recording mode; that is, each data bit recorded on the diskette has an associated clock bit recorded with it. Data written on and read back from the diskette takes the form shown in Figure 1-5. As shown in Figure 1-6, the clock bits and data bits (if present) are interleaved.

#### Track Format:

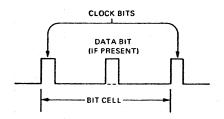

Each track recorded on a diskette consists of 26 fixed length records along with the necessary gaps for record updating. Figure 1-7 illustrates the format of one complete track.

Each field on a track is separated from adjacent fields by a number of bytes containing no data. These areas are referred to as gaps and are provided to allow the updating of one field without affecting adjacent fields. As can be seen from Figure 1-7, there are four different types of gaps on each track:

- Gap 1 Post-Index Gap

This gap is defined as the 32 bytes between Index Address Mark and the ID Address Mark for Sector one (excluding the address mark bytes). This gap is always 32 bytes in length and is not affected by any updating process.

- Gap 2 ID Gap

The seventeen bytes between the ID Field and the Data

Field are defined as Gap 2 (ID Gap). This gap may

vary in size slightly after the Data field has been

updated.

FIGURE 1-5 DATA BIT

FIGURE 1-6 BIT CELL

FIGURE 1-7

TRACK FORMAT

#### • Gap 3 - Data Gap

The thirty-three bytes between the Data field and the next ID field are defined as Gap 3 (Data Gap). As with the ID Gap, the Data Gap may vary slightly in length after the adjacent Data field has been updated.

# • Gap 4 - Pre-Index Gap

The three hundred and twenty bytes between the last Data field on a track and the Index Address Mark are defined as Gap 4 (Pre-Index Gap). Initially, this gap is nominally 320 bytes in length; however, due to write frequency tolerances and diskette speed tolerances this gap may vary slightly in length. Also, after the data field of record 26 has been updated this gap may again change slightly in length.

#### Address Marks:

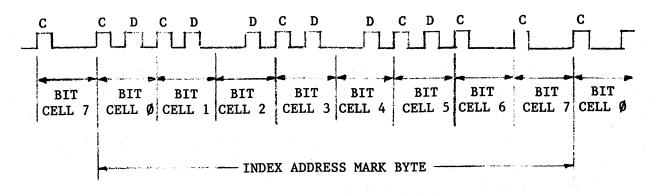

Address Marks are unique bit patterns one byte in length which are used to identify the beginning of ID and Data fields and to synchronize the descrializing circuitry with the first byte of each field. Address Mark bytes are unique from all other data bytes in that certain bit cells do not contain a clock bit (all other data bytes have clock bits in every bit cell.) There are four different types of Address Marks used. Each of these is used to identify different types of fields.

#### • Index Address Mark

The Index Address Mark is located at the beginning of each track and is a fixed number of bytes in front of the first record. The bit configuration for the Index Address Mark is shown in Figure 1-8.

#### • ID Address Mark

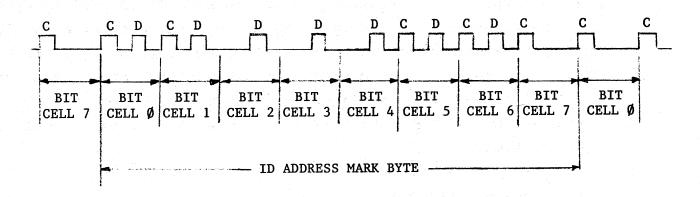

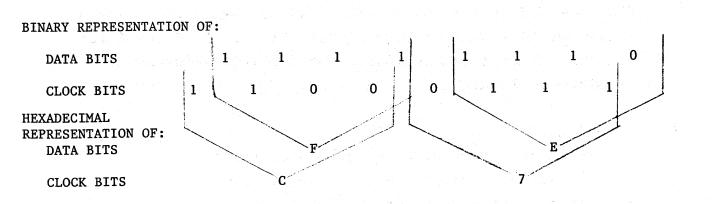

The ID Address Mark byte is located at the beginning of each ID field on the diskette. The bit configuration for this Address Mark is shown in Figure 1-9.

#### BINARY REPRESENTATION OF:

1 1 1 1 DATA BITS 0 1 1 CLOCK BITS 1 0 1 **HEXADECIMAL** REPRESENTATION OF: DATA BITS CLOCK BITS

FIGURE 1-8

INDEX ADDRESS MARK

FIGURE 1-9

ID ADDRESS MARK

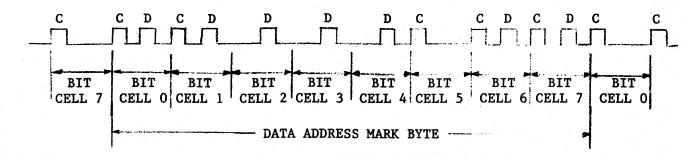

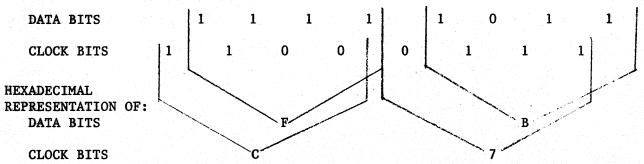

• Data Address Mark

The Data Address Mark byte is located at the beginning of each Data Field on the diskette. The bit configuration for this Address Mark is shown in Figure 1-10.

• Deleted Data Address Mark

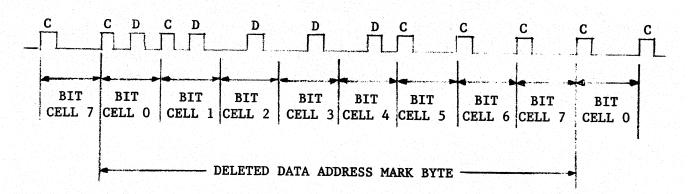

The Deleted Data Address Mark byte is located at the beginning of each "deleted Data" Field on the diskette. The bit configuration for this Address Mark is shown in Figure 1-11. (Note: This bit pattern may be used to flag a data sector as unused or unusable.)

#### CRC Bytes:

Each field written on the diskette is appended with two Cyclic Redundancy Check (CRC) bytes. These two CRC bytes are generated from a cyclic permutation of the data bits starting with bit zero of the address mark and ending with bit seven of the last byte within a field (excluding the CRC bytes). This cyclic permutation is the remainder from the division of the data bits in the field (represented as an algebraic polynomial) by a generator polynomial G(X). For all fields recorded on a diskette, this generator polynomial is:

$$G(x) = x^{16} + x^{12} + x^5 + 1$$

When a field is read back from a diskette, the data bits (from bit zero of the address mark to bit seven of the second CRC byte) are divided by the same generator polynomial G(X) and a non-zero remainder indicates an error within the data read back from the drive while a remainder of zero indicates the data has been read back correctly from the diskette or an undetectable error has been read back.

#### BINARY REPRESENTATION OF:

FIGURE 1-10

DATA ADDRESS MARK

#### BINARY REPRESENTATION OF:

FIGURE 1-11

DELETED DATA ADDRESS MARK

#### CHAPTER 2

# OPERATIONAL SUMMARY AND PROGRAMMING CONSIDERATIONS

All diskette operations are initiated by a Central Processor Unit (CPU) within the Computer system. Once initiated, however, the Diskette Channel completes the specified operation without further intervention on the part of the CPU. From the CPU's point of view, there are only three general steps required to complete any diskette operation:

- The CPU must prepare and store in system memory an I/O Parameter Block (IOPB) for each operation to be performed. If multiple operations are desired, several IOPBs may be linked together in the proper order. An IOPB (ten bytes) specifies a particular diskette operation and provides all of the parameters required for execution of that operation.

- The CPU must then pass the memory address of the first (or only) IOPB to the Diskette Channel.

- The CPU must process the result information from the Diskette Channel upon completion of the operation(s).

The preparation of the IOPB(s) by the CPU, in itself, requires no interaction with the Diskette Channel. The passing of the memory address for the IOPB and the result processing, however, do require interaction. Seven channel commands have been defined to allow the CPU to perform these interactive steps. Four of the channel commands are the result of the CPU executing an output instruction to a dedicated I/O port address, while the other three commands are the result of input instructions to dedicated ports. The seven channel commands are:

- 1) Write memory address lower (output)

- 2) Write memory address upper and start the diskette operation (output)

- 3) Stop diskette operation (output)

- 4) Reset the channel (output)

- 5) Read subsystem status (input)

- 6) Read result type (input)

- 7) Read result byte (input)

The CPU outputs the memory address of the first (or only) IOPB by executing channel commands 1 and 2. Upon execution of channel command 2, the Diskette Channel will request master control of the SBC system bus, fetch the diskette instruction and associated parameters from the IOPB(s), and proceed to perform the specified diskette operation(s). The diskette instruction byte in the IOPB can specify any one of seven diskette operations:

- 1) Recalibrate (seek track 00)

- 2) Seek

- 3) Format a track

- 4) Write data (with data address marks)

- 5) Write data (with deleted address marks)

- 6) Read data

- 7) Verify CRC

The Diskette Channel can interrupt the CPU when the operation (or group of linked operations) is completed or when the drive's ready status changes. The host system software can implement its CPU interrupt mechanism via this direct interrupt feature or it can

"poll" the Diskette Channel by executing channel command 5 (read subsystem status). When the CPU determines that the operation sequence has been completed (either by receiving an interrupt request or by reading the interrupt status), the CPU should execute channel commands 6 and 7 (read result type and read result byte) to determine whether the diskette operations were successfully completed, and if not which type of error occurred.

Thus, in summary, we see that certain channel commands are executed by the CPU to point the Diskette Channel to an IOPB (or group of linked IOPB's) in system memory, and initiate the operation sequence. The Diskette Channel, then, accesses the IOPB(s) to perform the diskette operation(s) specified by the instruction byte of the IOPB(s). The Diskette Channel will, if enabled by the IOPB, generate an I/O complete interrupt request:

- upon completion of each unchained diskette operation,

- upon completion of the last operation in a chain of linked diskette operations, or

- upon detection of an error during an intermediate operation in a chain of linked operations.

The CPU, then, executes other channel commands to determine the result(s) of the diskette operation(s).

In the preceding paragraphs, we have mentioned the channel commands, diskette operations and the IOPB without defining them explicitly. That is because up until now, our primary intention has been to identify clearly the function of each in the overall operation of the Diskette Channel. In the subsequent sections of this chapter, however, we will provide detailed information on the use and format of the channel commands (Section 2.1), the diskette operations (Section 2.2) and the IOPB (Section 2.3). Section 2.4 will define each of the error conditions that can be indicated when the "read result byte" channel command is executed by the CPU.

#### 2.1 CHANNEL COMMANDS

There are seven channel commands to which the Diskette Channel will respond. Four of the channel commands are issued when a CPU in the computer system executes output (I/O write) instructions with the appropriate eight-bit I/O addresses. The other three commands are issued when the CPU executes input (I/O read) instructions with the appropriate I/O addresses.

When the CPU executes one of the output channel commands, it activates the I/O write (IOWC/) line and duplicates the appropriate 8-bit I/O address on address lines ADRO/ - ADR7/ and ADR8/ - ADRF/ of the SBC system bus. Depending on the particular channel command, the CPU may also place relevant data on data lines DATO/ - DAT7/ of the SBC bus. The CPU maintains the data lines until the Diskette Channel returns the transfer acknowledge (XACK/) signal.

When the CPU executes one of the input channel commands, it activates the I/O read (IORC/) line and duplicates the appropriate I/O address on both halves of the SBC bus. The CPU expects the Diskette Channel to activate the transfer acknowledge (XACK/) line when it has placed the requested data on data lines DATO/ - DAT7/.

The Diskette Channel differentiates between the different channel commands by interrogating the I/O read (IORC/) and I/O write (IOWC/) lines and the three least significant address lines (ADRO/ - ADR2/). The five most significant I/O address lines (ADR3/ - ADR7) define the switch-selectable BASE address for the Diskette Channel.

If the Diskette Channel is not busy, it will respond to an output channel command within 3 microseconds. If it is busy, the "write MA lower" and "write MA upper" commands are ignored; no acknowledge is returned. [IMPORTANT NOTE: Because no acknowledge is returned in this case, it could be possible to "hang up" the host system if the system does not include a Fail Safe time-out provision.] The "stop"

and "reset" commands, however, are acknowledged even if the Diskette Channel 1s busy. "Stop" is stored and executed at the end of the current diskette operation. "Reset" is executed immediately (if issued during a data write operation, garbled data will be written).

The Diskette Controller responds to "read subsystem status" and "read result type" input channel commands within 1 microsecond. The information returned in response to a "read subsystem status" command is always valid. The eight bits of data returned in response to a "read result type" command, however, are only valid if the Diskette Channel had previously issued an interrupt request to the CPU. The Diskette Channel will, if not busy, respond to a "read result byte" input command within 3 microseconds. If the Diskette Channel is busy, however, it ignores the "read result byte" command (i.e., no acknowledge is returned). The "read result type" and "read result byte" commands must be executed sequentially ("read result type" first), and should be executed only in response to an interrupt request from the Diskette Channel; execution at other times could produce erroneous result data.

The use and format of each of the seven channel commands is described below: (Note: In the following discussion, "BASE" refers to the switch selectable address on the Channel Board.)

# Write memory address lower (output)

This channel command outputs the low order byte of the 16-bit memory address that points to byte 1 ("channel word") of the first (or only) IOPB.

System address bus: BASE + 1

System data bus: Eight least significant bits of the 16-bit memory address that point to the first IOPB.

# Write memory address upper and start the diskette operation (output)

This channel command outputs the high order byte of the 16-bit memory address that points to byte 1 of the first (or only) IOPB. This command also causes the Diskette Channel to begin executing the diskette operation specified in byte 2 (instruction byte) of

the addressed IOPB.

System address bus: BASE + 2

System data bus: Eight most significant bits of the 16-bit

memory address that point to the first IOPB.

# Stop diskette operation (output)

This output channel command causes the Diskette Channel to cease operations after completing the current diskette operation. The Diskette Channel will not proceed to the next linked IOPB.

System address bus: BASE + 3

System data bus: Not used.

# Reset Diskette System (output)

This output channel command causes all control logic in the Diskette Channel to be reset to an initialized state. If this command is issued while a "write data" diskette operation is in progress, the data in the sector currently being written will be garbled. This command is intended to clear a "hang up" in the Diskette Channel.

System address bus: BASE + 7

System data bus: Not used.

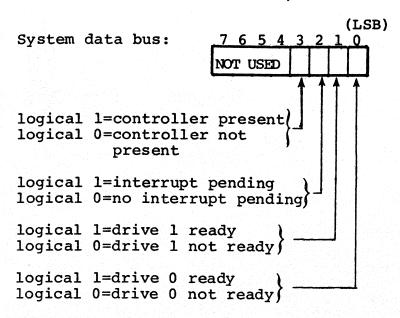

# Read subsystem status (input)

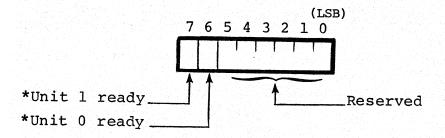

This input channel command causes the Diskette Channel to return four status bits to the CPU. The four bits are:

- bit 0 ready status of drive Ø.

- bit 1 ready status of drive 1.

- bit 2 state of the channel's interrupt flip-flop

- bit 3 controller presence indicator

These indications allow the user's system to monitor the operation of the Diskette Channel.

System address bus: BASE + ø

# Read result type (input)

This input channel command causes the Diskette Channel to return eight bits of information to the CPU. The two least significant bits specify one of four different types of result byte (see next paragraph) associated with diskette operations. The remaining six bits are interpreted according to the code presented in the two least significant bits.

Note: In normal operation, a read result type command <u>must</u> be issued to clear the interrupt indicator. In case of a hardware malfunction, control reset ("master clear") can also be used to clear the indicator.

System address bus: BASE + 1

System data bus:

7 6 5 4 3 2 1 0

\*Block number if \_\_\_ type code = 01; otherwise, these bits are not used.

Type Code

00 - I/O Complete (unlinked);

result byte contains

error bits.

01 - I/O complete (linked);

result byte contains

error bits;

six most significant bits

of this word are block

number.

10 - Result byte contains diskette ready status.

11 - Reserved

\*NOTE: A block number is a 6-bit binary number that uniquely identifies an IOPB (See Section 2.3). The block number is returned in the result type word to identify the IOPB associated with the current interrupt. This scheme is only required when several IOPB's are linked together to perform multiple operations, because there is no uncertainty about the origin of an interrupt request when only a single IOPB exists.

#### Read result byte (input)

This input channel command causes the Diskette Channel to return eight bits of information to the CPU. The interpretation of these bits is dependent upon the type code returned in the result type word (see previous paragraph). The "read result byte" channel command should only be executed after a "read result type" command has been executed.

System address bus: BASE + 3

System data bus:

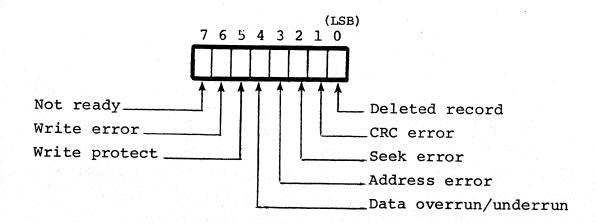

If the type code in the result type word = 00 or 01, the result byte, input on the data bus, will contain error bits (see Section 2.4 for error explanations) and will be formatted as follows:

If the type code = 10, the controller has detected a change in the ready status of a drive and the contents of the result byte will indicate the current ready status of the diskette drives:

A logical 1 means that the drive is currently ready; a \*NOTE: logical 0 means the drive is not ready. It is the responsibility of the host system software to maintain appropriate tables to track these status changes. There is one instance in which a drive can appear "not ready" to the host system, when in fact it is ready. For example, assume that while drive 0 is selected, drive 1 just goes not ready then returns to the ready state (perhaps the diskette platter was changed). When the drive 0 operation is completed, the diskette controller will return two consecutive status change interrupts, the first showing drive 1 not ready, the second showing drive 1 ready. The first interrupt, indicating drive 1 to be not ready, is returned even though the drive is now actually ready because it is important that the operator know that the ready status of the drive changed while the other drive was selected. For instance, this would protect against inadvertently accessing an "unknown" disk, if the drive went not ready then ready again because someone changed diskette platters.

#### 2.2 DISKETTE OPERATIONS

The Diskette System is capable of performing seven different operarecalibrate, seek, format track, write data (with data marks), write data (with deleted data marks), read data, and verify To initiate any diskette operation (or group of linked operations), the CPU will output both bytes of the 16-bit memory address that points to the first byte of an I/O Parameter Block (IOPB). second byte in the IOPB specifies one of the seven diskette operations (see Section 2.3 for IOPB format). After the Diskette System receives the upper byte of the 16-bit memory address, it accesses the IOPB to determine the operation to be performed and to acquire the various parameters that are necessary for execution of the diskette instruction. The Diskette System will perform the specified operation, then set its interrupt flip-flop. If several IOPB's are linked together (see Section 2.3), the Diskette System will perform all of the specified operations (each IOPB specifies one diskette operation) before interrupting the CPU with a request for service.

NOTE: The Diskette Channel automatically unloads the read/write head after a fixed length of time following a diskette operation or group of linked operations. This feature is meant to reduce head wear. The feature is implemented by counting index pulses after a "read result byte" channel command is executed. When the specified count is achieved, the head is unloaded, and the count is re-initialized.

At present, the count is set for 6; that is, the head will remain loaded for at least five complete revolutions following each diskette operation or group of linked diskette operations.

The seven diskette operations are defined in the following paragraphs: (Refer to pages 2-21 and 2-18 for the exact bit patterns required to execute each operation.)

#### RECALIBRATE

This operation causes the head of the selected diskette unit to be moved over track 00. The diskette drive's track 0 sensor is sampled to determine successful completion of this operation. This is often the first instruction executed after a diskette is loaded, or when a seek error occurs (see Section 2.4).

#### SEEK

This operation causes the head of the selected diskette unit to be moved to the track specified in byte 4 of the IOPB. The Diskette Channel will verify the head position by reading the track address from the diskette platter before completing the operation. If at the completion of the head movement, the head is not over the expected track, a "seek error" will be indicated (see Section 2.4).

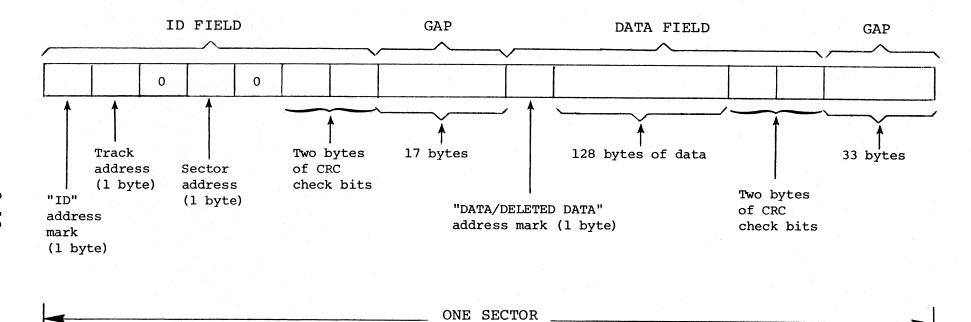

#### FORMAT TRACK

This operation initializes the track specified in byte 4 of the IOPB, by writing all address marks, gaps, address fields and data fields, as shown in Figure 2-1. The various address marks and fields are defined in Section 1.2.

The method of assigning logical sector addresses, which are written into the sector address fields, is specified by bit 6 of the first IOPB byte (the channel word). If this bit is equal to logical 0 the sequence of logical sector addresses will match the physical sequence on the diskette (i.e., sector address "01" is written into the first physical sector after the index mark, sector address "02" is written into the second physical sector, and so on). In addition, the data byte stored in the memory location specified by the 16-bit buffer address contained in bytes 6 and 7 of the IOPB will be written into the 128-byte locations of each sector's data field. No other data bytes need to be stored in this buffer.

FIGURE 2-1

SECTOR FORMAT

If, on the other hand, the sequence of logical addresses being assigned to the sectors is "random" (that is, do not match the physical sequence of sectors), bit 6 of the channel word will be equal to logical 1, and 52 bytes (26 pairs) of data will be stored in memory beginning at the 16-bit buffer address contained in bytes 6 and 7 of the IOPB. Each of the 26 pairs of data bytes will specify the logical sector address to be written into the sector address field of the corresponding physical sector, and the data character which will be written (128 times) into the data field portion of that sector. For example, if the first four bytes of the buffer are:

| Byte | Contents | (hex) |                      |

|------|----------|-------|----------------------|

| 1    | 01       |       | First sector number  |

| 2    | FF       |       | Data                 |

| 3    | 0E       |       | Second sector number |

| 4    | 00       |       | Data                 |

|      |          |       |                      |

Then, sector address "01" will be written into the sector address field of the first physical sector after the index mark, and "FF $_{16}$ " (all ones) will be written into each of the 128 byte locations in the data field portion of this sector. The sector address "0E $_{16}$ " (14 $_{10}$ ) will be written into the sector address field of the second physical sector (i.e., the sector which is physically next to the first sector), and "00 $_{16}$ " (all zeros) will be written into each of the 128 byte locations in the data field portion of this sector. And so on, until a logical sector address has been written into the sector address field of each of the 26 physical sectors on the track, and a data byte is written into each of the 128 byte locations in the data field portion of each of the 26 sectors.

The firmware implementation of the format command is such that in order to format track n  $(n\neq 0)$ , track n-1 must already be formatted (i.e., already have readable address information written into it). Track 0 can always be formatted, even if no valid address information is written on the disk.

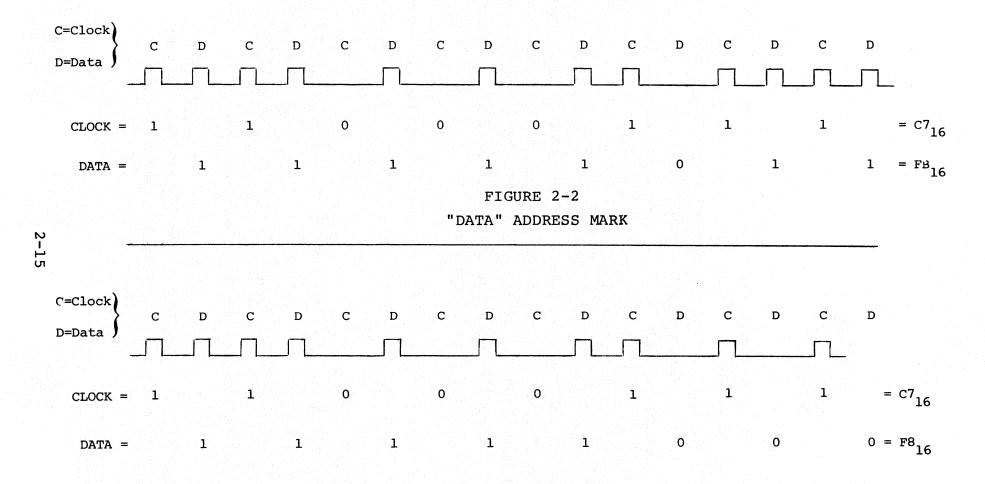

During formatting, a "data mark" (i.e., a character which has a clock pattern equal to  ${\rm C7}_{16}$  and a data pattern equal to  ${\rm FB}_{16}$ ; see Figure 2-2) is written into the "data/deleted data address mark" character position of each sector (i.e., the character position immediately preceding the 128 byte data field).

If, when the format track operation is initiated, the head is not already positioned over the track specified in byte 4 of the IOPB, the format track instruction will cause the head to move (seek) to the proper track before the actual formatting begins.

## WRITE DATA

This operation transfers N x 128 bytes of contiguous data from memory to the diskette. N represents the number of sectors to be written. N is specified by the contents of byte 3 of the IOPB. The 16-bit buffer address stored in bytes 6 and 7 of the IOPB specifies the memory location containing the first data byte to be transferred. The contents of bytes 4 and 5 of the IOPB (track and sector addresses, respectively) specify the logical address of the first sector to be written into.

Each 128 byte data field will be preceded by a "data" address mark (see Figure 2-2) that is used for synchronization. Two bytes (16 bits) of CRC check bits will be generated and written after each data field; the CRC bytes are generated from the address mark, as well as the 128 data bytes.

A multi-sector operation (i.e.,  $N\geq 2$ ) may begin at any sector, but must <u>not</u> go beyond the last logical sector on a track (sector 26).

If the head is not already positioned over the track specified in byte 4 of the IOPB, the write data instruction will cause the head to move (seek) to the proper track before the actual writing begins.

FIGURE 2-3

"DELETED DATA" ADDRESS MARK

## WRITE "DELETED" DATA

This operation is identical to the WRITE DATA operation, described above, except that each 128 byte data field is preceded by a "deleted data" address mark, shown in Figure 2-3.

## READ DATA

This operation transfers N sectors of data (128 bytes per sector) from diskette to memory. N is specified by the contents of byte 3 of the IOPB. The contents of bytes 4 and 5 of the IOPB (track and sector addresses, respectively) specify the logical address of the first sector to be read. The 16-bit buffer address stored in bytes 6 and 7 of the IOPB specifies the memory location into which the first data byte will be written.

Two bytes of CRC check bits will be generated as each sector is being read. When the "data" address mark and all 128 data bytes of a sector have been read, the generated CRC bits are compared with the 16 CRC bits previously written. If there is a mismatch, a CRC error is indicated (see Section 2.4).

A multi-sector operation (i.e,  $N\geq 2$ ) may begin at any sector, but must not go beyond the last logical sector on a track (sector 26).

If the head is not already positioned over the track specified in byte 4 of the IOPB, the read data instruction will cause the head to move (seek) to the proper track before the actual data reading begins.

## VERIFY CRC

This operation is identical to the READ DATA operation, described above, except that no data is transferred to memory.

## 2.3 I/O PARAMETER BLOCK

The CPU in the SBC system initiates a diskette operation, or group of linked operations, by outputting a 16-bit address that points to the beginning (the channel word) of the first (or only) I/O Parameter Block (IOPB) in system memory. The Diskette Channel then accesses the IOPB. An IOPB specifies one of the seven diskette operations (see Section 2.2) and provides all of the parameters required for the completion of that operation. An IOPB consists of ten bytes, as shown in Figure 2-4.

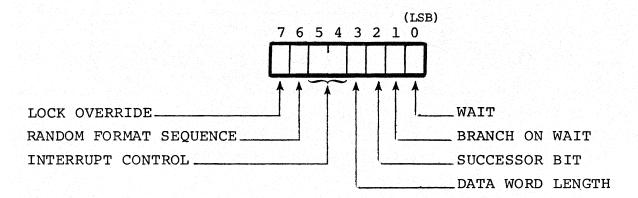

# Byte 1. Channel Word

This byte contains channel control information to be used by the Diskette System. Bit assignments in this byte are as follows:

The "random format sequence" bit (6) specifies the method of assigning logical sector addresses when formatting a track. If this bit is reset (logical 0), sector addresses are assigned in sequential order. If this bit is set (logical 1), sector addresses are assigned in random order according to the pattern listed in the 52 byte memory buffer, which begins at the location addressed by the contents of IOPB bytes 6 and 7. (Refer to the description of the FORMAT TRACK operation in Section 2.2.)

The "interrupt control" bits (4 and 5) enable or disable Diskette Channel interrupts according to the scheme shown in Table 2-1.

| BYTE |                           |

|------|---------------------------|

| *1   | Channel Word              |

| 2    | Diskette Instruction      |

| 3    | Number of Records         |

| 4    | Track Address             |

| 5    | Sector Address            |

| 6    | Buffer Address (Lower)    |

| 7    | Buffer Address (Upper)    |

| 8    | Block Number              |

| 9    | Next IOPB Address (Lower) |

| 10   | Next IOPB Address (Upper) |

<sup>\*</sup> The 16-bit address output to the Diskette System by the two "Write MA" channel commands points to the first byte of an IOPB.

FIGURE 2-4

I/O PARAMETER BLOCK (IOPB) FORMAT

TABLE 2-1

INTERRUPT CONTROL BITS

| BIT: 5 4 | FUNCTION                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0      | I/O complete interrupt request to be issued  (a) upon completion of an unchained diskette operation, (b) upon completion of the last operation in a chain of linked operations, or (c) upon detection of an error in any intermediate operation in a chain of linked operations. |

| 0 1      | All I/O complete interrupts are disabled.                                                                                                                                                                                                                                        |

| 1 0      | I/O complete interrupt to be issued after current operation even though it is an intermediate link in a chain.                                                                                                                                                                   |

| 1 1      | Illegal code                                                                                                                                                                                                                                                                     |

NOTE: The interrupt control bits do not affect interrupt requests which are issued as the result of a change in diskette ready status.

The "data word length" bit (3) must be reset (logical 0) when the Diskette Channel is being used with 8-bit systems, or set (logical 1) when being used with 16-bit systems. This bit must be logical 0 when being used with the SBC system (an 8-bit system).

The "successor" bit (2) will be reset (logical 0) if the current IOPB is the last (or only) IOPB to be executed. This bit will be set (logical 1) if at least one more IOPB is to follow. If this bit is reset, an I/O complete interrupt request will be issued when the operation specified by the current IOPB is completed. If there is a successor IOPB, that IOPB will begin at the memory location specified by bytes 9 and 10 of the current IOPB.

The "branch on wait" (1) and "wait" (0) bits are interrelated. the "wait" bit is reset (logical 0), the Diskette Channel immediately performs the diskette operation specified by the current IOPB. the "wait" bit is set (logical 1), however, the Diskette Channel examines the "branch on wait" bit. If "branch on wait" is set (logical 1) and "wait" is set, the Diskette Channel performs an unconditional branch to the memory location specified by the 16-bit address in bytes 9 and 10 of the current IOPB; the next IOPB to be executed should reside at this memory location. If "branch on wait" is reset (logical 0) but "wait" is set, the Diskette Channel will idle for 10 msec., then examine the "wait" bit again, remaining in this loop until "wait" is reset. This gives the programmer greater flexibility in establishing a sequence of operations to be performed by the Diskette Channel. Note that "branch on wait" MUST be reset (logical 0) if "wait" is reset (logical 0). The Diskette Channel sets the "wait" bit after completing the operation specified in the IOPB (unless the "lock override" bit is set). This protects again inadvertent execution of an uninitialized IOPB.

The "lock override" bit (7) when set, specifies that the "wait" bit is <u>not</u> to be set upon completion of the operation specified in the IOPB. This prevents the IOPB from being overwritten by the controller; this is a useful feature during system debugging.

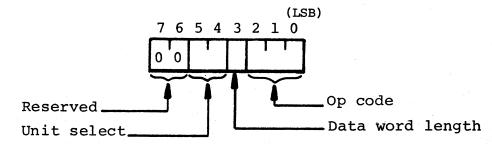

# Byte 2. Diskette Instruction

This byte specifies the diskette operation to be performed and identifies the diskette unit to be used:

The "unit select" bits (4-5) specify drive #0 when reset (logical  $00_2$ ), or drive #1 when set (logical  $11_2$ ).

The "data word length" must contain the same value as the corresponding bit in the channel word (byte 1).

The "op code" bits (0-2) specify one of the seven diskette operations (refer to Section 2.2):

| BIT: <u>3</u> | 2 | 1 | OPERATION            |

|---------------|---|---|----------------------|

| 0             | 0 | 0 | No operation         |

| 0             | 0 | 1 | Seek                 |

| 0             | 1 | 0 | Format track         |

| 0             | 1 | 1 | Recalibrate          |

| 1             | 0 | 0 | Read data            |

| 1             | 0 | 1 | Verify CRC           |

| 1             | 1 | 0 | Write data           |

| 1             | 1 | 1 | Write "Deleted" Data |

|               |   |   |                      |

Byte 3. Number of Records

This binary number specifies the number of sectors to be transferred. Multi-sector operations are allowed, but they must not go beyond the last sector on a track (sector 26); that is, an address error (see Section 2.4) will be indicated if (starting sector address) + (number of records)> $26_{10}$ . Therefore, the maximum block transfer is 26 sectors (from sector 1 to sector 26).

# Byte 4. Track Address

This binary number identifies the track. Acceptable values are 0 to  $^{4\text{C}}_{16}$  (76 $_{10}$ ), inclusive.

## Byte 5. Sector Address

Bits 4 through 0 of this byte contain a binary number which specifies the first sector to be accessed during transfer operations. Acceptable values are 1 to  $1A_{16}$  ( $26_{10}$ ), inclusive. Bit 5 of this word MUST correspond to bit 5 (select bit) of the diskette instruction word (byte 2). Bits 6 and 7 are not used.

# Byte 6. Buffer Address (lower)

This byte contains the eight least significant bits of the 16-bit buffer memory address.

# Byte 7. Buffer Address (upper)

This byte contains the eight most significant bits of the 16-bit buffer memory address. Bytes 6 and 7 together contain the 16-bit address of the first word of the buffer in system memory. During read data operations, the data from the diskette is transferred to the buffer. During write operations, data from the buffer is written to diskette. During format track operations, the address assignment pattern and/or the data field "format characters" are stored in the buffer. (Note: Bytes 6 and 7 must contain a valid address for all diskette operations.)

## Byte 8. Block Number

This byte contains a 6-bit (right-justified) binary number that uniquely identifies the current IOPB. The block number allows the CPU to associate an I/O complete interrupt request from an intermediate link in a chain of IOPB's with the IOPB which actually caused the interrupt. The block number need only be initialized for linked IOPB's, since there can be no uncertainty when only a single IOPB exists.

# Byte 9. Next IOPB Address (lower)

This byte contains the eight least significant bits of the 16-bit memory address that points to the beginning of the next IOPB in the chain.

# Byte 10. Next IOPB Address (upper)

This byte contains the eight most significant bits of that 16-bit memory address that points to the first byte of the next IOPB in a chain. The Diskette System will access the next IOPB after the current operation if the "successor" bit (byte 1) in the current IOPB is set, or immediately if both the "wait" and "branch on wait" bits (byte 1) in the current IOPB are set.

#### 2.4 ERROR INDICATIONS

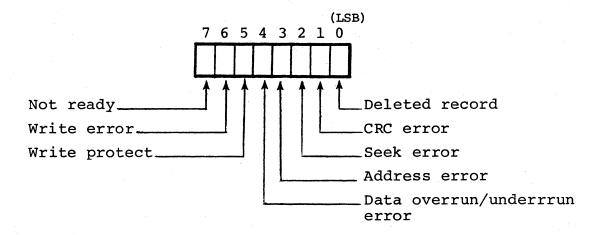

If the CPU executes a "read result byte" channel command (in response to a "read result type" channel command which returned a code of 00 or 01), the Diskette Channel will return the following result word on the system data bus:

The bits are defined as follows:

<u>Not ready</u>. This bit (7) indicates that the selected unit was not ready or that the selected unit changed to a not ready state during an operation.

<u>Write error</u>. This bit (6) indicates that, during a write operation, a condition existed which precluded data integrity. This error is detected by the drive and monitored by the Diskette Channel controller. An example of a condition that could cause this error is an attempt to write through an unloaded head.

<u>Write protect</u>. This bit (5) indicates that the selected drive contains a diskette platter which is in the "read only" mode. This condition is checked on format track, write data (with data address marks) and write data (with deleted data address marks) operations.

<u>Data overrun/underrun error</u>. This bit (4) indicates that the Diskette System controller was not able to service a byte transfer request from the drive before the next request occurred. The data byte is "lost".

Address error. This bit (3) indicates that the disk address received from the CPU is invalid; that is:

- track address > 76<sub>10</sub>,

- sector address = 00,

- 32<sub>10</sub> > sector address > 26<sub>10</sub>

- sector address + number of records > 26<sub>10</sub>

<u>Seek error</u>. This bit (2) indicates that, at the completion of a head movement sequence, the head is not positioned over the expected track. This bit indicates the Diskette System controller and/or drive are malfunctioning, and a recalibrate diskette operation (see Section 2.2) should be performed. Because all of the diskette operations may implicitly cause the head to move, a seek error can occur during any diskette operation.

<u>CRC error</u>. This bit (1) indicates that the two CRC characters generated during a read data or verify CRC operation were not the same as the two CRC characters appended to the data field (see Section 1.2) when it was written on diskette.

<u>Deleted record</u>. This bit (0) indicates that a sector addressed during a read data or verify CRC operation was preceded by a deleted data address mark.

Four other error conditions are indicated when more than one error bit is true:

<u>ID CRC error</u>. If the address error (3) <u>and CRC error</u> (1) bits are true, it indicates that the CRC characters generated during the reading of an ID field (see Section 1.2) were not the same as the CRC characters appended to the field when it was written by a format track operation.

SYNC error. If the deleted record (0) and CRC error (1) bits are true, it indicates that an unexpected address mark pattern (see Section 1.2) was encountered while trying to establish data synchronization. This usually indicates that the ID field is garbled.

NO ADDRESS MARK. If the address error (3), seek error (2) and CRC error (1) bits are true, it indicates that no address mark (see Section 1.2) was encountered for a full revolution of the diskette. This usually indicates that the track has not been formatted.

<u>DATA MARK error</u>. If the address error (3), seek error (2), CRC error (1), and deleted record (0) bits are true, it indicates that the data field of a particular sector was <u>not</u> preceded by either a data mark or a deleted data mark.

# CHAPTER 3 THE CHANNEL BOARD

The Channel Board is the primary control module within the Diskette System. The Channel Board receives, decodes and responds to channel commands from the Central Processing Unit (CPU) in the OEM computer system. The Channel Board can access common system memory to determine the particular diskette operations to be performed and to fetch the parameters required for the successful completion of the specified operations. The Channel Board also monitors subsystem status and error conditions, and organizes these indications into "result type" and "result byte" words that can be read by a CPU in the computer system.

The control functions of the Channel and Interface Boards are provided by an 8-bit microprogrammed processor, implemented with Intel's Series 3000 Bipolar Microcomputer Set. The 8-bit controller includes four 3002 Central Processing Elements (2-bit slice per CPE), a 3001 Microprogram Control Unit and 512 x 32 bits of 3604 programmable-read-only-memory (PROM) which stores the microprogram. The processing and control capabilities of the diskette controller are achieved by execution of the microprogram.

The Channel Board and the Interface Board may reside within System 80 backplane, SBC 604/614 cardcage, or a custom backplane. The Channel Board, together with the Interface Board, constitute what we refer to as the Diskette Controller.

### 3.1 FUNCTIONAL ORGANIZATION OF THE CHANNEL BOARD

For description purposes, the circuitry on the Channel Board can be divided into six functional blocks:

- Channel command block

- Micro control unit (MCU) block

- Microprogram memory block

- Central processing element (CPE) block

- Data/clock shift register (SR) block

- Data flow control block

as shown in Figure 3-1.

The <u>channel command block</u> is responsible for recognizing and decoding channel commands being executed by a CPU in the computer system. When the channel command block recognizes the switch-selectable BASE address of the Diskette Operating System on the SBC system address bus, it decodes the three least significant address bits (ADRO/ - ADR2) to determine which of the seven channel commands is being executed (see Section 2.1). The three address bits are also latched and made available to the MCU block, which is ultimately responsible for controlling the diskette controller's response to a channel command. The channel command block also includes the interrupt latch which stores the fact that an interrupt request has been issued to the CPU by the microprogram.

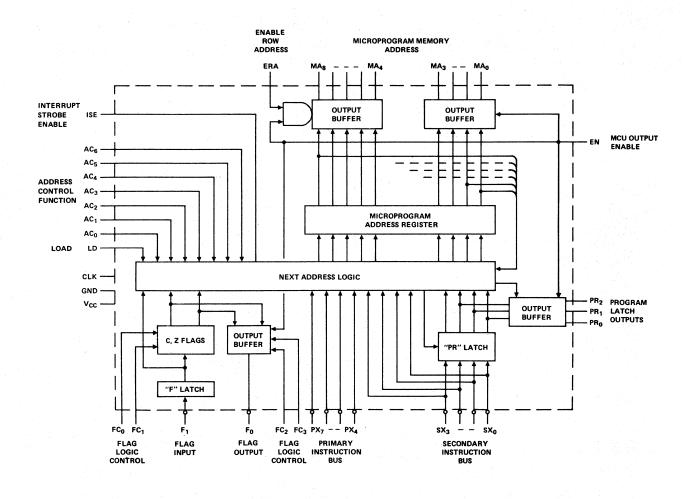

The micro control unit (MCU) block accepts and decodes the three address bits from the channel command block (ADRO/ - ADR2/) specifying a channel command or the three least significant data outputs from the CPE block (DO-D2) specifying one of the seven diskette operations. The two groups of 3 bits select one of the ten routines which implement the channel commands and I/O operations. Having determined the microprogram routine to be executed, the MCU block then generates and outputs the appropriate nine-bit memory address from the microprogram memory. The MCU continuously examines the two flag control

FIGURE 3-1

CHANNEL BOARD: FUNCTIONAL BLOCK DIAGRAM

lines and the seven address control lines (ACO - AC6) from the microprogram memory block to determine the address of the next microinstruction to be fetched and executed.

The microprogram memory block, as its name implies, stores the microprogram. The microprogram memory is organized into 512 words of 32 bits each. The nine address bits from the MCU block determine which 32-bit microinstruction will be output from the microprogram memory. Nine bits of the microinstruction (the address control and flag control bits) are applied to the MCU block, as mentioned above, while the seven function bits (F0-F6) are applied to the CPE block and specify the operation to be performed by the processing elements. The other sixteen bits of the microinstruction words perform a variety of control functions, that will be described completely in Section 3.2.

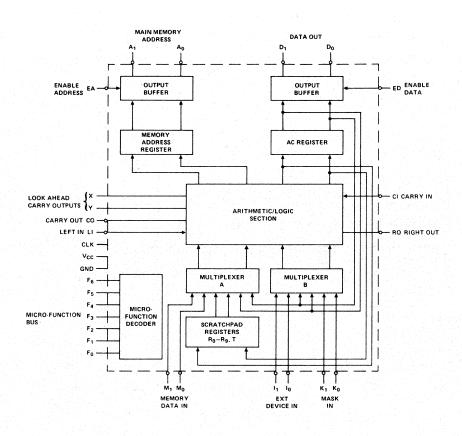

The <u>CPE block</u> includes four Intel® 3002 Central Processing Elements, which form an 8-bit processor. The CPE block receives data from the data flow control block and the data/clock shift register block and receives status information from the Interface Board. The CPE can operate on these various types of input data under the direction of the function and mask control bits from the microprogram memory. The results of these arithmetic/logical operations can then be output onto the eight most significant system address lines (ADR8/ - ADRF/) or the eight CPE data lines (DO - D7). DO - D7 are, in turn, made available to the MCU block, the data/clock shift register block and the data flow control block.

The <u>data/clock shift register block</u> includes the shift registers that accept the serial data bits and the serial clock bits and input them, in parallel, to the CPE block during read operations.

During write operations, the data and clock bytes are (parallel) loaded into the shift registers from the CPE block and shifted out (serially) to the Interface Board.

The <u>data flow control block</u> routes data from the CPE data lines (D0 - D7) to the eight least significant SBC system address lines (ADR0/ - ADR7/) or to either the lower or upper eight lines of the SBC system data bus (DATA0/ - DATA7/ or DATA8/ - DATAF/). This block also routes data from either half of the SBC data bus onto the memory data input lines (MD0/ - MD7/) that feed the CPE block.

## 3.2 THEORY OF OPERATION: CHANNEL BOARD

In this section we will describe the circuitry on the Channel Board. We will divide this theory of operation discussion into six subsections, each dealing with one of the functional blocks defined in Section 3.1.

The Channel Board accepts/transmits signals, data and power through three different PC edge connectors:

- Pl Bus connector (to/from system bus)

- P2 Controller connector (to/from Interface Board)

- J1 Test points only

To avoid any ambiguity when referring to connector pins in subsequent paragraphs, we will always list the connector as well as the pin whenever such references are required; for example, P1-57 refers to pin 57 on connector P1. Pin lists for the three connectors are provided in Section 3.3.

The schematic drawing (4 sheets) for the Channel Board is also provided in Section 3.3.

## 3.2.1 CHANNEL COMMAND BLOCK

The channel command block recognizes and decodes all channel commands directed to the diskette controller. This block includes an eight position switch (S1) for BASE address assignment, eight 74LS86 EXCLUSIVE-OR gates for address recognition, two 3205 three-to-eight decoders, two 7474 D-type flip-flops, a 74175 quad latch, and other assorted gating circuits, as shown on sheet 1 of the board schematic (Section 3.3).

Recall from Chapter 2, that the CPU specifies channel operations for the Diskette System by executing one of the seven channel commands. A channel command may be the result of either an input or output instruction to a dedicated I/O port address on the Channel Board:

- 1) Write MA Lower (output to "BASE+1")

- 2) Write MA Upper and Start I/O (output to "BASE+2")

- 3) Stop Diskette Operation (output to "BASE+3")

- 4) Reset Channel (output to "BASE+7")

- 5) Read Subsystem Status (input to "BASE+0")

- 6) Read Result Type (input to "BASE+1")

- 7) Read Result Byte (input to "BASE+3")

The three least significant bits (ADRO/ - ADR2/) of the 8-bit I/O address (received at pins P1-51 through P1-58) differentiate between the various input or output channel commands. The five most significant address bits (ADR3/ - ADR7/) select the Channel Board if they match the BASE address that is assigned by setting five positions of switch S1. These five switch positions each feed one input on five EXCLUSIVE-OR gates. If ADR3/ - ADR7/ match the switch-selected BASE address, the 7410 NAND gate (A31-8) is activated and, in turn, enables one of the two 3205 decoders.

If an input channel command is being received, the RD CMD line (pin P2-60) will be true, and the 3205 decoder at A20 will be enabled. Address bits ADRO - ADR2 (once inverted) are applied to the three data inputs on the 3205 section (A0 - A2), and activate one of three inverted outputs  $(\overline{O_0}, \overline{O_1} \text{ or } \overline{O_3})$ , depending on the channel command. If it is "read subsystem status" command, output 0 goes true and READ INT/ is asserted at pin P2-57. (On the Interface Board, READ INT/ is used to gate the device  $\emptyset$  and device 1 ready indicators onto system data bus lines  $\emptyset$  and 1, DAT $\emptyset$ / and DAT1/.) The low level on READ INT/ also enables two 8093 circuits, one of which transmits the output of the interrupt latch (INT/) to the data bit 2 line (DAT2/) of the system data bus. The other 8093 circuit transmits a low-level to the data bit 3 line (DAT3/), indicating that the diskette controller is present. INT/ is also passed to the Interface Board via pin P2-40.

If a "read result type" command is being received, the output from the decoder goes true, and the RD RI/ signal is generated (pin P2-37). The low level on RD RI/ pre-sets the interrupt latch (A37-10), thus removing the active-low system interrupt request (INT/).

The interrupt latch can subsequently be clocked reset (i.e., reset to the active-low state) by a pulse on the CLK line, when the central processing element block (Section 3.2.4) determines that an "I/O complete" or "ready status change" interrupt should be issued (also refer to Chapter 2).

If a "read result byte" command is being received, output 3 from the decoder will go true, and the 74175 quad latches are clocked, latching up address bits ADRO - ADR2. The three most significant quad latch outputs are made available to the micro control unit block (Section 3.2.2), which responds to this command via a routine stored in microprogram memory. Either read result command will generate the RD RES/ signal which is used by the data flow control block (Section 3.2.6) to gate the appropriate status word onto the system data bus.

If an output channel command is being received, the WRT CMD line (pin P2-53) will be true, and the other 3205 decoder will be enabled. Address bits ADRO - ADR2 are applied to inputs AO - A2, causing one of the eight inverted decoder outputs to go true. If outputs 0, 1 or 2 go true, the WSUB1/ line (pin P2-48) is activated. If outputs 4, 5 or 6 from the decoder go true, the WSUB2/ line (pin P2-47) is activated. Either WSUB1/ or WSUB2/ will cause the 74175 quad latches to be clocked and latch up address bits ADRO - ADR2, just as a "read result byte" command did. The three most significant outputs of the quad latches are made available to the mecro control unit block which responds to the "write MA lower", the "write MA upper and start I/O" and the "read result byte" channel commands, using routines stored in microprogram memory. The response mechanisms for the other channel commands are implemented in hardware, not micro code.

If a "stop diskette operation" command is being received, output 3 from