## ISBX 218™ FLEXIBLE DISK CONTROLLER HARDWARE REFERENCE MANUAL

Manual Order Number: 121583-001

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

and the combination of ICE, iCS, iSBC, iSBX, MCS, or RMX and a numerical suffix.

### **PREFACE**

This manual provides general information, preparation for use instructions, programming information, principles of operation and service information for the iSBX 218 Flexible Disk Controller. Additional related information is provided in the following Intel documents:

- iSBX<sup>TM</sup> Bus Specification, Order Number 142686

- Intel MCS-80 User's Manual, Order Number 9800153

- Intel Multibus Specification, Order Number 9800683

- Intel 8080/8085 Assembly Language Programming Manual, Order Number 9800301

- Intel 8272 Single/Double Density Floppy Disk Controller, Data Sheet

# **CONTENTS**

| CHAPTER 1<br>GENERAL INFORMATION | Page                           | Page Input/Output Parameter Blocks 3-15 |

|----------------------------------|--------------------------------|-----------------------------------------|

| Introduction                     | _                              | Subroutine Addresses 3-15               |

| Description                      | 1-1                            | Power-On Initialization 3-17            |

| Equipment Supplied               | 1-1                            | Programming the 8272 FDC Chip,          |

| Compatible Equipment             | 1-1                            | General Flow Chart 3-17                 |

| Specifications                   | 1-1                            | Sample Call to I/O Drivers 3-19         |

|                                  |                                |                                         |

|                                  |                                | CHAPTER 4                               |

| CHAPTER 2                        |                                | PRINCIPLES OF OPERATION                 |

| PREPARATION FOR USE              |                                | Introduction 4-1                        |

| Introduction                     | 2-1                            | Interface Signal Description 4-1        |

| Unpacking and Inspection         |                                | iSBX Bus Interface 4-1                  |

| Installation Considerations      | 2-1                            | Control Lines 4-2                       |

| Power Requirement                | 9-1                            | Command Lines 4-2                       |

| Power Requirement                | 2-1<br>2-1                     | DMA Lines 4-2                           |

| Cooling Requirement              |                                | Initialize Line 4-2                     |

| Mounting Requirement             | <u>2-1</u><br>9 <sub>-</sub> 1 | System Control Line 4-2                 |

| Physical Dimensions              | 4-1<br>9 1                     | Address and Chip Select Lines 4-2       |

| Electrical Considerations        |                                | Address Line 4-2                        |

| General Bus Considerations       |                                | Chip Select Line 4-2                    |

| Environmental                    | 0.0                            | Data Lines 4-2                          |

| Connector Configurations         | 2-4                            | Interrupt Lines 4-2                     |

| DC Specifications                | <u>Z</u> -0                    | Option Lines 4-2                        |

| Timing                           | <b>Z-</b> 0                    | Power Lines 4-3                         |

| Jumper Configuration             | 2-6                            | MMIO Command Operations 4-3             |

| I/O Cabling                      | 2-6                            | I/O Read 4-3                            |

| Termination                      | 2-9                            | I/O Write 4-3                           |

| Installation Procedure           | 2-11                           | Direct Memory Access (DMA) 4-4          |

|                                  |                                | Disk Drive Interface 4-4                |

|                                  |                                | Power Lines 4-4                         |

| CHAPTER 3                        |                                | Control/Drive Status Lines 4-4          |

| PROGRAMMING INFORMATIO           | N                              | Drive Select Lines 4-5                  |

| Introduction                     |                                | Side Select/ 4-5                        |

| 8272 FDC Operation               | 3-1                            | Direction 4-5                           |

| I/O Addressing                   | 3-1                            | Step/ 4-5                               |

| 8272 Command Set                 | 3-1                            | Head Load/ 4-5                          |

| 8272 Registers — Main Status/    |                                | Write Enable/ 4-5                       |

| Data Registers                   | 3-2                            | Low Current/ 4-5                        |

| Status Register                  | 3-2                            | Two-Sided/ 4-5                          |

| Command Descriptions             | 3-5                            | Fault/ 4-5                              |

| Read Data                        | 3-5                            | Fault Reset/ 4-5                        |

| Write Data                       |                                | Index/ 4-5                              |

| Write Deleted Data               |                                | Ready/ 4-5                              |

| Read Deleted Data                | 3-9                            | Track 00/ 4-5                           |

| Read A Track                     | 3-9                            | Write Protect/ 4-5                      |

| Read ID                          | 3-9                            | Data Lines 4-6                          |

| Format A Track                   | 3.9                            | Write Data/ 4-6                         |

|                                  |                                | Read Data/ 4-6                          |

| Scans                            | 3-10                           | Board Circuit Description 4-6           |

| Seek                             |                                | 8272 FDC Chip 4-6                       |

|                                  |                                | Clock 4-7                               |

| Recalibrate Status               |                                | Write Clock 4-7                         |

| Sense Interrupt Status           | 3-14<br>3-14                   | Read Data 4-7                           |

| Invalid Commands                 |                                | Data Window 4-7                         |

| invalid Commands                 | 0-14<br>2 15                   | PLO and Phase Comparator 4-8            |

# **CONTENTS** (Continued)

| CHAPTER 5 Pag       | ge Page                           |

|---------------------|-----------------------------------|

| SERVICE INFORMATION | Service and Repair Assistance 5-1 |

| Introduction 5      | 6-1                               |

| Replaceable Parts 5 | 3-1 APPENDIX A                    |

| Service Diagrams 5  | 5-1 PLM/80 Sample ProgramA1       |

### **TABLES**

| Table        | Title                          | Page                    | Table | Title                              | Page       |

|--------------|--------------------------------|-------------------------|-------|------------------------------------|------------|

| 1-1.         | Specifications                 | $\dots \overline{1}$ -2 | 3-5.  | Transfer Capacity                  |            |

| <b>2</b> -1. | Logical and Electrical States  | 2-3                     | 3-6.  | ID Information When Processor      | 00         |

| 2-2.         | Connector P1 Assignment        | 2-4                     |       | Terminates Command                 | 3-8        |

| 2-3.         | Connector J1 Assignment        | 2-5                     | 3-7.  | Sector Size Relationships          |            |

| 2-4.         | Typical Diskette Drive         |                         | 3-8.  | Scan Status Codes                  | 3-12       |

|              | Interface Signal Pinout        | 2-5                     | 3-9.  | Head Unload Time Programming Table |            |

| <b>2</b> -5. | Output Specifications (P1)     | 2-6                     | 3-10. | Step Rate Time Programming Table . | 3-12       |

| 2-6.         | Input Specifications (P2)      | 2-6                     | 3-11. | Head Load Time Programming Table   | 3-13       |

| 2-7.         | iSBX Bus™ Multimodule          |                         | 3-12. | Seek, Interrupt Codes              |            |

|              | Board I/O AC Requirements      | 2-7                     | 3-13. | Sample Declare Table               | 3-16       |

| 2-8.         | Diskette Select Jumpers        |                         | 3-14. | I/O Driver Subroutine Addresses    |            |

| 3-1.         | Status/Data Register Selection | 3-1                     | 3-15. | Delay Count                        |            |

| 3-2.         | Main Status Register Bits      | 3-3                     | 5-1.  | Replaceable Parts                  |            |

| 3-3.         | Status Register                | 3-4                     | 5-2.  | Manufacturer Codes                 | 5-2<br>5-2 |

| 3-4          | Command Mnemonics              |                         |       |                                    | 0-2        |

## **ILLUSTRATIONS**

| Figure      | Title                              | Page | Figure | Title Page                               |

|-------------|------------------------------------|------|--------|------------------------------------------|

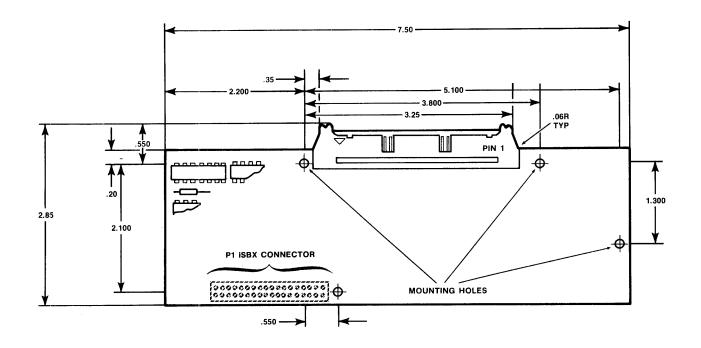

| 2-1.        | Board Dimensions (Inches)          | 2-2  | 2-9.   | Typical Diskette Drive Installation 2-10 |

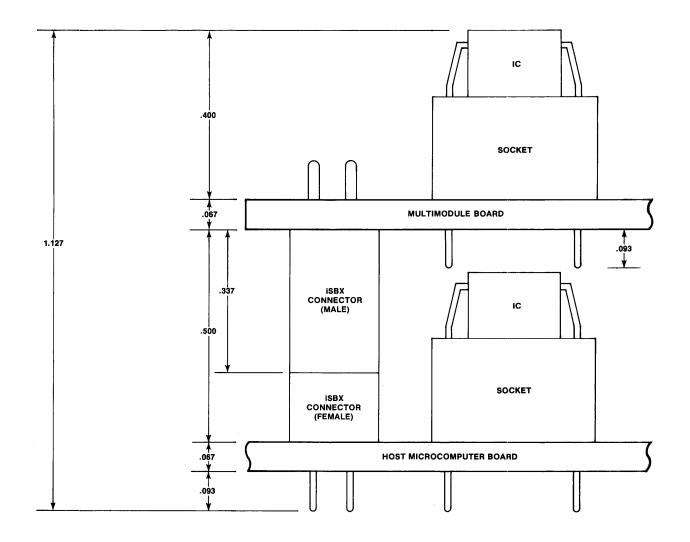

| 2-2.        | Mounting Clearances (Inches)       | 2-3  | 2-10.  | Mounting Technique 2-11                  |

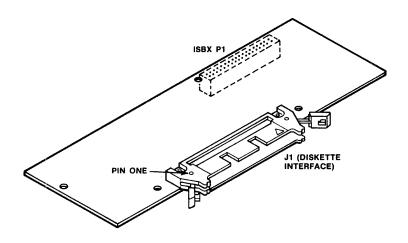

| <b>2-3.</b> | MMIO Connector Locations           | 2-4  | 3-1.   | 8272/DMA Mode Block Diagram 3-2          |

| 2-4.        | iSBX Multimodule Board I/O         |      | 3-2.   | Status Register Timing 3-3               |

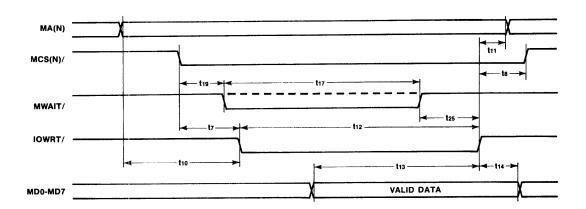

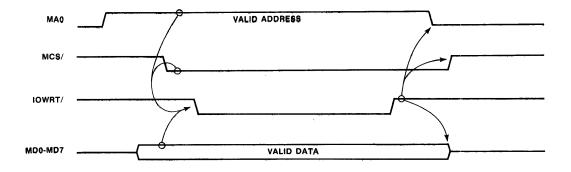

|             | Write Timing                       | 2-8  | 3-3.   | Generalized Diskette Track Format 3-7    |

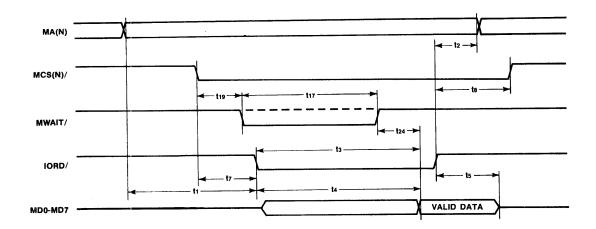

| 2-5.        | iSBX Multimodule Board I/O         |      | 3-4.   | Read Data Command 3-7                    |

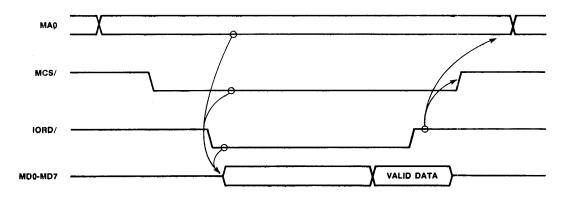

|             | Read Timing                        | 2-8  | 3-5.   | Write Data Command 3-9                   |

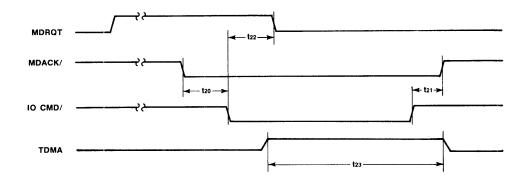

| 2-6.        | iSBX Multimodule Board I/O         |      | 3-6.   | Write Deleted Data Command 3-9           |

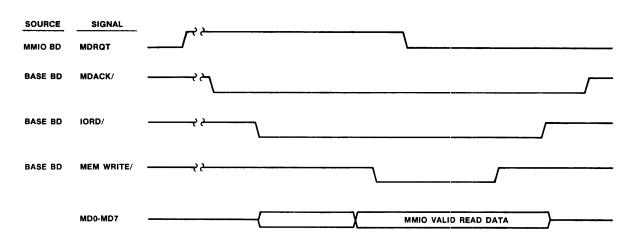

|             | DMA Timing                         | 2-8  | 3-7.   | Read Deleted Data Command 3-10           |

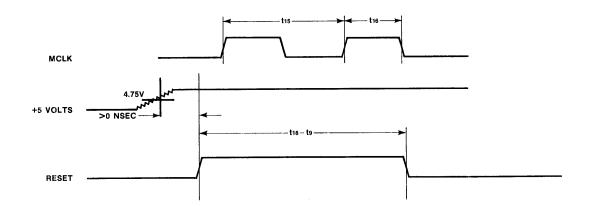

|             | iSBX Multimodule Board Reset Tim   |      | 3-8.   | Read A Track Command 3-10                |

| 2-8.        | Diskette Drive Cable Configuration | 2-9  | 3-9.   | Read ID Command 3-10                     |

# FIGURES (Continued)

| Figure         | Title                          | Page | Figure | Title                           | Page   |

|----------------|--------------------------------|------|--------|---------------------------------|--------|

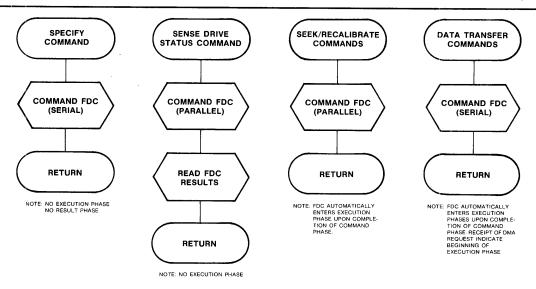

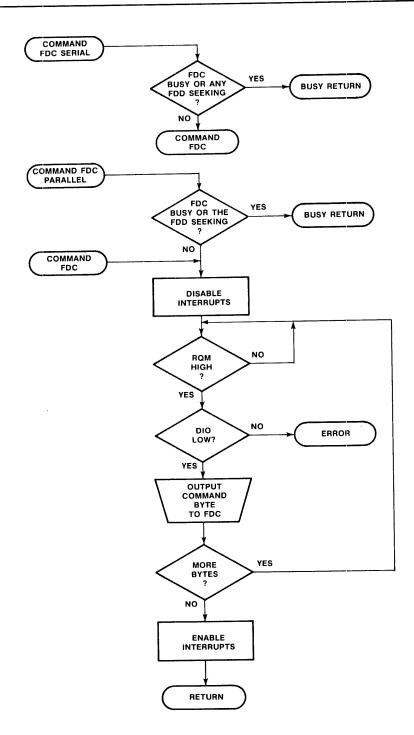

| 3-10.          | Format A Track Command         | 3-10 | 3-22.  | Serial/Parallel Command         |        |

| 3-11.          | Scan Equal Command             |      |        | Phase Flow Chart                | . 3-18 |

| 3-12.          | Scan High or Equal Command     |      | 3-23.  | Interrupt Process or            |        |

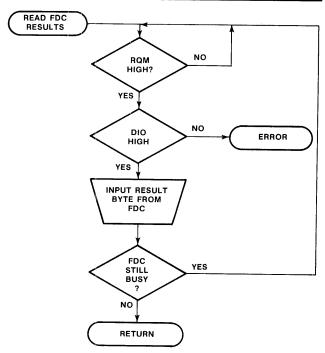

| 3-13.          | Scan Low or Equal Command      |      |        | Result Phase Flow Chart         | . 3-19 |

| 3-13.<br>3-14. | Specify Command                |      | 3-24.  | Sample IOPB for Read Data       | . 3-19 |

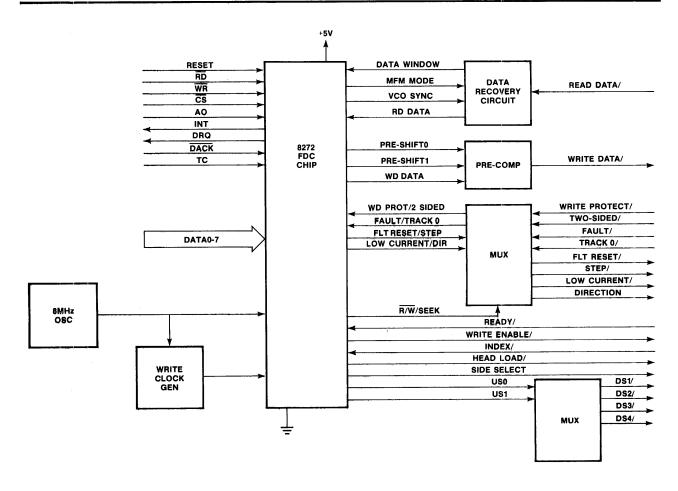

| 3-15.          | Seek Command                   |      | 4-1.   | Block Diagram of iSBX 218 Board | 4-1    |

| 3-16.          | Recalibrate Command            |      | 4-2.   | I/O Read Timing                 | 4-3    |

| 3-10.<br>3-17. | Sense Interrupt Status Command |      | 4-3.   | I/O Write Timing                | 4-3    |

| 3-17.<br>3-18. | Sense Drive Status Command     |      | 4-4.   | DMA Read Timing                 |        |

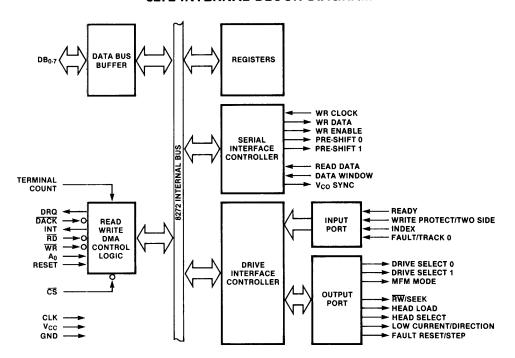

| 3-10.<br>3-19. | Invalid Command                |      | 4-5.   | 8272 Internal Block Diagram     | 4-6    |

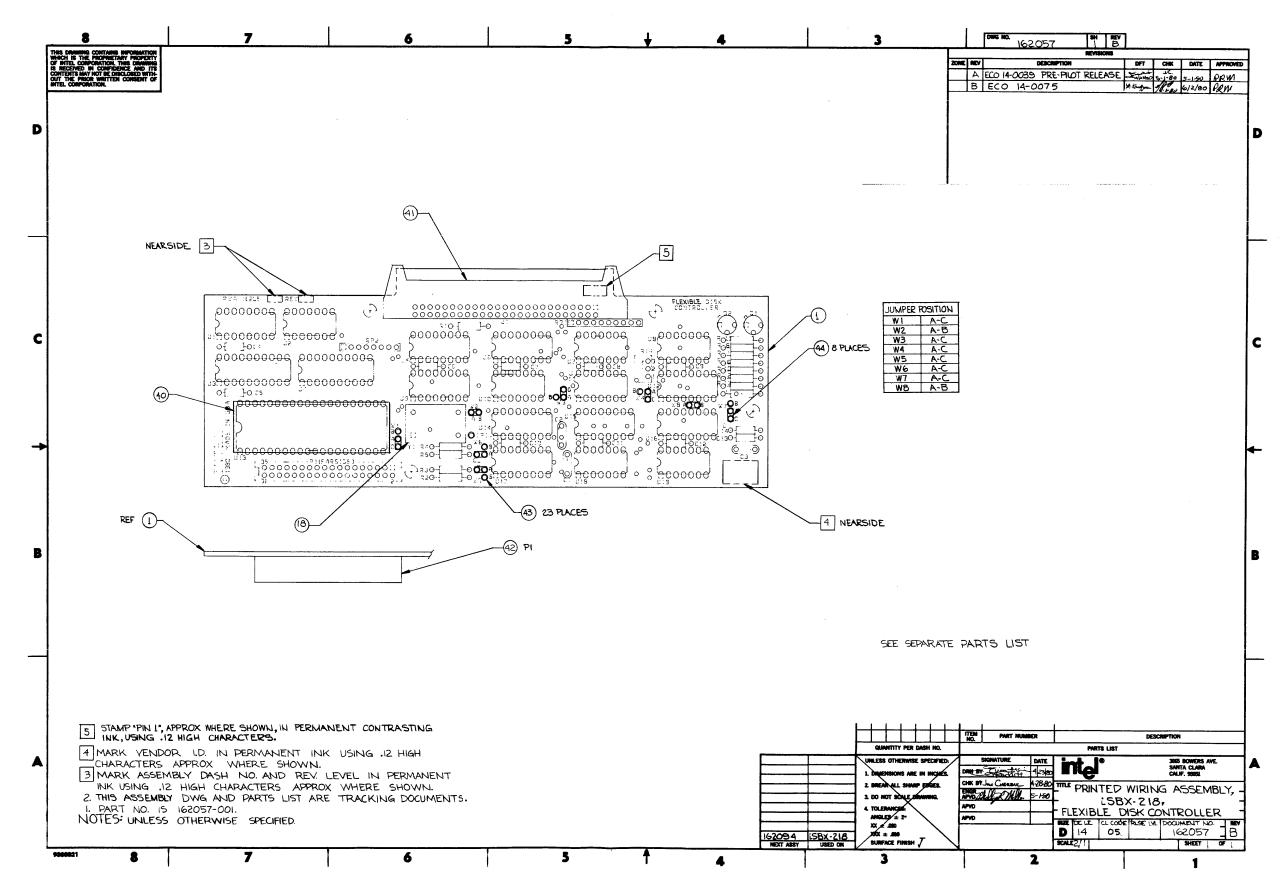

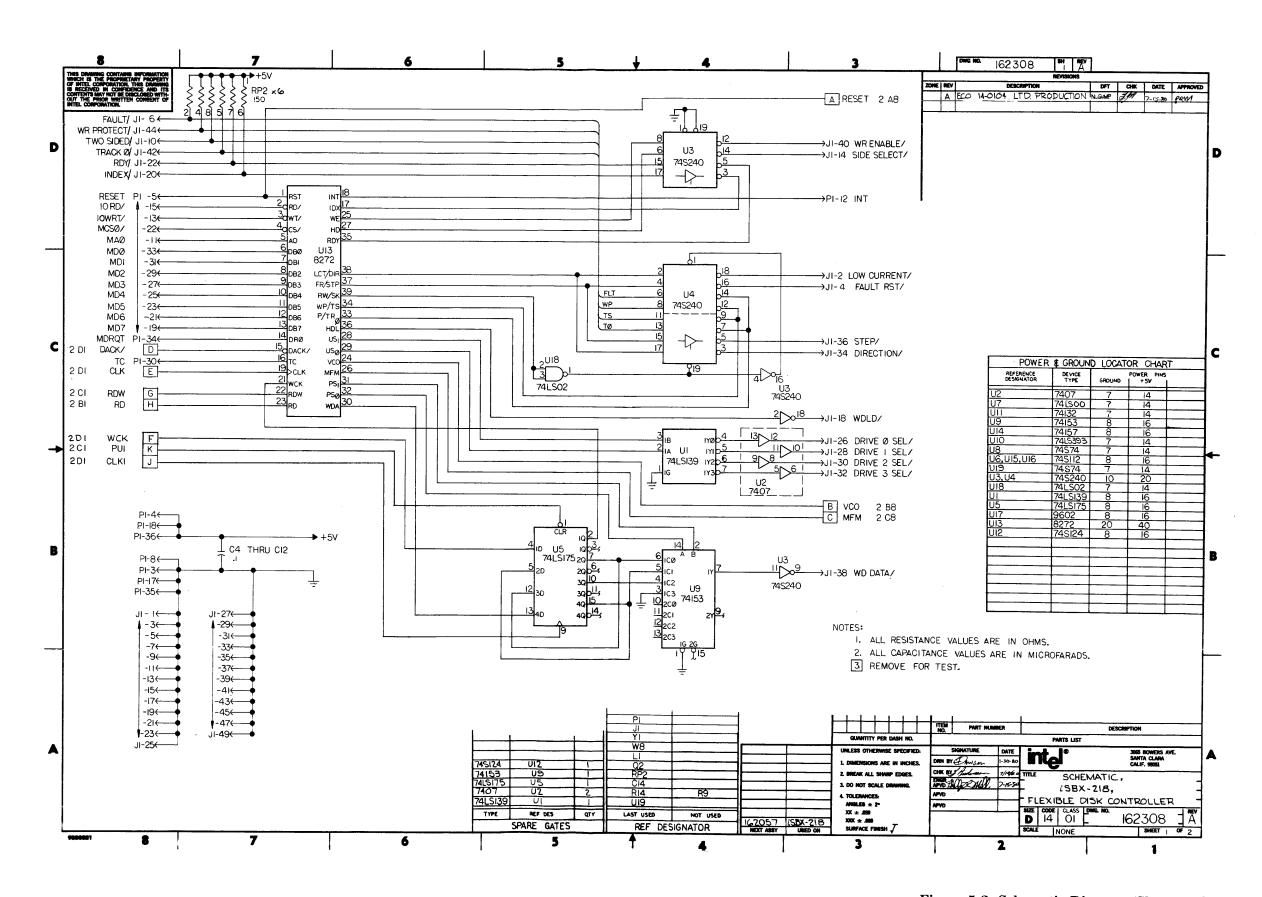

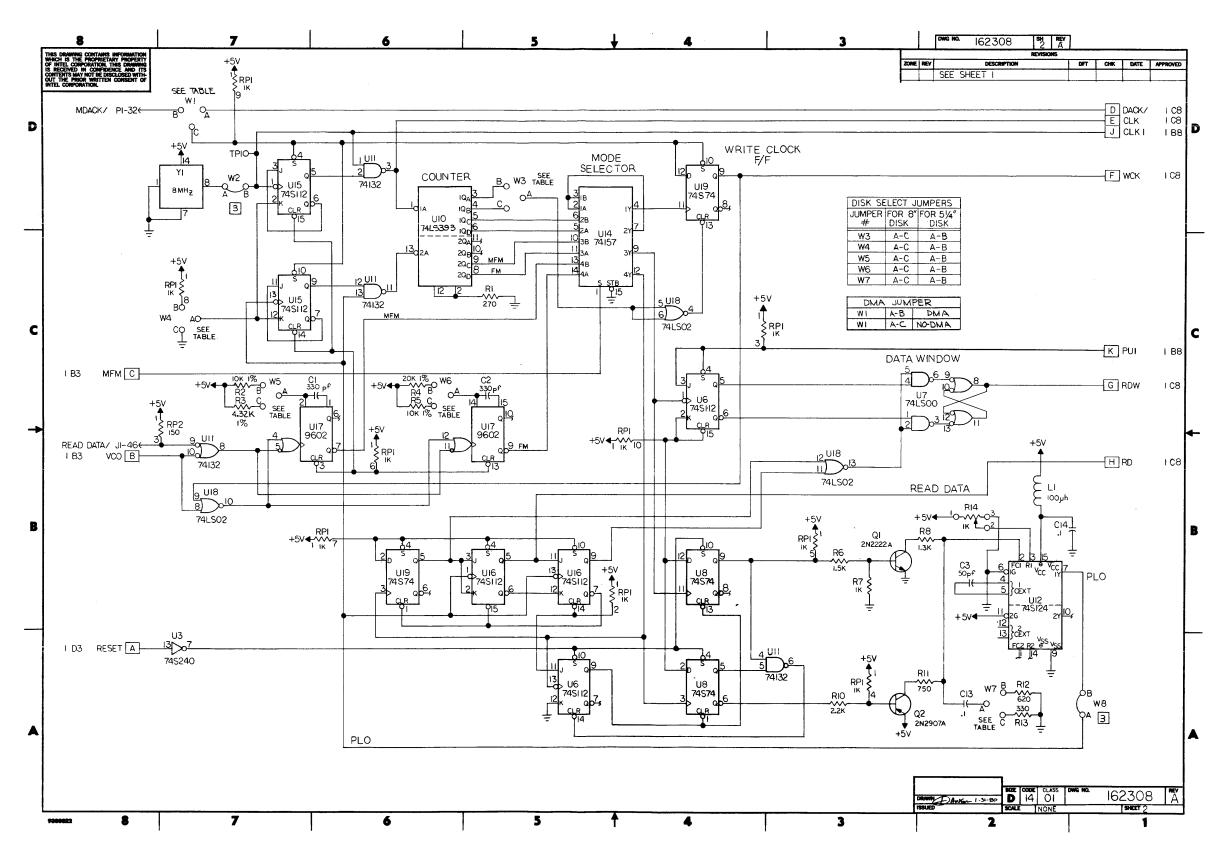

| 3-19.<br>3-20. | Memory Map                     |      | 5-1.   | Parts Location Diagram          |        |

| 3-20.<br>3-21. | Generalized FDC Command Phase  | 0.10 | 5-2.   | Schematic Diagram               |        |

| 0-21.          | Elem Chart                     | 3.17 |        | _                               |        |

# CHAPTER 1 GENERAL INFORMATION

#### 1-1. INTRODUCTION

The iSBX 218 Flexible Disk Controller Multimodule Board (hereinafter called the iSBX 218 board or controller) is a member of Intel's growing line of expansion Multimodule boards designed to augment the iSBC microcomputers, and other iSBC boards equipped with an iSBX connector.

The iSBX 218 board provides for integration of system mass storage by interfacing with up to four 8" double sided, double density floppy diskette drives. Each drive has a storage capacity of 1.6 Megabytes of unformatted data, providing a total capacity of 6.4 Megabytes of unformatted data. This chapter contains a description of the iSBX 218 board and lists the equipment supplied, compatible equipment, and specifications.

#### 1-2. DESCRIPTION

The iSBX 218 Controller is a double-wide Multimodule printed circuit board that interfaces with Intel iSBC boards equipped with iSBX connectors conforming to the iSBX<sup>TM</sup> Bus Specifications. The iSBX 218 board also interfaces with the diskette drives and issues appropriate commands for accessing, reading, and writing data on the diskette. Design of the board is based around the Intel 8272 Single/Double Density Floppy Disk Controller (FDC) chip. Included in the design is the logic to write pre-compensate the Modified Frequency Modulation (MFM) data, interface to the disk drives, and separate the MFM (or FM) data and clocks read from the diskettes. The controller operates exclusively on +5 Vdc power supplied via the iSBX connector. The 8272 FDC chip utilizes fifteen commands for communication between the host iSBC board and the disk drives. Other TTL logic is required to interface to the disk drives. When operating in the MFM mode, logic is provided to pre-compensate the

write data before it is sent to the drive. Additionally, data separation logic takes the raw read data from the diskette drive and converts it to NRZ data.

The iSBX 218 board may be wired to generate an interrupt on request from the 8272 FDC chip, or operate in the DMA mode. Interrupt priority is determined on the host iSBC board. Jumpers are also provided to wire the iSBX 218 board for 8" or 5¼" diskette drives. Due to the wide variety of available 5¼" diskette drive interfaces, the user is responsible for insuring that the specifications of a particular 5¼" disk drive are compatible with the iSBX 218 board.

#### 1-3. EQUIPMENT SUPPLIED

The following equipment is supplied with the iSBX 218 board:

- a. Schematic Diagram, dwg. no. 162308

- b. Assembly Diagram, dwg. no. 162057.

- c. 6 Screws, ¼" 6-32 nylon.

- d. 3 Spacers, 1/2" 6-32 nylon

#### 1-4. COMPATIBLE EQUIPMENT

The iSBX 218 board must be used with an iSBC host board that is equipped with an iSBX connector.

The controller board cannot directly access the MULTIBUS bus structure. Multibus interfacing is provided through the P1 Multibus connector on the iSBC host board.

#### 1-5. SPECIFICATIONS

Specifications for the iSBX 218 Flexible Disk Controller Multimodule Board are provided in Table 1-1.

iSBX 218 **General Information**

#### Table 1-1. Specifications

I/O ADDRESSING

I/O addressing is dependent on the iSBX connector used on the iSBC host board

(I/O Port Address)

POWER REQUIREMENT

+5 Volts, ±0.25 Volts, @ 895 mA (max).

INTERFACE CONNECTORS:

|                   | No. of | Pin Centers |      |                   |

|-------------------|--------|-------------|------|-------------------|

| Interface         | Pins   | in          | mm   | Mating Connectors |

| P1 host board     | 36     | 0.1         | 2.54 | Intel 103059-001  |

| J1 diskette drive | 50     | 0.1         | 2.54 | 3M 3425-0000      |

**ENVIRONMENTAL REQUIREMENTS**

Operation Temperature:

0°C to 55°C (32°F to 131°F)

Relative Humidity:

To 90% without condensation

PHYSICAL CHARACTERISTICS

Width:

7.24 cm (2.85 inches).

Length:

19.1 cm (7.50 inches).

Height:

1.40 cm (0.56 inch) iSBX 218 board only. 2.82 cm (1.13 inches) iSBX 218 board and iSBC board.

Weight:

91 gm (3.20 ounces).

# CHAPTER 2 PREPARATION FOR USE

#### 2-1. INTRODUCTION

This chapter provides instructions for installing the iSBX 218 Controller Board onto a host microcomputer or other iSBC board equipped with an iSBX connector. Included are instructions on unpacking and inspection, installation considerations such as power, cooling, mounting, and size requirements, dc characteristics, connector pin assignments, jumper configurations, and installation procedures.

#### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened, and the contents are damaged, keep the carton and packing materials for the agent's inspection.

For repairs to a product damaged in shipment, contact the Intel Product Service Hotline to obtain a Return Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

It is suggested that all salvageable shipping cartons and packing materials be retained for future use in the event the product must be shipped.

#### 2-3. INSTALLATION CONSIDERATIONS

The iSBX 218 board is designed to interface with all Intel Single Board Computers that support the I/O interface connector required for the Multimodule boards. Other installation considerations such as power, cooling, mounting, and physical size requirements, are provided in the following paragraphs.

#### 2-4. POWER REQUIREMENT

The power requirement for the Controller board is +5V ( $\pm 0.25V$ ) at 895 mA maximum. All power is provided to the iSBX 218 board from the host iSBC board via the P1 connector on the iSBX 218 board.

#### 2-5. COOLING REQUIREMENT, iSBX 218

The iSBX 218 Controller dissipates 4.75 watts. Adequate circulation of air must be provided to prevent a temperature rise above +55°C (+131°F).

#### 2-6. MOUNTING REQUIREMENT

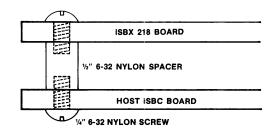

Figure 2-1 shows the iSBX connector and spacer locations. The iSBX 218 board mounts onto an iSBC board supporting an iSBX connector and the proper mounting holes. The mounting hardware supplied as part of the iSBX board includes:

- a. 3 nylon spacers, ½" threaded, separate from the board.

- b. 6 nylon screws,  $\frac{1}{4}$ " 6-32, separate from the board.

- c. One 36-pin connector (P1), factory-installed onto the board.

- d. One 50-pin connector (J1), factory-installed onto the board.

#### NOTE

The iSBX 218 board, when installed onto a host iSBC board, occupies an additional card slot adjacent to the host iSBC board in the 604/614 card cage.

#### 2-7. PHYSICAL DIMENSIONS

Physical dimensions of the iSBX 218 board are as follows:

a. Width: 7.24 cm (2.85 inches).

b. Length: 19.1 cm (7.50 inches).

c. Height: 1.40 cm (0.56 inches)

iSBX 218 board only. 2.82 cm (1.13 inches)

iSBX 218 board and host iSBC board.

Figure 2-2 shows the clearances for a Multimodule board mounted onto a host iSBC board. Height dimensions shown are maximum.

Figure 2-1. Board Dimensions (Inches)

#### 2-8. ELECTRICAL CONSIDERATIONS

The following paragraphs define all the electrical requirements for the iSBX 218 board. First the dc requirements are listed and then the ac timing is described.

## 2-9. GENERAL iSBX BUS CONSIDERATIONS

Table 2-1 shows the relationship between logical and electrical states. The sample signals shown in table 2-1 are IORD/ and IORD. IORD/ is an active low signal and IORD is an active high signal.

#### 2-10. ENVIRONMENTAL

All iSBX bus requirements should be met while the environment is within the following ranges:

Temperature:

0°C to +55°C (+32°F to 131°F) Free moving air across the host iSBC board and the iSBX 218 board. Humidity: 90% maximum relative (non-con-

densing).

Shock: 30 g's of force for an 11 msec dura-

tion, 3 times in 3 planes, both sides

(total of 18 drops).

Vibration: Sweeping from 10 Hz to 55 Hz and

back to 10 Hz, at a distance of 0.010 inches peak-to-peak, lasting 15 minutes in each of the three planes.

#### 2-11. CONNECTOR CONFIGURATIONS

Connectors P1 and J1 are shown in Figure 2-3. Connector P1 on the iSBX 218 board interfaces to the host iSBC board. The pin assignments for connector P1 are listed in Table 2-2. Connector J1 on the iSBX 218 board interfaces to the diskette drives, and the pin assignments for this connector are listed in Table 2-3. The signal names provided in Table 2-3, for the diskette drive interface, may vary somewhat, depending on the drive manufacturer's signal name definitions. A typical drive connector pin configuration is shown in Table 2-4.

Figure 2-2. Mounting Clearances (Inches)

Table 2-1. Logical and Electrical States

| Signal<br>Name | Logical<br>State | Electrical<br>Signal Level | At<br>Receiver  | At<br>Driver    |

|----------------|------------------|----------------------------|-----------------|-----------------|

| IORD/          | 0                | H = TTL High State         | 5.25 ≥ H ≥ 2.0V | 5.25 ≥ H ≥ 2.4V |

| IORD/          | 1                | L = TTL Low State          | 0.8 ≥ L ≥ -0.5V | 0.5 ≥ L ≥ 0V    |

| IORD           | 0                | L = TTL Low State          | 0.8 ≥ L ≥ -0.5V | 0.5 ≥ L ≥ 0V    |

| IORD           | 1                | H = TTL High State         | 5.25 ≥ H ≥ 2.0V | 5.25 ≥ H ≥ 2.4V |

$V_{\text{CC}}$  = 5 volts  $\pm 5\%$  referenced to logical ground.

V = volts.

Preparation for Use iSBX 218

Figure 2-3. iSBX 218 Connector Locations

Table 2-2. Connector P1 Assignment

| Pin | Mnemonic | Description   | Pin | Mnemonic | Description       |

|-----|----------|---------------|-----|----------|-------------------|

| 35  | GND      | Signal Ground | 36  | +5V      | +5 Volts          |

| 33  | MD0      | MDATA Bit 0   | 34  | MDRQT    | M DMA Request     |

| 31  | MD1      | MDATA Bit 1   | 32  | MDACK/   | M DMA Acknowledge |

| 29  | MD2      | MDATA Bit 2   | 30  | тс       | Terminal Count    |

| 27  | MD3      | MDATA Bit 3   | 28  | _        | Reserved          |

| 25  | MD4      | MDATA Bit 4   | 26  | _        | Reserved          |

| 23  | MD5      | MDATA Bit 5   | 24  | _        | Reserved          |

| 21  | MD6      | MDATA Bit 6   | 22  | MCS0/    | M Chip Select 0   |

| 19  | MD7      | MDATA Bit 7   | 20  |          | Reserved          |

| 17  | GND      | Signal Gnd    | 18  | +5V      | +5 Volts          |

| 15  | IORD/    | I/O Read Cmd  | 16  | _        | Not Used          |

| 13  | IOWRT/   | I/O Write Cmd | 14  | _        | Not Used          |

| 11  | MA0      | M Address 0   | 12  | MINTR1   | M Interrupt 1     |

| 9   | _        | Reserved      | 10  | _        | Reserved          |

| 7   | _        | Reserved      | 8   | MPST/    | M Present         |

| 5   | RESET    | Reset         | 6   |          | Not Used          |

| 3   | GND      | Signal Gnd    | 4   | +5V      | +5 Volts          |

| 1   |          | Reserved      | 2   | _        | Reserved          |

MUST BE SUPPLIED BY HOST iSBX 218 Preparation for Use

Table 2-3. Connector J1 Assignment

| Pin   | Description              | Pin        | Description    |

|-------|--------------------------|------------|----------------|

| 1     | Signal Ground            | 2          | Low Current/   |

| 3     | Signal Ground            | 4          | Fault Reset/   |

| 5     | Signal Ground            | 6          | Fault/         |

| 7     | Signal Ground            | 8          | Reserved       |

| 9     | Signal Ground            | 10         | Two-Sided/     |

| 11    | Signal Ground            | 12         | Reserved       |

| 13    | Signal Ground            | 14         | Side Select    |

| 15    | Signal Ground            | 16         | Reserved       |

| 17    | Signal Ground            | 18         | Head Load/     |

| 19    | Signal Ground            | 20         | Index/         |

| 21    | Signal Ground            | 22         | Ready/         |

| 23    | Signal Ground            | 24         | Reserved       |

| 25    | Signal Ground            | 26         | Drive 0 Sel/   |

| 27    | Signal Ground            | 28         | Drive 1 Sel/   |

| 29    | Signal Ground            | 30         | Drive 2 Sel/   |

| 31    | Signal Ground            | 32         | Drive 3 Sel/   |

| 33    | Signal Ground            | 34         | Direction      |

| 35    | Signal Ground            | 36         | Step/          |

| 37    | Signal Ground            | 38         | Write Data/    |

| 39    | Signal Ground            | 40         | Write Enable/  |

| 41    | Signal Ground            | 42         | Track 00/      |

| 43    | Signal Ground            | 44         | Write Protect/ |

| 45    | Signal Ground            | 46         | Read Data/     |

| 47    | Signal Ground            | 48         | Reserved       |

| 49    | Signal Ground            | 50         | Reserved       |

| NOTE: | See Chapter 4 for detail | iled signa | l description. |

CAUTION

J1 pin numbers refer to the iSBX 218 board connector only. The pin numbers on the mating connector at the diskette drive may not be the same.

#### 2-12. DC SPECIFICATIONS

The dc specifications for the iSBX bus interface (P1) are summarized in Tables 2-5 and 2-6. Table 2-5 is the output specifications; Table 2-6 is the input

specifications. The output specifications are the requirements on the output drivers of the iSBX 218 board, (i.e., the data bus output drivers must guarantee at least 1.6 mA @ 0.5 volts). The output specifications in Table 2-5 are the minimum drive requirements. The input specifications are the requirements of the receivers on the iSBX 218 board. (e.g., the loading of the address lines (MA0-MA2) can be no greater than 0.5 mA @ 0.8 volts). These tables also summarize the maximum loading permitted on an iSBX Multimodule board interface at any one time.

#### 2-13. **TIMING**

Table 2-7 summarizes all the ac timing requirements for an iSBX Multimodule board I/O interface. The timing diagrams are shown in Figures 2-4 through 2-7. The MWAIT/ signal is not used on the iSBX 218 board.

Table 2-4. Typical Diskette Drive Interface Signal Pinout

| Drive Connector Pin Number | Signal Name          |

|----------------------------|----------------------|

| 1-49 odd                   | Ground               |

| 2                          | Write Current Switch |

| NC                         |                      |

| NC                         |                      |

| NC                         |                      |

| 10                         | Two-sided            |

| 12                         | Disk Change          |

| 14                         | Side Select          |

| 16                         | In Use               |

| 18                         | Head Load            |

| 20                         | Index                |

| 22                         | Ready                |

| 24                         | Sector               |

| 26                         | Drive Select 1       |

| 28                         | Drive Select 2       |

| 30                         | Drive Select 3       |

| 32                         | Drive Select 4       |

| 34                         | Direction Select     |

| 36                         | Step                 |

| 38                         | Write Data           |

| 40                         | Write Gate           |

| 42                         | Track 00             |

| 44                         | Write Protect        |

| 46                         | Read Data            |

| 48                         | FM Sep Data          |

| 50                         | FM Sep Clock         |

NOTE: The above pin numbers are for a typical OEM diskette drives including Shugart Associates SA850, Pertec FDX50, MFE700, Memorex 552, and other industry drives.

Preparation for Use iSBX 218

| Table 2-5. Output | Specifications | (P1) |

|-------------------|----------------|------|

|-------------------|----------------|------|

| Bus Signal<br>Name | Type¹<br>Drive | IOL Max<br>—Min (mA) | @ Volts<br>(Vol Max) | Iон Max<br>−Min (μA) | @ Volts<br>(Voн Min) | Co (Min)<br>(pf) |

|--------------------|----------------|----------------------|----------------------|----------------------|----------------------|------------------|

| MD0-MD7            | TRI            | 1.6                  | 0.5                  | -200                 | 2.4                  | 130              |

| MINTR0-1           | TTL            | 2.0                  | 0.5                  | -100                 | 2.4                  | 40               |

| MDRQT              | TTL            | 1.6                  | 0.5                  | - 50                 | 2.4                  | 40               |

| OPT1-2             | TTL            | 1.6                  | 0.5                  | - 50                 | 2.4                  | 40               |

| MPST/              | TTL            | Note 2               |                      |                      |                      |                  |

<sup>1.</sup> TTL = standard totem pole output. TRI = Tri-state. 2. iSBX MMIO board must connect this signal to ground.

Table 2-6. Input Specifications (P1)

| Bus Signal<br>Name | Type¹<br>Receiver | II∟ Max<br>(mA) | @ Vin Max<br>(volts) | Iін Мах<br>(μА) | @ VIN Max<br>(volts) | Cı Max<br>(pf) |  |

|--------------------|-------------------|-----------------|----------------------|-----------------|----------------------|----------------|--|

| MD0-MD7            | 1D0-MD7 TRI       |                 | 0.8                  | 70              | 2.0                  | 40             |  |

| MA0-MA2            | TTL               | -0.5            | 0.8                  | 70              | 2.0                  | 40             |  |

| MCS0/-MCS1/        | TTL               | -4.0            | 0.8                  | 100             | 2.0                  | 40             |  |

| MRESET             | TTL               | -2.1            | 0.8                  | 100             | 2.0                  | 40             |  |

| MDACK/             | TTL.              | -1.0            | 0.8                  | 100             | 2.0                  | 40             |  |

| IORD/<br>IOWRT/    | TTL               | -1.0            | 0.8                  | 100             | 2.0                  | 40             |  |

| OPT1-OPT2          | TTL.              | -2.0            | 0.8                  | 100             | 2.0                  | 40             |  |

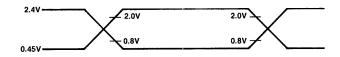

#### NOTE

The input waveforms for the ac timing specifications are as follows:

#### 2-14. JUMPER CONFIGURATION

The iSBX 218 board contains several jumpers that permit the user to select the board operation for a particular diskette drive or data transfer option. Two jumpers (W2 and W8) are installed for testing only and should never be removed. Jumper W1 can be connected between "A" and "C" for non-DMA operation, or between "A" and "B" for DMA operation.

Jumpers W3 through W7 must be configured for the type of diskette drive to be used, i.e., 8" or 5\\daggeq". Table 2-8 shows how to connect these jumpers to enable the iSBX 218 board to operate with the desired drive type. The iSBX 218 board cannot be configured to operate with two different types of diskette drives at the same time. For actual physical location of jumpers, see Figure 5-1.

#### 2-15. I/O CABLING

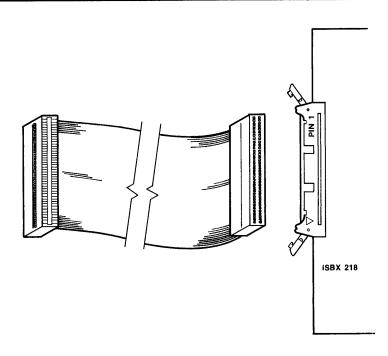

The user-supplied cabling for the iSBX 218 board provides the interface between the Controller and the diskette drives. This cable is connected to iSBX 218 connector J1 with a mating connector 3M Part Number 3425-0000. This connector is a 50-pin ribbon cable, mass-terminated connector, whose connection configuration is shown in Figure 2-8. The drive end of this interface cable must be configured to match the specific diskette drive being used. The interface cables between the drives are configured as described in each of the manufacturer's user manuals.

Table 2-7. iSBX Bus™ Multimodule Board I/O AC Requirements

| Symbol                       | Parameter                                  | Min (ns) | Max (ns) | Figure<br>Reference |

|------------------------------|--------------------------------------------|----------|----------|---------------------|

| t <sub>1</sub>               | Address stable before read                 | 50       | _        | 2-4                 |

| t2                           | Address stable after read                  | 30       | _        | 2-4                 |

| t <sub>3</sub>               | Read pulse width                           | 300      | _        | 2-4                 |

| t4 <sup>2</sup>              | Data valid from read                       | 0        | 250      | 2-4                 |

| t5 <sup>2</sup>              | Data float after read                      | 0        | 150      | 2-4                 |

| t <sub>6</sub> 3             | Time between RD and/or WRT                 | _        | _        | _                   |

| t <sub>7</sub>               | CS stable before CMD                       | 25       | _        | 2-4                 |

| t <sub>8</sub>               | CS stable after CMD                        | 30       | _        | 2-4                 |

| t9                           | Power up reset pulse width                 | 50 Msec  | _        | 2-6                 |

| t <sub>10</sub>              | Address stable before WRT                  | 50       | _        | 2-3                 |

| t <sub>11</sub>              | Address stable after WRT                   | 30       | _        | 2-3                 |

| t <sub>12</sub> 1            | Write pulse width                          | 300      | _        | 2-3                 |

| t <sub>13</sub> 1            | Data valid to write                        | 250      | _        | 2-3                 |

| t <sub>14</sub>              | Data valid after write                     | 30       | _        | 2-3                 |

| t <sub>15</sub>              | MCLK cycle                                 | 100      | 110      | 2-6                 |

| t <sub>16</sub>              | MCLK width                                 | 35       | 65       | 2-6                 |

| t <sub>17</sub> 1            | MWAIT/ pulse width                         | 0        | 4 msec   | 2-3, 2-4            |

| t <sub>18</sub>              | Reset pulse width                          | 50 Msec  | _        | 2-6                 |

| t <sub>19</sub>              | MCS/ to MWAIT/ valid                       | 0        | 75       | 2-3, 2-4            |

| t <sub>20</sub>              | DACK set up to I/O CMD                     | 100      | _        | 2-5                 |

| t <sub>21</sub>              | DACK hold                                  | 30       | _        | 2-5                 |

| t <sub>22</sub>              | CMD to DMA RQT removed to end of DMA cycle |          | 200      | 2-5                 |

| t23                          | TDMA pulse width                           | 500      | _        | 2-5                 |

| t <sub>24</sub> 1            | MWAIT/ to valid read data                  | _        | 0        | 2-4                 |

| t <sub>25</sub> <sup>1</sup> | MWAIT/ to WRT CMD                          | 0        |          | 2-3                 |

#### NOTES:

- 1. Required only if WAIT is activated.

2. If MWAIT/ not activated.

3. Time dependent on the host iSBC board to which the Multimodule board is connected.

Figure 2-4. iSBX Multimodule Board I/O Write Timing

Figure 2-5. iSBX Multimodule Board I/O Read Timing

Figure 2-6. iSBX Multimodule Board I/O DMA Timing

iSBX 218 Preparation for Use

Table 2-8. Diskette Select Jumpers

| Jumper | For 8" Diskette | *For 5¼" Diskette |

|--------|-----------------|-------------------|

| W3     | A-C             | A-B               |

| W4     | A-C             | A-B               |

| W5     | A-C             | A-B               |

| W6     | A-C             | A-B               |

| W7     | A-C             | A-B               |

<sup>\*</sup>The user is responsible for insuring that the specifications of a particular 51/4" disk drive are compatible with the iSBX 218 board.

#### 2-16. TERMINATION

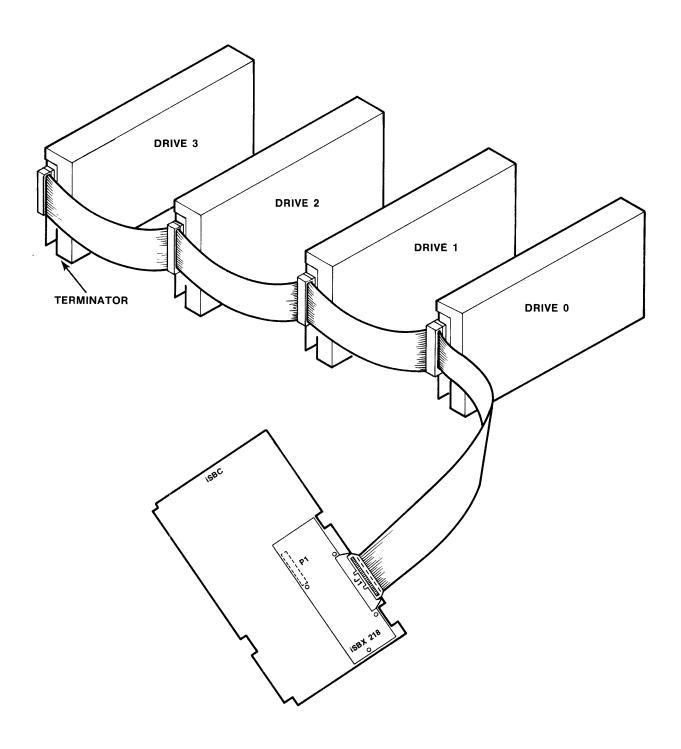

All line terminations required on the iSBX 218 board are provided through the 150 ohm resistors in resistor pack RP2. This is a factory installed device and is not field removable. Termination requirements for the diskette drive are listed in the drive manufacturer's user manual. The last drive in the daisy chain string must be terminated. A typical four diskette drive installation, showing cabling and termination location is shown in Figure 2-9. More detailed information on drive installation is provided in the user manual for the specific drive employed.

Figure 2-7. iSBX Multimodule Board Reset Timing

Figure 2-8. Diskette Drive Cable Configuration

Figure 2-9. Typical Diskette Drive Installation

iSBX 218 Preparation for Use

#### 2-17. INSTALLATION PROCEDURE

The iSBX 218 board mounts onto the host iSBC board. Install the board as follows:

- a. With the 6-32 screws, secure the three ½ inch plastic spacers to the host iSBC board as shown in Figure 2-10.

- b. Locate pin 1 on the iSBX connector (P1) of the Multimodule board and align it with pin 1 of the iSBX connector on the host iSBC board.

- Align the iSBX 218 board mounting holes with the spacers on the host iSBC board. See Figure 2-1 for hole location.

- d. Gently press the two boards together until the connector seats.

- e. Fasten the iSBX 218 board to the spacer with the three remaining 6-32 nylon screws.

#### NOTE

The position of an installed Multimodule board and the host board connector number may vary according to the type of host iSBC board that is used.

Figure 2-10. Mounting Technique

# CHAPTER 3 PROGRAMMING INFORMATION

#### 3-1. INTRODUCTION

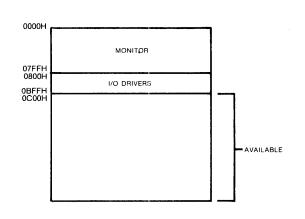

This chapter provides programming information for the iSBX 218 Flexible Disk controller board. Included is information on I/O addressing, system initialization, and 8272 FDC programming. The logic and design of the iSBX 218 board is based around the 8272 FDC chip. The 8272 FDC chip is the only programmable device on the controller.

This chapter provides information to invoke the total command set from the base board to the iSBX 218 board permitting the use of 8" single/double sided, single/double density floppy disk drives or 5¼" mini-flexible disk drives. Included in the programming information is the complete status register bit definitions, DMA operation, and interrupt handling.

The 8272 FDC chip command set and its implementation are explained in the following text. Each host iSBC board must meet the requirements to implement this command set. It is therefore necessary that each iSBC board be configured with the appropriate PROMs containing the required firmware to meet these requirements.

#### 3-2. 8272 FDC OPERATION

The 8272 is an LSI Floppy Disk Controller (FDC) chip, which contains the circuitry and control functions for interfacing the host iSBC microprocessor board with up to four floppy disk drives. It is capable of supporting either IBM 3740 single density format (FM), or IBM System 34 double density format (MFM) including double sided recording.

Address mark detection circuitry is internal to the FDC, thus simplifying the Phase Locked Loop (PLL) and read electronics. The track stepping rate, head load time, and head unload time may be programmed by the user. The FDC also permits multiple sector transfers in both read and write modes with a single instruction.

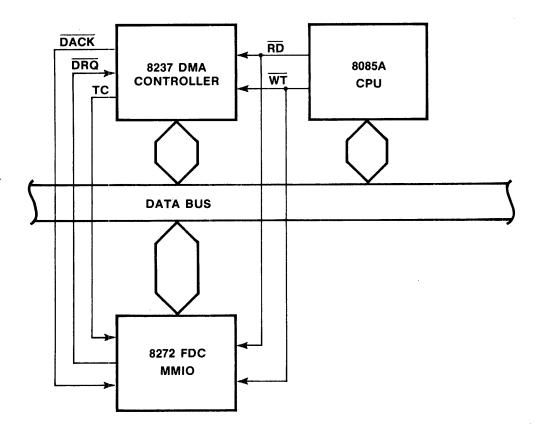

Signals provided by the 8272 FDC permit the iSBX 218 board to operate in the Direct Memory Access (DMA) mode or the Non-DMA mode. In the Non-DMA mode, the FDC generates interrupts to the processor to transfer each data byte. In the DMA mode, the processor initializes the DMA controller on the host board to perform all data transfers and then loads a command into the FDC. Figure 3-1

shows a typical configuration using the host iSBC board with an Intel 8085 microprocessor, 8237 DMA controller, and the associated busses. The iSBX 218 board must be configured with jumpers for either the DMA or Non-DMA mode operation, refer to paragraph 2-14. When using DMA mode the iSBX 218 requires the Terminal Count (TC) input signal.

#### 3-3. I/O ADDRESSING

The microprocessor on the host iSBC board communicates with the programmable 8272 FDC chip through a sequence of I/O Read and I/O Write Commands, via the iSBX connector (P1). The address of the iSBX I/O connector is determined by the host iSBC board configuration. There are three basic communication functions that occur between the host and the 8272 FDC chip and they are: read main status register; read from data register; and write into data register. Each function is specified by the state of  $A_0$ ,  $\overline{RD}$ , and  $\overline{WR}$  shown in table 3-1.

Table 3-1. Status/Data Register Selection

| <b>A</b> 0 | RD | WR | FUNCTION                  |

|------------|----|----|---------------------------|

| 0          | 0  | 1  | Read Main Status Register |

| 0          | 1  | 0  | Illegal                   |

| 0          | 0  | 0  | Illegal                   |

| 1          | 0  | 0  | Illegal                   |

| 1          | 0  | 1  | Read from Data Register   |

| 1          | 1  | 0  | Write into Data Register  |

#### 3-4. 8272 COMMAND SET

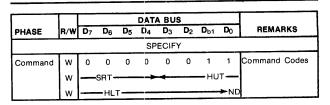

There are 15 separate commands that comprise the command set for the Intel 8272 FDC. These commands are loaded into the iSBX 218 board through connector P1. Each of these commands require multiple bytes to fully specify the operation that the FDC is to implement. The command set is as follows:

| Read Data          | Write Data              |

|--------------------|-------------------------|

| Read ID            | Format a Track          |

| Read Deleted Data  | Write Deleted Data      |

| Read a Track       | Seek                    |

| Scan Equal         | Recalibrate (Restore to |

| Scan High or Equal | Track 0)                |

| Scan Low or Equal  | Sense Interrupt Status  |

| Specify            | Sense Drive Status      |

|                    |                         |

Figure 3-1. 8272/DMA Mode Block Diagram

Typically, these commands are issued in short sequences of seek (to the desired track), followed by either a read, write, scan or format command, and finished by a sense command. Scan commands allow searching to take place in parallel with the host processor activity. Sense commands provide status of command operations. Specify commands provide initial 8272 timer information. Recalibrate moves the read/write head to track 0. Details of these commands are provided in following paragraphs of this chapter.

#### 3-5. 8272 REGISTERS — MAIN STATUS/ DATA REGISTERS

The 8272 contains two registers that are accessed by the host iSBC processor; a Status Register and a Data Register. The main status register can only be read by the host iSBC processor and is used to facilitate the transfer of data between the 8272 and processor. The 8-bit Main Status Register contains the status information of the FDC, and can be accessed at any time. Data bytes are written into the Data Register to program commands into the 8272.

Data bytes are also read out of the data register to obtain results after execution of a command. The 8-bit Data Register consists of several registers in a stack. Only one of these registers is presented to the data bus at a time. The data registers store data, commands, parameters, and Floppy Disk Drive (FDD) status information. The relationship between the main Status/Data registers and the signals  $\overline{RD}$ ,  $\overline{WR}$ , and  $A_0$  is shown in table 3-1.

#### 3-6. STATUS REGISTER

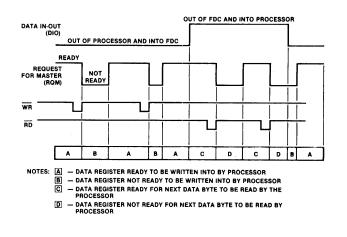

The Main Status Register bits are defined and listed in table 3-2. The DIO and RQM bits in the Status Register indicate when data is ready and in which direction it will be transferred on the data bus. Figure 3-2 shows the Status Register timing. Status Register bits for ST0 through ST3 are defined and listed in table 3-3. ST0-ST3 are status data registers which can only be accessed in sequence after a command completion.

Each of the 15 different commands executed by the 8272 FDC chip is initiated by multi-byte transfer

from the host processor, and the result, after execution, may also be a multi-byte transfer to the host processor. Each command is broken down into the following three phases:

a. Command Phase: The FDC receives all informa-

tion required to perform a particular operation from the

host iSBC processor.

b. Execution Phase: The FDC performs the opera-

tion it was instructed to do.

Table 3-2. Main Status Register Bits

| Bit<br>Number   | Name                                    | Symbol           | Description                                                                                                                                                                                                |

|-----------------|-----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB <sub>0</sub> | FDD 0 Busy                              | D <sub>0</sub> B | FDD number 0 is in the Seek mode.                                                                                                                                                                          |

| DB <sub>1</sub> | FDD 1 Busy                              | D₁B              | FDD number 1 is in the Seek mode.                                                                                                                                                                          |

| DB <sub>2</sub> | FDD 2 Busy                              | D <sub>2</sub> B | FDD number 2 is in the Seek mode.                                                                                                                                                                          |

| DB <sub>3</sub> | FDD 3 Busy                              | D <sub>3</sub> B | FDD number 3 is in the Seek mode.                                                                                                                                                                          |

| DB <sub>4</sub> | FDC Busy                                | СВ               | A read or write ** command is in process.                                                                                                                                                                  |

| DB <sub>5</sub> | Non-DMA mode                            | NDM              | The FDC is in the non-DMA mode. This bit is set only during the execution phase in non-DMA mode. Transition to "0" state indicates execution phase has ended.                                              |

| DB <sub>6</sub> | Data Input/Output  22 OUTPUT  1 = IMPUT | DIO              | Indicates direction of data transfer between FDC and Data Register. If DIO = "1" then transfer is from Data Register to the Processor. If DIO = "0", then transfer is from the Processor to Data Register. |

| DB <sub>7</sub> | Request for<br>Master                   | RQM              | Indicates Data Register is ready to send or receive data to or from the Processor. Both bits DIO and RQM should be used to perform the handshaking functions of "ready" and "direction" to the processor.  |

BITS 0 > 3 will stry high until Sense interrupt commanio is executed. c. Result Phase:

After completion of the operation, status and other house-keeping information are made available to the host iSBC processor.

During the command and result phases, the main status register must be read by the host CPU until DB7, Request for Master, is in a 1 state. This ensures that the 8272 is ready to accept or provide the next command or result byte before each byte of information is written into or read from the data register.

Bits DB6 and DB7 are in a 0 and 1 state, respectively, before each command word byte is written into the 8272. Many of the commands require multiple bytes, the main status register is read prior to each byte transfer to the 8272 FDC chip. During the result phase, DB6 and DB7 in the main status register are both 1's before reading each byte from the data register. Reading the main status register before each data byte transfer is required only in the command and result phases.

During the execution phase, in the Non-DMA mode, the receipt of each data byte (when reading data from the disk) is indicated by the interrupt signal (INT). Activation of the read signal  $\overline{\text{RD}}$  by the host CPU, resets the interrupt and loads the data register contents onto the data bus. When performing a write command, the  $\overline{\text{WR}}$  signal resets the interrupt signal. If the processor cannot handle interrupts fast enough (every  $13\mu\text{s}$  for M/M), it may poll the main status register where bit 7 (RQM) functions as the interrupt signal.

Figure 3-2. Status Register Timing

IN THE PROCESS OF READING RESULT BYTES OR WRITING PARAMETERS -

Table 3-3. Status Register

|                | BIT                |             |                                                                                                                                                                                                |  |  |  |  |  |

|----------------|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| No.            | Name               | Sym-<br>bol | DESCRIPTION                                                                                                                                                                                    |  |  |  |  |  |

|                |                    |             | TATUS REGISTER 0                                                                                                                                                                               |  |  |  |  |  |

| D <sub>7</sub> | Interrupt<br>Code  | IC          | D <sub>7</sub> = 0 and D <sub>6</sub> = 0<br>Normal Termination of Command.<br>(NT). Command was completed and<br>properly executed.                                                           |  |  |  |  |  |

| D <sub>6</sub> |                    |             | D <sub>7</sub> = 0 and D <sub>6</sub> = 1<br>Abnormal Termination of Command,<br>(AT). Execution of Command was started,<br>but was not successfully completed.                                |  |  |  |  |  |

|                |                    |             | D <sub>7</sub> = 1 and D <sub>6</sub> =0<br>Invalid Commandissue. (IC). Command<br>which was issuedwas never started.                                                                          |  |  |  |  |  |

|                |                    |             | D <sub>7</sub> = 1 and D <sub>6</sub> =1<br>Abnormal Termination because during<br>command execution the ready signal<br>from FDD changed state.                                               |  |  |  |  |  |

| D <sub>5</sub> | Seek End           | SE          | When the FDC completes the SEEK Command, this flag is set to 1 (high).                                                                                                                         |  |  |  |  |  |

| D4             | Equipment<br>Check | EC          | If a fault Signal is received from the FDD, or if the Track 0 Signal fails to occur after 77 Step Pulses (Recalibrate Command) then this flag is set.                                          |  |  |  |  |  |

| D <sub>3</sub> | Not Ready          | NR          | When the FDD is in the not-ready state and a read or write command is issued, this flag is set. If a read or write command is issued to Side 1 of a single sided drive, then this flag is set. |  |  |  |  |  |

| D <sub>2</sub> | Head<br>Address    | HD          | This flag is used to indicate the state of the head at Interrupt.                                                                                                                              |  |  |  |  |  |

| D <sub>1</sub> | Unit Select 1      | US 1        | These flags are used to indicate a Drive                                                                                                                                                       |  |  |  |  |  |

| D <sub>0</sub> | Unit Select 0      |             | Unit Number at Interrupt                                                                                                                                                                       |  |  |  |  |  |

|                |                    |             | TATUS REGISTER 1                                                                                                                                                                               |  |  |  |  |  |

| D <sub>7</sub> | End of<br>Cylinder | EN          | When the FDC tries to access a Sector beyond the final Sector of a Cylinder, this flag is set.                                                                                                 |  |  |  |  |  |

| D <sub>6</sub> |                    |             | Not used. This bit it always 0 (low).                                                                                                                                                          |  |  |  |  |  |

| D <sub>5</sub> | Data Error         | DE          | When the FDC detects a CRC error in either the ID field or the data field, this flag is set.                                                                                                   |  |  |  |  |  |

| D4             | Over Run           | OR          | If the FDC is not serviced by the main-<br>systems during data transfers, within a<br>certain time interval, this flag is set.                                                                 |  |  |  |  |  |

| D <sub>3</sub> |                    |             | Not used. This bit always 0 (low).                                                                                                                                                             |  |  |  |  |  |

| D <sub>2</sub> | No Data            | ND          | During execution of READ DATA, WRITE DELETED DATA or SCAN Command, if the FDC cannot find the Sector specified in the IDR Register, this flag is set.                                          |  |  |  |  |  |

|                |                    |             | During executing the READ ID Command, if the FDC cannot read the ID field without an error, then this flag is set.                                                                             |  |  |  |  |  |

|                |                    |             | During the execution of the READ A<br>Cylinder Command, if the starting sector<br>cannot be found, then this flag is set.                                                                      |  |  |  |  |  |

|                |                    |             |                                                                                                                                                                                                |  |  |  |  |  |

| l              | l                  | 1           |                                                                                                                                                                                                |  |  |  |  |  |

| ВІТ            |                                             |             |                                                                                                                                                                                                            |  |  |  |

|----------------|---------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No.            | Name                                        | Sym-<br>bol | DESCRIPTION                                                                                                                                                                                                |  |  |  |

|                | s                                           | TATU        | S REGISTER 1 (CON'T.)                                                                                                                                                                                      |  |  |  |

| D <sub>1</sub> | Not<br>Writable                             | NW          | During execution of WRITE DATA, WRITE DELETED DATA or Format A Cylinder Command, if the FDC detects a write protect signal from the FDD, then this flag is set.                                            |  |  |  |

| D <sub>0</sub> | Missing<br>Address<br>Mark                  | МА          | If the FDC cannot detect the ID Address<br>Mark after encountering the index hole<br>twice, then this flag is set.                                                                                         |  |  |  |

|                |                                             |             | If the FDC cannot detect the Data Address<br>Mark or Deleted Data Address Mark, this<br>flag is set. Also at the same time, the MD<br>(Missing Address Mark in Data Field) of<br>Status Register 2 is set. |  |  |  |

|                |                                             | S           | TATUS REGISTER 2                                                                                                                                                                                           |  |  |  |

| D <sub>7</sub> |                                             |             | Not used. This bit is always 0 (low).                                                                                                                                                                      |  |  |  |

| D <sub>6</sub> | Control<br>Mark                             | СМ          | During executing the READ DATA or<br>SCAN Command, if the FDC encounters a<br>Sector which contains a Deleted Data<br>Address Mark, this flag is set.                                                      |  |  |  |

| D <sub>5</sub> | Data Error<br>in Data Field                 | DD          | If the FDC detects a CRC error in the data field then this flag is set.                                                                                                                                    |  |  |  |

| D4             | Wrong<br>Cylinder                           | wc          | This bit is related with the ND bit, and when the contents of C on the medium is different from that stored in the IDR, this flag is set.                                                                  |  |  |  |

| D <sub>3</sub> | Scan Equal<br>Hit                           | SH          | During execution, the SCAN Command, if the condition of "equal" is satisfied, this flag is set.                                                                                                            |  |  |  |

| D <sub>2</sub> | Scan Not<br>Satisfied                       | SN          | During executing the SCAN Command, if the FDC cannot find a Sector on the cylinder which meets the condition, then this flag is set.                                                                       |  |  |  |

| D <sub>1</sub> | Bad<br>Cylinder                             | вс          | This bit is related with the ND bit, and when the content of C on the medium is different from that stored in the IDR and the content of C is FF, then this flag is set.                                   |  |  |  |

| D <sub>0</sub> | Missing<br>Address<br>Mark in<br>Data Field | MD          | When data is read from the medium, if the FDC cannot find a Data Address Mark, or Deleted Data Address Mark, then this flag is set.                                                                        |  |  |  |

|                |                                             | S           | TATUS REGISTER 3                                                                                                                                                                                           |  |  |  |

| D <sub>7</sub> | Fault                                       | FT          | This bit is used to indicate the status of the Fault signal from the FDD.                                                                                                                                  |  |  |  |

| D <sub>6</sub> | Write<br>Protected                          | WP          | This bit is used to indicate the status of the Write Protected signal from the FDD.                                                                                                                        |  |  |  |

| D <sub>5</sub> | Ready                                       | RDY         | This bit is used to indicate the status of the Ready signal from the FDD.                                                                                                                                  |  |  |  |

| D4             | Track 0                                     | T0          | This bit is used to indicate the status of the Track 0 signal from the FDD.                                                                                                                                |  |  |  |

| D <sub>3</sub> | Two Sided                                   | TS          | This bit is used to indicate the status of the Two Side signal from the FDD.                                                                                                                               |  |  |  |

| D <sub>2</sub> | Head<br>Address                             | HD          | This bit is used to indicate the status of Side Select signal to the FDD.                                                                                                                                  |  |  |  |

| D <sub>1</sub> | Unit Select 1                               |             | the Unit Select 1 signal to the FDD.                                                                                                                                                                       |  |  |  |

| D <sub>0</sub> | Unit Select 0                               | us o        | This bit is used to indicate the status of the Unit Select 0 signal to the FDD.                                                                                                                            |  |  |  |

During the execution phase, when performing a read in the DMA mode, interrupts are not generated for each data byte transfer. The 8272 generates DMA requests when each byte of data is available. The DMA controller responds with a DMA acknowledge and the RD signal. When the DMA acknowledge goes low, the DMA request is reset. When execution is completed (Terminal Count), the interrupt signal activates, indicating the beginning of the result phase. Reading of the first byte of data in the result phase (ST0) automatically resets the interrupt signal in the DMA mode.

During the result phase all bytes shown in the result part of each command must be read. The Read Data Command, for example, has seven bytes of data in the result phase. All seven bytes must be read to complete the Read Data Command. The 8272 FDC chip will not accept a new command until the previous command is completed.

The 8272 FDC chip contains five status registers. The main status register, table 3-2, mentioned previously, can be accessed by the host processor at any time. The other four status registers (ST0, ST1, ST2, ST3), table 3-3, are only available during the result phase, and are read as data from the Data Register only at the completion of the command. The number of status registers read is determined by the particular command executed.

The data bytes sent to the 8272 FDC chip comprising the command phase are read out during the result phase. The writing and reading of these data bytes is performed in the order shown for each command. After the last data byte in the command phase is written to the 8272 FDC chip, the execution phase starts automatically. When the last data byte is read out in the result phase, the command is automatically ended and the 8272 FDC chip is ready for a new command. A command may be aborted at any time by activating the Terminal Count signal. The host iSBC board must activate the Terminal Count (TC) signal when the proper number of drive data bytes have been written or read for a particular command.

#### 3-7. COMMAND DESCRIPTIONS

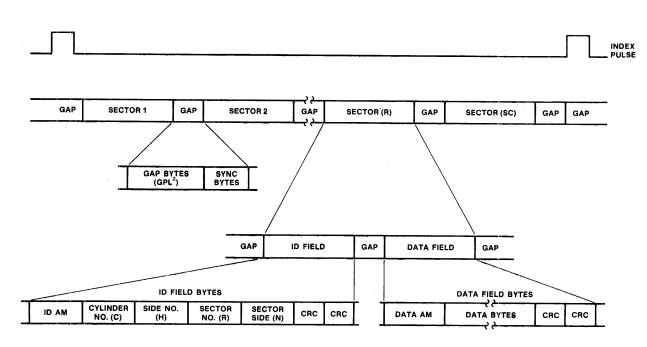

During the command phase, the main status register must be polled by the host processor before each byte is written into the data register. The DIO (DB6) and RQM (DB7) bits must be in the 0 and 1 states respectively, before each byte of the command is written into the 8272 FDC chip. The start of the execution phase of any command causes DIO and ROM to switch to 1 and 0 states respectively. The mnemonics for the byte designations for both the command and result phase of the command set are listed in table 3-4. Figure 3-3 is provided as a reference for typical track format definitions and

mnemonics used in the following command descriptions. The values of N, SC, and GPL for the various sector sizes are defined in Table 3-7. Paragraph 3-16 covers the specification of Head Load Time (HLT), Head Unload Time (HUT), and Step Rate Time (SRT) used in the execution of other commands.

#### 3-8. READ DATA

The Read Data command shown in figure 3-4 requires nine bytes to load the command and the command data. After execution, the host reads seven bytes to complete the result phase of the command. After the Read Data command is issued the FDC loads the heads (if they are not loaded), waits the specified head settling time and begins reading ID Address Marks and ID fields. When the current sector number (R=byte four of the command) stored in the ID register compares with the sector number read from the diskette, the FDC transfers data (from the data field) byte-by-byte to the data bus. The Read/Write head must have been previously positioned to the desired track by a Seek command.

After completion of the read operation from the current sector, the Sector Number is incremented by one, and the data from the next sector is read and set onto the data bus. This action constitutes a Multisector read operation. The read command is terminated by receipt of the Terminal Count signal. P. 4-3 Activation of Terminal Count causes the FDC to stop outputting data onto the data bus, but it continues to read data from the current sector, check CRC bytes (Cyclic Redundancy Count), and terminates the command at the end of the current sector read.

The amount of data transferred with a single command to the FDC depends on the MT-bit, MFMbit (byte 0 of the read command), and N-byte (byte five of the read command). The 'N' byte determines the number of bytes per sector. Table 3-5 lists the different transfer capacities, persuant to the different bit configurations.

The Multi-track function (MT) allows the FDC to STRRTS read data from both sides of the diskette. For a particular cylinder, the data transfer starts at Sector N Side 0 and ends at the last sector on Side 1. This function pertains to only one cylinder (the same track on each side of the diskette).

MLSO.

When N=0, the Data length (DTL), (byte nine of the command), defines the number of bytes the FDC considers a sector. If the DTL is smaller than the actual data length in the sector, the extra data in the sector is not sent to the data bus. The FDC reads (internally) the complete sector and performs the CRC check. Depending on the manner of command

3-5

termination, a Multi-sector read operation may be performed. When N=1, the DTL has no meaning and should be set to 0FFH.

At the completion of the read data command, the read/write head remains loaded until the specified Head Unload Time (HUT) has elapsed. If the host processor issues another command before the head unloads, the head settling time can be ignored between subsequent read operations.

If the FDC detects the Index Hole twice without finding the right sector, the FDC sets the No Data (ND) flag in status register 1 and terminates the read data command.

After reading the ID and Data fields in each sector, the FDC checks the CRC bytes. If a read error is detected in the ID field, the FDC sets the Data Error (DE) flag in status register 1. If a CRC error occurs in the data field, the FDC also sets the Data Error in the Data Field (DD) flag in status register 2, and terminates the command.

If the FDC reads a Deleted Data Address Mark from the diskette, and SK=0, the FDC sets the Control Mark (CM) flag in status register 2. The command is terminated after the complete sector is read. If SK=1, the FDC skips the sector with the Deleted Data Address Mark and reads the next sector.

Table 3-4. Command Mnemonics

| SYMBOL                         | NAME             | DESCRIPTION                                                                                                                     |

|--------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub>                 | Address Line 0   | $A_0$ controls selection of Main<br>Status Register ( $A_0$ = 0) or Data<br>Register ( $A_0$ = 1).                              |

| С                              | Cylinder Number  | C stands for the current selected<br>Cylinder track number 0 through<br>76 of the medium.                                       |

| D                              | Data             | D stands for the data pattern which is going to be written into a Sector.                                                       |

| D <sub>7</sub> -D <sub>0</sub> | Data Bus         | 8-bit Data Bus where $D_7$ is the most significant bit, and $D_0$ is the least significant bit.                                 |

| DS0, DS1                       | Drive Select     | DS stands for a selected drive number 0 or 1.                                                                                   |

| DTL                            | Data Length      | When N is defined as 00, DTL stands for the data length which users are going to read out or write into the Sector.             |

| EOT                            | End of Track     | EOT stands for the final Sector number of a Sylinder TRACK.                                                                     |

| GPL                            | Gap Length       | GPL stands for the length of Gap<br>3 (spacing between Sectors<br>excluding VCO Sync Field).                                    |

| Н                              | Head Address     | H stands for head number 0 or 1, as specified in ID field.                                                                      |

| HDS                            | Head Select      | HDS stands for a selected head number 0 or 1 (H = HDS in all command words).                                                    |

| HLT                            | Head Load Time   | HLT stands for the head load time in the FDD (2 to 254 ms in 2 ms increments).                                                  |

| HUT                            | Head Unload Time | HUT stands for the head unload<br>time after a read or write opera-<br>tion has occurred (16 to 240 ms<br>in 16 ms increments), |

| MFM                            | FM or MFM Mode   | If MF is low, FM mode is selected<br>and if it is high, MFM mode is<br>selected.                                                |

| МТ                             | Multi-Track      | If MT is high, a multi-track<br>operation is to be performed (a<br>cylinder under both HD0 and<br>HD1 will be read or written). |

|                                |                  |                                                                                                                                 |

| SYMBOL                       | NAME                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z                            | Number                                       | N stands for the number of data bytes written in a Sector.                                                                                                                                                                                                                                                                                                                                                         |