## SYSTEM 86/300 SERIES DIAGNOSTIC MAINTENANCE MANUAL

Order Number: 144813-004

# SYSTEM 86/300 SERIES DIAGNOSTIC MAINTENANCE MANUAL

Order Number: 144813-004

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update or to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9 (a) (9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BITBUS        | iLBX                               | iPDS            | Plug-A-Bubble |

|---------------|------------------------------------|-----------------|---------------|

| COMMputer     | i <sub>m</sub>                     | iRMX            | PROMPT        |

| CREDIT        | i M M X                            | iSBC            | Promware      |

| Data Pipeline | Insite                             | iSBX            | QUEX          |

| Genius        | int <sub>e</sub> l                 | iSDM            | QUEST         |

| Δ             | $int_e$ lBOS                       | iSXM            | Ripplemode    |

| 1             | Intelevision                       | Library Manager | RMX/80        |

| i             | int <sub>e</sub> ligent Identifier | Megachassis     | RUPI          |

| $I^2ICE$      | inteligent Programming             | MICROMAINFRAME  | Seamless      |

| ICE           | Intellec                           | MULTIBUS        | SOLO          |

| iCS           | Intellink                          | MULTICHANNEL    | SYSTEM 2000   |

| iDBP          | iOSP                               | MULTIMODULE     | UPI           |

| iDIS          |                                    |                 |               |

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

MULTIBUS is a patented Intel bus.

<sup>© 1984,</sup> Intel Corporation

| REV. | REV. REVISION HISTORY                                                                                                                                                                                  |       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| -001 | Original issue. Contains information formerly found in SYSTEM 86/300 SERIES DIAGNOSTIC REFERENCE MANUAL. This issue updates the SCT, adds the SDT8630 test, and updates the remaining SDT test suites. | 06/82 |

| -002 | Adds the SDT534 and SDT309 test suites.                                                                                                                                                                | 09/82 |

| -003 | Updates RSAT material.                                                                                                                                                                                 | 07/83 |

| -004 | Deletes RSAT material; reorganizes SCT and SDT material.                                                                                                                                               | 05/84 |

|      |                                                                                                                                                                                                        |       |

|      |                                                                                                                                                                                                        |       |

### CAUTION

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A Computing Device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

This manual explains how to use the System Confidence Test (SCT) and System Diagnostic Test (SDT) programs available for Intel System 86/300 Series Microcomputer Systems. You can use these programs to determine whether the system is operating properly and as an aid in troubleshooting malfunctions in the system's hardware. The information in this manual is intended for service and engineering personnel who understand how the System 300 Series microcomputers work.

### WARNING

There are hazardous voltages present within 86/300 Series Microcomputer systems. To avoid electrical shock and damage to the system observe the following precautions:

- 1. Do not work on the system unless you are technically qualified to do so.

- 2. Disconnect the power cord before performing any type of maintenance or service.

- 3. Always refer to the appropriate reference manuals for the correct service procedures for your system.

Briefly, the subjects covered in each chapter are as follows:

- Chapter 1 describes the System Confidence Test in detail. It tells you how to invoke the SCT and how to interpret the results of its tests. It also includes troubleshooting hints.

- Chapter 2 introduces the System Diagnostic Tests (SDTs). It tells you how to invoke the tests and how use the Test Management commands to control test execution and error reporting.

- Chapter 3 describes the SDTs for the processor boards used in the System 86/300 Series microcomputers.

- Chapter 4 describes the SDTs for the memory boards used in the System 86/300 Series microcomputers.

- Chapter 5 describes the System Diagnostic Tests for mass storage components used in the System 86/300 Series microcomputers.

- Chapter 6 describes the System Diagnostic Tests available for the optional communications expansion boards used in System 86/300 Series microcomputers.

- Appendix A describes how to modify the System Diagnostic Tests to suit your particular system.

### RELATED PUBLICATIONS

The following manuals contain information about the System 86/310 Microcomputer.

System 310 Installation and Operation Guide, Order Number 173211

System 310 Hardware Integration Guide, Order Number 173203

System 310 Hardware Maintenance Manual, Order Number 173208

The following manuals contain information about the System 86/380 and 86/330A Microcomputers.

Introduction To The System 86/380 And System 86/330A Microcomputer Systems, Order Number 172758

System 86/330A Hardware Reference Manual, Order Number 172759

System 86/380 Hardware Reference Manual, Order Number 172761

The following manuals contain information about software used on the System 86/300 Series microcomputers.

iRMX™86 Release 5 Basic I/O System Reference Manual for System 86/300 Series Microcomputer Systems, Order Number 172766

iRMX86 Release 5 Extended I/O System Reference Manual for System 86/300 Series Microcomputer Systems, Order Number 172767

The following manuals contain information about hardware components used in System 86/300 Series microcomputer systems.

iSBC  $^{\circ}$  86/14 and iSBC 86/30 Single Board Computer Hardware Reference Manual, Order Number 144044

- iSBC 86/12A Single Board Computer Hardware Reference Manual, Order Number 9803074

- iSBC 337 MULTIMODULE™ Numeric Data Processor Hardware Reference Manual, Order Number 142887

- iSBC 016A/032A/064A/028A/056A RAM Board Hardware Reference Manual, Order Number 143572

- iSBC 308/309 Memory Management and Protection MULTIMODULE Board Hardware Reference Manual, Order Number 144686

- iSBC 215G Winchester Disk Controller Hardware Reference Manual,Order Number 144780

- iSBX™ 218A Flexible Diskette Controller Board Hardware Reference Manual, Order Number 145911

- iSBX 351 Serial MULTIMODULE Board Hardware Reference Manual, Order Number 9803190

- iSBC 534 Four-Channel Communications Expansion Board Hardware Reference Manual, Order Number 9800450

- iSBC 544 Intelligent Communications Controller Board Hardware Reference Manual, Order Number 9800616

United States customers may obtain service and repair assistance by contacting the Intel Product Service Center in Phoenix, Arizona. Customers outside the United States should contact their sales source (Intel Sales Office or Authorized Distributor) for service information.

Before calling the Product Service Center you should have the following information:

- The date you received the product.

- The complete part number (including the dash number) of the product. This number is usually silk-screened onto printed circuit boards and stamped on the label of other products.

- The serial number of the product. This is usually silk-screened onto printed circuit boards and stamped on the label of other products.

- Your shipping and billing addresses.

- Λ purchase order number for billing purposes if your Intel product warranty has expired.

- Extended warranty agreement information, if applicable.

### SERVICE AND REPAIR ASSISTANCE

Use the following telephone numbers to contact the Intel Product Service Marketing Administration group:

| Regional Telephone Numbers |                                                    |  |

|----------------------------|----------------------------------------------------|--|

| (602) 869-4951             | 910-951-1330                                       |  |

| $(602)\ 869-4392$          | 910-951-0687                                       |  |

| (602) 869-4045             |                                                    |  |

| (602) 869-4391             |                                                    |  |

|                            | (602) 869-4951<br>(602) 869-4392<br>(602) 869-4045 |  |

Always contact the Intel Product Service Marketing Administration group before returning a product to Intel for repair. When you make the request you will be given a repair authorization number, shipping instructions, and other information that will help Intel provide you with fast, efficient service.

If you are returning a product because of damage sustained during shipment or if the product is out of warranty, a purchase order is required before Intel can initiate repair.

Use the original factory packaging material in preparing a product for shipment to the repair center. If that material is not available, ensure the product is adequately protected by wrapping it in cushioning material before enclosing it in a heavy-duty corrugated shipping carton. All cartons should be labeled "FRAGILE" to ensure careful handling. If a printed circuit board is being returned, a material such as Air Cap TH-240, manufactured by the Sealed Air Corporation of Hawthorne, New Jersey, should be used to give adequate cushioning.

Address and ship only to the address specified by Intel Product Service Marketing Administration group personnel.

### CONTENTS

| CHAPTER 1                                         | PAGE |

|---------------------------------------------------|------|

| SYSTEM CONFIDENCE TEST                            |      |

| Running the SCT                                   | 1-1  |

| Test Descriptions                                 | 1-4  |

| USART/Timer Test                                  | 1-4  |

| USART/Timer Errors                                | 1-4  |

| Programmable Interrupt Controller Test            | 1-5  |

| PIC Errors                                        | 1-5  |

| ROM Test                                          | 1-5  |

| Programmable Peripheral Interface Test            | 1-6  |

| PPI Errors                                        | 1-6  |

| Memory Test                                       | 1-6  |

| Memory Errors                                     | 1-7  |

| Winchester Test                                   | 1-7  |

| Winchester Errors                                 | 1-8  |

| Flexible Diskette Test                            | 1-9  |

| Flexible Diskette Errors                          | 1-9  |

| Tape Test                                         | 1-9  |

| Tape Errors                                       | 1-9  |

| Additional Troubleshooting Hints                  | 1-10 |

| Additional froubleshooting finits                 | 1 10 |

| CHAPTER 2                                         |      |

| USING THE SYSTEM DIAGNOSTIC TESTS                 |      |

| System 86/300 Diagnostic Diskettes                | 2-2  |

| Installing the SDT Test Suites on Winchester Disk | 2-2  |

| Loading an SDT into Memory                        | 2-3  |

| Test Management Commands                          | 2-4  |

| Command Notation and Usage                        | 2-5  |

| Syntax Diagrams                                   | 2-4  |

| Abbreviations                                     | 2-5  |

| Continuation Lines and Comments                   | 2-6  |

| Command Delimiters                                | 2-6  |

| Input Radices                                     | 2-7  |

| Test Range Parameter                              | 2-7  |

| CLEAR Command                                     | 2-8  |

| DEBUG Command                                     | 2-8  |

|                                                   | 2-9  |

| DESCRIBE Command                                  | 2-10 |

| ERRONLY Command                                   |      |

| EXIT Command                                      | 2-10 |

| IGNORE Command                                    | 2-11 |

| LIST Command                                      | 2-11 |

| QUERY Command                                     | 2-12 |

| RECOGNIZE Command                                 | 2-13 |

| REPEAT and ENDREPEAT Commands                     | 2-13 |

| RESET Command                                     | 2-15 |

| SUMMARY Command                                   | 2-15 |

| TEST Command                                      | 2-17 |

|                                                | PAGE                |

|------------------------------------------------|---------------------|

| V Command                                      | 2-19                |

| Interrupting the Diagnostic Tests              | 2-20                |

| CHAPTER 3                                      |                     |

| PROCESSOR SYSTEM DIAGNOSTIC TESTS              |                     |

| SDT8630 Test Suite                             | 3-1                 |

| SDT8630 Initialization                         | 3-1                 |

| Using the RESET Command                        | 3-3                 |

| SDT8630 Test 0, ROM Checksum                   | 3-3                 |

| SDT8630 Test 1, Parallel Port                  | 3-3                 |

| SDT8630 Test 2, PIC                            | 3-3                 |

| SDT8630 Test 3, Timer                          | 3-4                 |

| SDT8630 Test 4, Fixed Patterns                 | 3-5                 |

| SDT8630 Test 5, Address March                  | 3-5                 |

| SDT8630 Test 6, iSBC 86/30 Sliding Ones        | 3-5                 |

| SDT8630 Test 7, Dual Port RAM Contention       | 3-5                 |

| SDT8612 Test Suite                             | 3-7                 |

| SDT8612 Test 0, ROM Checksum                   | 3-8                 |

| SDT8612 Test 1, Parallel Port                  | 3-8                 |

| SDT8612 Test 2, PIC                            | 3-8                 |

| SDT8612 Test 3, Timer                          | 3-9                 |

| SDT8612 Test 4, Fixed Patterns                 |                     |

| (iSBC 86/12A Board)                            | 3-9                 |

| SDT8612 Test 5, Fixed Patterns                 |                     |

| (iSBC 300A Board)                              | 3-10                |

| SDT8612 Test 6, Address Patterns               | 3-10                |

| SDT8612 Test 7, Sliding Ones                   | 3-10                |

| SDT8612 Test 8, Sliding Ones (iSBC 300A Board) | 3-10                |

| SDT8612 Test 9, Dual Port RAM Contention       | 3-10                |

| SDT337 Test Suite                              | 3-12                |

| CHAPTER 4                                      |                     |

| MEMORY SYSTEM DIAGNOSTIC TESTS                 |                     |

| SDTRAM Test Suite                              | 4-1                 |

| SDTRAM Initialization                          | 4-1                 |

| Using the RESET Command                        | 4-2<br>4-7          |

| SDTRAM Test 0, Fixed Patterns                  |                     |

| SDTRAM Test 1, Address March                   | 4-10<br>4-10        |

| SDTRAM Test 1, Address March                   | 4-10                |

| SDTRAM Test 3, Execute from RAM                | 4-11                |

| SDTRAM Test 4, A-Series Parity Logic and RAMs  | 4-11                |

| SDTRAM Test 5, A-Series Interrupt Detection    | $\frac{4-11}{4-12}$ |

| SDTRAM Test 6, C-Series Check Bit Logic        | 4-12                |

| SDTRAM Test 7, C-Series Check Bit RAMs         | 4-12                |

| SDTRAM Test 8, C-Series Error Correction       | 4-12                |

| SDTRAM Test 9, C-Series Interrupt Detection    | $\frac{4-12}{4-13}$ |

| SDTRAM Test A, Rd/Wr Scope Loop Utility        | 4-13                |

| SDT309 Test Suite                              | 4-13                |

| SDT309 Initialization                          | 4-14                |

| SDT309 Test 0, Interrupt Processing            | 4-14                |

| SDT309 Test 1, Exception Conditions            | 4-17                |

| SDT309 Test 2, Physical Address Verification   |                     |

| SDT309 Test 3, Memory Bounds                      | 4-20         |

|---------------------------------------------------|--------------|

|                                                   | 4-20         |

| · · · · · · · · · · · · · · · · · · ·             | 4-20         |

| CVI A DEFINE                                      |              |

| CHAPTER 5 MASS STORAGE SYSTEM DIAGNOSTIC TESTS    |              |

| SDTWIN Test Suite                                 | 5-1          |

| SDTWIN Initialization                             | 5-2          |

| Using the RESET Command                           | 5-5          |

| SDTWIN Test 0, Reset/Initialize Disk Test         | 5-5          |

| SDTWIN Test 1, ROM Checksum Test                  | 5-5          |

| SDTWIN Test 2, RAM Window Test                    | 5-5          |

| SDTWIN Test 3, RAM Address Test                   | 5-6          |

| SDTWIN Test 4, Transfer Status                    | 5-6          |

| SDTWIN Test 5, Buffer I/O Test                    | 5-6          |

| SDTWIN Test 6, Format Diagnostic Track            | 5-6          |

| SDTWIN Test 7, Microdiagnostic Test               | 5-7          |

| SDTWIN Test 8, Verify Format/Format Test          | 5-7          |

| SDTWIN Test 9, Seek/Verify Test                   | 5-7          |

| SDTWIN Test A, Worst-Case Seek Test               | 5-8          |

| SDTWIN Test B, Read/Write/Verify Diagnostic Track | 5-8          |

| SDTWIN Test C, Drive Selection Test               | 5-8          |

| SDTWIN Test D, Platter/Head Selection Test        | 5-8          |

| SDTWIN Test E. Sector Selection Test              | 5-9          |

| SDTWIN Test 10 Alternate Track Test               | 5-9          |

| SDTWIN Test 10, Alternate Track Test              | 5-9<br>5-9   |

| SDTWIN Test 11, Zero Fill Test                    | 5-9<br>5-9   |

|                                                   | 5-9<br>5-10  |

|                                                   | 5-10         |

| · · · · · · · · · · · · · · · · · · ·             | 5-10         |

|                                                   | 5-11         |

|                                                   | 5-11         |

|                                                   | 5-12         |

| SDTWIN Test 1B, Display/Edit Defective Track List | 0 12         |

|                                                   | 5-12         |

| SDTWIN Test 1C, Display/Clear Error Log Utility   | 5-12         |

| <b>O</b>                                          | 5-12         |

| 3                                                 | 5-14         |

|                                                   | 5-17         |

|                                                   | 5-18         |

| 0                                                 | 5-20         |

|                                                   | 5-21         |

| ·                                                 | 5-21         |

|                                                   | 5-21         |

|                                                   | 5-21         |

| , , , , , , , , , , , , , , , , , , ,             | 5-21         |

| •                                                 | 5-22         |

| , , , , , , , , , , , , , , , , , , ,             | 5-22<br>5-22 |

|                                                   | 5-22<br>5-22 |

| · ·                                               | 5-22         |

|                                                   | 5-27         |

|                                                   | 5-29         |

|                                                    | PAGE   |

|----------------------------------------------------|--------|

| CHAPTER 6                                          |        |

| COMMUNICATIONS SYSTEM DIAGNOSTIC TESTS             |        |

| SDT351 Test Suite                                  | 6-1    |

| SDT351 Initialization                              | 6-1    |

| Using the RESET Command                            | 6-4    |

| SDT351 Test 0, PIT Initialization                  | 6-5    |

| SDT351 Test 1, USART Initialization                | 6-6    |

| SDT351 Test 2, USART Interrupts                    | 6-8    |

| SDT351 Test 3, Baud Rate Verification              | 6-9    |

| SDT351 Test 4, Character Transmitter               | 6-10   |

| SDT351 Test 5, Character Receiver                  | 6-10   |

| SDT534 Test Suite                                  | 6-11   |

| SDT534 Initialization                              | 6-11   |

| Using the RESET SOFTWARE Command                   | 6-13   |

| Using the RESET HARDWARE Command                   | 6-15   |

| SDT534 Test 0, PIT Initialization                  | 6-15   |

| SDT534 Test 1, USART Initialization                | 6-16   |

| SDT534 Test 2, PIC Initialization                  | 6-17   |

| SDT534 Test 2, FIG Initialization                  | 6-17   |

| SDT534 Test 4, USART Interrupt Verification        | 6-17   |

|                                                    | 0-1(   |

| SDT534 Test 5, PIT Timer 4 and 5 Interrupt         | 0 10   |

| Verification                                       | 6-19   |

| SDT534 Test 6, Baud Rate Verification              | 6-20   |

| SDT534 Test 7, USART Load Test                     | 6-20   |

| SDT534 Test 8, USART Character Transmitter         | 6-20   |

| SDT534 Test 9, USART Character Receiver            | 6-21   |

| SDT544 Test Suite                                  | 6-22   |

| SDT544 Initialization                              | 6-22   |

| Using the RESET SOFTWARE Command                   | 6-25   |

| Using the RESET HARDWARE Command                   | 6-26   |

| SDT544 Test 0, MULTIBUS RAM Test                   | 6-27   |

| SDT544 Test 1, iRMX86/XENIX 86 Firmware Jump-Out   |        |

| Command Test                                       | 6-28   |

| SDT544 Test 2, Dual Port RAM                       | 6 - 29 |

| SDT544 Test 3, Board Interrupt Verification        | 6-29   |

| SDT544 Test 4, iRMX 86/XENIX 86 Firmware           |        |

| Verification                                       | 6-30   |

| SDT544 Test 5, PIT Initialization                  | 6-31   |

| SDT544 Test 6, USART Initialization                | 6-32   |

| SDT544 Test 7, PIC Initialization                  | 6-33   |

| SDT544 Test 8, PPI Port A Verification             | 6-34   |

| SDT544 Test 9, USART Interrupt Verification        | 6-34   |

| SDT544 Test A, Baud Rate Verification              | 6-35   |

| SDT544 Test B, Port Character Transmitter          | 6-35   |

| SDT544 Test C, Port Character Receiver             | 6-36   |

|                                                    |        |

| APPENDIX A CONFIGURING THE SYSTEM DIAGNOSTIC TESTS |        |

| Making Changes to the Test Suites                  | A-1    |

| maning changes to the rest buttes                  | M-1    |

| INDEX                                              |        |

xiv

### TABLES

| TAB  | E TITLE                        | PAGE |

|------|--------------------------------|------|

| 3-1  | SDT8630 Tests                  | 3-1  |

| 3-2  | SDT8612 Tests                  | 3-7  |

| 4-1  | SDTRAM Tests                   | 4-1  |

| 4-2  | SDT309 Tests                   | 4-14 |

| 5-1  | SDTWIN Tests                   | 5-1  |

| 5-2  | SDT218 Tests                   | 5-17 |

| 6-1  | SDT351 Tests                   | 6-1  |

| 6-2  | USART Modes of Operation       | 6-6  |

| 6-3  | SDT534 Tests                   | 6-11 |

| 6-4  | SDT544 Tests                   | 6-22 |

| FIGU | RES                            |      |

| FIGU | RE TITLE                       | PAGE |

| 1-1  | System Confidence Test Display | 1-3  |

## CHAPTER 1 SYSTEM CONFIDENCE TEST

The System Confidence Test (SCT) is a self-test program supplied as part of the system firmware in factory-standard System 86/300 Series microcomputers. The SCT tests the following major subsystems:

- Serial I/O port on the processor board

- Parallel I/O port on the processor board

- RAM on the processor and memory boards

- ROM on the processor board

- Priority interrupt controller on the processor board

- Winchester disk drive and controller

- Flexible diskette drives and controller

- Tape drive and controller

There are two versions of the SCT: one for systems with Winchester drives (SCT 86/300W firmware) and one for systems having only flexible drives (SCT 86/300F firmware). The two SCT versions are identical except that SCT 86/300F contains no tests for the Winchester or Tape systems.

### RUNNING THE SCT

In order to run the SCT, the processor board must be at least partly functional, otherwise the tests cannot begin. The microprocessor must be running and able to access at least part of the on-board ROM and RAM, and the RS-232 port on the processor board (normally used for the system console) must be working well enough that the test results can be reported on the terminal.

To run the SCT, proceed as follows:

- 1. Set up a Video Display Terminal for 9600 baud operation (see note following step 2), with parity off, and connect it to the processor board's RS-232 port on the rear panel. Turn the terminal on and let it warm up.

- 2. Turn on the system. (If it is already on, press the Reset switch.) After a short delay, the system begins sending a series of asterisks to the terminal.

### NOTE

Strictly speaking, the terminal does not have to be set up for 9600 baud, since the firmware contains an automatic baud rate determining feature that is activated when you enter an uppercase "U" just after power-up (step 3). However, if the terminal is not set to 9600 baud, no asterisks will be displayed on the terminal at power-up or reset.

- 3. Enter an uppercase U on the terminal's keyboard. The U initiates the SCT. (If you do not enter the U, the system eventually starts the SCT anyway, with slightly different results--this is discussed later in this section.)

- 4. Shortly after you enter the uppercase U, the system will display a message asking you for input from the keyboard. The display appears approximately as follows:

TEST USART/Timer PIC. \*. INPUT "I" STATUS

At this point you have four options:

- a. Do nothing. If you do not respond within six seconds, the PIC (programmable interrupt controller) test is reported "NO GO" and control of the system passes to the system monitor program. You can press the Reset switch to start testing again.

- b. Cause the SCT to continue by entering any character except CONTROL-C, CONTROL-D, or CONTROL-L. (CONTROL-D and CONTROL-L will cause the system to "hang up.")

- c. Abort testing and return control of the system to the system monitor by entering CONTROL-C.

- d. Select extended memory testing by entering the letter m (upper- or lowercase). For each error, the SCT displays the segment and offset address of the error, the expected data and the actual data read at that location, and the Exclusive-OR of the actual and expected data (showing the locations of the bits that were in error). See "Memory Tests" later in this Chapter.

As the SCT proceeds, the terminal display shows which part of the system is being tested and the status of that part. The display shown in Figure 1-1 is typical of one produced by a Winchester-disk-based

| SCT 86/300W, V1.2     | Co            | pyright 1982, 1983 Intel | Corporation |

|-----------------------|---------------|--------------------------|-------------|

| TEST                  |               |                          | STATUS      |

| <b>USART/ Timer</b>   |               |                          | GO          |

| PIC                   | .*. Input "I" | •                        | GO          |

| ROMCKSM               |               |                          | GO          |

| PPI                   |               |                          | GO          |

| Processor Subs        | ystem         |                          | GO          |

| Onboard               |               |                          | GO          |

| Offboard              |               |                          | GO          |

| Memory Subsy          | stem          | Total Memory = 768K      | GO          |

| Winchester            |               |                          | GO          |

| Floppy                |               |                          | GO          |

| Tape                  |               |                          | OFFLINE     |

| <b>Boot Subsyster</b> | m             |                          | GO          |

SCT Successful...Now Booting System

Figure 1-1. System Confidence Test Display

system. For testing purposes, the system is divided into three subsystems: processor, memory, and boot (disk) subsystems. The subsystems are further divided into component parts, such as the priority interrupt controller or the parallel port in the processor subsystem. As each part passes a test, the SCT displays a period (.) just to the right of the part's name; a failed test is indicated by a question mark. If the part passes all tests, its status is GO; any failed test produces a NO GO status. A diskette or tape drive may be reported OFFLINE if no diskette is installed or the drive is disconnected.

Shown below is an abbreviated SCT display that occurs when you do not respond at initialization by entering the uppercase "U." This display indicates only the status of the major subsystems.

| SCT 86/300W, V1.2   | Copyright 1982, 1983 Intel Corporation |    |  |

|---------------------|----------------------------------------|----|--|

| Processor Subsystem |                                        | GO |  |

| Memory Subsystem    | Total Memory = 768K                    | GO |  |

| Boot Subsystem      | •                                      | GO |  |

### SCT Successful...Now Booting System

Notice that (if you have a diskette installed) as the SCT accesses the flexible diskette drive during testing, the head load indicator on the front of the drive goes on and you can hear the head mechanism as it moves from track to track. This can be a useful indication of

processor and disk subsystem activity if the RS-232 port is not working, or if there is no terminal connected to the port.

You can abort the SCT at any time by entering CONTROL-C on the keyboard or by pressing the Interrupt switch on the front panel. These actions return control of system to the system monitor.

If the tests run without errors, control transfers to the Bootstrap Loader. If the SCT detects an error, control passes to the system monitor at completion of the test.

In situations where you need to reload the system software frequently you can bypass the SCT (and save the contents of RAM) by pressing the Interrupt switch within two seconds after pressing the Reset switch. You may find this useful during system software debugging.

### TEST DESCRIPTIONS

The following sections describe the individual SCT tests in detail. For each test there is an operational description followed by an interpretation of the test's error messages.

### **USART/TIMER TEST**

USART/TIMER The test checks the 8251A Universal Synchronous/Asynchronous Receiver-Transmitter (USART) and the 8253 Programmable Interval Timer (PIT) on the processor board. First the USART and PIT are initialized. Next the USART is tested by transmitting a character (the first asterisk that appears on the display screen after power-up or reset), then reading the USART's status register. If the TxReady bit in the status register indicates that the USART was able to shift the character out of its transmit buffer, the USART and PIT are considered to have passed their tests. This does not guarantee that the terminal connected to the RS-232 port received the character.

### **USART/Timer Errors**

If the HALT and RUN indicators flash alternately (System 86/330 and 86/380) or the the RUN indicator flashes on and off (System 86/310), replace the processor board. If no asterisks appear on the terminal and the HALT and RUN indicators do not flash, take the following corrective actions:

- 1. Check that the terminal is operating properly and that it is set to 9600 baud, no parity.

- 2. Check that the RS-232 cable is securely connected.

- 3. Check the voltage on the +12 and -12 volt power supplies.

- 4. Replace the processor board.

### PROGRAMMABLE INTERRUPT CONTROLLER TEST

The Programmable Interrupt Controller Test checks the 8259A Programmable Interrupt Controller (PIC) on the processor board. First the test program initializes the PIC and reads the mask register within the PIC. The test program then tests the PIC using interrupt requests from three sources: the timer, the USART's transmitter, and the USART's receiver. If any of these interrupts does not occur, an error condition is reported on the terminal. In testing the USART receiver interrupt, the test program prompts you to enter a character on the terminal's keyboard (as explained earlier under "Running the SCT"). If the receiver interrupt request does not come within six seconds, the test program indicates an error condition and goes on to subsequent tests.

### Priority Interrupt Controller Errors

Errors found during the PIC test are displayed on the terminal's screen as follows:

| PIC | ?   | *?  | INPUT "I" | <u>i</u> ? | NO GO |

|-----|-----|-----|-----------|------------|-------|

|     | (1) | (2) |           | (3)        | (4)   |

- 1. A question mark at position 1 indicates that the timer interrupt did not occur. To correct this malfunction, replace the processor board.

- 2. A question mark at position 2 indicates that the USART transmit interrupt did not occur. The "\*" displayed just in front of the question mark is the character sent by the USART to check the transmit interrupt. To correct this malfunction replace the processor board.

- 3. A question mark at position 3 indicates that the USART receive interrupt did not occur. The "i" just in front of the question mark represents the character entered on the keyboard in response to the INPUT "I" prompt. If the interrupt does not occur within six seconds, the question mark is displayed and the test program goes on to other tests. To correct this malfunction (if you entered a character and still got an error) replace the processor board.

- 4. The "NO GO" message is displayed when any interrupt does not occur.

### ROM TEST

The ROM test verifies the contents of the ROM on the processor board and checks that the address and data lines to the ROM are operating properly.

The ROM test accesses all ROM locations and calculates a checksum of their contents. The calculated checksum is compared with a checksum stored in the ROM. If the checksums match, a "GO" message appears on the CRT; if the checksums do not match, a "NO GO" message appears.

### PROGRAMMABLE PERIPHERAL INTERFACE TEST

The Programmable Peripheral Interface Test checks the 8255A Programmable Peripheral Interface (PPI) that drives the parallel port on the processor board. The test first initializes the PPI and sends a value to each of the PPI's three ports. The test then reads each port and the data read is compared with the data sent.

### NOTE

If your system is connected to an Intel Micro-computer Development System via the parallel port, the SCT will report the PPI "OFFLINE" and will go on to subsequent tests.

### PPI Errors

Errors found during the PPI test are reported on the terminal's display screen as follows:

| PPI | ?   | ?   | ?   | NO GO |

|-----|-----|-----|-----|-------|

|     | (1) | (2) | (3) | (4)   |

- 1. A question mark at position 1 indicates a failure at port A. Replace the processor board to correct this malfunction.

- 2. A question mark at position 2 indicates a failure at port B. Replace the processor board to correct the malfunction.

- 3. A question mark at position 3 indicates a failure at port C. Replace the processor board to correct this malfunction.

- 4. A failure at any of the ports results in a "NO GO" status.

### MEMORY TEST

The Memory Test checks the system's Random Access Memory (RAM), both on and off the processor board. For testing purposes, the the RAM is divided into two areas: on-board RAM, which consists of all RAM on the processor board; off-board RAM, which consists of the RAM normally contained on separate memory boards in factory-standard versions of the system.

In two successive passes, the memory test writes a checkerboard pattern of ones and zeros (A55AH on one pass; 5AA5H on the next) into RAM. During each pass the test reads the RAM to verify that the data read matches the data written and that the data bytes are at the proper addresses. This verifies that the RAM devices, data paths, and address lines are functioning properly. Memory locations from 0000:0000H through C000:000FH (768K) are tested, provided that all blocks of memory are contiguous (no gaps beginning at 16K boundaries).

Extended testing, which goes beyond the checkerboard pattern test and provides more detailed error reporting, may be selected by entering "m" during the PIC test.

### Memory Errors

If any errors are found during testing, a NO GO message appears in the status column for the area (on-board or off-board) in which the error occurred. If a failure is reported in on-board memory, replace the processor board; otherwise replace the appropriate memory board.

Errors found during extended testing (selected by entering "m" during the PIC test) are reported on the terminal as follows:

| Error at | <b>3333:</b> aaaa                                                                           | RECrrrr      | EXPeeee    | XORxxxxxxx                      | xxxxxxxx  |

|----------|---------------------------------------------------------------------------------------------|--------------|------------|---------------------------------|-----------|

| where    |                                                                                             |              |            |                                 |           |

| SSSS     | is the seg                                                                                  | ment porti   | on of the  | address where                   | the error |

| aaaa     | is the off occurred.                                                                        | set portion  | n of the a | ddress where                    | the error |

| rrrr     | is the data occurred.                                                                       | a actually r | ead at the | address where                   | the error |

| eeee     | is the data that the test program expected to find at the address where the error occurred. |              |            |                                 |           |

| x        |                                                                                             |              |            | ting the Exclusions of the bits |           |

### WINCHESTER TEST

The Winchester Test checks the iSBC 215G® Winchester Disk Controller and the Winchester disk drive. The Winchester test has three subtests; each subtest must be passed before the next one can start. The subtests are as follows:

Winchester controller and drive initialization

- Winchester controller on-board diagnostics invocation

- Winchester controller interrupt generation

### Winchester Errors

Errors found during the Winchester test are reported on the terminal as follows:

| Winchester | ?   | ?   | ?   | NO GO |

|------------|-----|-----|-----|-------|

|            | (1) | (2) | (3) | (4)   |

1. A question mark in position 1 indicates that the Winchester controller and drive could not be initialized.

Since the processor communicates with the Winchester controller by means of "control blocks" in memory, a memory failure can cause a Winchester initialization failure as well. If a memory error is reported, replace the appropriate memory board before replacing any Winchester component.

If no memory error is reported, take the following steps, checking the system after each step.

- a. In 8-inch drive systems, ensure that the head is unlocked. Check all interconnecting cables.

- b. Make sure that the disk is properly formatted, using a program such as DISKVERIFY, which is supplied with the iRMX 86 operating system. If a format problem is found, reformat the disk.

### **CAUTION**

Reformatting destroys all data on the disk. Make a back-up copy of the files on the disk before reformatting.

- c. Replace the Winchester controller (after checking that jumpers are properly set).

- d. Replace the Winchester drive.

- 2. A question mark at position 2 indicates that an error was found by the Winchester controller's diagnostics. Corrective action is the same as in steps a through d for the initialization error.

- 3. A question mark at position 3 indicates that a Winchester controller interrupt did not occur. If the PIC also failed its test, replace the processor board; otherwise, replace the Winchester controller board.

#### FLEXIBLE DISKETTE TEST

The Flexible Diskette Test checks the iSBX<sup>™</sup> 218A Flexible Diskette Controller and the flexible diskette drives. First the controller is initialized, then track 0 on the diskette is read to determine diskette characteristics. If the initialization fails, the controller status register is read to determine if the drive is "not ready" (door open or cable disconnected) or a fault condition exists. If the drive is not ready, it is reported "OFFLINE."

### Flexible Diskette Errors

For systems containing a Winchester disk (where the iSBC 218A board flexible diskette controller is mounted on the iSBC 215 board and SCT 86/300W firmware is used), errors found by the Flexible Diskette Test are reported on the terminal as follows:

Floppy ? NO GO

For systems containing only flexible diskette drives (where the iSBC 218A board is mounted on the iSBC 86/30 board, and SCT 86/300F firmware is used) the Flexible Diskette Test reports errors as follows:

Floppy ? ? NO GO

The first question mark indicates an initialization failure; the second indicates an iSBC 218A interrupt failure. To correct flexible diskette errors, take the following steps:

- 1. Check that the diskette is properly formatted using a verification program such as DISKVERIFY, which is supplied with the iRMX 86 operating system.

- 2. Check that the jumper settings on the iSBC 218A and its host board are correct.

- 2. Replace the flexible diskette controller.

- 3. Replace the diskette drive.

### TAPE TEST

The Tape Test initializes and verifies the operation of the iSBX 217B Cartridge Tape Drive Controller and tape drive. The tape system is reported "OFFLINE" if the drive is "not ready" (cartridge not in place or drive disconnected).

### Tape Errors

Errors found during the tape test are reported on the terminal as follows:

Tape ? NO GO

If a tape error is reported, take the following corrective actions.

- 1. Make sure that the tape format is correct.

- 2. Replace the iSBX 217B board.

- 3. Replace the tape drive.

### ADDITIONAL TROUBLESHOOTING HINTS

The System Diagnostic Tests (SDTs), to which the remaining chapters of this manual are devoted, provide more extensive testing and more detailed error reporting than the SCT. You should run the appropriate SDT if any of the SCT tests report an error.

Before replacing any hardware, check the jumper settings on the circuit boards. An improper jumper configuration on a circuit board could cause the tests for that board (and other boards) to report errors. Also, when disk drive errors occur, check the configuration of the drives before replacing any of the hardware. Refer to the reference manuals for your system to determine the proper jumper settings.

Here are some additional items to look for:

- Broken or loose wires or cables

- Improperly seated circuit boards in the cardcage

- Improperly seated connectors

- Broken or loose components

- Power supply voltages out of tolerance

### WARNING

There are hazardous voltages present within 86/300 Series Microcomputer systems. To avoid electrical shock and damage:

- 1. Do not work on the system unless you are technically qualified to do so.

- 2. Disconnect the power cord before performing any type of maintenance or service.

- 3. Always refer to the appropriate reference manuals for the correct service procedures for your system.

## intel

## CHAPTER 2 USING THE SYSTEM DIAGNOSTIC TESTS

The System Diagnostic Tests (SDTs) are collections of tests (test suites) that can be used to determine the cause of malfunctions in System 86/300 Series Microcomputers. SDTs are available for most standard and optional circuit boards used in the 86/300 Series systems. Once an SDT has been loaded into memory, you can use its tests individually or in groups, and you can choose detailed error reporting or simple pass/fail error messages.

The SDTs and their functions are as follows:

- SDT8630 tests the CPU, USART, ROM, RAM, PPI (programmable peripheral interface), PIT (programmable interval timer), PIC (programmable interrupt controller), and associated logic circuitry on the 86/30 processor board.

- SDT8612 tests the CPU, USART, ROM, RAM, PPI, PIT, PIC and associated logic circuitry on the iSBC 86/12A processor board.

- SDT337 tests the 8087 Numeric Processor Extension on the processor board.

- SDTRAM tests memory board RAM devices, address and data lines, and parity circuitry.

- SDT309 tests the memory mapping and protection features of the iSBC 309 Memory Management board.

- SDTWIN tests the Winchester disk drives and the 8089 I/O Processor, ROM, RAM, and other circuitry on the iSBC 215B and iSBC 215G Winchester Disk Controller boards. It also verifies the circuitry on iSBC 220 controllers and SMD drives (currently not supported in the System 310).

- SDT218 tests the iSBX 218 (and 218A) Flexible Disk Controller Board and flexible diskette drives.

- SDT351 tests the USART and PIT on the iSBX 351 Serial Communications Expansion Board.

- SDT534 tests the USARTs, PITs, and PICs on the iSBC 534 Four Channel Communications Expansion Board.

- SDT544 tests the USARTs, PPI, PITs, and PICs on the iSBC 544 Intelligent Communications Controller Board.

### SYSTEM 86/300 DIAGNOSTIC DISKETTES

Intel distributes the System 86/300 diagnostic software on two 8" or five  $5\frac{1}{4}$ " flexible diskettes. The diskettes are labeled as follows:

SYP 86/300 DIAGNOSTICS, # n

DS/DD iRMX 86 DISKETTE PART NO. xxxxxx-yyy

91982, 1983 INTEL CORP.

where n is the diskette number. The contents of the diskettes are as follows:

- 8" diskette #1 contains the executable SDT program files. Use this diskette when loading the SDTs.

- 8" diskette #2 contains configuration files for the SDTs. Use these files to change the default values that the SDTs use at initialization for test limits and other variables. See Appendix A for additional information.

- 5¼" diskettes #1A and #1B contain the same SDT program files as 8" diskette #1.

- $5\frac{1}{4}$ " diskettes #2A, #2B, and #2C contain the same configuration files as 8" diskette #2.

### INSTALLING SDT TEST SUITES ON WINCHESTER DISK

The SDT test suites reside on the diagnostic diskettes shipped with your system. If you are using the iRMX 86 operating system, you should, upon receipt of the diagnostic diskettes, install the SDT tests on the Winchester disk. That way, if you have a problem with either the Winchester or flexible diskette drives, you will have an alternate means of invoking the tests.

If you are using the XENIX\* 86 operating system, you must invoke the diagnostics from a flexible diskette. In this case, the following discussion does not apply.

The following procedure assumes that you are familiar with the iRMX 86 operating system. Refer to the iRMX 86 Operator's Manual for detailed information.

Install the SDTs on the Winchester disk as follows:

l. After loading the iRMX 86 operating system from your Winchester disk, invoke the SUPER command. When the prompt

### ENTER PASSWORD:

<sup>\*</sup>XENIX is a trademark of Microsoft Corporation.

appears, enter the password associated with the system manager.

2. Create a Winchester drive directory for the SDTs by entering

### CREATDIR :SD: SDTDIR

3. Attach the flexible disk device using the ATTACHDEVICE command:

### ATTACHDEVICE wwww AS:FD0:

where wwww is the physical device name of the drive to be used. Use the physical device name WFDD0 for an 8" double-sided double-density flexible diskette drive when the flexible diskette controller board is mounted on the iSBC 215G Winchester Controller board. (This is the factory-standard configuration for systems that have a Winchester drive installed.) Use the physical device name WMFDX0 for a  $5\frac{1}{4}$ " flexible diskette drive.

- 4. Insert 8" diagnostic diskette 1 or  $5\frac{1}{4}$ " diagnostic diskette 1A into the flexible diskette drive.

- 5. Enter

## COPY:FD0:SDTDIR/SDTnnnn TO:SD:SDTDIR/SDTnnnn

where *nnnn* is the number of an SDT. Repeat this step for each SDT on 8" diskette 1 or  $5\frac{1}{4}$ " diskettes 1A and 1B. (See the list of SDTs at the beginning of this chapter.)

### LOADING AN SDT INTO MEMORY

To run tests in an SDT test suite, you must first load the SDT into memory. Proceed as follows.

- 1. Press the Reset switch on the system's front panel.

- 2. After you press the Reset switch, the sytem begins to send a series of asterisks to the terminal's screen. As soon as the asterisks appear, enter an uppercase U on the terminal.

- 3. Shortly after you enter the uppercase U, the system displays a message asking you for input from the keyboard, as follows:

TEST

USART/Timer

PIC . \*. INPUT "I"

When this message appears, enter CONTROL-C on the terminal or press the Interrupt switch on the system front panel. This passes control to the system monitor program.

4. If the SDT test suites are contained on the Winchester disk boot the desired test by entering

### b /SDTDIR/testnumber

where testnumber is one of the following SDT test suite identifiers: SDT8630, SDT8612, SDT337, SDTRAM, SDTWIN, SDT218, SDT351, SDT534, SDT544, or SDT309.

You must leave a space between the "b" and the first "/" in the invocation line. You may use upper- or lowercase characters.

To invoke the tests from a flexible diskette, enter

### b:WF0:/SDTDIR/testnumber

if the flexible diskette controller is mounted on the iSBC 215G Winchester Controller board (the standard location in Winchester-disk-based systems), or enter

### b:PF0:/SDTDIR/testnumber

if the flexible disk controller is mounted on the iSBC 86/30 Single Board Computer.

After invoking a particular SDT test suite, you can run all of the tests in the suite, run a selected series of tests, loop on a particular test or series of tests, or run a single test by using the test management commands described in the next section.

### TEST MANAGEMENT COMMANDS

The test management commands, available with all of the SDT test suites, allow you to select specific tests, control the way in which the tests run, and control the extent and manner of error reporting. The commands are as follows:

- CLEAR resets the execution and error count values.

- DEBUG enables or disables the printing of debug messages (or lists the status of the command).

- DESCRIBE prints a description of the tests.

- ERRONLY enables or disables the printing of status messages (or lists the status of the command).

- EXIT returns control from a test to the system monitor.

- IGNORE causes the TEST and SUMMARY commands to ignore selected tests.

- LIST copies all console I/O to a file.

- QUERY displays the status of DEBUG and ERRONLY.

- RECOGNIZE reverses the effect of an IGNORE.

- REPEAT/ENDREPEAT begins and ends a loop of commands.

- RESET resets the hardware and/or software.

- SUMMARY prints a result log of the tests that have run.

- TEST selects and runs one or more SDT tests.

- V displays and sets the the values of global variables used by the tests.

### COMMAND NOTATION AND USAGE

This section explains the notational conventions and the various rules of use that apply to the Test Management Commands.

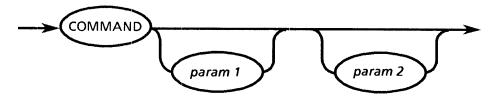

### Syntax Diagrams

The Test Management Command descriptions use syntax diagrams to illustrate the various ways commands may be entered. The tracks on the diagrams indicate the possible paths through the various combinations of a command's elements. For example, the following diagram illustrates a command with two optional parameters.

F-0126

You could enter this command in any of the following forms:

COMMAND

COMMAND param1

COMMAND param2

COMMAND param1 param2

To use the diagram, start at the left-hand side and follow the tracks through all those elements that you want to use. The arrows on the tracks indicate the proper direction of travel. When leaving a track, you must continue in the direction of the smooth curve; sharp turns and going against the arrows are not allowed.

The following notational conventions are used for elements within the syntax diagrams:

- Elements shown in uppercase letters are literal quantities and must be entered using exactly the characters shown. They may, however, be entered in upper- or lowercase characters. In addition, certain command names and keywords may be abbreviated, as described later in this section.

- Elements shown in lowercase italics are variable quantities.

You must enter the appropriate value or symbol, as specified in the test descriptions.

### **Abbreviations**

When you enter commands, you can abbreviate command names, and keywords used with the commands, to their first three characters. For example, you can abbreviate

TEST 1 REPEAT UNTIL ERROR

as follows:

TES 1 REP UNT ERR

### Continuation Lines and Comments

You can continue a command on the next line by using an ampersand (&) as a continuation character. This character informs the SDT that the command continues on the next line.

The SDT treats all characters entered after the ampersand but before the end-of-line character (carriage return) as comments.

You can also insert a comment by entering /\*.

For example, the command

```

TEST 1 & Run the first test

**REPEAT UNTIL ERROR /* until an error occurs

```

is a continued command with comments inserted using both methods. The SDT displays the double asterisk at the beginning of the second line to indicate that the line is a continuation line.

### Command Delimiters

You can enter more than one command on a single line. To do this, you must delimit the commands with a semicolon (;). For example, the SDT runs the following commands as if you entered them on separate lines.

IGNORE 1; TEST REPEAT 5; SUMMARY

### Input Radices

The SDT always displays numerical output in hexadecimal form. However, when you provide input to the SDT, you can specify the radix of numerical quantities by including a radix character immediately after the number. The valid radix characters include:

| radix       | character | <u>example</u> |

|-------------|-----------|----------------|

| hexadecimal | h or H    | 16h, 7CH       |

| decimal     | t or T    | 23t, 100T      |

| octal       | q or Q    | 27q, 33Q       |

| binary      | y or Y    | 101y, 11100Y   |

If you omit the radix character in numerical input, the SDT assumes the number is hexadecimal.

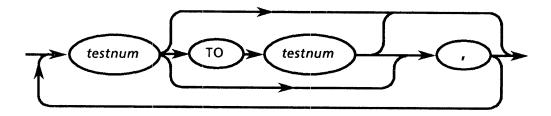

### Test Range Parameter

Throughout this chapter, the command descriptions use the term test-range as a parameter name. When a command description lists this term as a parameter, you must enter the range of test numbers on which the command is to operate. The syntax for test-range is as follows:

F-0127

To select individual tests, separate the test numbers with commas. For example, 1,3 selects tests 1 and 3. If you separate two test numbers with the word TO, you also select all tests between the first number and the second number (for example, 1 TO 3 selects tests 1, 2, and 3); however, when you separate test numbers with TO, the first number must be smaller than the second number.

You can use a combination of commas and the word TO when entering the test range. For example, 0 TO 2,4,6 TO 8 selects tests 0, 1, 2, 4, 6, 7, and 8.

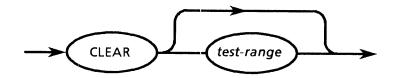

### CLEAR COMMAND

Each test has an execution count and an error count, showing how many times the test has run and how many errors occurred. For each test in the test range (except those specified in an IGNORE command), CLEAR sets the execution count and error count to zero.

Command syntax is as follows:

F-0128

where test-range is the range of test numbers upon which the command operates. If you omit the test range, CLEAR resets the execution count and error count for all tests in the SDT test suite to zero.

### Examples:

\*CLEAR

Clears the execution and error count values for all tests in the SDT test suite.

\*CLE 7

Clears the execution and error count values for test 7.

\*CLE 1 TO 4,8

Clears the execution and error count values for tests 1, 2, 3, 4, and 8.

Error Messages:

### ERROR: test out of range

One or more of the test numbers that you specified was larger than the largest test number in the test suite.

### ERROR: in "a TO b", b is less than a

When specifying test numbers using "a TO b," a must be less than b.

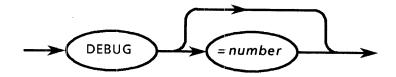

### DEBUG COMMAND

During execution, a test can return debug messages. A debug message lists detailed information about test failures that is useful if you are writing a diagnostic test or troubleshooting the hardware. The

DEBUG command controls whether or not the SDT displays debug messages at the console during test execution.

Command syntax is as follows:

F-0129

where *number* is a value that determines the debug status. An even value (least-significant bit set to 0) sets the debug status to FALSE (off). An odd value (least-significant bit set to 1) sets the debug status to TRUE (on). If you omit the number parameter, the SDT displays the current value of DEBUG. The default value is FALSE.

If you set DEBUG to TRUE and ERRONLY to FALSE (refer to the description of the ERRONLY command), the SDT displays the name and number of each test before running the test; it also displays the usual debug messages after the test runs. If you set DEBUG to FALSE, the SDT omits the information that precedes the test and the detailed debug messages.

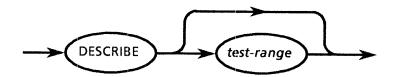

### DESCRIBE COMMAND

The DESCRIBE command displays the names and numbers of specified tests. Command syntax is as follows:

F-0130

where *test-range* is the range of test numbers for which DESCRIBE displays information. If you omit the test range, DESCRIBE displays information about all tests in the SDT test suite.

### Example:

\*DES 1 TO 5,7

lists the test names and numbers for tests 1, 2, 3, 4, 5, and 7. If you are running the SDT215 test suite, the display looks like this:

| 0001H | TRANSFER STATUS   |

|-------|-------------------|

| 0002H | BUFFER I/O TEST   |

| 0003H | ROM CHECKSUM TEST |

| 0004H | RAM WINDOW TEST   |

| 0005H | RAM ADDRESS TEST  |

| 0007H | SEEK/VERIFY TEST  |

| _     |                   |

Error messages:

## ERROR: test out of range

One or more of the test numbers specified was larger than the largest test number in the SDT test suite.

# ERROR: in "a TO b", b is less than a

When specifying test numbers using "a TO b," a must be less than b.

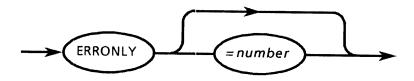

#### **ERRONLY COMMAND**

The ERRONLY command controls whether or not the SDT displays status messages on the terminal during test execution. Command syntax is as follows:

F-0131

where *number* is a value that determines the ERRONLY status. An even value (least-significant bit set to 0) sets the ERRONLY status to FALSE. An odd value (least-significant bit set to 1) sets the ERRONLY status to TRUE. If you omit *number*, the SDT displays the current value of ERRONLY. The default value is FALSE.

If you set ERRONLY to TRUE, the SDT displays test results only for tests that fail. It does not display information for tests that pass, nor does it display the names and numbers of the tests before running them, even if DEBUG is set to TRUE. (Refer to the description of the DEBUG command.) If you set ERRONLY to FALSE, the SDT displays test results for both passing and failing tests.

#### EXIT COMMAND

The EXIT command causes an exit from the SDT and returns control to the system monitor. This allows you to load other programs, such as the other SDT test suites or the iRMX 86 Operating System. Command syntax is as follows:

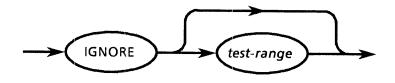

#### IGNORE COMMAND

The IGNORE command causes specified tests to be bypassed when you invoke the TEST command. After the IGNORE command is invoked for a test, it remains ignored until you issue a RECOGNIZE command for that test. Command syntax is as follows:

F-0134

where test-range is the range of test numbers that are ignored during a TEST command. If you omit the test range, all tests in the test suite are ignored. If you specify the number of a test that has already been ignored, the IGNORE command has no effect on that test.

Error Messages:

# ERROR: test out of range

One or more of the test numbers specified was larger than the largest test number in the SDT test suite.

## ERROR: in "a TO b", b is less than a

When specifying test numbers using "a TO b," a must be less than b.

## Examples:

\*IGNORE

\*

ignores all tests in the SDT test suite. Future TEST commands have no effect until you recognize the tests using the RECOGNIZE command.

\*IGN 3,6 TO 9

ignores tests 3, 6, 7, 8, and 9.

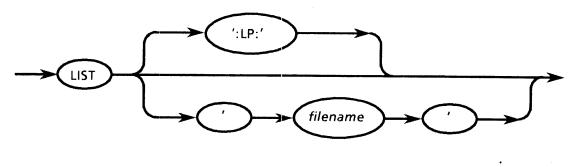

#### LIST COMMAND

The LIST command causes the SDT to copy all terminal I/O to a specified file or device. Command syntax is as follows:

where

':LP:'

represents the line printer. You must enclose :LP: in single quote characters. If you use this parameter, LIST copies terminal I/O to the line printer connected to your system.

#### NOTE

If there is no line printer connected to your system, specifying ':LP:' causes the system to malfunction, requiring you to reset the system and reload the SDT.

'filename'

is an ISIS-II filename. You must enclose the filename in single quote characters.

You can specify an ISIS-II file to receive terminal I/O only if your system is connected to an Intel Microprocessor Development System through the processor board's parallel interface.

If you use the LIST command without parameters, LIST stops copying console I/O and closes the current list file (if any).

Error Messages:

# **Bad EMDS Connection**

This message indicates a bad communication link between the System 86/300 Series Microcomputer and the Microprocessor Development System. To recover from this error, you must reload the SDT software.

## QUERY COMMAND

The QUERY command displays the current logical values of the DEBUG and ERRONLY command variables. Command syntax is as follows:

Examples:

\*QUERY

Produces the following display:

DEBUG=0000 ERRONLY=0000

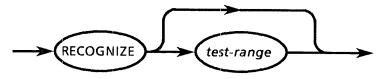

#### RECOGNIZE COMMAND

The RECOGNIZE command reverses the effect of all or part of a previously issued IGNORE command, allowing the specified tests to run when the TEST command is invoked. Command syntax is as follows:

F-0137

where test-range is the range of test numbers upon which the command operates. If you omit the test range, RECOGNIZE operates on all tests in the SDT test suite. If you specify the number of a test that has already been recognized, the RECOGNIZE command has no effect on that test.

Error Messages:

## ERROR: test out of range

One or more of the test numbers specified was larger than the largest test number in the SDT test suite.

## ERROR: in "a TO b", b is less than a

When specifying test numbers using "a TO b," a must be less than b.

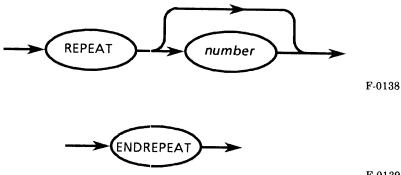

#### REPEAT AND ENDREPEAT COMMANDS

The REPEAT and ENDREPEAT commands allow you to repeat a group of commands any number of times. The REPEAT command denotes the start of the group; the ENDREPEAT command denotes the end of the group. Command syntax is as follows:

where number is the number of times the group of commands is to be If you omit the number parameter, the delimited commands are repeated indefinitely, until you enter CONTROL-C or reset the system.

The REPEAT and ENDREPEAT commands provide a mechanism for creating command loops. When you enter the REPEAT command, the SDT issues the following prompt:

.\*

to remind you that succeeding commands are part of a REPEAT loop. The SDT does not execute any of the commands until you enter the ENDREPEAT command to end the loop.

You can nest REPEAT loops by entering another REPEAT command in response to the prompt. If you do this, the SDT issues following prompt:

..\*

indicating that succeeding commands are part of the nested loop. You can end the nested loop by entering an ENDREPEAT command. The SDT does not execute any commands until you end the outermost REPEAT loop with an ENDREPEAT command.

You can nest up to eight levels of REPEAT loops. At each level, the SDT adds an additional period to its prompt. The SDT issues an error message if you attempt to nest more than eight levels of REPEAT loops.

# Examples:

- \*REPEAT

- .\*TEST 1

- .\*TEST 0

- \*TEST 3

- .\*ENDREPEAT

The preceding sequence repeats tests 0, 1, and 3 in nonsequential order. The SDT will repeat the tests until you enter a CONTROL-C character to terminate the testing.

- \*REPEAT

- \*TEST 0

- .\*REPEAT 5

- ..\*TEST 9

- ..\*ENDREPEAT

- .\*ENDREPEAT

The preceding sequence is a nested repeat loop in which the SDT runs test 0 followed by five iterations of test 9. It continues this testing sequence until you enter a CONTROL-C.

Error Messages:

## ERROR: too many nested IFs or REPEATS

You attempted to create more than eight levels of REPEAT loops.

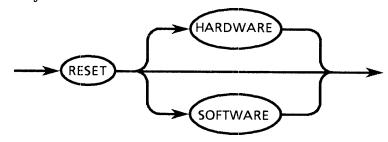

#### RESET COMMAND

The RESET command initializes the test software and the hardware that it is testing. The RESET command does not reset the values of the DEBUG and ERRONLY commands, nor does it specify that ignored tests are to be recognized, in all cases. After using the RESET command, you should examine the individual SDT test suites to determine the state of ignored tests.

Command syntax is as follows:

where

F-0140

HARDWARE resets the hardware to its initial state. The SDT test suite may request additional information from

you about the state of the hardware.

SOFTWARE resets the SDT software to its initial state. The

SDT test suite may request additional information

about test ranges and devices.

If you specify the RESET command without parameters, the SDT first resets the software and then resets the hardware.

#### SUMMARY COMMAND

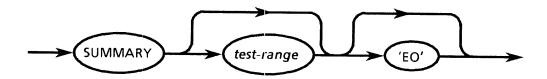

The SUMMARY command displays a log of test results for specified tests. Command syntax is as follows:

where

test-range

is the range of test numbers for which a test summary is required. If you omit this parameter, the SDT assumes the test range to be all tests in the SDT test suite.

'EO'

displays the "error only" information. If you specify this parameter, SUMMARY displays information only for failed tests in the test range. Otherwise, SUMMARY displays information for all tests in the test range.

The SUMMARY command displays the name and number of each test in the test range, followed by the number of test tries and the number of failures (both in hexadecimal). You can reset the number of tries and failures to zero by entering the CLEAR command.

Information about the number of tries and failures does not appear for any tests specified in the IGNORE command. Instead, the following message appears:

## \*\*\* IGNORED \*\*\*

## Example:

# \*SUMMARY

0000H FIXED PATTERNS 0000 FAILED IN 0004 TRIALS 0001H ADDRESS MARCH 0000 FAILED IN 0004 TRIALS 0002H SLIDING ONES 0000 FAILED IN 0004 TRIALS 0003H EXECUTE FROM RAM \*\*\*\* IGNORED \*\*\*

This command displayed a log of test results for all tests in the current test suite, which in this case is the SDTRAM test suite. IGNORE status is set for the last test; that test does not run and SUMMARY does not display information for it.

## Error Messages:

# ERROR: test out of range

One or more of the test numbers you specified was larger than the largest test number in the SDT test suite.

# ERROR: in "a TO b", b is less than a

When specifying test numbers using "a TO b," a must be less than b.

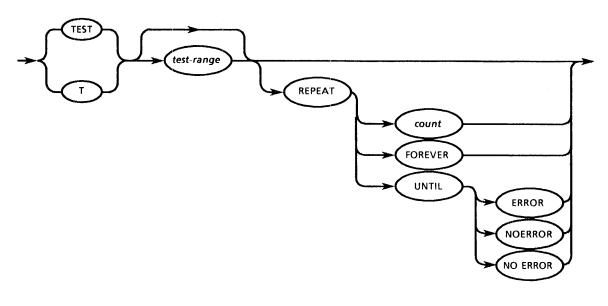

## TEST COMMAND

The TEST command selects and runs diagnostic tests. Command syntax is as follows:

F-0142

where

test-range is the range of tests to run. The SDT runs all

tests in the test range except those you have specified in an IGNORE command. If you omit this parameter, the SDT assumes the test range

to be all tests in the test suite.

REPEAT means repeat the tests as specified in the

succeeding parameters. If you omit the succeeding parameters, the SDT repeats the tests indefinitely. If you omit this parameter,

the SDT runs the tests once.

count is the number of times to repeat the tests.

FOREVER means repeat the tests indefinitely.

UNTIL ERROR means repeat the tests until an error occurs.

UNTIL NO ERROR means repeat the tests until no errors occur.

The TEST command runs all tests in the test suite except those specified in an IGNORE command. See the IGNORE command description for more information.

The amount of information that the TEST command displays after running a test depends on the settings of the DEBUG and ERRONLY commands. (See the descriptions of the DEBUG and ERRONLY commands.)

Normally, the SDT displays the number, name, and result (passed or failed) of each test. If a test has "ignored" status, the name field for the test contains the message:

## \*\*\* IGNORED \*\*\*

If you set the DEBUG variable to an odd value (TRUE), the SDT displays the name and number of each test before running the test. In addition, detailed debug messages that individual tests generate to describe error conditions are displayed. If you set DEBUG to an even value (FALSE), the SDT omits the pre-test message and the detailed debug messages.

If you set the ERRONLY variable to an odd value (TRUE), the SDT displays results only for failed tests. It does not display information for tests that pass, nor does it display the names and numbers of the tests before running them, even if DEBUG is set to TRUE. If you set ERRONLY to an even value (FALSE), the SDT displays test results for both passing and failing tests.

#### NOTE

If you set ERRONLY to TRUE and issue the Test Command using the REPEAT, REPEAT FOREVER, REPEAT or UNTIL parameters, you may find it impossible to stop test execution with CONTROL-C. If all tests run without errors, ERRONLY causes the SDT to omit messages to the terminal. Since the SDT can respond to a CONTROL-C only during terminal I/O, any CONTROL-C you enter will be ineffective. In this case, you must press the INTERRUPT switch to stop test execution. You must then reload the SDT test suite to run further tests.

Error Messages:

## ERROR: test out of range

One or more of the test numbers specified was larger than the largest test number in the SDT test suite.

# ERROR: in "a TO b", b is less than a

When specifying test numbers using "a TO b," a must be less than b.

# Example:

\*TEST

| 0003H *** IGNORED *** |          |

|-----------------------|----------|

| 0000H FIXED PATTERNS  | "PASSED" |

| 0001H ADDRESS MARCH   | "PASSED" |

| 0002H SLIDING ONES    | "PASSED" |

|                       |          |

This command ran each of the tests in the suite once, except for test 3, which has "ignored" status. This example assumes the SDTRAM test suite is the current test suite.

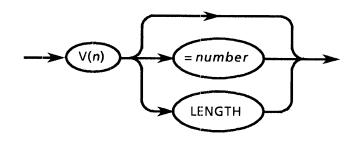

## V COMMAND

The V command displays or sets values for global variables used by the tests. Command syntax is as follows:

F-0143

where

n

is the variable's number, in the range 0 through 0FH. Not all Intel-supplied diagnostic tests make use of global variables. You can use these variables if you write your own diagnostic tests.

number

is the value to which the global variable is set. Variables can be set to any 16-bit value. If you omit value, the SDT displays the current value of the global variable.

LENGTH

is the length of the list of variables whose current value you want to display.

## Examples:

\*V(B)=100

assigns the hexadecimal value 100 to variable V(B).

\*V(C)

displays the current value of the variable V(C).

\*V(0) len 6

displays the current values of variables V(0) through V(5).

Error Messages:

ERROR: "V" variable out of bounds

You specified a value greater than OFH for a variable.