# 16 Bit Series Reference Manual

# 0 Interdata

# 16 Bit Series Reference Manual

Publication Number 29-398R03

INFORMATION CONTAINED IN THIS MANUAL IS SUBJECT TO DESIGN CHANGE OR PRODUCT IMPROVEMENT

# **TABLE OF CONTENTS**

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                            |

| MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                            |

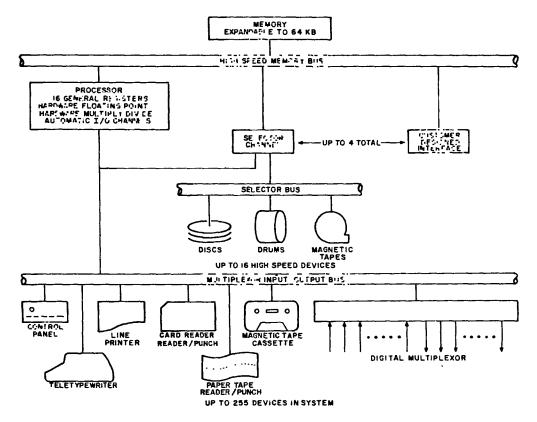

| YSTEM ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                            |

| NSTRUCTION SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                            |

| NPUT/OUTPUT SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                                                                                                                                            |

| OFTWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                                                                                            |

| OPTIONS AND PERIPHERALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                                                                                            |

| UMMARY OF 7/16 FEATURES AND OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                                                                                                                            |

| CHAPTER 2 SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                            |

| ROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                                                                                                                                            |

| Program Status Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                                                            |

| Wait State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                            |

| External Interrupt Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                            |

| Machine Malfunction Interrupt Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                                                                                            |

| Fixed Point Divide Fault Interrupt Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                            |

| Automatic I/O and Immediate Interrupt Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                            |

| Floating Point Fault Interrupt Mask.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                            |

| System Queue Service Interrupt Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                                                                                                                                                                            |

| Protect Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                                                                                                                                            |

| Condition Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7                                                                                                                                                                                            |

| General Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                                                                                                            |

| Floating Point Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                                                                                                                                                            |

| Processor Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                            |

| Reserved Memory Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                                                                                                                            |

| Processor Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                            |

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                                                                                                                            |

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                                                                                                                            |

| PATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8<br>9                                                                                                                                                                                       |

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                                                                                                                            |

| PATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8<br>9<br>9                                                                                                                                                                                  |

| PATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8<br>9<br>9<br>9                                                                                                                                                                             |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>9<br>9<br>9<br>9                                                                                                                                                                        |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9<br>9<br>9<br>10<br>10                                                                                                                                                                      |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>10                                                                                                                                                      |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>10                                                                                                                                                      |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11                                                                                                                                               |

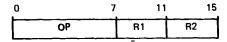

| Fixed Point Data . Floating Point Data . Logical Data .  NSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9<br>9<br>9<br>9<br>10<br>10<br>11<br>11<br>13                                                                                                                                               |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>13                                                                                                                                    |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>11<br>11<br>13<br>13                                                                                                                                    |

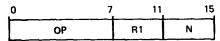

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9<br>9<br>9<br>9<br>10<br>10<br>11<br>11<br>13<br>13<br>14                                                                                                                                   |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>13<br>13<br>14<br>15                                                                                                                  |

| Fixed Point Data Floating Point Data Logical Data  NSTRUCTION FORMATS  Register to Register (RR) Format Short Form (SF) Format Register to Indexed (RX) Format Register to Immediate Storage (RI) Format Branch Instruction Formats  CHAPTER 3 LOGICAL OPERATIONS  DATA FORMATS BISONLEAN OPERATIONS LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS                                                                                                                                                                                                                                        | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>13<br>13<br>14<br>15<br>15                                                                                                            |

| Fixed Point Data Floating Point Data Logical Data  NSTRUCTION FORMATS  Register to Register (RR) Format Short Form (SF) Format Register to Indexed (RX) Format Register to Immediate Storage (RI) Format Branch Instruction Formats  CHAPTER 3 LOGICAL OPERATIONS  DATA FORMATS BOOLEAN OPERATIONS LIST PROCESSING LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  Logical Halfword                                                                                                                                                                                                        | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>13<br>13<br>14<br>15<br>15                                                                                                            |

| Fixed Point Data . Floating Point Data . Logical Data .  NSTRUCTION FORMATS .  Register to Register (RR) Format . Short Form (SF) Format . Register to Indexed (RX) Format . Register to Immediate Storage (RI) Format . Branch Instruction Formats .  CHAPTER 3 LOGICAL OPERATIONS .  DATA FORMATS . BOOLEAN OPERATIONS . LIST PROCESSING . LOGICAL INSTRUCTION FORMATS . LOGICAL INSTRUCTION FORMATS . LOGICAL INSTRUCTIONS .  Logical Halfword . Logical Halfword . Logical Halfword Register .                                                                                           | 9<br>9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>13<br>13<br>14<br>15<br>16                                                                                                            |

| Fixed Point Data . Floating Point Data . Logical Data .  NSTRUCTION FORMATS  Register to Register (RR) Format . Short Form (SF) Format . Register to Indexed (RX) Format . Register to Immediate Storage (RI) Format . Branch Instruction Formats .  CHAPTER 3 LOGICAL OPERATIONS .  DATA FORMATS . BOOLEAN OPERATIONS . LIST PROCESSING . LOGICAL INSTRUCTION FORMATS . LOGICAL INSTRUCTIONS .  Logical Halfword . Load Halfword Register . Load Halfword Register . Load Halfword Immediate                                                                                                | 8<br>9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>13<br>13<br>14<br>15<br>16<br>16                                                                                                      |

| Fixed Point Data . Floating Point Data . Logical Data  NSTRUCTION FORMATS  Register to Register (RR) Format . Short Form (SF) Format . Register to Indexed (RX) Format . Register to Immediate Storage (RI) Format . Branch Instruction Formats . CHAPTER 3 LOGICAL OPERATIONS  DATA FORMATS . BOOLEAN OPERATIONS . LIST PROCESSING . LOGICAL INSTRUCTION FORMATS . LOGICAL INSTRUCTION FORMATS . LOGICAL INSTRUCTIONS . Logical Halfword . Load Halfword Register . Load Halfword Immediate . Load Immediate Short .                                                                        | 8 9 9 9 10 10 10 11 11 13 13 14 15 16 16 16 16 16                                                                                                                                            |

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8 9 9 9 10 10 10 11 11 13 13 14 15 16 16 16 16 16 16                                                                                                                                         |

| Fixed Point Data Floating Point Data Logical Data  NSTRUCTION FORMATS  Register to Register (RR) Format Short Form (SF) Format Register to Indexed (RX) Format Register to Immediate Storage (RI) Format Branch Instruction Formats  CHAPTER 3 LOGICAL OPERATIONS  DATA FORMATS SOOLEAN OPERATIONS LIST PROCESSING LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  Logical Halfword Load Halfword Register Load Halfword Immediate Load Immediate Short Load Complement Short Load Multiple                                                                                                | 8 9 9 9 10 10 10 11 11 13 13 14 15 16 16 16 16 16 16 17                                                                                                                                      |

| Fixed Point Data . Floating Point Data . Floating Point Data . Logical Data  NSTRUCTION FORMATS  Register to Register (RR) Format . Short Form (SF) Format . Register to Indexed (RX) Format . Register to Immediate Storage (RI) Format . Branch Instruction Formats .  CHAPTER 3 LOGICAL OPERATIONS  DATA FORMATS . BOOLEAN OPERATIONS . LIST PROCESSING . LOGICAL INSTRUCTION FORMATS . LOGICAL INSTRUCTIONS .  Logical Halfword . Load Halfword Register . Load Halfword Immediate . Load Halfword Immediate . Load Immediate Short . Load Complement Short . Load Oblighe . Load Byte . | 8 9 9 9 9 10 10 10 11 11 13 13 14 15 16 16 16 16 16 17 18                                                                                                                                    |

| Fixed Point Data Floating Point Data Logical Data  NSTRUCTION FORMATS  Register to Register (RR) Format Short Form (SF) Format Register to Indexed (RX) Format Register to Immediate Storage (RI) Format Branch Instruction Formats  CHAPTER 3 LOGICAL OPERATIONS  DATA FORMATS SOOLEAN OPERATIONS LIST PROCESSING LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  Logical Halfword Load Halfword Register Load Halfword Immediate Load Immediate Short Load Complement Short Load Multiple                                                                                                | 8<br>9<br>9<br>9<br>9<br>9<br>10<br>10<br>11<br>11<br>13<br>13<br>14<br>15<br>16<br>16<br>16<br>16<br>16<br>17<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18 |

|         | Store Multiple                                  |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 2      |

|---------|-------------------------------------------------|------------|------|------|----|---|---|---|-----|-----|---|---|---|---|---|---|---|---|---|---|-----|-----|-----|-----|----------|

|         | Store Byte                                      |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 2      |

|         | Store Byte Register                             |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 2      |

|         | AND Halfword                                    |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 2      |

|         | AND Halfword Register                           |            |      |      |    | - |   |   |     |     |   | - |   |   |   |   |   |   |   |   |     | _   |     |     | . 2      |

|         | AND Halfword Immediat                           |            | •    | •    | •  | • | • | • | •   | •   | • | • | • | • | • | • | ٠ | • | • | • | •   | •   | •   | •   | 2        |

|         | OR Halfword                                     |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | OR Halfword Register.                           |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | OR Halfword Register .                          |            | •    | •    | •  | ٠ | • | • | •   |     | • | • | • | • | ٠ | • | • | • | • | • | •   | •   | •   | •   | . 2      |

|         | OR Halfword Immediate                           |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Exclusive OR Halfword                           |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Exclusive OR Halfword F                         |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Exclusive OR Halfword I                         |            | -    | -    | -  | _ | - | - | -   |     | _ | _ | - | - |   | - | - | - |   | - | _   | -   | -   |     | _        |

|         | Test Halfword Immediate                         | e          |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 2      |

|         | Compare Logical Halfwo                          | rd         |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 2      |

|         | Compare Logical Halfwor                         |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Compare Logical Halfwo                          |            |      |      | _  | - |   | - |     | -   |   |   |   |   |   |   |   |   |   |   |     |     |     |     | _        |

|         | Compare Logical Byte                            |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Shift Left Logical                              |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         |                                                 |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Shift Right Logical                             |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Shift Left Halfword Logi                        |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Shift Left Logical Short                        |            |      |      |    |   |   |   | •   |     | • | ٠ | • |   |   |   |   |   |   | • |     |     |     |     | . 3      |

|         | Shift Right Halfword Log                        | gical      |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 3      |

|         | Shift Right Logical Short                       |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 3      |

|         | Rotate Left Logical                             |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Rotate Right Logical .                          |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Add to Top of List                              |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Add to Post                                     |            | •    |      | •  | • | • | • | •   |     | • | • | • | ٠ | • | • | • | • | • | • | •   | •   | •   |     | . 3      |

|         | Add to Bottom of List                           |            | •    | •    | •  | • | • | ٠ | •   |     | • | ٠ | • | • | • | • | • | • | • | • | •   | •   | •   | - • | . 3      |

|         | Remove from Top of Lis                          | t          | •    | •    |    | • | • | • | •   |     | • | ٠ | • | • | • | • | • | • | • | • | •   | •   | •   |     | . 3      |

|         | Remove from Bottom of                           | List       | •    |      |    | • | • | • |     |     | • |   | • |   |   |   | • | • |   |   |     | •   |     |     | . 3      |

| CHAPTE  | R 4 BRANCHING                                   |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 3      |

|         |                                                 |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

| OPERAT  | IONS                                            |            | ٠    | •    | •  | • | • | • | •   |     | • | ٠ | ٠ | • | • | • | • | • | • | • | •   | •   | •   | •   | . 3      |

|         | Decision Making                                 |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | 2        |

|         | Subroutine Linkage                              |            | •    | •    | •  | • | • | • | •   |     | • | ٠ | • | • | • | • | • | • | • | • | •   | •   | •   | • • | · .      |

|         | Subroutine Linkage                              |            | •    | •    | •  | • | • | • | •   |     | • | • | • | • | • | • | • | • | • | • | •   | •   | •   | •   | . 3      |

|         |                                                 |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | _        |

| BRANCE  | INSTRUCTION FORMA                               | 115        | •    | •    | •  | • | • | ٠ | •   |     | • | • | ٠ | • | • | • | • | • | • | • | •   | •   | •   |     | . 3      |

| BRANCH  | INSTRUCTIONS                                    |            | •    | •    |    | • | • | • | •   |     | • | ٠ | • | ٠ | • | ٠ | • | ٠ | • | • | •   | •   | •   |     | . 3      |

|         |                                                 |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Branch on False Condition                       | on         |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | - 38     |

|         | Branch on False Condition                       | n Registe  | r    |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 39     |

|         | Branch on False Condition                       | n Backwa   | rd : | Sho  | rt |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 3      |

|         | Branch on False Condition                       | n Forwar   | d S  | hor  | t. |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | . 30     |

|         | Branch on True Conditio                         | n          |      |      | •  |   |   |   |     |     |   |   |   |   |   |   | _ | _ |   |   | _   |     |     |     | 30       |

|         | Branch on True Conditio                         | n Register | . •  | •    | •  | • | Ī | Ī |     |     |   | Ī | Ī | • |   |   |   | • |   |   | •   | •   | •   |     | 20       |

|         | Branch on True Conditio                         | n Rackwa   | -d 9 | Sho  | -+ | • | • | • | •   |     | • | • | • | • | • | • | • | • | • | • | •   | •   | •   | • • | . 38     |

|         | Branch on True Conditio                         | - Earwar   | 10.  | ,,,d |    | • | • | • | •   |     | • | • | • | • | • | • | • | • | • | • | •   | •   | •   |     | 39       |

|         | Branch on True Condition                        | II FOI Wai |      | 1011 | •  | ٠ | • | • | •   |     | • | • | • | • | • | • | • | • | • | • | •   | •   | •   | ٠.  | 39       |

|         | Branch and Link                                 |            | •    | •    | •  | • | • | • | •   |     | • | • | • | • | • | • | • | ٠ | • | • | •   | •   | •   |     | 40       |

|         | Branch and Link Register                        | Carral     | •    | ٠.   | •  | ٠ | • | • | •   |     | • | ٠ | • | • | • | • | • | • | • | • | •   | •   | •   | ٠.  | 40       |

|         | Branch on Index Low or                          | Equal .    | •    | •    | •  | ٠ | • | • | •   |     | • | • | ٠ | • | ٠ | • | • | • |   | ٠ | •   | •   | •   |     | 41       |

|         | Branch on Index High .                          |            | •    | •    | •  | • | • | • | •   |     | • | ٠ | • | • | • | • | • | • | • | ٠ | •   | •   | •   |     | 42       |

| CHAPTE  | R 5 FIXED POINT                                 |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         |                                                 |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

| DATA F  | ORMATS                                          |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | 42       |

| CONDIT  | ION CODE                                        |            | _    |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | 40       |

| FIXED P | OINT INSTRUCTION FO                             | RMATS      |      |      | •  | • | • | • | •   | • • | • | • | • | • | • | • | • | • | • | • | •   | •   | •   | • • | 43       |

| FIXED P | DINT INSTRUCTIONS                               |            | •    | ٠.   | •  | • | • | • | •   | • • | ٠ | • | • | • | • | • | • | • | • | • | •   | •   | •   | • • | 44       |

|         | I IIIO I IIOCI IONS                             |            | •    | ٠.   | •  | • | • | • | ٠   |     | • | • | • | • | • | ٠ | • | • | • | • | •   | •   | •   |     | 44       |

|         | Add Hale                                        |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     |          |

|         | Add Halfword                                    |            |      |      |    |   |   | • |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | 45       |

|         | Add Halfword Register                           |            |      |      |    |   |   |   |     |     |   | _ | _ | _ |   | _ | _ | _ | _ | _ |     |     |     |     | 45       |

|         | Add Halfword Immediate                          |            |      |      |    |   |   |   |     |     |   |   |   |   |   | _ | _ |   |   |   |     |     |     |     | 45       |

|         | Add Immediate Short .                           |            |      |      |    |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |     |     |     |     | 45       |

|         | Add Halfword to Memory                          | , <u>.</u> |      |      | _  |   | _ |   | _ ' |     | - | - | - |   | _ | - |   | • |   |   | . ' | . ' |     |     | 4s       |

|         |                                                 |            | -    | •    | •  | - | - | - |     |     | • | • | • | • | • | * | • | • | • | • |     |     | - • | •   | 47       |

|         | Add with Carry Halfword                         |            |      |      | _  |   | _ | _ | _   |     |   |   |   |   |   |   |   |   |   |   |     |     | _   |     |          |

|         | Add with Carry Halfword Add with Carry Halfword | Register   | •    | • •  | •  | • | • | • | •   |     | • | • | • | • | • | • | • | • | • | • |     |     | • • | • • | 4/<br>47 |

|         | Subtract Halfwo       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|---------|-----------------------|-----------|--------|--------|-----|-----|-----|-----|----|---|---|---|-----|-----|---|---|-----|---|---|---|---|---|---|---|-----|-------|

|         | Subtract Halfwo       | ord Regis | ter .  |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 48    |

|         | Subtract Halfwo       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Subtract Immed        |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Subtract with C       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Subtract with C       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Compare Halfw         | ord       |        |        | •   | •   |     | •   | •  |   | • | • |     | •   | • |   |     | • | • | • | ٠ | • | • | • |     | 50    |

|         | Compare Halfw         |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Compare Halfw         | ord Imm   | ediate | е.     | •   | •   |     | •   | ٠  | • | • | • |     | •   | ٠ | • | ٠.  | • | • | • | • | • | • | • |     | 50    |

|         | Multiply Halfwo       | ord       |        |        | ٠   | •   |     | •   | •  | • | • | • |     | •   | • | • | ٠.  | • | • | • | • | • | • | • |     | 51    |

|         | Multiply Halfwo       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Multiply Halfwo       | ord Unsig | ned    |        | ٠   | •   |     |     | ٠  | • | - | • |     | •   | • | • |     | • | • | ٠ | • | • | • | • |     | 52    |

|         | Multiply Halfwe       | ord Unsig | gned i | Regis  | ter | •   | ٠.  | •   | •  | ٠ | • | • |     | •   | ٠ | • |     | ٠ | • | ٠ | • | ٠ | • | • |     | 52    |

|         | Divide Halfword       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Divide Halfword       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Shift Left Arith      |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Shift Left Halfv      |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Shift Right Arit      |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Shift Right Half      | word Ar   | ithme  | etic . | •   | •   |     | •   | •  | • | • |   |     | •   | • |   |     | • | • | • | ٠ | • | • |   |     | 57    |

|         |                       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

| CHAPTE  | R 6 FLOATIN           | G POINT   | AR     | THM    | ET  | TIC |     |     | •  |   | • |   |     |     |   |   |     | • |   | • | • |   | • | • |     | 59    |

|         |                       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

| DATA FO | DRMATS                | <i>.</i>  |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   | - |   | • |   |   | • |     | 59    |

|         |                       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Normalization .       |           |        |        |     |     |     |     |    |   | ٠ |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 59    |

|         | <b>Exponent Overl</b> | low and   | Unde   | rflov  | ٧.  |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   | • |     | 59    |

|         | Conversion from       | n Decima  | ił .   |        | ٠   |     |     |     |    |   |   |   |     |     |   |   |     |   |   | ٠ |   |   |   |   |     | 60    |

|         |                       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

| FLOAT   | NG POINT INST         | RUCTIO    | N FC   | RM/    | ATS | S   |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 6     |

| FLOATI  | NG POINT INST         | RUCTIO    | NS.    |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 6     |

|         | Load                  |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | ~     |

|         |                       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Load Register .       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Store                 |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Add                   |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Add Register .        |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Subtract              |           | • •    |        | ٠   | •   |     | •   | •  | • | • | • | • • | ٠   | ٠ | • | •   | • | • | ٠ | • | • | • | • |     | 65    |

|         | Subtract Registe      |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Compare               |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Compare Regist        | er        | • •    | • •    | •   | •   |     | ٠   | ٠  | • | • | • |     | •   | • | • |     | • | • | • | • | • | • | • | • • | 66    |

|         | Multiply              |           |        |        | ٠   | ٠   | ٠.  | •   | •  | ٠ | • | • |     | •   | • | • | •   | • | ٠ | • | • | • | • | • | • • | 6/    |

|         | Multiply Regist       | er        |        |        | •   | •   |     | •   | •  | ٠ | • |   |     | •   | • | • | •   | • | • | • | • | • | ٠ | • |     | 67    |

|         | Divide                |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Divide Register       | • • •     |        |        |     |     | ٠.  | •   |    | - | • |   |     | •   | • | • |     | • | • | • | • | • | • | • |     | 68    |

|         |                       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

| CHAPTE  | R 7 STATUS            | SWITCH    | ING .  | AND    | IN  | ITE | RR  | UP  | TS | ٠ | • | • |     |     | • | • |     | • | ٠ | • | ٠ | • | • | • |     | . 65  |

| SIJTATS | SWITCHING A           | ND INT    | FRR    | IPTS   | 3   |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 69    |

| 017100  | om on the             |           |        | J      | •   | •   | •   | • • | •  | ٠ | • | • | •   | • • | • | • |     | • | • | • | • | • | • | • | •   | . ••• |

|         | M STATUS WO           | PD.       |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 60    |

| rnogna  | MISTATUS NO           | ND        |        | ٠.     | •   | •   | • • | •   | •  | • | • | • | ٠.  | •   | • | • | • • | • | • | • | • | • | • | • | • • | •     |

|         | Wait State            |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 70    |

|         | Protect Mode .        |           | ٠.     | ٠.     | •   | •   | ٠.  | •   | •  | ٠ | • | • | • • | •   | • | • | • • | ٠ | • | • | • | • | • | • |     | 70    |

|         | TTOGECT MOGC.         |           |        | • •    | •   | •   | ٠.  | •   | •  | • | • | • | • • | •   | • | • | •   | • | • | • | • | • | ٠ | • |     | •     |

| INTERRI | JPT SYSTEM .          |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     | 71    |

| .,      | 5. 1 0 10 1C.m .      |           | • •    | ٠.     | ٠   | •   | • • | •   | •  | • | • | • | • • | •   | • | • | •   | • | • | • | • | • | • | • | • • | • •   |

|         | External Interru      | int .     | _      |        | _   |     | _   |     |    | _ |   |   | _   |     | _ |   |     |   | _ | _ | _ |   |   |   |     | 71    |

|         | Machine Malfun        |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Fixed Point Fau       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Immediate Inter       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Console Interru       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Floating Point 8      |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | System Queue I        |           | •      |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Protect Mode V        |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Illegal Instruction   | -         |        | •      |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Supervisor Call       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | System Queue (        |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Simulated Inter       |           |        |        |     |     |     |     |    |   |   |   |     |     |   |   |     |   |   |   |   |   |   |   |     |       |

|         | Juliulaten IIItel     | ·upt      |        |        | -   | •   |     |     | •  | • | • | • |     | •   | • | • |     | • | • | • | • | • | • | • |     | / (   |

|          | SWITCHING INSTRU<br>SWITCHING INSTRU       |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|----------|--------------------------------------------|------------|-------|-----|---|---|---|---|-----|---|-----|-----|-----|---|---|---|---|----|---|-----|---|---|-------|

|          | Load Program Status<br>Exchange Program St |            |       |     |   |   |   |   |     |   | -   |     |     |   | - |   |   |    |   |     |   |   |       |

|          | Simulate Interrupt .                       |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     | ٠ |   | . 78  |

|          | Supervisor Call                            |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 79  |

|          |                                            |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

| CHAPTE   | R 8 INPUT/OUTPU                            | T OPERA    | rions |     | • | • | • | • |     | • | •   | •   | •   | • | • | • | • | •  | • | •   | ٠ | • | . 81  |

| INPUT/O  | UTPUT OPERATION                            | ıs         |       |     | • | • | • |   |     | • | •   |     | •   | • | • | • | • |    |   | •   | • | • | . 81  |

| DEVICE   | CONTROLLERS                                |            |       |     | • | • | • | • |     | • | •   |     |     | • | • | • |   |    |   |     | • |   | . 81  |

|          | Device Addressing .                        |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 81  |

|          | Processor/Controller                       | Communic   | ation |     |   |   |   |   |     |   |     |     |     | ٠ |   |   |   |    |   |     |   |   | . 82  |

|          | Device Priorities                          |            |       |     |   |   |   |   |     |   |     | . , |     |   |   |   |   |    |   |     |   |   | . 82  |

|          |                                            |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | UPT SERVICE POINT                          |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

| I/O INST | <b>RUCTION FORMATS</b>                     | 3          |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 83  |

| I/O INST | RUCTIONS                                   |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 83  |

|          |                                            |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Acknowledge Interru                        | pt         |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 84  |

|          | Acknowledge Interru                        |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Sense Status                               |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Sense Status Register                      |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          |                                            |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Output Command Re                          |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Read Data                                  |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Read Data Register .                       |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Read Halfword                              |            |       |     | • | • | • | • |     | • | •   |     | •   | • | • | ٠ | • |    |   |     |   |   | . 88  |

|          | Read Halfword Regis                        |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Read Block                                 |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     | - | - | . 89  |

|          | Read Block Register                        |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Write Data                                 | · · · · ·  |       |     | • | • | • | ٠ |     | • | •   | •   |     | • | • | • | • | •  | • |     | • | • | . 91  |

|          | Write Data Register . Write Halfword       |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Write Halfword Regis                       |            |       |     | • | • | • | • |     | • | •   | •   | •   | • | ٠ | • | • | •  | • | • • | • | • | . 32  |

|          | Write Block                                |            |       | ٠.  | • | • | • | • | • • | • | •   | •   | • • | • | • | • | • | •  | • |     | • | ٠ | . 02  |

|          | Write Block Register                       |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | Autoload                                   |            |       |     | • | • | • | • | • • | • | •   | •   | • • | • | • | • | • | •  | • | • • | • | • | . OF  |

|          | Autologo                                   |            |       |     | • | • | • | • | • • | • | •   | •   | • • | • | • | • | • | •  | • | • • | • | • |       |

| CONTRO   | OL OF I/O OPERATIO                         | )NC        |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | 96    |

|          | MONITORING I/O                             |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          | UPT DRIVEN I/O                             |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

|          |                                            |            | • •   | • • | ٠ | ٠ | • | • | •   | • | •   | •   | •   | ٠ | ٠ | • | • | •  | • |     | • | - |       |

|          | Automatic Vectoring                        |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 97  |

|          | Software Vectoring .                       |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 98  |

|          | _                                          |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

| SELECT   | OR CHANNEL I/O                             |            |       |     | • | ٠ | • | • |     | • | •   | •   |     | ٠ | • | • | • | •  | • |     | • | • | . 98  |

|          | Selector Channel Dev                       | vices      |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 99  |

|          | Selector Channel Ope                       | eration .  |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 99  |

|          | Selector Channel Pro                       |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 100 |

|          |                                            |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   |       |

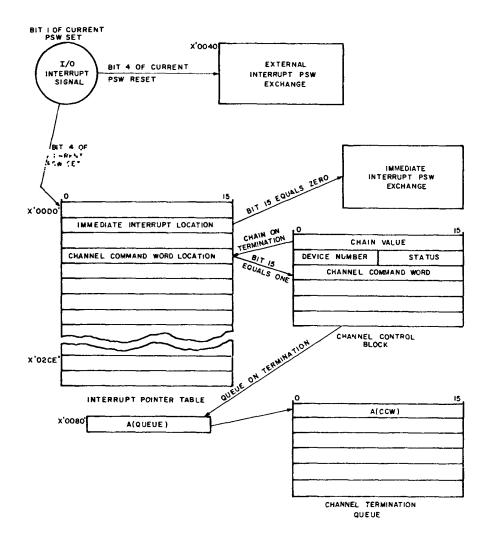

| AUTOM    | ATIC I/O CHANNEL                           |            |       |     | • | • | • | • |     |   | •   | •   |     | • | • | • | • | •  | • |     | • | • | . 100 |

|          | Interrupt Service Poi                      | nt Table . |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 100 |

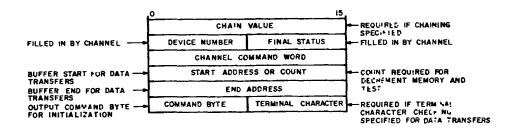

|          | Channel Control Bloc                       | ck         |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     | • |   | - 100 |

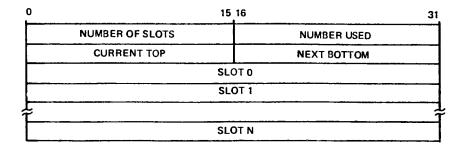

|          | System Queue                               |            |       |     |   |   |   |   |     |   |     |     |     |   |   |   |   |    |   |     |   |   | . 101 |

|          | General Operation                          |            |       |     |   |   |   |   |     |   |     |     |     | • |   |   |   | ٠. | • |     |   |   | . 102 |

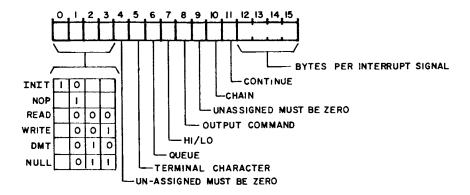

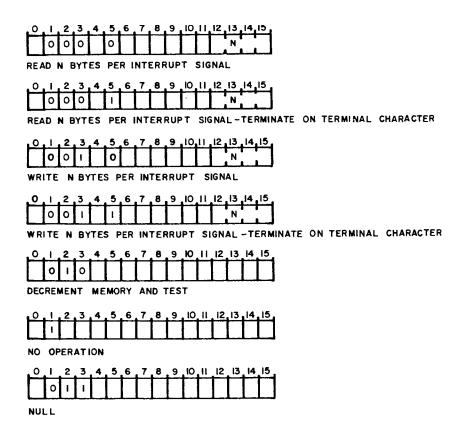

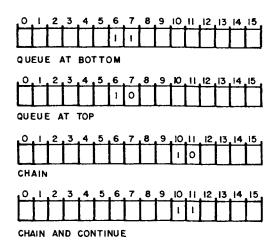

|          | Channel Command V                          | Vords      |       |     |   |   |   |   |     |   | •   |     |     | • | • | • | • | ٠  | • |     | • | • | · 102 |

|          |                                            |            |       |     |   |   |   |   |     |   |     |     |     |   | - |   |   |    |   |     |   |   |       |

|          | Initialization                             |            |       |     |   | - | • |   |     | • | •   |     | •   | • | • | • | • | •  | • |     | • | • | . 103 |

|          | I/O Operation                              |            |       |     |   | • |   | • |     | • | • - | •   |     | • | ٠ | • | • | ٠  | • |     | • |   | . 103 |

|          | Termination                                |            |       |     |   | - | • | - |     |   | •   | •   |     | • | • | • | • | •  |   |     |   |   | . 105 |

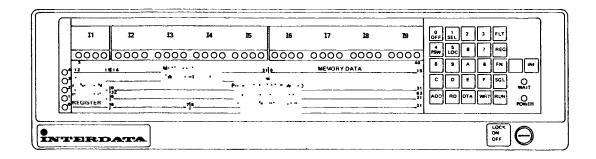

| CHAPTER                  | R 9 HEXADECIMAL DISPLAY PANEL                | 107               |

|--------------------------|----------------------------------------------|-------------------|

| INTRODUC                 | JCTION                                       | 107               |

| COMPIGOR                 | JAMON                                        |                   |

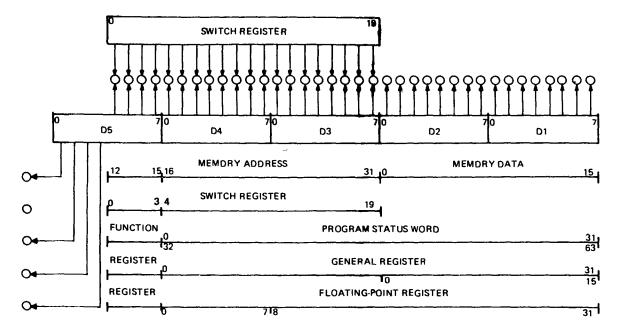

|                          | Display Registers and Indicators             | 108               |

| K                        | Key Operated Security Lock                   | 109               |