# MODEL 70 MICRO-INSTRUCTION REFERENCE MANUAL

# MODEL 70 MICRO-INSTRUCTION REFERENCE MANUAL

# 1. INTRODUCTION TO MICRO-PROGRAMMING

The INTERDATA Processor is a very fast micro-programmable machine controlled by a Read-Only-Memory (ROM). Micro-programs in the ROM direct the flow of information within the registers and core storage of the machine. These micro-programs are a sequence of micro-instructions. Each micro-instruction causes one machine function to be executed; such as transferring the contents of one register to another, addition, subtraction, and logical operations between registers; input/output operations; or core memory accesses. Each micro-instruction constitutes one 16-bit word of ROM. The ROM is a high speed, non-volatile, solid-state device organized into pages of 256 words each.

## 2. THE MICRO-PROGRAMMED PROCESSOR

The Processor is designed to execute micro-instructions stored in a Read-Only-Memory (ROM). Each micro-instruction performs one hardware function. A series of these micro-instructions (a micro-program) can solve highly complex problems. The Micro-Program in the Processor is an emulator. That is, the program completely simulates the instruction set, interrupt handling features, and display functions of a quite different machine. This emulated computer is similar to the IBM 360 family of Processors and has a very powerful instruction set.

Special hardware is built into the Processor to assist the micro-program in its emulation task. When executing instructions of the emulated machine, the micro-program directs the hardware to read the instruction to be performed from core memory. The instruction decoding circuitry then steers the Processor to a micro-subroutine that has been designed to perform the emulated instruction. The loop is then closed by incrementing the instruction location counter and returning to the point that will fetch the next instruction from core memory.

The Read-Only-Memory is a very fast, non-volatile, solid-state device. The Processor is designed to match the ROM's performance, executing most micro-instructions in 250 nanoseconds. The combination of special hardware and micro-instructions running at many times core speed allows most emulated instructions to be executed in the time it takes to fetch them from core.

## 3. BLOCK DIAGRAM ANALYSIS

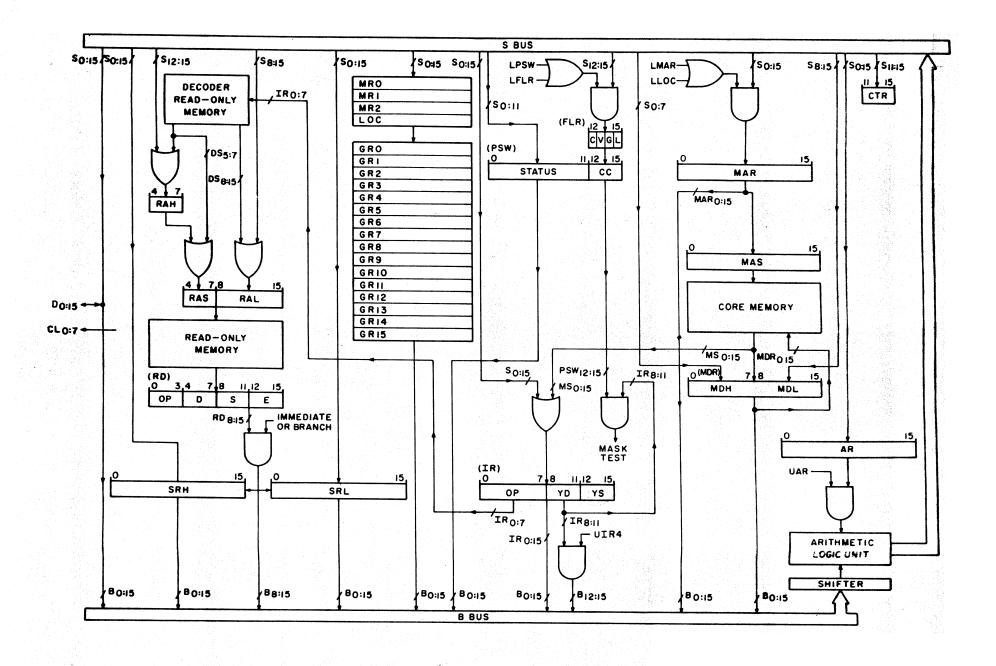

Refer to Figure 1 during the following description. Processor operation is controlled by the Read-Only-Memory (ROM). Locations in ROM are addressed by a 12-bit register comprising an 8-bit incrementing address register (RAL) and a 4-bit non-incrementing page register (RAS). RAS is loaded from the "outer rank" page register (RAH) when RAL is loaded.

Information read out of ROM is placed in a 16-bit data register (RD). Bits 0 through 3 of RD are the micro-instruction operation code. The meaning of the remaining bits in RD depends on the particular micro-operation to be performed.

There are three 16-bit general purpose micro-registers labeled MR0, MR1, and MR2. Two additional 16-bit micro-registers, SRH and SRL, are available for general use. SRH and SRL may also be used together as a 32-bit shift left/shift right register for multiply, divide, and double-precision shifts.

The Program Status Word (PSW) is a 16-bit register which indicates the system status relative to the user program being emulated. Bits 0 through 11 of PSW define machine status. Bits 12 through 15, the Condition Code (CC), may only be loaded from the Flag Register (FLR). When PSW is loaded, Bits 12 through 15 of the S Bus are captured in the FLR. This permutes the user status to the micro-code level. The Location Counter (LOC) is a 16-bit appendum to PSW which holds the address of the next user instruction to be performed.

Figure 1. Hardware Block Diagram

The Memory Address Register (MAR) is a 16-bit buffer used to address core memory locations. Memory is actually addressed by the Memory Address Slave Register (MAS). When memory is not busy, MAS is automatically loaded from MAR. The 16-bit Memory Data Register (MDR) holds data read from or written into core memory. MDR is separated into two bytes, MDH and MDL, which may be loaded separately for efficient byte handling.

The 16-bit Instruction Register (IR) holds the instruction word of the current user instruction. Bits 8 through 11 may be unloaded to the B Bus Bits 12 through 15 (IR4).

The user's sixteen 16-bit General Registers (GR0 through GR15) are not directly addressable by the micro-program. The General Registers are addressed by IR Bits 8 through 11 (YD) or by IR Bits 12 through 15 (YS). The micro-program can only access the General Registers by specifying the field of IR, YD, or YS, that contains the appropriate General Register address.

The Counter Register (CTR) is a 5-bit decrementing register. It is always initialized to a value of 16; however, it may be preset to any value from 0 to 31 to control the number of repetitions of a single micro-instruction or a sequence of micro-instructions. The Counter is used in the multiply and divide hardware to control the number of shifts.

The 16-bit A Register (AR) holds the second operand for arithmetic and logical micro-operations. It is one of two direct inputs to the Arithmetic Logic Unit (ALU). The other input is the output of the B Bus Shifter. The Shifter can shift B Bus data left or right one position, rotate eight positions, or gate directly into the ALU. The ALU comprises a 16-bit parallel adder/subtracter logic network. The arithmetic or logical result is gated to the 16-bit S Bus.

Bits 0 through 7 of IR, the user's operation code, are used to address locations in the Decoder Read-Only-Memory (DROM). DROM is a separate Read-Only-Memory that has 256 12-bit words. DROM is interrogated prior to entering the microsubroutine that executes a user instruction. The DROM readout is jammed into the ROM address registers. The DROM readout corresponds to the starting micro-program address for a given user instruction.

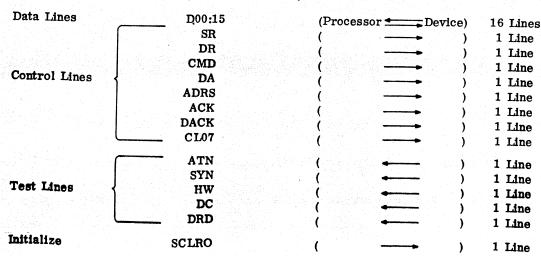

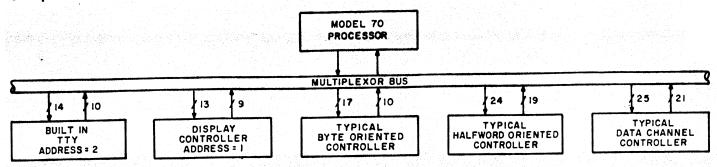

Input/Output operations are accomplished by activating one of eight control lines and gating the S Bus onto the Data Lines or gating the Data Lines onto the B Bus.

## 4. WORD FORMATS

## 4.1 General

1111

The Processor executes 16 basic micro-instructions (see Table 1). Bits 0 through 3 of the ROM Data Register (RD) specify the operation to be performed.

MICRO-INSTRUCTION OP-CODE Meaning Symbolic 0123 DO 0000 D C COMMAND 0001 Т TEST 0010 В BRANCH 0011 L LOAD 0100 L LOAD IMMEDIATE 0101 0 OR 0110 O OR IMMEDIATE 0111 N AND 1000 N AND IMMEDIATE 1001 1010 X EXCLUSIVE OR EXCLUSIVE OR IMMEDIATE 1011 X 1100 A ADD ADD IMMEDIATE 1101 Α S SUBTRACT 1110 S

TABLE 1. BASIC MICRO-INSTRUCTIONS

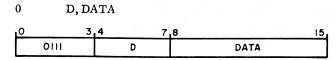

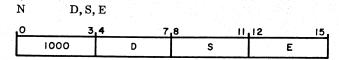

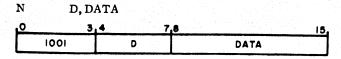

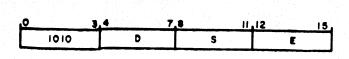

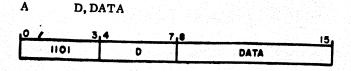

Micro-instructions can have any one of four machine language formats, depending on the operation specified by the OP-CODE. The formats are listed in the following paragraphs by the micro-instructions which use them.

SUBTRACT IMMEDIATE

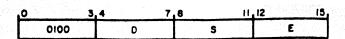

# 4.2 Add, Subtract, And, Or, Exclusive Or, and Load

| 0 3     | .4 7, | 8 11, | 12 15              |

|---------|-------|-------|--------------------|

| OP-CODE | D     | S     | 58 ( E ( ) ( ) ( ) |

Bit 3 of the Op-Code in this format is always reset.

- D = Destination field. The result of the operation is placed into the register whose address is in this field.

- S = Source field. The address of the register containing the first operand is in this field. The second operand is contained in the A Register (AR).

- E = Extended operation field. Instruction options are specified in this field.

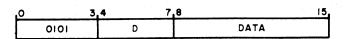

- 4.3 Add Immediate, Subtract Immediate, And Immediate, Or Immediate, Exclusive Or Immediate, and Load Immediate

| 0 |       | 3  | 4 |   | 7 | 8 |      |   | 4 | 15 |

|---|-------|----|---|---|---|---|------|---|---|----|

|   | OP-CO | DE |   | D |   |   | DATA | 1 |   |    |

Bit 3 of the op-code in this format is always set.

- D = Destination field. The result of the operation is placed into the register whose address is in this field. DATA = The first operand is contained in this field. The second operand is contained in the A Register (AR).

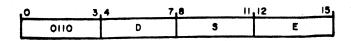

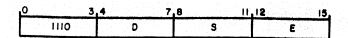

- 4.4 Do, Command, and Test

| 1 | 0 3     |          | 15 |

|---|---------|----------|----|

|   | OP-CODE | FUNCTION |    |

FUNCTION = Specifies the function to be performed or tested.

## 4.5 Branch

| OP-CO | DE | CONDITI | ON  | ADDRES | S   |

|-------|----|---------|-----|--------|-----|

| 0     | 3  | ,4      | 7,8 |        | 15, |

CONDITION = specifies the condition to be tested.

ADDRESS = if the specified condition is true, the program is transferred to the address specified by this field.

## 5. SOURCE AND DESTINATION REGISTERS

Source registers are only available to non-immediate micro-instructions, RD Bit 3 = 0. The sources that may be addressed are shown in Table 2.

TABLE 2. ADDRESSABLE SOURCES

| RD Bits                                                                                | SYMBOLIC REGISTER                                    | RD Bits                                                                     | SYMBOLIC REGISTER             |  |  |

|----------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------|--|--|

| 8 9 10 11<br>0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0 | MR0<br>MR1<br>MR2<br>LOC<br>PSW<br>MAR<br>SRH<br>SRL | 8 9 10 11<br>1 0 0 0<br>1 0 0 1<br>1 0 1 0<br>1 0 1 1<br>1 1 0 0<br>1 1 1 1 | NULL IR MDR IO IR4 YS YD YDP1 |  |  |

|                                                                                        |                                                      |                                                                             |                               |  |  |

The source registers may be used freely in the micro-program. The following paragraphs point out special cases.

MAR can be used as a source register at any time. However, MAR may or may not contain the same data as MAS depending on the state of memory busy. In the latter case, when memory becomes un-busy, whatever is in MAR is copied into MAS.

SRH and SRL are special purpose shift registers. The Command micro-instruction specifying Multiply, Divide, Shift Right or Shift Left, uses SRH and SRL as a 32-bit shift register; SRH containing the most significant 16 bits and SRL the least significant 16 bits. When the NULL source, Address '8', is used, zeros are gated to all 16 bits of the B Bus. When MDR is specified as the source, the execution of the micro-instruction is suspended until memory data is available.

When I/O (Address 'B') appears as the source, an input operation is to be performed. Only in a Load micro-instruction can I/O be a source. The nature of the input request is encoded into the Extended Operation Field of the Load instruction. When the device responds, the data is gated onto the B Bus. Completion of the micro-instruction is suspended until the device responds.

Specifying IR4 causes Bits 8 through 11 of IR to be gated onto the B Bus Bits 12 through 15. Zeros are gated onto B Bus Bits 0 through 11.

The user's 16 general purpose registers do not have individual source addresses. Instead, common symbolic addresses - YS (Address 'D'), YD (Address 'E') and YDP1 (Address 'F') cause the General Registers to be selected from IR Bits 8 through 11 or 12 through 15. When YS appears as the source, the General Register whose address is in IR Bits 12 through 15 is gated onto the B Bus. When YD appears as the source, the General Register whose address is in IR Bits 8 through 11 is gated onto the B Bus. When YDP1 (User's Destination plus 1) appears as the source, the odd member of the even/odd pair of General Registers addressed by IR Bits 8 through 11 is gated onto the B Bus.

The destinations that may be addressed are shown in Table 3.

TABLE 3. ADDRESSABLE DESTINATIONS

| RD BITS | SYMBOLIC REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 5 6 7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0 0 0 0 | RAH * MR0 **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0 0 0 1 | RAL * MR1 **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0 0 1 0 | PSW * MR2 **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0 0 1 1 | LOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 1 0 0 | FLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 1 0 1 | MAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 1 1 0 | SRH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 1 1 1 | SRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1 0 0 0 | AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 0 0 1 | IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 0 1 0 | MDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1 0 1 1 | IO STATE OF THE ST |

| 1 1 0 0 | CTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1 1 0 1 | YS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 1 1 0 | YD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1111    | YDP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

<sup>\*\*</sup> The Bank flip-flop must be set to load MR0, MR1, or MR2

The destination registers may be used by the micro-program noting the following restrictions or special cases.

Loading RAH loads only the outer rank page register of the ROM address register. The ROM decodes the page from the inner rank (RAS). When RAL is loaded, RAH is copied into RAS so that all 12 bits of ROM address change simultaneously.

When PSW is loaded, Bits 12 through 15 of the S Bus are captured in the FLR. PSW Bits 12 through 15 (the condition code) can only be loaded from the FLR on a Do micro-instruction.

When LOC is loaded, MAR is loaded simultaneously.

Anytime memory is not Busy. MAR is copied into MAS.

Loading the FLR in an instruction that normally sets flags causes an OR-ing of the resulting flags and S Bus data.

If an attempt is made to load MDR when memory is Busy, execution of that micro-operation is suspended until memory becomes not Busy. If MDR is the destination in a cross-shift operation, only the high byte (MDH) is loaded if MAR is even and the cross-shift function is performed. If MAR is odd, only the low byte (MDL) is loaded and the cross-shift function is not performed. The portion of the MDR (i.e. MDH or MDL) not loaded remains unchanged. If MDR is the destination and cross-shift is not exercised, both bytes (MDH and MDL) are loaded.

When I/O appears as the destination, an output operation is to be performed. Only in a Load micro-instruction can I/O be a destination. The nature of the output operation is encoded into the Extended operation field of the Load instruction. The S Bus is gated onto the Data Lines. Completion of the micro-instruction is suspended until the device responds or a false SYN is generated.

When YS is the destination, S Bus data is copied into the General Register whose address is in IR Bits 12 through 15.

When YD is the destination, the General Register whose address is in IR Bits 8 through 11 is loaded.

When YDP1 is the destination, the odd member of the even/odd pair of General Registers addressed by IR Bits 8 through 11 is loaded.

## 6. MICRO-INSTRUCTIONS

This section describes each micro-instruction. For each instruction, the assembler format is shown. The machine instruction format is diagrammed, a description of the instruction is provided, and options within the instruction are described.

#### 6.1 Do

## D FUNCTION

| 1 | 0 |      | 3 | 4 |          |      | 15 |

|---|---|------|---|---|----------|------|----|

|   |   | 0000 |   |   | FUNCTION | CODE |    |

| L | 4   | 5   | 6 | 7 | 8 | 9 | 10 | Ш  | 12 | 13 | 14 | 15 |

|---|-----|-----|---|---|---|---|----|----|----|----|----|----|

|   | 1   | 0   |   |   |   |   |    |    |    |    | -  |    |

|   | 0   | -   |   |   |   |   |    | 14 |    |    | 1  |    |

|   | Ī   | -   |   |   |   |   |    |    |    |    | 1  |    |

|   |     |     | 1 |   |   |   |    | 31 |    |    | 1  |    |

|   |     |     |   | 1 |   |   | •  |    |    |    | 1  |    |

| [ |     |     |   |   | 1 |   |    |    |    | A. | 1  |    |

|   |     |     |   |   | 1 | 1 |    |    |    |    | 1  |    |

| I | 5-1 | 77. |   |   |   |   | 1  |    |    | 37 | 1  |    |

|   |     |     |   |   |   |   |    | 1  |    |    | 1  |    |

|   |     | 39  |   |   |   |   |    |    | 1  |    | 1  | 8  |

|   |     |     |   |   |   |   |    |    |    |    | 1  | 1  |

| <u> </u>   | SYMBOLIC MEANING  |

|------------|-------------------|

| MR         | MEMORY READ       |

| MW         | MEMORY WRITE      |

| P <b>W</b> | PRIVILED ED WRITE |

| INC        | INCREMENT LOC     |

| JAM        | COPY FLR TO CC    |

| PC         | PHASE CHANGE      |

| CLR        | CLEAR             |

| SWA        | SET WAIT          |

| CWA        | CLEAR WAIT        |

| ALRM       | LOAD ALARM FLAGS  |

| POW        | POWER DOWN        |

The Do micro-instruction is always written with Bit 14 set.

All zeros in RD are interpreted as illegal unless RD is zero because of initialization. A blanking flip-flop (RUN) covers the initialize period. When the Processor is initialized, the ROM Address Registers and RD are cleared and the RUN flip-flop is reset. Location X'000' in ROM contains all zeros. When this instruction is read, the RUN flip-flop is still reset and the Processor does nothing. The next instruction in sequence (Address X'001') is executed and the RUN flip-flop sets. The next time all zeros occur in RD, the illegal condition will exist, forcing the Processor to Phase Three and ROM address to X'100'.

The DO micro-instruction is executed in one clock period unless a memory cycle is requested (MR, MW, PW) and memory is Busy or phase change is specified and the new phase is Phase zero.

In the former case, the DO micro-instruction can take realistically 1, 2, or 3 clocks depending on when the current memory cycle began. In the latter case, the time depends upon the state of Memory Busy and the type of user instruction to be performed.

The type of user instruction is identified by the most significant four bits of the op-code in IR. Table 4 shows the user repertoire. From Table 4, the following list of op-codes by category is derived.

| RR Instructions: | ړ0_        |

|------------------|------------|

|                  | 1n         |

|                  | 2n         |

|                  | 3n         |

|                  | 8 <b>n</b> |

|                  | 9n         |

|                  |            |

| RX Instructions: | 4n         |

|                  | 52         |

5n 6n 7n An Bn Dn Fn

OP CODES

RS Instructions: Cn

TABLE 4. INSTRUCTION REPERTOIRE

| / | 0    | 1     | 2    | 3     | 4   | 5     | 6    | 7  | 8                                     | 9    | A     | В  | C    | D   | E    | F   |

|---|------|-------|------|-------|-----|-------|------|----|---------------------------------------|------|-------|----|------|-----|------|-----|

| 0 |      |       | BTBS |       | STH | ¥45.6 | STE  |    |                                       | SRLS |       |    | вхн  | STM |      |     |

| 1 | BALR |       | BTFS |       | BAL |       | АНМ  |    | ing.                                  | SLLS |       |    | BXLE | LM  | SVC  |     |

| 2 | BTCR |       | BFBS |       | BTC |       | 4000 |    |                                       | STBR |       |    | LPSW | STB | SINT |     |

| 3 | BFCR |       | BFFS |       | BFC |       |      |    |                                       | LBR  |       |    | THI  | LB  |      |     |

| 4 | NHR  |       | LIS  | 10/11 | NH  |       | ATL  |    | 3.53                                  | EXBR |       |    | NHI  | CLB |      |     |

| 5 | CLHR |       | LCS  |       | CLH |       | ABL  |    |                                       | EPSR |       |    | CLHI | AL  |      |     |

| 6 | OHR  | 17 ag | AIS  |       | ОН  |       | RTL  |    |                                       | WBR  |       |    | OHI  | WB  |      |     |

| 7 | XHR  |       | SIS  |       | XH  |       | RBL  |    |                                       | RBR  | 48.69 |    | хні  | RB  |      |     |

| 8 | LHR  |       | LER  |       | LH  |       | LE   |    |                                       | WHR  |       |    | LHI  | WH  |      |     |

| 9 | CHR  |       | CER  |       | СН  |       | CE   |    |                                       | RHR  |       |    | CHI  | RH  |      |     |

| A | AHR  |       | AER  |       | AH  |       | AE   |    |                                       | WDR  |       |    | AHI  | WD  | RRL  | 1.4 |

| В | SHR  |       | SER  |       | SH  |       | SE   |    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | RDR  |       |    | SHI  | RD  | RLL  |     |

| C | MHR  |       | MER  |       | MH  |       | ME   |    |                                       | MHUR |       |    | SRHL | MHU | SRL  |     |

| D | DHR  |       | DER  |       | DH  |       | DE   |    |                                       | SSR  |       |    | SLHL | SS  | SLL  |     |

| E | ACHR |       |      |       | ACH |       |      |    | La Maria                              | OCR  |       |    | SRHA | OC  | SRA  |     |

| F | SCHR |       |      |       | SCH |       |      |    |                                       | AIR  |       |    | SLHA | AI  | SLA  |     |

| / | RR   | RR    | RR   | RR    | RX  | RX    | RX   | RX | RR                                    | RR   | RX    | RX | RS   | RX  | RS   | RX  |

If an RR instruction is to be performed, the DO micro-instruction requires 2 or 3 clocks. If an instruction other than RR is to be performed, the DO micro-instruction requires 4 or 5 clocks.

When phase change is specified, the new state of the Phase Pointer and the new ROM address depends upon the current phase, the type of user instruction to be executed, and whether or not an interrupt is pending. These factors are summarized in Table 5.

The Phase Pointer has four states. One of these, Phase Zero, exists in hardware only and does not have an associated set of micro-code.

In Phase Zero, the user instruction is loaded into MDR and IR simultaneously. The AR is loaded from YS and the OP flip-flop is set to reflect the length of the user instruction; 0 if RR, 1 if RX or RS. If the user instruction is RX or RS, a second memory read is started to fetch the second half of the instruction word. If the user instruction is not RR, the YS field of IR distinguishes Indexed instructions from unindexed. If the YS field is zero, the instruction is not indexed. If the user instruction is RR or unindexed RS, Phase Zero is exited and the Phase Two entry point is derived from the DROM. If the user instruction is RX or indexed RS, Phase Zero is exited and the appropriate Phase One entry point is generated. There are three micro-sequences associated with Phase One. These sequences are shown below:

| ROM<br>ADRS | ROM<br>DATA |              |                          |                         |

|-------------|-------------|--------------|--------------------------|-------------------------|

|             |             | *INDEXED     | RS ENTRY                 |                         |

| 0002        | CAA3        | AMODRS A     | MDR, MDR INDEX 'A' FIELD | Second overend in MIR   |

| 0003        | 00C2        | $\mathbf{D}$ | PC+CLR GO TO PHASE 2     | Second operand in MO/2. |

|             |             | *NO INDEX    | RX ENTRY                 | The las energy          |

| 0004        | 45A3        | NMODRX L     | MAR, MDR ADRS 'A'        |                         |

| 0005        | 08C2        | D            | MR+PC+CLR GO TO PHASE 2  |                         |

|             |             | *INDEXED RX  | X ENTRY                  |                         |

| 0006        | C5A3        | AMODRS A     | MAR, MDR ADRS 'A' +(X2)  |                         |

| 0007        | 08C2        | D            | MR+PC+CLR GO TO PHASE 2  |                         |

The Do micro-instruction exiting Phase One of an RX instruction would normally execute in three clocks because a memory read is requested and memory is still busy from the read cycle started as Phase Zero was exited. If the user opcode is 40,41,42, or 43, the Do micro-instruction takes only 1 clock. These user instructions (STH, BAL, BTC, and BFC) do not require a second operand so the memory read is not attempted. An unnecessary memory read does occur on STM, STE, AL, and RH instructions.

INDEXED NEW **NEW ROM** CURRENT INTERRUPTS NEXT ADDRESS PHASE ? PHASE INSTR 2 From DROM 1 '010' 2 Yes 3 From DROM 2 No RR 0 then 2 2 From DROM No RS No 0 then 2 10021 2 RS Yes No 0 then 1 2 10041 No No RX0 then 1 10061 2 No RXYes 0 then 1 3 From DROM RR 0 then 2 From DROM 3 No 0 then 2 RS '002' 3 0 then 1 Yes RS '004' 3 RX No 0 then 1 '006' 3 RX Yes 0 then 1

TABLE 5. DECODE PHASE CHANGES

The Phase Two sequence starting address is derived from the Decoder Read-Only-Memory. There are as many Phase Two sequences as there are unique entries in the DROM. Illegal instruction handling is explained in Section 8.

There are three Phase Three entry points: Location X'100' for the Illegal Instruction (RD=0), Location X'010' for Interrupts, and X'00A' for aborted sequences. When Phase 2 is exited, the hardware automatically tests for interrupts. The interrupts tested for are Primary Power Fail (PPF), Machine Malfunction (MALF), Console Attention (CATN), Console Single Mode (SNGL), Data Channel Request (DC), and I/O Attention (ATN). If an interrupt is found pending when the Do micro-instruction that exits Phase Two is executed, the Phase Pointer is set to Phase Three, the INC and MR specifications in the Do micro-instruction are suppressed, and ROM address is forced to X'010'.

The micro-sequence at X'010' determines the nature of the interrupt and executes the appropriate service sequence.

When Phase Two is entered, an Enable flip-flop (EBL) is set. As long as EBL is set, the occurrence of a Data Channel Request (DC) or regular I/O Interrupt (ATN) or a Machine Malfunction (MALF) will cause the user instruction sequence to be aborted. The Processor enters Phase Three and ROM address is forced to X'00A'. The micro-routine at X'00A' decrements the Location Counter by 2 if the user instruction was RR or by 4 if RX or RS, and then enters the common interrupt polling subroutine at X'010'. (Instruction type can be known by testing the OP flip-flop.) After the interrupt is serviced, the user instruction is re-started from the beginning.

The Enable flip-flop is reset whenever the micro-program loads a General Register, loads PSW or LOC, does a Memory Write or Priviledged Write or an I/O operation. When Enable resets, the instruction is not interruptable until the terminating Do micro-instruction is executed.

## **OPTIONS**

The function code bits specify the function(s) to be performed. The Phase Change function has been described; the other functions are described below:

MR Memory Read

MW Memory Write

PW Priviledged Write

A memory cycle consists of two half cycles: Read and Write; in that order. The Read cycle places the contents of the addressed location into MDR. The addressed location then contains zeros (destructive read-out). During the Write cycle, the contents of MDR are written into the addressed location.

Memory Read (MR) is a combination of the Read/Write cycles. The memory location is read-out then restored from MDR. Memory Write (MW) or Priviledged Write (PW) work like this; the memory location is read-out but the data is not saved. Instead, the contents of MDR are written into the addressed location.

Memory Write (MW) and Priveledged Write (PW) commands operate identically if the memory system does not include the Memory Protect option. If the Memory Protect option exists, the PW command unconditionally writes to memory. However, the MW command is subject to memory protect and will be converted to an MR command if the address is in a protected area of memory and if PSW 7 is set. If PSW 7 is reset, the Memory Protect feature is disabled.

INC - Increment LOC - The Location Counter is incremented by two. The result is also copied into MAR.

JAM - Copy FLR to CC - The Condition Code (Bits 12:15) of PSW is loaded from the Flag Register (FLR).

CLR - Clear - The Bank flip-flop and Utility flip-flop are cleared. The Flag Register is cleared. The counter is set to 16.

SWA - Set Wait Alarm - The Wait indicator is set.

CWA - Clear Wait Alarm - The Wait indicator is reset.

ALRM - Copy Alarm Bits - The bits set in the Alarm Register are copied to the Condition Code Register. If JAM is also specified, the Alarm Bits are "ORed" with the Flag Register Bits. The Alarm Register bits are then reset. See Section 8.

POW - Power Down - The system is initialized.

## 6.2 Command

## C FUNCTION

| 0001 |   |     |     |     | FUN | ICTI | ON   | 000 | E    |      |      |    | ]   |                   |

|------|---|-----|-----|-----|-----|------|------|-----|------|------|------|----|-----|-------------------|

|      |   |     |     |     |     |      |      |     |      |      |      |    |     |                   |

|      | 4 | , 5 | , 6 | , 7 | , 8 | , 9  | , 10 | 111 | , 12 | , 13 | , 14 | 15 | 1 - | SYMBOLIC MEANING  |

|      | 1 | 0   |     |     |     |      |      |     |      |      |      |    | MR  | MEMORY READ       |

|      | 0 | ī   |     |     |     |      |      |     |      |      |      |    | MW  | MEMORY WRITE      |

|      | 1 | T   |     |     |     |      | T    |     |      |      |      |    | PW  | PRIVILEDGED WRITE |

|      |   |     | T   | T   |     |      |      |     |      |      | ī    | ı  | MPY | MULTIPLY          |

|      |   |     | T   |     | ī   |      |      |     |      |      | 0    | 1  | DIV | DIVIDE            |

|      |   |     | 1   |     |     | 1    |      |     |      |      |      |    | RPT | REPEAT            |

| 1 | 1 | 1 | 1 |   |   | -1 |   |   |   | " | 1 |     |                |

|---|---|---|---|---|---|----|---|---|---|---|---|-----|----------------|

|   |   |   |   |   | 1 |    |   |   |   |   |   | RPT | REPEAT         |

|   |   | 0 | 1 |   |   |    |   |   |   |   |   | SRI | SHIFT RIGHT    |

|   |   | 0 |   | ī |   |    |   |   |   |   |   | SLI | SHIFT LEFT     |

|   |   |   |   |   |   | ī  | 0 |   |   |   |   | SUT | SET UTILITY    |

|   |   |   |   |   |   | 0  | 1 |   |   |   |   | СПТ | RESET UTILITY  |

|   |   |   |   |   |   | 1  | 1 |   |   |   |   | TUT | TOGGLE UTILITY |

| Г |   |   |   |   |   |    |   | T |   |   |   | SB  | SET BANK       |

|   |   |   |   |   |   |    |   |   | ī |   |   | СВ  | CLEAR BANK     |

|   |   |   |   |   |   |    |   |   |   | ī |   | CI  | CARRY IN       |

|   |   |   |   |   |   |    |   |   |   |   |   |     |                |

The Command micro-instruction results in the performance of the machine functions specified by the Function Code Bits. The functions are described below.

CO

CARRY OUT

MR Memory Read

MW Memory Write

PW Priviledged Write

MPY - Multiply - The Processor multiplies the 16 bit multiplicand in AR by the 16 bit multiplier in SRL. The 32-bit product resides in SRH and SRL. To achieve this, the following setup conditions must exist. The counter contains 16; SRH contains zero; SRL and AR contain the operands; and the Carry Flag is reset. The C MPY instruction executes in sixteen Processor clock periods (16t). After the C MPY instruction, the 32-bit product in SRH and SRL must be shifted right one more position.

DIV - Divide - The Processor divides the 32 bit dividend in SRH and SRL by the 16 bit divisor in AR. To achieve this, the following setup conditions must exist. The counter contains 16; SRH/SRL contains a positive dividend that is less than 65,536 times the divisor. The AR contains the divisor in two's complement negative form; and the Carry Flag is reset. The C DIV instruction executes in 16t. After the C DIV instruction, the quotient resides in SRL and the remainder is in SRH.

RPT - Repeat - If the counter is not zero, the next sequential micro-instruction is repeated the number of times specified in the Counter Register. If the counter is zero, the next sequential micro-instruction is skipped. Any reasonable instruction may be repeated that does not result in a Branch (Branch, Load RAL or Decode Phase Change).

SR1 - Shift Right - The 32-bit shift register (SRH/SRL) is shifted right one position. Carry in and out are specifiable.

SLI - Shift Left - The 32-bit shift register (SRH/SRL) is shifted left one position. Carry in and out are specifiable.

SUT - Set Utility

CUT - Reset Utility

TUT - Toggle (complement) Utility

The Utility flip-flop has no hardware function assigned to it. It is for program control and may be tested with the test micro-instruction.

SB - Set Bank

CB - Clear Bank

The Bank flip-flop controls the addressing of certain registers.

If no functions are specified, the Assembler leaves the function code field reset.

6.3 Test

T FUNCTION

| 1 | 0 3  | 4             |

|---|------|---------------|

| 1 | 0010 | FUNCTION CODE |

|   | 4  | 5 | 6 | 7 | 8     | 9     | 10 | 11 | 12  | 13 | 14  | 15 |

|---|----|---|---|---|-------|-------|----|----|-----|----|-----|----|

| ٠ | 1  |   |   |   |       |       |    |    |     |    |     |    |

|   | 11 | - |   |   |       |       |    |    |     |    |     |    |

|   |    |   | 1 |   | 10.00 | 1 4 4 |    |    |     |    |     |    |

|   |    |   |   | 1 |       |       |    |    |     |    |     |    |

|   |    |   |   |   | -     |       |    |    | 1   |    |     |    |

|   |    |   |   |   |       | I     |    |    | · . |    |     |    |

| 1 |    |   |   |   |       |       | 1  |    |     |    |     |    |

|   |    |   |   |   |       |       |    | 1  |     |    |     |    |

|   |    |   |   |   |       |       |    |    | 1   |    | 3.1 |    |

|   |    |   |   |   |       |       |    |    |     | 1  |     |    |

|   |    |   |   |   |       |       |    |    |     |    | 1   |    |

|   |    |   |   |   |       |       |    |    |     |    |     | ı  |

|      | SYMBOLIC MEANING      |

|------|-----------------------|

| FAST | FAST I/O INTERRUPT    |

| ATN  | I/O ATTENTION         |

| ARST | AUTO RESTART          |

| CATN | CONSOLE ATTENTION     |

| SNGL | CONSOLE SINGLE MODE   |

| UT   | UTILITY FLIP-FLOP     |

| MALF | MACHINE MALFUNCTION   |

| PPF  | PRIMARY POWER FAIL    |

| DC   | DATA CHANNEL REQUEST  |

| DRD  | DATA CHANNEL READ     |

| MSK  | MASK BITS             |

| OP   | USER OPERATION LENGTH |

If any of the machine functions specified by the function code bits are true, the Greater than (G) flag is set and the Less than (L) flag is reset. If none of the tested functions are true, the Less than (L) flag is set and the Greater than (G) flag is reset. The Testable functions are:

FAST - High Speed Interrupt - This flip-flop is AC set when the FAST0 interrupt line becomes active. This interrupt line is separate from the normal ATN line and may have any priority the micro-programmer decides. The FAST0 interrupt may be enabled by a PSW bit (PSW04) by back-panel strapping. After the micro-program tests the FAST flip-flop, the flip-flop automatically resets.

ATN - I/O Attention - An external device is requesting Processor service and PSW Bit 1 is set.

ARST - Automatic Restart - This is a hardwire strap option with significance only to the emulator.

CATN - Console Attention - The console EXEcute Switch has been depressed.

SNGL - Console Single Mode - The SNGL flip-flop in the display controller is set.

# UT - Utility flip-flop set

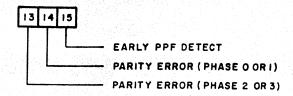

MALF - Machine Malfunction - One of the bits in the Machine Malfunction Alarm Register is set. The alarm bits are Parity Error Phase Zero or One, Parity Error Phase Two, and Early Power Fail Detect.

PPF - Primary Power Fail - This signal occurs one millisecond after Early Power Fail Detect. The Micro-Code has one millisecond before system initialize occurs.

DC - Data Channel Request

DRD - Data Channel Read/Write

A special halfword device on the data channel is requesting memory access. The state of DRD determines Read or Write, 0 or 1, respectively.

MSK - Mask Bits - The AND of the Condition Code Bits (PSW 12:15) with IR4 (IR8:11) is tested.

OP - User Operation Length - This flip-flop is adjusted in Phase Zero. It is set to one if the user instruction is RX or RS. It is set to zero if the user instruction is RR.

## 6.4 Branch

B COND, ADDRESS

| 0 3  | 4 7       | ,8 <u>15</u> , |  |

|------|-----------|----------------|--|

| 0011 | CONDITION | ADDRESS        |  |

The Branch micro-instruction results in a transfer in the micro-program sequence if any of the specified conditions are true. If none of the conditions are true, the next sequential instruction is performed.

The condition is specified by RD Bits 4 through 7.

| RD BIT  | CONDITION     |                             |

|---------|---------------|-----------------------------|

| 4 5 6 7 | SYMBOLIC      | MEANING                     |

| 0 0 0 0 | CTR           | Branch if Counter not 1     |

| 1 X X X | $\mathbf{c}$  | Branch if Carry true        |

| X 1 X X | v             | Branch if Overflow true     |

| X X 1 X | G             | Branch if Greater than zero |

| X X X 1 | $-\mathbf{L}$ | Branch if Less than zero    |

The Branch on Counter instruction results in a transfer if the Counter Register does not equal 000012. The counter is decremented by one regardless of its previous state.

The conditions C, V, G, or L may be specified singularly or in combination. Each condition bit is matched against the corresponding bit in the Flag Register. If a match is made, the ADDRESS field is copied to RAL, and RAS is loaded from RAH. If no match is made, the next instruction in sequence is executed. The instruction requires two Processor clocks (2t) if a branch is made. If no branch, the instruction takes 1t.

# 6.5 Load

L D, S, E

The contents of the register specified by the Source (S) Field are copied into the register specified by the Destination (D) Field.

If neither the Source nor Destination field specify I/O, the E field has the following meaning:

| 12 13 14 15        | SYMBOLIC | <u>MEANING</u>                                                                                                                                                                                                                                                                                                                 |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 X X<br>0 1 X X | SR       | No shifts.                                                                                                                                                                                                                                                                                                                     |

|                    |          | Shift Right. The source data is shifted right one bit position and copied into the Destination Register.                                                                                                                                                                                                                       |

| 1 0 X X            | SL       | Shift Left. The source data is shifted left one bit position and copied into the Destination Register.                                                                                                                                                                                                                         |

| 1 1 X X            | CS       | Cross Shift. The source data is rotated eight bit positions and copied into the Destination Register. If MDR is the Source or Destination, the cross-shift will occur only if MAR is even. If MDR is the Destination and MAR is even, only the high byte (MDH) of MDR is loaded. If MAR is odd, only the low byte (MDL) of MDR |

| X X 0 0            | NC       | is loaded. The byte not loaded remains unchanged.                                                                                                                                                                                                                                                                              |

| X X 0 1            | CO       | No Carry. The Carry Flag is unaltered.  Carry Out but not in. If a one is shifted out, the Carry Flag is set. If a zero is shifted out, the Carry Flag is reset.                                                                                                                                                               |

| X X 1 0            | CI       | Carry In but not out. The state of the Carry Flag is shifted into the most significant bit if Shift Right or the least significant bit if Shift Left.                                                                                                                                                                          |

| X X 1 1            | С        | Carry In and Out.                                                                                                                                                                                                                                                                                                              |

If no options are specified, the Assembler sets the E Field to 0011.

If the Destination (D) Field specifies I/O, an output operation is to be performed. The E Field has the following meaning: