# 32 Bit Series Reference Manual

# 0 INTERDATA

# 32 Bit Series Reference Manual

Publication Number 29-365R01

INFORMATION CONTAINED IN THIS MANUAL IS SUBJECT TO DESIGN CHANGE OR PRODUCT IMPROVEMENT

# TABLE OF CONTENTS

| CHAFT   | LN I SIS                  | LENIDE                | _ocn    | 11 11   | ON          | ٠.       | •    | •    | •          | •   | •  | •  | • | • | • | ٠ | • | • | •   | • | • | •   | • | • - |     | • |   |     | ٦. |

|---------|---------------------------|-----------------------|---------|---------|-------------|----------|------|------|------------|-----|----|----|---|---|---|---|---|---|-----|---|---|-----|---|-----|-----|---|---|-----|----|

| MEMOR   | RY SYSTE                  | м                     |         |         |             |          |      | •    |            |     |    |    | • |   |   | • | ٠ |   |     |   |   |     |   |     | ٠.  |   |   |     | 1  |

| r       | Direct Mer                | norv Ac               | cocc    |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

|         |                           |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| Ī       | Relocation                | and Pro               | tecti   | on .    |             |          |      |      |            |     |    |    |   |   | Ċ | : | : | : | •   | • | • | •   | • | • • | •   | ٠ | • | •   | 2  |

|         |                           |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| MULTIP  | LEXOR !                   | NPUT/C                | OUTP    | UT E    | BUS         |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 2  |

| PERIPH  | ERALS .                   |                       |         |         | •           |          | -    |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 2  |

| _       |                           |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

|         | Digitial Mu               | iltiplexo             | r       |         | •           |          | ٠    | •    | •          | •   | •  | ٠  | • | ٠ | ٠ | ٠ | • | • | •   | • | • |     | • |     |     | • |   |     | 2  |

|         | Intertape (<br>Industry C | assette               | Syste   | m .     | :- T        | • •      | ç.,  | •    | •          | •   | •  | •  | • | ٠ | • | ٠ | • | • | •   | • | • | •   | • |     | •   | • | • | •   | 3  |

|         | Removable                 | ompauu<br>Cartrid     | ae Di   | er Sv   | IC II       | ape<br>n | Эу   | ste  | ms         | •   | •  | •  | • | • | • | • | • | • | •   | • | • | •   | • | • • | •   | • | • | •   | 3  |

| 7       | Alphanum                  | eric Disc             | olav T  | ermi    | inals       |          | •    | •    | •          | •   | •  | •  | • | • | • | • | • | • | •   | • |   | •   | • | • • | . • | • | • | •   | 3  |

| Ē       | Data Com                  | nunicati              | ons E   | quip    | men         | it.      | Ċ    | •    | :          | :   | :  | :  | : | : | : | : |   |   | •   | : |   |     |   | •   |     | • | • | •   | 3  |

| ŀ       | High Speed                | l Paper 1             | Гаре 3  | Syste   | m           |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 3  |

| S       | System Mo                 | dules .               |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 3  |

|         |                           |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

|         | SSOR                      |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| F       | Program S                 | tatus Wo              | rd .    |         | •           |          | •    | ٠    | •          | •   | •  | •  | • | • | • | • | • | • | •   | • | • | •   | • |     | •   | ٠ | • | •   | 4  |

|         | ,                         | Wait State            |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 4  |

|         |                           | mmediat               | e Inter | rupt    | Mask        |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 4  |

|         |                           | Machine N             | Aalfun  | ction   | Inte        | rrup     | t M  | ask  |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 5  |

|         | :                         | Arithmeti             | c Faul  | t Inte  | rrup        | t Ma     | sk   | •    | •          |     | •  |    |   |   |   |   |   | • |     |   |   |     | • |     |     | • |   |     | 5  |

|         |                           | Relocation            | n Prot  | ection  | <u>Inte</u> | erruj    | ot A | Aasi | <u>.</u>   | ٠   | •  | •  | ٠ | • |   | • | • | • | •   |   | • | •   | • |     |     | • | • | •   | 5  |

|         | ;                         | System O<br>Protect M | ueue S  | ervici  | e Inte      | erruj    | pt N | Mas1 | <u>K</u> . | •   | ٠  | •  | • | ٠ | • | ٠ | • | • | •   | • | • | •   | • | •   |     | ٠ | • | •   | 5  |

|         |                           | Register S            | or Cal  | <br>Bot | •           |          | •    | •    | •          | •   | •  | ٠  | • | • | • | • | • | • | •   | ٠ | • | •   | • |     |     | • | • | •   | 5  |

|         |                           | Condition             | Code    | •       | :           | • •      | •    | •    | :          | •   | :  | •  | • | • | : | • | : | : | :   | • | • | •   | • |     |     |   | • | •   | 5  |

|         |                           | Location (            |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| G       | General Re                |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| F       | Floating Po               | oint Reg              | ister   | : :     | •           |          |      | •    | •          | •   |    |    | • | • | : | • | • | • | •   |   |   |     |   |     | •   | • | • | •   | 6  |

| F       | Processor                 | nterrupt              | ts .    |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     | _ |   |     | 6  |

| F       | Reserved N                | femory i              | Locat   | ions    |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 6  |

| P       | rocessor (                | Operation             | n.      |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 7  |

| DATA F  | ORMATS                    |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 7  |

| _       |                           | _                     |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| F       | Fixed Poin                | t Data                |         |         |             |          | •    | •    |            |     |    |    | • |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 7  |

| , r     | Floating Po               | oint Data             | а.      |         |             |          | •    | •    | •          | •   | •  | •  | • | • | • | ٠ | • | • | •   |   | • |     | • |     |     | • | • | •   | 7  |

| L       | Logical Da                | ld                    |         |         | •           | • •      | •    | •    | ٠          | •   | •  | •  | • | ٠ | • | ٠ | • | • | •   | • | • | •   | • |     | •   | • | • | •   | /  |

| INSTRU  | ICTION F                  | ORMAT                 | S.      |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 8  |

|         | Register to               | Ragioto               | , /DD   | ) Fa    | <b></b>     |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | ^  |

|         | Short Form                |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   | :   | _  |

|         | Register ar               |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| F       | Register ar               | d Index               | ed St   | orage   | Tw          | 10 (I    | RX   | 2)   | Fo         | rm  | at |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 10 |

| F       | Register ar               | d Index               | ed St   | orage   | : Th        | ree      | (R   | ХЗ   | ) F        | orr | ma | t  |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 10 |

|         | Register an               |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| F       | Register ar               | d Imme                | diate   | Stor    | age '       | Two      | ) (J | R12  | ?) F       | or  | ma | it | ٠ | • | • | • | ٠ | • | •   |   | • | •   |   |     | •   | • | ٠ | •   | 11 |

|         | Branch Ins                |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| r       | rogrammi                  | ng Note               |         |         | •           | • •      | •    | •    | •          | •   | •  | •  | • | ٠ | • | • | • | • | •   | • | • | • • | • |     | •   | • | • | ٠   | 11 |

| СПУВТЕ  | EB 2 100                  | ICAL O                | DE D    | A T 10  | MIC         |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| OHA! IE | ER 2 LOG                  | IIOAL U               | r CR/   | 4 I IC  | MA          | •        | •    | •    | •          | •   | •  | •  | • | • | • | • | • | • | • • | • | ٠ | •   | • | •   | ٠   | • | ٠ | • ' | 13 |

|         | ORMATS                    |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     | 13 |

| OPERAT  | TIONS                     |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

|         |                           | _                     |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

|         | Boolean Op                | perations             | •       | • •     | •           |          | •    | •    | •          | •   | •  | •  | • | • | • | • | • |   | •   |   | • |     |   |     | •   | • |   | •   | 14 |

| _       | ranslation<br>ist Proces  |                       |         |         |             |          |      |      |            |     |    |    |   |   |   |   |   |   |     |   |   |     |   |     |     |   |   |     |    |

| L       | .iat F(OCES               | only .                |         |         | •           |          | •    |      | ٠          | •   | •  | •  | • | • | • |   | • | • | •   |   |   |     |   |     | •   | • |   |     | 15 |

| LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS |   | • . |     |   |     |   |   |     |   |   | • |     | •  |   | • |   |     | 16       |

|--------------------------------------------------|---|-----|-----|---|-----|---|---|-----|---|---|---|-----|----|---|---|---|-----|----------|

|                                                  |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     |          |

| Load                                             |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | . 15     |

| Load Register                                    |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   | • |     | 18       |

| Load Immediate                                   |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 18       |

| Load Immediate Short                             |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 18       |

| Load Complement Short                            |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 18       |

| Load Halfword                                    |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 19       |

| Load Halfword Immediate                          |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 19       |

| Load Address                                     |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 20       |

| Load Halfword Logical                            |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 21       |

| Load Multiple                                    |   |     |     |   |     |   |   |     |   |   | - |     |    |   |   |   |     | 22       |

| Load Byte                                        |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 23       |

| Load Byte Register                               |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 23       |

| Exchange Halfword Register                       |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 24       |

| Exchange Byte Register                           |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 25       |

| Store                                            |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 26       |

| Store Halfword                                   |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 27       |

| Store Multiple                                   |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 28       |

| Store Byte                                       |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 20       |

| Store Byte Register · · · · · ·                  | • |     |     | • |     |   | • |     |   | • | • |     | •  |   |   |   |     | 29       |

| Compare Logical · · · · · · · ·                  |   |     |     |   |     |   |   |     |   | • |   |     |    |   |   |   |     | . 20     |

| Compare Logical Register · · · · ·               |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | . 30     |

| Compare Logical Immediate · · · ·                |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | . 30     |

| Compare Logical Halfword · · · ·                 |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 31       |

| Compare Logical Halfword Immediate               |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 31       |

| Compare Logical Byte                             |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 32       |

| AND                                              |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | . 32     |

| AND Register                                     |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 33       |

| AND Immediate                                    |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 33       |

| AND Halfword                                     |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 3/       |

| AND Halfword Immediate                           |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 3/       |

| OR                                               |   |     |     |   |     |   |   |     |   |   | • |     |    |   |   |   |     | 35       |

| OR Register                                      |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     | 35       |

| OR Immediate                                     |   |     |     |   |     |   |   |     |   |   |   |     | Ī  |   |   |   |     | . 3E     |

| OR Halfword                                      |   |     |     |   |     |   | _ |     | - | Ĭ |   |     | Ĭ. | Ī | - |   | •   | 36       |

| OR Halfword Immediate                            | • |     | •   | • |     | • | • | • • | • | • | • | • • | •  | • | • | • | •   | 36       |

| Exclusive OR                                     | • | •   | • • | • |     | • |   |     | • | • | • | • • | •  | • | • | • | •   | 27       |

| Exclusive OR Register                            | • | •   |     | • |     | • | • | • • | Ċ | • | • | • • | •  | • | • | • | •   | 27       |

| Exclusive OR Immediate                           | • | •   | • • |   | •   | • | • | • • | • | • | • | • • | •  | • | • | • | • • | 27       |

| Exclusive OR Halfword                            | • | :   |     | • |     | • | • | • • | • | • | • |     | •  | • | • | • | • • | 20       |

| Exclusive OR Halfword Immediate                  | • | •   |     | · | •   | • | • | •   | • | • | • | • • | •  | • | • | • | ٠.  | 20       |

| Test Immediate                                   | • | •   | • • | • |     | • | • | • • | • | • | • | • • | •  | • | • | • | •   | 20       |

| Test Halfword Immediate                          | • | •   |     | • |     | • | • |     | • | • | • | • • | •  | • | • | • |     | 40       |

| Shift Left Logical                               | • |     |     | • |     | • | • | •   | • | • | • | •   | •  | • | • | • | •   | 40       |

| Shift Left Logical Short                         | • | •   | •   | • | •   | • | • | • • | • | • | • | • • | •  | • | • | • |     | 41       |

| Shift Right Logical                              | • | :   | •   | : |     | • | • | •   | • | • | • | • • | •  | • | • | • | •   | 41       |

| Shift Right Logical Short                        | • |     |     | • | •   | • | • | • • | • | • | • | • • | •  | • | • | • | •   | 42       |

| Shift Left Halfword Logical                      | • | •   | • • | • | •   | • | • | • • | • | • | • | • • | •  | • | • | • | • • | 42       |

| Shift Left Halfword Logical Short                | • |     | •   | • | •   | • | • | • • | • | • | • | • • | •  | • | • | • | ٠.  | 40       |

| Shift Right Halfword Logical                     | • | •   | • • | • | ٠.  | • | • | • • | • | • | • | • • | •  | • | • | • | ٠.  | 43       |

| Shift Right Halfword Logical Short .             | • | •   | •   | • | •   | • | • | • • | • | • | • | • • | •  | • | • | • | •   | 44       |

| Rotate Left Logical                              | • |     | •   | • | •   | • | • | •   | • | • | • | • • | •  | • | • | • | ٠.  | 44       |

| Rotate Right Logical                             | • | •   | • • | • | • • | • | • | • • | • | • | • |     | •  | • | • | • |     | 40       |

| Test and Set                                     | • | •   | • • | • | • • | • | • | • • | • | • | • | • • | •  | • | • | • | ٠.  | 40       |

| Test Bit                                         | • | •   | • • | • | • • | • | • | • • | ٠ | • | • | • • | ٠  | • | • | • | • • | 4/       |

| Set Bit                                          |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     |          |

| Complement Bit                                   | • | •   | • • | • |     | • | • | • • | • | • | • | • • | •  | • | • | • | ٠.  | 43       |

| Reset Bit                                        |   |     |     |   |     |   |   |     |   |   |   |     |    |   |   |   |     |          |

| Cyclic Redundancy Check Modulo 12                | • | •   | •   | • |     | • | • | • • | • | • | • | • • | •  | • | • | • |     | 2 l      |

| Cyclic Redundancy Check Modulo 16                | • | •   | • • | • | • • | • | • | • • | • | • | • | • • | •  | • | • | • |     | 52       |

| Translate                                        | • | •   | • • | • |     | • | • | • • | • | • | • |     | •  | • | • | • |     | 52       |

| Add to Top of List                               | • | •   | •   | • |     | • | • | •   | • | • | • | • • | •  | • | ٠ | • | • • | 53<br>E4 |

| Add to Bottom of List                            | • | •   | • • | • |     | • | • | •   | • | • | • | • • | •  | • | • | • | ٠.  | 04<br>E4 |

| Remove from Top of List                          | • | •   | • • | • |     | • | • | • • | • | • | • | • • | •  | • | ٠ | • |     | 54<br>EE |

| Remove from Bottom of List                       | • |     | •   | • |     | • | • | • • | • | • | • | • • | •  | • | • | • | • • | 55<br>55 |

| CHAPTER 3 BRANCHING                    | •  | • | - | • | • | • | • |     | • | • | • | • • | •   | • | • | • |     | • | • | · 57         |

|----------------------------------------|----|---|---|---|---|---|---|-----|---|---|---|-----|-----|---|---|---|-----|---|---|--------------|

| OPERATIONS                             |    |   |   | • |   |   | • |     |   | • |   |     | •   |   |   |   |     |   | • | · 57         |

| Decision Making                        |    | • | : |   | • |   |   |     |   | : | • |     |     |   | • |   |     |   |   | · 57<br>· 57 |

| BRANCH INSTRUCTION FORMATS             |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 57         |

| BRANCH INSTRUCTIONS                    | •  | • | • | • | • | • | • |     | • | • | • | •   | •   | • | ٠ | • | • • | • | • | · 58         |

| Branch on False Condition              |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | - 59         |

| Branch on False Condition Register     | .: |   | • | • | • | • | • |     | • | • | • | •   | •   | • | • | • |     | • | • | - 59         |

| Branch on False Condition Backwar      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch on False Condition Forward      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch on True Condition               |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch on True Condition Register      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch on True Condition Backware      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch on True Condition Forward       |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch and Link                        |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch and Link Register               |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Brnach on Index Low or Equal           |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Branch on Index High,                  | •  | • | • | • | ٠ | • | • |     | • | ٠ | • | •   |     | • | • | • |     | • | • | · 63         |

| CHAPTER 4 FIXED POINT ARITHMETIC       | c. |   |   |   |   |   |   |     | • |   |   | •   |     |   |   | • |     |   |   | · 65         |

| DATA FORMATS                           |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | . 65         |

| OPERATIONS                             |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 65         |

| CONDITION CODE                         |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 66         |

| <b>FIXED POINT INSTRUCTION FORMATS</b> | ;  |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | . 66         |

| FIXED POINT INSTRUCTIONS               |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 86         |

|                                        |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Add                                    |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 67         |

| Add Register                           |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 67         |

| Add Immediate                          |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 67         |

| Add Immediate Short                    |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 67         |

| Add Halfword                           |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 68         |

| Add Halfword Immediate                 |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 68         |

| Add to Memory                          |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Add Halfword to Memory                 |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | . 70         |

| Subtract                               |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Subtract Register                      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Subtract Immediate                     |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Subtract Immediate Short               |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Subtract Halfword                      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | . 72         |

| Subtract Halfword Immediate            |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | . 72         |

| Compare                                |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Compare Register                       |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 73         |

| Compare Immediate                      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 73         |

| Compare Halfword                       |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 74         |

| Compare Halfword Immediate             |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 74         |

| Multiply                               |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 75         |

| Multiply Register                      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 75         |

| Multiply Halfword                      |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 76         |

| Multiply Halfword Register             |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 76         |

| Divide                                 |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · 70<br>· 77 |

| Divide Register                        |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | · //         |

| Divide Halfword                        |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | • •          |

| Divide Halfword Register               | •  | • | • | • | • | • | • |     | • | • | • | •   | . • | • | • | • |     | • |   | · 78         |

| Shift Left Arithmetic                  | •  | • | • | • | • | • | • | •   | • | • | • | •   | . • | • | • | • |     | • |   | · 78         |

| Shift Left Halfword Arithmetic         | •  | • | • | • | • | • | • | • • | • | • | • | •   | • • | • | • | • |     | • | • | · 79         |

| Shift Right Arithmetic                 | •  | • | • | • | • | • | • | •   | • | • | • | •   | •   | • | • | • |     | • | • | · 80         |

| Shift Right Halfword Arithmetic        | •  | • | • | • | • | • | • | •   | • | • | • | •   | •   | • | • | • | • • | • | • | . QI         |

|                                        |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   |              |

| Convert to Halfword Value Register     |    |   |   |   |   |   |   |     |   |   |   |     |     |   |   |   |     |   |   | . 83         |

| CHAPTER 5 FLOATING POINT ARITHMETIC                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | 35<br>35<br>36                                                             |

| CONDITION CODE                                                                                                                                                                                                                                                                                                                                                                                                               | 36                                                                         |

| Load Register       8         Load Multiple       8         Store       9         Store Multiple       9         Add       9         Add Register       9         Subtract       9         Subtract Register       9         Compare       9         Compare Register       9         Multiply       9         Mutilply Register       9         Divide       9         Divide Register       9         Fix Register       9 | 39<br>30<br>31<br>32<br>32<br>33<br>34<br>34<br>35<br>36<br>36<br>36<br>37 |

| CHAPTER 6 STATUS SWITCHING AND INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                    | 99                                                                         |

| PROGRAM STATUS WORD                                                                                                                                                                                                                                                                                                                                                                                                          | <del>79</del>                                                              |

| Wait State                                                                                                                                                                                                                                                                                                                                                                                                                   | )O                                                                         |

| INTERRUPT SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

| Immediate Interrupt                                                                                                                                                                                                                                                                                                                                                                                                          | 02<br>03<br>03<br>04<br>05<br>05                                           |

| STATUS SWITCHING INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| Load Program Status Word                                                                                                                                                                                                                                                                                                                                                                                                     | 08<br>09<br>10                                                             |

| CHAPTER 7 INPUT OUTPUT OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                         |

| DEVICE CONTROLLERS                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                         |

| Device Addressing                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                         |

| INTERRUPT SERVICE POINTER TABLE |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 114                                     |

|---------------------------------|---|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|-----|-----------------------------------------|

| I/O INSTRUCTION FORMATS         | • | • | ٠ | • | • | • | • | • | • | • | •   |   | • | ٠ | ٠ | • | ٠ | • | • | • | ٠.  | 115                                     |

| I/O INSTRUCTIONS                | • | • | • | • | • | • | • | • | • | • | •   |   | • | • | • | • | • | • | • | • | • • | • • • • • • • • • • • • • • • • • • • • |

| Sense Status                    |   |   |   |   |   |   |   |   |   |   | . , |   |   |   |   |   |   |   |   |   |     | 116                                     |

| Sense Status Register           |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 116                                     |

| Output Command                  |   |   |   | • |   |   | • | • |   |   |     |   |   |   |   |   |   |   |   |   |     | 117                                     |

| Output Command Register         | • | - | • | • | • |   | • |   |   | • |     |   | • | • |   |   | • |   | • | • |     | 117                                     |

| Read Data                       | • | • | • | • | • | • | • | • | • | • | •   | • | • | ٠ | ٠ | • | • | ٠ | • | • |     | 110                                     |

| Read Data Register              | • | ٠ | • | • | • | • | • | • | • | • | •   | • | • | ٠ | • | • | • | ٠ | • | • |     | 110                                     |

| Read Halfword Register          | • | • | • | • | • | • | • | • | • | • | •   | • | • | • | • | • | • | ٠ | • | • | • • | 119                                     |

| Read Block                      | • | • | • | • | • | • | • | • | • | • | •   | • | • | • | • | • | • | ٠ | • | • | • • | 120                                     |

| Read Block Register             |   | _ |   |   | _ |   | _ | _ |   |   |     |   | _ |   |   | _ |   | _ |   |   |     | 121                                     |

| Write Data                      | _ | _ | _ | _ | _ | _ |   | _ |   | _ |     |   | _ | _ | _ | _ | _ | _ | _ | _ |     | 122                                     |

| Write Data Register             |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 122                                     |

| Write Halfword                  |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 123                                     |

| Write Halfword Register         |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 123                                     |

| Write Block                     |   |   |   |   |   |   |   |   | _ |   |     |   |   | _ |   |   | _ |   |   |   |     | 124                                     |

| Write Block Register            |   | • |   |   |   | • |   |   | • | - |     |   |   |   |   |   |   |   |   |   |     | 125                                     |

| Autoload                        |   |   |   | • | • |   |   |   |   |   |     |   | • |   |   |   | • |   | • | • |     | 120                                     |

| Simulate Channel Program        | • | • | • | • | • |   | • | • | • | • |     |   |   | • | • | • | • | • | • | • |     | 127                                     |

| CONTROL OF I/O OPERATIONS       |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 128                                     |

| STATUS MONITORING I/O           | • | • | • | • | • | ٠ | • | • | • | • | •   | • | • | ٠ | • | • | • | ٠ | • | • |     | 128                                     |

|                                 |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| INTERRUPT DRIVEN I/O            |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| SELECTOR CHANNEL I/O            |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 130                                     |

|                                 |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| Selector Channel Devices        |   |   |   | • |   |   |   |   |   | - |     |   |   |   |   |   | • |   |   |   |     | 130                                     |

| Selector Channel Operation      |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   | • |   |     | 130                                     |

| Selector Channel Programming    |   | • | • | • | • | • | • | • | • |   |     | • | • | • | • | • | • | • | • |   |     | 131                                     |

| AUTO DRIVER CHANNEL             |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 121                                     |

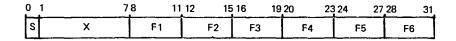

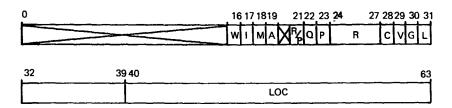

| CHANNEL COMMAND BLOCK           | • | • | ٠ | • | • | ٠ | • | • | • | • | ٠.  | • | • | • | • | • | • | • | • | • | ٠.  | 122                                     |

| CHANNEL COMMAND BLOCK           | • | • | ٠ | • | • | • | • | • | • | • | •   | • | • | • | • | ٠ | ٠ | • | • | • | • • | 132                                     |

| Subroutine Address              |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 132                                     |

| Buffer                          |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| Translation                     |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| Check Word                      |   | • | • | • |   |   | : |   |   |   |     |   | · |   | : | : |   | • | : | • | : : | 133                                     |

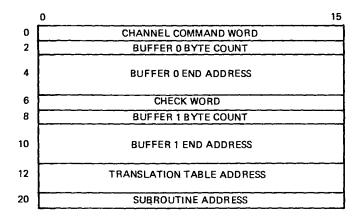

| Channel Command Word            |   |   |   | Ċ |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 134                                     |

|                                 |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| Status Mask                     |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 134                                     |

| Execute Bit (E)                 |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 124                                     |

| Fast Bit (F)                    |   |   |   |   | • | • |   |   |   |   |     |   |   | • |   |   |   | ٠ | • |   | ٠.  | 134                                     |

| Read/Write Bit (R/W)            |   |   | • |   | • | • | • | • | • | • |     |   | • | • | • | • | • |   | • | • |     | 134                                     |

| Translate Bit (T)               |   |   | • | • | • | • | • | • | • | • | •   |   | • | • | ٠ | • | • | • | • | • |     | 134                                     |

| Check Type Bit (C)              |   | • | ٠ | • | • | ٠ | • | • | • | • | •   | • | • | • | • | • | • | • | • | • | ٠.  | 135                                     |

| Buffer Switch Bit (B)           | • | • | ٠ | • | ٠ | • | • | • | • | • | •   | • | • | • | • | • | • | • | • | • | •   | 135                                     |

| Valid Channel Command Codes     |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

|                                 | • | • | • | • |   |   | - | - |   |   |     | , | - |   |   |   |   |   |   |   |     | 135                                     |

| CHAPTER 8 MEMORY MANAGEMENT .   |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 127                                     |

| CHAFTER O WIEWIORT MANAGEMENT.  | • | • | • | • | • | • | • | • | • | • | •   | • | • | • | • | • | • | • | • | • | • • | 13/                                     |

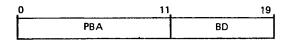

| BLOCK ADDRESS CONVENTION        |   |   | _ | _ |   |   |   | _ |   | _ |     |   |   |   |   |   | _ |   |   |   |     | 138                                     |

| SEGMENTATION REGISTERS          |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| SEGMENTATION REGISTER SELECTION | N |   |   | · |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     | 139                                     |

| FUNCTION OF THE CONTROL FIELD . |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |     |                                         |

| INTERRUPTS                      |   |   |   |   |   |   |   |   |   |   |     |   | _ |   |   |   |   |   | _ |   |     | 141                                     |

# ILLUSTRATIONS

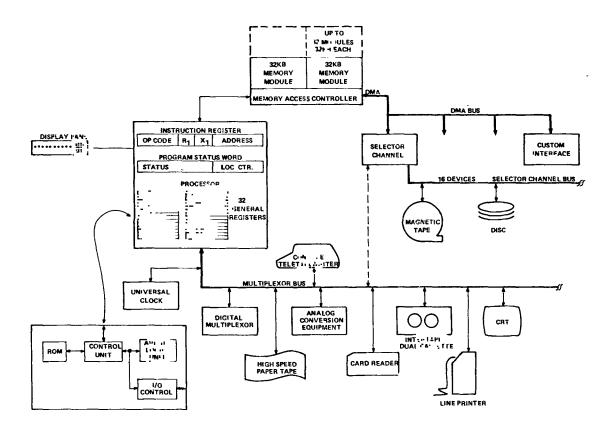

| Figure 1.  | System Diagram               |  |  |  |  |  |  |  |  |  |  |  | , | 1 |

|------------|------------------------------|--|--|--|--|--|--|--|--|--|--|--|---|---|

| Figure 2.  | Program Status Word .        |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 3.  | Instruction Formats .        |  |  |  |  |  |  |  |  |  |  |  |   |   |

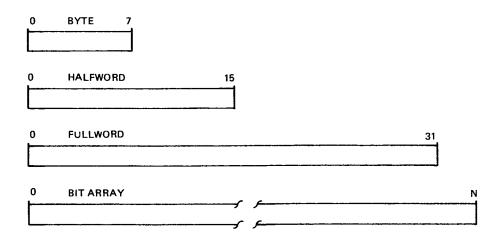

| Figure 4.  | Logical Data                 |  |  |  |  |  |  |  |  |  |  |  |   |   |

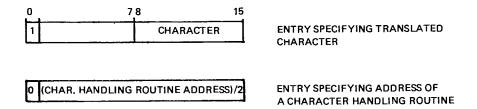

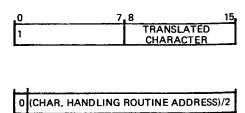

| Figure 5.  | Translation Table Entry      |  |  |  |  |  |  |  |  |  |  |  |   |   |

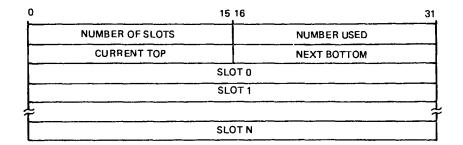

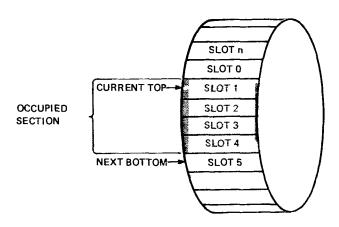

| Figure 6.  | Circular List Definition     |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 7.  | Circular List                |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 8.  | Fixed Point Data Words F     |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 9.  | Floating Point Data Form     |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 10. | Program Status Word .        |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 11. | <b>Channel Command Block</b> |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 12. | <b>Channel Command Word</b>  |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 13. | Program Address              |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 14. | Real Address                 |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 15. | Segmentation Registers       |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 16. | Program Addresses            |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 17. | Limit and Relocation Fiel    |  |  |  |  |  |  |  |  |  |  |  |   |   |

| Figure 18. | Segment Control Fields       |  |  |  |  |  |  |  |  |  |  |  |   |   |

|            |                              |  |  |  |  |  |  |  |  |  |  |  |   |   |

# **APPENDICIES**

| APPENDIX 1 | INDEX                              | , A1-1/A1-8 |

|------------|------------------------------------|-------------|

| APPENDIX 2 | INSTRUCTION SUMMARY - ALPHABETICAL | A2-1/A2-4   |

|            | INSTRUCTION SUMMARY - NUMERICAL    |             |

| APPENDIX 4 | EXTENDED BRANCH MNEMONICS          | A4-1/A4-2   |

|            | ARITHMETIC REFERENCES              | A5-1/A5-4   |

# CHAPTER 1 SYSTEM DESCRIPTION

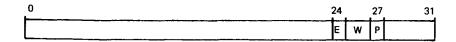

Aware of the growing need for minicomputers with improved performance and increased memory capacity, INTERDATA has combined the field proven and a reliable technologies used in the Models 70, 74, and 80 with its traditional concern for programming simplicity and economy to produce the extended series architecture. This new architecture is a logical step in the evolution of the INTER-DATA family of minicomputers. Through the use of 32 bit general registers and revised instruction formats, it provides fullword data processing power and direct memory addressing up to a limit of 16 million bytes. Figure 1 shows the interrelationship of the various elements contained in this advanced system.

#### **MEMORY SYSTEM**

The basic system contains 32KB of memory. Memory may be expanded in either 16KB or 32KB increments up to the maximum allowed. Storage addressing is consecutive, starting at zero, for each eight hit byte. Memories may be set to maintain odd parity on the halfword level, one parity bit for each 16 data bits.

Figure 1. System Diagram

#### **Direct Memory Access**

Direct Memory Access devices may be added to the system. Direct Memory Access devices allow the operation of high speed peripherals (e.g., discs or drums), directly to or from memory. This enables the user to perform simultaneous processing together with the high speed data transfer. The DMA port uses a memory cycle stealing technique.

#### Selector Channel

The Selector Channel is a standard Direct Memory Access device that allows the connection of high speed peripheral devices directly to memory. To use the Selector Channel, the program initializes the device itself, sends a start and a final memory address to the Selector Channel, and commands the channel to start. The Processor, at this point, can proceed to another function. When the Selector Channel terminates the transfer, it generates a hardware interrupt to the Processor.

#### Relocation and Protection

The memory access and protect controller provides hardware relocation, segmentation, and protection of programs. Programs may be divided up into as many as 16 segments. Segments may be located anywhere in available memory. The memory access and protect controller provides direct address translation, that is, program addresses are automatically converted into real memory addresses.

The memory access and protect controller provides protection in two ways. First, it isolates the currently running program from all others in the system. The currently running program cannot reference, for any reason, memory locations outside its preassigned areas. Second, within its assigned areas, the program may be prevented from executing instructions or writing into memory.

# MULTIPLEXOR INPUT/OUTPUT BUS

All medium and low speed devices connect to the Multiplexor Bus. This is a request/response bus, consisting of 30 lines: 16 bidirectional data lines, 8 control lines, 5 test lines, and 1 initialize line. Interrupt detection and automatic hardware vectoring for each of 1,023 devices are standard.

#### **PERIPHERALS**

A complete line of standard, off-the-shelf, peripheral devices is available with the system. All system modules and device controllers previously designed for other INTERDATA Processors are plug compatible with the Multiplexor Bus. These field-proven designs enable the user to select the devices or modules required for his specific application. The following are examples of what is available.

#### **Digital Multiplexor**

The digital multiplexor provides an economical set of modular blocks to monitor or control digital lines. A single controller, augmented with input and output modules of 128 lines each, provides the capability for monitoring 2,048 inputs and controlling 2,048 outputs. The digital multiplexor uses a biased core technique for input sampling. This technique insures absolute DC isolation from the sense contact, excellent common mode transient response and DC offset capability, which make the digital multiplexor particularly well suited for reliable use in noise contaminated environments.

#### Intertape Cassette System

The Intertape cassette system provides dual drive transports, capable of transferring data at a rate of 1,000 characters per second. This reliable and inexpensive unit makes an ideal substitute for paper tape equipment. With a storage capacity of 500,000 bytes per cassette, hardware read-after-write check, and longitudinal redundancy check, the Intertape cassette system is ideal for low speed auxiliary storage.

#### **Industry Compatible Magnetic Tape Systems**

Nine track, industry compatible magnetic tape systems are available in both 800 and 1,600 bits per inch (bpi) densities. These units operate at 45 inches per second (ips). The 800 bpi unit includes hardware read-after-write and cyclic redundancy checking hardware. The 1,600 bpi version includes read-after-write check and phase encoded formatter. Transfer rate for the 800 bpi version is 36,000 characters per second. Transfer rate for the 1,600 bpi version is 72,000 characters per second.

#### Removable Cartridge Disc System

The removable cartridge disc system is a reliable and inexpensive mass storage system, capable of providing 2.5 or 5.0 megabytes of storage per unit. Up to four disc drivers can operate on each controller, providing a maximum storage capacity of 20.0 megabytes per system. Average access time is 70 milliseconds and the transfer rate is 180,000 bytes per second.

#### Alphanumeric Display Terminals

Several types of alphanumeric display terminals are available. Display units provide a 1,920 character display (24 lines x 80 characters), standard 64 character ASCII subset, complete Processor and operator cursor control, and a full range of editing features with both message and character modes. Units operate at 110 to 9,600 baud.

#### **Data Communications Equipment**

A complete line of character buffered adapters is available to service Bell 103, 201, 202, and 301 data sets, as well as the 801 automatic dialer. This enables the Processor to accommodate applications requiring either synchronous or asynchronous communications.

#### High Speed Paper Tape System

The high speed paper tape system provides a 300 character per second reader and a 75 character per second punch. These units can be provided individually, or as a combined package using the same controller.

#### System Modules

A complete line of system modules provides the user with a simple and convenient means of creating special interfaces. These general purpose interface modules greatly reduce or eliminate special design effort. Standard modules are available to handle 8 bit or 16 bit parallel input or output, manual data entry, and decimal indicators.

#### **PROCESSOR**

The Central Processing Unit (CPU), or Processor, controls activities in the system. It executes instructions in a specific sequence and performs arithmetic and logical functions. Included in the Processor's components are:

Program Status Word register General registers Floating point registers Hardware multiply and divide Floating point hardware

#### **Program Status Word**

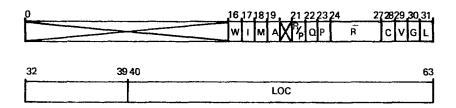

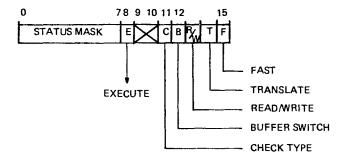

The 64 bit Program Status Word (PSW), shown below, defines the state of the Processor at any given time.

Figure 2. Program Status Word

Bits 0:31 are reserved for status information and interrupt masks. Bits 40:63 contain the Location Counter. Unassigned Program Status Word bits must not be used and must always be zero. Status information and interrupt mask bits are defined as follows:

| Bit 16     | Wait state                           |

|------------|--------------------------------------|

| Bit 17     | Immediate interrupt mask             |

| Bit 18     | Machine malfunction interrupt mask   |

| Bit 19     | Arithmetic fault interrupt mask      |

| Bit 21     | Relocation/protection interrupt mask |

| Bit 22     | System queue service interrupt mask  |

| Bit 23     | Protect mode                         |

| Bits 24:27 | Register set select bits             |

| Bits 28:31 | Condition Code                       |

#### Wait State

When this bit is set, the Processor halts normal program execution. It is still responsive to machine malfunction and immediate interrupts, if enabled.

# Immediate Interrupt Mask

This bit controls requests for service from devices on the Multiplexor Bus, including the Selector Channel. If this bit is set, the Processor responds to the requests. If it is reset, the requests are queued. This bit also controls the Auto Driver Channel.

#### Machine Malfunction Interrupt Mask

This bit controls interrupts generated when power fails, when power returns, and when parity checking indicates a memory parity error.

#### **Arithmatic Fault Interrupt Mask**

This bit controls internal interrupts caused by arithmetic faults -- fixed-point quotient overflow, floating point overflow or underflow. If it is set, the interrupt is taken. If it is reset, the error condition is ignored.

#### Relocation Protection Interrupt Mask

This bit serves two purposes. It enables the memory access and protect controller so that program addresses are automatically relocated. It also enables the relocation/protection interrupt, which is generated by the memory access and protect controller.

#### System Queue Service Interrupt Mask

This bit controls the interrupt generated when the system queue requires service.

#### Protect Mode

This bit describes an operational state of the Processor. If it is set, the Processor is in the protect mode, and only non-privileged instructions may be executed. If this bit is reset, the Processor is in the Supervisor mode, and the currently running program may execute any legal instruction.

#### Register Set Select

Bits 24:27 of the Program Status Word are used to designate the current register set. All 32 bit series machines must have at least two register sets. Register sets are numbered 0 through 15. If fewer than 16 sets are implemented, the last set is always numbered 15.

#### **Condition Code**

Bits 28:31 of the Program Status Word contain the Condition Code. As part of the execution of certain instructions, the state of the Condition Code may be changed. The state of the Condition Code following these instructions indicates the nature of the result. Not all instructions affect the Condition Code. The state of the Condition Code may be tested with Conditional Branch instructions.

#### Location Counter

The Location Counter controls the sequencing of instruction execution. In normal sequential operation, the Location Counter contains the address of the next instruction to be executed. The instruction is fetched from memory. While the instruction is being executed, the Location Counter is incremented by either two, or four, or six, depending on the length of the instruction. Upon completion of instruction execution, the next instruction is fetched from the location specified by the incremented Location Counter, and the process is repeated.

This sequential mode of operation is altered by Branch instructions and by interrupts. Branch instructions cause the Location Counter to be replaced by a new value derived from the instruction. Interrupts cause the entire Program Status Word to be replaced by a new Program Status Word.

#### General Registers

In the current implementation, there are two sets of general registers. Each set contains 16 registers. Each register is 32 bits wide. The sets are numbered 0 and 15. Register set selection is determined by the state of Bits 24:27 of the current Program Status Word. Registers 1 through 15 of either set may be used as index registers.

When interrupts occur, the Processor loads pertinent information into preselected registers of register set 0, the supervisor set. The details of this operation are described in Chapter 6. Register set 15, the user set, does not have any specific functional assignments.

#### Floating Point Registers

There are eight floating point registers, each 32 bits wide. The registers are identified by the even numbers, 0 through 14. Floating point operations must always identify the registers with even numbers. The results are undefined if odd numbers are used.

#### **Processor Interrupts**

Interrupt conditions cause the entire Program Status Word to be replaced by a new Program Status Word, thus breaking the usual sequential flow of instruction execution. When an interrupt condition arises, the Processor saves its current Program Status Word either in memory or in a pair of general registers belonging to register set 0. It loads information related to the interrupt condition in other registers of set 0. It loads a new Program Status Word from a memory location reserved for the specific interrupt condition. (The immediate interrupt is an exception to the rule. The status portion of the new Program Status Word, Bits 0:31, is forced to a preset value. The Location Counter is loaded from a memory location reserved for the interrupting device.) Refer to Chapter 6 for details on interrupt processing.

#### **Reserved Memory Locations**

The following memory locations are reserved for interrupt pointers, Program Status Words, and system constants.

| <u>L</u>   | ocatio | <u>n</u>  | <u>Use</u>                                      |

|------------|--------|-----------|-------------------------------------------------|

| X'000000'  | _      | X'00001F' | Reserved                                        |

| X'000020'  | -      | X'000027' | Machine malfunction interrupt old PSW           |

| X'000028'  | -      | X'00002F' | Not used, must be zero                          |

| X'000030'  | -      | X'000037' | Illegal instruction interrupt new PSW           |

| X'000038'  | -      | X'00003F' | Machine malfunction interrupt new PSW           |

| X'000040'  | -      | X'000047' | Not used, must be zero                          |

| X'000048'  | -      | X'00004F' | Arithmetic fault interrupt new PSW              |

| X'000050'  | -      | X'00007F' | Bootstrap loader and device definition table    |

| X'000080'  | -      | X'000083' | System queue pointer                            |

| X'000084'  | -      | X'000085' | Current PSW save pointer                        |

| X'000086'  | -      | X'000087' | Register save pointer                           |

| X'000088'  | -      | X'00008F' | System queue service interrupt new PSW          |

| X'000090'  | -      | X'000097' | Relocation/protection interrupt new PSW         |

| X'000098'  | -      | X'00009B' | Supervisor call new status                      |

| X'00009C'  | -      | X'0000BB' | Supervisor call interrupt new location counters |

| *X'0000BC' | -      | X'0000CF' | Not used, must be zero                          |

| X'0000D0'  | -      | X'0002CF' | Interrupt service pointer table                 |

| X'0002D0'  | -      | X'0004CF' | Expanded interrupt service pointer table        |

| X'0004D0'  | -      | X'0008CF' | Expanded interrupt service pointer table        |

<sup>\*</sup>Used by Micro-Program

These reserved locations play an important role in both interrupt and input/output processing. For details on these subjects refer to Chapters 6 and 7. In addition to the above, certain locations are reserved for use by the Memory Access Controller. Refer to Chapter 8 for details.

#### Processor Operations

Fixed point arithmetic and logical operation are performed between:

The contents of two fullword registers.

The contents of a fullword register and the contents of a fullword located in memory.

The contents of a fullword register and the contents of a halfword located in memory.

Where the second operand is contained in memory, it may be located in the instruction stream (immediate operation), or it may be located in indexed storage.

In fixed point arithmetic and logical operations between a fullword register and a halfword operand in memory, the halfword operand is expanded to a fullword by propagating the most significant bit into the high order bits before the operation is started. This permits the use of halfword to fullword operations with consistent results, and it provides for space economy in that small values do not have to be contained in fullword locations.

Arithmetic operations on fixed point halfword quantities may produce results that are not entirely consistent with the results that would be obtained in a 16 bit Processor. Where this is a problem, the convert to halfword value instruction adjusts both the result and the Condition Code so that they are correct and consistent with the same operations in a 16 bit Processor.

Floating point operations take place between the contents of two floating point registers, or between the contents of a floating point register and a floating point operand contained in a full-word in memory. Following floating point operations, the Condition Code is set to indicate the nature of the result.

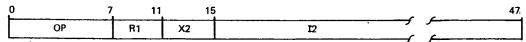

#### **DATA FORMATS**

The Processor performs logical and arithmetic operations on single bits, 8 bit bytes, 16 bit half-words, 32 bit fullwords, and 64 bit double words. This data may represent a fixed point number, a floating point number, or logical information.

#### **Fixed Point Data**

Fixed point arithmetic operands are either 16 bit halfwords or 32 bit fullwords. In multiply and divide operations, 64 bit operands are manipulated. Fixed point data is treated as 15 bit signed integers in the halfword format, and as 31 bit signed integers in the fullword format. Positive numbers are expressed in true binary form with a Sign bit of zero. Negative numbers are represented in two's complement form with a Sign bit of one. The numerical value of zero is represented with all bits zero. Refer to Chapter 4 for details on fixed point data representation.

#### Floating Point Data

A floating point number consists of a signed exponent and a signed fraction. The quantity expressed by this number is the product of the fraction and the number 16 raised to the power of the exponent. Each floating point value requires a 32 bit fullword, of which eight bits are used for the sign and exponent, and 24 bits are used for the fraction. Refer to Chapter 5 for details on floating point data representation.

#### Logical Data

Logical operations manipulate 8 bit bytes, 16 bit halfwords, and 32 bit fullwords. In addition, it is possible to perform logical operations on single bits located in bit arrays. Refer to Chapter 2 for details on logical data representation.

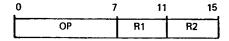

#### **INSTRUCTION FORMATS**

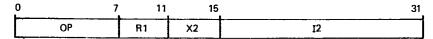

The INTERDATA instruction formats provide a concise method of representing required operations for easy interpretation by the Processor. There are seven basic formats, shown in Figure 3. The abbreviations used in the figure have the following meanings:

| OP        | Operation code                       |

|-----------|--------------------------------------|

| R1        | First operand register               |

| R2        | Second operand register              |

| N         | A four bit immediate value           |

| <b>X2</b> | Second operand single index register |

| D2        | Second operand displacement          |

| FX2       | Second operand first index register  |

| SX2       | Second operand second index register |

| A2        | Second operand direct address        |

| <b>I2</b> | Second operand immediate value       |

|           |                                      |

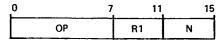

# REGISTER TO REGISTER (RR)

#### SHORT FORMAT (SF)

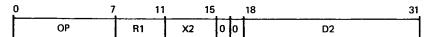

#### **REGISTER AND INDEXED STORAGE 1 (RX1)**

# REGISTER AND INDEXED STORAGE 2 (RX2)

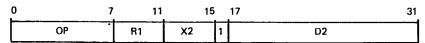

# **REGISTER AND INDEXED STORAGE 3 (RX3)**

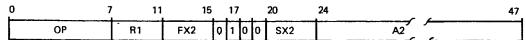

#### REGISTER AND IMMEDIATE STORAGE (RI1)

# REGISTER AND IMMEDIATE STORAGE (RI2)

Figure 3. Instruction Formats

Most instructions in the extended series may be expressed in two or more formats, which provides flexibility in data organization and instruction sequencing.

In the examples accompanying each format description, it is assumed that proper values have been assigned to the symbols used in the assembler representation. Register specifications in these examples are expressed as absolute numbers to show the correspondence between the machine code format and the assembler notation. In actual practice, these numbers could be expressed symbolically.

#### Register to Register (RR) Format

In this 16 bit format, Bits 0:7 contain the operation code. Bits 8:11 contain the R1 field, and Bits 12:15 contain the R2 field. In most RR instructions, the register specified by R1 contains the first operand, and the register specified by R2 contains the second operand. For example:

Assembler Notation Machine Code AR 1, 2 0A12

instructs the Processor to add the contents of Register 1 to the contents of Register 2, and store the result in Register 1.

#### Short Form (SF) Format

This 16 bit format provides space economy when working with small values. Bits 0:7 contain the operation code. Bits 8:11 contain the R1 field. Bits 12:15 contain the N field. In arithmetic and logical operations, the register specified by R1 contains the first operand. The N field contains a four bit immediate value used as the second operand. For example:

Assembler Notation Machine Code SIS 1, 10 271A

instructs the Processor to subtract the quantity 10 from the contents of Register 1, and store the result in Register 1.

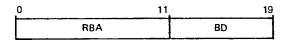

### Register and Indexed Storage One (RX1) Format

This is a 32 bit format in which Bits 0:7 contain the operation code, Bits 8:11 contain the R1 field Bits 12:15 contain the X2 field, Bits 16 and 17 must be zero, and Bits 18:31 contain the D2 field. In general, the register specified by R1 contains the first operand. The second operand is located in memory at the address obtained by adding the contents of the second operand index register, specified by X2, to the 14 bit displacement contained in the D2 field. The displacement is always positive. For example:

Assembler Notation Machine Code S 2, D2(3) 5B233400

instructs the Processor to subtract the fullword contents of the memory location, whose address is obtained by adding X'3400' to the contents of index Register 3, from the contents of Register 2. The result replaces the contents of Register 2.

#### Register and Indexed Storage Two (RX2) Format

This format provides relative addressing capability in a 32 bit instruction word. Bits 0:7 contain the operation code. Bits 8:11 contain the R1 specification. Bits 12:15 contain the X2 specification. Bit 16 must always be one. Bits 17:31 contain the relative displacement, D2.

In this format, the register specified by R1 contains the first operand. The second operand is located in memory at the address obtained by adding to the incremented Location Counter the sum of the contents of the index register specified by X2 and the contents of the D2 field. The D2 field may contain either a positive or a negative number. Negative numbers are expressed in two's complement notation. For example:

Assembler Notation A 6, D2 (4)

Machine Code 5A648040

instructs the Processor to add to the contents of Register 6 the fullword quantity found in memory at the address obtained by adding to the incremented Location Counter the sum of X'0040' and the contents of the index register, Register 4. The result replaces the contents of Register 6.

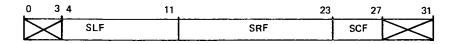

#### Register and Indexed Storage Three (RX3) Format

This is a 48 bit format in which double indexing is permitted. Bits 0:7 contain the operation code. Bits 8:11 contain the R1 specification. Bits 12:15 contain the first index specification, FX2. Bit 16 must be zero. Bit 17 must be one. Bits 18:19 must be zero. Bits 20:23 contain the second index specification, SX2. Bits 24:47 contain a 24 bit address, A2.

In general, the first operand is contained in the register specified by R1. The second operand is located in memory. Its memory address is obtained by adding the contents of the first index register to the contents of the second index register, and then adding this result of the contents of the A2 field. For example:

Assembler Notation S 7, A2 (9, 4) Machine Code 5B7944000420

instructs the Processor to subtract from the contents of Register 7 the fullword quantity located in memory at the address obtained by adding the contents of the first index register, Register 9, to the contents of the second index register, Register 4, and then adding this result to the address quantity, X'000420'. The result of the operation replaces the contents of Register 7.

NOTE

Second level indexing is allowed only if first level indexing is also specified.

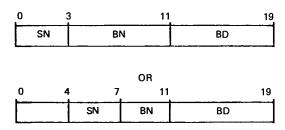

#### Register and Immediate Storage One (RI1) Format

This format represents a 32 bit instruction word. Bits 0:7 contain the operation code. Bits 8:11 contain the R1 specification. Bits 16:31 contain the 16 bit immediate value, I2.

In this format, the register specified by R1 contains the first operand. The second operand is obtained by adding the contents of the index register specified by X2 to the value contained in the I2 field. Before adding the immediate value to the contents of the index register, the 16 bit immediate value is expanded to a 32 bit fullword quantity by propagating the most significant bit through the high order bits. For example:

Assembler Notation Machine Code

AHI 4,12 (2) CA423444

instructs the Processor to add to the contents of Register 4 the quantity obtained by adding X'00003444' to the contents of Register 2. The result replaces the contents of Register 4.

#### Register and Immediate Storage Two (RI2) Format

This is a 48 bit instruction format. Bits 0:7 contain the operation code. Bits 8:11 contain the R1 specification. Bits 12:15 contain the X2 specification. Bits 16:47 contain the 32 bit immediate value, I2.

The first operand is contained in the register specified by R1. The second operand is obtained by adding the contents of the index register, specified by X2, to the 32 bit immediate value contained in the 12 field. For example:

Assembler Notation Machine Code

AI 3,I2 (2) FA3224647318

instructs the Processor to add to the contents of Register 3 the value obtained by adding Y'24647318' to the contents of Register 2. The result replaces the contents of Register 3.

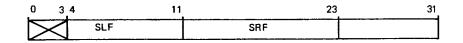

#### **Branch Instruction Formats**

The Branch instructions use the RR, SF, and all variations on the RX formats. However, in the Conditional Branch instructions, the R1 field does not specify a register. Instead, it contains a mask value (labeled M1 in the instruction descriptions), which is tested with the Condition Code.

#### **Programming Note**