# SYSTEM BUS (S-BUS)

Theory of Operation Manual

63-002 R00

The hardware description in this document is intended solely for use in assisting with the operation, installation, maintenance, or repair of Concurrent Computer Corporation equipment. The information in this document is subject to change without notice and should not be construed as a commitment by Concurrent Computer Corporation. Concurrent Computer Corporation assumes no responsibility for any errors that may appear in this document. Use of this document for all other purposes, without prior written approval from Concurrent Computer Corporation is prohibited.

This documentation is furnished under a license, and it can be used or copied only in a manner permitted by that license. Any copy of the described documentation must include any copyright notice, trademarks, or other legends or credits of Concurrent Computer Corporation and/or its suppliers. Title to and ownership of the described documentation and any copies thereof shall remain in Concurrent Computer Corporation and/or its suppliers.

The licensed materials described herein may contain certain encryptions or other devices which may prevent or detect unauthorized use of the licensed materials.

Any approved copy of this manual must include the Concurrent Computer Corporation copyright notice.

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

© 1987 Concurrent Computer Corporation — All Rights Reserved

Concurrent Computer Corporation, 2 Crescent Place

Oceanport, New Jersey 07757

Printed in the United States of America

#### NOTICE

Before tracing signals, the technician should take the following into consideration.

On each sheet in a Functional Schematic set, signals are represented by mnemonics composed of capital letters and numbers. At the end of each signal mnemonic, either a one/zero (1/0) or nothing/negative sign (/-) is used to designate the high or low active state of the signal, respectively. Therefore,

- a one (1) or nothing () indicates a high active state and,

- a zero (0) or negative sign (-) indicates a low active state.

For example:

High Active Low Active

# SYSTEM CLEAR (SCLR)

| One/Zero    | Nothing/Negative |

|-------------|------------------|

| Designation | Designation      |

| SCLR1       | SCLR             |

| SCLR0       | SCLR-            |

Both are correct, but only one type of designation (either 1/0 or nothing/-) may appear on the sheets in a Functional Schematic set. The designations cannot be mixed within a Functional Schematic set. As systems documentation packages contain multiple Functional Schematic sets, it is probable that both types of designations will be present.

#### PREFACE

This manual describes the functional and operational capabilities of the system bus (S-bus). Chapter 1 presents an overview of the S-bus and the modules that comprise an S-bus system. Chapter 2 describes the conventions used in naming signal mnemonics and In addition, signal definitions are given. A structures. functional description of the S-bus is provided in Chapter Here, details on bus acquisition, clocks, the transmission protocol and the effects of the power clear signals are given. Chapter 4 discusses the various memory operations that are facilitated by the S-bus. Chapter 5 provides an account direct data transfers on the S-bus including interprocessor messages, broadcast interrupts and direct input/output (I/O). Chapter 6 discusses the electrical specifications of the S-bus. Signal types and clock distribution are also discussed. 7 provides the physical specification of the S-bus backpanel.

# TABLE OF CONTENTS

| PR | EFACE                                                                                     |                                                                                                                                                                                                                                                                                        | v                                                                                |

|----|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1  | INTRODU                                                                                   | CTION                                                                                                                                                                                                                                                                                  | 1-1                                                                              |

|    | 1.1<br>1.1.2<br>1.1.3<br>1.1.4<br>1.1.5<br>1.1.6<br>1.1.7                                 | DESCRIPTION Control/Diagnostic System (CDS) Synchronous Operation Modules Bus Transfers Parity Memory Operations Messages, Broadcasts and Direct Input/Output (I/O) on F-Path Series 3200 Input/Output (I/O) CACHE OPERATION Quadword Blocks Cache Consistency REFERENCE DOCUMENTATION | 1-1<br>1-2<br>1-3<br>1-4<br>1-4<br>1-5<br>1-5<br>1-5<br>1-5                      |

| 2  |                                                                                           | DEFINITIONS AND CODES                                                                                                                                                                                                                                                                  | 1-6<br>2-1                                                                       |

|    | 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4 | F-Path Function Codes                                                                                                                                                                                                                                                                  | 2-1<br>2-2<br>2-2<br>2-3<br>2-3<br>2-4<br>2-4<br>2-5<br>2-6<br>2-8               |

| 3  | FUNCTION                                                                                  | NAL DESCRIPTION                                                                                                                                                                                                                                                                        | 3-1                                                                              |

|    | 3.2.3.4<br>3.3<br>3.3.1.1<br>3.3.1.2<br>3.3.1.3<br>3.3.1.4                                | Reset Initialization on Power-On Operation Early Power-Fail (EPF) Warning BUS ACQUISITON AND PRIORITY Bus Request and Grant Bus KEEP Bus Request Pending                                                                                                                               | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-4<br>3-5<br>3-5<br>3-6<br>3-6 |

|   | 3.4<br>3.4.1<br>3.5<br>3.5.1                                                                                                                  | Bus Acquisition Signals UNIT IDENTIFICATION (ID) Multiple IDs Per Unit TRANSMISSION PROTOCOL Bus Acknowledge Bus Busy Acknowledge Holding the T-Path After Busy Bus Fault Acknowledge Parity Bits Bus Time-Out | 3-7<br>3-8<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10<br>3-11                                 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 4 | MEMORY O                                                                                                                                      | PERATIONS                                                                                                                                                                                                      | 4-1                                                                                      |

|   | 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>4.7.1<br>4.7.1                     | Preserving Memory Operation Sequence<br>Address Space<br>T-PATH AND F-PATH USAGE FOR MEMORY<br>MEMORY READ OPERATIONS                                                                                          | 4-1<br>4-1<br>4-2<br>4-2<br>4-2<br>4-2<br>4-3<br>4-5<br>4-6<br>4-7<br>4-7<br>4-8<br>4-10 |

| 5 | DIRECT I                                                                                                                                      | RANSFERS ON F-PATH                                                                                                                                                                                             | 5-1                                                                                      |

|   | 5.1<br>5.2<br>5.2.1<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.4<br>5.5<br>5.5.5<br>5.5.1<br>5.5.2<br>5.5.2<br>5.5.3<br>5.5.3.1<br>5.5.3 | Direct Memory Access (DMA) Bus Operations Direct Memory Interface (DMI) Virtual Address Translation (VAT)                                                                                                      | 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-6<br>5-8<br>5-9<br>5-10<br>5-11              |

|   | 551                                                                                                                                           | Attention Interrupt                                                                                                                                                                                            | 5-12                                                                                     |

| 6   | ELECTRIC                                                                  | AL SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                   | 6-1                                                                                             |

|-----|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|     | 6.1.4<br>6.1.5<br>6.2<br>6.2.1<br>6.2.2                                   | Tristate Bus Signals Bus Termination Open-Collector Bus Signals Power Clear Signals                                                                                                                                                                                                                                                                                                                                | 6-1<br>6-2<br>6-4<br>6-4<br>6-6<br>6-7<br>6-8<br>6-8<br>6-9                                     |

| 7   | MECHANIC                                                                  | AL SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                   | 7-1                                                                                             |

|     | 7.1                                                                       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                | 7-1                                                                                             |

| LIS | T OF FIGU                                                                 | RES                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                 |

| LIS | 4-4<br>5-1<br>5-2<br>5-3<br>6-1                                           | Conventions for Naming Data Structures Power Clear Signal Timing S-Bus Acquisition Logic Read Singleword (MR1) Read Quadword (MR4) Quadword Write (WR4) Special Memory Operations Message Sequence Broadcast Interrupt Direct I/O S-Bus Clock Distribution - Timing and Skew S-Bus Electrical Timing Pin-Outs for T-Path and F-Path                                                                                | 1-2<br>1-3<br>2-4<br>3-3<br>3-8<br>4-5<br>4-6<br>4-10<br>5-2<br>5-3<br>5-7<br>6-3<br>6-5<br>7-2 |

|     | 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2 | S-BUS FIELDS AND SIGNAL DEFINITIONS SIGNAL MNEMONIC CONVENTION TTL LEVELS T-PATH FUNCTION CODES F-PATH FUNCTION CODES SUMMARY OF F-PATH TRANSFERS FIRST AND LAST WORD CONTROL BYTES WRITTEN FOR SINGLE-WORD WRITE (MW1) BYTE AND HALFWORD OPERATIONS I/O SUBFUNCTIONS FOR IOR AND IOW OPERATIONS TO EVEN DMI ID I/O SUBFUNCTIONS FOR IOR AND IOW OPERATIONS TO ODD DMI ID BUS ENABLING AND DISABLING TIMING DELAYS | 2-1<br>2-3<br>2-3<br>2-6<br>2-7<br>2-9<br>4-8<br>4-8<br>4-9<br>5-9<br>5-11<br>6-8               |

| TNF | EΧ                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                    | IND-1                                                                                           |

# CHAPTER 1 INTRODUCTION

#### 1.1 DESCRIPTION

The system bus (S-bus) is a high-performance synchronous bus used in the 3280 System. It interconnects major system modules: processors, input/output (I/O) controllers and memories. The S-bus conveys messages between modules on two distinct 32-bit data paths: the To-path (T-path) transfers addresses and write data to memory; the From-path (F-path) transfers read data from memory. This path is also used for interprocessor messages, direct I/O and interrupts.

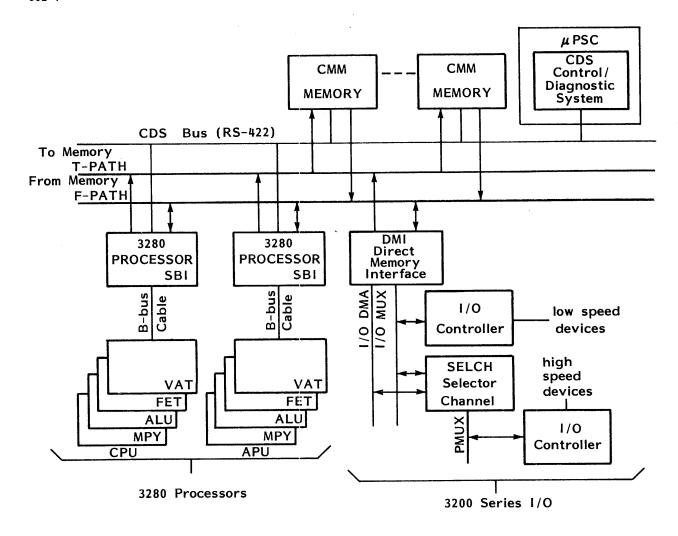

The two paths are electrically identical. Each path contains 50 data lines which are divided into four fields: 5-bit function, 8-bit identification (ID), 32-bit data and 5-bit parity. These four fields comprise a data item. The parity bits help assure system integrity. Each path also contains two acknowledge and six acquisition signals. The acknowledges indicate the receipt of each data item. The acquisition signals control when each unit can use the bus. Figure 1-1 shows the modules that are connected to the S-bus in a 3280 System.

# 1.1.1 Control/Diagnostic System (CDS)

The CDS is used to configure, initialize and monitor the operation of the computer system. The CDS consists of a network of microprocessors linked by a full-duplex serial bus called the level 1 link. Processor and memory modules contain one of these microprocessors. All are slaves on the CDS bus (level 1 link).

The master of the CDS bus is a microcomputer in the power supply. This microcomputer communicates to the system console. It controls the power supplies and the power clear signals. It assigns and records the configuration and error status of all modules.

Each microprocessor can identify itself based on codes included in its firmware. These codes identify the module, serial number, options and revisions. The microprocessor can identify its location by reading an 8-bit slot number which is encoded into the backplane wiring. The slot number includes the chassis number and the position within that chassis. The slot number is used as an ID for all communications on the CDS bus.

Figure 1-1 3280 System Block Diagram

# 1.1.2 Synchronous Operation

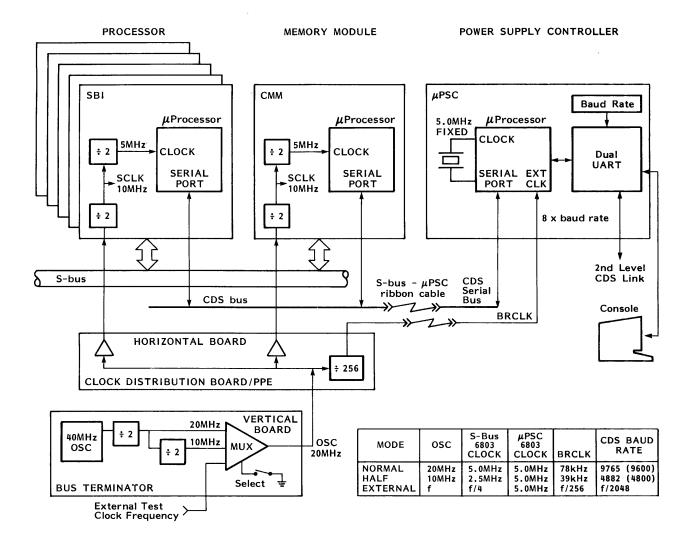

Bus operation is synchronous with the 10MHz system clock shown in Figure 1-2. This clock is derived from a 20MHz oscillator which is distributed to each board. Addresses and data are transferred from a master to a slave during one or more clock cycles. The master of each path has temporary control of that path. The next master is determined at the end of each operation. Bus acquisition circuitry allows positional priority, round-robin and high-priority access.

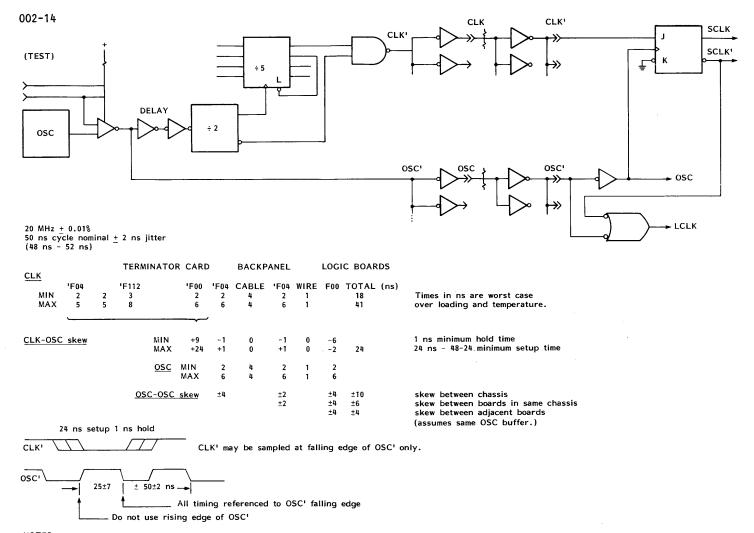

Figure 1-2 S-Bus and CDS Clock Distribution

#### 1.1.3 Modules

The S-bus connects modules to form a system. Each module performs a function required in a computer system. These modules are implemented on printed circuit boards which plug into an S-bus backplane. Modules will usually be on separate boards, but several functions may be combined. Similarly, a complex module may require several boards.

Three types of modules are used to describe operations on the S-bus. Memory modules are selected by memory address. The other modules are selected by unique unit IDs, which are assigned by the CDS.

- 1. Memory modules consist of an array of random access memory (RAM) circuits and a controller. The controller interfaces to the S-bus, controls the RAM array and buffers data. All operations to the memory module are via the S-bus. Memory modules are not considered units.

- 2. Processors are programmed units which access data stored in the memory modules. The processors use cache buffers to improve performance. Processors can communicate with each other and can send commands to I/O units.

- Special purpose processors, such as array or display processors, may also be connected to the S-bus. These units contain local memories which may be modified independently of the S-bus. They can be accessed directly via the S-bus, provided that they respond with 'do not cache' codes.

- 3. I/O units provide an interface between the S-bus and peripheral devices. These devices are used for secondary storage (i.e., disk and tape drives), communications and interaction with the user. I/O transfers may either be direct I/O controlled by a processor or direct memory access (DMA) controlled by the device.

#### 1.1.4 Bus Transfers

The module which has gained control of a path is called the master of that path. It can send a data item to another module, called the slave. On the T-path, any unit can be the master. The slave is a memory board; it is selected by the 32-bit memory address in the first word transferred. On the F-path, any module may be the master. The slave is a processor or direct memory interface (DMI); it is selected by the 8-bit bus ID.

Processors are identified by unit ID numbers. Each puts its ID on the T-path when it initiates a memory operation and recognizes its ID when it receives responses on the F-path.

# 1.1.5 Parity

All data transfers on T-path and F-path are protected using even parity. Five parity bits are used. TPAR4 and FPAR4 are parity on the function and ID fields; TPAR3:0 and FPAR3:0 are parity on the four data bytes.

Even parity means that the total number of 1-bits in the field, including the parity bit, is even. That is, if the field has an even number of ones, the parity bit is zero; otherwise, the parity bit is one. Parity is computed on logical values, not on the voltage levels on the bus; high signals are zero. When the bus is inactive (high), all bits are zero and the parity is even (correct).

#### 1.1.6 Memory Operations

Memory is referenced solely by memory address; memory modules do not have unit IDs. Although memory modules normally contain just memory, memory within other units can be accessed via the S-bus, if that unit responds to memory commands.

Units initiate memory operations on the T-path. The function specifies a memory operation. The data field contains a memory address. Each memory module recognizes the addresses it contains. For memory writes, subsequent cycles send data to be written. For memory reads, the addressed memory module performs the operation then returns data on the F-path. Special memory operations provide test-and-set operations used for software interlocks. These operations read a word and then immediately modify that word in main memory.

# 1.1.7 Messages, Broadcasts and Direct Input/Output (I/O) on F-Path

Processors can communicate directly using the F-path. Messages can be sent to interrupt another unit. Broadcast interrupts are received simultaneously by all processors; this provides a means for the operating system to preempt lower priority processes and to delete old virtual address translations (VATs). Direct I/O operations allow a processor to directly access an I/O device.

# 1.1.8 Series 3200 Input/Output (I/O)

The Series 3200 I/O subsystem is supported in S-bus systems using the DMI board. This board generates the Series 3200 I/O multiplexer (MUX) and DMA buses. The MUX bus communicates with an assigned processor using special codes on the S-bus. The DMA bus accesses memory using standard S-bus operations. The bus is limited to 24-bit addresses, but the DMI board can translate these to 32-bit addresses for use in extended memory systems.

#### 1.2 CACHE OPERATION

Processors use cache buffers to reduce memory operations. A cache is a small high-speed memory which is used to retain recently used data. This data is likely to be used again soon. When it is, the cache provides the data, thus avoiding the delay and contention of using main memory. Caches are a hardware feature; their operation is transparent to the running program.

#### 1.2.1 Quadword Blocks

Cache block size is a quadword. A quadword is a block of four consecutive words aligned on a quadword boundary (any multiple of 16 bytes). These blocks can be efficiently loaded using the quadword read (MR4) function. The desired (addressed) word is

transferred first. Larger blocks may be used, but the bus cannot transfer more than a quadword in a single operation.

# 1.2.2 Cache Consistency

Caches significantly improve speed and reduce contention for bus cycles. However, each processor must ensure that the data in its cache is current. To do so, it monitors the activity of other units on the T-path for memory writes and special memory operations. Whenever a write affects a block stored in the cache, that block must be invalidated. The cache contents cannot be updated from the data on the bus.

All S-bus operations which modify memory use at least two cycles on the T-path. Thus, two cycles are available for each address that needs to be checked.

The need to ensure that caches are kept current puts constraints on cache design of processors on the S-bus. Caches must use write through organization. That is, when a processor writes to memory, both that cache and main memory are updated immediately. Otherwise, other processors could not guarantee that their data was current.

New blocks may be added to a cache only by loading them with a quadword read (MR4). Existing cache blocks are updated by any memory write, but new blocks may not be created by a write even if a complete quadword is written.

#### 1.3 REFERENCE DOCUMENTATION

Additional documentation which describes other aspects of the 3280 System is available. Those manuals listed below provide either module-level theory or information on the 3280 System on a system level.

- 3280 System Control/Diagnostic System (CDS) Maintenance Manual

- 3280 System Operator Guide

- Model 34-043 Power Subsystem Theory of Operation Manual

- Composite Memory Module (CMM) Theory of Operation Manual

- Direct Memory Interface (DMI) Theory of Operation Manual

- 3280 System Central Processing Unit (CPU) Theory of Operation Manual

- 3280 System Installation and Configuration Manual

#### CHAPTER 2 SIGNAL DEFINITIONS AND CODES

#### 2.1 INTRODUCTION

To-path (T-path) and From-path (F-path) signals are identical. All T-path signals have T prefixes and all F-path signals have F prefixes. The clock and control signals serve both paths. The oscillator and clock signals are distributed radially. Separate buffers for OSC- exist on each slot. Buffers for CLK- are present on every three slots. Each slot has individual request and grant signals for each path. See Table 2-1 for a summary of the system bus (S-bus) signal lines and data fields.

TABLE 2-1 S-BUS FIELDS AND SIGNAL DEFINITIONS

| T-PATH<br>  SIGNALS                            | F-PATH<br>SIGNALS                                     | SIGNAL DEFINITION                                                                                                                                                                                                                       |

|------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                |                                                       | DATA FIELDS                                                                                                                                                                                                                             |

| T31:00-<br>TFN4:0-<br>TID7:0-                  | F31:00-<br>FFN4:0-<br>FID7:0-                         | 32-bit address/data field<br>5-bit function select<br>8-bit unit identification number                                                                                                                                                  |

|                                                | - then then the the than that plan day the day of     | PARITY BITS ON MESSAGE                                                                                                                                                                                                                  |

| TPAR4-<br>TPAR3-<br>TPAR2-<br>TPAR1-<br>TPAR0- | FPAR4-<br>FPAR3-<br>FPAR2-<br>FPAR1-<br>FPAR0-        | even parity bit for ID and FN fields even parity bit for data bits 31:24 even parity bit for data bits 23:16 even parity bit for data bits 15:08 even parity bit for data bits 07:00                                                    |

|                                                | RES                                                   | PONSES (FROM PATH RECEIVER)                                                                                                                                                                                                             |

| TAK1:0-                                        | FAK1:0-                                               | acknowledge: here, busy, fault                                                                                                                                                                                                          |

|                                                |                                                       | BUS ACQUISITION SIGNALS                                                                                                                                                                                                                 |

| TRQn- TGRn- TKEEP- TREQ- TRREQ- THREQ-         | FRQn-<br>FGRn-<br>FKEEP-<br>FREQ-<br>FRREQ-<br>FHREQ- | positional priority request (per slot)   positional priority grant (per slot)   keep bus for next cycle (open-collector)   request bus (open-collector)   round-robin request (open-collector)   high-priority request (open-collector) |

| H F-PATH<br>LS SIGNALS | SIGNAL DEFINITION                                                                                                              |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                        | CLOCKS                                                                                                                         |

|                        | 20.00MHz oscillator<br>2.000MHz clock<br>Twice line frequency                                                                  |

|                        | CONTROL                                                                                                                        |

|                        | Memory clear (sets memory nonvalid) Processor clear (forces processors into reset)                                             |

|                        | System clear (forces system into reset   state)                                                                                |

| : 0<br><u>'</u><br>'   | Slot ID number (for CDS address)  CDS serial line "To Power Supply Controller"  CDS serial line "From Power Supply Controller" |

|                        | LS SIGNALS                                                                                                                     |

#### 2.2 NOTATION

The following sections describe the conventions used to name signal mnemonics and data structures.

# 2.2.1 Mnemonic Naming Conventions

Signals are represented by mnemonics composed of capital letters and numbers. A signal is logic 1 (active) when the condition named by its mnemonic is true; otherwise, it is logic 0 (inactive). Postfix numbers identify individual signals within a field. A field is labelled with its bit range using a colon (:), for example, T31:00 represents T31 through T00 (32 signals). The most significant bit is listed first. A postfix minus indicates the complement of a signal, which is active when at logic low. Otherwise, the signal is assumed active when at logic high. The true definition of mnemonics is assumed in all circuit descriptions; the minus is used only when the polarity of the signal is significant. See Table 2-2 for additional information on signal mnemonics.

TABLE 2-2 SIGNAL MNEMONIC CONVENTION

|   |                                            | ~   |                |        |     |                |       |   |

|---|--------------------------------------------|-----|----------------|--------|-----|----------------|-------|---|

|   | LOGIC                                      | 1   | TRUE           | SIGNAL | 1   | COMPLI         | EMENT | ! |

| ľ |                                            | ==: |                | ====== | ==: | ======         | -==== | 1 |

|   | Signal active 'l'<br>  Signal inactive '0' |     | Logic<br>Logic |        |     | Logic<br>Logic |       |   |

|   |                                            |     |                |        |     |                |       |   |

Signal voltages are assigned transistor-to-transistor logic (TTL) levels as shown in Table 2-3.

TABLE 2-3 TTL LEVELS

|   |       |       |      |     |         |       |     |       | - |

|---|-------|-------|------|-----|---------|-------|-----|-------|---|

| 1 | LOG   | IC    |      |     | VOLTAGE | LEVEI | S   |       |   |

| Ì |       | ===== | ==== |     |         |       | === |       | = |

| İ | Logic | low   | 1    | Low | voltage | (0.0V | to  | (V8.0 | 1 |

|   |       |       |      |     | voltage |       |     |       | I |

|   |       |       |      |     |         |       |     |       | - |

# 2.2.2 Logic Equations and Tables

The operation of circuitry is described in equations and tables. In these, the mnemonics indicate the true meaning of the signal. The logic polarity of the actual signal is ignored. Instead, the postfix minus sign is used to indicate the logical complement.

|   |   | Complement<br>SIG- |  |            |  |

|---|---|--------------------|--|------------|--|

| 0 | 1 | 1                  |  | complement |  |

# 2.2.3 Data Words, Halfwords, Bytes

A word is 32 bits wide; a halfword is 16 bits wide; a byte is 8 bits wide. Binary values are represented in hexadecimal (hex) notation; each 4-bit nibble has a value of 0 to 15. The values 10 through 15 are represented by characters A through F respectively.

#### 2.2.4 Power-of-Two Notation and Memory Addressing

Power-of-two notation is used to number bits within a field. Bits T31, TFN4, TID7, etc., are the most significant bits; bit 0 is the least significant. The weight of each bit 'n' equals two raised to the power 'n'. Therefore, bits 0, 1, 2, 3 through 'n' have weights 1, 2, 4, 8 through  $2^n$ .

To maintain functional compatibility with earlier machines, memory bytes and halfwords are numbered left to right. Byte 0 is the most significant and byte 3 is the least significant. Similarly, halfword 0 is the most significant and halfword 1 is the least significant. See the following table and Figure 2-1 for a graphic representation of these data structures.

| Bytes (8 bits)                               |     |     | Halfwords (16 bits)          |

|----------------------------------------------|-----|-----|------------------------------|

| Byte 0 = bits 31:24<br>  Byte 1 = bits 23:16 | H   | W O | = bits 31:16 (bytes 0 and 1) |

|                                              | i H | W 1 | = bits 15:00 (bytes 2 and 3) |

|                                              |     |     |                              |

002-3

| BITS      | 31 24 | 23 16 | 15 08 | 07 00 |

|-----------|-------|-------|-------|-------|

| BYTES     | 0     | 1     | 2     | 3     |

| HALFWORDS |       | 0     |       | 1     |

|           | MS    |       |       | LS    |

Figure 2-1 Conventions for Naming Data Structures

#### 2.3 FUNCTION CODES (FN)

On each path, the 5-bit function code specifies the type of data that is on the path during each cycle. For memory write, I/O write and messages, the data cycle(s) immediately follows the address cycle. Other data cycles (memory read, I/O read) are separate.

Function 0 specifies an idle cycle during which there is no transfer. The other fields, including parity, are ignored. The master must drive the function code to zero during idle cycles; the other fields need not be driven.

#### 2.3.1 T-Path Function Codes

The T-path is used solely to initiate memory operations. Each T-path operation begins with an address cycle and with TFN4 set. TFN4 is zero for data and idle cycles.

The four memory read functions cause the memory module to read one to four words from the same quadword. This data is returned to the requesting unit via the F-path. The contents of memory are not modified.

The four memory write functions modify one to four words within a quadword in a memory module. The first and last words may be written partially, where only selected bytes are modified. This facilitates writing byte strings into memory. When the entire word is written, the memory module computes an error check and correction (ECC) code and writes into its array. When only part of a word is written, the module must first read and check the previous contents of that word and then calculate a new ECC on the changed data. There is no response on the F-path.

The six special memory functions perform read-modify-write operations as an indivisible sequence. These operations are useful for coordinating tasks in a multiprocessor system. Special functions operate as a combination of memory read and memory writes: one data word must follow each address, the previous contents of the addressed word are returned on the F-path.

The four data functions accompany the data items following memory write or special memory functions. The code identifies the last (least significant) byte which is to be modified. DW3 must be used when the entire word is written and for all special functions. See Table 2-4 for the T-path function codes.

TABLE 2-4 T-PATH FUNCTION CODES

| HEX                           | TFN4:0                                            | MNEMONIC                        | OPERATION                                                                                                                                                                    |                                             |

|-------------------------------|---------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 00 01-03                      | 00000<br>                                         | IDL                             | Idle bus cycle<br>  Reserved                                                                                                                                                 | <br>                                        |

| 04<br>05<br>06<br>07<br>08-0F | 00100<br>00101<br>00110<br>00111                  | DW0<br>DW1<br>DW2<br>DW3        | Data word, end at byte 0 Data word, end at byte 1 Data word, end at byte 2 Data word, end at byte 3 Reserved                                                                 | D  <br>  A  <br>  T  <br>  A                |

| 10<br>11<br>12<br>13          | 10000<br>  10001<br>  10010<br>  10011            | MR1<br>MR2<br>MR3<br>MR4        | Memory Read: 1 word<br>  Memory Read: 2 words<br>  Memory Read: 3 words<br>  Memory Read: 4 words                                                                            | R  <br>  E  <br>  A                         |

| 14<br>  15<br>  16<br>  17    | 10100<br>  10101<br>  10110<br>  10111            | MW1<br>MW2<br>MW3<br>MW4        | Memory Write: 1 word<br>Memory Write: 2 words<br>Memory Write: 3 words<br>Memory Write: 4 words                                                                              | W  <br>  R  <br>  I  <br>  T                |

| 18<br>19<br>1A<br>1B<br>1C    | 11000<br>  11001<br>  11010<br>  11011<br>  11100 | MRS<br>MRR<br>MRI<br>MRD<br>MRW | Memory Read and Set Memory Read and Reset Memory Read and Increment Memory Read and Decrement Memory Read and Write word (Exchange word with memory) Memory Write Diagnostic | <br>  S  <br>  P  <br>  E  <br>  C  <br>  I |

| 1E<br>  1F                    |                                                   |                                 | Reserved<br>Reserved                                                                                                                                                         | L                                           |

#### 2.3.2 F-Path Function Codes

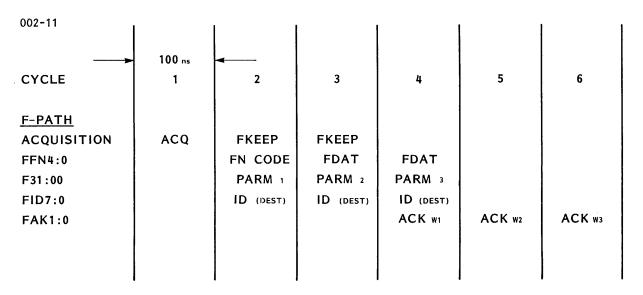

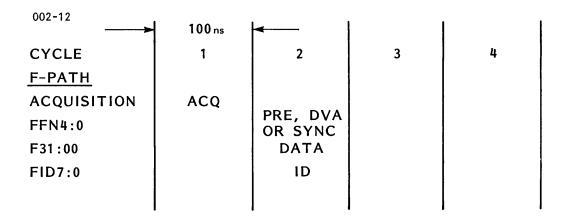

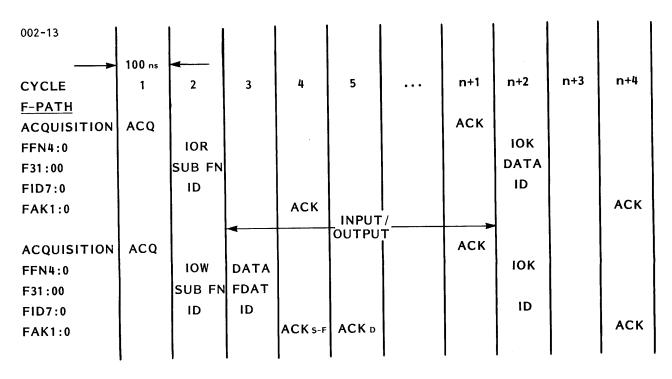

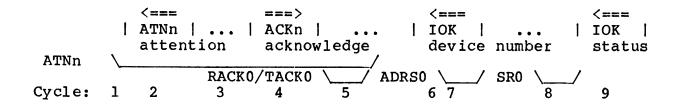

The F-path is used for memory read data, direct I/O, broadcast interrupts and messages between units. The four broadcast functions are received and decoded by all units. Memory read data, direct I/O and the four message functions are decoded only by the unit addressed by FID7:0.

IOW and FDAT must be sent as a pair of consecutive items; each MSGn must be followed consecutively by two FDAT items. The other transfers may be sent singly. Compatible I/O and messages use subfunction commands on F31:28. See Table 2-5 for the F-path function codes.

TABLE 2-5 F-PATH FUNCTION CODES

| HEX  FFN4:0                                                                                                                                                | MNEMONIC                                                    | OPERATION                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00   00000                                                                                                                                                 |                                                             | Idle bus cycle                                                                                                                                                                                                                                 |

| ]                                                                                                                                                          | DI                                                          | RECT I/O RESPONSE                                                                                                                                                                                                                              |

| 01   00001<br>  02   00010<br>  03   00011                                                                                                                 | ATN<br>  IOK<br>  IER                                       | Attention (I/O interrupt lines)<br>  I/O acknowledge, data okay<br>  I/O acknowledge, data error                                                                                                                                               |

|                                                                                                                                                            |                                                             | MEMORY RESPONSE                                                                                                                                                                                                                                |

| 04   00100<br>  05   00101<br>  06   00110<br>  07   00111<br>  08   01000<br>  09   01001<br>  0A   01010<br>  0B   01011<br>  0C   01100<br>  0D   01101 | MDC0 MDC1 MDC2 MDC3 MOK0 MOK1 MOK2 MOK2 MOK3 MER0 MER1 MER2 | Memory read, word 0, disable cache.  word 1,  word 2,  word 3,  Memory read, word 0, data correct.  word 1,  word 2,  word 3,  Memory read, word 0, data error.  word 1,  word 2,  word 3,  Memory read, word 0, data error.  word 1,  word 2, |

| OF   O1111                                                                                                                                                 | MER3                                                        | word 3,                                                                                                                                                                                                                                        |

|                                                                                                                                                            |                                                             | DIRECT I/O                                                                                                                                                                                                                                     |

| 10   10000<br>  11   10001<br>  12   10010<br>  13   10011                                                                                                 | IOR<br>  *<br>  IOW<br>  FDAT                               | I/O read (see I/O subfunction)<br>  reserved<br>  I/O write (see I/O subfunction)<br>  F-path data (follows IOW or MSGn)                                                                                                                       |

| 14   10100  <br>  15   10101  <br>  16   10110  <br>  17   10111                                                                                           | PRE<br>DVA<br>SYNC<br>*                                     | Preempt interrupt<br>  Delete virtual address interrupt<br>  Start real-time clock interrupt<br>  reserved broadcast interrupt                                                                                                                 |

|                                                                                                                                                            | an 1880 Mars door dies dies 1897 Mars days days das das d   | MESSAGES                                                                                                                                                                                                                                       |

| 18   11000  <br>  19   11001  <br>  1A   11010  <br>  1B   11011                                                                                           | MSG0<br>MSG1<br>MSG2<br>MSG3                                | Message #0<br>  Message #1<br>  Message #2<br>  Message #3                                                                                                                                                                                     |

| 1C-iF                                                                                                                                                      | *                                                           | reserved                                                                                                                                                                                                                                       |

# 2.3.3 F-Path Response Codes

IOK and IER are responses to IOR and IOW commands. (See Section 5.4 for details.) MOKn, MERn and MDCn are responses for memory read operations. The responses for a multiple word read operation will usually occur on successive cycles, but this is not required. (See Chapter 4 for additional details.)

The responses (IOK, IER, MOK, MER, MDC) send one item to indicate completion of a direct I/O or memory operation. All direct I/O is acknowleged; this signals the processor to proceed. For IOR responses, read data is returned on F31:00. For IOW responses, the data on F31:00 is not used. Memory reads, including special operations, are responded to with the read data returned on F31:00. Each word of a quadword memory read is sent (MOK, MER or MDC) separately. The memory module may retain the bus for all four words. For memory writes, there is no response on the F-path; the processor does not wait.

# 2.3.4 Summary of F-Path Transfers

All F-path transfers are illustrated in Table 2-6. Each line represents the item sent during one S-bus cycle. When a transfer requires two or three words, these must be sent on consecutive cycles.

TABLE 2-6 SUMMARY OF F-PATH TRANSFERS

|                  | WORD           | •                        | FID                        | ^                                                                                      | ^       | F15                                 | ••••     | F00    |

|------------------|----------------|--------------------------|----------------------------|----------------------------------------------------------------------------------------|---------|-------------------------------------|----------|--------|

| ATN:             | 1:             | 01                       | unit-d                     |                                                                                        |         |                                     |          | .P3210 |

| IOK,             | 1:<br>1:       | 02-03                    | unit-d<br>unit-d           |                                                                                        |         | f read or<br>f read or              |          |        |

| MDC MOK MER      | 1:<br>1:<br>1: | 08-0B                    | unit-d<br>unit-d<br>unit-d | 1<                                                                                     | data :  | read from<br>read from<br>read from | memory   | >      |

| IOR:             | 1:             | 10                       | unit-d                     | SFN                                                                                    | PR  <-  | SID-> <                             | device   | >      |

| IOW:             | 1:             | 12<br>13                 | unit-d<br>unit-d           |                                                                                        |         | SID-> <<br>rite data                |          |        |

| PRE:             | 1:             | 14                       | sender                     | <1 e                                                                                   | vel> <- | unused-                             | >   <-m  | ask->  |

| DVA:             | 1:             | 15                       | sender                     | <vi< td=""><td>rtual a</td><td>ddress to</td><td>be del</td><td>eted&gt;   </td></vi<> | rtual a | ddress to                           | be del   | eted>  |

| SYNC             | : 1:           | 16                       | sender                     | I <                                                                                    |         | not used-                           |          | >i     |

| (rese            | erved)         | 17                       | sender                     |                                                                                        |         |                                     |          |        |

| MSG0:            | 2:             | <br>  18<br>  13<br>  13 | unit-d<br>unit-d<br>unit-d | <                                                                                      | Param   | ID> <-1<br>eter#2 (a<br>eter#3      | address) | >      |

| MSG1:<br>  FDAT: | 2:             | 19<br>  13<br>  13       | unit-d<br>unit-d<br>unit-d | I <                                                                                    | Param   | ID> <- <br>eter#2 (a<br>eter#3      | address) | >      |

| MSG2             | 2:             | 1A<br>13<br>13           | unit-d<br>unit-d<br>unit-d | i <                                                                                    | Param   | ID> <-1<br>eter#2 (a<br>eter#3      | address) | >      |

| MSG3             | 2:             | 1B<br>  13<br>  13       | unit-d<br>unit-d<br>unit-d | i <                                                                                    | Param   | ID> <-1<br>eter#2 (a<br>eter#3      | address) | >      |

# Where:

| FFN | lists the F-path function codes used for eatransfer.                                                             | ch |

|-----|------------------------------------------------------------------------------------------------------------------|----|

| FID | specifies whether the master transmits its of 8-bit unit ID (sender) or the ID of the destination unit (unit-d). |    |

F31:00 illustrates the type of information sent in each word. For attentions (ATN), P3210 represents the status of the DMI's external power fail and interrupts levels 3, 2, 1 and 0.

The first word of IOR, IOW and MSG operations is divided into the following subfields:

| F31:28 | SFN | Subfunction code      | (4 bits)  |

|--------|-----|-----------------------|-----------|

| F27:24 | PR  | Priority code         | (4 bits)  |

| F23:16 | SID | Sender unit ID number | (8 bits)  |

| F15:00 | DEV | Device select         | (16 bits) |

See Chapter 5 for additional information.

The sender inserts its unit ID into the items it sends. For I/O operations and messages, this allows the receiving unit to respond to the sender's ID. For broadcasts, the sender puts its own ID onto FID7:0, so that it may be monitored for diagnostics.

## CHAPTER 3 FUNCTIONAL DESCRIPTION

#### 3.1 CLOCKS

Bus timing is synchronous with a 10.00MHz system clock SCLK is generated on each board using two timing signals which are distributed radially on the system bus (S-bus) backplane:

- OSC is a 20.00  $\pm$  0.001%MHz oscillator. OSC has a 50ns period with less than 2ns jitter. It has a 50%  $\pm$  10% duty cycle at the connector.

- CLK is a 2.00MHz signal used to synchronize SCLKs. derived from OSC and is active for one OSC period (50ns) every 500ns.

Bus timing is relative to the falling edge of OSC- on the backpanel. Timing skew from OSC- to SCLK must be minimized. The rising edge of OSC- is imprecise; hence, it is not used for any bus operation.

The bus distributes the double frequency (20MHz) OSC clock for use internally on each board. Bus activity occurs only at 10MHz.

#### 3.2 POWER CLEAR SIGNALS

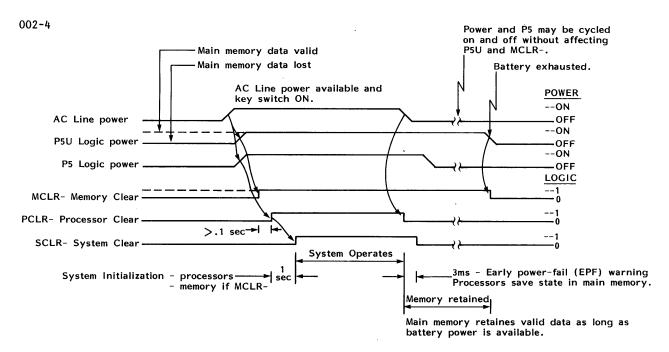

The three clear signals indicate the status of the power supplied to the system. These signals are used to reset circuitry.

MCLR-Memory Clear (P5U powered circuitry)

PCLR-Processor Clear

SCLR-System Clear

## 3.2.1 Power Supplies

S-bus systems operate from two 5V power supplies. These power supplies are controlled by the power supply controller. This includes a microprocessor which is also the master node of the control/diagnostic system (CDS). The microprocessor provides the three power status signals to the S-bus. The microprocessor operates from its own power supply, so it can switch the main power supplies on and off.

P5 (Power, 5V) is the main logic power for the system, derived from AC line power. P5U (Power, 5V, Uninterrupted) is auxiliary logic power which operates from a battery when AC line power is not available. P5U uses AC line power when available. P5 and P5U are independently switched on and off by console commands.

P5U powers the volatile semiconductor random access memory (RAM) chips and associated control circuits on the memory modules. Battery power retains data during short power outages. Battery back-up is optional. However, P5U is still distinct from P5 when there is no battery. P5U is active whenever AC power is present, even if P5 power is switched off by console command.

# 3.2.2 Memory Clear (MCLR)

The MCLR indicates that P5U power is not available and main memory data is invalid. MCLR resets circuitry powered by P5U on memory modules. After MCLR, the contents of the memory array are assumed not valid. During the next initialize period, the memory module must write zeros (or other values) into all memory words. This guarantees that each location has a valid error check and correction (ECC) code and will not create spurious memory failure errors. The memory has at least one second to initialize before the processor initialization begins. Power clear (PCLR) and system clear (SCLR) are always active whenever MCLR is active.

When MCLR is inactive and both PCLR and SCLR are active, the memory modules operate in a standby mode. In this mode, the memory array is powered and refresh cycles are performed, keeping the contents of memory valid.

# 3.2.3 Logic Power Sequencing

Logic power-on/-off cycles occur when the AC power is lost or upon commands from the system console to turn the P5 supply on or off. PCLR and SCLR encode four steps in each power cycle. This sequence is repeated each time power is cycled on and off. P5U power and MCLR are not affected by power cycles as long as the battery has enough stored energy to provide P5U power. For test purposes, the power supply controller must be able to issue this sequence without actually turning power off.

| PCLR | SCLR |                                                       |

|------|------|-------------------------------------------------------|

| 1    | 1    | Reset all circuits powered by P5.                     |

| 0    |      | Initialization.                                       |

| 0    | 0    | Operation. System is powered and running.             |

| 1    | 0    | Early power-fail (EPF) warning; save state in memory. |

Normal Sequence:  $11 \rightarrow 01 \rightarrow 00 \rightarrow 10 \rightarrow 11 \dots$  Aborted Init.:  $11 \rightarrow 01 \rightarrow 01 \rightarrow 11 \dots$  Reset Init Run EPF Reset

The power supply controller determines the timing of each period. The reset period is at least one second long. The initialization period is normally at least one second long. It is aborted if there is a power failure during initialization; PCLR/SCLR changes immediately from "01" to "11"; the operation and EPF states are omitted.

Subsystems must be able to abort their initialization cycle without causing errors. Initialization lasts far longer than the 3ms ride-out time of the power supply. Therefore, power may fail again during initialization. When this happens, PCLR is reasserted without SCLR ever going inactive. See Figure 3-1 for a timing diagram of the three S-bus power clear signals.

Figure 3-1 Power Clear Signal Timing

#### 3.2.3.1 Reset

P5 power is unavailable. All circuits powered by P5 must be reset. Reset lasts at least one second.

#### 3.2.3.2 Initialization on Power-On

The power subsystem turns P5 on when AC line power is available. When P5 is fully on and within regulation limits, the power system deactivates PCLR. SCLR is deactivated one second later, unless a power failure occurs. During this interval, all processors perform power-on diagnostics and initialize all registers. Furthermore, memory modules reset and test their controllers. If MCLR was active at any time since the last initialization step, each memory module initializes all words in its memory array. Each word is set to zero with a correct ECC code. Otherwise, memory data is valid and must be retained.

## 3.2.3.3 Operation

The system operates when both PCLR and SCLR are inactive.

# 3.2.3.4 Early Power-Fail (EPF) Warning

PCLR goes active to indicate an EPF warning. This informs the processors that power will fail, and SCLR will go active 3ms later. This warning is issued when either the power supply is turned off using a console command or when the AC line fails to provide enough power to operate the computer. The P5 and P5U power supplies remain within regulation during this interval. Meanwhile, processors store their registers into main memory so that they can resume processing when power is restored. Main memory remains valid during short power outages (with battery option).

The EPF warning is issued whether or not the power supply includes battery back-up. The system may perform some I/O or other emergency operations, within the 3ms limit.

# 3.3 BUS ACQUISITON AND PRIORITY

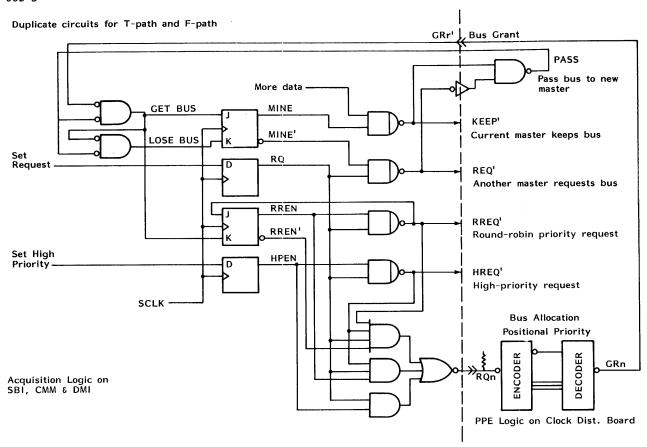

The To-path (T-path) and From-path (F-path) have identical but independent circuitry which allocates bus cycles between boards. This includes acquisition circuits on each board and a positional priority encoder mounted on the backplane. These circuits determine the sequence in which requests are granted; more urgent requests are given priority. Each board slot has positional priority over slots with higher location numbers; slot 0 has the highest priority.

Bus requests have three levels of priority:

High-priority (highest priority level)

Round-robin

Simple (lowest priority level)

All requests at a higher level are granted before any request at a lower level. Within any level, positional priority determines which request is granted first. Within the round-robin level, requests are selectively enabled to provide rotating priority.

To use a path, a board must request and acquire the path. Bus allocation operates in parallel with transfers on the S-bus. Each cycle determines which board gets each path on the following cycle. The board which has a path is known as the path's master and has its MINE flipflop set. At any cycle, there is only one master of each path. For all other boards, MINE is reset.

# 3.3.1 Bus Request and Grant

For each path, every S-bus slot is allotted one bus request signal, RQn-, and one bus grant signal, GRn- ('n' is the slot number). The requests and grants are active low; pull-up resistors assure that the request lines of empty slots remain inactive. Unused request lines may be left unconnected.

A board requests a path by asserting its RQn-. The positional priority encoder determines which board has the highest priority request pending and grants it control of the path for the next cycle (GRn-). All other grant signals remain inactive (high); the other boards must wait.

The positional priority is modified by four open-collector bus signals. These operate by disabling selected categories of requests, which allow the more urgent requests from other slots to be granted.

KEEP- Master retains the bus to complete the current operation.

REQ- Any unit, other than the master, requests use of the bus.

RREQ- Round-robin priority request.

HREQ- High-priority request.

#### 3.3.1.1 Bus KEEP

The master asserts KEEP during operations that require two or more cycles. This prevents loss of the bus in the middle of an operation. KEEP is asserted when the master needs the bus on the following cycle to complete the current operation; normally, KEEP is inactive on the last cycle of any operation. However, KEEP is not used to retain the bus for consecutive operations. KEEP is inactive during idle cycles.

Any board may use KEEP to retain the T-path for retrying a memory operation, if it has already gotten two busy acknowledges on that operation. (See Section 3.5.1.1 for further details.)

# 3.3.1.2 Bus Request Pending

REQ (bus request pending) is asserted by any board that needs to acquire the bus. This enables transferring control. Otherwise, the master retains the bus, even if it is idle. The master should not assert REQ. The bus is transferred only when KEEP=0 and REQ=1. The priority circuits determine which board is granted use of the bus; the master will retain the bus if it has the highest enabled request.

# 3.3.1.3 Priority Requests

HREQ or RREQ can be asserted with REQ for high-priority or round-robin requests. HREQs have priority over RREQs; both have priority over other simple requests. These signals operate by inhibiting (and thus delaying) requests from boards with lower level of priority. When HREQ is active, only high-priority requests are enabled. When RREQ is active, simple requests are disabled.

Processors should have high-positional priority since they are most sensitive to memory access time. (System throughput degrades when a processor must wait for the bus.) Consequently, processors should be placed in slots with higher priority (low number slots). To avoid direct memory access (DMA) lock-out, processors do not assert HREQ.

# 3.3.1.4 Round-Robin Allocation

Round-robin priority is used to allocate use of the bus equally to all processors. Otherwise, a high-performance processor could monopolize the bus during periods of high-memory usage. Lower priority processors might stall since they could not acquire the bus. The round-robin control line RREQ permits processors to share the bus more equally. Processors in lower slots still have priority for a single cycle, but each may do only one operation until all have had access.

Processors request their first operation with both REQ and RREQ. This gives them priority over simple requests. When several processors have pending requests, RREQ stays active until each gets one operation. A processor which requests a second cycle while RREQ is still active must assert only REQ. This is a low-priority request; it can be granted only if no round-robin requests are asserted. When RREQ goes inactive, all processors may again use RREQ.

Memory modules use RREQ to share the F-path equally. When possible, the four words of a quadword are sent on consecutive cycles without relinquishing the F-path. Processor messages and direct I/O also use RREQ.

## 3.3.1.5 High-Priority Allocation

High-priority requests are serviced first; the HREQ signal inhibits round-robin and simple requests. Thus, the high-priority request will get the next access. If several high-priority requests are pending, the positional priority encoder determines which board gets the bus.

HREQ is not used indiscriminately, otherwise it would lose its effectivness due to heavy bus contention. Boards which routinely require rapid access should be given high-positional priority.

The direct memory interface (DMI) generates a Series 3200 DMA bus. Some controllers designed for this bus require prompt response because they do not include sizable buffers. Thus, the DMI can be configured to request high-priority for DMA operations.

# 3.3.1.6 Bus Acquisition Signals

Figure 3-2 illustrates bus acquisition circuitry. All priority modes are shown; RREN and/or HPEN requests may be deleted if they are not needed.

MINE flipflop: board is master of the path.

RQ flipflop: board requests the bus.

RREN flipflop: round-robin priority enable.

HPEN flipflop: high-priority enable.

PASS=KEEP-\*REQ pass the bus to a new master.

GETBUS =PASS\*GRn gain use of bus (sets MINE, resets RREN).

LOSEBUS=PASS\*GRn- lose use of bus (resets MINE).

assert KEEP if MINE\* (next cycle is needed for this operation)

assert REO if RO\*MINE-

assert RREQ if RQ\*RREN round-robin

assert HREQ if RQ\*HPEN high-priority

#### bus request:

ROn = RO\*HPEN high-priority request

+ RO\*RREN\*HREO- round-robin, unless inhibited

+ RQ\*RREQ-\*HREQ- simple, unless inhibited

Figure 3-2 S-Bus Acquisition Logic

#### 3.4 UNIT IDENTIFICATION (ID)

Processors and channels use 8-bit ID codes. On the T-path, TID7:0 identifies the requesting unit. Memory modules latch TID and echo it on FID when responding with read data. On the F-path, FID7:0 addresses the destination unit. Each unit compares FID with its unit address and latches all messages which match.

Broadcast interrupts must be received by all processors regardless of the ID match. No acknowledge is sent. For any other F-path function code, only the addressed unit may respond. The FID field must identify the unit which sent the broadcast; this ID is required to allow diagnostic hardware to monitor activity on the S-bus; it is not used for normal operation.

## 3.4.1 Multiple IDs Per Unit

Bus ID codes must be unique within an S-bus system. However, units may use several IDs to keep track of overlapped memory read operations. Due to memory interleaving, the data sequence may differ from the request sequence. High-performance processors, like the 3280, can use concurrent memory reads to reduce interference between instruction and data fetches.

#### 3.5 TRANSMISSION PROTOCOL

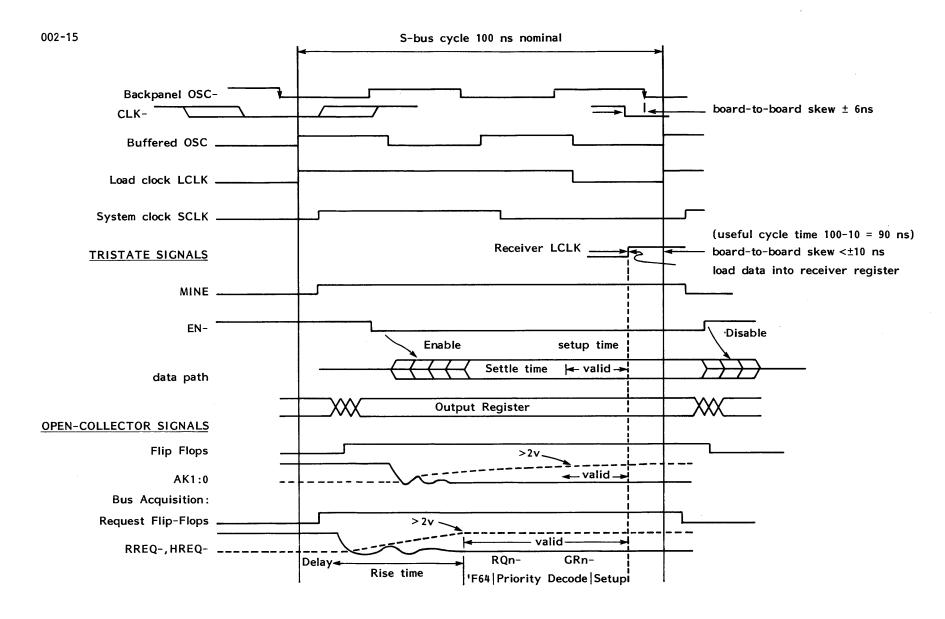

The master of each path can send one item during each clock cycle. The master enables its bus drivers when it gains control and disables them when it relinquishes control to another module.

Every slave receives every item. The item is decoded during the following cycle; no logic delays are allowed during the transfer itself. The slave determines whether or not it is addressed. If it is not, or if the function code is idle, it takes no further action. The slave checks the parity of each item it receives. This check must be performed after the item has been latched in a register, to ensure that all bits are stable. Parity of idle cycles is ignored.

## 3.5.1 Bus Acknowledge

On each path, the selected slave acknowledges each item it receives two cycles after that item was sent. This pipelining of the acknowledges permits high transfer rates.

These lines acknowledge only receipt of the message. The Here response does not imply that the requested operation can be performed.

The acknowledge lines are driven with open-collector gates. The response is the logical-OR of all slaves responding. Normally only one slave will respond, but a parity fault or improper configuration can cause two boards to respond to the same message. The fault code can be aliased if one of these boards is busy.

| AK1:0_ | <u>Meaning</u>                                    |

|--------|---------------------------------------------------|

| 0 0    | No response. (Idle cycle or device not present.)  |

| 0 1    | Here. (Slave is present and accepted the item.)   |

| 1 0    | Busy. (Slave is present but did not accept item.) |

| 1 1    | Fault. (Slave detected parity error.)             |

#### 3.5.1.1 Bus Busy Acknowledge

The slave responds as busy if its input buffer is full and cannot accept the operation. Except for the memory module, the master reacquires the bus and repeats the operation. The slave empties the buffer expeditiously.

Memory and other slaves assert busy only on address cycles. They assert here only when it can accept the entire operation. On the T-path, the function code bit, TFN4, is 1 for an address cycle, 0 for a data cycle.

#### 3.5.1.2 Holding the T-Path After Busy

The master repeats an operation if it receives a busy acknowledge. Normally, the unit reacquires the path using the same priority while other units may use the path. The unit must retry the operation as long as it receives busy acknowledges. In rare cases, this could continue indefinitely. Although the slave cannot remain busy for long, other units can refill its input queue while the unit waits to reacquire the path. To avoid indeterminate delays, the unit may hold the bus after it has received two consecutive busys. It holds the bus by asserting KEEP continuously. It continues to repeat the operation until it is accepted.

Holding the path in this manner assures that priority requests will be completed promptly. Bus bandwidth may be momentarily reduced because of the idle cycles. In this case, however, the system's performance is limited by the memory's bandwidth rather than the bus's.

#### 3.5.2 Bus Fault Acknowledge

The fault acknowledge is sent when a slave detects a parity error in any field of an item addressed to it. This represents a hardware malfunction. Both the master and slave should inform the CDS of all faults. Processors take machine malfunction interrupts. Error recovery is determined by software. The S-bus interface circuits should not automatically retry operations which cause a fault.

When a fault is detected on an address word, the slave aborts the operation. If a memory module detects a fault on a memory write data word, that word is not written, but any preceding word is written. Any subsequent data words are ignored.

#### 3.5.3 Parity Bits

Parity bits accompany the data, function and ID fields. Parity detects errors which alter an odd number of bits; it cannot affect errors which alter an even number of bits. These bits are generated by the master and checked by all slaves. A parity

error is detected if the parity check bit differs from the bus parity bit.

If the addressed slave detects a parity error, it ignores the data item and sends a 'fault' acknowledge to the master. If the error alters the ID field or memory address, the intended may not respond. If the altered field selects another slave, that slave will report the error.

Parity bits are numbered corresponding to power-of-two notation, which is the reverse of the memory byte numbering convention. For instance, parity bit 3 covers bits 31:24 (byte 0).

#### 3.5.4 Bus Time-Out

All operations on the S-bus are deferred response. The master releases the bus after issuing a command; the immediate acknowledge assures that the command was received. The master waits for a response after the operation is done. However, the master does not hang indefinitely if the response never occurred due to a hardware fault. The master contains time-out logic which handles missing responses.

Memory operations should complete within 25 s. Longer delays are faults. Compatible I/O operations should allow 50 s; this allows time for the DMI to detect a false-sync after 30 s. False-sync is a time-out on the multiplexor (MUX) bus when a nonexistent device is addressed; it is signalled by an input/output error response (IER). False-sync does not indicate a hardware fault and it does not cause an S-bus time-out.

# CHAPTER 4 MEMORY OPERATIONS

#### 4.1 INTRODUCTION

System bus (S-bus) memory comprises one or more memory modules, each containing a controller and an array of semiconductor memory chips. Modules are selected by memory address using decoders on each board. Different size and speed modules can be mixed on the same bus.

There are three types of memory operations: read, write and special. The special operations combine a read-modify-write operation into a single primitive command.

#### 4.2 INTERLEAVING

Burst transfers are divided into quadword block transfers. Each module interleaves four ranks of memory to match bus bandwidth for a quadword transfer. However, one module cannot match the bandwidth of both buses. Byte, halfword and special operations are slower than bus speed.

Improved bandwidth is possible when there are two or more modules to share the work. These modules share the bus most effectively when bus operations alternate between modules. Thus, two or four modules can be interleaved by quadwords. Burst transfers access each module cyclically, with successive quadwords sent to different modules in turn. Module interleaving is determined by the address decoders. Memory is configured using the control/diagnostic system (CDS).

#### 4.3 MEMORY MODULE QUEUES

Each module contains an input first-in/first-out (FIFO) buffer. This queue stores addresses and data received while the module is busy performing previous operations. The queue improves performance by allowing more effective sharing. The buffer size is limited to queue four read or write operations. This provides adequate access time for high-priority read operations. (Operations already in the buffer are completed first.)

Each memory module may also contain an output queue for data sent on the From-path (F-path). Memory read data is loaded into this queue queue transmission on the F-path as soon as the module gains control of the bus. Meanwhile, the memory can continue

with subsequent operations. This improves performance especially for intermixed reads and writes.

# 4.3.1 Preserving Memory Operation Sequence

Memory operations are logically performed in the order they appear on the To-path (T-path). The input buffers on each memory module must preserve the sequence of operations to any given memory location. Otherwise, memory values could be uncertain, and cache invalidate logic could not operate precisely.

Operations to different addresses may proceed in any order; the queue on any module is independent of the other modules. In particular, when a high-bandwidth unit performs concurrent quadword reads to overlap access times, the data may come back out of order from interleaved memory. The unit must use unique IDs for concurrent read operations in order to identify the data on the F-path.

# 4.3.2 Address Space

32-bit memory addresses are transferred on the T-path. This provides 4GB of real address space.

For compatibility, some processors and input/output (I/O) units use 24-bit real memory addresses. The high 8 bits of their addresses will be zero. These units are limited to the first 16MB of memory.

## 4.4 T-PATH AND F-PATH USAGE FOR MEMORY

Processors initiate memory operations by sending addresses and data on the T-path. This is the only function of the T-path. Read data is returned by memory on the F-path. The F-path is also used for communication between processors.

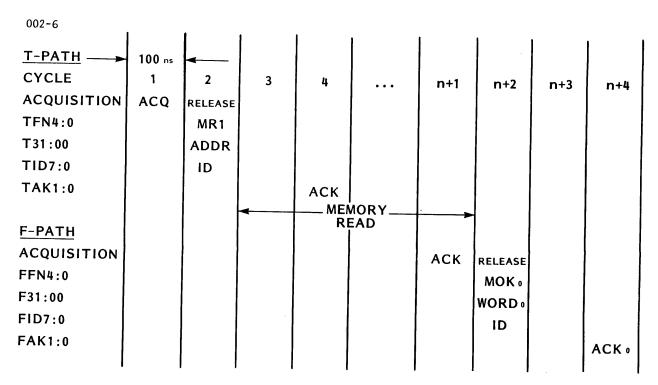

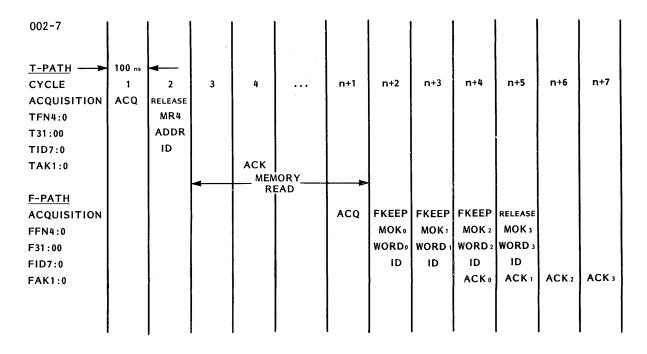

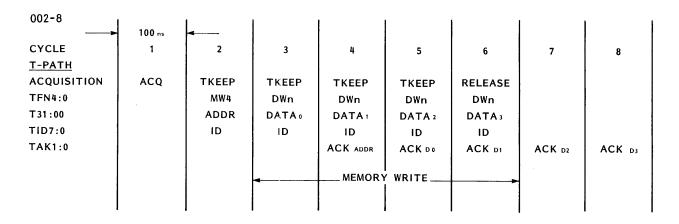

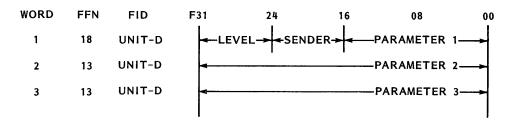

#### 4.5 MEMORY READ OPERATIONS