### MODEL 7/32 REFERENCE MANUAL

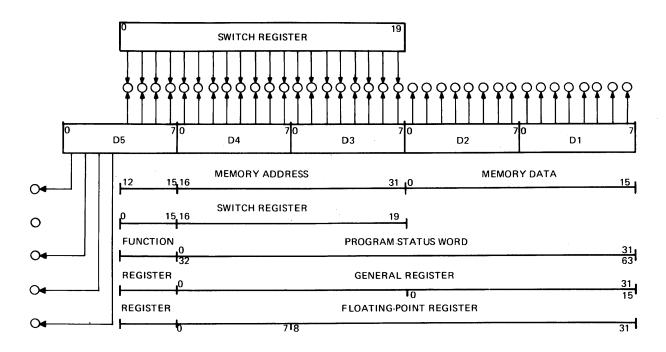

#### **CONSISTS OF:**

| Functional Characteristics of Model 7/32            | 29-399R01A1 |

|-----------------------------------------------------|-------------|

| Hexadecimal Display Programming Specification       | 09-065R01A2 |

| Memory Access Controller Programming Specification  | 02-348R01A2 |

| Extended Selector Channel Programming Specification | 02-328R01A2 |

2 Crescent Place, Oceanport, New Jersey 07757

© INTERDATA INC., 1974 All Rights Reserved Printed In U.S.A. September 1974

# FUNCTIONAL CHARACTERISTICS OF MODEL 7/32

#### 1. INTRODUCTION

Model 7/32 is one implementation of the 32 Bit Series Architecture described in 32 Bit Series Reference Manual (29-365). The 7/32 implementation does not include all the features described in the 32 Bit Series Reference Manual, and is therefore a logical subset of the complete system. The purpose of this manual is to describe all programming features specific to the Model 7/32. Therefore, this manual does not repeat all the descriptions in 29-365, but supplements it.

#### 2. MODEL 7/32 PROCESSOR AND MEMORY

#### 2.1 Program Status Word

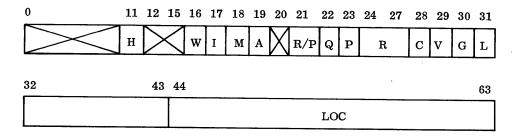

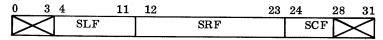

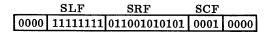

The 64 bit Program Status Word (PSW) for Model 7/32 is shown below:

Bits 44:63 contain the Location Counter. Only twenty bits are used for Location Counter. The maximum memory available in Model 7/32 is 2<sup>20</sup> bytes (i.e., 1,048,576 bytes or approximately 1 Megabyte). Program references to memories beyond maximum possible (i.e., beyond 1 Mbyte) result in wraparound. For example: if an attempt is made to address memory location X'100000', the instruction addresses location X'00000'.

If an attempt is made to read from a non-existing memory location in the local memory (Bank 0, first 256KB of memory), the data read is all zeros. If an attempt is made to read from a non-existing memory using the Memory Access Controller interface, the data read is undefined. (Also, see Section 2.4.4).

Bits 0:31 are reserved for status information, interrupt masks and machine mode (halfword or fullword). These bits are defined as follows:

Bit 11 - Halfword Mode

Bit 16 - Wait State

Bit 17 - Immediate Interrupt Mask

Bit 18 - Machine Malfunction Interrupt Mask

Bit 19 - Arithmetic Fault Interrupt Mask

Bit 21 - Relocation/Protection Interrupt Mask

Bit 22 - System Queue Service Interrupt Mask

Bit 23 - Protect Mode

Bits 24:27 - Register Set Select Bits

Bits 28:31 - Condition Code

Unassigned PSW bits must not be used and must always be zero. PSW bit 20 is not to be used by any program that runs on Model 7/32. Bits 17 and 20 together define the Priority Interrupt Enable Mechanism for 32 Bit Series machines as described below:

| Bit 17 | Bit 20 |                                                             |

|--------|--------|-------------------------------------------------------------|

| 0      | 0      | Disable I/O Interrupts at all levels                        |

| 0      | 1      | Enable at higher level; disable at current and lower levels |

| 1      | 0      | Enable I/O Interrupts at all levels                         |

| 1      | 1      | Illegal combination                                         |

Note that when bit 20 is a zero, as it must be on Model 7/32, priority interrupt system is not enabled. In that case, interrupts are unconditionally enabled or disabled by bit 17 of the PSW.

PSW bits 24:27 are used to designate the current register set. In Model 7/32, there are only two register sets - set 0 and set 15. Register set 0 is the I/O and Interrupt register set and register set 15 is the user register set. In order to maintain upward compatibility with future INTERDATA 32-Bit machines, it is necessary to select the I/O register set by loading 0 into bits 24:27 and select the user register set by loading X'F' into bits 24:27.

Bit 11 of the PSW selects a special mode called Halfword Mode. This bit is used only for certain special applications and is normally not used. The Halfword Mode and its implications are described in detail in Section 2.3.

#### 2.2 Reserved Memory Locations

The following memory locations are reserved for interrupt pointers, Program Status Words and system constants.

| Location             | <u>Use</u>                                                 |

|----------------------|------------------------------------------------------------|

| X'000000'-X'00001F'  | Floating point registers                                   |

| X'000020'-X'000027'  | Machine malfunction interrupt old PSW                      |

| X'000028'-X'000029'  | Used by microprogram to save console status                |

| X'00002A'-X'00002F'  | Not used, must be zero                                     |

| X'000030'-X'000037'  | Illegal instruction interrupt new PSW                      |

| X'000038'-X'00003F'  | Machine malfunction interrupt new PSW                      |

| *X'000040'-X'000047' | Old, New PSW Ext. Interrupt Halfword Mode                  |

| X'000048'-X'00004F'  | Arithmetic fault interrupt new PSW                         |

| X'000050'-X'00007F'  | Bootstrap loader and device definition table               |

| X'000080'-X'000083'  | System queue pointer                                       |

| X'000084'-X'000085'  | Current PSW save pointer                                   |

| X'000086'-X'000087'  | Register save pointer                                      |

| X'000088'-X'00008F'  | System queue service interrupt new PSW                     |

| X'000090'-X'000097'  | Relocation/protection interrupt new PSW                    |

| X'000098'-X'00009B'  | Supervisor call new status                                 |

| X'00009C'-X'0000BB'  | Supervisor call interrupt new location counters (32 Bytes) |

| X'0000BC'-X0000CF'   | Not used, must be zero                                     |

| X'0000D0'-X'0002CF'  | Interrupt service pointer table (256 Halfwords)            |

| X'0002D0'-X'0004CF'  | Expanded interrupt service pointer table (256 Halfwords)   |

| X'0004D0'-X'0008CF'  | Expanded interrupt service pointer table (256 Halfwords)   |

<sup>\*</sup> Used only in Halfword Mode. See Section 2.3.4 for explanation.

These reserved locations play an important role in both interrupt and I/O processing. They are explained in detail in Section 2.4. It should be noted here that the new PSW Location for each external interrupt and Supervisor Call is a halfword (16 bits). Therefore, all the interrupt processing routines (or at least the first instruction of such routines) must reside in first 64K bytes of memory.

The basic machine is set up for handling 255 device addresses. Device numbers may range from X'001' through X'3FF' (Device number X'000' is not used). Dedicated numbers are X'001' for the console and X'007' for the LSU.

The Interrupt Service Pointer table at memory locations X'D0'-X'2CF' is used for vectoring the device interrupts. This table can be expanded optionally to handle either 511 or 1023 device interrupts. This is accomplished by expanding the bus buffer through the use of Sub Channel Controllers to provide two additional bits of address decoding, in which case, the service pointer table is expanded either to X'4CF' or to X'8CF'.

All the memory addresses stored in these memory locations for Old or New PSW locations are absolute values and are <u>not</u> translated by the Memory Access Controller (MAC), if present. Refer to Section 4 for the detailed description of the MAC.

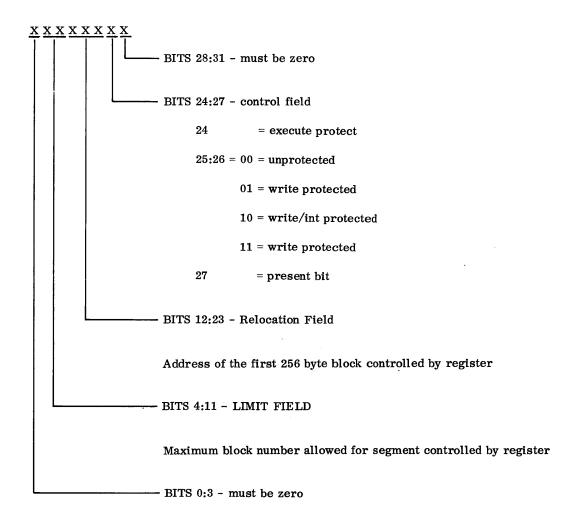

If the configuration has provision for no more than 255 external devices, the Memory Access Controller (MAC) segmentation registers are assigned locations X'000300' thru X'00033F'. The MAC status register is assigned the fullword location at X'000340'. If the configuration has provision for more than 255 external devices, the block of memory locations assigned to the controller starts at the nearest multiple of X'000100' above the expanded interrupt service pointer table. For example, if the Interrupt Service Pointer Table is expanded to X'0004CF', the MAC registers would be assigned locations X'000500 through X'000540'.

Bit 21 of the current program status word enables the segmentation, relocation and protection features of MAC. If this bit is reset, all memory references are absolute and all protection is disabled.

When bit 21 is reset, the controller is still active in that it traps memory references to the location assigned to its registers. If the processor references any location trapped, but not used, by the Controller, the results are undefined. The Controller traps at least a 256 byte block of memory beginning at X'000300'. It is therefore recommended that all programs reside in memory above memory location X'000A00'.

#### 2.3 Machine Modes

The INTERDATA 7/32 Processor is a microprogrammed computer which is equipped with additional Read Only Memory (ROM) which enables it to emulate INTERDATA Models 7/16, 70, 74, and 80. Program compatibility at the machine language level is achieved by providing a special compatibility mode called Halfword Mode.

#### NOTE

The Halfword Mode, as described below, is included in the 7/32 to allow the execution of certain 16-bit series programs, such as some test programs. The Halfword mode feature will not necessarily be included in future members of the 32-bit series of machines.

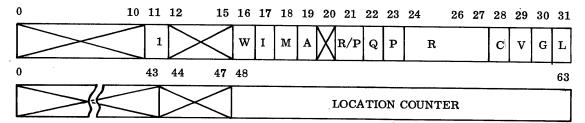

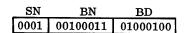

The 7/32 Processor can be made to operate in halfword mode by setting a bit (bit 11) in the Program Status Word. The 64 bit program status word for Model 7/32 (in halfword mode) is shown below:

The PSW bits from 16 to 31 have the same meaning as explained in 2.1. Bits 48:63 contain the Location Counter.

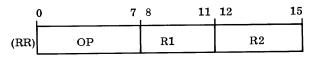

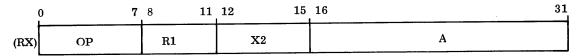

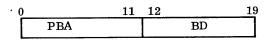

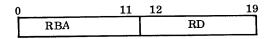

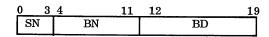

Figure 1 shows the instruction formats in halfword mode. These formats are identical to the formats of a 16 bit processor.

REGISTER TO REGISTER

SHORT FORMAT

REGISTER TO INDEXED MEMORY

REGISTER TO STORAGE

Figure 1. Instruction Formats (Halfword Mode)

The eight-bit OP field in all formats specifies the machine operation to be performed. Operation codes are represented as two hexadecimal characters.

The four-bit R1 field in the instruction formats specifies the address of the first operand. The R1 field is normally the address of a General Register.

The four-bit R2 field in the RR instruction format specifies the address of the second operand, which is normally a register address.

The four-bit DATA field of the SF instructions supplies data in the case of Fixed-Point Arithmetic instructions, or a displacement from the current Location Counter in the case of Branch instructions.

A non-zero X2 field in the RX and RS formats specifies a General Register whose contents is used as an index value. The index value (X2) may be positive or negative. If X2 is zero, no address modification takes place. General Registers 1 through 15 can optionally be used for indexing, but General Register 0 can never be used for indexing.

The 16-bit Address field specifies a memory address in the RX format, or contains a value (data) to be used as an immediate operand in the RS format.

The instructions shown in Appendix 2 can be executed in halfword mode. This set of instructions corresponds to a Model 70, 80, or 7/16 with HSALU option. The machine, when operating in halfword mode, executes all non-privileged instructions (except SVC) exactly the same way they are executed on 16-bit INTERDATA processors. The SVC instruction, in halfword mode, is executed as follows:

The SVC instruction has RX format. The second operand address, A+(X2) replaces bits 16:31 of Register 13 of Register set 0. Bits 0:15 of this register are undefined and should be ignored. The current Program Status Word replaces the contents of Registers 14 and 15 of Register set 0. The fullword quantity located at '000098' in memory replaces bits 0:31 of the current Program Status Word. The R1 field is doubled and added to X'00009C'. The halfword quantity located at this address becomes the current Location Counter.

#### CAUTION

When an interrupt is generated that causes a mode change from the halfword mode to the fullword mode, higher-order bits of all registers are undefined with the exception of Register 0 or 14 (register set 0) which contains the old PSW status (See Figure 2.)

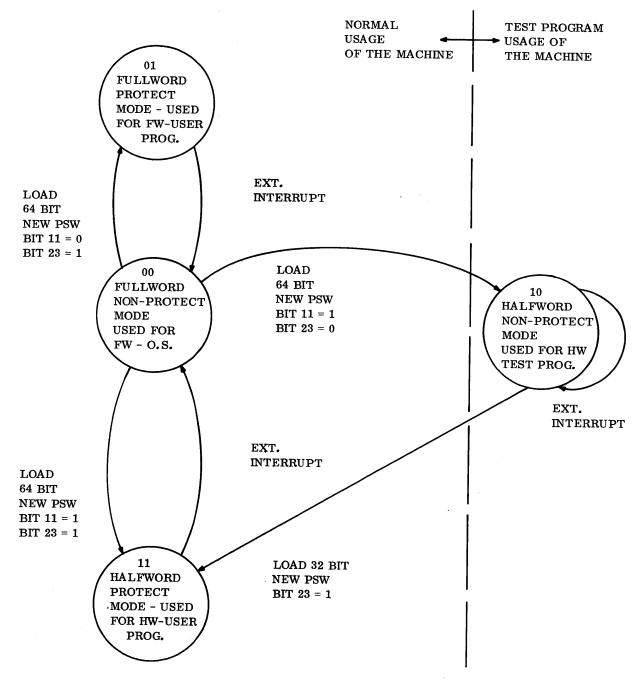

| INTERRUPT              | OLD PSW            | NEW PSW                                          | OTHER PARAMETERS                                                   |

|------------------------|--------------------|--------------------------------------------------|--------------------------------------------------------------------|

| MACHINE<br>MALFUNCTION | MEM. LOC.<br>20-27 | MEM. LOC.<br>38-3F                               |                                                                    |

| ILLEGAL<br>INSTRUCTION | REG. 14,15         | MEM. LOC.<br>30-37                               |                                                                    |

| ARITHMETIC<br>FAULT    | REG. 14,15         | MEM. LOC.<br>48-4F                               |                                                                    |

| MAC INTERRUPT          | REG. 14,15         | MEM. LOC.<br>90-97                               |                                                                    |

| SVC INTERRUPT          | REG. 14,15         | MEM. LOC.<br>98-9B<br>(STATUS)<br>ONE OF<br>9CBB | REG. 13 = ADDRESS OF<br>SVC PARAMETER<br>BLOCK                     |

| IMMEDIATE<br>INTERRUPT | REG. 0,1           | NEW PSW = X'00002800'                            | REG. 2 = DEVICE ADDR. REG. 3 = DEVICE STATUS REG. 4 = INTRPT ADDR. |

| SYSTEM Q<br>SERVICE    | REG. 14,15         | MEM. LOC.<br>80-8F                               | REG. 13 = ADDR. OF<br>SYSTEM Q.                                    |

Figure 2. Register Set 0 Modifications By Interrupts

Except SINT, LPSW, and EPSR, all privileged instructions are also executed as defined by 16 bit architecture (refer to the 7/16 Reference Manual, 29-398, or the User's Manual, 29-261). Supervisor call (SVC), and Simulate Interrupt (SINT) instructions are executed as defined in the 32-bit series architecture manual. Load Program Status Word (LPSW) and Exchange Program Status Register (EPSR) instructions are executed as described below:

#### LSPW:

```

PSW(16:31) \leftarrow A+(X2)

PSW(48:63) \leftarrow A+(X2)+2

```

#### EPSR:

$PSW(16:31) \longrightarrow (R1)$  $PSW(16:31) \longleftarrow (R2)$

where: A - 16-bit address specified by RX instruction

X2 - The address of a general register, the contents of which is used as an index value

R1 - First operand register

R2 - Second operand register

It should be noted that in halfword mode, all the instructions shown in Appendix 2 use 16-bit General Registers. These 16-bit General Registers are defined by the low-order portion (Bits 16-31) of the 32-Bit General Registers. The high-order portion (bits 0-15) of all the 32-bit General Registers are undefined in halfword mode.

The interrupt system in halfword mode is different from the interrupt system on 16-bit processors, as described in the following sections.

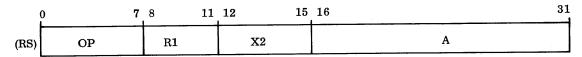

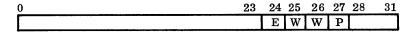

Bit 23 of the Program Status Word controls the protect mode of the 7/32 Processor. If this bit is set, the processor is in protect mode, and only non-privileged instructions may be executed. The halfword mode bit (Bit 11) and protect mode bit define a total of four machine modes for the 7/32 processor. The following paragraphs define these machine modes. Refer to Figures 3 and 4.

| Mode # | PSW<br>Bit 11 | PSW<br>Bit 23 | Machine<br>Mode         | Normal Legal<br>Usage Instructions                       |                                                                                       | External<br>Interrupt<br>Handling                              |  |

|--------|---------------|---------------|-------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| 00     | 0             | 0             | Fullword<br>Non-protect | O. S.,<br>32-bit<br>Stand-alone<br>Programs              | All Model 7/32<br>Instructions<br>(see Appendix 1)                                    | Interrupt Service Pointer Table LOC. X'D0 thru X'2CE'          |  |

| 01     | 0             | 1             | Fullword<br>Protect     | Fullword<br>User Prog.                                   | All Model 7/32<br>Non-privileged<br>Instructions<br>(see Appendix 1)                  | Interrupt Service<br>Pointer Table<br>LOC. X'D0 thru<br>X'2CE' |  |

| 11     | 1             | 1             | Halfword<br>Protect     | Halfword<br>User Prog.                                   | All Model 7/32<br>Halfword Mode<br>Non-privileged<br>Instructions<br>(see Appendix 2) | Interrupt Service pointer table LOC. X'D0' thru X'2CE'         |  |

| 10     | 1             | 0             | Halfword<br>Non-Protect | Halfword<br>Peripheral<br>Test Prog.<br>(see Appendix 4) | All Model 7/32<br>Halfword Mode<br>instructions<br>with certain<br>restrictions       | LOC.<br>X'40'-'43' = Old<br>PSW<br>X'44'-'47' - New<br>PSW     |  |

Figure 3. Machine Modes

Figure 4. Model 7/32 Machine Mode Transition by an External Interrupt

2.3.1 Mode 00: Bit 11 = 0, Bit 23 = 0. This is the Fullword Non-protect mode. All the instructions in Appendix 1 - privileged and non-privileged - can be executed in this mode. Note that the following instructions, which are legal in the halfword mode, are illegal in this mode:

| Mnemonic | Op-Code    | Name                            |

|----------|------------|---------------------------------|

| ACHR     | OE         | Add With Carry Halfword RR      |

| SCHR     | OF         | Subtract With Carry Halfword RR |

| ACH      | <b>4E</b>  | Add With Carry Halfword         |

| SCH      | <b>4F</b>  | Subtract With Carry Halfword    |

| MHUR     | 9C         | Multiply Halfword Unsigned RR   |

| AIR      | <b>9</b> F | Acknowledge Interrupt RR        |

| MHU      | DC         | Multiply Halfword Unsigned      |

| AI       | DF         | Acknowledge Interrupt           |

When an external interrupt occurs in this mode and if it is enabled by bit 17 of the current PSW, the interrupt Service pointer table (memory locations X'D0' through X'2CE') is used to perform an immediate interrupt or an Auto Driver channel operation. This mode is normally used by the Operating System and other stand-alone programs for Model 7/32 for privileged instruction execution. Refer to 29-365 for details.

- 2.3.2 <u>Mode 01</u>: Bit 11 = 0, Bit 23 = 1. This is the Fullword Protect mode. All the <u>nonprivileged</u> instructions in the Model 7/32 instruction repertoire are executable in this mode. External interrupts are treated in the same manner as in Mode 00. The machine will be in this mode when Fullword user programs are run under an operating system.

- 2.3.3 Mode 11: Bit 11 = 1, Bit 23 = 1. This is the Halfword Protect Mode. All the nonprivileged instructions shown in Appendix 2 can be executed in this mode and (except SVC) they work exactly the same way as they work on 16-bit processors. The SVC instruction is executed as in the Fullword Protect mode. The External Interrupts are treated in the same manner as in Mode 00.

The machine will be in this mode when Halfword user programs are run under an operating system. An operating system for Model 7/32 can use this mode to run user programs written for 16-bit processors.

2.3.4 Mode 10: Bit 11 = 1, Bit 23 = 0. This is the Halfword Non-protect Mode. It is a special mode. Most programs written for INTERDATA 16-bit processors can be run in this mode. The external interrupts are handled as follows:

Note that only 16-bit new PSW status and 16-bit new PSW Location Counter are loaded. The program must acknowledge the interrupt by using either an Acknowledge Interrupt (AI) or Acknowledge Interrupt Register (AIR) instruction.

In Mode 10, all other interrupts are handled the same as in Fullword Modes as explained in Section 2.4. Mode 10 can be used to run peripheral test program software. This is explained in detail later in Section 3. Note that not all old stand alone software runs in this mode because SVC and SINT instructions, which generate internal interrupts, alter the 64 bit new PSW as defined in Section 2.4.

2.3.5 Change of Mode in Model 7/32. In general, a machine mode can be changed by executing an instruction which loads a new PSW to change the state of bits 11 and/or 23 by taking an internal interrupt.

The machine mode can be changed from Mode 00 to any other mode by loading a new 64 bit PSW.

#### Example 1:

|      | LPSW | PSW1        |             |

|------|------|-------------|-------------|

| PSW1 | DC   | X'00000100' | <b>P</b> =1 |

|      | DC   | A(LOC1)     |             |

| LOC1 | EQU  | *           |             |

In this example, the new machine mode (at location LOC1) is mode 01, i.e., Fullword Protect mode.

#### Example 2:

|      | LPSW | PSW2        |

|------|------|-------------|

| PSW2 | DC   | X'00100100' |

|      | DC   | A(LOC2)     |

| LOC2 | EQU  | *           |

Here, the new machine mode is 11, i.e., Halfword Protect mode.

When an external interrupt occurs in mode 01 or 11, the mode is changed to 00. This is done by the hardware (microprogram) and a new PSW of X'00002800' is loaded. A mode change from Mode 01 (or 11) to 00 can occur only by an interrupt since no privileged instruction can be executed, when bit 23 is set, to load a new PSW.

When an external interrupt occurs in Mode 10, a new PSW is loaded from memory locations X'44' - X'45' into PSW bits 16 through 31. Bit 11 remains set. Normally PSW bit 23 will be reset in the new PSW. Contents of memory locations X'46'-X'47' replace the program location counter. Thus, a mode change from 10 to 10 (no change), or 10 to 11 can occur.

The above are the normal mode changes and that is how the machine is expected to be used. However, the following mode changes can occur:

While in mode 10, a new PSW of X'0100' can be loaded to change the mode to 11. However, this is done only by the Processor Test to check this mode.

Finally, the memory locations in the low core can be modified to select any other mode by selecting the appropriate new PSW on an internal interrupt.

The following sequence of instructions will force the fullword non-protect mode from any other mode:

| 2400<br>4000<br>0030 | LIS<br>STH | R0, 0<br>R0, X'30' | STORE NEW PSW STATUS                          |

|----------------------|------------|--------------------|-----------------------------------------------|

| 4000<br>0032         | STH        | R0, X'32'          | TO SELECT MODE 00                             |

| 4000<br>0034         | STH        | R0, X'34'          |                                               |

| C810<br>XXXX         | LHI        | R1, ILGL           | STORE NEW PSW LOC.                            |

| 4010<br>0060         | STH        | R1, X'36'          |                                               |

| 0000<br>XXXX ILGL    | DC<br>EQU  | X'0'<br>*          | ILLEGAL INSTRUCTION<br>MACHINE NOW IN MODE 00 |

#### 2.4 Interrupt System

When bit 11 of the current PSW is set, the processor is in the halfword mode. Refer to Section 2.3.4 for the description of external interrupt mechanism in the halfword mode. The interrupt mechanism for all other interrupts does not depend on the state of bit 11. Refer to Figure 2.

With the exception of the machine malfunction interrupt, when the current PSW becomes the old PSW it is saved in a pair of registers belonging to register set 0. The machine malfunction old PSW is stored in a reserved memory location. Again with one exception, when a new PSW becomes the current PSW, it is loaded from a reserved memory location. The exception is the immediate interrupt. On an immediate interrupt, the current status is forced to a pre-determined value (X'00002800'). The current Location Counter is loaded from the interrupt service pointer table.

The new Program Status Word for any interrupt should, if possible, disable interrupts of its own class, and should specify register set 0 to avoid the overhead of saving registers.

2.4.1 Immediate Interrupt. The immediate interrupt is used for I/O control. Through this mechanism, external devices can request and obtain Processor service. Bit 17 of the current PSW controls the immediate interrupt. If this bit is set, the Processor is responsive to device requests. If this bit is reset, requests are queued until the Processor is able to recognize them. When the Processor recognizes a request from a device it:

Saves the current PSW in Registers 0 and 1 of general register set 0.

Loads the status portion (bits 0:31) of the current PSW with a value of X'00002800'.

Acknowledges the request and obtains the device number and status from the device. The device number is placed in Register 2 of the register set 0. The status is placed in Register 3.

Adds two times the device number to X'0000D0' (the starting location of the interrupt service pointer table) to obtain the halfword address within the table that corresponds to the interrupting device. For the immediate interrupt, the value in the table must be even. The halfword value in the table becomes the current Location Counter.

In setting up the registers for the immediate interrupt service routine, the Processor loads the device number into the least significant 10 bits and status into the least significant 8 bits of Registers 2 and 3 respectively. The most significant bits are forced to zero.

Note that the current PSW for immediate interrupts disables the immediate interrupt and specifies register set 0. If it is desired to run the interrupt routine with interrupts enabled, the routine must save the information contained in Registers 0:4, and should switch to register set 15.

2.4.2 Console Interrupt. The console interrupt is a special case of the immediate interrupt. It too is controlled by Bit 17 of the current PSW. If this bit is set, a console interrupt is generated by:

Depressing the Function key on the console and Depressing 0

The effect of the console interrupt is to cause an immediate interrupt, as described previously from device X'001'.

- 2.4.3 <u>Simulated Interrupt</u>. The Simulate Interrupt instruction simulates an immediate interrupt. When this instruction is executed, the Processor goes through the immediate interrupt procedure as if a request for service had been received from an external device. The current PSW is saved, and the new PSW loaded just as for the immediate interrupt. The device is addressed, and the status returned in Register 3. The halfword address from the interrupt service pointer table is placed in Register 4. The state of Bit 17, immediate interrupt enable, has no effect on this interrupt, as it is always enabled.

- 2.4.4 <u>Machine Malfunction Interrupt</u>. Bit 18 of the current PSW controls the machine malfunction interrupt. This interrupt, if enabled, occurs on a memory parity error, following the detection of primary power failure, and during the restart procedure after power has been restored. When a machine malfunction interrupt occurs, the current PSW is saved in memory location X'000020'. The new PSW from memory location X'000038' becomes the current PSW. The Condition Code of the new PSW as stored in memory must contain zeros. After the interrupt is taken, the state of the Condition Code indicates the specific cause of the interrupt.

Condition Code states are:

| C | V | G | L |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| x | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| x | 1 | 0 | 0 |

| 1 | x | 0 | x |

Power restore

Power failure

Parity error on instruction fetch

Parity error on data fetch

Parity error or power failure during auto driver channel operation

Power failure micro code sequence is executed when the primary power fail detector senses a low voltage, when the Initialize key (INT) of the display console is depressed, when the initialize switch (INT) of a Loader Storage Unit (LSU) is placed in the UP position, or when the key operated Power switch is turned to the OFF position. Following the PSW exchange, the software has approximately one millisecond to perform any necessary operations before the automatic shut down micro code sequence is activated. During automatic shut down, the Processor saves the current PSW at the memory location specified by the contents of location X'000084'. This Halfword save address must exist within the first 65KB of memory. Both sets of general registers, starting with register set 0, are saved at the location specified by the contents of memory location X'000086'. Pointers contained in memory locations X'000084' and X'000086' are absolute addresses. Note that the register save requires 128 consecutive bytes of memory.

When power returns, actual or simulated, the Processor first senses the configuration on the multiplexor bus. If the LSU is not present, it restores the PSW and general registers from their respective store areas. If one is present, the Processor obtains the following information from the user PROMs:

- (1) PSW status

- (2) PSW location

- (3) Addresses where loading from user PROMs is to commence and to be completed

- (4) Address to which control is to be transferred following the loading process

In either case, if Bit 18 of the restored PSW is set, the Processor takes another machine malfunction interrupt, this time with no bits set in the Condition Code of the current PSW.

During write operations to memory, the Parity bit of each memory word is set by the hardware to maintain odd parity if the parity option is installed. The Parity bit is recomputed on each memory read. If the computed bit is not equal to the parity bit read out of memory, the Processor generates a machine malfunction interrupt, setting the V or the G flag to indicate error on data fetch or instruction fetch.

If a machine malfunction interrupt condition arises during an auto driver channel operation, the PSW, current at the time the channel was activated, becomes the old machine malfunction PSW. Register 4 of register set 0 contains the address of the Channel Command Block. The C flag of the current PSW is set along with either the L flag or the V flag to indicate either power failure or parity error on a data fetch.

#### Programming Note:

If an attempt is made to access a nonexisting memory location, a parity error will be detected if the parity option is installed and machine malfunction is enabled. At this time, a machine malfunction interrupt will be generated, with condition code set to indicate parity error on data fetch. If the machine malfunction interrupt is disabled, no interrupt is generated. In each case the data read consists of all zeros.

2.4.5 <u>Arithmetic Fault Interrupt</u>. Bit 19 of the current PSW controls the arithmetic fault interrupt. This interrupt, if enabled, can occur for any of the following reasons:

Fixed point division by zero

Fixed point quotient overflow

Floating point division by zero

Floating point overflow or underflow

When this interrupt occurs, the current PSW is saved in Registers 14 and 15 of register set 0. The new PSW, from memory location X'000048', becomes the current PSW. All Condition Code bits in the new PSW as stored in memory must be zero. Before going to the interrupt service routine, the Processor sets the carry flag in the Condition Code if the interrupt is the result of a floating point operation. If the interrupt is the result of a fixed point operation, the carry flag is not set.

Any of the following conditions cause fixed point quotient overflow:

- A halfword divide operation produces a result greater than 32,767.

- A halfword divide operation produces a result less than -32.768.

- A fullword divide operation produces a result greater than 2,147,483,647.

- A fullword divide operation produces a result less than -2, 147, 483, 648.

When a fixed point division by zero or a fixed point quotient overflow occurs, the operand registers remain unchanged.

Floating point overflow occurs when in a floating point operation, the value of the exponent exceeds 63. Floating point underflow occurs when, during the execution of a Floating Point instruction, the value of the exponent becomes less than 64. Following floating point overflow, the result is forced to plus or minus X'7FFF FFFF'. Following a floating point underflow, the result is forced to true zero X'0000 0000'. After a floating point division by zero, the operand register remains unchanged.

After any arithmetic fault interrupt, the Location Counter of the old PSW contains the address of the instruction immediately following the one that caused the interrupt.

- 2.4.6 <u>Relocation/Protection Interrupt</u>. Bit 21 of the current PSW controls the relocation/protection interrupt. If this bit is set, and the currently running program violates any of the relocation and protection conditions available in the Memory Access Controller, the Processor saves the current PSW in Registers 14 and 15 of register set 0. The new PSW at memory location X'000090' becomes the current PSW.

- 2.4.7 System Queue Service Interrupt. Memory location X'000080' contains the address of the system queue. In the course of executing any of the following instructions:

Load Program Status Word Load Program Status Word Register Exchange Program Status

the Processor tests Bit 22 of the new status being loaded. If this bit is set, the Processor checks the state of the system queue. If there is an entry in the queue, the just loaded PSW becomes the old PSW. It is saved in Registers 14 and 15 of register set 0. The address of the queue, taken from location X'000080' is placed in Register 13 of register set 0. The new PSW from location X'000088' becomes the current PSW.

2.4.8 <u>Protect Mode Violation Interrupt.</u> Bit 23 of the current PSW controls the execution of Privileged instructions. When this bit is set, the Processor is in the Protect mode. Programs running in the Protect mode are not allowed to execute Privileged instructions. Privileged instructions are:

All I/O instructions Load Program Status Word Load Program Status Word Register Exchange Program Status Register Simulate Interrupt Simulate Channel Program

If a program running in the protect mode attempts to execute a Privileged instruction, the instruction is not executed. The Processor saves the current PSW in Registers 14 (PSW Bits 0:31) and 15 (PSW Bits 32:63) of register set 0. The new PSW at location X'000030' becomes the current PSW. The Location Counter of the old PSW (register 15, set 0) contains the address of the privileged instruction.

Programming Note: Refer to Appendix 1 for the privileged instructions in the fullword mode (PSW Bit 11 = 0). Refer to Appendix 2 for the privileged instructions in the halfword mode (PSW bit 11 = 1).

2.4.9 <u>Illegal Instruction Interrupt</u>. The illegal instruction interrupt cannot be disabled. The interrupt occurs whenever the Processor fetches an instruction word containing an operation code that is not one of those permitted by the system. The Processor saves the current PSW in Registers 14 and 15 of register set 0. The illegal instruction new PSW from memory location X'000030' becomes the current PSW.

When the Processor encounters an illegal instruction, it makes no attempt to execute it. The Location Counter of the old PSW (register 15 set 0) contains the address of the illegal instruction.

Refer to Appendix 1 (or Appendix 2) for the legal op-codes in the fullword (or halfword) mode.

- 2.4.10 <u>Supervisor Call Interrupt</u>. This interrupt occurs as the result of the execution of a Supervisor Call instruction. This instruction provides a means for user level programs to communicate with system programs. The supervisor call interrupt is always enabled. When the Processor executes a Supervisor Call instruction, it:

- Saves the current PSW in Registers 14 and 15 of register set 0.

- Places the address of the supervisor call parameter block (address of the second operand) in Register 13 of register set 0.

- Loads the current PSW status with the value contained at memory location X'00098', supervisor call new status.

- Loads the current PSW Location Counter from one of the supervisor call new PSW Location Counter locations.

#### 3. PERIPHERAL TEST PROGRAMS FOR MODEL 7/32 IN THE HALFWORD MODE

A number of test programs are furnished with Model 7/32 to help the user in trouble-shooting. There are two types of test programs: those which run in the fullword mode and those which run in the halfword mode. The test programs which run on all 32 Bit Series machines are designed to run in the fullword mode (Bit 11 of the PSW = 0). These include Series 32 Processor Tests, Series 32 Memory Tests, Extended Selector Channel test, Series 32 System Exerciser, etc. The corresponding program descriptions include detailed operating instructions for running these programs.

Some test programs are written using Model 7/16 Instruction repertoire (e.g., Single Address 360/370 Interface Test (06-166). They run on Model 7/16 as well as on Model 7/32. It is necessary for the user to change certain parameters to run these programs on Model 7/32. Refer to the corresponding program descriptions for these modifications.

Some of the peripheral test programs which are used on INTERDATA 16 Bit machines (e.g., Card Reader Test 06-038) also run on the Model 7/32 in the halfword mode with certain limitations. Refer to Appendix 4 for a list of such programs.

The corresponding program descriptions explain how to load and execute these programs on 16-Bit processors.

In order to run these programs on Model 7/32, the following procedure should be followed:

- 1. Load the special 50 Sequence described in Figure 5. Read each memory location to verify that the data is loaded correctly.

- 2. Address memory location X'30' using the Console Panel switches. Depress the SGL switch. The processor will try to execute the illegal instruction X'00'. An illegal instruction interrupt is generated and the new PSW from memory location X'30' is loaded. This new PSW has PSW bit 11 set and therefore the processor is in the halfword mode. The new location counter at this time is X'50'.

- 3. Place the program paper tape for the General Loader (06-025) into the paper tape reader. Depress RUN switch on the Console Panel. The 50 Sequence loads the General Loader at the top of memory if it is less than 64KB or at memory location X'FA00' if more than 64KB of memory is in the machine.

- 4. Refer to the General Loader description and set the bias value to load the test program. The bias value must be selected so that the entire test program can be loaded in the first 64KB of memory. Also if the Memory Access Controller (MAC) is present, the bias value must be above the memory locations assigned to the MAC registers. This can be achieved by selecting a bias value larger than X'A00'. Using the Console Panel write data X'4000' into memory location X'80' and X'400C' into location X'84'.

- 5. Load the test program using the General Loader.

- 6. The test program can then be executed referring to the Operating procedures in the test program description.

7. It must be noted that only the external interrupt handling in Model 7/32 is the same as in 16 Bit processors. No other interrupts are executed the same. Therefore, if a program has any other interrupts enabled, and if one occurs, it will be handled as explained in Section 2. Since 16-bit oriented software would not have low memory locations set up for the 7/32 Old and New PSW locations, this action may change the processor mode to a fullword mode depending on the low core set up. The results are totally unpredictable in such a situation and it is recommended that the user reload the program.

| MEMORY<br>LOC | DATA  | MEANING                                      |

|---------------|-------|----------------------------------------------|

| 0030          | 0010  | Illegal Instruction Interrupt                |

| 0032          | 00F0  | New PSW (STATUS and LOC)                     |

| 0034          | 0000  |                                              |

| 0036          | 0050  |                                              |

| 0038          | 0010  | Machine Malfunction New PSW                  |

| 003A          | 00F0  |                                              |

| 003C          | 0000  |                                              |

| 003E          | 0050  |                                              |

| 0048          | 0010  | Arithmetic Fault New PSW                     |

| 004A          | 00F0  |                                              |

| 004C          | 0000  |                                              |

| 004E          | 0050  |                                              |

| 0050          | D500  | AL X'CF'                                     |

| 0052          | 00CF  |                                              |

| 0054          | 4300  | B X'80'                                      |

| 0056          | 0080  |                                              |

| 0078          | XX YY | XXYY = 0294 for a Teletype Paper Tape Reader |

|               |       | = 0399 for a High Speed Paper Tape Reader    |

|               |       | = 1399 for a High Speed Paper Reader/Punch   |

50 Sequence to load the General Loader (06-025) on Model 7/32 in the halfword mode.

Figure 5. Special 50 Sequence

## APPENDIX 1 MODEL 7/32 LEGAL OP-CODES IN FULLWORD MODE PSW BIT 11 = 0

|            | 0    | 1      | 2    | 3    | 4   | 5     | 6   | 7    | 9            | С            | D            | E     | F            |

|------------|------|--------|------|------|-----|-------|-----|------|--------------|--------------|--------------|-------|--------------|

| ۰ ۲        |      | SRLS   | втвѕ |      | STH | ST    | STE |      | SRHLS        | вхн          | STM          | TS    |              |

| ŀ          | BALR | SLLS   | BTFS |      | BAL | AM    | АНМ | STME | SLHLS        | BXLE         | LM           | svc   |              |

| 1   2      | BTCR | CHVR   | BFBS |      | втс |       |     | LME  | STBR         | *LPSW        | STB          | *SINT |              |

| ` <b> </b> | BFCR | CITYII | BFFS |      | BFC |       |     | LHL  | LBR          | THI          | LB           | *SCP  | TI           |

| 3          |      |        | LIS  | EXHR | NH  | N     | ATL | ТВТ  | EXBR         | NHI          | CLB          |       | NI           |

| 4          | NR   |        | LCS  |      | CLH | CL    | ABL | SBT  | *EPSR        | CLHI         | *AL          |       | CLI          |

| 5          | CLR  |        |      |      | ОН  | 0     | RTL | RBT  | *WBR         | оні          | *wB          | LA    | OI           |

| 6          | OR   |        | AIS  |      | XH  | ×     | RBL | CBT  | *RBR         | XHI          | *RB          | TLATE | ΧI           |

| 7          | XR   |        | SIS  |      |     |       | LE  |      | *WHR         | LHI          | *wH          |       | LI           |

| 8          | LR   | *LPSWR | LER  |      | LH  | L     |     |      | *RHR         | СНІ          | *RH          |       | CI           |

| 9          | CR   |        | CER  |      | CH  | С     | CE  |      | <del> </del> | <del> </del> | *WD          | RRL   | AI           |

| Α          | AR   |        | AER  |      | AH  | Α     | AE  |      | *WDR         | AHI          | <del> </del> |       | <del> </del> |

| В          | SR   |        | SER  |      | SH  | s     | SE  |      | *RDR         | SHI          | *RD          | RLL   | SI           |

| С          | MHR  | MR     | MER  |      | мн  | М     | ME  |      |              | SRHL         |              | SRL   | 1            |

| D          | DHR  | DR     | DER  |      | DH  | D     | DE  |      | *SSR         | SLHL         | *ss          | SLL   | ļ            |

| E          |      |        | FXR  |      |     | CRC12 |     |      | *OCR         | SRHA         | *oc          | SRA   |              |

| F          |      |        | FLR  |      |     | CRC16 |     |      |              | SLHA         |              | SLA   |              |

<sup>\*</sup> Privileged Instructions

#### APPENDIX 2 MODEL 7/32 LEGAL OP-CODES IN HALFWORD MODE (PSW BIT 11 = 1)

|   | 0    | 1 | 2    | 3 | 4   | 5 | 6   | 7 | . 8 | 9     | Α | В | С     | D    | E     | F |   |

|---|------|---|------|---|-----|---|-----|---|-----|-------|---|---|-------|------|-------|---|---|

| 0 |      |   | BTBS |   | STH |   | STE |   |     | SRLS  |   |   | вхн   | STM  |       |   | 0 |

| 1 | BALR |   | BTFS |   | BAL |   | АНМ |   |     | SLLS  |   |   | BXLE  | LM   | svc   |   | 1 |

| 2 | BTCR |   | BFBS |   | втс |   |     |   |     | STBR  |   |   | LPSW* | STB  | SINT* |   | 2 |

| 3 | BFCR |   | BFFS |   | BFC |   |     |   |     | LBR   |   |   | ТНІ   | LB   |       |   | 3 |

| 4 | NHR  |   | LIS  |   | NH  |   | ATL |   |     | EXBR  |   |   | NHI   | CLB  |       |   | 4 |

| 5 | CLHR |   | LCS  |   | CLH |   | ABL |   |     | EPSR* |   |   | CLHI  | AL*  |       |   | 5 |

| 6 | OHR  |   | AIS  |   | он  |   | RTL |   |     | WBR*  |   |   | оні   | WB*  |       |   | 6 |

| 7 | XHR  |   | SIS  |   | хн  |   | RBL |   |     | RBR*  |   |   | хні   | RB*  |       |   | 7 |

| 8 | LHR  |   | LER  |   | LH  |   | LE  |   |     | WHR*  |   |   | LHI   | WH*  |       |   | 8 |

| 9 | CHR  |   | CER  |   | СН  |   | CE  |   |     | RHR*  |   |   | СНІ   | RH*  |       | : | 9 |

| Α | AHR  |   | AER  |   | АН  |   | AE  |   |     | WDR*  |   |   | АНІ   | WD*  | RRL   |   | Α |

| В | SHR  |   | SER  |   | SH  |   | SE  |   |     | RDR*  |   |   | SHI   | RD*  | RLL   |   | В |

| С | MHR  |   | MER  |   | мн  |   | MĖ  |   |     | MHUR* |   |   | SRHL  | MHU* | SRL   |   | С |

| D | DHR  |   | DER  |   | DH  |   | DE  |   |     | SSR*  |   |   | SCHL  | SS*  | SLL   |   | D |

| E | ACHR |   |      |   | ACH |   |     |   |     | OCR*  |   |   | SRHA  | oc*  | SRA   |   | E |

| F | SCHR |   |      |   | SCH |   |     |   |     | AIR*  |   |   | SLHA  | AI*  | SLA   |   | F |

|   | 0    | 1 | 2    | 3 | 4   | 5 | 6   | 7 | 8   | 9     | Α | В | С     | D    | E     | F |   |

<sup>\*</sup> Privileged Instructions

### APPENDIX 3

#### INSTRUCTION EXECUTION TIMES

| INSTRUCTION |                    | EXECUTION<br>(FOR 750 I | erie y ve     |                      |               |                                    |

|-------------|--------------------|-------------------------|---------------|----------------------|---------------|------------------------------------|

|             | RR or SF<br>FORMAT | RI 1<br>FORMAT          | RI2<br>FORMAT | RX1 or RX2<br>FORMAT | RX3<br>FORMAT | COMMENTS                           |

|             |                    |                         |               | 3.25                 | 3.75          |                                    |

| -<br>∟R     | 1.0                |                         |               | ;                    |               | ,                                  |

| -n<br>_1    | 1.0                |                         | 2.5           |                      |               |                                    |

| -'<br>LIS   | 1.0                | 1.                      |               |                      |               |                                    |

| _CS         | 1.5                |                         |               |                      |               |                                    |

| _00<br>_H   |                    |                         |               | 2.75                 | 3.25          |                                    |

| LHI         |                    | 1.75                    |               |                      |               |                                    |

| LHS         |                    |                         |               | 3.5                  | 4.0           |                                    |

| _HL         |                    |                         |               | 2.75                 | 3.25          |                                    |

| LA          |                    |                         |               | 2.25                 | 2.75          |                                    |

| LM          |                    |                         |               | 3.5+1.5n             | 4.0+1.5n      | n=no. of registers<br>to be loaded |

| ST          |                    |                         |               | 3.5                  | 4.0           |                                    |

| STH         |                    | •                       |               | 2.5                  | 3.0           |                                    |

| STM         |                    |                         |               | 2.75+1.5n            | 3.25+1.5n     | n=no. of registers<br>to be stored |

| EXHR        | 1.0                |                         |               |                      |               |                                    |

| A           |                    |                         |               | 3.25                 | 3.75          |                                    |

| AR          | 1.0                |                         |               |                      |               |                                    |

| AI          |                    |                         | 2.5           |                      |               |                                    |

| AIS         | 1.25               |                         |               |                      |               |                                    |

| АН          |                    | 1 .                     |               | 2.75                 | 3.25          |                                    |

| AHI         |                    | 1.75                    | 1             |                      |               |                                    |

| AM          |                    |                         |               | 5                    | 5.5           |                                    |

| AHM         |                    |                         |               | 3.5                  | 4             |                                    |

| S           |                    |                         | -             | 3.25                 | 3.75          |                                    |

| SR          | 1.0                |                         |               |                      | ,             |                                    |

| Si          |                    | }                       | 2.5           |                      | *             |                                    |

| SIS         | 1.25               |                         |               |                      |               |                                    |

| SH          |                    |                         |               | 2.75                 | 3.25          | 1                                  |

| SHI         |                    | 1.75                    |               |                      |               |                                    |

| C ·         |                    | ,                       |               | 4.25/4.5             | 4.75/5        | SIGNS ALIKE/<br>SIGNS DIFFER       |

| CR          | 2.0/2.25           |                         |               |                      |               | SIGNS ALIKE/<br>SIGNS DIFFER       |

| CI          |                    |                         | 3.5/3.75      |                      |               | SIGNS ALIKE/<br>SIGNS DIFFER       |

| СН          |                    |                         |               | 3.75/4.0             | 4.25/4.5      | SIGNS ALIKE/<br>SIGNS DIFFER       |

| INSTRUCTION |                    | EXECUTION TIME IN MICROSECONDS (FOR 750 NANOSECOND MEMORY) |               |                         |                          |                              |  |  |  |

|-------------|--------------------|------------------------------------------------------------|---------------|-------------------------|--------------------------|------------------------------|--|--|--|

| INSTRUCTION | RR or SF<br>FORMAT | RI1<br>FORMAT                                              | R12<br>FORMAT | RX1 or RX2              | RX3<br>FORMAT            | COMMENTS                     |  |  |  |

| СНІ         |                    | 2.75/3.0                                                   |               |                         |                          | SIGNS ALIKE/<br>SIGNS DIFFER |  |  |  |

| CHVR        | 2.75/4.0           |                                                            |               |                         |                          | NO OVF/OVF                   |  |  |  |

| M           |                    |                                                            |               | 24.0/26/<br>26.5/25     | 24.5/26.5<br>27/25.5     | ++,+-,-+,                    |  |  |  |

| MR          | 21.75/23.75/       |                                                            |               |                         |                          | ++,+-,-+,                    |  |  |  |

| МН          | 24.25/22.75        |                                                            |               | 6.25                    | 6.75                     |                              |  |  |  |

| MHR         | 4.25               |                                                            |               |                         | ,                        |                              |  |  |  |

| D           |                    |                                                            |               | 82.5/88.25/<br>96.25    | 83/88.75/<br>96.75       | MINIMUM/AVERAGE/             |  |  |  |

| DR          | 80.25/86/94        |                                                            |               |                         |                          | MINIMUM/AVERAGE/<br>MAXIMUM  |  |  |  |

| DH          |                    |                                                            |               | 13.0/13.0<br>14.25/13.0 | 13.5/13.5/<br>14.75/13.5 | ++,+- (AVE),-+ (AVE),-       |  |  |  |

| DHR         | 11/11/12.25        |                                                            |               |                         |                          | ++,+- (AVE),-+ (AVE),-       |  |  |  |

|             | 11                 |                                                            |               |                         |                          |                              |  |  |  |

| N ·         |                    |                                                            |               | 3.25                    | 3.75                     |                              |  |  |  |

| NR          | 1.0                |                                                            |               |                         |                          |                              |  |  |  |

| NI          |                    |                                                            | 2.5           |                         |                          |                              |  |  |  |

| NH          |                    |                                                            |               | 2.75                    | 3.25                     |                              |  |  |  |

| NHI         |                    | 1.75                                                       |               |                         |                          |                              |  |  |  |

| 0           | }                  |                                                            |               | 3.25                    | 3.75                     |                              |  |  |  |

| OR          | 1.0                |                                                            |               |                         | ,                        |                              |  |  |  |

| 01          |                    |                                                            | 2.5           |                         |                          |                              |  |  |  |

| он          |                    |                                                            |               | 2.75                    | 3.25                     |                              |  |  |  |

| ОНІ         |                    | 1.75                                                       |               |                         |                          |                              |  |  |  |

| x           |                    |                                                            |               | 3.25                    | 3.75                     |                              |  |  |  |

| XR .        | 1.0                |                                                            |               |                         |                          |                              |  |  |  |

| XI .        |                    |                                                            | 2.5           |                         |                          |                              |  |  |  |

| XH          |                    |                                                            | 3             | 2.75                    | 3.25                     |                              |  |  |  |

| хні         |                    | 1.75                                                       | l             |                         |                          |                              |  |  |  |

| CL          |                    |                                                            |               | 3.25                    | 3.75                     |                              |  |  |  |

| CLR         | 1.0                | l                                                          |               |                         |                          |                              |  |  |  |

| CLI         | '                  |                                                            | 2.5           |                         | ·                        |                              |  |  |  |

| CLH         |                    |                                                            | İ             | 2.75                    | 3.25                     | *                            |  |  |  |

| CLHI        |                    | 1.75                                                       |               |                         |                          |                              |  |  |  |

| rı          |                    |                                                            | 2.5           |                         |                          |                              |  |  |  |

| THI         |                    | 1.75                                                       |               |                         |                          |                              |  |  |  |

| SRL         |                    | 3.25+[n-2]*<br>.25                                         |               |                         |                          | n=No. of SHIFTS              |  |  |  |

| INSTRUCTION |                    | <del></del>                           |               | ID MEMORY)           |               | · · · · · · · · · · · · · · · · · · · |

|-------------|--------------------|---------------------------------------|---------------|----------------------|---------------|---------------------------------------|

|             | RR or SF<br>FORMAT | RI1<br>FORMAT                         | R12<br>FORMAT | RX1 or RX2<br>FORMAT | RX3<br>FORMAT | COMMENTS                              |

| SRHLS       |                    | 1.75+[n-1]*                           |               | į                    |               | n=No. of SHIFTS                       |

|             |                    | .25                                   |               |                      |               |                                       |

| SRHL        |                    | 2.25 <del>+[</del> n-1]*<br>.25       |               |                      |               | n=No. of SHIFTS                       |

| SRLS        |                    | $2.75 + \left[\frac{n-2}{2}\right]_*$ |               |                      |               | n=No. of SHIFTS                       |

| SLL         |                    | 3.25+[n-2] *<br>.25                   |               |                      |               | n=No. of SHIFTS                       |

| SRA         |                    | $3.75 + \left[\frac{n-2}{2}\right]$   | *.25          |                      |               | n=No. of SHIFTS                       |

| SLHLS       |                    | 1.75+[n-1]*<br>.25                    |               |                      |               | n=No. of SHIFTS                       |

| SLHL        |                    | 2.25+[n-1]*<br>.25                    |               |                      |               | n=No. of SHIFTS                       |

| SLLS        |                    | 2.75+[n-2]*<br>.25                    |               |                      |               | n=No. of SHIFTS                       |

| SRHA        |                    | 2.5 <del>1[</del> n-1]*<br>.25        |               |                      |               | n=No. of SHIFTS                       |

| SLA         |                    | 3.75+\[\frac{n-2}{2}\]* .25           |               |                      |               | n=No. of SHIFTS                       |

| SLHA        |                    | 2.75+[n-1]*<br>.25                    |               |                      |               | n=No. of SHIFTS                       |

| RRL         |                    | 2.25/1.75+<br>1.0n                    | ,             |                      |               | n=0/n>0 (n=No. of SHIFTS)             |

| RLL         |                    | 2.25/1.75+<br>1.0n                    |               |                      |               | n=0/n>0 (n=No. of<br>SHIFTS)          |

| LB          |                    |                                       |               | 2.75                 | 3.25          |                                       |

| LBR         | 1.25               |                                       |               |                      |               |                                       |

| STB         |                    |                                       | ٠             | 3.25                 | 3.75          |                                       |

| STBR        | 2.0                |                                       |               |                      |               |                                       |

| EXBR        | 1.0                |                                       |               |                      |               |                                       |

| CLB         |                    |                                       |               | 3.0                  | 3.5           |                                       |

| втс         |                    |                                       |               | 2.0/2.0              | 2.0/2.5       | NO BR/BR                              |

| BTCR        | 1.5                |                                       |               |                      | ·             |                                       |

| BTFS        | 1.5/2.0            |                                       |               |                      |               | NO BR/BR                              |

| BTBS        | 1.5/2.0            |                                       |               |                      |               | NO BR/BR                              |

| вгс         |                    |                                       |               | 2.0/2.0              | 2.0/2.5       | NO BR/BR                              |

| BFCR        | 1.5                |                                       |               |                      |               |                                       |

| BFFS        | 1.5/2.0            |                                       |               |                      |               | NO BR/BR                              |

| BFBS        | 1.5/2.0            |                                       |               |                      |               | NO BR/BR                              |

| BAL         |                    | l                                     | ļ             | 2.0                  | 2.5           |                                       |

| BALR        | 1.5                |                                       |               |                      |               |                                       |

| вхн         |                    | . ]                                   |               | 4.75/4.25            | 5.25/4.75     | NO BR/BR                              |

| INSTRUCTION |                      |               | TIME IN MIC   | CROSECONDS           |                     |                                      |

|-------------|----------------------|---------------|---------------|----------------------|---------------------|--------------------------------------|

|             | RR or SF<br>FORMAT   | RI1<br>FORMAT | R12<br>FORMAT | RX1 or RX2<br>FORMAT | RX3<br>FORMAT       | COMMENTS                             |

| BXLE        |                      |               |               | 4.75/4.25            | 5.25/4.75           | NO BR/BR                             |

| ТВТ         |                      |               |               | 6.0/6.75/<br>7.5     | 6.5/7.25/<br>8.0    | MIN/AVE/MAX                          |

| SBT         |                      |               |               | 6.25/7.0/<br>7.75    | 6.75/7.5/<br>8.25   | MIN/AVE/MAX                          |

| RBT         |                      |               |               | 6.25/7.0/<br>7.75    | 6.75/7.5/<br>8.25   | MIN/AVE/MAX                          |

| СВТ         |                      |               |               | 6.25/7.0<br>7.75     | 6.75/7.5<br>8.25    | MIN/AVE/MAX                          |

| ATL         |                      |               |               | 4.75/9.0             | 5.25/9.5            | OVF/NO OVF                           |

| ABL         |                      |               |               | 4.75/9.0             | 5.25/9.5            | OVF/NO OVF                           |

| RTL         |                      |               |               | 4.75/9.75            | 5.25/10.25          | EMPTY/NOT EMPTY                      |

| RBL         |                      |               |               | 4.75/9.25            | 5.25/9.75           | EMPTY/NOT EMPTY                      |

| AE          |                      |               |               | 12/17/22.5           | 12.5/17.5/<br>23    | MIN/AVE/MAX                          |

| AER         | 11/16/21.5           |               |               |                      |                     | MIN/AVE/MAX                          |

| SE          |                      |               |               | 12.5/17.5/23         | 13/18/23.5          | MIN/AVE/MAX                          |

| SER         | 11.5/16.5/22         | 2             |               |                      |                     | MIN/AVE/MAX                          |

| CE          |                      | Ì             |               | 6.5/7.5/8.75         | 7/8/9.25            | MIN/AVE/MAX                          |

| CER         | 5.5/6.5/7.75         |               |               |                      |                     | MIN/AVE/MAX                          |

| ME          |                      |               |               | 29.25/29.5/          | 29.75/30/           | MIN/AVE/MAX                          |

|             |                      |               |               | 31.25                | 31.75               |                                      |

| MER         | 28.25/28.5/<br>30.25 |               |               |                      |                     | MIN/AVE/MAX                          |

| DE          |                      |               |               | 48.5/48.5/<br>50.25  | 49/49/<br>50.75     | MIN/AVE/MAX                          |

| DER         | 47.5/47.5/<br>49.25  |               |               |                      |                     | MIN/AVE/MAX                          |

| LE          |                      |               |               | 7.5/10.5/<br>14.25   | 8.0/11/<br>14.75    | MIN/AVE/MAX                          |

| LER         | 6.5/9.5/<br>13.25    |               |               |                      |                     | MIN/AVE/MAX                          |

| LME         |                      |               |               | 7.25+[n-1] *<br>3.0  | 7.75+[n-1] *<br>3.0 | n=No. of Float.<br>Reg. to be loaded |

| STE         |                      | Ī             |               | 5.25                 | 5.75                |                                      |

| STME        |                      |               |               | 7.5+[n-1] *<br>3.0   | 8.0+[n-1] *<br>3.0  | n=No. of Float.<br>Reg to be stored  |

| FXR         | 8/10/16              |               |               |                      |                     | MIN/AVE/MAX                          |

| FLR         | 10.5/13.75/<br>18    | 1             |               |                      |                     | MIN/AVE/MAX                          |

| LPSW        |                      |               |               | 6.0                  | 6.5                 |                                      |

| LPSWR       | 3.0                  |               |               |                      |                     |                                      |

| EPSR        | 3.25                 |               |               |                      |                     |                                      |

| SVC         | !                    | J.            |               | 6.25                 | 6.75                | l                                    |

| _INSTRUCTION |                    |                               | TIME IN MIC   | ROSECONDS            |                      |                                       |

|--------------|--------------------|-------------------------------|---------------|----------------------|----------------------|---------------------------------------|

| <u></u>      | RR or SF<br>FORMAT | RI1<br>FORMAT                 | R12<br>FORMAT | RX1 or RX2<br>FORMAT | RX3<br>FORMAT        | COMMENTS                              |

| AL           |                    |                               |               | 8.75+2.5 L+<br>2.75n | 9.25+2.5 L<br>+2.75n | L=Leader Bytes;<br>n=data bytes       |

| SINT         |                    | 1.0+Interrup<br>processing ti |               |                      |                      |                                       |

| RD           |                    |                               |               | 3.75                 | 4.25                 |                                       |

| RDR          | 2.25               |                               |               | <u> </u><br>         |                      |                                       |

| RH           |                    |                               |               | 4.75/4.0             | 5.25/4.5             | Byte Dev/Halfword Dev                 |

| RHR          | 3.0/2.25           |                               |               |                      | ]                    | Byte Dev/Halfword Dev                 |

| RB           |                    |                               |               | 6.75+2.75n           | 7.25+2.75n           | n=No. of Bytes                        |

| RBR          | 4.75+2.75n         |                               |               |                      |                      | n=No. of Bytes                        |

| WD           |                    |                               |               | 3.75                 | 4.25                 |                                       |

| WDR          | 2.25               |                               |               |                      |                      |                                       |

| WH           | Ì                  |                               |               | 4.25/3.5             | 4.75/4.0             | Byte Dev/Halfword Dev                 |

| WHR          | 3.25/2.5           |                               | ļ.            |                      |                      | Byte Dev/Halfword Dev                 |

| WB           | 1                  |                               |               | 6.25+3.0n            | 6.75+3.0n            | n=No. of Bytes                        |

| WBR          | 4.25+3.0n          |                               |               |                      |                      | n=No. of Bytes                        |

| SS           |                    |                               |               | 4.0                  | 4.5                  |                                       |

| SSR          | 3.0                |                               |               |                      | :                    |                                       |

| ос           |                    |                               |               | 4.0                  | 4.5                  |                                       |

| OCR          | 2.25               |                               |               |                      |                      |                                       |

| CRC12        |                    |                               |               | 11.5/13.25/<br>15    | 12/13.75/<br>15.5    | MIN/AVE/MAX                           |

| CRC16        |                    | •                             |               | 13/15.25/<br>17.5    | 13.5/15.75<br>18     | MIN/AVE/MAX                           |

| TLATE        | !<br>!             |                               |               | 4.5/5.25             | 5.0/5.75             | Translation/<br>Special Char.         |

| SCP          | ·                  |                               |               | 5.5/9.25/            | 6.0/9.75             | Byte Count > 0/<br>Inc. Byte Count    |

|              | !                  |                               |               | 9.75/11.0            | 10.25/11.5           | Incr. Byte Count ≤ 0<br>(Fast Mode)/  |

|              |                    |                               |               |                      |                      | Incr. Byte Count > 0<br>(Normal Mode) |

NOTE: [n-1] is zero if n = 0

$\begin{bmatrix} \frac{n-2}{2} \end{bmatrix} \text{ is maximum positive integer} \\ \text{value less than or equal to } \frac{n-2}{2}$

(for n = 1,2,or 3  $\left[\frac{n-2}{2}\right]$  = 0)

#### AUTO DRIVER CHANNEL EXECUTION TIMES (IN MICROSECONDS)

FAST MODE (F BIT = 1)

| FUNCTION                 | EXE-<br>CUTE<br>BIT<br>RESET | BAD<br>DEVICE<br>STATUS | BUFFER<br>BYTE<br>COUNT IS<br>> 0 | INCR.<br>BUFFER<br>BYTE COUN<br>IS NOT >0 | INCR. BUFFER BYTE CT. IS > 0 |

|--------------------------|------------------------------|-------------------------|-----------------------------------|-------------------------------------------|------------------------------|

| READ (BYTE DEV.)         | 9.5                          | 10.75                   | 12.0                              | 15.75                                     | 16.0                         |

| READ (HALFWORD           | 9.5                          | 10.75                   | 12.0                              | 16.5                                      | 16.75                        |

| WRITE (BYTE DEV.)        | 9.5                          | 10.75                   | 12.0                              | 15.75                                     | 16.0                         |

| WRITE (HALFWORD<br>DEV.) | 9.5                          | 10.75                   | 12.0                              | 17.0                                      | 17.25                        |

#### NORMAL MODE (F BIT = 0)

| FUNCTION                        | EXECUTE<br>BIT<br>RESET | BAD<br>DEVICE<br>STATUS | BUFFER<br>BYTE<br>COUNT<br>> 0 | INCR. BUFFER BYTE COUNT IS NOT>0 | INCR. BUFFER BYTE COUNT > 0 | NOTES |