## MODEL 7/32 PROCESSOR USER'S MANUAL

Subsidiary of PERKIN-ELMER Oceanport, New Jersey 07757, U.S.A.

© INTERDATA INC., 1976 All Rights Reserved Printed in U.S.A. May 1976

## PAGE REVISION STATUS SHEET

PUBLICATION NUMBER 29-405

TITLE 7/32 PROCESSOR USER'S MANUAL

REVISION ROO

DATE 6/76

| PAGE                  | REV.  | DATE | PAGE                 | REV. | DATE | PAGE | REV. | DATE |

|-----------------------|-------|------|----------------------|------|------|------|------|------|

| 1-1<br>Thru<br>1-18   | R00   | 6/76 | A2-1<br>Thru<br>A2-4 | R00  | 6/76 |      |      |      |

| 2-1<br>Thru<br>2-52   | R00   | 6/76 | A3-1<br>Thru<br>A3-6 | R00  | 6/76 |      |      |      |

| 3-1<br>Thru<br>3-24   | R00   | 6/76 | A4-1<br>Thru<br>A4-2 | R00  | 6/76 |      |      |      |

| 4-1<br>Thru<br>4-24   | R00   | 6/76 | A5-1<br>Thru<br>A5-6 | R00  | 6/76 |      |      |      |

| 5-1<br>Thru<br>5-36   | R00   | 6/76 | A6-1<br>Thru<br>A6-8 | R00  | 6/76 |      |      |      |

| 6-1<br>Thru<br>6-16   | R00 . | 6/76 | A7-1<br>Thru<br>A7-4 | R00  | 6/76 |      |      |      |

| 7-1<br>Thru<br>7-26   | R00   | 6/76 |                      |      |      |      |      |      |

| 8-1<br>Thru<br>8-8    | R00   | 6/76 |                      |      |      |      |      |      |

| 9-1<br>Thru<br>9-10   | R00   | 6/76 |                      |      |      |      | ·    |      |

| 10-1<br>Thru<br>10-12 | R00   | 6/76 |                      |      | ,    |      | -    |      |

| Al-1<br>Thru<br>Al-2  | R00   | 6/76 |                      |      |      |      |      |      |

|                       |       |      |                      |      |      |      |      |      |

## TABLE OF CONTENTS

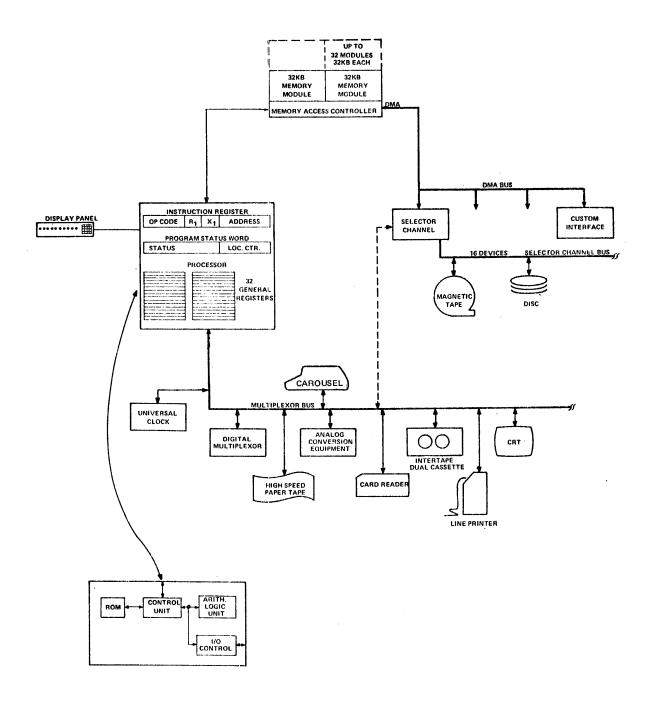

| CHAPTER 1 SY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | STEM DESCRIPTION.       |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------|-----------|-------|------|-----|-------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|-----|-------|------|

| PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         | ·           |           |       |      |     | ٠.    |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-4  |

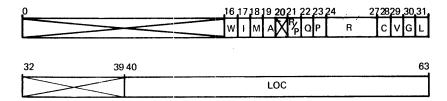

| Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ım Status Word          |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-4  |

| Gener                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | al Register             |             |           |       |      |     |       |       |     |     |     |     | . : |     |     |     |     |   |     |       | 1.6  |

| Floati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ng Point Register       |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-6  |

| Proces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ssor Interrupts         |             |           |       | ٠    |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1.6  |

| Resear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ved Memory Locations    |             |           |       |      |     |       |       |     |     | •   |     | • • | • • | •   | •   | •   | • | • • | • •   | 1.6  |

| Proces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ssor Operations         |             |           |       |      |     |       |       |     | : : | : : |     |     |     | •   |     |     |   |     |       | 1-7  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rs                      |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       |      |

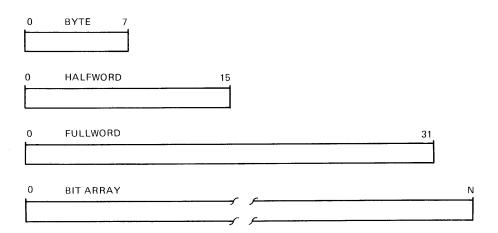

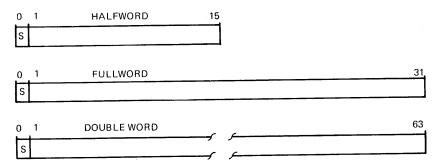

| Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Point Data              |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-7  |

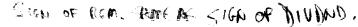

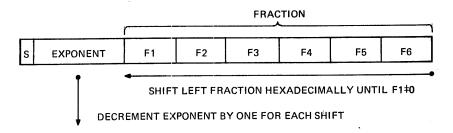

| Floati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ng Point Data           |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-7  |

| Logica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | d Data                  |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-8  |

| THE THE PERSON IN THE PERSON I | EODM ATIG               |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       |      |

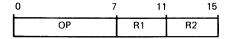

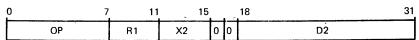

| INSTRUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FORMATS                 |             |           |       | • •  | • • |       | • •   | • • |     | • • | • • | • • |     | •   | •   |     | • |     |       | 1-8  |

| Branc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | h Instruction Formats   |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 1-9  |

| Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | imming Note             |             |           |       |      |     |       |       |     |     | • • | • • |     |     | •   | •   |     | - |     | • •   | 1-9  |

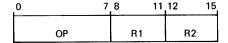

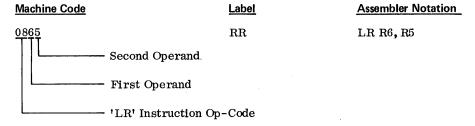

| Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er to Register (RR) For | mat         |           |       | • •  | • • |       | • • • |     | • • |     |     | • • | • • | •   | •   |     | ٠ | ٠.  |       | 1.0  |

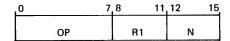

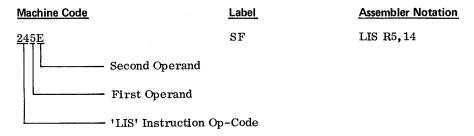

| Short                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Form (SF) Format .      |             |           |       | • •  | • • |       | • •   | • • |     |     |     | • • |     | • • | •   | • • | • |     | • •   | 1.0  |

| Doning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er and Indexed Storage  | <br>Ωπο (D) | <br>(1) E |       |      | • • |       | • •   |     | • • | • • | • • | • • |     | •   | •   |     | • | • • | • •   | 1-7  |

| Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er and indexed Storage  | One (R)     | X1) F     | ormat | • •  | • • |       | • •   | • • | • • | • • |     | • • |     | •   |     | • • | • |     | . 1   | -11  |

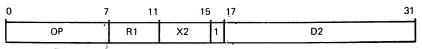

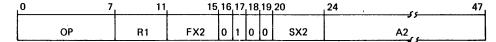

| Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er and Indexed Storage  | TWO (R.     | X2) F     | ormat | •    | • • |       |       |     |     |     |     |     |     |     |     |     | • |     | . 1   | -12  |

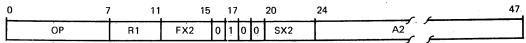

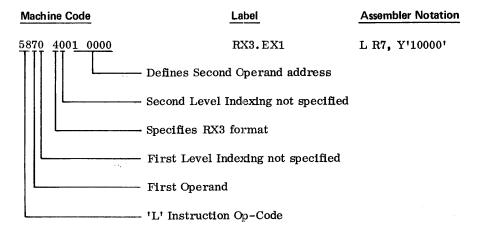

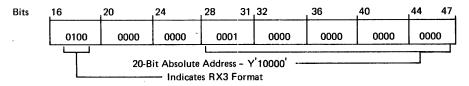

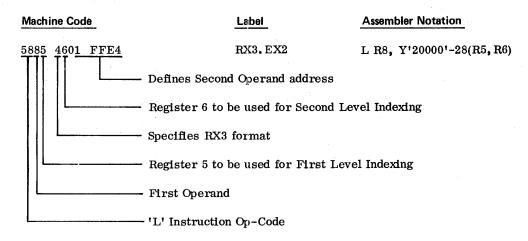

| Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er and Indexed Storage  | Three (F    | (XX       | Forma | at . |     |       |       |     |     |     |     |     |     |     |     |     |   |     | . 1   | -14  |

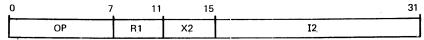

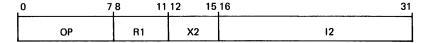

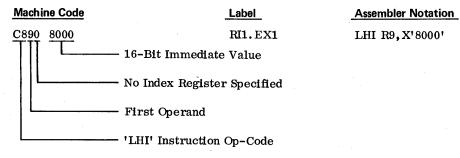

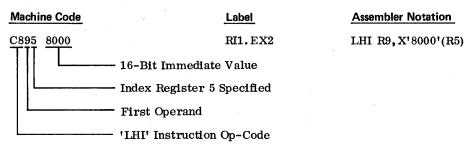

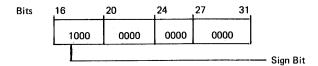

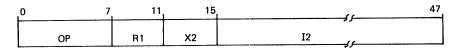

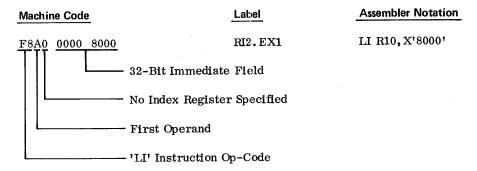

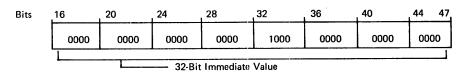

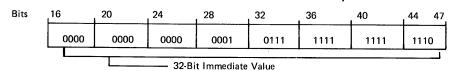

| Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er and Immediate Stora  | ge One (    | RI1)      | Forma | at . |     |       |       |     |     |     |     |     |     |     |     |     |   |     | . 1   | -15  |

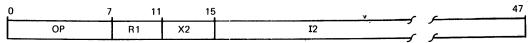

| Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er and Immediate Stora  | ge Two (    | (RI2)     | Form  | at . |     |       |       |     |     |     |     |     |     |     |     |     |   |     | . 1   | -16  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                       |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       |      |

| CHAPTER 2 LO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GICAL OPERATIONS        |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 2-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       |      |

| DATA FORMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rs                      |             |           |       |      |     |       |       |     |     |     |     |     |     | • : |     |     |   |     |       | 2-1  |

| OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 2-2  |

| • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       |      |

| Boolea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | an Operations           |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 2-2  |

| Transl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ation                   |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       | 2-2  |

| List P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rocessing               |             |           |       |      |     |       |       |     |     |     |     |     |     |     | , . |     |   |     |       | 2-3  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |             |           |       |      |     |       |       |     |     |     |     |     |     |     |     |     |   |     |       |      |