# PART I TUTORIAL

# **CONTENTS**

| PR | E | F | A | C | E |

|----|---|---|---|---|---|

|----|---|---|---|---|---|

CHAPTER 1 INTRODUCTION

CHAPTER 2 WRITING THE DRIVER

CHAPTER 3 INCLUDING THE DRIVER IN YOUR OPERATING SYSTEM

CHAPTER 4 SAMPLE DRIVERS

CHAPTER 5 ADVANCED DRIVER CONCEPTS

APPENDIX A REVIEW OF ASSEMBLY LANGUAGE INPUT/OUTPUT (I/O) COMMANDS

APPENDIX B DEBUG TECHNIQUES

APPENDIX C CRASH CODE ANALYSIS

# **PREFACE**

Part I of the Guide to Writing OS/32 Driver's Manual is a tutorial for writing basic drivers, with the last chapter devoted to more advanced concepts. Chapter 1 is a review of basic terminology and concepts. Chapter 2 covers the essentials for writing driver code and Chapter 3 gives complete information for including a driver in the operating system. Two sample drivers are provided in Chapter 4, a simple digital input/output (DIO) interface and a complex TELEX tridensity magnetic tape driver. Chapter 5 introduces advanced concepts in drivers. These include the translation table, nonphysical device drivers and supervisor call 6 (SVC6) and trap generating device drivers.

# CHAPTER 1

# INTRODUCTION

| 1.1 | BASIC CONCEPTS                                      | 1  |

|-----|-----------------------------------------------------|----|

| 1.2 | TERMINOLOGY                                         | 2  |

| 1.3 | COMPONENTS OF A DEVICE DRIVER                       | 3  |

| 1.4 | OS/32 DRIVER INTERFACE ROUTINES                     | 6  |

| 1.5 | DRIVER COMMUNICATION WITH THE TOTAL COMPUTER SYSTEM | 8  |

| 1.6 | A SPECIAL NOTE ON DEVICE TIME-OUTS                  | 11 |

# LIST OF FIGURES

Figure 1-1. The Customized Driver as Interface

1

#### CHAPTER 1

#### INTRODUCTION

# 1.1 BASIC CONCEPTS

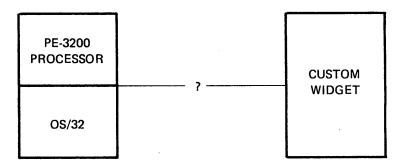

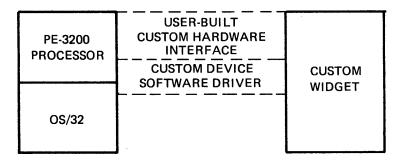

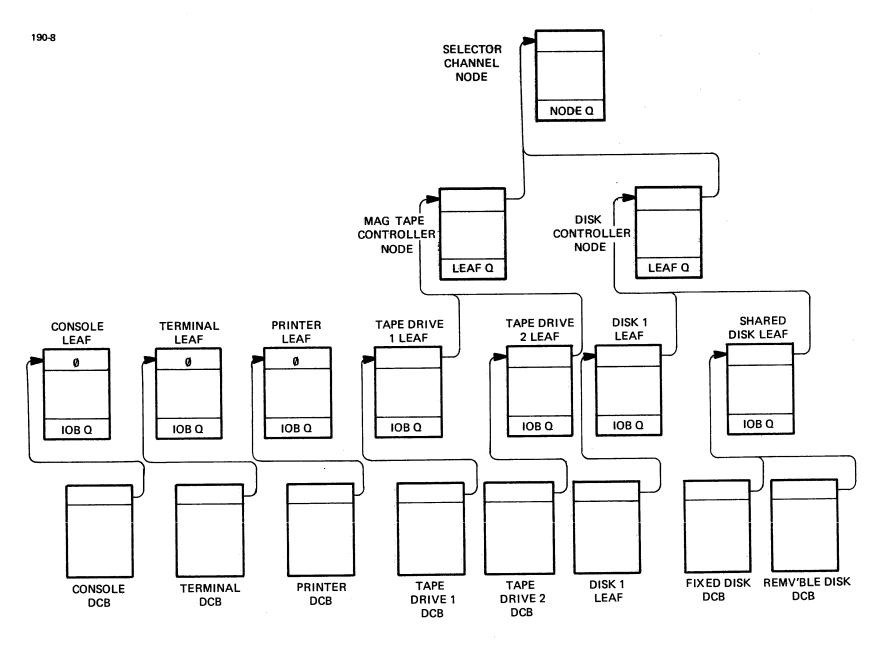

When a new user installs Perkin-Elmer's 0S/32, it is often necessary to connect the operating system to the user's equipment and peripherals via a customized driver. Figure 1-1 demonstrates this situation.

190-3

#### PROBLEM:

#### SOLUTION:

Figure 1-1. The Customized Driver as Interface

The Perkin-Elmer input/output (I/O) driver performs I/O to the device at the hardware level, such that user programs merely issue reads and writes, thus making the command sequences for each type of device transparent to the user. FORTRAN and other high-level languages use READ and WRITE statements which are translated into supervisor call 1 (SVC1) instructions by their respective compilers. The operating system then executes the SVC1 which calls the device driver to do the I/O to the requested device.

How does the system get into the I/O driver?

**EXAMPLE: A FORTRAN program**

READ(1,900) IX

is translated by the compiler into:

SVC 1, PBLK (assembly code)

which is then assembled into object code:

E110 xxxx

The E1 is the op code for an SVC which causes the OS to initiate the I/O.

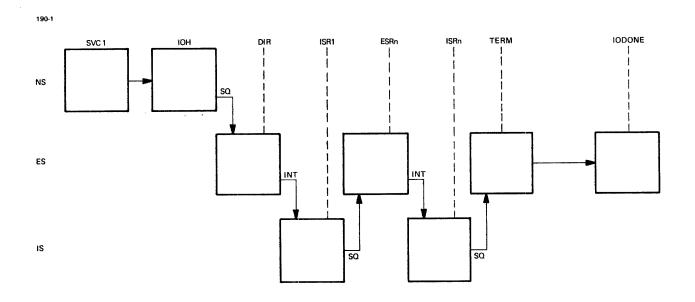

For those of you who are interested, the operating system processes the SVC instruction in module EXIN (set up in low memory to handle microcoded vectors from the SVC instruction). EXIN passes the I/O request (SVC1) to module EXIO which handles pre and postprocessing of the I/O. EXIO validates the request, dispatches the driver and processes I/O termination as in the following:

#### 1.2 TERMINOLOGY

For the user who is unfamiliar with Perkin-Elmer terminology, those terms required for use of this manual are given here. The order in which these terms are presented correspond to the structural level within the software at which they are encountered.

- User task (u-task): a complete applications job, typically written in a high-level language such as FORTRAN, COBOL and Pascal. A u-task can be written in Common Assembly Language/32 (CAL/32), although the existence of powerful optimizing compilers greatly reduces the requirements for u-tasks written in CAL/32. A u-task performs a useful applications function.

- SVC1: an SVC code 1 is a single machine-level instruction that can be issued by a u-task to initiate an I/O operation. All Series 3200 Processors provide this instruction. Typically, the SVC1 instruction is issued by a user-callable subroutine or by code compiled as the result of high-level language statements being processed into machine code by a compiler. Typically, the user is not explicitly aware of the SVC1 instruction. The user simply issues reads and writes.

- SVC1 parameter block: the SVC1 instruction references a six-fullword (24 byte) block which defines the I/O operation and is interpreted by the OS/32 I/O subsystem. The definition of the SVC1 parameter block does not necessarily concern the writer of a device driver. If

1-2 48-190 F00 R00

the driver performs device-dependent functions, then the SVC1 parameter block can be partially redefined by the device driver.

- Device control block (DCB): This is the principle structure with which the writer of a device driver must be concerned. The DCB provides all of the parameters required to define the device to both the device driver and to the OS/32 I/O subsystem software. The DCB consists of a device-independent and a device-dependent segment. The device-independent segment is defined in the same manner for all devices. A device driver can reference data in this area, but in general can alter only a few specific items, since it is reserved for the OS/32 I/O subsystem. The device-dependent segment can be defined differently for each type of device and can be of arbitrary size. There is exactly one, and only one, DCB for each device configured in a system. For example, a system with four CRTs and a disk drive contains five DCBs.

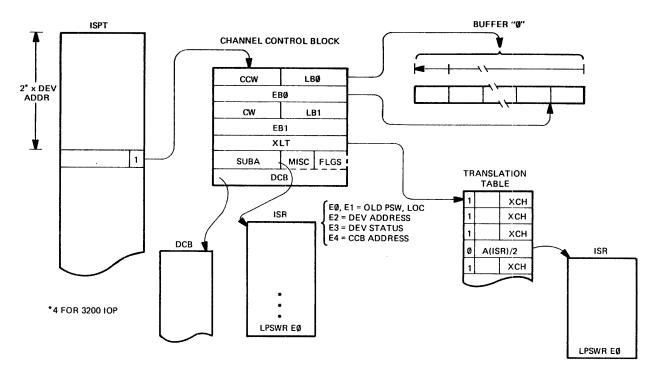

- Channel control block (CCB): This is a small control block defined by the interrupt service features implemented in the microcode of the Series 3200 Processors. An additional area of the CCB has been defined by OS/32 for use by device drivers. The CCB is the mechanism available to the device driver for passing control and device information to the interrupt service routines in the device driver.

- Device driver: A software module consisting of both a definition of the DCB for a specific type of device, and various sections of executable code required to actually control the device, communicate with the OS/32 I/O subsystem, and service device interrupts in a manner consistent with the Series 3200 Processor interrupt service scheme. In addition to the DCB, a device driver written to control any interface consists of a CCB, a driver initialization routine (DIR), one or more interrupt service routines (ISRs) and one or more event service routines (ESRs). Several other routines, specified by the I/O handler list (IOH) are options.

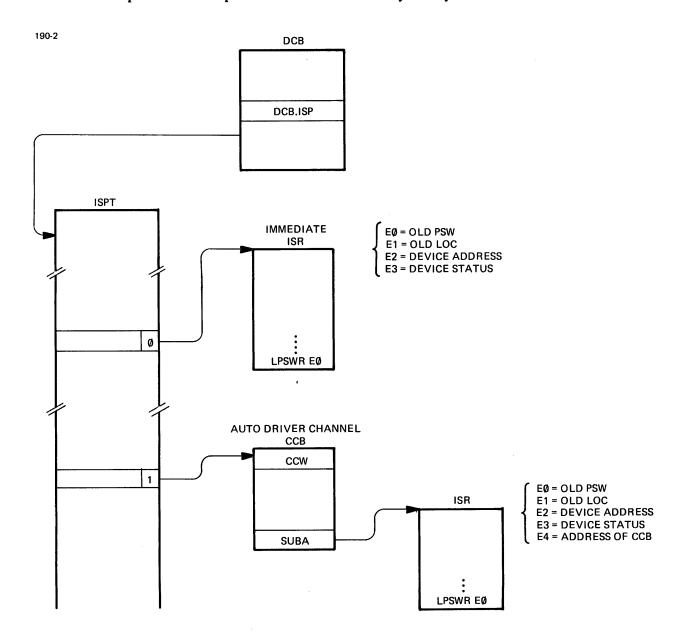

- Interrupt service pointer table (ISPT): An ordered list containing one entry for each possible device address in the system. This table starts at memory location X'D0' with each entry occupying one halfword. It is the responsibility of the software controlling the I/O (the device driver) to set up this table with the address of the immediate ISR or the address of the CCB+1 for auto driver channel operation.

- Auto driver channel: A microcode routine which is entered whenever the halfword entry in the ISPT is odd. This routine interprets the address in the ISPT as the address of a CCB plus one. The CCB consists of a description of the operation to be performed, and a list of parameters associated with the operation.

## 1.3 COMPONENTS OF A DEVICE DRIVER

A device driver is divided into major components that carry out all necessary functions. The most important functions are described in the following list.

# • Driver initialization routine (DIR):

The DIR is the first section of code executed in a device driver. Generally, it performs certain bookkeeping functions and the initial communication to the device hardware interface to set up the I/O operation. The I/O subsystem uses register set 5 for driver initialization service. The user does not have to worry about saving and restoring registers upon entry and exit from driver initialization routines. The writer of an I/O driver can use 15 of the 16 registers of set 5. Register D, which contains the DCB address, must not be destroyed. Routines in EXIO require that this register contain the DCB address after exit from the driver.

## • Interrupt service routine (ISR):

ISRs service the hardware interrupts from the device interface. Generally, the ISR performs the minimum amount of control required to maintain the progress of the I/O operation and to determine when the operation is complete. When coding an ISR, certain register conventions must be upheld to insure the integrity of the system. The operating system expects registers 8-F of set 0 to be untouched by the driver. Therefore, the writer of an ISR should use only registers 0-7 of set 0. The register set selected (0,1,2, or 3) depends upon the hardware configuration. Normally, this would be set 0. If other than 0, in addition to backplane wiring, Sysgen32 or cupmt must also reflect the interrupt level in the device specifications.

#### NOTE

If set 1, 2, or 3 is used, of course, all registers would be available for ISR use; however, for compatibility, it is strongly suggested that only 0-7 be used.

When an ISR is entered, the microcode sets the program status word (PSW) to X'2800', which enables all higher level interrupts and machine malfunction interrupts. If it is necessary to start two or more devices at the same time, it is usually necessary to disable all interrupts if your interrupt level is 1, 2 or 3. This prevents higher level interrupts from disrupting the appropriate sequencing of operations. The PSW to disable all interrupts, leaving machine malfunction enabled is X'2000'.

#### • Event service routine (ESR):

ESRs provide termination functions, such as shutting down the device, issuing retries where appropriate and doing various bookkeeping functions for the OS/32 I/O subsystem.

## • The I/O handler (IOH):

An IOH is an ordered parameter list which defines the appropriate processing routines for various I/O functions. The list is defined by the \$IOH macro. Special routines for initialization, end of task, as well as device-dependent functions can be defined via an IOH.

1-4 48-190 F00 R00

These IOH routines are called by various modules within the operating system. EXIO checks for read, write and command function IOH entries. EXIN checks for the presence of an initialization IOH during the SYSINIT routine. If an INIT IOH has been specified, EXIN does a branch and link to the routine. EXSV, during end of task processing, checks for the presence of an EOT IOH. If this routine exists, EXSV does a branch and link to the routine.

The following is a sample of the way the IOH macro is used within a device driver. Since this is a macro, column 72 must contain a continuation character, and each item except the last is followed by a comma.

| IOH | NAME=MMDIOH,   | 1 |

|-----|----------------|---|

|     | READ=BARERD,   | 1 |

|     | WRITE=BAREWR,  | 1 |

|     | AIT=SVC1WAIT,  | 1 |

|     | TEST=SVC1TEST, | 1 |

|     | SET=BARERD,    | 1 |

|     | HALT=SVC1NOOP, | 1 |

|     | REW=SVC1NOOP,  | 1 |

|     | BSR=SVC1NOOP,  | 1 |

|     | FSR=SVC1NOOP,  | 1 |

|     | FFM=SVC1NOOP,  | 1 |

|     | BFM=SVC1NOOP,  | 1 |

|     | INIT=INIT.MMD, | 1 |

|     | WFM=SVC1NOOP   |   |

Some of the entries in the IOH list are as follows:

# INIT:

If a device requires some special setup at system initialization time, the INIT parameter can be used to specify the name of the routine to be executed. The sysinit code in EXIN branches and links to this routine. An example of such processing would be the initialization of a driver's internal table.

Evi+.

Register Conventions:

Entru

| Eller y:          | EXIC:                      |

|-------------------|----------------------------|

| R8 return address | R8return address           |

| R11DCB address    | R11DCB address             |

|                   | All other registers can be |

|                   | destroyed.                 |

#### EOT:

If a driver must perform special cleanup operations when a task terminates, then the EOT parameter must be specified. At EOT time, the SVC3 process or (module EXSV) checks for an EOT handler for each logical unit (lu). The drawback to this cleanup method is that if the logical units are already closed, then no cleanup is done, since there is no close IOH.

Register Conventions:

| Entry:              | Exit:                     |

|---------------------|---------------------------|

| R8return address    | R8 address                |

| R9TCB of task going | R9TCB of task going       |

| to end of task      | to end of task            |

| R10DCB address      | R10DCB address            |

|                     | All other register can be |

|                     | destroyed.                |

## • DDF:

A device-dependent function is a routine that is to be executed for a particular device. The function code for all device-dependent functions is X'81'; however, each device driver defines this code in a manner specific to each device. See Chapter 4 for more information on mag tape drivers.

#### 1.4 OS/32 DRIVER INTERFACE ROUTINES

The writer of an I/O driver needs only to know when and how to call OS/32 routines. There is no need to be intimately familiar with the details of the operating system interface routines.

DIRDONE - a routine called at the end of a DIR. This routine sets DCB.ESR with a default termination handler. (Register D must contain the address of the DCB.)

# B DIRDONE

IODONE - a routine called at the end of ESR. This routine places the status in the SVC1 parameter block (if any), sets a requested task trap, removes the task from an I/O wait and disconnects the leaf from the tree. (Register D must contain the address of the DCB.)

#### B IODONE

EVRTE - a routine which is called after a driver has modified the address of the termination routine. This routine is called in place of DIRDONE. (Register D must contain the address of the DCB.)

B EVRTE

EVMOD - a routine in module EXIO to set another entry as the ESR address (modifies DCB.ESR). For current revisions of the operating system, some system overhead can be eliminated by performing this function directly:

LA UE, TERMXXX1

OI UE, Y'80000000' set ind:

set indicator like EVMOD does

ST UE, DCB.ESR (UD)

In most cases, it is recommended that this subroutine convention be used, so that the driver is compatible with future revisions of OS/32. (Register D must contain the address of the DCB.)

LA UE, TERMXXX1 set new term address

BAL U8, EVMOD

EVREL - a routine to release resources such as controllers and selector channels (SELCHs) acquired by a driver.

LIS UE, 3 release at SELCH level

L UF, DCB.LEAF (UD)

BAL U8.EVREL

TOCHON - a timer routine that is called, usually before a SINT instruction, to enable the system to return a time-out condition if a device does not respond within a given period of time. (Register D must contain the address of the DCB.)

BAL U8, TOCHON

TOCHOFF - a timer routine that is called, after the driver has finished its work, to remove a given device from the time-out chain. (Register D must contain the address of the DCB.)

BAL U8, TOCHOFF

III - an entry point in module EXTI. This routine is the null interrupt routine which performs an LPSWR. The address of III is stored in the ISPT when the system is to perform no action upon a device interrupt.

LA E7,III

STH E7, ISPTAB (E2, E2)

SQ - the address of the system queue. This structure is used by a driver ISR to schedule driver termination.

L E6, DCB.LEAF (E5)

ATL E6,SQ

The above routines are the major interfaces between a device driver and OS/32.

Associated subroutine file: SUBS.MAC - contains commonly used subroutines for driver use. For efficiency, since many of these routines are only one or two lines of code, it is recommended that the code be placed in-line (especially for interrupt service coding).

# 1.5 DRIVER COMMUNICATION WITH THE TOTAL COMPUTER SYSTEM

The DCB is the principle means by which a device driver communicates with the rest if the system. Most of the DCB fields are used by various other components of the system to define the environment or a specific operation to the driver; a few DCB fields are used by the driver to report the results of an operation to the remainder of the system. In certain situations, specific registers are used to communicate between the driver and the operating system or processor firmware.

The following system components communicate with a device driver:

- 1. The user, who issues an SVC1 instruction.

- 2. The operating system, which provides several services.

- 3. The user, who defines the system through system generation (sysgen) parameters.

- 4. The sysgen process, which allocates data structure areas.

- 5. The processor firmware, which responds to interrupts.

- 6. The writer of the driver, who defines values in the DCB.

The writer of a driver must be aware of how each one of these system components communicates with the device driver.

The user of the system issues an SVC1 instruction to initiate an I/O operation. The associated SVC1 parameter block defines the operation to be done and receives some information on the results of the operation. The communication between the user and the driver is carried out by the operating system. The situation is equivalent to two people carrying on a phone conversation: each person accesses his own telephone set; the telephone company's equipment moves the signals between the two telephone sets.

```

The USER accesses

an SVC1 parameter

block:

SVC1.FC ------ I/O function code -----> DCB.FC

SVC1.LU ------- lu number -----> DCB.LU

SVC1.STA <---- operation result status ----- DCB.STAT

SVC1.SAD ------ I/O buffer start address ---> DCB.SADR

SVC1.EAD ------ I/O buffer end address ----> DCB.EADR

SVC1.RAD ------- "random address" -----> DCB.RAND

SVC1.LXF <------ length of transfer ------> DCB.LXF

SVC1.XOP ------- (user-defined) ------> DCB.SV1X

```

1-8

In addition to moving operation parameters between the DCB and the user's SVC1 parameter block, the operating system is responsible for starting the execution of various sections of the driver, being sure that the driver does not take too much time to complete the operation and informing the driver as to which device the operation is to be directed to.

```

The Driver:

The Operating

System:

Register 13 ----- address of DCB ----> Register 13

address of the

DCB.ESR <----- next event service ----- DCB.ESR

routine to execute

DCB.TOUT <----> time-out value ----> DCB.TOUT

SQ <---- event tree leaf address ----- DCB.LEAF

(schedules ESR execution)

address of the

DCB.UPBK -----> user's SVC1 block ----> DCB.UPBK

as seen by the

user

address of the

DCB.PBLK -----> DCB.PBLK

as seen by the

driver

address of the

DCB.TCB ----- task control block -----> DCB.TCB

for the user

```

Note that since register 13 always points to the DCB, it is important that the driver never modify it. The DCB.TOUT field is used by all drivers. The DCB.ESR field is occasionally used. The fields DCB.UPBK, DCB.PBLK and DCB.TCB are almost never needed by a device driver. These fields are listed here only because a few special circumstances require them.

The user (perhaps unknowingly) defines some parameters through the specifications written in a sysgen file. For example, the user writes the statement:

D300: FE, 54, SELCH=FO, CONTR=FB

This is mapped to the DCB as follows:

```

"FE" -----> DCB.DN

"54" -----> device type code -----> DCB.DCOD

"SELCH=FO" --- SELCH address ----> DCB.SDN

"CONTR=FB" --- controller address ----> DCB.CDN

```

For another example, the user writes:

```

MD5E:, 5E, 39, XDC=X0810, RECL=132

```

This is mapped to the DCB as follows:

```

"5E" ------ device address ------> DCB.DN

"39" ------ device type code -----> DCB.DCOD

"XDC=X0810" --- user-defined -----> DCB.XDCD

"RECL=132" --- device record length ---> DCB.RECL

```

When the sysgen procedure is run, various data structure areas (such as the DCB) are assigned physical locations within the operating system. It is necessary that these data structures contain pointers to other data structures within the system, so that the various operating system routines can find their way around. For example, a device driver must be able to locate the DCB if it knows only the location of the CCB. The operating system must be able to locate the start of the device driver if it knows only the location of the DCB. Since these pointers are set up at sysgen time, they are static and must never be modified by the driver. Some of these pointers are:

```

Sysgen procedure Driver

DCB.CCB ----- address of CCB -----> DCB.CCB

CCB.DCB ----- address of DCB -----> CCB.DCB

DCB.LEAF --- event tree leaf address -> DCB.LEAF

```

Some entries in the DCB are used primarily by the operating system to locate various routines within the driver. These fields are set up at sysgen time, and are not modified by the driver. These fields include:

```

DCB.INIT ---- address of driver's -----> DCB.INIT

initialization routine

DCB.TERM ---- address of driver's -----> DCB.TERM

termination routine

address of driver's

DCB.FUNC ---- command function ------> DCB.FUNC

processing routine

```

A device driver must also communicate directly with the processor firmware routines that process interrupts. The driver must tell the processor what ISR is to be executed to process the next interrupt from the device. The processor must in turn tell the ISR what device interrupted and where the associated CCB is located. Also, the processor provides the ISR with the proper PSW and location counter with which to exit from interrupt service. The communication between the processor and the driver is as follows:

```

Processor hardware Device and firmware driver:

ISPTAB <----- address of CCB ------- DCB.CCB

CCB.SUBA <---- address of ISR to execute -- "LA" instruction hardware -- address of interrupting device -> register 2 hardware -- status of interrupting device --> register 3 microcode --- address of CCB -------> register 4 microcode --- PSW at time of interrupt ----> register 0 microcode --- LOC at time of interrupt ----> register 1

```

#### 1.6 A SPECIAL NOTE ON DEVICE TIME-OUTS

OS/32 uses the line frequency clock (LFC) (which interrupts 120 times per second) to maintain the device time-out mechanism. Every second, the system decrements the time-out constant for each device by one. If the time-out constant is X'7FFF', the device cannot be timed out. When a driver's interrupt service has gone to completion, the time-out constant should be set to -1 (X'FFFF') to indicate that a time-out did not occur. If the time-out constant decrements to zero, the device did not respond in the specified length of time and the driver should set an X'8282' status, to indicate time-out.

The timer management routine which controls the device time-out mechanism is the OS/32 module EXTI in routine TIMCH3. If this routine finds X'7FFF', 0, or a negative value in DCB.TOUT, it processes the next device on the time-out chain. The value in DCB.TOUT is decremented by one and if the value is now zero, the device has timed out. If this time-out condition occurs, EXTI adds the device leaf to the system queue for termination processing.

Drivers should always check for time-out before adding a leaf to the system queue. Crash code 153 may result if a leaf is added to the system queue twice. A safety check mechanism in EXIO prevents the item from being added twice (if the system is generated with safety checks enabled).

# CHAPTER 2

# WRITING THE DRIVER

| 2.1 | INTRODUCTION                                       | 1  |

|-----|----------------------------------------------------|----|

| 2.2 | WRITING DRIVER CODE                                | 1  |

| 2.3 | WRITING DEVICE CONTROL BLOCK/CHANNEL CONTROL BLOCK |    |

|     | (DCB/CCB) SPECIFICATIONS                           | 21 |

#### **CHAPTER 2**

#### WRITING THE DRIVER

#### 2.1 INTRODUCTION

The previous chapter outlined the basic components required to write a device driver. These basic components included the device control block (DCB) relationships, the input/output (I/O) subsystems relationships and the specific routines required within the device driver. With this conceptual background, the user can now address the essential question, "How do I write the code?"

## 2.2 WRITING DRIVER CODE

The best way to begin a discussion of writing driver code is to begin with an anyalysis of some simple examples. The following examples show very basic drivers.

## Step 1: The Simplest Case

The following is the simplest possible routine that satisfies the basic operating system interface requirement for a driver. This driver performs only the function of branching back to the operating system. The termination routine is never executed, since the initialization routine branches to the I/O operation complete routine in the operating system.

The last instruction executed by a driver must be a branch to IODONE, which is an entry point to the operating system. This is the only way that a driver can indicate to the operating system that the I/O operation is complete. The operating system enters the driver at the label INITDVR1. This label is specified in the DCB. Standard Perkin-Elmer convention requires that the first four characters be INIT.

```

INITDVR1 B IODONE branches back to the operating system *

TERMDRV1 EQU * this will never be executed but must be here because it must be specified in the DCB.

END

```

Step 2: Scheduling Event Service Routine (ESR)

To schedule an ESR routine, add the contents of the DCB.LEAF field to the system queue. This can be done anywhere in the driver, but normally is done only in an interrupt service routine (ISR), as is illustrated later. Since this driver only has one ESR routine, (the termination routine), this is the ESR scheduled, by default.

This driver also illustrates another basic operating system interface, which is the branch to DIRDONE. A driver which has initiated an I/O operation, but has not completed that operation, should branch to DIRDONE (another entry in the operating system) to allow the processor to do other unrelated tasks while the I/O operation is in progress. Branching to DIRDONE normally forces the next ESR routine that is executed to be the termination routine, labeled TERM..., as specified in the DCB definition.

This driver also illustrates the fact that register 13 (UD) always points to the DCB of the device to which the I/O is directed. The operating system sets up this register before branching to the driver. The contents of register 13 should never be modified by the driver, for several reasons that will be shown more completely later.

```

*

* SCHEDULE ESR EXECUTION THROUGH SYSTEM QUEUE SERVICE

*

INITDRV2 L UO,DCB.LEAF(UD) Driver is always entered

ATL UO,SQ with reg 13 = addr of DCB

B DIRDONE Register set 5 is always

* used, except on some

* 8/32 and all 7/32 CPUs.

TERMDRV2 B IODONE

*

END

```

Step 3: Setting Up Entry To ISRs

The following example illustrates the basic execution sequence of a typical driver: from initialization to interrupt service to termination. This driver utilizes the minimum possible code to set up a path for entry to an ISR. It also illustrates the important step of entering an ISR to initiate an I/O operation. This is done to avoid responding to an unexpected interrupt while the device is being started. Also, as will be shown later, it is sometimes necessary to insure that certain sequences of operations are executed without any interruption, due to timing requirements. This can only be accomplished in an ISR.

In this driver, the initialization routine consists only of the code required to set up the interrupt service routine. The termination routine consists only of the exit to the operating system. The one ISR is entered by execution of the SINT instruction, since it is the first ISR to be executed. Since it is also the last ISR to be executed, it dismantles the path to itself, to avoid responding to any additional interrupts from the device.

2-2 48-190 F00 R00

```

entry point specified by DCB

INITDRV3 EQU

U2, DCB.DN (UD)

get physical address of device

_{

m LH}

get address of CCB for device

_{

m LHL}

UC, DCB.CCB (UD)

LIS

set up a nonexecute command

UO,O

STH

into the channel control word

UO, CCB.CCW (UC)

put the address of the

LA

UO, ISRO

ISR into the CCB

STH

UO, CCB.SUBA (UC)

AIS

UC, 1

make CCB address odd for ISPT

put CCB addr into ISPT

STH

UC, X'DO'(U2, U2)

U1, DCB.ILVL (UD)

get the interrupt level

LH

SINT U1,0(U2)

force entry into the ISR

(the code at "ISRO" is now executed; after the

ISR exits, the following instruction is executed)

after exit from first ISR,

В

DIRDONE

go back to the OS.

The following ESR is executed sometime after

the branch to DIRDONE is executed. It is executed

because it was scheduled by the ISR routine.

TERMDRV4 EQU

termination routine entry

exits to operating system

В

IODONE

The following ISR is entered

by execution of the SINT instruction. The ISR is in

"PURE" code to insure that it is located

* in the lower part of memory (it must be in the first

64KB of memory). The ISR schedules the ESR for

execution, and disables further interrupts.

* Note that on entry to the ISR, the following registers

* have been set up by the processor microcode:

EO, E1 = return program status word (PSW)/location counter (LOC)

= address of interrupting device

E 2

= status of interrupting device

E3

= address of CCB for interrupting device

E4

```

| ISRO | EQU   | *                  |                            |

|------|-------|--------------------|----------------------------|

|      | L     | E5,CCB.DCB(E4)     | get address of associated  |

|      |       |                    | DCB out of CCB.            |

|      | LA    | E7,III             | put address of null        |

|      | STH   | E7, X'DO' (E2, E2) | interrupt return into ISPT |

|      | L     | E6, DCB.LEAF (E5)  | now schedule the ESR for   |

|      | ATL   | E6,SQ              | execution.                 |

|      | LPSWR | EO                 | exit interrupt service     |

#### NOTE

The examples in Steps 1, 2, and 3 are all complete drivers with respect to the operating system. The reader can include any one of them into a system; an supervisor call 1 (SVC1) directed at a "device" handled by one of these drivers always returns immediately to the caller. Any one of these three drivers can be used to time basic SVC1 service processor overhead.

# Step 4: Executing a Sequence of ISR

In the example in Step 3, there was only one ISR, which is generally not very useful. To control a real device, we must have a minimum of two ISR routines: one to start the device and one to stop the device. The initialization routine sets up the interrupt path to the first ISR; the first ISR sets up the interrupt path to the second ISR and starts the device. The second ISR receives the hardware interrupt, stops the device, dismantles the interrupt path and schedules the ESR for execution; the ESR exits to the operating system.

For ease of understanding the sequence of execution of code, the following driver is written in a way such that the lines of code are in the same order as they are executed by the processor. This is an acceptable way to write a driver, as long as the placement of the IMPUR and PURE statements is correctly done.

However, the reader will probably find that a listing of the driver with the code organized as shown in the example for Step 3 is easier to use when debugging on a system, as all of the IMPUR and PURE code listings are separated into two separate blocks, just as it is in memory.

```

IMPUR

entry point from operating system

INITDRV4 EQU

get physical address of device

LH

U2, DCB.DN (UD)

get address of CCB for device

UC, DCB.CCB (UD)

LHL

set up a nonexecute command

LIS

UO, O

into the channel control word

STH

UO, CCB.CCW (UC)

put the address of the

LA

UO, ISRO

STH

UO, CCB. SUBA (UC)

ISR into the CCB

make CCB address odd for ISPT

AIS

UC,1

STH

UC, X'DO'(U2, U2)

put CCB addr into ISPT

LH

U1, DCB. ILVL (UD)

get the interrupt level

force entry into the ISR

SINT U1,0(U2)

PURE

entered from SINT instruction

ISRO

EQU

get address of next ISR

LA

E7, ISR1

& put into CCB to set up path

STH

E7, CCB. SUBA (E4)

(commands to start the device go here)

exit from this ISR

LPSWR EO

(returns to instruction after

SINT, which is as follows:

IMPUR

Now exit to the operating system to let the CPU do some unrelated

activity while we wait for the hardware interrupt:

this is logically part of

В

DIRDONE

the initialization routine

ISR1

EQU

The interrupt from the

hardware will force this to

be executed.

get address of null interrupt

LA

E7,III

routine & put into ISPT to

STH

E7, ISPTAB (E2, E2)

disable receipt of more int's.

(commands to stop the device go here)

```

```

get address of DCB for device

L

E5, CCB.DCB (E4)

L

E7, DCB.LEAF (E5)

get value to put on SQ to

schedule ESR execution

ATL

E7,SQ

exit this ISR.

LPSWR EO

IMPUR

TERMDRV4 EOU

termination routine

IODONE

exits to operating system.

В

```

Step 5: Setting Up Device Time-outs and User Status

The operating system is used to force an ESR to be executed if the I/O operation takes too much time. This happens if the device somehow does not work right. The code sequence shown below is used to tell the operating system to force a "time-out" (which means forcing an ESR to be executed) if the operation does not complete within a the number of seconds specified by the driver.

A time-out should always be set up before starting an I/O operation. The reason for doing this is that if the device should ever fail to interrupt, the I/O operation would not complete. This in turn would cause the user task (u-task) that issued the I/O operation to be "stuck": it could not be removed from the system (cancelled).

This sample driver illustrates the proper interface to the operating system for "getting on and off the timer chain": in other words, specifying the time-out interval, and how to tell the operating system to start and stop timing the I/O operation. Notice that the value DCB.TOUT must be set and reset in an ISR to avoid a possible conflict with the operating system routines that are necessary for the timing of the I/O operation.

|          | IMPUR |                    |                                                       |

|----------|-------|--------------------|-------------------------------------------------------|

| INITDRV5 | EQU   | *                  | entry point from operating system                     |

|          | BAL   | U8, TOCHON         | this call tells the operating $\operatorname{system}$ |

| *        |       |                    | to be ready to time an $I/O$ operation                |

| *        |       |                    | This call MUST be made in either                      |

| *        |       |                    | the initialization routine or                         |

| *        |       |                    | an ESR routine, NEVER in an ISR!                      |

| *        |       |                    | This call leaves DCB.TOUT='7FFF'                      |

| *        |       |                    |                                                       |

|          | LH    | U2, DCB.DN (UD)    | get physical address of device                        |

|          | LHL   | UC, DCB.CCB (UD)   | get address of CCB for device                         |

|          | LIS   | UO,O               | set up a nonexecute command                           |

|          | STH   | UO, CCB.CCW (UC)   | into the channel control word                         |

|          | LA    | UO,ISRO            | put the address of the                                |

|          | STH   | UO, CCB. SUBA (UC) | ISR into the CCB                                      |

|          | AIS   | UC,1               | make CCB address odd for ISPT                         |

|          |       |                    |                                                       |

2-6 48-190 F00 R00

```

UC, X'DO'(U2, U2) put CCB addr into ISPT

STH

LH

U1,DCB.ILVL(UD)

get the interrupt level

force entry into the ISR

SINT U1,0(U2)

PURE

entered from SINT instruction

ISRO

EQU

LA

E7,ISR1

get address of next ISR

& put into CCB to set up path

STH

E7, CCB.SUBA (E4)

E5, CCB.DCB (E4)

get address of DCB

now "turn on" the timing of the operation by the operating system:

LIS

E7,5

specify a five second time-out

STH

E7, DCB. TOUT (E5)

by putting 5 into DCB.TOUT

(notice: it is a HALFWORD!)

(commands to start the device go here)

LPSWR EO

exit from this ISR

IMPUR

DIRDONE

В

this is logically part of

the initialization routine

Since a value of 5 was set into DCB.TOUT, no more than

five seconds can elapse before the hardware interrupts.

If the interrupt does not occur, the driver is

reentered by the operating system at 'TERMDRV5', and

the code at 'ISR1' is not executed.

EQU

The interrupt from the

ISR1

hardware forces this to

be executed.

get address of null interrupt

LA

E7, III

STH

E7, ISPTAB (E2, E2)

routine & put into ISPT to

disable receipt of more int's.

(commands to stop the device go here)

L

E5, CCB.DCB (E4)

get address of DCB for device

```

```

* Now check that the operating system did not time-out the

operation just prior to the hardware interrupt occurring,

but before the ESR could dismantle the interrupt path.

This is a unlikely event, but must be checked for the

possibility. If the operating system times out the operation,

DCB.TOUT = 0, and the execution of the ESR is already

scheduled. Therefore, if the ISR finds that DCB.TOUT = 0,

then the ISR should not try to schedule the ESR. Doing so

can cause a system crash under some software configurations.

E7, DCB.TOUT (E5)

get current DCB value

LH

if already zero, exit now.

ΒZ

ISR1EXIT

Since some time elapses between now and the time that

the ESR is executed, it is necessary to indicate to both

the operating system and the ESR that the operation

completed (i.e., the expected interrupt was received within

the specified length of time). The operating system expects

that the value 'FFFF' is used for this purpose.

get value of 'FFFF'

LCS

E7.1

to set in DCB.TOUT

STH

E7, DCB.TOUT (E5)

get value to put on SQ to

E7, DCB.LEAF (E5)

L

schedule ESR execution

ATL

E7,SQ

ISR1EXIT LPSWR EO

exit this ISR.

* The termination routine customarily sets a status for the

* user of '8282' if a time-out has occurred; otherwise some

* other status is set, such as '0000' if the operation completes

* normally. Thus, the termination routine checks the time-out

* value to determine what has happened. The value put into

* into DCB.STAT is copied by the operating system into the

* user's SVC1 parameter block, so that the user can know

* of the success or failure of the requested operation.

IMPUR

TERMDRV5 EOU

termination routine

LH

U1, DCB.TOUT (UD)

get the time-out value

if zero, we timed out

BZ

TIMEOUT5

LIS

U2,0

and set zero user status

STH

U2, DCB.STAT (UD)

```

2-8 48-190 F00 R00

| TERM5X   | EQU | *               |                              |

|----------|-----|-----------------|------------------------------|

|          | BAL | U8,TOCHOFF      | now tell operating system    |

| *        |     |                 | that we do not need any more |

| *        |     |                 | timing services              |

| *        |     |                 |                              |

|          | В   | IODONE          | exit to operating system.    |

| *        |     |                 |                              |

| TIMEOUT5 | LHI | U2,X'8282'      | on time-out, tell user what  |

|          | STH | U2,DCB.STAT(UD) | happened.                    |

|          | В   | TERM5X          | go to common processing      |

Step 6: Selector Channel (SELCH) I/O, Data Buffer Addresses, and Length of Transfer

#### NOTE

If your custom device operates under direct processor control on the processor multiplexor bus, you may wish to skip directly to Step 7.

Many custom devices operate under a SELCH. To control the I/O operation, both the custom interface and the SELCH must be controlled. The basic points to be considered when a SELCH is used to control a device are:

- 1. The SELCH must have the starting and ending addresses of the data buffer in memory written to it before the transfer starts.

- 2. Once the SELCH is commanded to start the transfer, the device under the SELCH cannot be addressed. The SELCH must be stopped before the device can be accessed.

- 3. The SELCH terminates the transfer, and interrupts the processor, when either of two conditions are met:

- a. The SELCH determines that the data transfer has proceeded to the end of the data buffer; in other words, either all of the data in the user's buffer has been sent to the device, or the user's buffer has been filled with data from the device.

- b. The device controller indicates to the SELCH that no further data transfer is possible, by activating the appropriate signals on the SELCH private bus. (How this happens electrically is of no importance to the driver software).

The following driver, which is complete except for the specific commands required to control the device, shows all of the steps required to control an I/O operation through a SELCH. To aid comprehension, all of the SELCH commands are explicitly written. In many Perkin-Elmer supplied device drivers, subroutines are called to interface to the SELCH. Those routines perform the same functions as the code written here. It is a matter of individual programming preference as to whether those subroutines are used, or the commands are written explicitly as shown here. The routines used by some Perkin-Elmer drivers can be found in the module SUBS.MAC; if you plan to

use these subroutines, you should refer to the source code in this module to determine the proper calling sequences.

The fields DCB.FC, DCB.SADR, DCB.EADR, and DCB.LLXF are used in this driver to control the SELCH. The driver references, but does not modify, DCB.FC, DCB.SADR and DCB.EADR. The driver does set DCB.LLXF, which is then copied by the operating system back into the user's SVC1 parameter block to allow the user to know how much data was actually transferred. The field DCB.FC, which is copied directly from the user's SVC1 parameter block, is used to determine whether to set the SELCH and the device in a device read or device write mode.

```

IMPUR

entry from operating system to start I/O

INITDRV6 EOU

go get on timer chain

U8, TOCHON

BAL

LH

U3, DCB.SDN (UD)

get address of the SELCH

get address of CCB for device

LHL

UC, DCB.CCB (UD)

set up a nonexecute command

LIS

UO, O

* in the channel control word

STH

UO, CCB.CCW (UC)

get the address of the first ISR,

LA

UO, ISRO

STH

& set up for start-up SINT instruction

UO, CCB. SUBA (UC)

make CCB address odd, for

AIS

UC,1

STH

UC, ISPTAB (U3, U3)

* set up of ISP table

(note SELCH address is used)

get the interrupt level

LH

U1,DCB.ILVL(UD)

force entry to first ISR

SINT

U1,0(U2)

PURE

EOU

entry from SINT to start I/O

ISRO

get address of DCB for device

L

E5, CCB.DCB (E4)

get address of next ISR

LA

E7, ISR1

& set up CCB for hardware interrupt

STH

E7, CCB. SUBA (E4)

get SELCH address

LH

E3, DCB.SDN (E5)

be sure SELCH is reset

OC

E3, SLCHSTOP

* The values DCB.SADR and DCB.EADR were set up by the operating system

* by copying the values SVC1.SAD and SVC1.EAD from the user's SVC 1 block,

* and converting those values to physical memory addresses.

E3, DCB.SADR+1(E5) write 24-bit starting addr

WD

E3, DCB.SADR+2(E5) * to the SELCH

WH

WD

E3, DCB.EADR+1(E5) write 24-bit ending address

WH

E3, DCB.EADR+2(E5) * to the SELCH

LIS

E6.5

set up the device time-out

value for the operating system

STH

E6, DCB.TOUT (E5)

```

2-10 48-190 F00 R00

```

* Here are some things to consider at this point relative * to programming a SELCH-controlled I/O operation:

```

- 1. Once the SELCH is commanded to a "go" state, the device is unaccessable from the processor. Thus, we must issue the appropriate commands to the device first, then start SELCH

- 2. Some devices (e.g., magnetic tapes and disks), require that the SELCH be started at essentially the same instant as the device, to insure that a data overflow/underflow does not occur. Thus, ALL interrupts must be shut off while the device and SELCH are started!

- 3. The SELCH (and typically the device) have different command sequences that must be used to start read and write modes. This driver uses two separate sets of code for starting read and write, to simplify understanding of the logic used.

- 4. Most simple devices that operate under a SELCH are most efficiently programmed in such a way that only the interrupt from the SELCH is needed toindicate the end of the transfer. Thus, the interrupts from the device may be left shut off or ignored, as is done in this driver.

```

EPSR E7,E7

get current PSW value

E7,Y'FF20F0'

reset bit 20 for

noninterruptable state

LB

E6, DCB.FC (E5)

get the function code that was

E6, X'40'

THI

specified by the user, then

BNZ

ISROR

test for read/write, and go

to the appropriate routine

ISROW

EQU

come here to start write I/O

EPSR E6,E7

become noninterruptable

OC

E2, DEVCWRIT

start the device in write mode

OC

start the SELCH in write mode

E3, SLCHWRIT

LPSWR EO

exit the ISR routine

ISROR

EQU

come here to start read I/O

EPSR E6, E7

become noninterruptable

E2, DEVCREAD

start the device in read mode

OC

E3, SLCHREAD

start the SELCH in read mode

exit the ISR routine

LPSWR EO

command to "stop" (reset) SELCH

SLCHSTOP DB

X'48'

SELCH "go & write" command

SLCHWRIT DB

X'50'

```

```

SELCH "go & read" command

X'70'

SLCHREAD DB

appropriate device write command

DEVCWRIT DB

appropriate device read command

DEVCREAD DB

. . . . .

IMPUR

DIRDONE

driver initialization routine

В

exit back to operating system.

PURE

ALIGN 2

be sure we are not on a

byte boundary due to DB entries

in previous ISR routine

SELCH interrupt forces this

ISR1

EQU

routine to be executed.

note that E2 contains the address of the SELCH

give the SELCH a stop command

OC

E2, SLCHSTOP

LA

E7, III

dismantle the interrupt path

* to avoid any more interrupts,

STH

E7, ISPTAB (E2, E2)

get address of DCB of device

L

E5, CCB.DCB (E4)

LH

E6, DCB.TOUT (E5)

chech the time-out constant

ISR1X

if already timed-out, do nothing,

ΒZ

LCS

E6,1

otherwise, indicate no time-out

STH

by setting flag to 'FFFF'

E6, DCB. TOUT (E5)

L

E7, DCB.LEAF (E5)

now schedule the ESR to

* be executed.

ATL

SQ,E7

ISR1X

LPSWR EO

exit from this ISR.

IMPUR

operating system enters here

TERMDRV6 EQU

for I/O operation termination

LH

U3, DCB.SDN (UD)

get SELCH address

OC

U3, SLCHSTOP

be sure SELCH is stopped

(if we timed-out, it may not be)

RDR

U3,UO

now get SELCH final address

(all 24 bits)

RHR

U3,U1

make up a 24-bit value...

SLL

UO,16

now UO contains SELCH final addr

OR

UO,U1

is final addr = user's end addr?

UO, DCB.EADR (UD)

BNE

TERM6X

if not, branch to special logic

```

2-12 48-190 F00 R00

```

TERM6A

UO, DCB. SADR (UD)

now calculate the length of xfer

S

adjust for inclusive addressing

AIS

UO,1

UO, DCB.LLXF (UD)

and save length of xfer for user

ST

no error if equal, so set status

U1,0

LIS

U1, DCB.STAT (UD)

for user.

TERM6B

STH

get off the timer chain

BAL

U8, TOCHOFF

and exit to operating system I/O termination.

В

IODONE

* The following code is executed only if there is not a final address match:

* SELCH end address equals user's specified end address. Exactly what

* should be done under these circumstances depends upon the device, and

* how the system designer wants it to behave. For the purpose of this

driver, make the following choices:

1. If the final address is not in the range of the

the user's start and end addresses, then set the

status = X'8490', the length of transfer to zero,

and exit. (Some Perkin-Elmer supplied drivers crash the system

deliberately if the final address is outside the

user's start/end address, under some conditions.)

2. If the operation timed-out, set the status = X'8282',

set the length of transfer to zero, and exit

3. If the operation did not time-out, but the end address

is less than the user's end address, calculate the

actual length of transfer, and set the status = 0.

come here if SELCH end addr

TERM6X

EQU

is not equal user's end address

С

check end address for being

UO, DCB.SADR (UD)

BM

TERM6E

out of range

UO, DCB. EADR (UD)

TERM6E

LH

U4, DCB. TOUT (UD)

did we time-out?

TERM6A

if not, no error

BNZ

U1, X'8282'

if time-out, set proper status

LHI

LA

U8,III

and reset the ISP table

STH

U8, ISPTAB (U3, U3)

TERM6B

if end address out of range,

TERM6E

LHI

U1, X'8490'

TERM6B

set appropriate status

B

```

# Step 7: Data Transfer Using Autodriver Channel Programming

Many low-speed devices, primarily interactive terminals and some communications equipment, have controllers that are designed to present an interrupt to the processor for each character transferred. The following driver provides an explanation of the specific coding sequences that are peculiar to autodriver channel programming.

Note that this driver is designed to operate on a byte transfer device. This means that:

- 1. The device controller, when addressed, leaves the HWO (halfword) signal on the multiplexor (MUX) bus in the inactive (high) state.

- 2. The device controller, in response to an active DR0 signal on the MUX bus (i.e., data request), activates only eight data lines (D080 through D150).

- 3. The device controller, in response to an active DA0 signal on the MUX bus (i.e., data available), responds to only eight data lines (D080 through D150).

It is important to note that the distinction between byte- and halfword-oriented devices is made based on the behavior of the device controller on the MUX bus (or private SELCH bus). The characteristics of the data lines that the device controller present to the device have no bearing on the byte vs. halfword distinction for the purposes of autodriver channel programming. The hardware design manual, or circuit logic diagrams, for the device controller must be consulted to determine if the device controller is a byte or halfword device.

```

INITDRV7 PROG

Sample driver #7.

NLIST

$REGS$

$DCB$

$CCB

LIST

EXTRN DIRDONE, III, IODONE, ISPTAB, SQ, TOCHOFF, TOCHON

ENTRY INITDRV7, TERMDRV7

IMPUR

entered here by operating system to do I/O op

INITDRV7 EQU

U2, DCB.DN (UD)

get the device address

LH

LHL

UC, DCB.CCB (UD)

get the address of the CCB

* For the purposes of showing how the two-buffer concept can be

* used in autodriver channel programming, this driver outputs

* a prefix and a suffix for each message the user writes to

* the device. Thus, both buffer 0 and buffer 1 are used.

* We initially set up buffer 0 to output the prefix and buffer 1 to output

* the user's message. Reuse buffer 0 to output the suffix of the message.

```

2-14 48-190 F00 R00

```

* Since, by design choice, we wish for the complete line

* of output to fit on the CRT screen, we will limit the

* user to a message of 40 characters or less. If the user

* specifies a message greater than 40 characters, the

* initialization routine outputs a status of X'8490'

* and a length of transfer of zero, and exit. This

* illustrates the common practice of doing some initial

* parameter and device status checks in the initialization

* routine, before the first ISR is entered.

UO, DCB.EADR (UD) get the user's ending address

ST

UO, CCB.EB1 (UC)

& save as buffer 1 address.

S

UO, DCB.SADR (UD)

calculate requested message

AIS

UO,1

* length, then verify it is

CHI

UO, 40

not greater than 40.

BP

INIT7ERR

If more than 40, error exit.

U1,1

now calculate value to put

LIS

U1,UO

* into CCB as buffer count

SR

& save for later use

STH

U1, CCB.LB1 (UC)

LA

U1, PREFIX.S

now set up the CCB for the

LA

UO, PREFIX.E

prefix to be output

ST

UO, CCB.EBO (UC)

(use buffer 0)

SR

U1,U0

calculate value for counter

and save for later use.

STH

U1,CCB.LBO(UC)

* At this point, both sets of buffer pointers are set up.

* Set up the remainder of the CCB in the usual way to point

* to the first ISR. Notice that we wait

* until after the initial parameter checks to initialize the

* I/O operation timing services of the operating system. We

* do that now, and go to the first ISR.

BAL

U8, TOCHON

go tell operating system we need timing done

LIS

UO,O

reset the channel command word

STH

UO, CCB.CCW (UC)

get address of first ISR

LA

UO, ISRO

STH

UO, CCB.SUBA (UC)

& save in CCB.

* Use the CCB.MISC field to allow the ISR routines

* to tell the ESR that a transfer failed, if this should

* happen. Thus, we initialize this field to zero.

```

```

LHI

UO, O

get a zero

UO, CCB.MISC (UC)

STH

make CCB addr odd for ISPT

AIS

UC,1

UC, ISPTAB (U2, U2) (set up ISPT)

STH

U1, DCB.ILVL (UD)

get the interrupt level

_{

m LH}

SINT

U1,0(U2)

go start the transfer

after first ISR, exit to do

DIRDONE

В

something else while I/O runs

initialization error exit

INIT7ERR EQU

U5, X'8490'

get a status code

LHI

STH

U5, DCB.STAT (UD)

& save for user.

reset the length of transfer

LIS

UO, O

ST

UO, DCB.LLXF (UD)

for user

В

IODONE

terminate the operation.

PURE

ISRO

EQU

come here to start transfer

LA

E7, ISR1

get address of next ISR to use

STH

E7, CCB.SUBA (E4)

and set up CCB for next ISR.

get DCB address

E5, CCB.DCB (E4)

LIS

set up an 8 second time-out

E6,8

STH

E6, DCB.TOUT (E5)

(this is an arbitrary choice)

give the COMM-MUX command 2,

OC

E2,CMD2

OC

E2,CMD1

& command 1

* The autodriver channel operates in response to interrupts.

* Since we are now in an ISR, we can not issue another SINT

\star to start the I/O operation. Instead, we utilize the SCP

* instruction to maintain the buffer pointer/counter in the

* CCB, and do a WD to the device. This causes a hardware interrupt,

* which is then handled by the autodriver channel firmware.

LH

E6,CCWO

set the channel command word

STH

E6, CCB.CCW (E4)

* for buffer 0

SCP

E7, CCB.CCW (E4)

get a character from buffer 0

write it to the device

WDR

E2, E7

and exit back to init routine

LPSWR EO

ALIGN 2

CCWO

DC

X'A084'

execute, buffer 0

CCW1

DC

X'A08C'

execute, buffer 1

CMD2

X'F8'

COMM-MUX command 2

DB

```

2-16 48-190 F00 R00

```

COMM-MUX command 1

CMD1

DB

X'63'

DISARM

DB

x'co'

kill interrupts on COMM-MUX

ALIGN 2

ISR1

EQU

come here when buffer O done:

LH

did all of buffer 0 go out?

E7, CCB.LBO (E4)

BNP

ISRERR

if count not positive, error

LA

E6, ISR2

set up the CCB for third ISR

STH

E6, CCB. SUBA (E4)

* to be used.

set command word for buffer 1

_{

m LH}

E7, CCW1

STH

E7, CCB.CCW (E4)

SCP

get 1st char from user's buffer

E7, CCB.CCW (E4)

WDR

E7,E2

and send to device

LPSWR EO

exit to wait for I/O

ISR2

EQU

come here when buffer 1 done:

LH

E7, CCB.LB1 (E4)

did all of buffer 1 go out?

BNP

ISRERR

if count not positive, error

LA

E6, ISR3

set up CCB to point to last

STH

E6, CCB. SUBA (E4)

* ISR routine to be used

LA

E7, SUFFIX.E

set up CCB for different

ST

E7, CCB.EBO (E4)

* buffer 0 pointers

LA

E6, SUFFIX.S

now get the value for the

SR

E6, E7

* count field, and then set

STH

E6, CCB.LBO (E4)

* it up.

SCP

E7, CCB.CCW (E4)

get 1st char from suffix buffer

WDR

E7,E2

and send it to device

exit to wait for I/O

LPSWR EO

ISR3

EQU

come here when all I/O done

check that all of the last

_{

m LH}

E6, CCB.LBO (E4)

BNP

ISRERR

transfer completed.

ISRDONE

L

E5, CCB.DCB (E4)

get address of DCB of device

LA

E7, III

clear the interrupt path

STH

E7, ISPTAB (E2, E2)

OC

E2, DISARM

kill device interrupts

LCS

E6,1

indicate no time-out occurred

STH

E6, DCB. TOUT (E5)

L

E7, DCB.LEAF (E5)

schedule the termination

ATL

* routine for execution

E7,SQ

LPSWR EO

and exit interrupt service.

ISRERR

EQU

come here if I/O fails

LHI

E6,X'8484'

set a status code for ESR

```

```

STH

E6, CCB.MISC (E4)

ISRDONE

& go exit ISR sequence

IMPUR

operating system enters here when I/O done

TERMDRV7 EQU

* The error checking sequence is somewhat arbitrary. Here, a time-out is

* the most important error; and failure to complete the transfer will be

* less important.

UO, DCB.TOUT(UD) get current time-out value

LH

ΒZ

error exit if timed-out

TIMEOUT7

LH

UC, DCB.CCB (UD)

get CCB address.

UO, CCB.MISC (UC) check error indicator

LH

if not zero, I/O failed

BNZ

IOFAIL7

otherwise, indicate no error.

LIS

U1,0

U1, DCB.STAT(UD) set error status

STH

TERM7B

indicate no more timing.

BAL

U8, TOCHOFF

* By design choice, we will report the length of transfer as only that part

* of the user's buffer that was actually transferred. We use the count

* value for buffer 1 for this calculation:

UO, DCB.EADR (UD) get user's end address

L

less user's start address

S

UO, DCB. SADR (UD)

AΗ

UO, CCB.LB1 (UC)

plus the residual buffer 1 count

UO, DCB.LLXF (UD)

equals count of bytes moved.

ST

go to operating system I/O termination

В

LODONE

TIMEOUT7 EQU

set time-out status

LHI

U1, X'8282'

TERM7B

IOFAIL7 EOU

set I/O failed status

U1, X'8484'

LHI

В

TERM7B

ALIGN 4

* Define the suffix and prefix output by this driver

PREFIX.S DC

C'<PREFIX>'

PREFIX.E EQU

*-1

SUFFIX.S DC

C'<SUFFIX>'

X'00', X'0D', X'00', X'0A', X'00', X'00'

DB

*-1

SUFFIX.E EQU

END

```

2-18 48-190 F00 R00

# Step 8: Generating User-Level Task Traps

In special circumstances, it is desirable to have the device driver add an item to the user's task queue, thereby generating a task trap. This feature is most likely to be used in applications that require buffer chaining, so that the u-task can be notified each time a data buffer has been processed by the driver.

The following small driver has been written to illustrate the code sequence required to add items to the user's task queue, and thus generate user-level task traps. This particular driver causes an item to be added to the user's task queue each time an I/O request is made to the driver. Note that this sample driver does not interface to a physical device; this is only because a physical device interface is not necessary in order to illustrate the add to task queue mechanism.

```

INITDRV8 EOU

entry from operating system

L

U9, DCB.TCB (UD)

get user's TCB address

LI

UA, QUEITEM

get value to put on task queue

BAL

U8,TMATQ1

branch to operating system

routine to add item to

the task queue.

IODONE

exit from driver.

TERMDRV8 EQU

not executed: used to

satisfy reference from

DCB.TERM entry in DCB.

QUEITEM

EQU

(item definition is arbitrary)

END

```

It should be noted that the routine "TMATQ1" is subject to being renamed in future revisions of the operating system. In revision 6.2 and lower, the label was "SV9.ATQ1". For this reason, the writer of a driver may want to replace the statement:

```

BAL U8, TMATQ1

```

with the macro call:

```

ADDTTSKQ REASON= (UA) , TASKSW=NO

```

This coding practice assures compatability with future releases of the operating system.

# Step 9: Making Changes for IOP Execution

The following two drivers operate identically. However, the first driver does not execute correctly on an IOP. The second driver contains calls to the new macros needed to generate code that operate correctly under an IOP.

```

INITDUMB PROG DUMMY DRIVER FOR OS/32 REVISION 7.

* THIS DRIVER WILL NOT OPERATE CORRECTLY ON AN IOP

MLIBS 8,9,10

DRIVER INITIALIZATION

ENTRY INITDUMB

DRIVER TERMINATION

ENTRY TERMDUMB

EXTRN DIRDONE, IODONE, SQ, III, ISPTAB

INITDUMB EQU

U2, DCB.DN (UD) GET THE DEVICE ADDRESS.

LH

SET NULL INTERRUPT VECTOR

LA

UF,III

STH UF, ISPTAB (U2, U2) FOR THE DEVICE.

UF, DCB.LEAF (UD) GET LEAF TO SCHEDULE TERMINATION

BY PUTTING IT ON SYSTEM QUEUE.

ATL

UF,SQ

EXIT TO OS ROUTINE.

DIRDONE

TERMDUMB EQU

DRIVER IS DONE - QUIT NOW.

В

IODONE

INITDUMB PROG DUMMY DRIVER FOR OS/32 REVISION 8.

* THIS CODE WILL EXECUTE CORRECTLY ON AN IOP

MLIBS 8,9,10

DRIVER INITIALIZATION

ENTRY INITDUMB

DRIVER TERMINATION

ENTRY TERMDUMB

EXTRN DIRDONE, IODONE, SQ, III, ISPTAB

INITDUMB EQU

U2,DCB.DN(UD) GET THE DEVICE ADDRESS.

LH

GET THE NULL INTERRUPT VECTOR.

LA

U6,III

ISPMOD ITEM= (U6), DCB= (UD), DN= (U2), WORK= (UF)

GET LEAF TO SCHEDULE TERMINATION

UF, DCB.LEAF (UD)

ADDSQ ITEM= (UF), DCB= (UD), WORK= (UE)

EXIT TO OS ROUTINE.

DIRDONE

TERMDUMB EQU

IODONE

DRIVER IS DONE - QUIT NOW.

В

```

# 2.3 WRITING DEVICE CONTROL BLOCK/CHANNEL CONTROL BLOCK (DCB/CCB) SPECIFICATIONS

Every device driver operates primarily on two associated data structures, the DCB and the CCB. It is the responsibility of the writer of the I/O driver to provide definitions of these two data structures, along with the actual I/O driver. The remainder of this chapter provides some procedures for specifying the DCB and CCB structures.

It is very important that the DCB and CCB specification be done exactly right the first time! An error in the DCB or CCB specification can result in any of the following symptoms:

- 1. Errors in the Sysgen32 phase of the sysgen procedure.

- 2. Errors in the macro expansion phase of the sysgen procedure.

- 3. Errors in the CAL assembly phase of the sysgen procedure.

- 4. Errors in the link phase of the sysgen procedure.

- 5. System crashes of all kinds when attempting to use the driver.

- 6. Other malfunctions of the driver.

The DCB definition contains all of the keyword definitions which can be used in the sysgen statement, such as the device name, device address, device code, controller address, SELCH address, and extended device codes. The DCB definition also provides a definition of all of the device-dependent data items that can be referenced by the driver, such as (for disks) the number of sectors per track, tracks per cylinder and cylinders per disk. Other device-dependent data can include special command tables for setting band rates on asynchronous lines, and tables of tape motion speeds for magnetic tape drives. For some devices, data buffers or scratchpads can be included in the DCB definition.

Fortunately, most custom devices can utilize a DCB definition that is very nearly the same as a DCB definition already provided for a standard Perkin-Elmer device. Due to the large amount of detail that must be provided in the DCB definition, the best way to build a new DCB definition is to start with an existing DCB definition. The following steps provide a guide for building a new DCB definition:

1. Copy a DCB specification of a similar type of device from SYSGEN32.MLB into a new file, DCBxxx.MAC (xxx is the new device code, which must be in the range of 240 to 255). This can be done using MLU32, and listing the appropriate macro definition directly to DCBxxx.MAC. For example, a device that operates under a SELCH and supports both read and write, but does not support random access, is similar to a magnetic tape drive, so the macro definition DCB65 would probably be a good starting point. For example, the following session copies the definition of a magnetic tape driver into a file named DCB248.MAC:

\*10 mlu32;st

PERKIN-ELMER OS/32 MACRO LIBRARY UTILITY O3-340 ROO-O1

MLU>get sysgen32.mlb/s

MLU>list dcb248.mac,DCB64

1 MACRO LISTED TO NEW FILE SYS:DCB248.MAC

MLU>end

RW -END OF TASK CODE= O PROCESSOR=0.907 TSK-ELAPSED=38

2. In DCBxxx.MAC, change the DCB number (e.g., 65), to the new device code (e.g., 240) everywhere that it appears. Be careful not to miss any appearances of the old DCB number, but also be careful (if you are using EDIT32) not to modify any other character strings that just happen to match the new DCB number (e.g., 240).

### 3. After the line:

CONVNUM

#### Add the statement:

USERINIT

- 4. Modify the parameters for the DCBI macro statement. This includes at least the INIT= and TERM= parameters, and probably the ATRB= parameter. This macro call specifies the values assumed by various data items within the DCB. Look over the DCBI macro statement carefully to be sure that you have adjusted all the terms that apply to your specific custom device. The device-dependent part of the DCB is specified in the DCBI macro statement with a COPY= parameter.

- 5. It is very unlikely that you will need to modify the CCBI macro statement, other than what was done in Step 2 above. The CCB is usually set up at run time by the driver. The possible exception would be a translation table name.

### 6. Add the statement

DCB%DCOD%IDVAL PROG USER DCB

after the CCBI macro statement, as shown in the example below. This provides a label that prints when the macro is assembled at sysgen time. This is a handy way to know if your DCB definition successfully passed that particular stage of the sysgen procedure.

7. Add the definition of any specific values in the device-dependent portion of the driver. This is done by the following constructs, which should be placed immediately preceding the \$ST%OFFS statement near the end of the DCBxxx.MAC file:

```

ORG DCB%OFFS+DCB.YYYY

DC .....

```

The label DCB.yyyy is a label defined in the device-dependent part of the DCB. The existence of the label, and its assigned value, are determined strictly by the requirements of your specific custom device.

8. After the statement

ORG \$ST%OFFS

Add the statements:

ASIS END

If these eight steps are carefully done, the DCB definition will be complete.

To use the new DCB definition, which has been created in the file DCBxxx.MAC, it must be put into a macro library known as USERDLIB.MLB. This is done by using the MLU32 utility program.

Note that the device-dependent part of the DCB is determined by the specific requirements of your driver. In general, write your driver code first to determine what, if any, specific device-dependent fields you need, then include them in your DCB definition.

For programmers who are familiar with the now unsupported Configuration Utility Program (CUP), it is important to know that the use of Sysgen/32 requires that the DCB and the actual driver code be constructed in separate files, and placed in separate libraries. This is considerably different from the procedures used with CUP. The Sysgen/32 procedures require that the DCBxxx macro definition be placed in a macro library, USERDLIB.MLB; the driver code is expanded, assembled, and included in object format in an object library, USERDLIB.LIB. After this is done, the supplied SYSGEN.CSS can be used to perform the sysgen.

The major item of concern in writing the DCBXXX macro is the specification of the DCB macro. This macro defines the initialization, termination, function, and IOH routines used by the driver. Also specified here is the device code, attributes, and size of the DCB.

# The DCB specification macro:

```

DCB DCOD = ,INIT = ,TERM =, ATRB = ,RECL = ,SIZE =, IOH =

```

DCOD - DCB number (gives each device type a unique code)

INIT - entry point to driver initialization routine.

TERM - name of first ESR to execute.

ATRB - attributes of the device

RECL - record length supported by the device

SIZE - size of the driver + dependent structures

IOH - name of I/O handler for this device.

## A sample DCBXXX macro to be included in USERDLIB.MLB:

```

MACRO

DCB243 %DCOD=, %DN=, %CLAS=, %ILVL=, %NAME=, %SHCCB=,

%SIZE=, %RECLN=, %XDCD=, %IOP=0

GBLC %IDVAL

BGBLA %ID243

LCLA %CCBFL

LCLA %CLASN

LCLC %RXLT, %RQU

LCLC %CORDNM, %PTRPAS

LCLC %OFFS

LCLA %RDN

LCLC %MDN,%MCNT,%MSLCH

LCLA %TRCNT, %UPTR

LCLB %FOUND, %DA

BGBLA %FIRST

DEFAULT DEVICE QHANDLER

SETC 'COMQ'

SETC '%DN'

DEVICE ADDRESS

SETA O

```

IOCLASS\*12

(T'%CLAS EQ 'U') &CLSNTD

%RQU

%MDN %CCBFL

%CLASN

AIF

SETA %CLAS\*12

```

ANOP

&CLSNTD

CONVNUM VAL=%ID243 CONVERT CURRENT ID TO HEX.

USERINIT

$DCB$

DCBI DCOD=243, SIZE=DCB.DVDP, INIT=INITCORD, IOC=2,

TERM=TERMCORD, FLGS=DFLG.LNM, RECL=132, ID=%IDVAL,

х

ATRB=2B80, IOP=%IOP

CCBI DCOD=243, ID=%IDVAL

CCB%DCOD%IDVAL

CCB%NAME EQU

SETA %ID243+1

%ID243

&DCBOPT ANOP

DCB%DCOD%IDVAL PROG USER DCB

ESTABLISH PROPER OFFSET

SETC '%DCOD':'%IDVAL'

%OFFS

DCB_%NAME EQU DCB%OFFS

ENTRY DCB_%NAME

DCB%OFFS+DCB.DN DEVICE ADDRESS

ORG

DC

H'%DN'

ORG DCB%OFFS+DCB.LEAF LEAF POINTER

AIF

(T'%SHCCB' EQ 'U') &NSLEAF

B IF NOT SHARED

DAC

USE SHARED DEVICE LEAF

LF%SHCCB

EXTRN LF%SHCCB

AGO

&NRMLFX

&NSLEAF ANOP

GENERATE STANDARD LEAF NAME

DAC

LF%OFFS

EXTRN LF%OFFS

&NRMLFX ANOP

&NOLEAF ANOP

(T'%CLAS EQ 'U') &NOCLAS

AIF

DCB%OFFS+DCB.CLAS IO CLASS

ORG

IOCLASS*12

DC

H'%CLASN'

&NOCLAS

ANOP

AIF

(T'%ILVL EQ 'U')&NOILVL

DCB%OFFS+DCB.ILVL

ILEVEL

ORG

DC

H'%ILVL'

&NOILVL ANOP

(T'%XDCD EQ 'U') &NOXDCD IF NOT ENTERED

AIF

ELSE MOVE XDCD

ORG

DCB%OFFS+DCB.XOPT

DC

%XDCD

EXTENDED DCOD

```

```

&NOXDCD ANOP

```

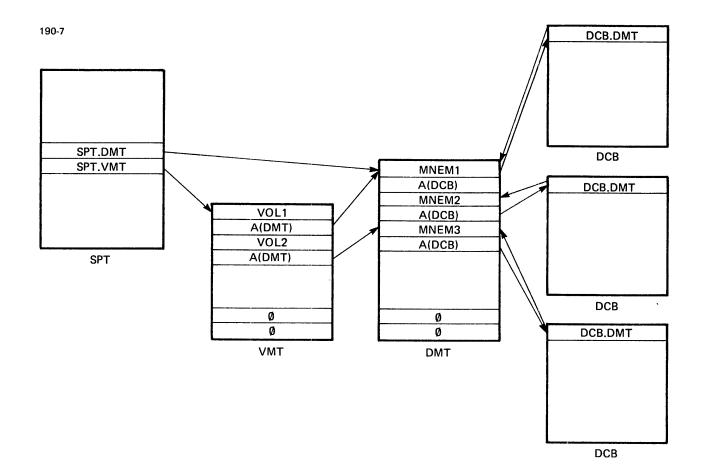

ORG DCB%OFFS+DCB.DMT

DC

DMT\_%NAME A (DMT ENTRY)

EXTRN DMT\_%NAME

('%RQU' EQ '')&NOQU AIF

DCB%OFFS+DCB.Q ORG

DAC %RQU

EXTRN %RQU

&NOQU ANOP

AIF. (T'%RECLN EQ 'U') &NORECLN

ORG DCB%OFFS+DCB.RECL RECORD SIZE

H'%RECLN' DC

&NORECLN ANOP

ORG \$ST%OFFS ORG TO END OF DCB

ASIS

END

%RDN

SETA %DN+1

MEND

# Chapter 3

# INCLUDING THE DRIVER IN YOUR OPERATING SYSTEM

| 3.1 | INTRODUCTION                              | 1  |

|-----|-------------------------------------------|----|

| 3.2 | EXPANDING AND ASSEMBLING DRIVERS          | 1  |

| 3.3 | SYSTEM GENERATION (SYSGEN) WITH CUPMT     | 3  |

| 3.4 | SYSTEM GENERATION (SYSGEN) WITH SYSGEN/32 | 10 |

| 3.5 | CUPMT VS. SYSGEN/32                       | 16 |

### **CHAPTER 3**

### INCLUDING THE DRIVER IN YOUR OPERATING SYSTEM

### 3.1 INTRODUCTION

Special procedures are necessary at system generation (sysgen) time to include the driver into your operating system. These include expanding and assembling the driver before incorporating the driver into the sysgen configuration. Please note that although the Configuration Utility Program (CUP) is no longer supported, instructions for sysgening with CUPMT have been included for those users who work with older versions of OS/32.

### 3.2 EXPANDING AND ASSEMBLING DRIVERS

The conventional name for operating system and driver source modules is XXXX.MAC (where XXXX is a symbolic name for the device which the driver controls). The command substitution system (CSS) procedures which follow are typical procedures which can be used; however, these can be modified for individual installations.

```

*EXPAND.CSS <name of module - (XXXX)>

XAL @1.CAL, IN, 80/8

L .BG, MACRO32, 50

T .BG

AS 1,@1.MAC,SRO

AS 2,@1.CAL

AS 3, NULL:

(this is the list file)

AS 7, SYSGEN.MAC/S, SRO

AS 8, SYSSTRUC.MLB/S, SRO

AS 9, SYSMACRO.MLB/S, SRO

AS 10, DVRM.MLB/S, SRO

AS 11, ITMS.MLB/S, SRO

AS 12, SYSMAC32.MLB/S, SRO

ST, MLIBS= (8,9,10,11,12)

SEXIT

```

```

*ASSEMBLE.CSS <name of module - (XXXX)>