# IRONICS

IV-1624 8-PORT INTELLIGENT SERIAL I/O CARD

UserGuide

# IV-1624 8-PORT INTELLIGENT SERIAL I/O CARD

Description: IV-1624 1.101

Doc. no.: 130.047.F Doc. type: manual Release date: 22-Aug-85

(c) Copyright Ironics Incorporated, 1985

This manual has been carefully checked for accuracy. We can, however, assume no responsibility for errors, nor can we assume any liability which arises from the use or application of this board.

As part of our continuing effort to improve the quality of the Ironics VMEbus productivity series, we solicit comments, criticism and suggestions of our customers. We would greatly appreciate your taking the time to provide us with any feedback. Your comments, positive or negative, about the manual, hardware or software are especially welcome. Send your remarks to:

Ironics Incorporated Quality Assurance 798 Cascadilla Street Ithaca, New York 14850

# CONTENTS

| 0. | READ  | THIS BEFORE UNPACKING                          | ) – :          |

|----|-------|------------------------------------------------|----------------|

| 1. |       |                                                | L – :          |

|    | 1.1   | History of the IRONICS multiprocessing         |                |

|    | 1.2   | family 1 Philosophy of Design: Multiprocessing | L - :          |

|    | 1.2   |                                                | L <b>–</b> :   |

|    | 1.3   |                                                | L — .<br>L — ! |

|    |       |                                                | L - !          |

|    |       |                                                | Ĺ – !          |

|    |       | 1.3.3 Memory                                   | L - !          |

|    |       | 1.3.4 Data transfer mechanisms                 | L - (          |

|    |       | 1.3.5 Interprocessor communication primitives  | L 8            |

|    | 1.4   |                                                | L — (          |

|    | T • 4 | 1.4.1 The IV-1601 VMXCPU board: the            |                |

|    |       |                                                | 9              |

|    |       | 1.4.2 The IV-1602 Single Board                 |                |

|    |       |                                                | 9              |

|    |       | 1.4.3 The IV-1624 8-port Intelligent           | • •            |

|    |       |                                                | -1(            |

|    |       | 1.4.4 IV-3201 68020 VME/VMX CPU                | -10            |

|    |       | board                                          | . T (          |

|    |       | 3                                              | -1(            |

|    | 1.5   |                                                | .25            |

|    | 1.5   |                                                | 25             |

|    |       | 1.5.2 Specific references 1-                   |                |

|    | 1.6   |                                                | -27            |

| 2. | INSP  | ECTION, INSTALLATION, AND CHECKOUT 2           | ! – 1          |

|    | 2.1   |                                                | ! - 3          |

|    | 2.2   | Inspection                                     | ! – 3          |

|    | 2.3   |                                                | _4             |

|    |       | 2.3.1 Minimum system requirements for          |                |

|    |       |                                                | -4             |

|    |       |                                                | -4             |

|    |       |                                                | -4             |

|    |       |                                                | -5             |

|    |       |                                                |                |

|    |       | 2.3.6 Power up and test procedure 2-           | 13             |

| 3. | IV-16 |                                                | -1             |

|    | 3.1   | Board control logic                            | -3             |

|    | 3.2   |                                                | -4             |

|    | 3.3   |                                                | - 5            |

|    |       | 3.3.1 The 68010 CPU                            | -5             |

|    |       | 3.3.2     | Mamanu man and lamal T/O            |       |

|----|-------|-----------|-------------------------------------|-------|

|    |       | 3.3.2     | Memory map and local I/O            | 3-!   |

|    |       | 2 2 2     | decoding                            |       |

|    |       | 3.3.3     | EPROM theory of operation:          |       |

|    |       | 3.3.4     | RESET/RETRY generation              |       |

|    |       | 3.3.5     | MC68B40 programmable timer          |       |

|    |       | 3.3.6     | Front panel LED indicators          | 3-17  |

|    |       | 3.3.7     | Local bus arbitration               | 3-17  |

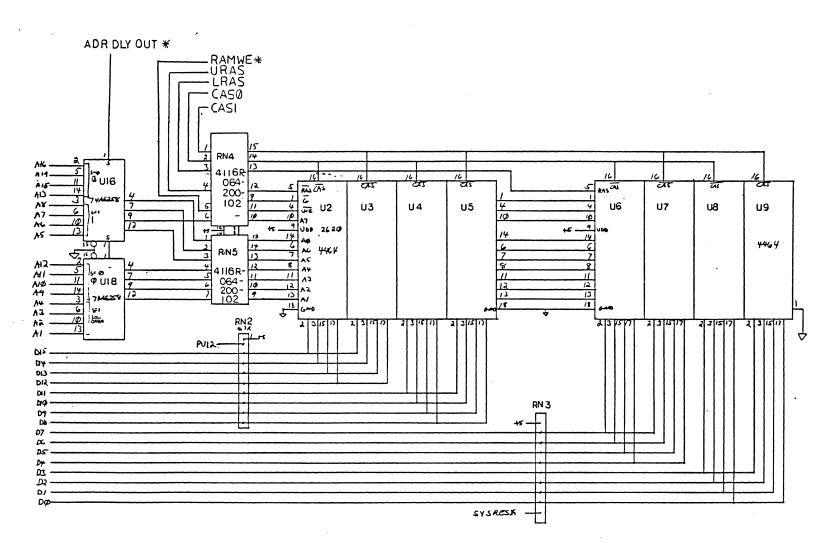

|    | 3.4   | Dynami    | c RAM and control interface         | 3-19  |

|    |       | 3.4.1     | Dynamic RAM address decoding        | 3-19  |

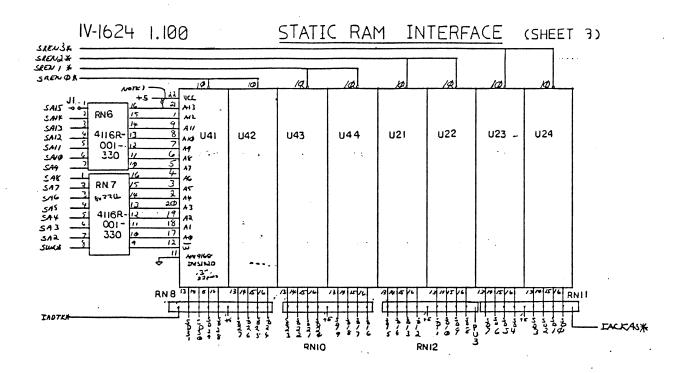

|    | 3.5   | Static    | RAM controller and interface:       | 3-20  |

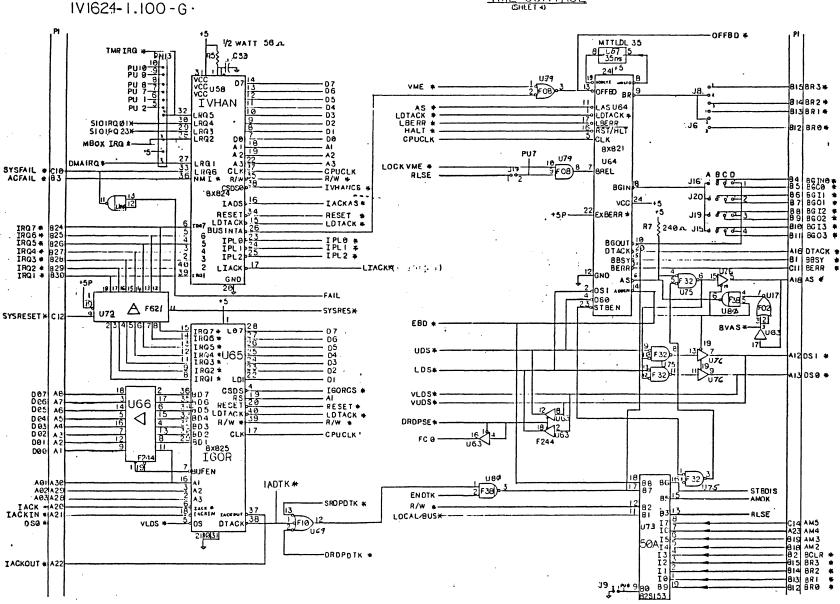

|    | 3.6   | VMEbus    | s interface                         | 3-2]  |

|    |       | 3.6.1     | VMEbus address and data             |       |

|    |       |           | interface                           | 3-21  |

|    |       | 3.6.2     | VMEbus connector/ backplane         | J 2.  |

|    |       | 3.0.2     |                                     | 3-21  |

|    |       | 2 ( 2     | specification                       |       |

|    | 2 7   | 3.6.3     | Dual port accesses                  | 3-21  |

|    | 3.7   | Serial    |                                     | 3-27  |

|    |       | 3.7.1     | Operating modes                     | 3-27  |

|    |       | 3.7.2     | Interrupts                          | 3-28  |

|    | 3.8   |           | ntroller                            | 3-30  |

|    |       | 3.8.1     | DMA controller performance notes    |       |

|    |       |           |                                     | 3-30  |

|    |       | 3.8.2     | DMAC applications                   | 3-30  |

|    |       | 3.8.3     | DMAC operation                      | 3-31  |

|    |       |           | •                                   |       |

| 4. | I V-1 | 624 CON   | FIGURATION GUIDE                    | 4-1   |

|    | 4.1   |           | r overview                          | 4-3   |

|    |       | 4.1.1     | EPROM shunt options                 | 4 – 4 |

|    |       | 4.1.2     | Dynamic RAM shunt installation      | 4 - 5 |

|    |       | 4.1.3     | Static RAM shunt installation       | 4-6   |

|    |       |           |                                     | 4-(   |

|    |       | 4.1.4     | Dual port RAM shunt                 |       |

|    |       |           | installation                        | 4 - 7 |

|    |       | 4.1.5     | VMEbus shunt installation           | 4-9   |

|    |       | 4.1.6     | Serial and DMA controller shunt     |       |

|    |       |           | installation                        | 4-13  |

|    |       |           |                                     |       |

| 5. | I V-1 | .624 PAR' | TS LIST                             | 5-1   |

|    | 5.1   | `Core a   | ssembly                             | 5-4   |

|    |       | 5.1.1     | Integrated Circuits                 | 5 – 4 |

|    |       | 5.1.2     | Resistor networks and sips          | 5-7   |

|    |       | 5.1.3     | Resistors                           | 5-8   |

|    |       | 5.1.4     | Diodes                              | 5-8   |

|    |       | 5.1.5     | Capacitors                          | 5-9   |

|    |       | 5.1.6     | Miscellaneous                       | 5-10  |

|    | 5.2   | Option    |                                     | 5-11  |

|    | J . L | 5.2.1     | 10 MHz CPU option                   | 5-11  |

|    |       |           |                                     | 5-11  |

|    |       | 5.2.2     | 12 MHz 68010 CPU option             | 2-11  |

|    |       | 5.2.3     | 64K dynamic RAM option (8 or 10 MHz | E 10  |

|    |       |           | CPU)                                | 5-12  |

|    |       | 5.2.4     | 64K dynamic RAM option (12.5 MHz    |       |

|    |       |           | CPU)                                | 5-12  |

|                | 5.2.     | . 5     | 256E    | K dy:   | nami    | c RA    | AM o | pti     | on      | (10   |       |       |       |       |

|----------------|----------|---------|---------|---------|---------|---------|------|---------|---------|-------|-------|-------|-------|-------|

|                |          |         |         |         |         |         |      |         |         |       |       |       |       | 5-13  |

|                | 5.2.     | 6       | 256F    | ⟨ dy    | nami    | c RA    | M o  | pti     | on      | (12.  | .5 M  | Hz    |       |       |

|                |          |         |         |         |         |         |      |         |         |       |       |       |       | 5-13  |

|                | 5.2.     | . 7     | (4K)    | (32)    | sta     | tic     | RAM  | op      | tion    | n (]  | 10 M  | Hz    |       |       |

|                |          |         |         |         |         |         |      |         |         |       |       |       |       | 5-14  |

|                | 5.2.     |         |         |         | sta     |         |      |         |         |       |       |       |       |       |

|                |          |         | -       | -       |         |         |      | _       |         |       |       |       |       | 5-14  |

|                | 5.2.     |         |         |         | trol    |         |      |         |         |       |       |       |       | 5-15  |

|                | 5.2.     |         |         |         | Cont    |         |      |         |         |       |       |       |       | 5-15  |

|                | 5.2.     |         |         |         | ROM     |         |      |         |         |       |       |       | •••   | 3 23  |

|                | J        |         |         |         | ate)    |         |      |         |         |       |       |       |       | 5-16  |

|                | 5.2.     |         |         |         | ROM     |         |      |         |         |       |       |       | • • • | J 1   |

|                | J • L •  |         |         |         | wait    |         |      |         |         |       |       |       |       | 5-16  |

|                | 5.2.     |         |         |         | PROM    |         |      |         |         |       |       |       | • • • | J-10  |

|                | J . Z .  | 13      |         |         | • • • • |         |      |         |         |       |       |       |       | 5-17  |

|                | 5.2.     | 1 /     |         |         |         |         |      |         |         |       |       |       |       | 3-17  |

|                | 5.2.     | T 4     |         |         | PROM    |         |      |         |         |       |       |       |       | E 17  |

|                | F 3      |         |         |         | stat    |         |      |         |         |       |       |       |       | 5-17  |

|                | 5.2.     |         |         |         | PROM    |         |      |         |         |       |       |       |       | - 10  |

|                |          |         | wait    |         |         |         |      |         |         |       |       |       | • • • | 5-18  |

|                | 5.2.     |         |         |         | PROM    |         |      |         |         |       |       |       |       | - 10  |

|                |          |         | CPU;    | 1 1     | wait    | sta     | te)  | • • •   | • • • • | • • • | • • • | • • • | • • • | 5-18  |

|                | 5.2.     |         |         |         | PROM    | -       |      | •       |         |       | -     |       |       |       |

|                |          |         | wait    |         |         |         |      |         |         |       |       |       | • • • | 5-19  |

|                | 5.2.     | 18      | 2751    | .2 E    | PROM    | opt     | ion  | (1)     | 0 01    | : 12  | . 5   | MHz   |       |       |

|                |          |         | CPU;    |         |         |         |      |         |         |       |       |       |       | 5-19  |

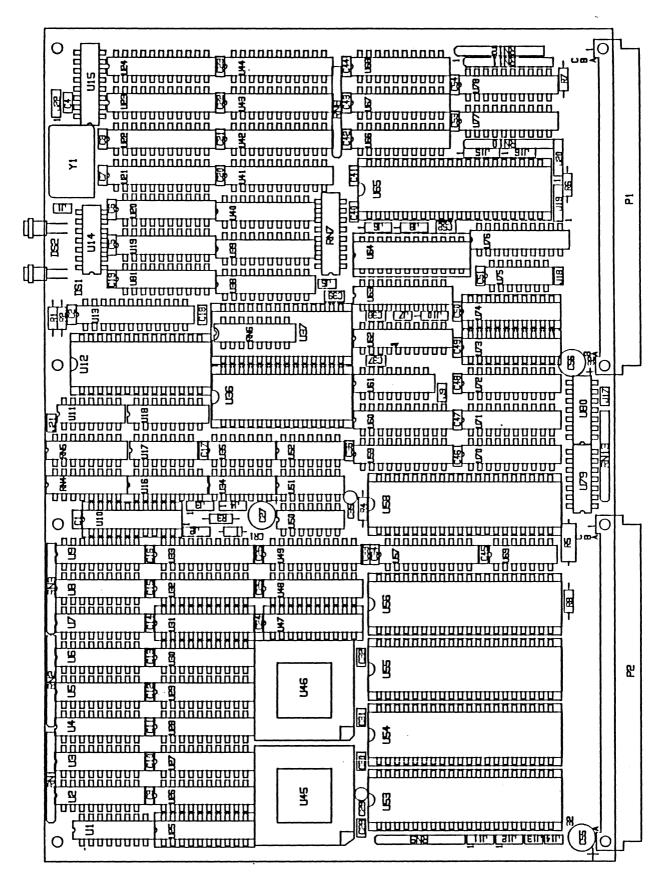

| 5.3            | IV16     | 24 c    | ompo    | nen     | t la    | yout    | di   | agra    | am (    | (1X)  |       |       | • • • | 5-21  |

|                |          |         |         |         |         |         |      |         |         |       |       |       |       |       |

| Appendix       | A        | I V-1   | 624     | feat    | ture    | s       |      | • • •   | • • • • |       |       |       | • • • | A-1   |

| A.1            | Phys     | ical    | spe     | cif:    | icat    | ions    |      |         | • • • • |       |       |       | • • • | À-3   |

| A.2            | Envi     | ronm    | enta    | 1 sp    | peci    | fica    | tio  | ns.     |         |       |       |       | • • • | A-3   |

| A.3            | Opti     | onal    | fea     | ture    |         |         |      |         |         |       |       |       |       | A-3   |

| A.4            | Stan     |         |         |         |         |         |      |         |         |       |       |       |       | A – 4 |

|                |          |         |         |         |         |         |      |         |         |       |       |       |       |       |

| Appendix       | В        | 6801    | 0 da    | ta.     |         |         |      |         |         |       |       |       |       | B-1   |

|                |          |         |         |         |         |         |      |         |         |       |       |       |       |       |

| Appendix       | C        | VM Eb   | us b    | acki    | olan    | e pi    | n a  | ssic    | anme    | ents  |       |       |       | C-1   |

| P.P.O.I.G.E.I. | <u>.</u> |         | •       |         |         |         | -    |         | ,       |       | • • • |       |       |       |

| Appendix       | D        | liser   | -def    | ined    | 1 T/0   | ) ba    | ckp  | lane    | o ni    | n     |       |       |       |       |

| assignmer      |          |         |         |         |         |         |      |         |         |       |       |       |       | D-1   |

| assignmen      | 163      | • • • • | • • • • | • • • • | • • • • | • • • • | •••  | • • • • | • • • • | • • • | •••   | • • • | • • • | -     |

| Appendix       | Er.      | 5010    | atod    | Dr 7    | 1 10    | ai a    | tah  | 100     |         |       |       |       |       | E-1   |

|                |          |         |         |         |         |         |      |         |         |       |       |       |       | E-3   |

| E.1<br>E.2     |          |         |         |         |         |         |      |         |         |       |       |       |       | E-5   |

|                |          |         |         |         |         |         |      |         |         |       |       |       |       | E-7   |

| E.3            | 177 7    | 624     | IACK    | uec     | :00e)   | L       |      |         | • • •   | • • • | • • • | • • • | • • • | E-7   |

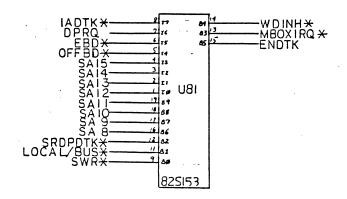

| E.4            | 1 V-1    | 024     | map     | aeco    | oger    | PLA     | (2   | 30K)    | • • •   | • • • | • • • | • • • | • • • |       |

| E.5            | 1 A-T    | 024     | мар     | aeco    | aer     | PLLA    | (6   | 4K) .   | • • • • | • • • | • • • | • • • | • • • | E-12  |

| <b>.</b>       | -        | a '     | • •     |         |         |         |      |         |         |       |       |       |       | T77 1 |

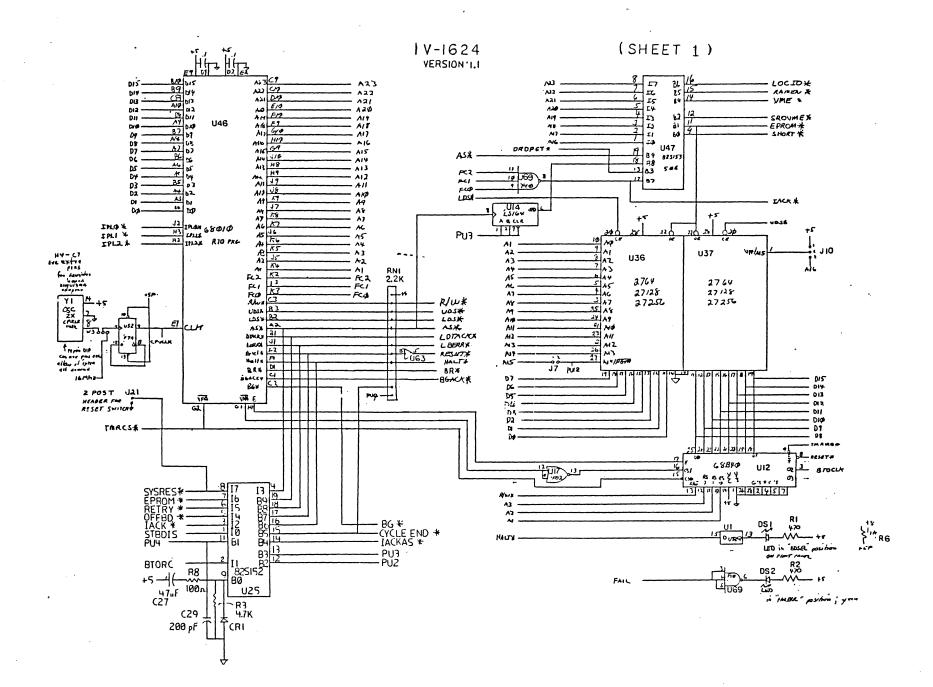

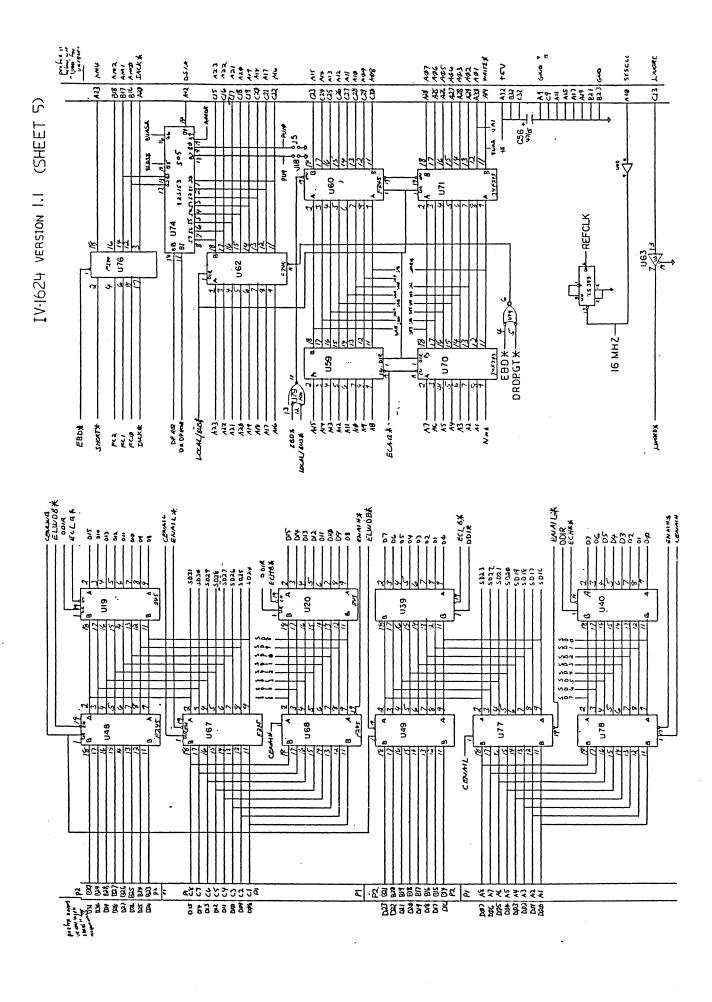

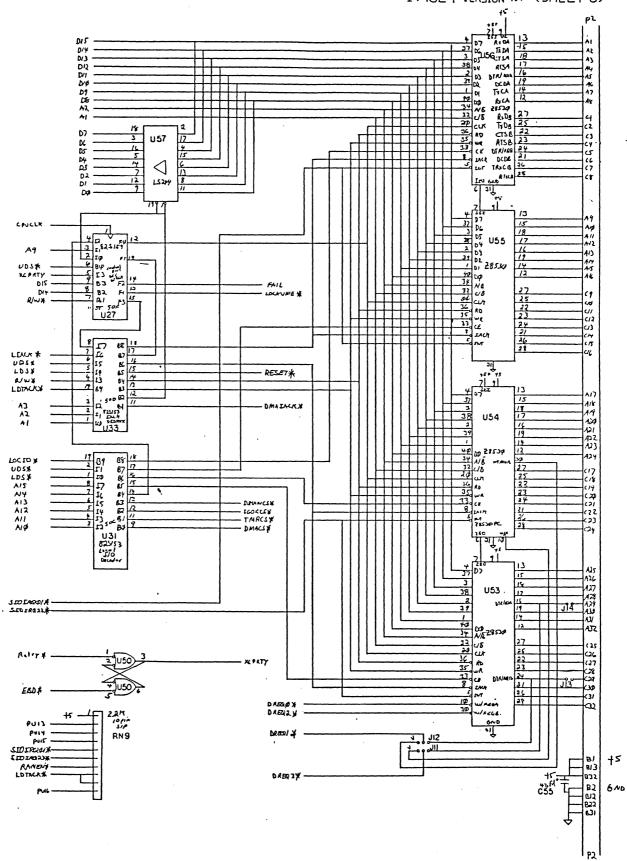

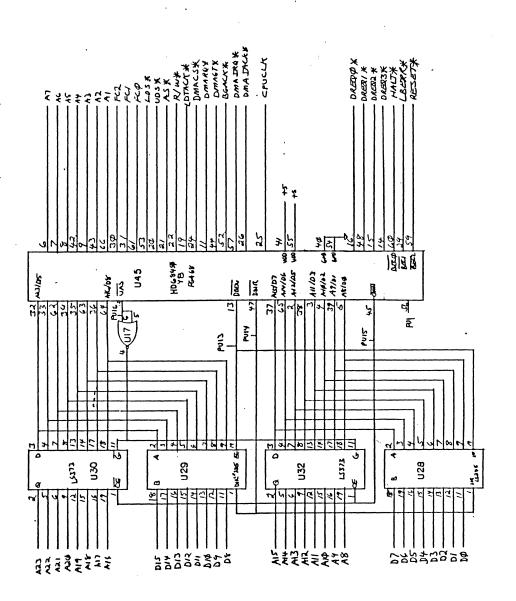

| Appendix       | r        | scne    | mat1    | CS.     |         |         |      |         |         |       |       |       | • • • | F-1   |

# LIST OF FIGURES

| Figure | 1-1. | IV-1601 VMXCPU block diagram                                  | 1-16  |

|--------|------|---------------------------------------------------------------|-------|

| Figure | 1-2. | IV-1602 CPU block diagram                                     | 1-18  |

| Figure | 1-3. | IV-1624 8-port Intelligent SIO board block diagram            | 1-20  |

| Figure | 1-4. | IV-3201 32-bit CPU block diagram                              | 1-22  |

| Figure | 1-5. | IV-3273 System Controller block diagram                       | 1-24  |

| Figure | 2-1. | Backplane pin designation                                     | 2-7   |

| Figure | 2-2. | IV-1624 cable installation                                    | 2-7   |

| Figure | 2-3. | Proper installation of cables 'A' and 'C' to backplane        | 2-8   |

| Figure | 2-4. | Proper installation of cable 'A' or 'C' on serial I/O adapter | 2-10  |

| Figure | 2-5. | Proper installation of power wires to serial I/O adapters     | 2-12  |

| Figure | 3-1. | Map decoder pin assignments                                   | 3-6   |

| Figure | 3-2. | Reset/Retry PLA inputs                                        | 3-10  |

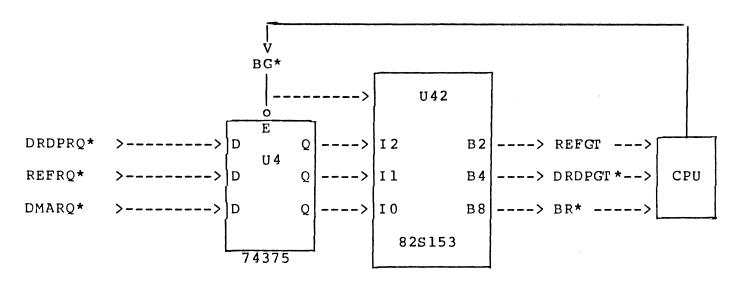

| Figure | 3-3. | Bus request circuit                                           | 3-17  |

| Figure | 4-1. | EPROM shunt header locations                                  | 4 – 4 |

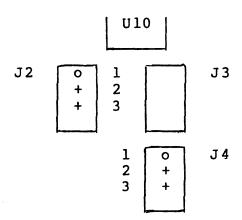

| Figure | 4-2. | Dynamic RAM shunt locations (J2 and J4)                       | 4 – 5 |

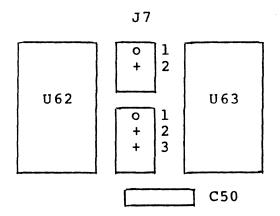

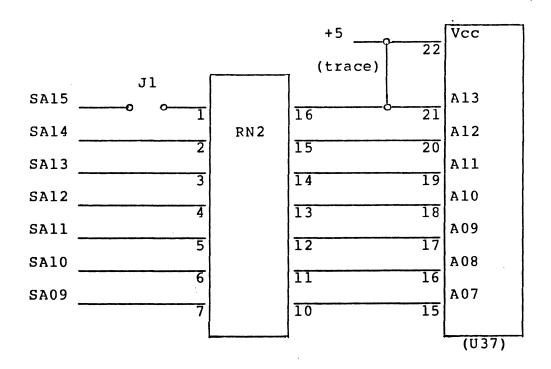

| Figure | 4-3. | Static RAM schematic representation                           | 4 – 6 |

| Figure | 4-4. | Dual port shunt locations                                     | 4-8   |

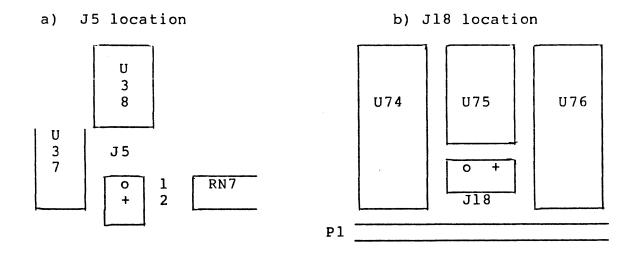

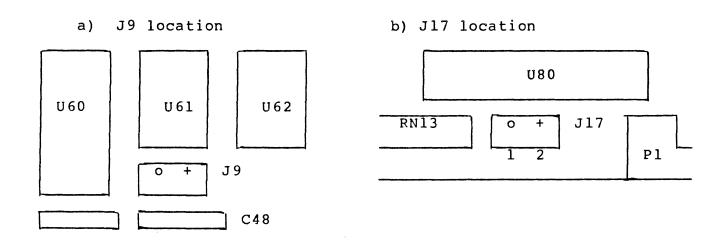

| Figure | 4-5. | Bus release shunts (J9 and J17)                               | 4-10  |

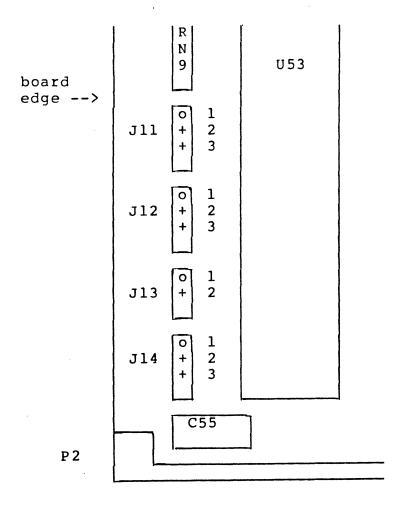

| Figure | 4-6. | Bus grant shunts                                              | 4-12  |

| Figure 4-7  | Location of serial I/O and DMA shunts |      |

|-------------|---------------------------------------|------|

| •           | or serial 1/0 and DNA shunes          | 4-14 |

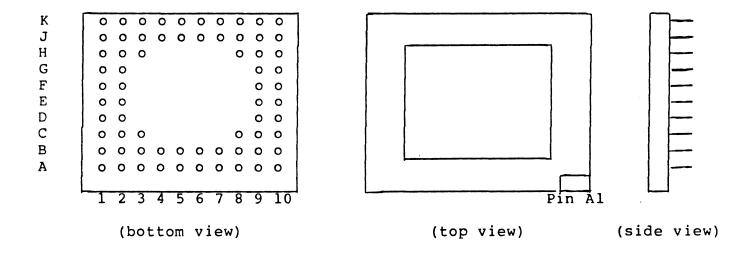

| Figure B-1. | Socket layout and footprint           | B-3  |

•

.

## LIST OF TABLES

| TABLE | 1-1. | IRONICS multiprocessing family feature comparison             | 1-13  |

|-------|------|---------------------------------------------------------------|-------|

| TABLE | 1-2. | IRONICS multiprocessing family feature comparison (continued) | 1-14  |

| TABLE | 1-3. | General references                                            | 1-25  |

| TABLE | 1-4. | Specific references                                           | 1-26  |

| TABLE | 2-1. | IV-1624 serial I/O adapter description                        | 2-5   |

| TABLE | 2-2. | Power cable pin assignment for electrical interface adapters  | 2-12  |

| TABLE | 3-1. | IV-1624 PLA/PAL descriptions                                  | 3-3   |

| TABLE | 3-2. | IV-1624 standard memory map configuration                     | 3-6   |

| TABLE | 3-3. | IV-1624 Local I/O map                                         | 3-8   |

| TABLE | 3-4. | Bytewide Devices                                              | 3-9   |

| TABLE | 3-5. | EPROM DTACK* speed                                            | 3-9   |

| TABLE | 3-6. | Programmable timer I/O map                                    | 3-15  |

| TABLE | 3-7. | Dynamic and static RAM dual port address ranges               | 3-23  |

| TABLE | 3-8. | Interrupt handler inputs                                      | 3-26  |

| TABLE | 3-9. | SCC Interrupt Priority                                        | 3-29  |

| TABLE | 4-1. | IV-1624 shunts                                                | 4-3   |

| TABLE | 4-2. | EPROM shunt installation matrix                               | 4 – 4 |

| TABLE | 4-3. | Dynamic RAM shunt installation matrix (J4)                    | 4 – 5 |

| TABLE | 4-4. | Dynamic RAM shunt installation matrix                         | 4-5   |

| TABLE 4-5.  | Static RAM shunt installation matrix                | 4 – 6 |

|-------------|-----------------------------------------------------|-------|

| TABLE 4-6.  | Dual port shunt installation for 64K DRAM option    | 4 – 7 |

| TABLE 4-7.  | Dual port shunt installation for 256K option        | 4 – 8 |

| TABLE 4-8.  | Bus release shunt installation matrix               | 4 – 9 |

| TABLE 4-9.  | VMEbus grant level selection shunt installation     | 4-11  |

| TABLE 4-10. | VMEbus request level selection                      | 4-12  |

| TABLE 4-11. | Shunt installation for serial I/O without DMA       | 4-13  |

| TABLE 4-12. | Half duplex and full duplex mode shunt installation | 4-13  |

| TABLE 5-1.  | Abbreviations for manufacturers                     | 5-3   |

| TABLE B-1.  | 68010 68-Terminal PGA pin designations              | B-4   |

| TABLE C-1.  | VMEbus J1/P1 Row Λ Pin Assignments                  | C-3   |

| TABLE C-2.  | VMEbus J1/P1 Row B Pin Assignments                  | C-4   |

| TABLE C-3.  | VMEbus J1/P1 Row C Pin Assignment                   | C-5   |

| TABLE C-4.  | VMEbus J2/P2 Row B Pin Assignments                  | C-6   |

| TABLE D-1.  | J2/P2 Row A Pin Assignments                         | D-2   |

| TABLE D-2.  | J2/P2 Row C Pin Assignments                         | D-3   |

.

#### 0. READ THIS BEFORE UNPACKING

Welcome to the family of IRONICS users. To expedite the integration of your card into a target system, the board has been shipped in a standard configuration. We hope that you will follow the UNPACKING, INSPECTION, and FUNCTIONAL CHECKOUT procedures outlined in chapter 2 before attempting your own configuration.

#### NOTE:

The preliminary functional tests outlined in section entitled "FUNCTIONAL CHECKOUT" require a specific board configuration. Your new board has been configured for test procedures. Do not alter jumper or shunt configuration prior to testing!

#### 1. GENERAL INFORMATION

#### 1.1 History of the IRONICS multiprocessing family

Members of the multiprocessing family represent the second generation of IRONICS high-performance, cost-effective CPU and intelligent I/O boards. The members of this family include:

- [1] the IV-1601 VMXCPU board

- [2] the IV-1602 Single Board Computer

- [3] the IV-1624 8-port Intelligent Serial I/O board

- [4] the IV-3201 68020 VME/VMX CPU board

- [5] the IV-3273 System Controller board

All members of this family conform to the Eurocard dual-height form factor without compromising the high performance levels pioneered by the IV-1600 System Foundation Module. This performance package has been achieved by coupling the IV-1600's 68000/VME architecture to designs with higher board density and with the use of chips with greater levels of internal integration.

#### 1.2 Philosophy of Design: Multiprocessing Engines

IRONICS has created a family of products designed to function as "multiprocessing engines". This implies:

- [1] that all family boards are designed to function and communicate with other CPU and intelligent I/O cards meeting VME (revision C) specifications;

- [2] that each board acts as an "engine": that is, each is dedicated to a range of system control and I/O functions for the VME multiprocessing environment.

These functions provide the basis for a complete, fully-integrated, multiprocessing system. The family architecture addresses specific needs of the multiprocessing environment, including:

- [1] the need for a diverse range of system tools

- [2] the need for maximum processing speed

- [3] the need for large amounts of local RAM, available to other processors with minimum latency

- [4] the need for efficient data transfer mechanisms

[5] the need for interprocessor communications tools (i.e., semaphoring tools and interrupt-on-access ("mailbox") interrupts)

Each of these needs is addressed in more detail in the following section.

#### 1.3 System performance considerations

#### 1.3.1 Functional diversity

Tables 1.1 and 1.2 show a comparison of major features available on IRONICS multiprocessing family boards. In spite of the functional diversity of the individual boards, all multiprocessing family members share a common, modular design which will, we believe, once mastered, reduce the overall time and effort required to integrate cards into a multiple processor system.

#### 1.3.2 CPU performance

Multiprocessing members use either the 68010 CPU (IV-1601, IV-1602, and IV-1624) operating at 10 or 12.5 MHz, or the 68020 CPU (IV-3201) operating at 12.5 or 16 MHz.

#### 1.3.3 Memory

The IRONICS multiprocessing architecture includes large amounts of local, no wait-state, dead-lock protected shared (dual-ported) memory. The large local memory ensures each processor within the multiple processor environment executes at close to full speed. Up to 1 Mbyte of state free memory can be provided on the IV-1601, IV-1602 and IV-3201 with a 512K RAM daughter board. Additional wait-state free memory can be provided on boards possessing a VMXbus interface (the IV-1601 and IV-3201 CPU boards). the RAM chips required to obtain full operation over the VMXbus or VMEbus are faster than required to obtain full speed operation of local RAM.)

A single, large local RAM is the least expensive path to high performance except for very large systems requiring multiple megabytes of RAM, which benefit from a cache. Note also that systems in which the CPUs are required to fetch instructions over the VMEbus typically run with two or three wait states. When more than two such CPUs are installed in the system, additional wait states are required because their VMEbus bandwidth is almost entirely consumed by instruction fetches. Thus, large local RAMs are essential to multiprocessing.

The IRONICS multiprocessing architecture provides a large local memory for each processor. As a result, each board may execute instruction fetches out of its own local memory, virtually eliminating the need for trans-VMEbus instruction fetching. This allows high bandwidth peripherals (local area networks, SMD drives, camera input devices, etc.) to be added to the system without degrading individual CPU performance.

#### 1.3.4 Data transfer mechanisms

The performance of the multiprocessing system described above is optimized by improving the efficiency of the basic data transfer mechanism. This involves increasing the data pathwidth, reducing the amount of time required to obtain access to the data pathway, and finally, by forcing the bus master to vacate the bus rapidly once a transfer has completed.

#### 1.3.4.1 Interprocessor communication pathways

The data transfer mechanism for interprocessor communication is a 32-bit data path to dual-ported static RAM (available on the IV-1624 8-port Intelligent Serial I/O board and IV-1601 CPU). The path width and rapid access time (less than 120 ns) provide a data rate that is four to twelve times faster than that available with dual-ported dynamic RAM with a 16-bit data pathway.

#### 1.3.4.2 Dual port access time

The static RAM access time is further reduced because of its separation from the local CPU, isolated from the CPU by a set of buffers. Accesses to the static RAM through its dual-port interface do not slow the local CPU unless the CPU is, simultaneously, trying to access the local static RAM. In addition, this memory is equipped with a fast, asynchronous arbiter which doesn't require that local CPU cycles be retried in order to resolve a deadlock.

#### NOTE:

This is not the case with dynamic RAM dual port arbiters such as that of the IV-1601 VMXCPU or that of other manufacturer's CPU boards. For a more detailed description of dynamic RAM dual-port lockout, see chapter 3.

#### 1.3.4.3 Rapid strobe deassertion

In a multiprocessing environment, the speed with which a bus master vacates the bus after completing a transaction is as important as the slave's access time in determining performance. All members οf the IRONICS multiprocessing family utilize "rapid feature called а strobe deassertion" on VMEbus write cycles. This feature gets them off the bus almost two CPU clock cycles faster is characteristic of CPU boards without rapid strobe This deassertion. feature also allows more interprocessor interrupt/response More message time. specifically: processors communicate by writing another's MAILBOX RAM location, then poll their own local dual-ported memory for the response. Thus, the majority of VMEbus traffic of this type are write cycles which require half as much bandwidth as read cycles. Fast strobe also frees the dual-port memory for use by its deassertion local master sooner.

#### 1.3.5 Interprocessor communication primitives

A major concern within the multiprocessing environment the integrity of interprocessor communication. In addition to the obvious advantages of having a fast message/response the system which can insure the integrity of semaphores sent from processor to processor greatly reduces the probability of system failure and loss of data. IRONICS architecture has deadlock-protected, shared memory, interrupt mechanisms, and quaranteed indivisibility semaphore operations. As part of the communications scheme, mailbox interrupt (MBOXIRO\*) is issued to the local processor when a message or semaphore is written upper 256 bytes of static RAM through the dual-port pathway (note: the interrupt occurs only when one or more of upper 256 bytes of static RAM are written to, and only on a write cycle). This comprises a complete interprocessor communications primitives which are required to take full advantage of multiple processors.

#### 1.4 IRONICS multiprocessing family members

The following sections provide a brief overview of individual family members. Block diagrams of each product are shown in figures 1-1 through 1-5. To obtain technical information, contact an IRONICS customer service representative.

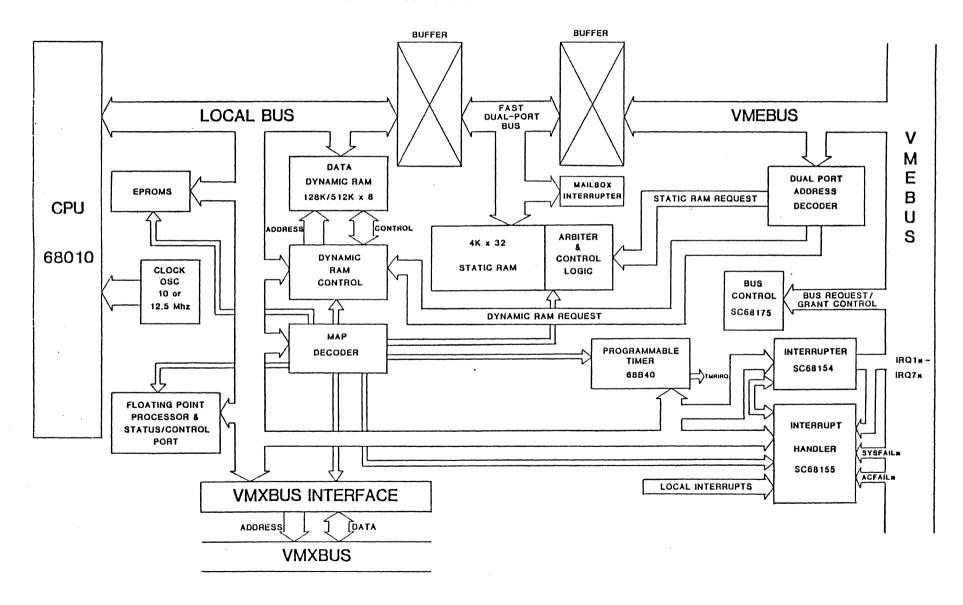

#### 1.4.1 The IV-1601 VMXCPU board: the multiprocessing engine

The 68010-powered IV-1601 provides the functionality of a "multiprocessing engine"; that is, a auxilary CPU with the intelligence and resources distribute and facilitate system tasks. Its self-contained resources (e.g., floating point processor) equip it for number crunching applications. Its VMEbus interface allows it to offload I/O control tasks from a main CPU: it simply uses the VMEbus to control "dumb" VMEbus I/O cards and to communicate with the master CPU. With the VMXbus, a user can quickly implement a two to six card intelligent I/O system using the VMXbus interface to I/O controllers.

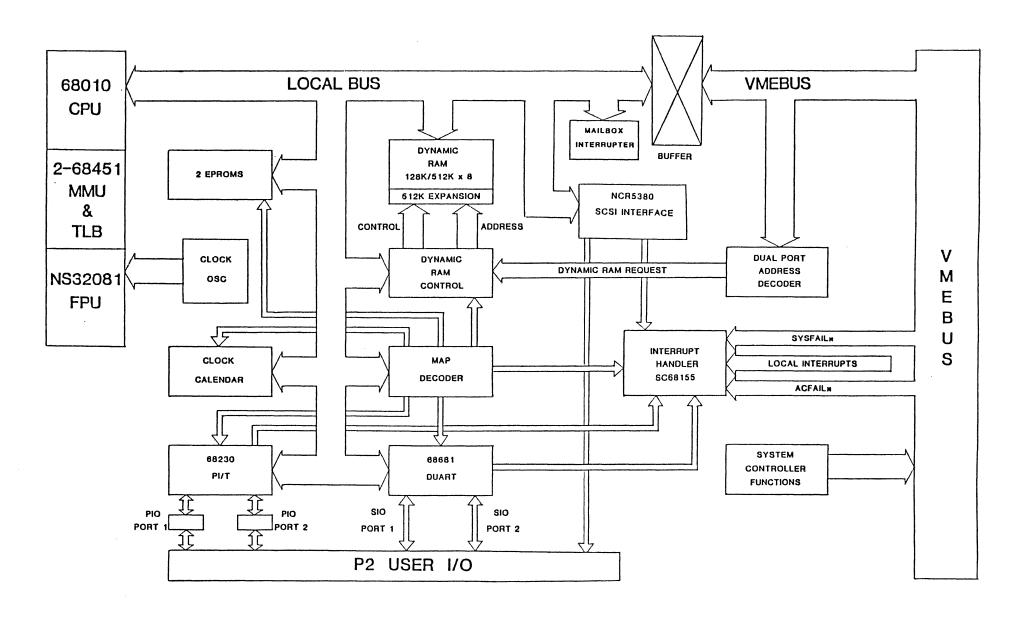

#### 1.4.2 The IV-1602 Single Board Computer

The IV-1602 VMEbus Single Board Computer provides all the self-contained resources for a central CPU. The IV-1602 is a VMEbus CPU board with optional memory management, optional floating point processor, large amounts of onboard, dynamic, wait-state free, dual-ported RAM (expandable to 1 Megabyte with a RAM daughter board). In contrast to its sibling, the IV-1601 VMXCPU, the IV-1602 has serial ports to accomodate a system console, and supports system controller functions. Its on board functions allow it to stand alone as a board computer. The IV-1602 architecture also includes a SCSI bus interface for connection to mass storage peripherals.

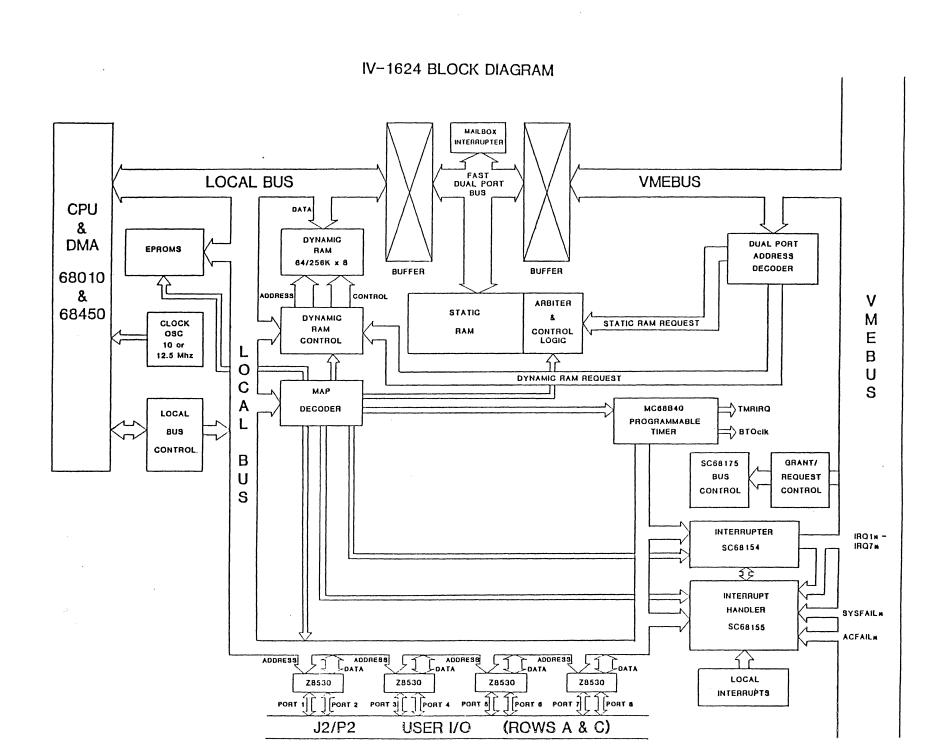

#### 1.4.3 The IV-1624 8-port Intelligent Serial I/O board

The IV-1624 8-Port Intelligent Serial I/O card retains many of the features as well as the modularity of design of other members of the Ironics multiprocessing family. 1624 card has, in addition to onboard dual-ported static and dynamic RAM, an optional four channel DMA and 8 fullduplex multi-protocol serial I/O channels. It is ideally suited as a communications processor for UNIX systems, especially 68020-based multi-user systems. The DMA controller option allows transfers on up to 6 channels at up to 9600 baud asynchronously plus two channels at l synchronously. Mbaud downloadable Α driver multichannel asynchronous operation is currently development. The IV-1624 is user-programmable for this and protocols. Complete electrical and physical specifications are included in Appendix A.

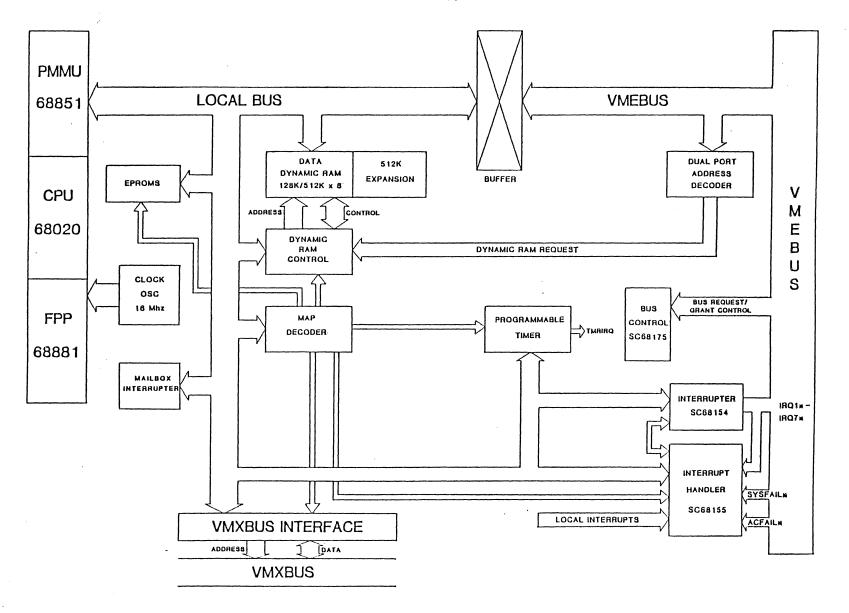

#### 1.4.4 IV-3201 68020 VME/VMX CPU board

The IV-3201 68020 VME/VMX CPU is the 32-bit analog of the IV-1601 VMX CPU. It provides up to 1 Megabyte of local, wait-state free RAM. Powered by a 16 or 12.5 MHz CPU, and supported the large local, dual-ported memory, the IV-3201 achieves superior performance without the cost of a cache. In addition, it has two independent 32-bit bus interfaces. This allows expansion of tightly resources via the VMXbus (private) bus and interprocesssor communication and global resource utilization via VMEbus. IV-3201 VME/VMX shares all The οf interprocessor

communications primitives of its sibling, the IV-1601, including: bus interrupter and interrupt handler modules, mailbox interrupts, indivisible read-modify-write cycles, etc.

#### 1.4.5 IV-3273 System Controller board

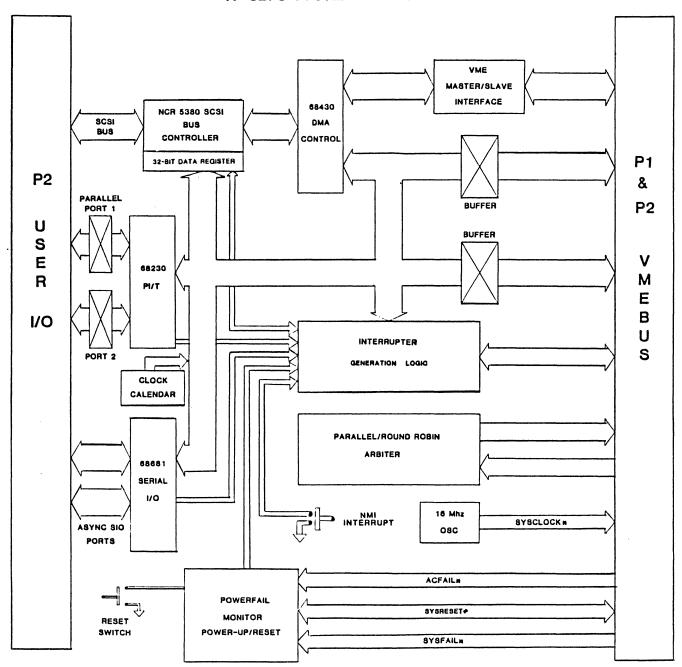

The IV-3273 is a non-processor board which provides all VMEbus system controller functions plus additional functions

needed to complete a system with the IV-1601, IV-3201, IV-IV-1624 1602, and/or boards. Its four level, parallel/round-robin arbiter design is fully asynchronous for optimum speed, yet fully protected from metastable states. Its SCSI bus interface supports full bus protocol including host to host communications and supports over 1 million transfers per second. The SCSI bus interface is DMA-driven and utilizes 16 or 32 bit VMEbus data transfers. The parallel Centronics printer interface is interruptdriven. The IV-3273 also includes a clock/calendar chip with battery backup, a power monitor module, system clock, system reset generator and two programmable timers.

TABLE 1-1. IRONICS multiprocessing family feature comparison

| FEAT URE       |      |      | PRODUCT |      |      |

|----------------|------|------|---------|------|------|

|                | 1601 | 1602 | 1624    | 3201 | 3273 |

| CPU:           |      |      |         |      |      |

| 68010 10 MHz   | +    | +    | +       | -    | _    |

| 12.5 MHz       | +    | +    | +       | -    | -    |

| 68020 12.5 MHz | _    | _    | _       | +    | _    |

| 16 MHz         | _    | -    | -       | +    | -    |

| DRAM*: 64K     | _    | _    | +       | _    |      |

| 128K           | +    | +    | -       | -    | -    |

| 512K           | +    | +    | -       | +    | -    |

| 1 Mbyte        | +    | +    | -       | +    | -    |

| SRAM*: 16K     | +    | ose  | +       | -    |      |

| 64K            | +    | -    | +       | -    | -    |

| EPROM: 8Kx8    | +    | +    | +       | +    |      |

| 16K×8          | +    | +    | +       | +    | -    |

| 32Kx8          | +    | +    | +       | +    | -    |

| 64Kx8          | +    | +    | +       | +    | -    |

| 128Kx8         | +    | +    | +       | +    | -    |

| INTERRUPTER:   | +    | +    | +       | +    | +    |

| INTERRUPT      |      |      |         |      |      |

| HANDLER:       | +    | +    | +       | +    | -    |

| FPP: NS32081   | +    | +    | -       | _    | _    |

| MC68881        | -    | -    | -       | +    | -    |

| VME INTERFACE: |      |      |         |      |      |

| master         | +    | +    | +       | +    | +    |

| slave          | +    | +    | +       | +    | +    |

| VMX INTERFACE  | +    | -    | -       | +    | -    |

# \* All RAM dual-ported

(table continued on next page)

TABLE 1-2. IRONICS multiprocessing family feature comparison (continued)

| FEAT URE                | PRODUCT     |        |                   |                                        |      |  |  |  |

|-------------------------|-------------|--------|-------------------|----------------------------------------|------|--|--|--|

|                         | 1601        | 1602   | 1624              | 3201                                   | 3273 |  |  |  |

| SERIAL I/O:             |             |        |                   | ************************************** |      |  |  |  |

| MC68681<br>Z8530        | -           | +      | <del>-</del><br>+ | -                                      | +    |  |  |  |

| 28530                   | <del></del> | -      | +                 | -                                      | -    |  |  |  |

| PARALLEL I/O:           |             |        |                   |                                        |      |  |  |  |

| SCN68230                | -           | +      | _                 | -                                      | +    |  |  |  |

| COUNTER/TIMER:          |             |        |                   |                                        |      |  |  |  |

| MC68B40                 | +           | -      | +                 | -                                      | -    |  |  |  |

| CLOCK/CALENDAR          | _           | +      | -                 | _                                      | +    |  |  |  |

|                         |             |        |                   |                                        |      |  |  |  |

| MMU: MC68851            | -           | +      | -                 | +                                      | -    |  |  |  |

| ARBITER:                |             |        |                   |                                        |      |  |  |  |

| MC68451 round-          |             |        |                   |                                        |      |  |  |  |

| robin/parallel          |             | -<br>+ | -                 | -                                      | +    |  |  |  |

| single-level            | -           | *      | -                 | -                                      | -    |  |  |  |

| SYSCLOCK                |             |        |                   |                                        |      |  |  |  |

| GENERATOR:              | -           | +      | -                 | -                                      | +    |  |  |  |

| SCSI INTERFACE          |             |        |                   |                                        |      |  |  |  |

| NCR5380                 | _           | +      | _                 | _                                      | +    |  |  |  |

| DV1                     |             |        | _                 |                                        |      |  |  |  |

| DMA: MC68450<br>MC68430 | -           | -<br>- | +                 | -                                      | -    |  |  |  |

|                         |             |        |                   |                                        | ·    |  |  |  |

| POWER FAIL              |             |        |                   |                                        | J    |  |  |  |

| MONITOR:                | -           | -      | -                 | , <b>-</b>                             | +    |  |  |  |

| CENTRONICS              | _           | +      | -                 | -                                      | +    |  |  |  |

| PORT:                   |             |        |                   |                                        |      |  |  |  |

|                         |             |        |                   |                                        |      |  |  |  |

# IRONICS MULTIPROCESSING FAMILY BLOCK DIAGRAMS

# Figure 1-1. IV-1601 VMXCPU block diagram (see drawing on opposite page)

## IV-1601 BLOCK DIAGRAM

# Figure 1-2. IV-1602 CPU block diagram

(see drawing on opposite page)

#### IV-1602 SINGLE BOARD COMPUTER

Figure 1-3. IV-1624 8-port Intelligent SIO board block diagram

(see drawing on opposite page)

Figure 1-4. IV-3201 32-bit CPU block diagram

(see drawing on opposite page)

## IV-3201 BLOCK DIAGRAM

Figure 1-5. IV-3273 System Controller block diagram (see drawing on opposite page)

# IV-3273 SYSTEM CONTROLLER

#### 1.5 Technical references

#### 1.5.1 General references

The following publications will be useful to all users of family products. We recommend that all users obtain and familiarize themselves with these documents. Each is available from the vendor.

TABLE 1-3. General references

| MANUAL                                                                                                                                                                                                                                                                            | VENDOR                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| MC68010 User's Manual MC68010 Programmer's Manual MC68010 Data Sheet MC68B40 Programmable Timer Data Sheet VMEbus Specifications (Revision C) SC8X821/68175 VME Bus Controller Data Sheet SC8X824/68155 VME Interrupt Handler Data Sheet SC8X825/68154 VME Interrupter Data Sheet | Motorola<br>Motorola<br>Motorola<br>Motorola<br>Signetics<br>Signetics<br>Signetics |

# 1.5.2 Specific references

The following table shows specific technical references which should be obtained by users of specific multiprocessing family boards. Copies of these documents may be obtained from vendors.

TABLE 1-4. Specific references

| IRONICS | PRODUCT | MANUAL                                                                                                                          | VENDOR                                                             |

|---------|---------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| IV-1601 |         | VMXbus Specification (revision A)                                                                                               | VME Users' Group                                                   |

|         |         | NS32081 FPP Data Sheet                                                                                                          | National Semi-<br>conductor                                        |

| IV-1602 |         | SCN68230 PI/T Data Sheet<br>SCN68681 DUART Data Sheet<br>MOS Microprocessor Data Manual<br>MM58274 Clock/calendar<br>Data Sheet | Signetics<br>Signetics<br>Signetics<br>National Semi-<br>conductor |

| IV-1624 |         | MC68450 DMA Controller Data Sheet                                                                                               | Motorola                                                           |

|         |         | Z8530 Data Sheet                                                                                                                | Zilog                                                              |

|         |         | Z8030/Z8530 SCC Technical Manual                                                                                                | Zilog                                                              |

|         |         | Z8030/Z8530 SCC Application Note                                                                                                | Zilog                                                              |

| IV-3201 |         | MC68851 HCMOS PAGED MMU                                                                                                         | Motorola                                                           |

|         |         | MC68881 Floating Point Processor Data Sheet                                                                                     | Motorola                                                           |

|         |         | MC68020 Data Sheet                                                                                                              | Motorola                                                           |

|         |         | MC68020 User's Manual                                                                                                           | Motorola                                                           |

|         |         | VMXbus Specification (revision A)                                                                                               | VME Users' Group                                                   |

| IV-3273 |         | NCR5380 SCSI Bus Controller<br>Data Sheet                                                                                       | NCR                                                                |

|         |         | SCN68430 DMA Interface Data Sheet                                                                                               | Signetics                                                          |

|         |         | MOS Microprocessor Data<br>Manual                                                                                               | Signetics                                                          |

|         |         | SCN68230 PI/T Data Sheet                                                                                                        | Signetics                                                          |

|         |         | SCN68681 DUART Data Sheet                                                                                                       | Signetics                                                          |

|         |         | MM58274 Clock/calendar                                                                                                          | National Semi-                                                     |

|         |         | Data Sheet                                                                                                                      | conductor                                                          |

#### 1.6 Customer service

For more information about IRONICS multiprocessing products, contact a customer service representative by writing or calling:

IRONICS Customer Service 798 Cascadilla Street Ithaca, New York 14850 (607) 277-4060 2. INSPECTION, INSTALLATION, AND CHECKOUT

#### 2.1 Unpacking Instructions

All IRONICS products are manufactured in a static-free environment to insure minimal degradation in component performance due to electrical discharge. All boards are shipped in conductive wrapping for protection during shipping. The following precautions should be observed during unpacking and installation:

- [1] All board handlers should be properly grounded and working in static-free work areas.

- [2] Boards should be handled by board edges, avoiding contact with all connector surfaces.

- [3] Avoid touching any MOS components.

#### 2.2 Inspection

After removing the board from its protective wrapping, inspect the board. Any loose debris should be be removed from the board surface. Inspect the following:

- [1] Check all chips in sockets (EPROMs, PLAs, etc.) for loose seating. Apply even pressure on top of chip to reseat, if necessary.

- [2] Check socketed chips for bent pin legs or bad connections.

- [3] Check bottom of the board for broken or loose jumper wires (if present).

- [4] Check the board surface for warping.

Report any serious board irregularities IMMEDIATELY to:

CUSTOMER SERVICE REPRESENTATIVE

IRONICS, INC.

798 Cascadilla Street

Ithaca, New York

(607) 277-4060

#### 2.3 Installation procedure

Before proceding, read the manual. Many of the board's finer design aspects have been described in chapter 3. Basic familiarity with the board could save hours of debugging, and will make our job of maintaining and servicing your IRONICS purchase faster and easier.

#### 2.3.1 Minimum system requirements for checkout

The minimum amount of hardware and software required for a board test is as follows:

- [1] IMON1624 v3.1 DEBUG MONITOR installed in the IV-1624 EPROM sockets (or some other suitable debug monitor allowing memory accesses).

- [2] VMEbus system controller card

- [3] IV-1624 8-Port Intelligent Serial I/O Board

- [4] Serial I/O module + cable assembly

# 2.3.2 Shunt installation

The board (as shipped) should have the shunts in place for minimum system functions (i.e., EPROM, local and dual port RAM access, etc). Verify that IV-1624 shunt installation is correct by comparing installation with descriptions in chapter 3. Make sure that the bus request/ bus grant shunts are installed.

#### Note:

The bus request/grant jumpers must be configured to level 3 when configured with the IV-1600 System Foundation Module or with any other CPU card with a single-level arbiter!

#### 2.3.3 VMEbus cable installation

The data and control lines which comprise eight serial ports are bussed to row A and row C of the P2 connector (J2/P2 pin assignments are provided in the Appendix section of the manual). These signals are relayed from the backplane to

line driver/receiver cards (and the eight female or male connectors) via a serial I/O module/cable assembly. This assembly and its installation will be described in more detail next.

#### WARNING:

Proper installation of the serial module/cable assembly is critical. Improper installation may result in damage to the board. Please read the next sections THOROUGHLY before attaching the cable and applying power!

#### 2.3.4 Serial I/O adapters

IRONICS provides the ability to transfer serial data through one of three standard electrical interfaces adapters. The three standard interfaces may be purchased with DTE or DCF connectors. The following table shows the available serial I/O adapters:

TABLE 2-1. IV-1624 serial I/O adapter description

| Description  |                                                                      |                                                                                             |                                                                                          |

|--------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| RS-232 DCE   | IV-1624                                                              | only                                                                                        |                                                                                          |

| RS-232 DTE   | 11                                                                   | "                                                                                           |                                                                                          |

| RS-449 DCE   | 11                                                                   | 11                                                                                          |                                                                                          |

| RS-449 DTE   | А                                                                    | il                                                                                          |                                                                                          |

| Current loop | **                                                                   | 11                                                                                          |                                                                                          |

| Current loop | **                                                                   | •                                                                                           |                                                                                          |

|              | RS-232 DCE<br>RS-232 DTE<br>RS-449 DCE<br>RS-449 DTE<br>Current loop | Description Not  RS-232 DCE IV-1624 RS-232 DTE "  RS-449 DCE " RS-449 DTE "  Current loop " | RS-232 DCE IV-1624 only RS-232 DTE " "  RS-449 DCE " "  RS-449 DTE " "  Current loop " " |

Modules may be purchased in groups of four (4). One cable is required for each group of four serial ports desired. Hence, two cables are required to use more than four (4) ports.

#### NOTE:

The type of serial interface (e.g., RS-232, RS-449 or current loop), connector sex (male or female), and the connector mode (DCE/DTE) should be specified at the time of purchase.

Modules are shipped assembled with the cable assembly attached.

#### 2.3.5 Adapter cable installation

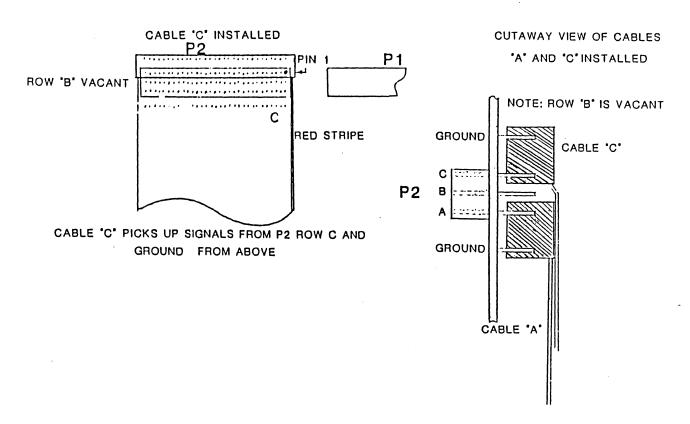

The cable required to connect the backplane serial I/O pins on P2 rows A or C to the serial I/O adapters is a 64-wire ribbon A 64-pin female connector busses the serial data and control lines from the 4 serial ports of row A or from row C (see figures 1.1 and 1.2; refer to the Appendix section of the manual for P2 channel designations).

The opposite end of the cable is split into four parts, each of which is terminated by a 16-pin female connector. Each of the four 16-pin connectors attach to a unique serial I/O adapter to interface a serial channel. Two cables are included.

To use ports 1 through 4:

- The cable marked "A" busses those serial ports (ports 1-4) which originate from row "A" of the backplane and the ground row immediately below it. The red cable stripe should be closest to pin 1 of P2 (refer to figures 2.2 and 2.3).

- The cable marked "C" busses those serial ports (ports 5-8) which originate from row "C" of the backplane and the ground row immediately above it. The red cable stripe should be closest to pin 1 of P2 (refer to figures 2.2 and 2.3).

- There is no cable "B": Connection of a cable to pins on row B will result in the shorting of power (+5V) to ground and in serious damage to the board.

Figure 2-1. Backplane pin designation

This figure shows the backplane pins as viewed by someone looking at the back of the card cage.

| P<br>I<br>N |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | P<br>I<br>N |                   |     |

|-------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------------|-------------------|-----|

| 3<br>2      |   |   |   |   |   |   |   |   |   |   |   |   |   | P | 2 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0<br>1      |                   |     |

| +           | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | +           | GND               | ROW |

| +           | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | +           | row<br>row<br>row | В   |

| +           | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | + | +           | GND               | ROW |

Figure 2-2. IV-1624 cable installation

| P |   |   |   |    |    |   |   |   |   |   |   |   |    |    |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   | P |     |     |

|---|---|---|---|----|----|---|---|---|---|---|---|---|----|----|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|-----|

| I |   |   |   |    |    |   |   |   |   |   |   |   |    |    |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   | I |     |     |

| N |   |   |   |    |    |   |   |   |   |   |   |   |    |    |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   | N |     |     |

| 2 |   |   |   |    |    |   |   |   |   |   |   |   |    |    |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   | ^ |     |     |

| 3 |   |   |   |    |    |   |   |   |   |   |   |   |    |    |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |     |     |

| 2 |   |   |   |    |    |   |   |   |   |   |   |   | I  | 2  |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   | 1 |     |     |

|   |   |   |   |    |    |   |   |   |   |   |   |   |    |    |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |     |

| + | + | + | + | +  | +  | + | + | + | + | + | + | + | +  | +  | + | + | +   | + | + | + | + | + | + | + | + | + | + | + | + | + | + | GND | ROW |

|   |   |   |   |    |    |   |   |   |   |   |   |   | CF | BL | E | • | 'C' | 1 |   |   |   |   |   |   |   |   |   |   |   |   |   | 1   |     |

| + | + | + | + | +  | .+ | + | + | + | + | + | + | + | +  | +  | + | + | +   | + | + | + | + | + | + | + | + | + | + | + | + | + | + | row | С   |

| + | + | + | + | +. | +  | + | + | + | + | + | + | + | +  | +  | + | + | +   | + | + | + | + | + | + | + | + | + | + | + | + | + | + | row | В   |

| + | + | + | + | +  | +  | + | + | + | + | + | + | + | +  | +  | + | + | +   | + | + | + | + | + | + | + | + | + | + | + | + | + | + | row | A   |

| 1 |   |   |   |    |    |   |   |   |   |   |   |   | CF | BL | Æ | • | 'A' | 1 |   |   |   |   |   | ٠ |   |   |   |   |   |   |   |     |     |

| + | + | + | + | +  | +  | + | + | + | + | + | + | + | +  | +  | + | + | +   | + | + | + | + | + | + | + | + | + | + | + | + | + | + | GND | ROW |

Figure 2-3. Proper installation of cables 'A' and 'C' to backplane

This view shows the 64-pin connector installed on the backplane. Cable "A" picks up signals from P2 row A and ground below. Cable "C" picks up signals from P2 row C and ground above. Note that row B is bussed on the P2 backplane. Neither cable should connect to P2 row B.

# ROW 'B' VACANTA GROUND A RED STRIPE

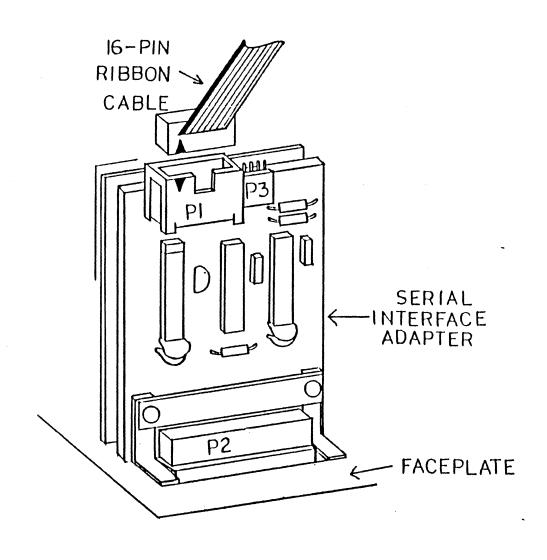

The opposite end of the cable (the four ends terminated with 16-pin male connectors should be shipped already attached to an electrical interface adapter. Refer to Figure 2-4 to insure that the SIO adapter end has been properly installed.

The board is now ready for power-up and test.

Figure 2-4. Proper installation of cable 'A' or 'C' on serial I/O adapter

Cables 'A' and 'C' terminate in eight 16-pin connectors which attach to one of eight electrical interface adapters. The diagram shows one of the cable ends attaching to an adapter. The arrows on the connector and adapter should be aligned.

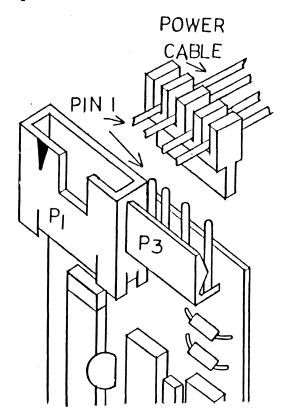

Power is supplied to the serial I/O adapters by way of a four-wire cable (refer to figure 2-5). Table 2-2 shows the voltage supplied by each wire. Make sure that each connector is properly inserted before applying power!

Figure 2-5. Proper installation of power wires to serial I/O adapters

TABLE 2-2. Power cable pin assignment for electrical interface adapters

| Adapter  | Adapter Type |             |  |  |  |  |  |  |

|----------|--------------|-------------|--|--|--|--|--|--|

| Pin No.  | RS-232       | RS-449      |  |  |  |  |  |  |

| <u> </u> | +5           | +5          |  |  |  |  |  |  |

| 2        | GND          | GND         |  |  |  |  |  |  |

| 3        | -12          | NC          |  |  |  |  |  |  |

| 4        | +12          | CHASSIS GND |  |  |  |  |  |  |

|          |              |             |  |  |  |  |  |  |

#### 2.3.6 Power up and test procedure

Turn on power and look for the IMON1624 monitor prompt:

IMON1624 v3.1>

## 2.3.6.1 EPROM checkout

Verify that the entire EPROM address range can be read by typing:

IMON1624 v3.1> MD F00000 FFFF <CR>

If the "MD" command terminates before F0FFFF, contact factory immediately and describe the failure. If the entire range may be read, attempt to write to the EPROM address space with the following command:

IMON1624 v3.1> MM F00000 F0FFFE 00 <CR>

The monitor response should be:

IMON1624 v3.1> MM F00000 F0FFFE 00 <CR>

Physical Address= 00F00000 0F0FFFE

Data did not store

Follow up by displaying the entire range again with the command:

IMON1624 v3.1> MD F00000 FFFF <CR>

The display of memory should show that the '00' pattern written to memory did not store. If the EPROM address

space appears to be written with a solid '00' pattern, notify the factory immediately.

#### 2.3.6.2 On board RAM checkout

Attempt to write and read the entire range of dynamic RAM using the following commands:

IMON1624 v3.1> MD 0 100000 <CR>

This read should terminate with a bus error at the end of the dynamic RAM address range (i.e., bus error at 10000H for 64K or bus error at 040000H for 256K option). If the read terminates before the expected address range, verify that shunts are properly installed.

Attempt to write the entire dynamic RAM address range using the command:

IMON1624 v3.1> BF 0 100000 FF <CR>

Verify visually that the entire range was successfully written. If problems continue (e.g., bus errors before the predicted end of memory, imcomplete writing of the address range), notify the factory.

Repeat the above procedure for the static RAM address range.

#### 2.3.6.3 Dual port access checkout

Attempt to read the IV-1624's dual ported static and dynamic RAM from a remote bus master with the IV-1624 withdrawn from its slot. A bus trap error should result, indicating that no conflicting device has been installed. Insert the IV-1624 and verify that its memory can be read over the entire dual port address.

## 2.3.6.3.1 VMEbus grant/request daisy chain checkout

Verify that the bus request/bus grant daisy chain is complete up to the IV-1624 slot (shunt BGIN\* to BGOUT\* on empty slots).

# 2.3.6.3.2 VMEbus access checkout

Test the VMEbus by attempting to read from and write to another VMEbus slave.

# 3. IV-1624 THEORY OF OPERATION

This chapter is intended to provide an general overview of IV-1624 operation. The board is divided up by functional areas outlined below. Users of other IRONICS multiprocessing boards will be able to see the simularities between the IV-1624 and other family members. We hope that these similarities will lead more rapid understanding of all multiprocessing family members, and hence, faster integration of IRONICS multiprocessing boards into a system.

#### 3.1 Board control logic

Much of the onboard control logic is contained within high-density programmable logic arrays (PLAs and PALs). The following table shows all programmable logic chips and their functions. More detailed descriptions of all PLA and PAL functions are included in the following section. Partial PLA and PAL table contents are provided in Appendix E.

TABLE 3-1. IV-1624 PLA/PAL descriptions

| PLA# | V | U#   | Туре    | Description                             |

|------|---|------|---------|-----------------------------------------|

| 501  | _ | U22  | 825152  | *IV-1624 Reset-retry PLA                |

| 503  | - | U13  | 82S153A | IV-1624 Dual port control PLA#1         |

| 504  | _ | U38  | 82S153A | IV-1624 Dual port control#2             |

| 505  | 0 | U74  | 82S153  | IV-1624 Dual port address decoder (64K) |

| 505  | 2 | U74  | 82S153  | IV-1624 Dual port address decoder(256K) |

| 50C  | _ | U31  | 82S153  | *IV-1624 Local I/O decoder              |

| 50D  | - | U33  | 82S153  | *IV-1624 IACK decoder                   |

| 50E  | 2 | U 47 | 82S153A | *IV-1624 Memory map decoder PLA (256K)  |

| 50E  | 3 | U47  | 82S153A | *IV-1624 Memory map decoder PLA (64K)   |

| 510  | _ | U27  | 82S159  | IV-1624 Control port and SCC timing     |

| 518  | _ | U10  | 82S153A | IV-1624 Dynamic RAM control PLA         |

| 518  | _ | U26  | 82S153  | IV-1624 Local bus arbiter PLA           |

| 51A  | - | U73  | 825153  | IV-1624 Bus release and AMchecker       |

| 51B  | - | U81  | 82S153  | IV-1624 Mail box interrupter            |

V = version number

Asterisk (\*) indicates that logic tables are provided in this manual;

U = location number

#### 3.1 Board level description

The block diagram of the IV-1624 board is provided in figure 1-3. The board is divided into six functional areas:

- 1. The CPU core containing:

- CPU

- Map decoding circuitry

- EPROMs

- RESET/RETRY circuitry

- clock/timer

- LED indicators

- Local bus arbitration circuitry

- 2. The dynamic RAM interface containing:

- dynamic RAM and dynamic RAM controller

- 3. The static RAM interface containing:

- Static RAM and control circuitry

- 4. The VMEbus interface containing:

- Interrupt requesting and handling circuitry

- VMEbus controller

- Bus release circuitry

- VME address, data lines, and buffers

- Dual port RAM control and arbitration circuitry

- 5. The serial I/O interface containing:

- serial ports

- serial port control interface

- 6. DMA controller interface

Each section will be treated in detail in the following section.

#### 3.3 The CPU core

The CPU core is comprised of the CPU, memory map decoder, EPROMS, RESET/RETRY generator, clock timer, and local bus aritration circuitry.

#### 3.3.1 The 68010 CPU

The 68010 microprocessor, coupled with innovative hardware design, forms the base for the IRONICS performance standard. The IV-1624 uses the 68-pin grid array (PGA) packaging. 68010 data (pin assignments and layout) are provided in Appendix B. It is assumed that the user has a basic knowledge of 68010 microprocessor architecture. For a review of this architecture see the MC68000 16/32-bit Microprocessor: Programmers Reference Manual (4th edition) available from Motorola.

#### 3.3.2 Memory map and local I/O decoding

Global memory mapping is accomplished by logic contained within a single PLA (50E). Table 3-2 shows the standard memory map configuration. Figure 3-1 shows map decoder pin assignments. The upper eight address lines (A23-A16) are read by the map decoder which asserts a device select line for the corresponding device. (See Appendix E for map decoder PLA logic).

#### **EXAMPLE:**

The CPU requests a byte-length read from location 001000H. The map decoder responds by asserting the chip select for dynamic RAM (RAMEN\*).

TABLE 3-2. IV-1624 standard memory map configuration

| Description          | Address Range        | Map Decoder  | PLA   |

|----------------------|----------------------|--------------|-------|

|                      |                      | Output       | Pin # |

|                      |                      |              |       |

| Local Dynamic RAM    | 000000-00FFFF (64K)  | RAMEN*       | 15    |

| Local Dyncmic RAM    | 000000-03FFFF (256K) | RAMEN*       | 15    |

| EPROM address space  | F00000-F0FFFF        | EPROM*       | 11    |

| Local I/O            | F70000-F7FFFF        | LOCIO*       | 16    |

| Static dual port RAM | FE0000-FEFFFF        | SROVME*      | 12    |

| VMEbus address (A23) | 010000-DFFFFF(64K)   | VME*+SROVME* | 14+12 |

| VMEbus address (A23) | 040000-DFFFFF (256K) | VME*+SROVME* | 14+12 |

| VMEbus address (A23) | F10000-F7BFFF        | VME*+SROVME* | 14+12 |

| VMEbus address (A23) | F7D000-F7FFFF        | VME*+SROVME* | 14+12 |

| VMEbus address (A23) | F90000-FEFFFF        | VME*+SROVME* | 14+12 |

| VMEbus address (A16) | FF0000-FFFFFF        | SHORT *+VME* | 9+14  |

| (see note below)     |                      | +SROVME*     | 12    |

|                      |                      |              |       |

note: refers to valid address bus bits per address modifier codes

Figure 3-1. Map decoder pin assignments

| 8           |     |     | 16         |

|-------------|-----|-----|------------|

| A23>        | I 7 | В6  | > LOCIO*   |

| 7           |     |     | 15         |

| A22>        | 16  | B5  | > RAMEN*   |

| 6           | T E | D.4 | 14         |

| A21><br>5   | 15  | B4  | > VME*     |

| A20>        | 14  | в3  | < DECDSBL* |

| 4           |     |     | 12         |

| A19>        | 13  | В2  | > SROVME*  |

| 3           |     |     | 11         |

| A18>        | I 2 | Bl  | > EPROM*   |

| 2           | _ • |     | 9          |

| A17>        | 11  | В0  | > SHORT *  |

| A16>        | 10  |     |            |

| 19          | 10  |     |            |

| AS*>        | В9  | "   |            |

| 18          |     |     |            |

| FORCEROM*-> | В8  |     |            |

| 16          |     |     |            |

| IACK*>      | В7  |     |            |

|             |     |     |            |

Note that the SROVME\* ("static RAM or VMEbus") output selects both the VMEbus and static RAM whenever a VMEbus or static RAM address is received. The VME\* output acts as a secondary select: if VME\* is asserted, the VMEbus transceivers are selected. If VME\* is not asserted, static RAM is enabled. The SHORT\* output is used as a VMEbus address modifier.

#### 3.3.2.1 Altering the memory map

It is possible to change the memory map for custom system configurations: for instance, the map decoder logic could be changed to address the bottom of dynamic RAM at 040000H instead of 000000H. A change of this nature would require a custom map decoder PLA which can either be designed and programmed by the user using the PLA table provided in Appendix E, or can be, in most cases, supplied by IRONICS. To request about a custom map decoder, contact an IRONICS customer service representative.

# 3.3.2.2 Local I/O decoding

The local I/O memory space is located in the range F70000-F7FFFFH. The memory map decoder PLA (506) asserts LOCIO\* when it sees an address within this hexadecimal range. This output enables the local I/O decoder (PLA 50C), which further decodes this range. The local I/O decoder asserts the chip select line for the designated device. All local I/O devices and their addresses are shown in table 3-3. The local I/O decoder PLA is included in Appendix E.

TABLE 3-3. IV-1624 Local I/O map

| Output                                   | Memory<br>Map                        | <b>A</b> 9       | Description                                                                                                      |

|------------------------------------------|--------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------|

| SCCOCS*<br>SCC1CS*<br>SCC2CS*<br>SCC3CS* | F7E0XX<br>F7E4XX<br>F7E8XX<br>F7ECXX | 0<br>0<br>0<br>0 | SIO channel 0 chip select<br>SIO channel 1 chip select<br>SIO channel 2 chip select<br>SIO channel 3 chip select |

| SCC or<br>CONTROL*                       | F7Exxx                               | 1                | SIO control port                                                                                                 |

| IVHANCS*<br>IGORCS*                      | F7F0xo<br>F7F4xo                     |                  | Interrupt Handler chip select<br>Interrupt Generator chip select                                                 |

| TMRCS* DMACS*                            | F7F8xe<br>F7FCxw                     |                  | Timer chip select<br>DMA controller chip select                                                                  |

```

o = chip selected when odd low byte written (byte accesses only!)

e = chip selected when even low byte written (byte accesses only!)

w = chip selected when "word" (16-bit) length data written

```

<sup>-- =</sup> don't care

<sup>\* =</sup> signal active low

#### 3.3.3 EPROM theory of operation:

The IV-1624 has two bytewide EPROM sockets capable of holding the devices specified in the following table.

TABLE 3-4. Bytewide Devices

| Device | Size | Organization    |

|--------|------|-----------------|

| 2764   | 64K  | (8192 X 8 bit)  |

| 27128  | 128K | (16384 X 8 bit) |

| 27256  | 256K | (32768 X 8 bit) |

| 27512  | 512K | (65536 X 8 bit) |

The standard addressing range is F00000-F0FFFFH.

## 3.3.3.1 EPROM DTACK\* generation

EPROM data transfer acknowledge (DTACK\*) is generated within the RESET/RETRY generator. DTACK\* is controlled by an RC circuit, whose discharge time, coupled with EPROM internal access speed, determine the number of wait states incurred during an EPROM data transfer. The following table shows RC capacitor values and EPROM internal access times necessary to perform data transfers with a minimum of wait states. The number of EPROM wait states desired should be specified at the time of purchase.

TABLE 3-5. EPROM DTACK\* speed

| CPU    | # of wait | EPROM  | capacitor |

|--------|-----------|--------|-----------|

| speed  | states    | speed  | value     |

| 10 MHz | 0         | 170 ns | 0 pf      |

| 10 MHz |           | 250 ns | 120 pf    |

## 3.3.4 RESET/RETRY generation

The RESET/RETRY generator performs the following functions:

- [1] it initiates power-up (cold), local, and system resets

- [2] it initiates a processor retry cycle when necessary

- [3] it monitors the watchdog timer

Each of these topics will be discussed in more detail.

#### 3.3.4.1 Reset generation

In 68000/68010 architecture, a "reset" is indicated by the assertion of the HALT\* and RESET\* lines. These lines are bidirectional: they can be driven "internally" (i.e., driven by the CPU to signal a reset to all local (onboard) devices), or "externally" (i.e., driven by either a local (onboard) or remote (offboard) device). An internal reset is triggered by execution of a software "RESET" instruction, asserting the RESET\* line for 124 clock pulses, and resulting in the resetting of all onboard LSI devices.

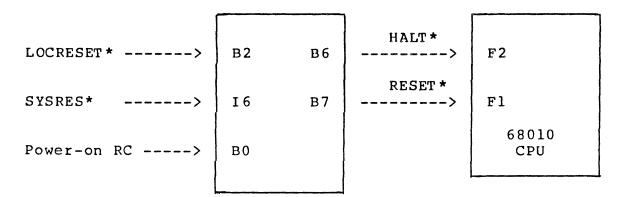

The RESET/RETRY PLA (501) monitors all of the external devices (onboard or offboard) capable of requesting a reset. The RESET/RETRY PLA responds to an external reset request by driving the HALT\* and RESET\* lines to the CPU (see figure 3-2).

# 3.3.4.1.1 Power-on (cold) resets

When power (Vcc) is initially applied to the IV-1624, an RC circuit generates a high input to B0 for a minimum of 250 milliseconds. The RESET/RETRY PLA responds by asserting FORCEROM\*, HALT\* and RESET\*. The simultaneous assertion of HALT\* and RESET\* forces the 68010 CPU to begin a reset cycle. The assertion of FORCEROM\* forces the selection of the EPROM address space. The CPU begins to read 4 words from memory address \$000000. Since the EPROM address space has been selected, the CPU reads address \$F00000H. These 4 words are comprise the reset vector. The first longword (32 bits) is vector number 0, which provides the initial value of the supervisor stack pointer (SSP). The following

Figure 3-2. Reset/Retry PLA inputs

RESET/RETRY PLA (501)

longword contains the initial program counter value (PC), which is the monitor entry point.

# 3.3.4.1.2 Local resets

Two members of the IRONICS multiprocessing family provide a 3-post connector for attaching a reset switch. The members of the family currently providing this capability are:

- [1] the IV-1601 VMX/VME CPU board

- [2] the IV-1624 8-Port Serial I/O board

The following members of the IRONICS multiprocessing family provide a local reset switch which is mounted through the front bezel:

- [1] the IV-1602 Single Board Computer

- [2] the IV-3201 32-bit CPU

- [3] the IV-3273 System Controller board

Depression of the local reset switch causes assertion of input B2 of the RESET/RETRY generator. The RESET/RETRY PLA responds by asserting HALT\* and RESET\* inputs to the CPU.

## 3.3.4.1.3 System ('warm') resets

A system reset occurs when a VMEbus master asserts the VMEbus system reset (SYSRES\*) line. The SYSRES\* line is monitored by the RESET/RETRY PLA, which responds by asserting the HALT\* and RESET\* inputs to the CPU. Since the IV-1624 is not a system controller, it does not have the capability to generate a system reset.

#### NOTE:

The IV-1602 VME CPU and the IV-3273 System Controller I/O board have the capability to generate a system reset.

#### 3.3.4.2 Retry cycles