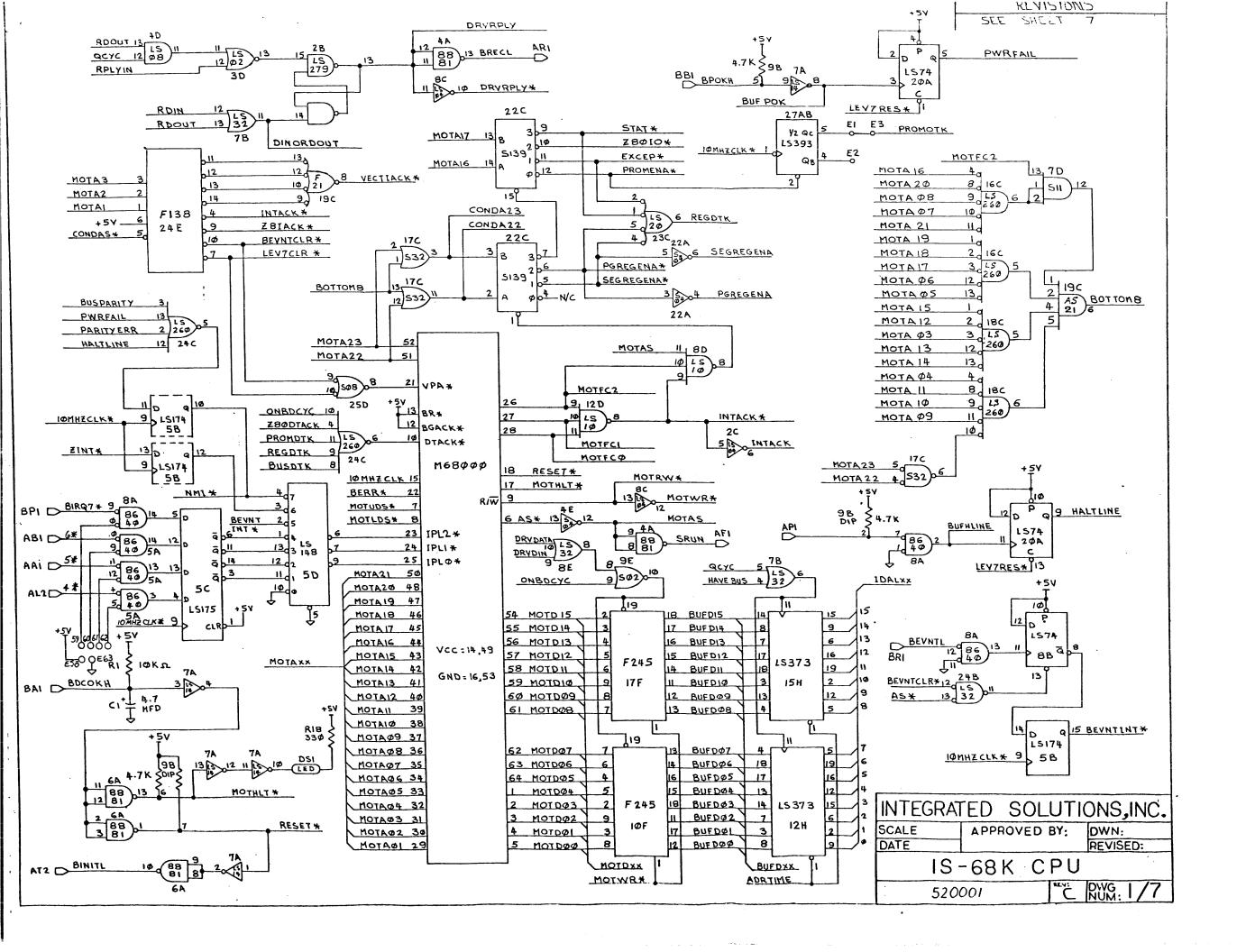

# IS-68K CPU

# INTEGRATED SOLUTIONS 68K CPU HARDWARE REFERENCE MANUAL

**REVISION 1.0**

March, 1984

INTEGRATED SOLUTIONS, INC. 2240 Lundy Ave. San Jose, Ca. 95131

## Preliminary Edition, January 1983 1st Edition, March 1984

Copyright (C) 1983 by Integrated Solutions, Inc.,

## All Rights Reserved

The material in this manual is for information only and is subject to change without notice.

Integrated Solutions, Inc., assumes no responsibility for any errors which may appear in this manual.

• Class A Computing Devices:

#### NOTICE:

This equipment generates, uses and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference in which case the user at his own expense may be required to take measures to correct the interference.

DEC, LSI-11, and RL02 are trademarks of Digital Equipment Corporation.

## PREFACE

This manual describes the Integrated Solutions IS-68K, LSI-11 Bus Compatible 68000/68010-based CPU Board. It contains specifications, installation procedures, a technical description and limited troubleshooting information for the IS-68K. It also contains initialization and programming procedures for the on-board serial ports and counter/timer chips. Part of the technical description assumes that the user is somewhat familiar with the architecture of the 68000/68010 processors. For more information on the architecture and programming of the 68000 family, see the appropriate Motorola, Hitachi, Rockwell or Signetics reference manuals.

# TABLE OF CONTENTS

| 1. Introduction                                       | Page<br>6 |

|-------------------------------------------------------|-----------|

| 1.1 Features                                          | 6         |

| 1.2 Performance                                       | 6         |

| 1.3 Specifications                                    | 6         |

| 1.4 Memory Management                                 | 9         |

| 1.5 On-Board/Local Bus Memory                         | 10        |

| 1.5.1 Local Memory Bus                                | 10        |

| 1.5.2 Local Bus Timing                                | 12        |

| 1.6 Serial Ports                                      | 13        |

| 1.7 Traps and Interrupts                              | 13        |

| 1.8 DMA Arbitration                                   | 15        |

| 1.9 . Memory Arbitration                              | 15        |

| 2.0 Configuration                                     | 17        |

| 2.1 Jumpers                                           | 17        |

| 2.1.1 Jumpers E1,E2,E3 - Eprom Speed                  | 17        |

| 2.1.2 Jumpers E4-E7 - Bus Timeout                     | 17        |

| 2.1.3 Jumpers E8-E11, E16-E21, E43-E48 Serial Port #0 | 17        |

| 2.1.4 Jumpers E12-E15,E22-E27, E37-E42 Serial Port #1 | 18        |

| 2.1.5 Jumpers E28-E29-E30 - CTC Input CLock           | 19        |

| 2.2 Dipswitch                                         | 19        |

| 2.3 I/O Connector Pinout                              | 20        |

| 3.0 Operation/Programming                             | 23        |

| 3.1 ON-Board I/O Addresses                            | 23        |

| 3.1.1 Segment Registers - 400001H -7F0001H            | 23        |

| 3.1.2 Page Registers - 800000H -BFF000H               | 24        |

| 3.1.2.1 Accessed Bit                                  | 25        |

| 3.1.2.2 Page Written Bit                           | 25 |

|----------------------------------------------------|----|

| 3.1.3 Exception/Context Register - C10001H         | 26 |

| 3.1.4 Serial Ports/Counter Timer - C20001H-C21007H | 27 |

| 3.1.5 Status Register - C30000H                    | 27 |

| Appendix A - Programming the Serial Ports          | 29 |

| Appendix B - MACSBUG Commands                      | 37 |

| Appendix C - Downloading and 'S' Record Format     | 49 |

| Appendix D - Memory Managment Unit                 | 51 |

| Appendix E - DART and CTC Application Notes        | 52 |

#### SECTION 1

## INTRODUCTION

#### 1.1 Features

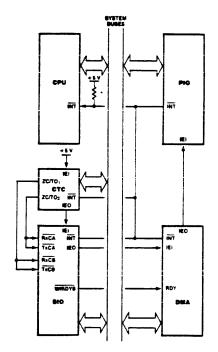

The IS-68K card is a high performance, highly integrated CPU on the LSI-11 Bus. It is specifically designed for those users who want to combine the processing speed, large instruction space and sophisticated instruction set of the Motorola 68000/68010 processors with the large variety of peripherals available on the LSI-11 bus. In addition, the card offers a higher level of integration than the existing LSI-11 processors, combining up to 1 megabyte of parity memory, up to 32k bytes of PROM, and two high speed serial ports with programmable baud rates on a single Quad form factor card.

#### 1.2 Performance

The IS-68K has been designed to maximize the performance available from the 68000/68010 processors. It will operate at 10MHz (12MHz -12 option) with no wait states out of the on-board or local bus expansion memory. Dual porting the on-board and local bus memory permits all on-board and local bus memory to be accessed by DMA devices on the LSI-11 Bus and also permits the 68000/68010 to continue operating while DMA transfers are underway. The 68000 continues executing at full speed while DMA transfers are occuring to LSI-11 bus memory. It continues executing at reduced speed if DMA accesses to on-board/local bus memory are made, while memory accesses are automatically arbitrated between the 68000 and the DMA bus master.

## 1.3 Specifications

#### 1.3.1 Processor

The processor of the IS-68K CPU board is a Motorola 68000 or 68010. There are no hardware differences between the 68000 and 68010 versions of the IS-68K. All IS-68K boards have hardware support for demand paging.

#### 1.3.2 Bus

The system bus of the IS-68K is LSI-11 compatible. It meets all requirements of DEC STD 160 WITH 22-bit addressing. The "B" revision of the processor board (released March, 1984) supports block mode transfers as defined in DEC STD 160.

## 1.3.3 Address Space

A 22-bit logical address space is mapped to a 22-bit physical address space through the memory management subsystem. The memory management subsystem together with the user mode of the 68000/68010 processors provides the protection features required to support a large multiuser environment.

## 1.3.4 Memory

## Configurations:

128k, and 256k implemented with 64k RAMS. 512k, and 1024k implemented with 256k RAMS. Byte parity generation and checking implemented on all versions.

## 1.3.5 Memory Management

The IS-68K board contains two levels of memory management, a segmentation front end and a paging back end. Each process can have from 1 to 64 segments associated with it. Segments contain from 1 to 16 4k byte pages. Support for demand paging through page accessed and page modified bits is associated with each page. These bits are automatically updated by hardware on each page reference.

## 1.3.6 Local Memory Bus

The on-board memory is expandable to 4 megabytes over the local memory bus. Local memory, as well as on-board memory runs with no wait states. All local memory is accessible from the LSI-11 bus through the two port memory arbitrator.

## 1.3.7 LSI-11 Bus Memory

All memory accesses above the local memory are routed over the LSI-11 bus. The transition between local and LSI-11 bus memory is controlled by the local memory limit switch on the IS-68K (see Section 1.3.12).

#### 1.3.8 PROM Sockets

The IS-68K contains two on-board PROM sockets configurable for 2716, 2732, 2764 or 27128 ROMS or EPROMS. The IS-68K is optionally available with two sets of EPROMS. On the IS-68K, the PROMs are located starting at address C00000H in the 68000/68010 on-board I/O space. In addition some special hardware has been added to the CPU board to map the bottom eight bytes of system mode logical address space (addresses 000000H to 000007H) into the bottom eight bytes of the PROM space (addresses C00000H to C00007H). In this manner when the IS-68K board powers up, the initial system stack pointer and initial PC are always taken as long words from the bottom eight bytes of the PROM.

MACS PROMs - The MACS PROMs are a set of 2732 EPROMs containing the Motorola MACSBUG monitor. A description of the commands supported under this monitor is contained in Appendix B.

UNIPS PROMs - The UNIPS PROMs are a set of 2764 EPROMs containing the UNIX bootstraps required to boot System 3 or System 5 Unix from a variety of different DEC compatible devices. For BSD 4.2 Unix the PROMs are 27128s because of the larger number of drivers and higher complexity of the bootstrap device drivers.

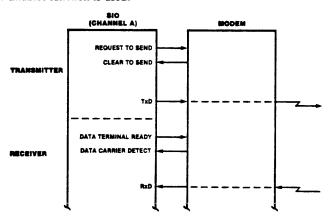

#### 1.3.9 Serial Ports

The two serial ports on the board both support either RS423 (RS232C compatible) asynchronous communication or RS422 balanced synchronous communication with external clocking. Both channels offer full modem control support while in asynchronous mode and limited modem control support in synchronous mode. Channels 0 and 1 can be independently configured for synchronous or asynchronous communications.

#### 1.3.10 Electrical Interface

The IS-68K interfaces with the 22 bit LSI-11 bus. A Quad form factor board is used with the bus interface implemented on A and B connectors. There are no signals on the C and D

connectors. DEC approved bus drivers, receivers and transceivers are used for all bus signals. All AC and DC requirements of DEC Standard 160 are adhered to. The board supports BPOK and BDCOK power up/down protocol, as well as BEVNTL and the generation of SRUN (pin AF1) signal. By using the CD connectors for power and ground only, the board is compatible with all LSI-11 bus backplanes.

#### 1.3.11 Indicators

- 4 LEDs at the top of the board:

- 1 Motorola 68000 HALT indicator

- 1 latched PWR FAIL

- 1 latched LOCAL PARITY ERROR

- 1 latched BUS PARITY ERROR

# 1.3.12 Configuration Switches (8 switches)

SW 1-4 - Local memory limit switch: All memory accesses above this limit go to the LSI-11 bus.

SW 5-6 - Default baud rate of console port: settable to 300, 1200, 2400 or 9600 baud. Settable to any other four standard baud rates (up to 38.4K), at the time of order upon customer request. Moving the jumper associated with pins E28-E29-E30 will also halve the baud rates produced. (See section 2.1.5.). These switches set the baud rate according to the above definition with both the MACS and UNIPS PROMs. However, the switches are software readible and the on-board firmware must make the conversion between switch setting and programmed baud rate.

SW 7-8 - Used by the UNIPS PROMs to control autobooting and the type of SMD disk from which to boot. See the appropriate Unix Installation notes for a more detailed description.

## 1.3.13 Power Requirements

+ 5v - 4.0 amps typical, 5 amps maximum

+ 12v - .1 amps maximum

#### 1.3.14 Environmental

Temperature: 0°C to 50°C (operating)

-40°C to 65°C (non-operating)

Humidity: 10% to 90% (non-condensing)

# 1.3.15 Options

- MACS two 2732 EPROMs containing

Motorola MACSBUG power up diagnostics and

autoboot capability (no PROMs standard)

- UNIPS two 2764 E Proms containing self test diagnostics

MMU initialization logic, and Unix bootstrap loaders

(required for Unix)

10 MHz board (8MHz standard)

12 MHz board

10 MHz board with 68010 virtual memory processor

12 MHz board with 68010 virtual memory processor (available 2nd quarter 1984)

128 128k bytes of parity memory (256k standard)

512 512k bytes of parity memory (available 2nd qtr 84)

1024 1024k bytes of parity memory(available 2nd qtr 84)

## 1.4 Memory Management

The memory management unit is based on 5 high speed static 1kx4 RAMS and consists of a segmentation front end followed by a paged back end. This is the same memory management style used on many current generation mainframe computers. The segmentation unit takes bits 21-16 of the 68000 logical address and uses it as an index into the segment register bank along with the contents of the context register (4 bits) to be described in more detail later. The segment register array consists of 1024 registers each 8 bits wide. The combination of 6 logical address bits and 4 context register bits select one unique segment register on each memory access. Out of the segment register bank come 8 bits, the upper two of which are used for to encode four protection modes and the bottom six of which are used as an index into the page table. The two protection bits are encoded as follows:

00 - no access

- 01 read and execute access only

- 10 read/write access

- 11 execute access only in user mode. Any access permitted in System mode

## 1.4.1 Page map

The six segment number bits coming out of the segment register are concatenated with bits 15-12 of the logical address to form a 10 bit entry into the page table. The page table is 1024 registers, each 12 bits wide. Out of the page table comes a 10 bit physical page number which is combined with bits 11-0 of the 68000 logical address to a form a 22 bit physical memory address. From the programmers point of view, each process consists of from 1-64 segments, each segment containing from 1 to 16 4k pages. This page size should be optimal for a large number of processes to be simultaneously memory resident without wasting memory space due to unused partial pages and at the same time minimizing the number of memory management registers that must be changed to load a new process. The 3FCH-3FFH number pages have special meanings, two pages (3FCH and 3FDH) being used as the non-existant page and two pages (3FEH and 3FFH) being used as the I/O page for the LSI-11 bus. The other two bits coming out of the page register are used as page

accessed and page dirty bits for demand paging. They are automatically updated by the hardware on each memory access.

## 1.4.2 Context register

In an effort to minimize context switching overhead, there are actually 16 sets of 64 segments present in the segment map. A four bit context register, settable only by the system, selects which user context (1-15) is to be used when a user program is running. Whenever the 68000 is in supervisor mode, the system context (0) is automatically used. The user context, however, is preserved when a switch is made from user mode to system mode and back to user mode such as when servicing interrupts. Thus, when 15 or fewer processes are simultaneously memory resident, context switching only requires modifying the context number in the context register.

## 1.5 On-board/Local Memory

The IS-68K CPU board comes equipped with 256k bytes (128k bytes optional) of on-board memory. This memory is implemented with high speed 64k dynamic RAMS and accesses from the 68000 are accomplished with no wait states. This type of performance is available because the on-board memory is dual-ported; the 68000 accesses it via a different path than the LSI-11 bus and does not have to follow LSI-11 bus protocol. For high performance applications, the on-board memory can be extended to the full 4 megabyte address space of the 22 bit LSI-11 bus via the two 34 pin local bus expansion connectors at the top of the IS-68K card. When configured this way, the IS-68K allows a full 4 megabyte 68000 system to run with no wait states at 8, 10 or 12 MHz.

All on-board local bus memory is fully accessible from the LSI-11 bus when DMA devices are bus master. Further, because of the performance limitations of the LSI-11 bus only 50% of the on-board memory bandwidth can be used even if a device transfers at the ideal maximum LSI-11 bus rate. The dual-ported memory system allows the remaining memory bandwidth to be used by the 68000.

#### NOTE

The first 256k bytes of memory always appears at the bottom of the LSI-11 bus physical memory space. If more memory is present on the local bus, it appears at the next ascending physical memory locations up to the limit of the local bus memory present.

Users of the first IS-68K boards with only 128k bytes (no longer available) also have a further limitation. Because the address limit switch selects addresses with a granularity of 256k bytes, the IS-68K always thinks that it has at least 256k of on-board memory. This means that with 128k byte boards, a 128k hole appears above the on-board memory where the other 128k bank of memory normally sits. Accesses to this memory space do not result in bus errors but no information can be read or written from this space. The effect of this problem can be negated to a large extent by programming the memory management unit never to access this physical memory space.

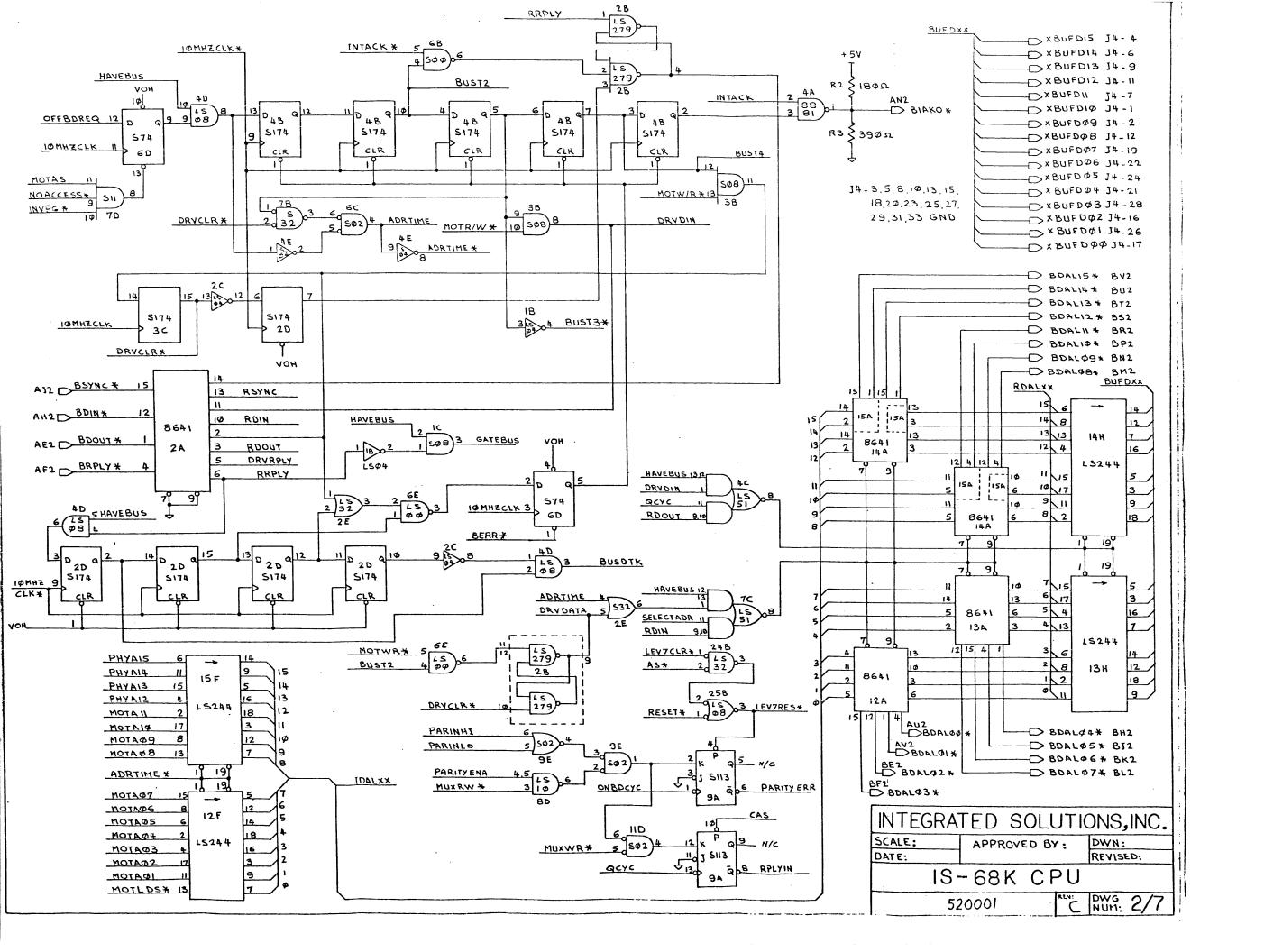

## 1.5.1 Local Memory Bus

The local memory bus is implemented as a means of extending the on-board memory with its fast access characteristics and dual-ported nature. The local memory bus is implemented with 38 control, data and signal lines on 2 34 pin ribbon cable connectors. The connectors are designated J3 and J4 at the top of the IS-68K.

#### NOTE

On early versions of the IS-68K, the J4 connector is designated J1.

The following signals are implemented on the J4 connector:

```

J4-1 XBUFD10 (external buffered data 10)

J4-2 XBUFD09

J4-4 XBUFD15

J4-6 XBUFD14

J4-7 XBUFD11

J4-8 XBUFD13

J4-9 XBUFD12

J4-12 XBUFD08

J4-14 XBPAROUTH (external buffered parity out -most sig byte)

J4-16 XBUFD02

J4-17 XBUFD00

J4-19 XBUFD07

J4-21 XBUFD04

J4-22 XBUFD06

J4-24 XBUFD05

J4-26 XBUFD01

J4-28 XBUFD03

J4-30 XBPAROUTL (external buffered parity out-least sig byte)

J4-32 XBPINH* (external buffered parity in -most sig byte)

J4-34 XBPINL* (external buffered parity in -least sig byte)

The following signals are implemented on the J3 connector:

J3-1 XBAD17 (buffered non-multiplexed address 17)

J3-3 XBCAS* (buffered column address strobe)

J3-5 XBREF (buffered refresh signal)

J3-7 XBRAS* (buffered row address strobe)

J3-9 XBMUX1 (buffered multiplexed address 1)

J3-11 XBMUX5

J3-13 XBMUX0

J3-15 XBMUX7

J3-17 XBMUX6

J3-19 XBMUX3

J3-21 XBMUX2

J3-23 XBMUX4

J3-25 XBAD21

J3-27 XBAD18

J3-29 XBAD19

J3-31 XBAD20

J3-33 XBWRL (buffered write low byte)

J3-34 XBWRH (buffered write high byte)

```

The signals on the local memory bus can be grouped into four functional groups:

#### 1.5.1.1 The Data Group

The data group consists of the 16 bidirectional data lines, the two byte parity in lines and the two byte parity out lines. The parity in and out lines are unidirectional.

## 1.5.1.2 The Multiplexed Address Group

There are eight unidirectional multiplexed address lines. These lines contain a physical addresses 1 through 8 at RAS time and physical addresses 9 through 16 at CAS time. The source of these physical addresses depends on whether the cycle is a 68000 cycle or an LSI-11 bus cycle. In addition, during refresh cycles, these lines contain the refresh address.

## 1.5.1.3 The Non-multiplexed Address Group

These five lines contain non-multiplexed physical addresses 17-21. The non-multiplexed addresses are guaranteed valid from 35ns before RAS is asserted and are valid through the entire RAS cycle.

## 1.5.1.4 The Control Group

The five signals in the control group are as follows:

XBRAS\* - This signal is asserted to indicate that a memory cycle has begun and that row addresses are valid on XBMUX0-7.

XBCAS\* - This signal always follows 40ns after XBRAS\* and indicates that the column addresses are valid on XBMUX0-7. In the case of refresh cycles, XBCAS\* still occurs but must be supressed at the memory chips themselves.

XBREF - This signal is asserted at least 40ns in advance of RAS to indicate that the forthcoming memory cycle is a memory refresh cycle. The RAS lines of all memory devices must be asserted low at RAS time and CAS must be suppressed to all memory devices.

XBWRH - This signal indicates that a write is to be performed on the most significant byte of the addresses memory location. This signal is always stable at least Ons before the assertion of XBCAS\* and is stable until the negation of XBRAS\*.

XBWRL - This signal indicates that a write is to be performed on the least significant byte of the addressed memory location. This signal is always stable at least Ons before the assertion of XBCAS\* and is stable until the negation of XBRAS\*.

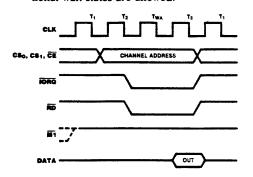

## 1.5.2 Local Bus Timing

Figure 1.5 shows the timing requirements of typical read and write signals on the Local Bus. The significant parameters are:

TARasSu - address set up time before RAS\* is asserted - 35ns (this parameter applies to both the multiplexed and non-multiplexed addresses)

TARasHd - multiplexed address hold time after RAS\* is asserted - 25ns

TACasSu - multiplexed address (column addr) set up time before CAS\* is asserted - Ons

TACasHd - multiplexed address (column addr) hold time after CAS\* is asserted - 100ns

TRASPr - minimum RAS precharge time - 85ns (12 MHz) 100ns (10 MHz) 125ns (8 MHZ)

TRASCy - minimum RAS cycle time - 130ns (12 MHz) 150ns (10 MHz) 187ns (8 MHz)

TDRAS - data access time from RAS - 100ns (12 MHz) 120ns (10 MHz) 158ns (8 MHz)

TRC - time interval between RAS assertion and CAS assertion - 45-55ns

TWCASSu - stable WRITE HIGH and WRITE LOW signals before CAS\* is asserted - Ons

TWDCASSu - stable write data high and low bytes before CAS\* is asserted including parity data - 25ns

TWDCASHd - stable write data, high, low bytes and parity, after CAS is asserted - 100ns

#### 1.6 Serial Ports

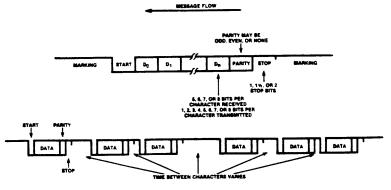

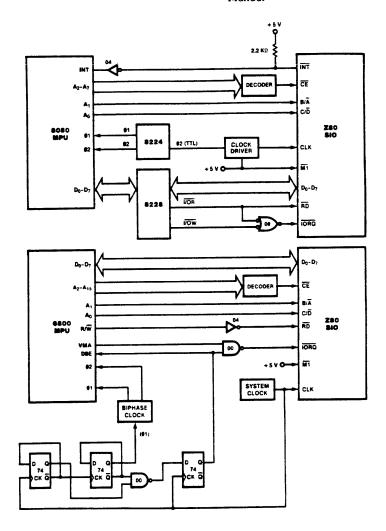

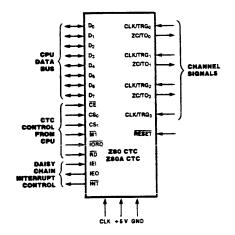

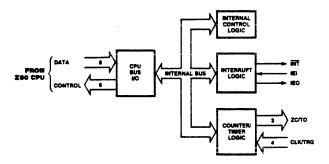

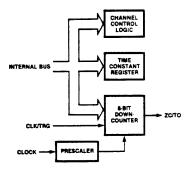

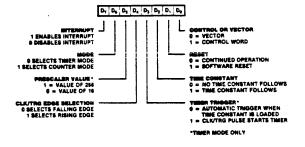

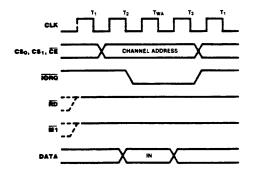

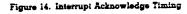

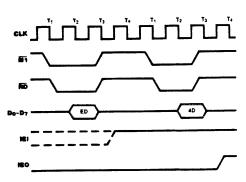

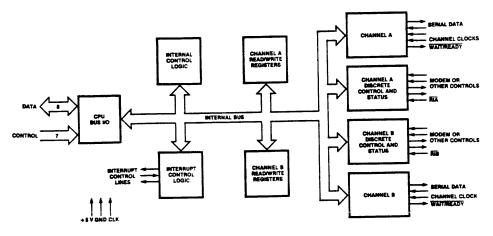

A combination of a Zilog CTC and a Zilog DART are used to implement two serial ports with programmable baud rate. The serial ports can be used in asynchronous communications at rates up to 38.4 kilobits per second and in synchronous communications up to 1 megabit per second. Almost all characteristics of the serial ports are programmable including the number of bits/word, the number of start bits, the number of stop bits, the number of bits per character, whether interrupts occur on various conditions, the interrupt vector, etc. (See Appendix A, and the Zilog application notes in Appendix E for more information on programming the DART and CTC.). The DART and CTC are properly initialized for operation at the baud rate set in switches 5 and 6 by both the MACS and UNIPS PROMs.

#### 1.7 Traps and Interrupts

## 1.7.1 Interrupts

The IS-68K uses the seven level interrupt scheme of the 68000 to service interrupts from sources on-board and off-board. The off- board interrupts include the four LSI-11 bus interrupt levels and four hardware related sources of level seven non-maskable interrupts. The 68000 level seven interrupt differs from the other six levels in that it is non-maskable, i.e., no matter what priority level is set, it will still be serviced.

## 1.7.1.1 Level 1-4 Interrupts

The LSI-11 Bus Interrupts. The four LSI-11 bus interrupts are mapped into the following 68000 interrupt levels:

| LSI-11 BUS | Motorola |

|------------|----------|

| IRQ4       | Level 1  |

| IRQ5       | Level 2  |

| IRQ6       | Level 3  |

| IRQ7       | Level 4  |

These four interrupts are vectored with the vector coming from the LSI-11 bus. The LSI-11 vector is converted to an address in the 68000 vector table by multiplying it by four. For example, the LSI-11 bus RL02 interrupt at 160(8) will vector through Motorola location 1C0h. The IS-68K does not have the same restriction that the LSI-11 bus does that vectors must have even addresses. The effect of this restriction, however, is to permit the LSI-11 bus to access only every other location in the vector table.

A second restriction requires the LSI-11 bus vectored interrupts to appear in the 68000 user interrupt space from 100h to 3FCh. This means that LSI-11 bus vectors from 100(8) to 377(8) are permitted. This range includes almost all LSI-11 bus standard vectors and

the bottom of the floating vector table.

## 1.7.1.2 Level 5 Interrupt

The BEVNTL line. The only interrupt at level 5 is the LSI-11 bus BEVNTL line. The BEVNTL line contains a 60Hz TTL level compatible signal generated by DEC or DEC compatible power supplies that is received by the IS-68K and latched on the falling edge. Because the BEVNTL line has no interrupt associated with it, the BEVNT interrupt is autovectored at level 5. This means that it always traps through location 074h.

## 1.7.1.3 Level 6 Interrupts

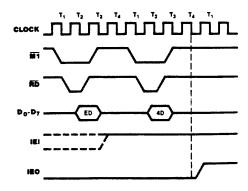

The On-Board Serial Ports. The on board serial ports and optionally the counter/timer chip interrupt at level 6. A vector is provided by the serial I/O ports and counter/timer chip at interrupt acknowledge time. Like the LSI-11 bus vectors, these vectors are multiplied by four to get the vector address at the bottom of the 68000 logical address space. Because the Zilog DART chips used for the serial ports and the Zilog CTC chips can modify their base vectors to respond to different interrupt sources, the user must be careful that the on-board level 6 interrupts do not conflict with the LSI-11 bus vectors. (See Appendix A for more information on programming the Zilog DART.)

## 1.7.1.4 Level 7 Interrupts

Level 7 interrupts are reserved for hardware related problems that must be brought to the immediate attention of the 68000. Because no vectors are associated with level seven interrupts, they are all autovectored through the same location, 07CH.

BPOKH falling edge - The falling edge of the BPOKH signal indicates that the power supply has only four milliseconds of power left. This falling edge generates a level 7 interrupt to get the processors immediate attention. In addition, this occurence is latched into the on-board STATUS register at location C30000H, bit 9.

On-board Parity Error - A parity error in on-board memory causes a level 7 interrupt when the memory access is made from the 68000. The occurence of the parity error is also latched into the STATUS register bit 7. If another device were bus master when the parity error occured in on-board memory, the response would be different. In this case, the response would be to suppress the bus REPLY signal and cause a bus error in the DMA device to indicate to it that the parity error had occured.

Bus Parity Error - The LSI-11 bus defines a protocol where the assertion of both address lines 17 and 18 (BDAL 17 and 18) at data in time indicates that a parity error has occured in the device being accessed. The IS-68K recognizes this protocol and immediately asserts a level 7 interrupt. This occurence is also latched into the STATUS register bit 8.

BHALT line - The falling edge of the LSI-11 bus BHALTL line causes a level 7 interrupt. This occurrence is also latched into the STATUS register bit 6.

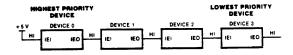

#### 1.8 DMA Arbitration

The IS-68K board serves as the DMA arbitrator for the LSI-11 system into which it is inserted. DMA arbitration is not handled by the 68000 but is instead handled by a completely separate piece of TTL logic for performance reasons. The arbitrator conforms to LSI-11 bus specifications with a maximum DMA latency (request to grant

time) of 200 ns (150 ns average) except in the situation where the 68000 is using the LSI-11 bus. In this case, the DMA arbitrator cannot issue the bus grant until the 68000 is through with its current bus cycle. If, however, the 68000 is using on-board/local bus memory at the time of the request, the GRANT is always issued with an average latency of 150 ns.

The second case where DMA latency may be affected is when one device has the bus AND another is requesting its use AND the 68000 is requesting its use concurrently. In this case, the 68000 will be given the bus for one cycle only at the conclusion of the first master's use of the bus. After completing one cycle, the second requester will be granted bus mastership. Note that when the 68000 is executing out of on-board/local bus memory, instruction execution and servicing of on-board interrupts can still occur concurrently with DMA transfers.

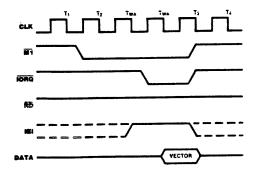

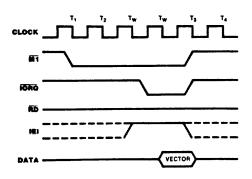

In the case of off-board interrupts, the 68000 will be suspended in the IACK (interrupt acknowledge) cycle until the current master relinquishes the bus. The 68000 will then conclude the interrupt acknowledge cycle, immediately after which the second master will be granted the bus if another bus request is pending.

## 1.9 Memory Arbitration

The memory arbitration unit allocates memory cycles among the three possible requesters of the on-board memory in the following priority order:

- 68000 memory requests

- refresh requests (one refresh request occurs every 12.8 microseconds)

- •LSI-11 bus requests

The priority order is important only when two or more requesters simultaneously request the use of on-board memory. In all other cases, memory cycles are awarded on a first come-first served basis. Further it is important to note that the on-board memory always runs at the maximum possible rate of a cycle every 260ns (12 MHz board, 300ns - 10MHz, 375ns - 8 MHz) when any requests are pending.

Even though the LSI-11 bus is at the minimum priority level, it is almost always guaranteed an access within one memory cycle. This is because the 68000, even if accessing memory at the maximum rate possible, does not request the use of the bus for one clock cycle after completing each memory cycle. Any LSI-11 memory request pending is honored at this time. The only exception to this is the case where a refresh request was also pending. In this case, the refresh request would be granted and then the LSI-11 bus memory request would be honored. Thus it would theoretically be possible for the LSI-11 bus and the 68000 to both request bus use constantly and alternate memory cycles. This would allow one LSI-11 cycle every 520ns for a memory transfer rate of 3.85 megabytes/second. Unfortunately, the LSI-11 bus protocol will not support memory requests that frequently. Empirical studies of the IS-68K have shown that what actually happens with a DMA device that performs fairly close to the upper limit of the LSI-11 bus bandwidth is that the LSI-11 DMA device will perform a memory cycle every two 68000 cycles for a total transfer rate of 2.4 megabytes per second. In situations where this level of performance is unacceptable, the performance can be improved a little by stopping the 68000 processor while doing DMA transfers. When this is done, the maximum transfer rate increases to 2.7 megabytes per second and is limited only by the memory arbitration time and the LSI-11 bus protocol itself.

The disadvantage of this method of increasing the DMA bandwidth is that the 68000 no longer can perform meaningful work while DMA transfers are underway. However, if the 68000 has nothing meaningful to do while a DMA transfer is pending, it is certainly better to STOP it (by executing the STOP instruction) rather than executing a tight code loop waiting for completion.

Average BDOUTL to REPLYL time on memory writes is 140ns (97ns min - 172ns max 12mhz board). Average BDINL to REPLYL time on memory reads is 315ns (12 mhz board). This time is much longer than the memory access time and is required in order to check the parity of the information coming out of the memory in order to suppress REPLY when a parity error occurs. The impact of slow READ operations is somewhat minimized by the fact that in most operating systems, writes from disk to memory are four times as frequent as reads from memory to disk.

## 1.9.4 Block Mode Memory Operation

Revision 2.0 of the IS68K board supports block mode memory operation as defined in the latest LSI-11 Bus Technical Specification. Under block mode operation, a single address serves as the starting address for multiple data transfers. With the IS68K block mode design, up to 16 words will be transferred in a single block transfer. Under block mode writes from the disk into memory (again four times as frequent as data reads from memory), one word transfer can occur approximately every 570ns for an effective transfer rate of just under 3.5 megabytes per second. With block mode read from memory to the disk, a word transfer can occur every 695ns for an effective transfer rate of 2.8 megabytes per second.

| Mode                 | Dual-Ported Memory Maximum Transfer Rate (MBytes |                |

|----------------------|--------------------------------------------------|----------------|

|                      | Disk to Memory                                   | Memory to Disk |

| Non-Block Mode       | 2.4*                                             | 2.2*           |

| Block Mode (Rev 2.0) | 3.5                                              | 2.8            |

Figure 1.9.4 LSI-11 Bus Memory DMA Bandwith

\*In these two cases, maximum transfer rate is almost completely a function

of LSI-11 bus protocol rather than the response time of the dual-ported memory.

#### **SECTION 2**

## CONFIGURATION

#### 2.1 Jumpers

## 2.1.1 Jumpers E1,E2,E3

These jumpers control the number of wait states when accesses are made to the onboard EPROMS.

E2-E3 - two wait states are inserted on 68000 accesses. EPROM access times of 260 ns or better are required fo 12 MHz operation, 320 ns or better for 10 MHz operation, 400 ns or better for 8 MHz operation.

E1-E3 - four wait states are inserted on 68000 accesses. EPROM access times of 430 ns or better are required for 12 MHz operation, 520 ns or better for 10 MHz operation, 650 ns or better for 8 MHz operation.

The factory configuration is E1-E3.

| Jumper | 12MHz | 10MHz |

|--------|-------|-------|

| E1-E3  | 430ns | 520ns |

| E2-E3  | 260ns | 320ns |

Figure 2.1.1 EPROM Access Time (nano seconds)

## 2.1.2 Jumpers E4-E7

E4, E5, E6 and E7 control the LSI-11 bus timeout timing. There are three possible timeout timings that can be set by tieing jumper post E4, E5 or E6 to E7. Only one post of these three should be attached to E7. The board is shipped from the factory with the default of E5-E7 and it should be left in that configuration for most applications.

| Jumper | 12MHz | 10MHz | 8MHz |

|--------|-------|-------|------|

| E6-E7  | 11.0  | 12.8  | 16   |

| E5-E7  | 22.0  | 25.6  | 32   |

| E4-E7  | 44.0  | 51.2  | 64   |

Figure 2.1.2 Bus Timeout Timing (microseconds)

## 2.1.3 Jumpers E31-36

Jumpers E31,E32,E33,E34,E35,E36 control the configuration of the EPROM sockets to allow the use of 2716,2732,2764,28128 type PROMS or EPROMS.

E32-E33 E35-E36 -2716 type EPROMS (2kx8)

E32-E33 E34-E36 -2732 type EPROMS (4kx8)

E32-E33 E34-E36 -2764 type EPROMS (8kx8)

E31-E33 E34-E36 -27128 type EPROMS (16kx8)

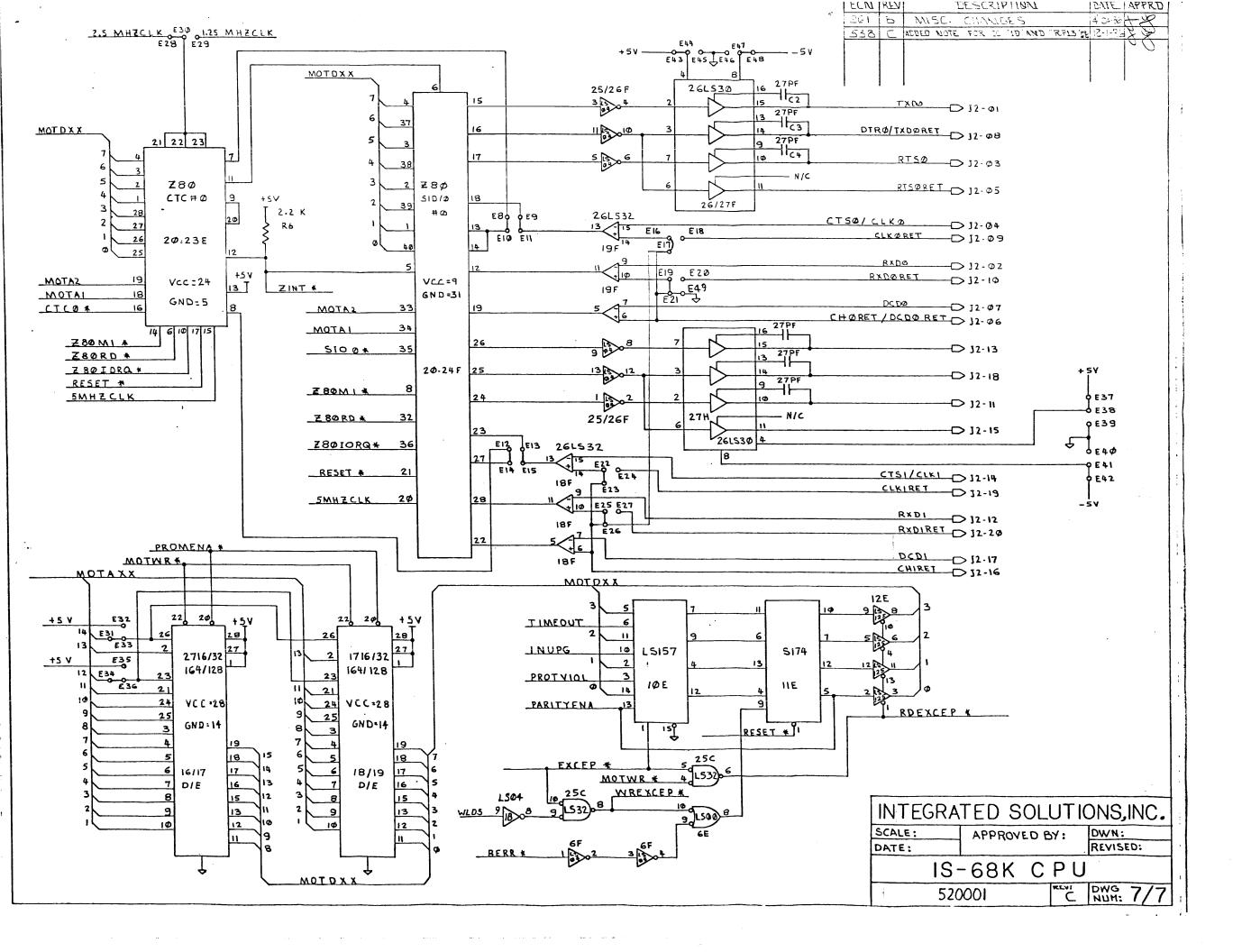

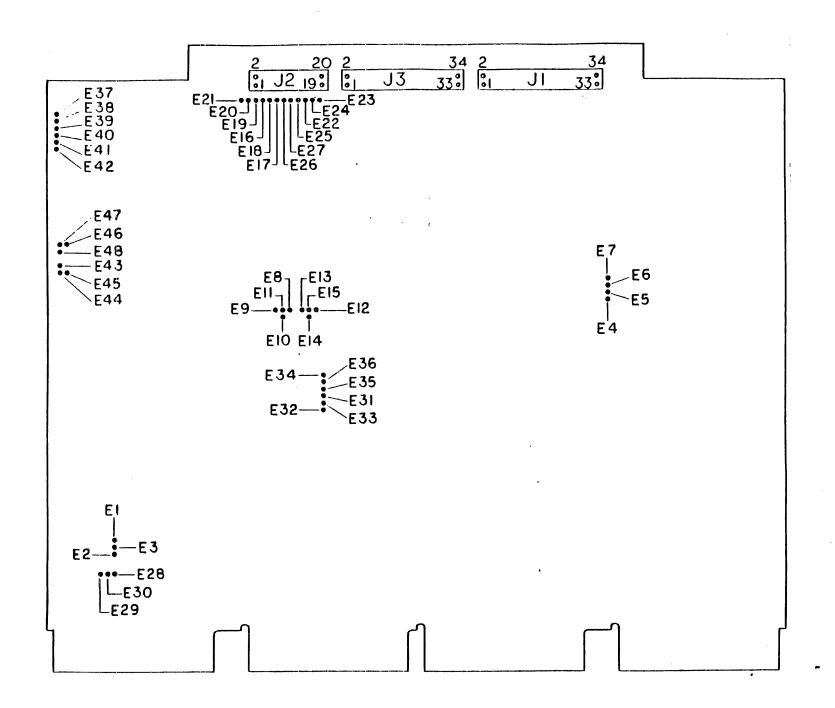

FIG.2.1 CONSIGURATION

## 2.1.4 Jumpers E8-E11,E16-E21,E43-E48

Jumpers E43,E44,E45,E46,E47,E48 configure serial port #0 to operate in RS423 (RS232C compatible) asynchronous mode or RS422 'valanced synchronous mode. In synchronous mode, an external clock must be provided on the CLK and CLK RET lines. Jumpers E16-E21 are used in conjunction with the above jumpers to allow each receiver to have its own RETURN line in synchronous mode or to tie all receivers together to a common ground point in asynchronous mode.

For asynchronous operation on Channel 0, the following connections should be made:

E8-E10 - This ties the internally generated counter timer channel 0 baud rate output to the transmitter and receiver clock inputs on the SIO/DART chips.

E9-E11 This ties the CTSO signal received on Pin 4 of the J2 connector into the SIO/DART chip.

E16-E17, E19-E21 This ties the return path for all serial channels to a common point. In addition, E49-E21 ties these return paths to Board Ground.

E43-E44, E47-E48 This provides the proper voltages to the Channel 0 26LS30 bus driver to allow it to operate in RS423 mode.

For synchronous operation on Channel 0, the following connections should be made:

E10-E11 This allows a baud clock generated externally to operate the SIO chip.

E16-E18, E20-E21 This configures each signal line to have its own RETURN. Since E49 (Board Ground) is not used in this configuration, these returns are not connected to ground for differential mode operation.

E44-E45, E46-E47 These provide the proper voltages to operate the 26LS30 chip in RS422 balanced synchronous mode.

For channel 1, a similar set of connections is made. For asynchronous operation:

E12-E14 - This ties the internally generated counter timer channel 1 baud rate output to the transmitter and receiver clock inputs for channel 1 on the SIO/DART chips.

E13-E15 This ties the CTS1 signal received on Pin 14 of the J2 connector into the SIO/DART chip.

E22-E23,E25-E26 This ties the return path for all serial receivers to a common point. In addition, these points must be tied to Board Ground. If channel 0 is wired up in asynchronous mode, this can be accomplished by tying E16-E17; otherwise, E16 should be tied directly to E49 (Board Ground).

E37-E38,E41-E42 This provides the proper voltages to the 26LS30 bus driver to allow it to operate in RS423 mode

For synchronous operation on Channel 1, the following connections should be made:

$\rm E14\text{-}E15$  This allows a baud clock generated externally to operate the  $\rm SIO/DART$  chip.

E22-E24,E25-E27 This configures each signal to have its own RETURN. These returns are not connected to ground for differential mode operation.

E38-E39, E40-E41 These provide the proper voltages to operate the Channel #1 26LS30 chip in RS422 balanced synchronous mode.

The factory default configuration is both channels wired for asynchronous operation.

#### ERRATA

On Rev 1.0 boards, there is no jumper post to tie the input RETURN lines to Board Ground. This is necessary for reliable operation of the asynchronous channels. This is accomplished on Rev 1.0 boards by tieing E17-E16 and E23 to the GND pin of chip J17 (pin 10). The board is factory configured in this manner.

# 2.1.5 Jumpers E28-E30 CTC Input

The CTC input clock can be programmed to be 1/4 or 1/8 the 68000 clock rate.

E28-E30 The CTC input clock is 1/4 the 68000 clock rate. This is the factory default position.

E29-E30 The CTC input clock is 1/8 the 68000 clock rate. The baud rates produced by the CTC are all exactly 1/2 the factory default rates. This jumper can effectively be used to support baud rates that are exactly 1/2 the four baud rates provided by MACSBUG. See Section 2.2.

## 2.2 Dipswitch

The single eight pin dipswitch at position B10 controls three independent functions.

Switch positions 1-4 control the transition between local bus memory and LSI-11 bus memory. These switches allow from 1 to 16 256k byte segments of physical memory to be placed on the local bus. When all four positions are closed, it indicates that only 256k bytes of memory are present on the local bus.

The following table indicates the switch settings for various amounts of memory present on the local bus:

| Memory on Local Bus Including CPU Resident Memory                            | Switch<br>1                                        | Switch 2                          | Switch<br>3                       | Switch<br>4                      |

|------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------|-----------------------------------|----------------------------------|

| 256k bytes<br>512k bytes<br>768K bytes<br>1024k bytes<br>1.25 meg<br>1.5 meg | close<br>close<br>close<br>close<br>close<br>close | close close open open close close | close close close close open open | close open close open close open |

| 1.75 meg | close        | <b>op</b> en | <b>o</b> pen | close        |

|----------|--------------|--------------|--------------|--------------|

| 2.00 meg | close        | open         | open         | open         |

| 2.25 meg | <b>o</b> pen | close        | close        | close        |

| 2.50 meg | <b>o</b> pen | close        | close        | open         |

| 2.75 meg | <b>o</b> pen | <b>o</b> pen | close        | close        |

| 3.00 meg | <b>o</b> pen | open         | close        | open         |

| 3.25 meg | <b>op</b> en | close        | <b>o</b> pen | close        |

| 3.50 meg | <b>o</b> pen | close        | open         | <b>o</b> pen |

| 3.75 meg | <b>o</b> pen | open         | <b>op</b> en | close        |

| 4.00 meg | <b>o</b> pen | <b>o</b> pen | <b>op</b> en | <b>op</b> en |

#### ERRATA

On boards Rev A2 and earlier, setting all four switches open will put all 4.00 megabytes on the local bus. This has the problem that the upper 8 kbytes of the four megabyte address space (the I/O page of the LSI-11 bus) cannot be accessed by the IS68K. There are two solutions to this problem. For those users who must have the capability of putting a full 4 megabytes of memory on their system, a one wire change is available from Integrated Solutions to fix this problem. The other solution is to limit high speed memory to 3.75 megabytes or less. The problem has been fixed on boards REV A3 and later. On these boards, setting all the switches open will result in all four megabytes of memory minus the I/O page being available on the high speed bus. All I/O page references will go out on the LSI-11 bus.

Switch positions 5,6,7,8 are software readable switches that appear in the STATUS register at bit positions 3,2,1,0:

```

SW5 - bit position 3

SW6 - bit position 2

SW7 - bit position 1

SW8 - bit position 0

```

Under MACSBUG the switches have the following functions:

SW5 and SW6 set the console baud rate at power up according to the following table:

```

SW5 - closed, SW6 - closed - 9600 baud

SW5 - closed, SW6 - open - 2400 baud

SW5 - open, SW6 - closed - 1200 baud

SW5 - open, SW6 - open - 300 baud

```

If the jumper between E29-E30 is installed, the baud rates will be 4800 baud, 1200 baud, 600 baud, and 150 baud respectively.

SW7 and SW8 have no function under MACSBUG.

## 2.3 I/O Connector Pinout

Connector J2 contains the I/O connections for the two serial ports. The signals on the connector are different depending on whether one or both ports are configured for synchronous operation.

NOTE - Pin 1 is marked by a square pad on the IS68K board for all ribbon cable

#### connectors.

# Port #0 - Asynchronous Configuration

```

J2-1 TXD0 out

J2-2 RXD0 in

J2-3 RTS0 out

J2-4 CTS0 in

J2-5 not used

J2-6 CH0 COMMON RET

J2-7 DCD0 in

J2-8 DTR0 out

J2-9 not used

```

# Port #0 - RS422 Synchronous

J2-10 not used

```

J2-1 TXD0 out

J2-2 RXD0 in

J2-3 RTS0 out

J2-4 CLK0 in

J2-5 RTS0 RET out

J2-6 DCD0 RET in

J2-7 DCD0 in

J2-8 TXD0 RET out

J2-9 CLK0 RET in

J2-10 RXD0 RET in

```

# Port #1 - Asynchronous Configuration

```

J2-11 TXD1 out

J2-12 RXD1 in

J2-13 RTS1 out

J2-14 CTS1 in

J2-15 not used

J2-16 CH1 COMMON RET

J2-17 DCD1 in

J2-18 DTR1 out

J2-19 not used

J2-20 not used

```

## Port #1 - Synchronous

```

J2-11 TXD0 out

J2-12 RXD0 in

J2-13 RTS0 out

J2-14 CLK0 IN in

J2-15 RTS0 RET out

J2-16 DCD0 RET in

J2-17 DCD0 in

J2-18 TXD0 RET out

J2-19 CLK0 RET in

J2-20 RXD0 RET in

```

Both ports are factory configured for asynchronous operation. One common use of port 1 is for loading information to/from another computer system via a serial link. In this mode, a cable that reverses TXD and RXD must be used to make both computers look like they are talking to terminals. This is commonly called a NULL MODEM. See the section on configuration for instructions on making the serial ports operate in synchronous mode.

## SECTION 3

## OPERATION/PROGRAMMING

## 3.1 On-Board I/O Addresses

The 68000 logical address space from 400000H to FFFFFFH is dedicated to onboard I/O. On-board I/O is only accessible when the 68000 is in Supervisor mode; an attempt to access on-board I/O while in user mode will result in a bus-error trap. Note that this restriction is controlled by the PROTECTION PROM on a socket in position D10. Contact Integrated Solutions directly if more information on the PROTECTION PROM is required.

#### 3.1.1 Segment Registers

There are 16 sets of of 64 segment registers; one set is assigned to each of the 16 contexts. Each segment register is eight bits long, is readable and writable, and is accessed over the least significant half of the bus (ie, the least significant byte of a word operation or an odd byte address).

The segment registers are loaded through the following I/O addressing mechanism:

| Address    | Contents                                                                                |

|------------|-----------------------------------------------------------------------------------------|

| bits 23,22 | 01 - indicates that the segment register bank is selected                               |

| bits 21-16 | OH-3FH - select one of the 64 registers in the context                                  |

| bits 15-12 | OH-FH - selects one of the 16 contexts                                                  |

| bits 11-1  | not decoded/don't care                                                                  |

| bit 0      | the 8 bits of the segment register are located on the least significant half of the bus |

#### NOTE

The segment registers are 8 bits long and are located on the least significant half of the bus. They can either be accessed via a byte access to the corresponding odd address or a word access to the corresponding even address. In the case of a word access, the upper eight bits of the bus are a don't care.

The following are examples of two typical segment register access addresses:

420001H - segment register #2 of context #0, the system context

536001H - segment register #19 of context #6

Each segment register contains 6 address translation bits, bits 5-0, which select one of

64 sets of 16 page registers and two protection bits 7 and 6. The protection bits are encoded for the following four access modes. Only mode 11, execute only, makes any distinction between supervisor and user mode in its functioning.

| bit 7 | bit 6 |                                                                                                                                  |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | no access, any attempt to access this segment (supervisor or user mode) will result in a bus error trap.                         |

| 0     | 1     | read only and execute access, any attempt<br>to write this segment (supervisor or user<br>mode) will result in a bus error trap. |

| 1     | 0     | read/write access, all forms of access are permitted in both supervisor and user modes.                                          |

| i     | 1     | all forms of access are permitted in<br>supervisor mode but program references<br>only are permitted in user mode.               |

The following examples give typical segment register entries:

80H - select page register set 0 (page registers 000H-00FH) for read/write access. The 68000 logical address bits 15 -12 select which page register is used to complete the translation.

7EH - select page register set 62 (3E0H-3EFH) for read only access. Again, logical address bits 15-12 select which page register in the set are used to complete the translation.

## 3.1.2 Page Registers

There are 1024 page registers which are accessed from 800000H-BFF000H in the 68000 logical address space. The page registers are each 12 bits long and are accessed by word references to even addresses according to the following mechanism:

| Address    | Contents                                                                               |

|------------|----------------------------------------------------------------------------------------|

| bits 23-22 | 10 - indicates that the page register bank is selected                                 |

| bits 21-12 | 000H-3FFH - selects one of the 1024 page registers                                     |

| bits 11-1  | not decoded/don't care                                                                 |

| bit 0      | 0 - page registers must be accessed via word accesses; byte accesses are not supported |

The addresses of the first and second page registers are 800000H and 801000H respectively and the addresses of the last two page registers are BFE000H and BFF000H. Each

page register contains 12 bits which are used as follows:

| Bit  |      | Function                                                                                                                                         |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bits | 11-2 | the 10 address translation bits which select<br>one of the 1024 physical pages (each page is 4 kbytes long)<br>of memory that are to be accessed |

| bit  | 1    | the page accessed bit                                                                                                                            |

| bit  | 0    | the page written bit                                                                                                                             |

To form a 22 bit physical address, the 10 tranlated address bits from the page register concatenated with the bottom 12 bits of logical address from the 68000:

```

selected page register logical address == > physical address contents bits 11-2 | bits 11-0 | bits 21-0

```

Four page register contents have special meaning:

3FCH and 3FDH - page register contents 3FCH and 3FDH always indicate the invalid page. Any attempt to access the invalid page either in supervisor mode or user mode will result in a bus error trap.

3FEH and 3FFH - page register contents 3FEH and 3FFH always refer to the LSI-11 bus I/O page. When these two pages are accessed, the LSI-11 bus BBS7 signal is asserted. In addition, the I/O page is always assumed to be located on the LSI-11 bus even if all 4 megabytes of physical memory are located on the local bus (see section 2.2). The upper 16 kilobytes of memory even if present in the system are not accessible by the 68000.

## 3.1.2.1 Page Accessed Bit (bit 1 of the page register)

The page accessed bit can be loaded as either 0 or 1 when the page register is loaded and it is changed to '1' whenever an access to that page is made: In normal operation, the page register accessed bits are written to zero as a process or part of a process is loaded into memory by the operating system. When any access to that page is made in the course of executing the process, the bit is converted to a '1'. The operating system, in the course of swapping out pages will examine the page accessed bits as part of deciding which pages to page out.

## 3.1.2.2 Page Written Bit (bit 0 of the page register)

The page written bit can be loaded as either 0 or 1 when the page register is loaded and it is changed to '1' whenever any change to that page is made. In normal operation, the page written bits are written to zero as a process or part of a process is loaded into memory by the operating system. When any change to that page is made in the course of executing the process, the bit is converted to a '1'. Pages which have not been changed can be paged out by simply loading the new page over them; the old page does not have to be written to the swapping device.

## 3.1.3 Context/Exception Register - C10001H -

The context/exception register is eight bits long is writable and readable and is located on the least significant half of the data bus. A special access method has been implemented to save hardware. The context/exception register MUST be written with a word reference to location C10000H (the upper byte of data is discarded) and it must be read with a byte reference to location C10001H. Attempting to write the register with a byte write to location C10001H will result in no update. The context/exception register has two four bit fields with the following functions:

## Context bits - bits 7-4 -

The context register allows the user to select which context, i.e., which set of segment registers is used when the processor is in user mode. When the processor is in supervisor mode, context 0 is always used regardless of the contents of the context register but the contents of the context register are preserved. In this manner, a user process can be interrupted, a switch to context 0 made automatically by the hardware and the interrupt serviced and a return to the previous user context made without touching the context register.

## Exception bits - bits 3-0 -

The exception register has 4 read/write bits, three of which allow the user to determine the source of a bus error and the fourth of which serves as a parity enable bit to enable on-board parity checking.

#### bit 3 - bus timeout

A bus timeout can occur for one of several reasons:

- an attempt was made in either supervisor or user mode to access memory which is not existent. In this case, bits 2 and 1 will be reset.

- an attempt was made in user mode to access the on/board I/O space. In this case, the bus timeout bit will be set as well as bit 1, the protection violation bit.

- an attempt was made to access segments which have been set no access in the segment register, an attempt was made to write segments which are read only, or an attempt was made to access pages which have been marked invalid and the physical memory was located on the LSI-11 bus. If the physical memory is present on the local bus, only the protection violation bit is set; no bus timeout occurs.

#### bit 2 - invalid page

This bit is set when an effort is made to access a page that has been marked invalid in the page register. The invalid page bit will occur by itself when the physical page is located in local bus memory and in conjunction with the bus timeout bit when the page is located on the LSI-11 bus. In neither case is any memory write performed even if the memory is physically present in the system.

## bit 1 - protection violation

A protection violation can occur either when an access is made to a protected segment, or in user mode, an attempt is made to access on-board I/O (a 68000 logical address above 3FFFFFH).

## bit 0 - parity enable

When this bit is set to 1, parity is enabled for on-board/local bus memory. When cleared, parity is not checked, but parity is generated for all on-board memory writes. Parity errors will occur if the memory is not written to before being accessed if parity is enabled. The memory must initially be purged of all parity errors before parity is enabled.

## NOTE

The four exception bits of the context/exception register are cleared to zero on system reset/power up.

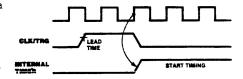

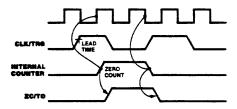

## 3.1.4 Serial Ports/Counter-Timer - C20001-C21007

The IS-68K board has two serial ports and four counter/timer channels. Two of the counter/timer channels are dedicated to providing programmable baud rate for the two serial channels and the remaining two channels are concatenated to form a single programmable timer. This timer can be used to generate interrupts every 1/60th of a second if the IS-68K is used in a system that does not have a power supply that generates a BEVNT every 1/60th of a second or it can be used as a general purpose programmable timer in control applications.

The counter/timer chip is a Zilog CTC chip and is accessed at the following addresses:

C20001 - Channel 0

C20003 - Channel 1

C20005 - Channel 2

C20007 - Channel 3

The serial chip is either a Zilog DART chip or a Zilog SIO chip. The SIO provides SDLC and HDLC capabilities that are not present in the DART. Both the DART and the SIO support asynchronous and high speed synchronous communications. All IS-68Ks are shipped with DARTS unless the SIO is specified. There are four ports associated with the DART:

C21001 - DART Channel 0 DATA

C21003 - DART Channel 1 DATA

C21005 - DART Channel 0 CONTROL

C21007 - DART Channel 1 CONTROL

## 3.1.5 Status Register - C30000H

The status register is located at word location C30000h and has ten bits which are read only. The four latched error bits, bits 5 through 9, can be cleared by any write operation to the status register. The data written is irrelevant; all four bits are always cleared by the write operation. The bits in the status register have the following functions:

#### Bit Function

9 PWR FAIL - The falling edge of the BPOK signal is latched. This indicates that a DEC compatible power supply has a minimum of 4

ms. of power remaining.

- 8 BUS PARITY ERROR An error has been detected and latched on an LSI-11 bus read

- 7 ON-BOARD PARITY ERROR A 68000 read access to on-board/local bus memory has resulted in a parity error.

- 6 HALT line The falling edge of the HALT line has been detected and latched.

- 5 Inverted BPOKH This signal goes low whenever BPOK is high and high whenever BPOKH is low. This signal could be used to resume processing after a power failure only when BPOKH has become active again.

- Inverted BHALTL This line is high when BHALTL is asserted on the LSI-11 bus and low when BHALTL is not asserted (processor enabled). This line could be used to emulate the DEC HALT function by inhibiting the processor from running when the HALT line is asserted.

- 3 Dipswitch bit 5

- 2 Dipswitch bit 6

- 1 Dipswitch bit 7

- O Dipswitch bit 8

Once an error is latched into the one of the upper four bits of the status register, it remains there until cleared by one of the following events:

- another error occurs in which case the new error will be latched into the appropriate bit of the STATUS register and a second level 7 interrupt will occur.

- a system RESET is executed externally by dropping BDCOKH on the LSI-11 bus or internally by executing the 68000 RESET instruction.

- any write operation to the STATUS register

#### APPENDIX A

## INITIALIZING AND PROGRAMMING THE SERIAL PORTS

## A.1 Initialising

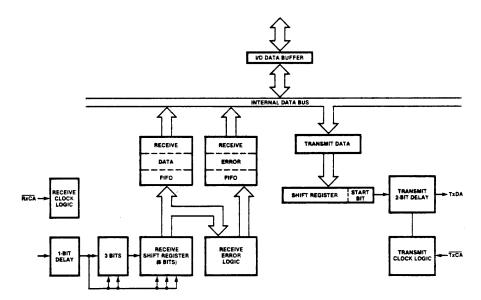

The Zilog DART on the IS-68K board is a two channel, full duplex asynchronous/synchronous serial control chip, with full modem control. Both channels are completely independent, so that one may be operating in synchronous mode at one clock rate while the other is operating in asynchronous mode at another clock rate. Baud rates in asynchronous mode are programmable through the programming of two channels of the associated counter/timer chip. In synchronous mode, the clock must be externally generated for both transmission and reception. Baud rates up to 1 megabit/second can be supported in this mode by the hardware.

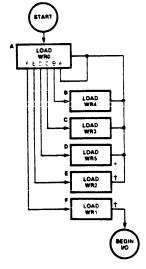

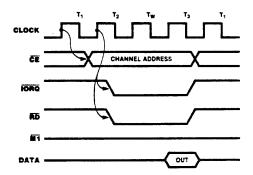

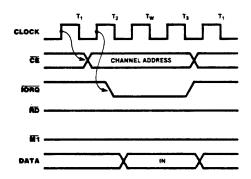

Before data can be transmitted and received via the DART, it must be initialized to define the operating characteristics of each of its two channels. Initialization of the DART consists of writing a string of control bytes to each of its two control registers which are located at C21005H and C21007H. The control register at C21005H corresponds to channel 0 and the control register at C21007H corresponds to channel 1. There are actually 5 write registers and 2 read registers associated with each channel of the DART. In addition, there is an additional read/write register associated with channel 1 which is not present in the channel 0 write register array. Of these 16 registers only WRITE REGISTER 0 and READ REGISTER 0 of the two channels are accessible directly. The remaining 12 registers must be accessed by writing a pointer to WRITE REGISTER 0 of the corresponding channel. The next read or write operation will then cause the pointed-to register to be accessed.

The following is a detailed description of the functions of the WRITE and READ REGISTER bits:

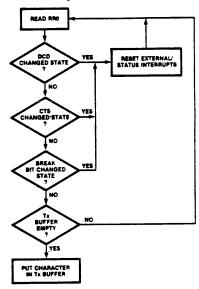

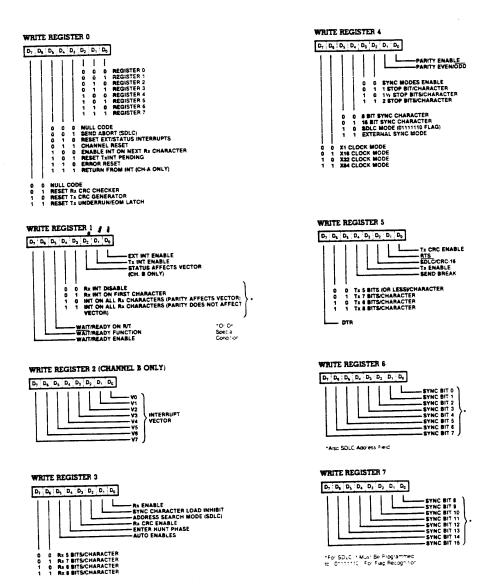

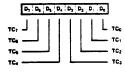

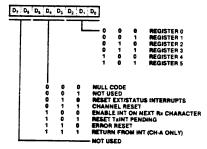

## WRITE REGISTER 0

WRITE REGISTER 0 has two functions; it has bits 5,4,3 which implement commands directly and bits 2,1,0 which serve as a pointer to allow accessing of other write and read registers. Bits 7 and 6 of write register 0 are not used in this application.

bits 5,4,3

000 - null code - no function directly implemented

010 - reset external status/interrupts

Performing this function has two effects. The piece of READ REGISTER 0 called external status is updated to agree with the current state of the lines entering the DART. This is important because once a change in one of the external status lines (including a BREAK condition on the data receive line) is detected by the DART, bits 7-3 are permanently latched in that condition until the next RESET EXTERNAL STATUS/INTERRUPTS is received.

The RESET EXTERNAL STATUS/INTERRUPTS, for example, must be issued repeatedly after a BREAK condition is detected by the DART in order to detect the end of the BREAK. If not issued, the BREAK bit in READ REGISTER 0 will stay latched

forever.

The second function of this command is to reset pending interrupts that are associated with this change in external status.

011 - channel reset

This command should always be the first command issued to each channel of the DART when the DART is initialized.

100 - enable interrupt on next received character

This command has meaning only when the DART is set up only to interrupt on the first received character. It resets the DART so that it will interrupt on the next received character and must be issued in the received character interrupt service routine when the DART is set up in this mode.

101 - reset transmitter interrupt pending

A transmitter interrupt will occur when the transmitter input buffer (a two deep SILO) goes empty. This command allows this interrupt to be reset without being serviced.

110 - error reset

This command should be issued when one of the three error conditions - parity error, data overrun error, or framing error (bits 4,5,6 in read register 1) is detected. These error bits have the same characteristic that the EXTERNAL STATUS bits in READ REGISTER 0 have, i.e., they are latched until cleared by this command.

111 - return from interrupt (channel 0 only)

This command is the last command issued before returning from the interrupt service routine. Its effect is to clear the DART interrupt that was serviced and setup the DART for subsequent interrupts.

The remaining combinations of bits 5,4,3 have no meaning in the DART.

bits 2,1,0

These bits are used to point to one of the other five write registers or one of the two directly inaccessible read registers of the DART. The next read or write operation to the DART will cause the pointed to register to be accessed. One of the commands in bits 5,4,3 is often simultaneously executed with the pointing operation. Often this command is the RESET EXTERNAL STATUS/INTERRUPTS command.

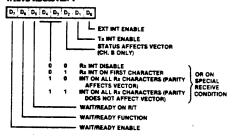

#### • WRITE REGISTER 1

bits 7,6,5 - not used in this application

bits 4,3 -

00 - disable receiver interrupts

- 01 interrupt on first received character only

- 10 interrupt on all received characters (vector is affected by parity error)

- 11 interrupt on all received characters (vector is not affected by parity error)

bit 2

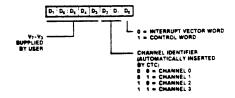

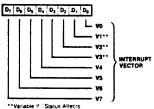

Enable STATUS affects vector (this bit present in channel 1 only but affects both channels). If this bit is enabled, bits 3,2,1 of the vector programmed into the DART will be modified to a value that depends on the source of the interrupt.

bit 1 - enable transmitter interrupts

bit 0 - enable interrupts on changes in external conditions (CTS,DCD)

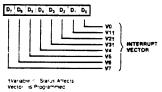

• WRITE REGISTER 2 (Present in channel 1 only but affects both channels)

bits 7-0

These 8 bits form the base interrupt vector. Remember that the raw interrupt vector must be multiplied by four to give the entry in the 68000 interrupt vector table at the bottom of physical memory. In addition, if the STATUS AFFECTS VECTOR bit in WRITE REGISTER 1 is on, bits 3-1 of the interrupt vector will be modified depending on the source of the interrupt.

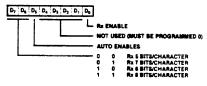

#### • WRITE REGISTER 3

bits 7,6

00 - 5 bits/char on receiving characters

01 - 7 bits/char on receiving characters

10 - 6 bits/char on receiving characters

11 - 8 bits/char on receiving characters

bit 5

Enables a feature called AUTOENABLE which automatically performs the following modem control functions:

DATA CARRIER DETECT (DCD on the serial I/O connector) must be asserted before reception of characters will take place and CLEAR TO SEND (CTS on the serial I/O connector) must be asserted before transmission of characters can begin. This bit should be programmed with caution because once set, the serial channel will hang if transmission or reception of characters is attempted without the appropriate signal line assertion.

bits 4-1 not used - must be 0s

bit 0 - receiver enable

This bit must be a '1' to enable reception of characters.

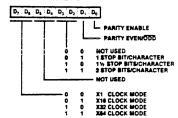

## • WRITE REGISTER 4

bits 7,6-

00 - straight thru mode. The incoming clock is used directly as the baud rate. This clock can ONLY be used if the incoming data is synchronized to be valid during the rising edge of the clock, i.e. only for synchronous operation.

01 - divide by 16 clock mode. The incoming clock from the CTC (counter timer chip) is divided by 16 before being used as the baud rate.

10 - divide by 32 clock mode. The incoming clock from the CTC is divided by 32 before being used as the baud rate.

11 - divide by 64 clock mode. The incoming clock from the CTC is divided by 64 before being used as the baud rate.

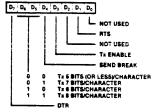

## • WRITE REGISTER 5

bit 7

DTR - This bit directly controls the DTR line on the serial interface. Setting the bit to 1 results in an active DATA TERMINAL READY line.

bits 6,5

00 - transmit with 5 bits/character

01 - transmit with 7 bits/character

10 - transmit with 6 bits/character

11 - transmit with 8 bits/character

bit 4

SEND BREAK - causes a continuous break to be sent on the TxD line of the corresponding channel until the bit is cleared.

bit 3

Tx ENABLE - This bit must be set to enable transmission of characters.

bit 2

Not used.

bit 1

RTS - This bit directly controls the RTS line on the serial interface. A '1' causes an active READY TO SEND signal.

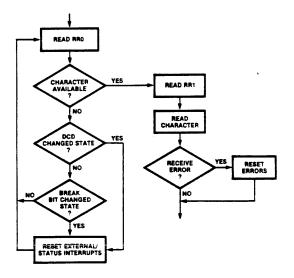

## • READ REGISTER 0

bits 7,5,3

These bits are the EXTERNAL STATUS bits. Bit 7 monitors a BREAK condition in the received data line while bits 5 and 3 monitor CTS and DCD respectively. Any

BREAK or change in the CTS or DCD lines will cause the corresponding bit to go to one and the other two bits latched in their zero state. This condition can be reset by issuing the RESET EXTERNAL STATUS/INTERRUPTS command.

bits 6,4

Not used.

bit 2

Tx Buffer Empty - This bit goes to '1' whenever the transmit buffer can receive another character. Because, the transmit path is double-buffered, it does not necessarily mean that the last character has been fully transmitted. See READ REGISTER 1 bit 0 for this function.

bit 1

Interrupt Pending - (implemented in channel 0 only) This bit indicates that some interrupt is currently pending in the DART.

bit 0

Rx Character Available - This bit goes to '1' whenever a character has been assembled in the receive SILO and is ready for pickup.

#### • READ REGISTER 1

bit 7

Not used.

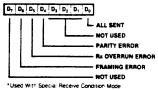

bit 6,5,4

Error Bits - These are the three latched error bits that can occur on character reception. Bit 6 corresponds to Framing Error, bit 5 corresponds to Receiver Overrun and bit 4 corresponds to Receiver Parity Error. Once one of these bits is latched, the three bits can be reset by issuing an ERROR RESET command.

bits 3,2,1

Not used.

bit 0

All Sent - This bit goes to one whenever all the characters put in the transmitter SILO have been transmitted.

## • READ REGISTER 2 (Channel 1 only)

bits 7-0

Interrupt Vector - This register allows the programmed interrupt vector to be read. If STATUS AFFECTS VECTOR is set, this register will have the current modified vector in it.

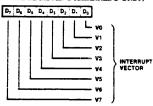

#### A.2 Interrupt Vectors

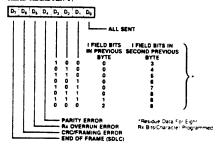

The Zilog DART has a versatile interrupt scheme in which the DART chip itself will automatically vary the interrupt vector under the different interrupt conditions. This is a useful construct when the speed of interrupt response is critical. The alternative of having only one interrupt vector and having the interrupt service routine sort out the source of the interrupt causes a speed degradation. There are eight possible vectors which may be issued by the DART, four for each channel. A bit in WRITE REGISTER 1 when set allows the modified vectors to be generated. Unfortunately, the DART modifies vectors by simply changing bits 3-1 of the vector word. This places two constraints on the vectors that can be generated by the DART:

- The base vector must be xxxx000xb (binary) in order for eight unique vectors to be generated. The eight vectors generated are the permutations of bits 3-1 with bits 7-4 and 0 remaining unchanged.

- The vectors, when multiplied by four, should remain within the Motorola user interrupt space. This means that vectors from 40H to FFH are permitted. Note that there is no protection in the 68000 against vectors below 40H but they should be used with caution so that they do not overlap the system traps.

The modified vectors than can be generated are:

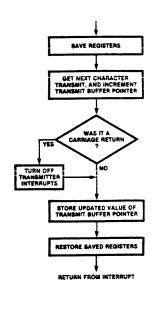

xxxx000x - channel 1 Transmit Buffer Empty - must have Tx Interrupt enabled.

xxxx001x - channel 1 External Status Transition - must have interrupt on changes in external conditions enabled.

xxxx010x - channel 1 Character Received - must have one form of receiver interrupts enabled

xxxx011x - channel 1 Special Receive Condition - the special receive condition interrupt always occurs if receiver interrupts have been enabled.

xxxx100x - Channel 0 Transmit Buffer Empty

xxxx101x - Channel 0 External Status Transition

xxxx110x - Channel 0 Character Received

xxxx111x - Channel 0 Special Receive Condition

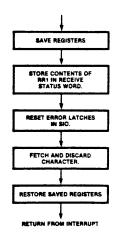

## A.3 Special Receive Condition

A special receive condition occurs if in the process of receiving a character one of the following erroneous conditions occurs:

- a parity error occurs if parity checking is enabled.

- a data overrun occurs. The three character SILO of the DART has overflowed.

- a framing error occurs.

Once a special receive condition has been detected, it will be latched in READ REG 1

bits 6,5,4 until the ERROR RESET command is issued.

# A.4 Typical DART Initialisation Sequence

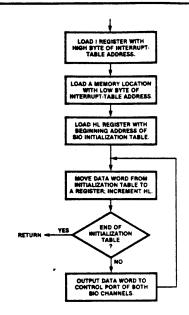

The DART is typically initialized in a short program loop which writes a string of bytes into the control register of each channel. The following code is the MACSBUG PROM resident code which initializes the DARTS.

| SIO0LP:            | LEA<br>MOVL<br>MOV<br>MOVB<br>DBRA          | SIOTAB,A1<br>#\$C21005,A0<br>#8,D0<br>(A1)+,A0<br>D0,SIO0LP                                 | ;LOAD ADDRESS OF PARAMETER TABLE<br>;CHANNEL 0 CONTROL PORT                                                   |

|--------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| SIO1LP:<br>SIOTAB: | ADDQ<br>LEA<br>MOV<br>MOVB<br>DBRA<br>.BYTE | #2,A0<br>SIOTAB,A1<br>#8,D0<br>(A1)+,A0<br>D0,SIO1LP<br>18,14,44,13,0C1,<br>15,0EA,11,00,00 | ;NOW PROGRAM CHANNEL 1<br>;POINT TO CHAN 1 CONTROL PORT<br>;POINT TO BEGINNING OF TABLE<br>;SET UP LOOP AGAIN |

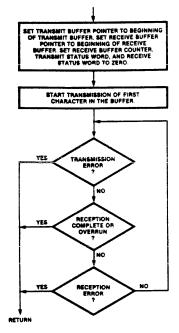

## A.5 Typical Operation of the DART:

Once the DART is initialized, it can be programmed by writing or reading 8 bit parallel data directly from the data port for the appropriate channel. To transmit data to the DART, the user would poll the TRANSMIT BUFFER EMPTY bit of READ REGISTER 0 before stuffing a character into the DART.

| TXLOOP: | BTST.B<br>BEQ |                       | ;CHK IF XMIT BUFFER IS EMPTY |

|---------|---------------|-----------------------|------------------------------|

|         | MOV.B         | TXLOOP<br>D0,\$C21001 | SEND DATA OUT                |

To read from channel 0 of the DART, the user would poll bit zero of READ REGISTER 0 until a character was received.

| RXLOOP: | BTST.B | #0, <b>\$</b> C21005 |                  |

|---------|--------|----------------------|------------------|

|         | BEQ    | RXLOOP               |                  |

|         | MOVB   | <b>\$</b> C21001,D0  | ;SAVE DATA IN DO |

A more complete routine would look at the break bit in READ REGISTER 0

| RXLOOP: | MOVB | \$C21005,D0         |                      |

|---------|------|---------------------|----------------------|

|         | BTST | #7,D0               | CHK THE BREAK BIT    |

|         | BNE  | BREAK               | ;BRANCH IF BREAK SET |

|         | BTST | #0,D0               |                      |

|         | BEQ  | RXLOOP              |                      |

|         | MOVB | <b>\$</b> C21001,D0 | SAVE DATA IN DO      |

BREAK:

MOVB

#\$18,\$C21005

;ISSUE RESET EXTERNAL

;STATUS/INTERRUPTS

**BTSTB**

#7,**\$**C21005

;IS BREAK STILL SET ;YES KEEP LOOPING

BNE

BREAK

NOW ENTER THE BREAK SERVICE ROUTINE

#### APPENDIX B

#### MACSBUG COMMANDS

#### **B.1** Overview

The MACSBUG option provides a resident firmware monitor for the 68000. This monitor supports a variety of commands for debugging and downloading progams, including commands to:

- display or change registers and memory

- control program execution through branching, breakpoints, and single and multiple stepping

- selectively display tracing information at breakpoints and while stepping

- communicate with a host computer

- use a limited form of relative addressing with certain of the above commands.

In addition, programming effort is eased somewhat by commands to perform arithmetic mode conversions and to allow symbolic access to numbers and memory locations.

These commands are discussed in detail in the following sections.

The MACSBUG command prompt is an asterisk (\*). This prompt is shown in the examples in this Appendix; it is not to be entered by the user.

Input to MACSBUG is buffered. A control X (^X) cancels the line being entered; ^H, RUBOUT, and DEL delete the last character entered (but do not erase it from the screen - to redraw the line enter ^D). A ^W will stop output to the console; entering any other character will start it again. The BREAK key will stop almost anything MACSBUG is doing (but will not kill a user program running under MACSBUG).

#### B.2 Displaying or Changing Registers and Memory

#### **B.2.1** Displaying Registers

The hex contents of any of the 68000's registers can be displayed by entering the name of the register in response to the MACSBUG prompt. For example,

\*A3<cr>

might produce

A3=0000146A.

The names of the registers are as follows:

D0, ..., D7 data registers

A0, ..., A7 address registers

PC program counter

SR status register

SS supervisor stack pointer

US user stack pointer.

Recall that A7 is SS in supervisor mode, US in user mode.

All of the address or data registers can be displayed by entering A or D, respectively. For example,

\*D<cr>

D0=00000000 D1=FFFFFFF D2=1479630A D3=00000001

D4=FFFFFFF D5=00000000 D6=00000000 D7=A0369741

Registers can also be displayed as part of a trace display. (See B.4.)

#### **B.2.2** Changing Registers

Data can be entered into registers in either hex or ASCII. Hex is the default; to enter ASCII data, enclose it in single quotes. The simplest way to change a register is to enter the register name followed by the new data; thus

\*SR 0<cr>

will clear the status register, while

\*D3 'Fred' < cr >

will put 46726564 (ASCII 'Fred') in data register 3. An attempt to put more than four characters of ASCII data in a register will result in a SYNTAX ERROR message, while an attempt to enter more than eight hex digits will result in simply ERROR. (MACBUG's error messages are sometimes slightly obscure.) Data items shorter then eight hex digits or four ASCII characters will be padded on the left with zeroes.

To display the contents of a register and optionally change it, enter the name of the register followed by a colon. For example,

\*A4:<cr>

might produce

A4=00001A47 ?

To change the value in A4, enter the new value after the question mark; e.g.,

A4=00001A47 ? 1A43

If the old value is satisfactory, simply enter a carriage return.

It is also possible to cycle through the address or data registers, examining and optionally changing them one at a time, by entering A: or D: and responding to the ensuing question marks with new data or carriage returns.

#### **B.2.3** Displaying Memory

Memory is displayed in chunks of sixteen (hex 10) bytes. Hex and ASCII representations are shown side-by-side. To display the contents of an address, use the DM command followed by the hex address. Thus,

\*DM 3000 might produce