**Computer Products**

The Double D

# JADE COMPUTER PRODUCTS PRESENTS

# Double D

THE DOUBLE DENSITY DISK CONTROLLER

HARDWARE MANUAL

IOD-1200M

REVISION C

Copyright (C) 1980

Jade Computer Products

4901 Rosecrans Ave

Hawthorne, California

90250

All Rights Reserved

# **Jade Double D, Double-Density Disk Controller**

The new Jade Double D Disk Controller represents a major advance in Floppy disk recording technology. Designed at the leading edge of state-of-art technology, it is the first truly universal disk controller.

The Double D is S-100 compatible and meets all specifications of the proposed IEEE S-100 standard. It is based on the Western Digital 1791 with advanced phase locked-loop frequency control.

- 51/4" or 8" drive capability

- Single or double-sided recording

- Single or double-density recording

- IBM 3740 or System 34 soft sector format

- Use programmable formatting

- Will handle Shugart, MFE, Sieman MPI, and other drives

- Fully CP/M compatible

- Programmable single or double-density, and single or double-sided

- Supported by a vast library of software, including an extensive business systems package

- Designed to work with dynamic or static memory cards

# **SPECIFICATIONS**

| BUS                | S-100                                                                | DIMENSIONS | Standard S-100<br>10.0" Wide         | 5.0" High, |

|--------------------|----------------------------------------------------------------------|------------|--------------------------------------|------------|

| COMPATIBLE CPU'S   | Z80,<br>8080 & 8085, Single Density                                  | CONNECTORS | S-100 — 100 pin<br>.125 spacing      | card edge, |

| STORAGE CAPACITY   | Greater than 8 Megabytes (8 Double-Density, Double-                  |            | 5¼" Disk — 34<br>edge, .100 spaci    | ng         |

|                    | Sided 8" Drives ) Greater than 1 Megabyte (3 Double-Density, Double- |            | 8" Disk — 50 pir<br>edge, .100 spaci |            |

|                    | Sided 51/4" Drives)                                                  | COST       | Assembled & Tested                   | \$299.00   |

| POWER REQUIREMENTS | + 8VDC @ 850 MA (Max)<br>+ 16VDC @ 50 MA (Max)                       |            | Kit                                  | \$249.00   |

| OPERATING TEMP.    | 0 to 50° C                                                           |            | Bare Board                           | \$ 55.00   |

CP/M is a Trademark of Digital Research

# TABLE OF CONTENTS

| SECTION                                                                                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     | PAGE                    |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1<br>1.1<br>1.2<br>1.3                                                                                             | INTRODUCTION SCOPE RELATED DOCUMENTATION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                            | 1<br>1<br>1             |

| 2.1<br>2.3<br>2.5<br>2.6<br>7<br>8<br>9<br>10<br>11<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1<br>2.1 | HARDWARE DESCRIPTION OVERVIEW MEMORY ADDRESS DECODING PORT ADDRESS DETECTION BUS CONTROL SIGNALS DISK PROCESSOR CONTROL PORT DISK PROCESSOR STATUS PORT CLOCK GENERATION PROCESSOR DISK CONTROLLER DISK INTERFACE INTERNAL I/O ADDRESSES BOARD LEVEL STATUS PORT BOARD LEVEL STATUS PORT ON-BOARD TIMER STEP CONTROL WAIT STATE GENERATOR VECTOR INTERRUPT GENERATOR EIA LEVEL INTERFACE MEMORY CONTROL WRITE PRECOMPENSATION PHASE-LOCKED LOOP | 33345566778891111223144 |

| 3<br>3.1<br>3.2<br>3.3                                                                                             | BOARD ASSEMBLY INTRODUCTION ASSEMBLY CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                              | 19<br>19<br>19<br>25    |

| A<br>B<br>C<br>D<br>E                                                                                              | APPENDICES  COMPONENT LAYOUT PARTS LIST INTERNAL SIGNAL DEFINITIONS S-100 BUS CONNECTIONS SCHEMATICS FEEDBACK                                                                                                                                                                                                                                                                                                                                   |                         |

#### SECTION 1

#### INTRODUCTION

#### 1.1 SCOPE

This manual contains the complete hardware description of the Jade Double Density Disk Controller. It provides the end user with construction and configuration procedures, and a functional description of the circuitry.

#### 1.2 RELATED DOCUMENTATION

Double D Software Manual P/N IOD-1201M FD 179X-01 Specifications Z80A-CPU Technical Manual

Jade Computer Products Western Digital Corp. Zilog, Inc.

#### 1.3 DESCRIPTION

The Double D is an intelligent S-100 based disk controller. It is capable of handling up to four full size (8") or mini (5") disk drives. Provisions have been made for double sided drives. Single and double sided drives may be mixed. The controller is capable of single density (FM) and double density (MFM) operation. It can be used in software polled as well as interrupt driven environments. Circuitry is implemented on a four layer printed circuit board where one inside layer is used as a ground plane. This provides for a minimal amount of ground noise. This board was designed to meet the proposed S-100 signal disciplines as defined in IEEE Task 696.1/D2

The Double D contains an on-board Z8OA microprocessor with 2K of static memory. The on-board processor runs simultaneously with and transparent to the S-100 bus. All critical timing is handled on-board; data transfers are fully buffered by sector in the on-board memory, two levels of interrupt are implemented on the Z8OA, and a wait state generator is used to synchronize the on-board processor to the disk transfer rate. The host system (8080, 8085, Z8O, or ?) need only transfer commands and data through a block of static memory, which can be accessed from the bus. This architecture provides a high degree of timing independence from the host system. Also, since the disk controller program is contained on-board in ram, this board's operational characteristics are redefinable at any time during system operation.

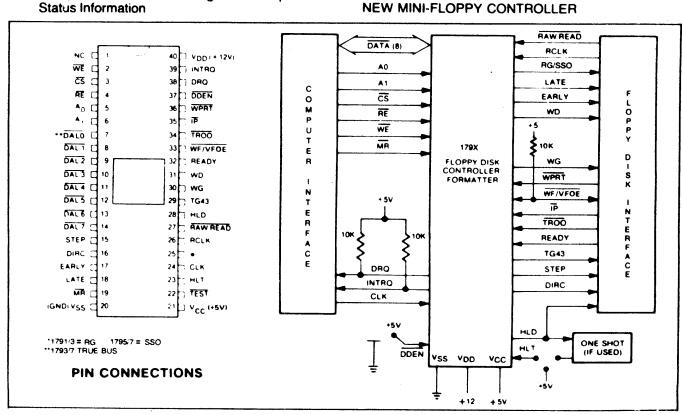

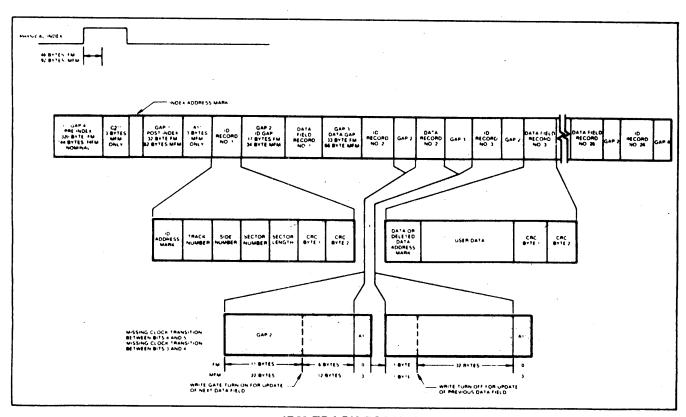

The powerful FD 1791-01 Formatter/Controller is used to encode and decode all data transfers to and from the disk drives. It also provides for the generation and checking of address marks, data marks, and the cyclic redundency characters. Write Precompensation can be selected under software control at three levels of intensity, providing flexible data recording. Data separation is achieved by the use of a phase-locked loop to insure maximum immunity to disk speed variation and to enhance data recovery margins in both single and double density.

#### 1.3 DEVICE SPECIFICATION

| Power requirements:           | +7 TO +11 Volts                                  | 0.90 Amp. Typical<br>1.50 Amp. Mayimum                          |

|-------------------------------|--------------------------------------------------|-----------------------------------------------------------------|

|                               | +14.5 to +21.5 volts                             | 25 Ma. Typical<br>50 Ma. Maximum                                |

|                               | -14.5 to -21.5 volts                             | 8 Ma. Typical<br>30 Ma. Maximum                                 |

| System Port<br>Requirement:   | One I/O port, switch selectable                  | 40,41,42,47 Hex                                                 |

| System Memory<br>Requirement: | 1K Byte block<br>switch selectable               | E000, E400, E800, EC00, F000, F400, F800, FC00 Hex              |

| Recording Method:             | Single density in FM Double density in MFM       |                                                                 |

| External                      |                                                  |                                                                 |

| Communication:                | One EIA compatable inp<br>One EIA compatable out | ut signal<br>put signal                                         |

| Disk Interface,               |                                                  |                                                                 |

| Connectors:                   | 8" Drives 50                                     | Pin Card Edge Connector<br>AMP P/N 888083-1<br>3M P/N 3415-0001 |

|                               | 5" Drives 34                                     | Pin Card Edge Connector<br>AMP P/N 583717-5<br>3M P/N 3463-0001 |

| System Interrupts:            | Optional Feature,<br>Vector Interrupt on         | VIO* thru VI7*                                                  |

#### SECTION 2

#### HARDWARE DESCRIPTION

#### 2.1 OVERVIEW

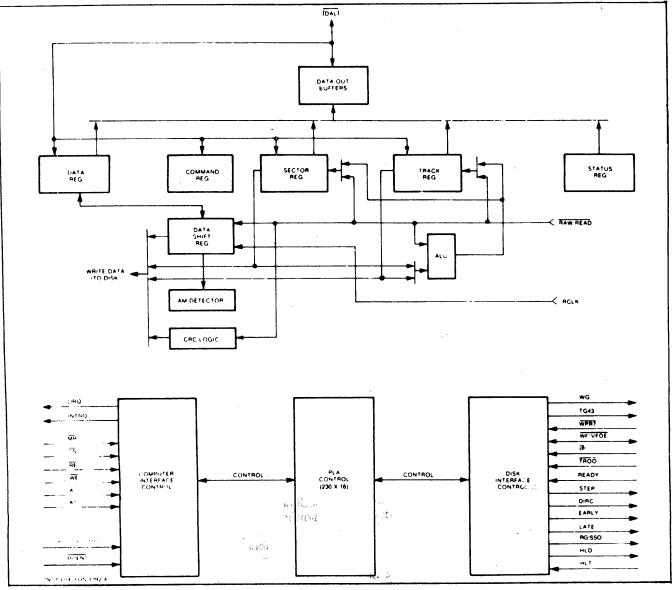

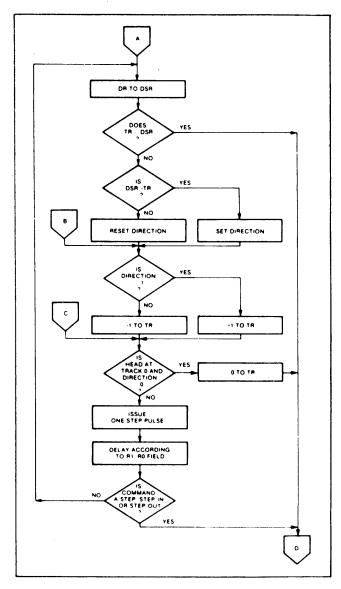

The operational characteristics of the DOUBLE D are a function of both hardware and on-board software. The hardware provides the data paths, logic functions, and control signals necessary to implement such operations as head loading, drive selection, head positioning, and transfering data. It is the software that determines how the disk controller commands are interpreted and in what sequence controller events take place. As in all microprocessor designs, the software can do no more than hardware implementation allows. The DOUBLE D is designed to allow the on-board software as much control as possible. For the user who will write control programs for this board, an understanding of the hardware is recommended. This section provides a description of the hardware.

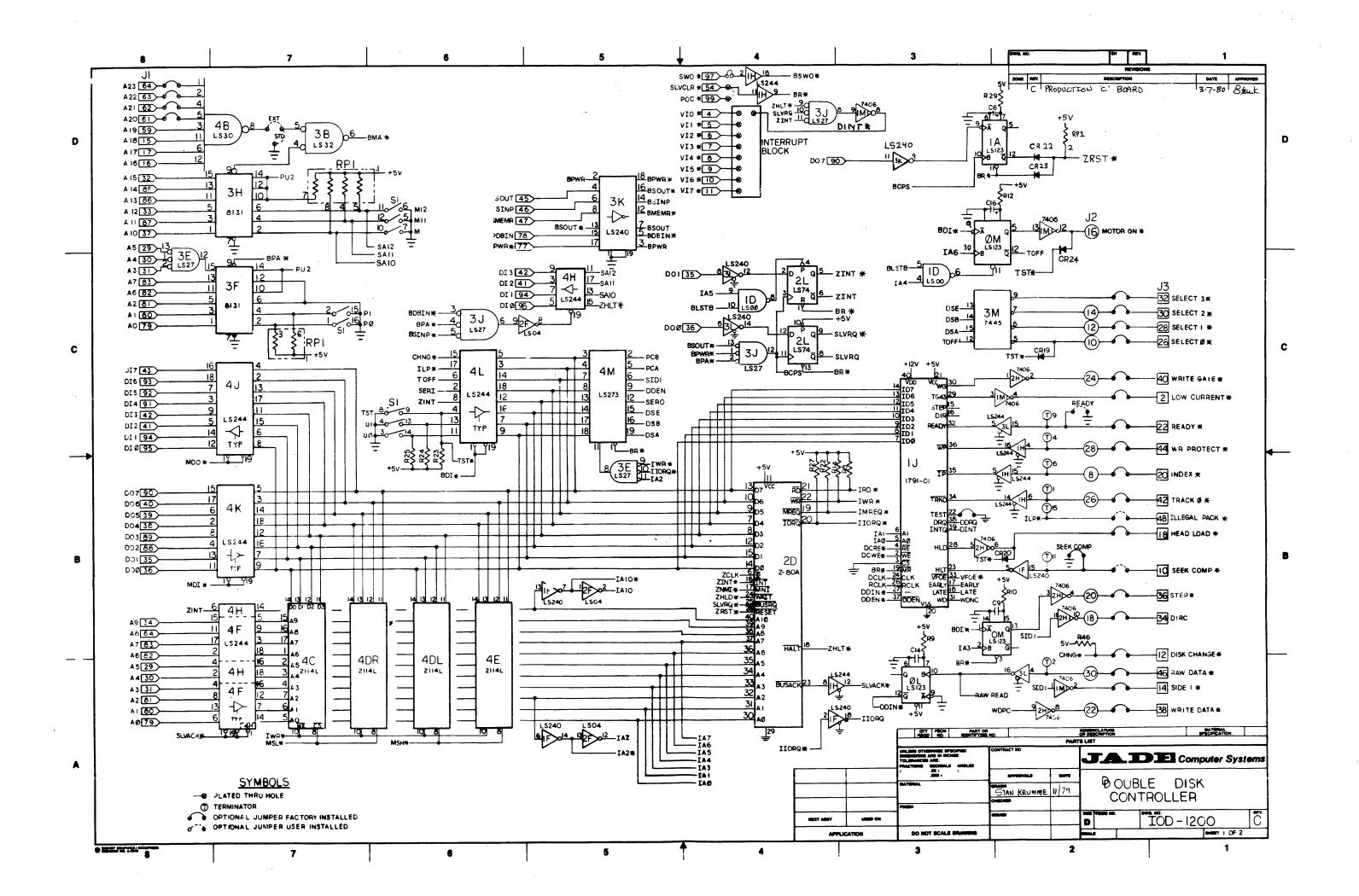

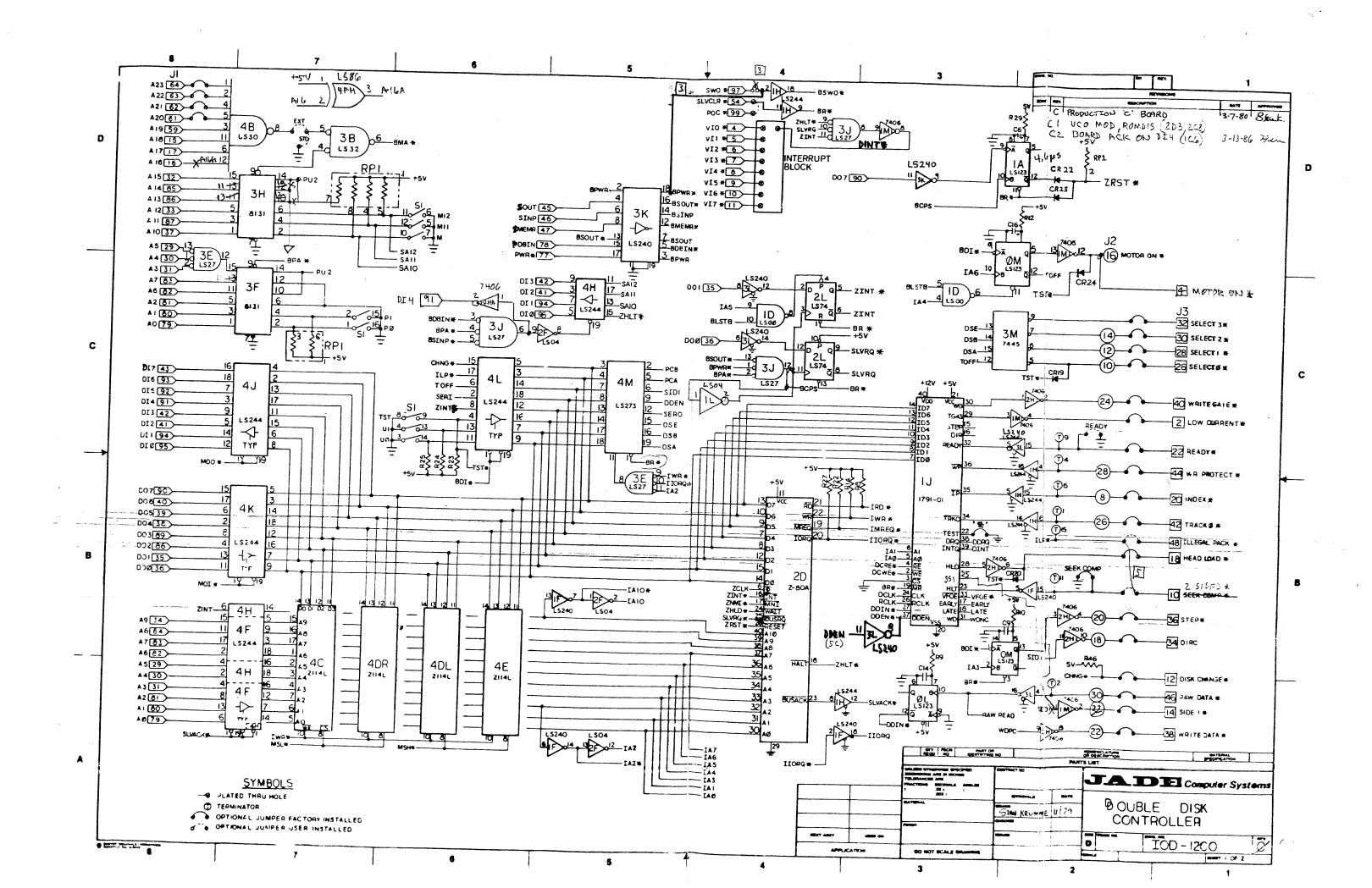

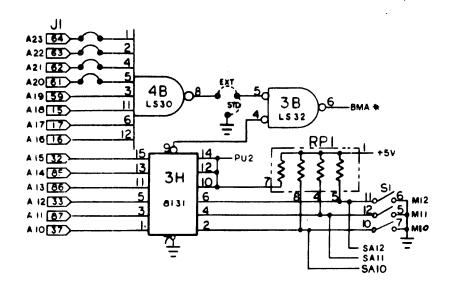

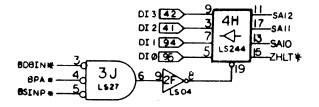

# 2.2 MEMORY ADDRESS DECODING

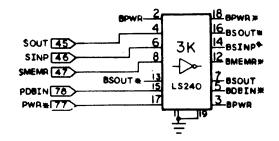

The S-100 bus address lines are constantly monitored by the Memory Address Detection circuit. See Figure 2-1. In the Standard address mode, ICs 3H and 3B implement detection of the selected 1K memory block. Switches M10, M11, and M12 are used to locate the selected memory block on any 1K boundry from E000 to FC00. Note: signals SA10, SA11, and SA12 indicate the corresponding address switch settings. See Table 2-1. For the Extended Address Mode, IC 4B must be installed and the Address Mode Block altered to the appropriate position. In this configuration, address decoding is provided for any 1K block in the upper 8K of the 24 bit address bus. In either mode, an address match is indicated by BMA\* (Bus - Memory Addressed) being asserted (low).

| SWITCH<br>M12                                                      | SWITCH<br>M11                                                                | SWITCH<br>M10                                           | SA12                       | SA11                            | SA10                            | ADDRESS RANGE<br>IN THE SYSTEM                                                                                         |

|--------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------|---------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Closed<br>Closed<br>Closed<br>Closed<br>Opened<br>Opened<br>Opened | Closed<br>Closed<br>Opened<br>Opened<br>Closed<br>Closed<br>Opened<br>Opened | Closed Opened Closed Closed Opened Closed Closed Closed | O<br>O<br>O<br>1<br>1<br>1 | O<br>O<br>1<br>1<br>O<br>O<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | E000 - E3FF<br>E400 - E7FF<br>E800 - EBFF<br>EC00 - EFFF<br>F00C - F3FF<br>F400 - F7FF<br>F800 - FBFF<br>★ FC00 - FFFF |

Table 2-1. Memory Address Selection

Figure 2-1. Memory Address Detection

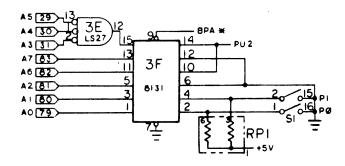

# 2.3 PORT ADDRESS DETECTION

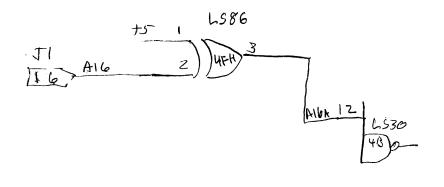

S-100 address lines AO thru A7 are constantly monitored by the Port Address Detection circuit. This circuit is composed of IC 3F and part of 3E. See figure 2-2. Switches "PO" and "P1" are used to vary the selected port address from 40 thru 43 hex. An address match is indicated by BPA\* (Bus - Port Addressed) being asserted.

Figure 2-2.

Port Address Detection

| SWITCH | SWITCH | ADDRESS |

|--------|--------|---------|

| P1     | PO     | PORT    |

| Close  | Close  | 40      |

| Close  | Cpen   | 41      |

| Open   | Close  | 42      |

| Open   | Open   | 43      |

Table 2-2.

Port Address Selection

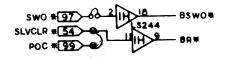

#### 2.4 BUS CONTROL SIGNALS

All Control Signals from the S100 bus are buffered by ICs 1H and 3K before internal use. These line recievers have schmitt trigger inputs typically offering 400 millivolts hysteresis. See Figure 2-3.

In some older mainframes SLVCLR\* is not implemented. For use in those systems POC\* (pin 99) can be connected to SLVCLR\* by a jumper (BRST\* to POC\*).

Figure 2-3. Control Signal Buffers

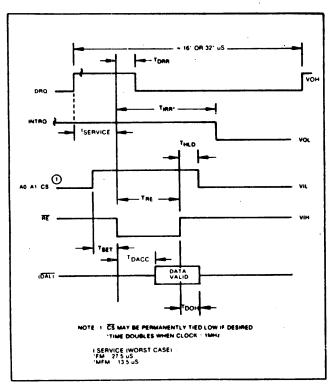

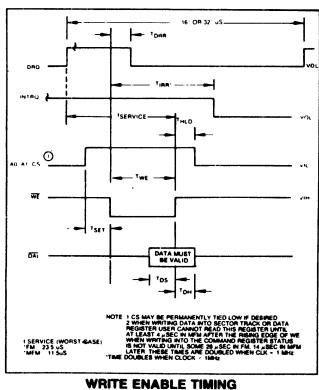

# 2.5 DISK PROCESSOR CONTROL PORT

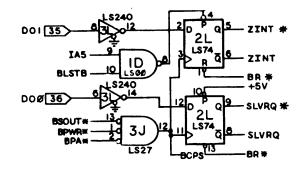

The Disk Processor Control Port is an S-100 output port which provides the host system with control of the on-board processor. The port is strobed by the occurance of sOUT, pWR\*, and a matching port address (BPA\*). The following functions are implemented.

- 1. Switch internal memory to and from the bus.

- 2. Issue an interrupt to the Z8OA processr

- 3. Reset the Z80A processor.

The board reset signal BR\* brings the port to the initial state where internal memory is switched into the S-100 bus. Refer to Figure 2-4 for circuit details.

SLVRQ is set by data bit 0. Asserting SLVRQ\* initiates the SLVRQ\* is memory switch process. applied to the Z8OA BUSRQ\* pin. When SLVRQ\* (BUSRQ\*) is asserted. Z80A tri-states its data. the control lines. The address, and SLVACK\* then asserts (PUSACK\*). the Z80A Refer to Assertion of TECHNICAL MANUAL. SLVACK\* enables the Memory Control circuit to respond to S-100 memory cycles.

Figure 2-4. Control Port

ZINT is set by data bit 1. ZINT(\*) serves a dual function. ZINT\* is the maskable interrupt request to the on-board Z8OA. Note, circuit implementation makes it possible for the on-board Z8OA to test and reset ZINT\* under software control. More on this later. ZINT also controls which 1K bank of internal memory is selected for bus access. When memory is switched to the S-100 bus, the on-board Z8OA has asserted SLVACK\* and will not respond to an interrupt. At this time ZINT is used as internal address bit 10.

ZRST\* is the reset line to the on-board Z8OA. It is an output of IC 1A, a one-shot, which is triggered by writing to this port while data bit 7 is asserted high.

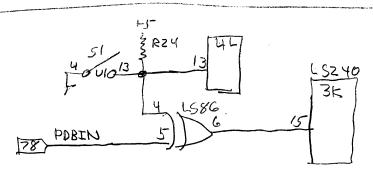

# 2.6 DISK PROCESSOR STATUS PORT

The Disk Processor Status Port is an S-100 input port which allows the host processor to examine the current state of the Disk Processor. The port responds to the occurence of pDBIN, sINP, and a matching port address (BPA\* asserted). The following states can be determined by reading this port.

- 1. On-board processor state (Run/Halt)

- 2. Address of the 1K memory window.

The address of the memory window is determined by reading the M10, M11, and M12 switch positions as indicated by signals SA10, SA11, and SA12. Table 2-1 shows the relation between signals SA10-SA12 and the selected window address. Processor Status Port

Figure 2-5.

Processor Status Port

The on-board processor state is indicated when reading ZHLT\*. This is the Z8OA halt flag. Reading a "O" on data bit  ${\bf O}$  indicates that the on-board processor has halted.

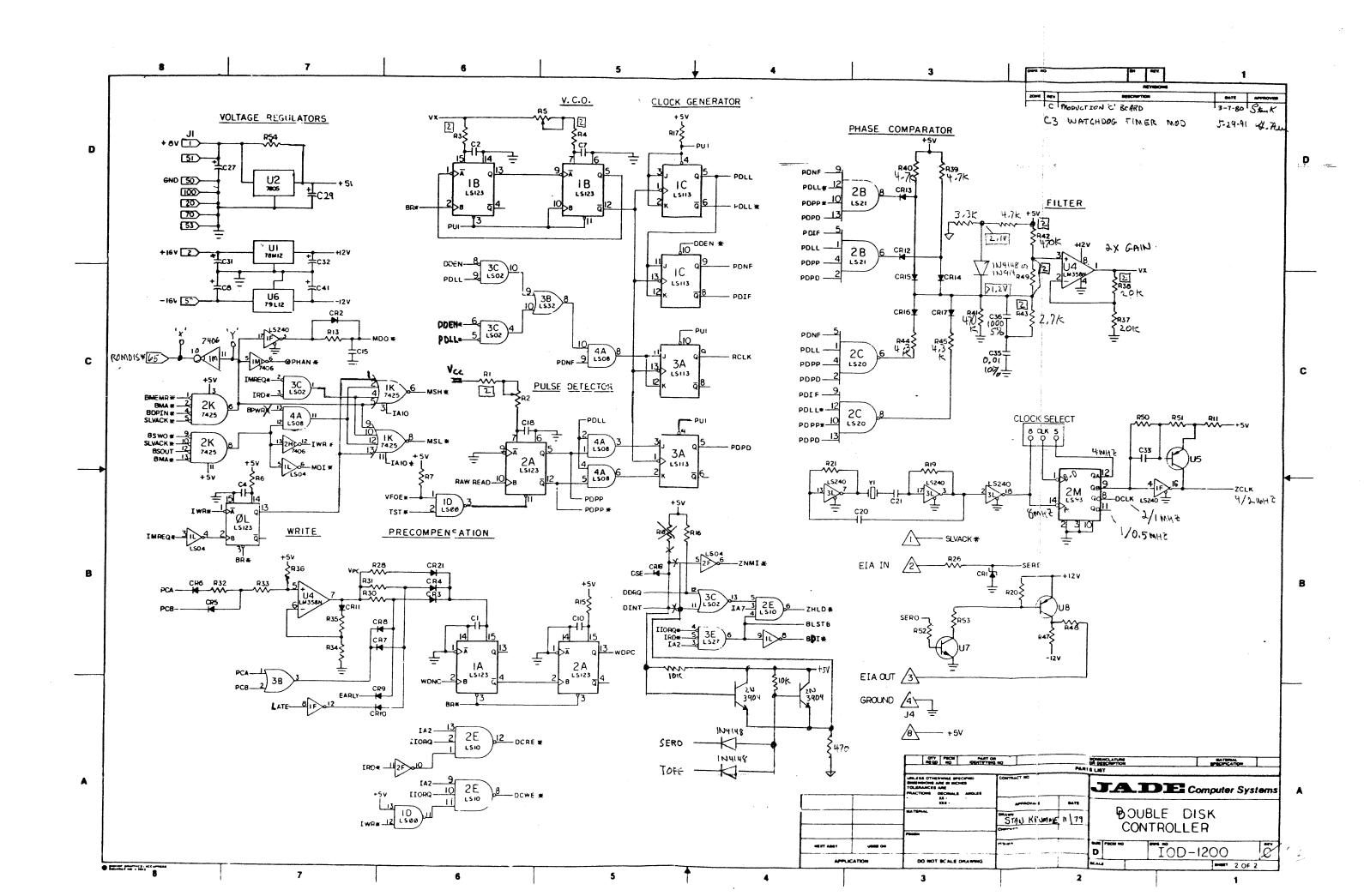

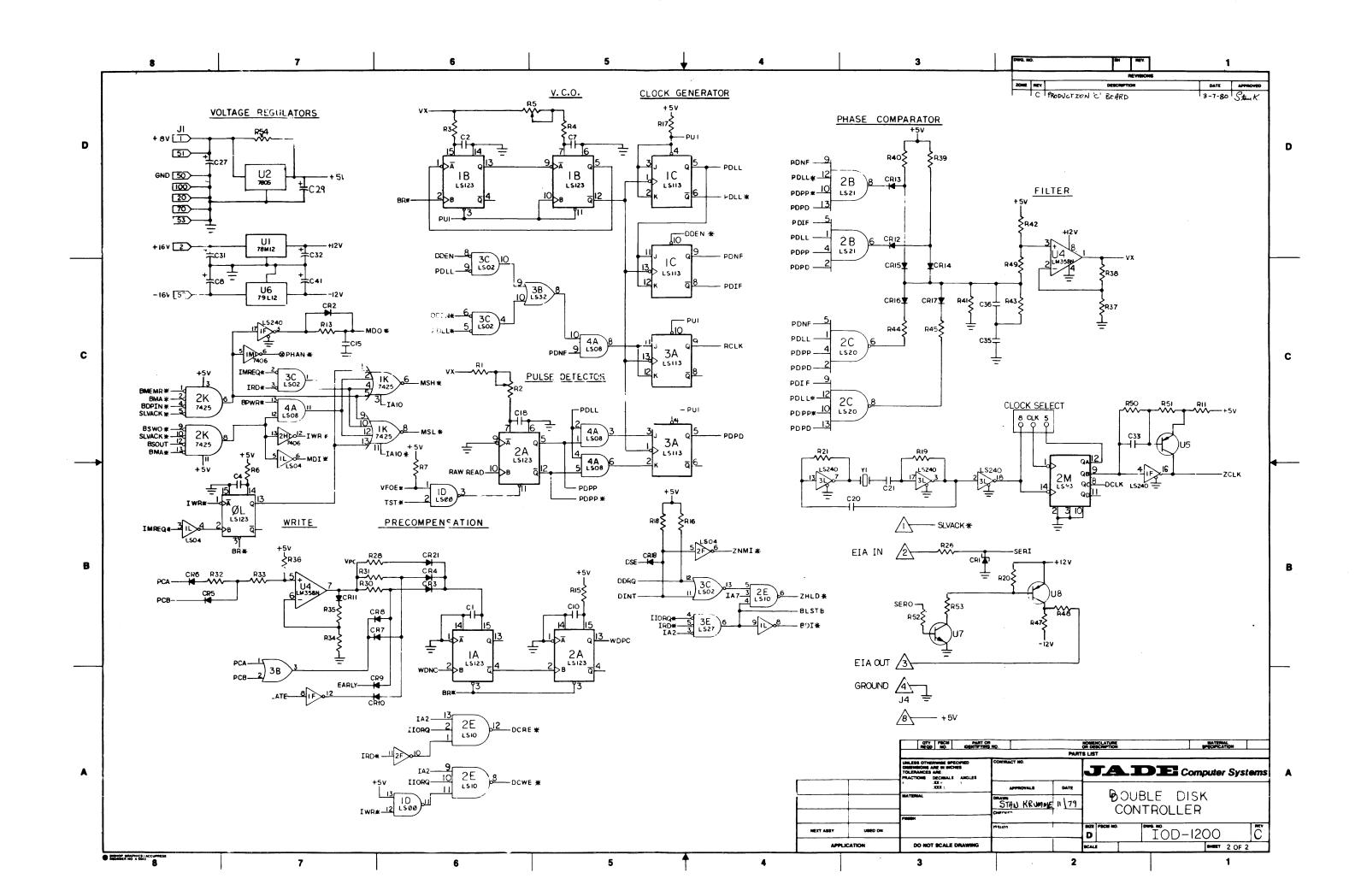

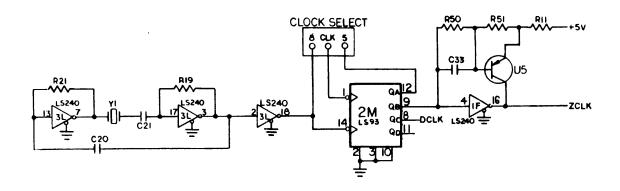

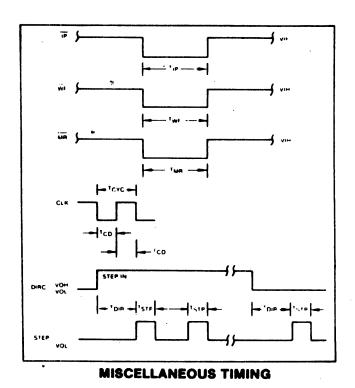

#### 2.7 CLOCK GENERATION

The clock signals for the Z8OA and FD 1791-01 are generated onboard by a crystal oscillator, divider and driver. See figure 2-6. The crystal is a fundamental type operating at 8.000 Mhz. oscillator is implemented with two sections of IC 3L. section is used to square the output of the oscillator. IC 2M used to divide the clock. The CLOCK SELECT JUMPER is set depending on the disk drive to be used. The FD 1791-01 requires a 2.000 clock for 8" drives and a 1.000 Mhz clock for the 5" drives. jumper provides for the selection of a additional divide by 2. 8" drives the Z80A is run at 4.000 Mhz. With 5" drives the Z80A runs at 2.000 Mhz to provide adequate port enable (RE\* and WE\*) timing for the FD 1791-01. A section of IC 1F and U-5 provide a MOS level clock driver for the Z8OA as recommended by Zilog.

Figure 2-6. Clock Circuit

#### 2.8 PROCESSOR

The on-board processor function is implemented with the Z8OA. It was selected because of execution speed and compatability with TTL logic families. The processor uses the on-board 2K static memory for program, stack, parameters, and for buffering single/multiple sectors of data. Because the 5 upper address bits are not decoded, this 2K block appears 32 times in the Z8OA 64K address range. This allows internal programs to be assembled on any 2K boundary. Note, the address selected for the memory window has no effect on the on-board processor or the on-board software.

The host system communicates with the on-board processor thru the remory window. During a system boot, the control program must be loaded thru the memory window before the on-board processor can operate properly. It is entirely possible for the initial control program to be a small bootstrap which then loads a larger control program from disk. For reading and writing disk sectors, the host system must block move sector data through the memory window.

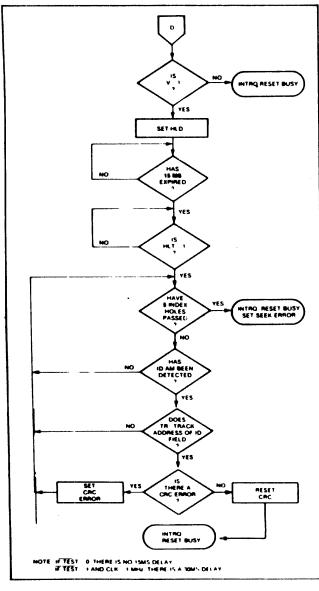

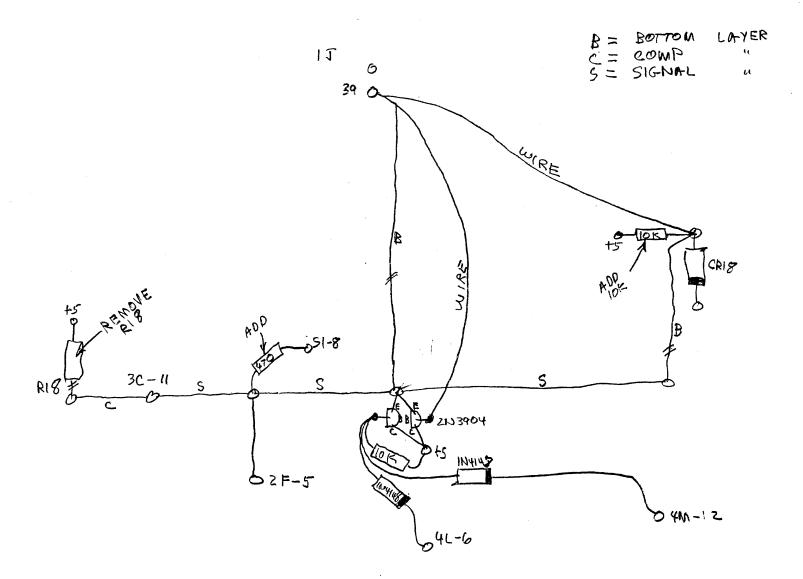

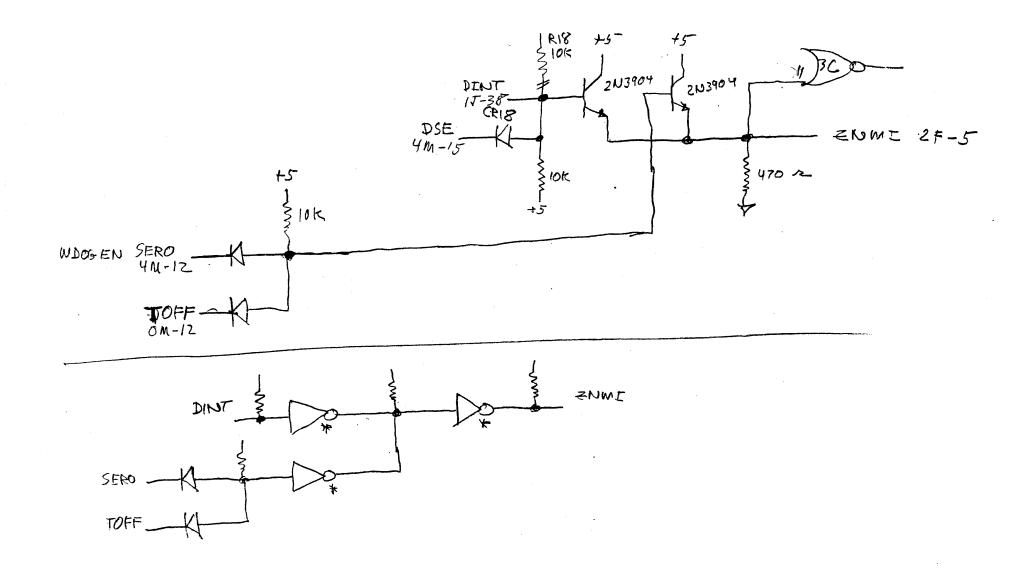

Both Z80A interrupts are implemented. The host system issues the maskable interrupt by executing an OUTPUT instruction to the Disk Processor Control Port. The FD 1791-01 issues an interrupt upon command completion. The Z80A NMI\* pin is used for interrupts from the 1791-01. This interrupt is clamped by CR18 when DSE (Drive Select Enable) is low.

# 2.9 DISK CONTROLLER

The Western Digital 1791-01 is used for all data transfers to and from disk. This device is addressed as four I/O ports from the on-board processor. The user should refer to FD 1791-01 specifications for a detailed description of this part. Access to the FD 1791-01 Status Port allows reading the disk interface signals. These are WRITE PROTECT\*, READY\*, INDEX\*, TRACK-ZERO\*, and SFEK-COMPLETE\*.

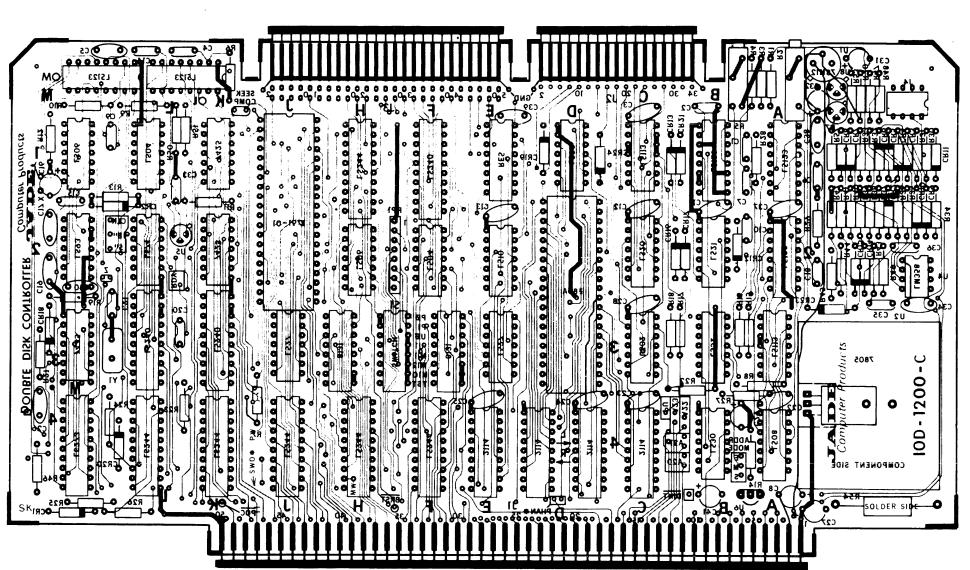

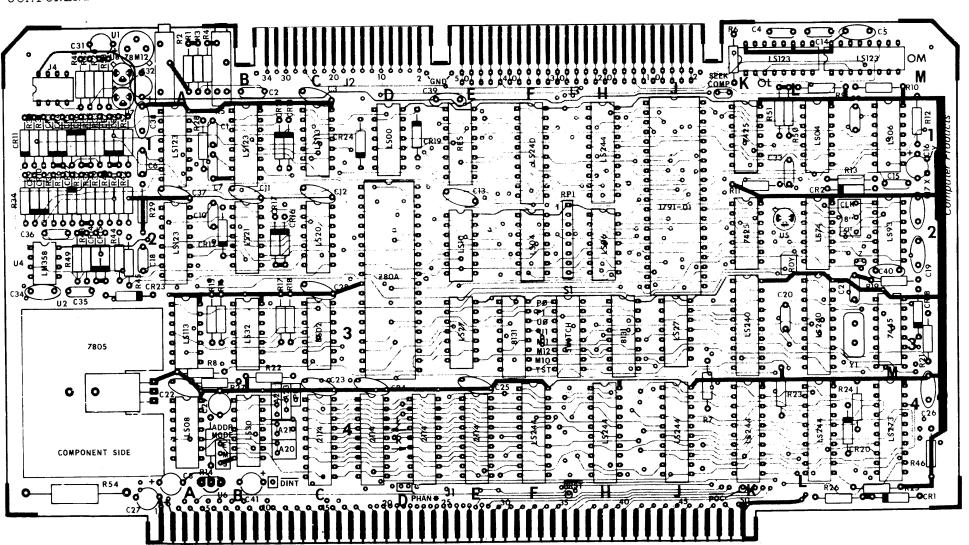

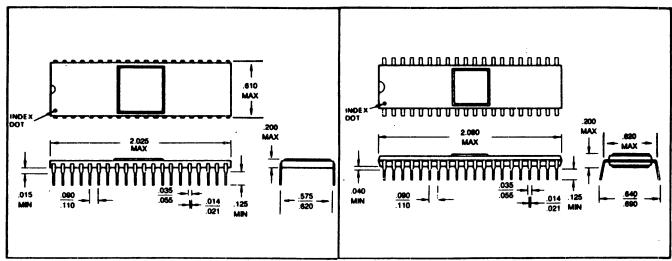

#### 2.10 DISK INTERFACE

Disk Interface is provided by two gold-plated card edges at the top of the P.C. board. The 50 pin (J-3) card edge is intended for the 8" disk drives. The mating connector is the same type as is used to connect the other side of the ribbon cable to the disk drive (with most drives). All even numbered contacts (component side) are connected to internal circuitry thru a double set of plate-thruholes. By cutting the connecting links and adding jumpers, the signal assignments for each contact can be altered. The 34 pin card edge (J-2) is intended for 5" disk drives. All unassigned contacts provide a plate-thru-hole for alteration. Additional signals can be assigned to this connector by jumping from J-3 to J-2. On connectors J-2 and J-3 all odd-numbered contacts are grounded.

# 2.11 INTERNAL I/O ADDRESSES

There are seven I/O ports available to the on-board processor. These internal ports are not accessable from the host system. They are used for control signals, status information, and data paths. They are decoded using address bits AO thru A2.

| ADDR                                   | TYPE                                  | DESCRIPTION                                                                                                                                             |

|----------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00<br>00<br>04<br>04<br>05<br>06<br>07 | Input Output Input Output I/O I/O I/O | Board Level Status Board Level Command Disk Controller Status Disk Controller Command Disk Controller Track Disk Controller Sector Disk Controller Data |

Table 2-3. Internal I/O Ports

Address bits A3 thru A7 have no effect on I/O operations except when accessing the Board Level Status Port. These upper address bits individually trigger on-board events when asserted high during an INPUT operation from this port. A list is provided in Table 2-4. For a detailed description refer to the appropriate section.

| BIT | FUNCTION             | SECTION |

|-----|----------------------|---------|

| A3  | Issue Step Pulse     | 2.15    |

| A4  | Clear Timer          | 2.14    |

| A5  | Reset Host Interrupt | 2.5     |

| A6  | Initiate Timer       | 2.14    |

| A7  | Wait State Request   | 2.16    |

Table 2-4. Address Bit Assignments

# 2.12 BOARD LEVEL STATUS PORT

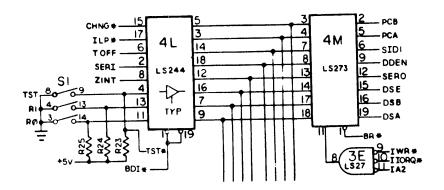

The Board Level Status Port is a parallel input port to the on-board Z8OA. It provides the processor with access to board signals that cannot be read from the FD 1791-01. These signals are listed and described in Table 2-5. See Figure 2-7 for circuit diagram.

| DATA<br>BIT                          | SIGNAL<br>NAME                       | DESCRIPTION                                                                                                                                             |

|--------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | UO U1 TST* ZINT SERI TOFF ILP* CHNG* | User O switch setting User 1 switch setting Test mode Interrupt req from host EIA level input bit Timer off Illegal pack inserted Disk has been changed |

Table 2-5. Board Level Status Bits

Figure 2-7. Board Level Ports

#### 2.13 BOARD LEVEL COMMAND PORT

The Board Level Command Port is a parallel output port of the on-board processor. It is used to select various parameters as listed in Table 2-6. See Figure 2-7 for circuit details.

| DATA<br>BIT                          | SIGNAL<br>NAME                     | DESCRIPTION                                                                                                                                                                         |

|--------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | DSA DSE DSE SERO DDEN SID1 PCA PCB | Drive select bit A (2**0) Drive select bit B (2**1) Drive select enable EIA signal output control Double density enable Side and direction select Precomp select A Precomp select B |

Table 2-6. Command Port Bits

The signals DSA and DSB are used to determine which drive is selected. DSE must be asserted for drive selection to take place. DSE is also used to enable the on-board processor to accept an interrupt from the 1791-O1. See Table 2-7 for drive selection.

| DSE | DSB | DSA | DRIVE |

|-----|-----|-----|-------|

| 0   | Х   | X   | NONE  |

| 1   | 0   | 0   | 0     |

| 1   | 0   | 1   | 1 1   |

| 1   | 1   | 0   | 2     |

| 1   | 1   | 1   | 3     |

Double Density operation is enabled when DDEN is set high. A low SERO signal corresponds with a negative EIA output.

Table 2-7. Drive Selection

SID1 serves a dual function. When using double-sided drives and performing any type of read or write operation, this signal selects which side of the diskette is used. A low SID1 selects the same side as used on single-sided drives. When stepping operations are being performed, SID1 functions as the direction select, a low SID1 will cause stepping operations to move the head toward track O (most drives).

Precompensation is controlled by signals PCA and PCB. These two signls allow precompensation to be enabled and at three different levels of intensity. Table 2-8 lists this function.

| PCB | PCA | PRECOMPENSATION |

|-----|-----|-----------------|

| 0   | 0   | OFF             |

| 0   | 1   | 200 ns.         |

| 1   | 0   | 160 ns.         |

| 1   | 1   | 120 ns.         |

Table 2-8. Write Precompensation

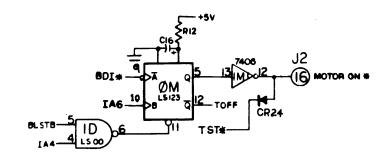

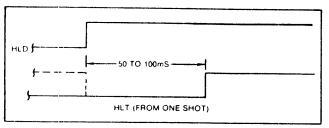

#### 2.14 ON-BOARD TIMER

The On-Board Timer provides both a motor control for 5" drives and a means for deselecting any drive if not used for a given period of time. The 1791-01 will unload the head of a drive if not used in 15 revolutions, in some drives the stepperwill still consume motor The timer is under power. complete control of the onboard processor. It can be set, reset, and examined appropriate I/O operations. See figure 2-8.

Figure 2-8. On-board Timer

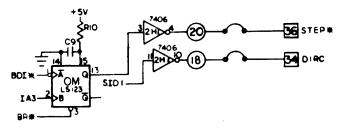

#### 2.15 STEP CONTROL

The STEP CONTROL circuit provides more flexible control of the step function than the 1791-01. Step pulses are issued under control of the on-board processor. The interval between step pulses are timed by on-board software and can be resolved to better than 0.10 milliseconds. The step pulse width has been set at 3 microseconds. This appears satisfactory for most disk drives. If needed, this value can be altered by chosing a new value for C9 or R10. See Figure 2-9.

Figure 2-9. Step and Direction

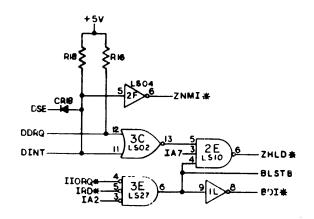

#### 2.16 WAIT STATE GENERATOR

The Wait State Generator is used to synchronize the on-board processor to the Disk Controller when data is being transferred between the Double-D and a disk wait state The generated during the execution of an input instruction from the Board Level Status Port while address bit A7 is held high. wait-state is held until the FD 1791-01 issues either Data а Request (DDRQ) or an interrupt (DINT). For circuit details refer to figure 2-10.

Figure 2-10. Wait States

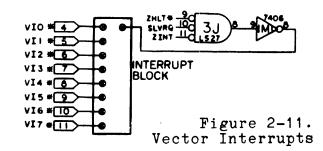

# 2.17 VECTOR INTERRUPT GENERATOR

The Vector Interrupt Generator may optionally be used to issue an interrupt to the host processor system. The interrupt is issued

on one of VIO\* thru VI7\*, selectable the on-board jumper. when HALT executes the The interrupt request instruction. terminated when the host switches processor either the Double-D memory into the S100 bus issues an interrupt to the figure 2-11 Double-D. See for circuit details.

# 2.18 EIA LEVEL INTERFACE

The EIA LEVEL INTERFACE provides the level conversions to and from TTL. These EIA level lines are made available at connector J4, an 8-pin DIP socket located close to IC 1A.

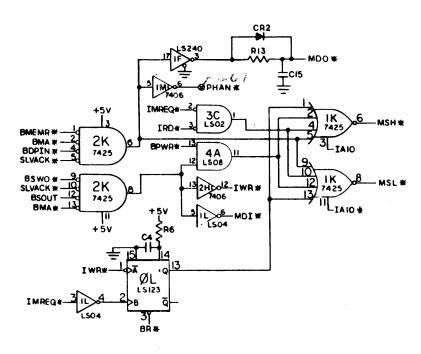

#### 2.19 MEMORY CONTROL

The Memory Control Circuit is used to operate the on-board memory. When SLVACK\* is high, the on-board Z8OA is performing memory read and write operations. When the internal memory is present in the S100 bus (SLVACK\* low), the host processor may perform read and write operations. Refer to Figure 2-12 for circuit diagram.

Figure 2-12. Memory Control Circuit

S100 bus requests for read and write operations are decoded by IC 2K pin 6, when high, indicates a memory read is taking IC 1M pin 6 can be used to provide PHANTOM\* to the S100 bus to avoid a bus driver conflict when using memory cards which overlap the selected memory window address. Many 64k dynamic RAMs cannot disable 1K segments. IC 1F pin 3 is used to enable the data out IC 4J. R13 and C15 provide approximately 120 ns. turn-on driver. allowing PHANTOM\* enough time to turn any other memory off. delay, pin 8 indicates a bus write is about to take place. pulls IWR\* down indicating to the 2114's that this is a write signal MDI\* is also asserted, which enables the data-in buffer (IC cycle. When pWR\* is asserted IC 4A pin 11 goes high. Either pin 6 or 4K). 8 of IC 1K then enables a bank of 2114. The memory bank selected is determined by IA10 and IA10\* applied to pins 3 and 11 of IC 1K.

IC 3C detects the on-board processor read cycle. IC 1K again provides the bank enable signal. An on-board processor write cycle is detected by one-shot OL (IWR\* and IMREQ\*). The output OL pin 13 is used to strobe the appropriate bank enable (through IC 1K). During this strobe IWR\* is held low, indicating a write cycle for the 2114s.

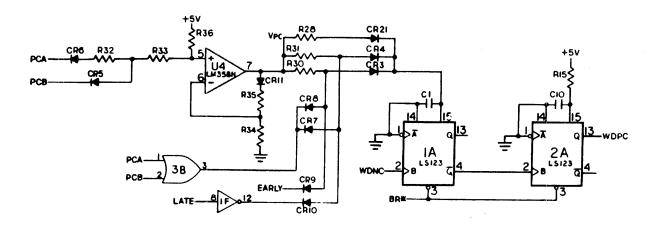

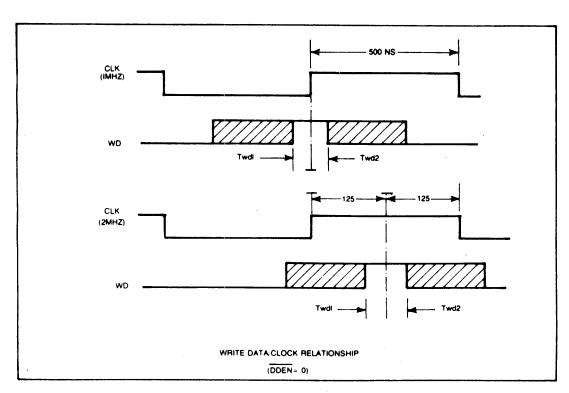

#### 2.20 WRITE PRECOMPENSATION

The Write Precompensation circuit is used advance or retard the individual write data pulses. This is done to correct for a distortion called BIT SHIFT. This bit shift is observed when reading a data stream from a diskette. Data pulses which are recorded close together, when read back, appear to spread apart. This circuit shifts the pulses being recorded in the direction opposite of the direction of this bit shift. The 1791-01 provides two signals, EARLY and LATE, which are used to advance or retard the individual data pulses. See Figure 2-13 for circuit diagram.

Figure 2-13. Write Precompensation Circuit

Signals PCA and PCB are used to produce three different voltage levels at U4 pin 5. This level is amplified by U4 and then used as the pull-up voltage source for one-shot 1A. R30 and R31 are individually switched by EARLY and LATE to vary the one-shot period. R28 is always in circuit. It determines the longest period. When neither EARLY nor LATE are applied, R28 and R31 in parallel determine the period. With EARLY asserted, R30 is included in parallel to provide the shortest period. The amount of precompensation applied is the difference between the normal period and either the short period or the long period. By selecting the voltage applied to the pull-up resistors, the amount of precompensation is varied. IC 3B is used to inhibit precompensation when PCA and PCB are both low.

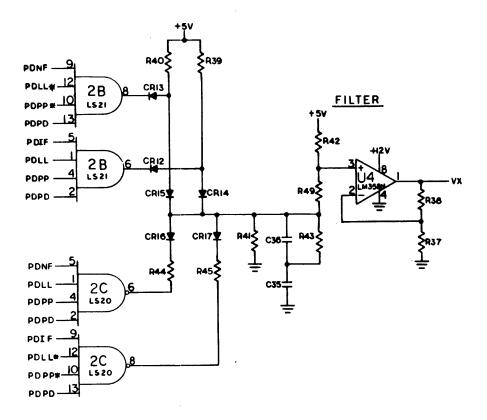

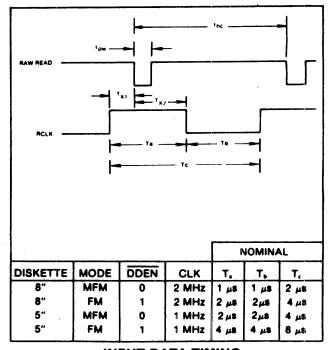

# 2.21 PHASE-LOCKED LOOP

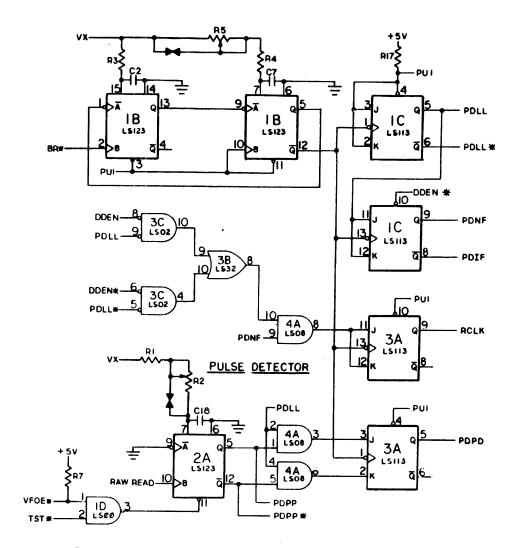

A Phased-Locked Loop is used to generate the read clock as required by the 1791-01 for data seperation. This method was selected as it provides maximum immunity to disk speed variation and provides enhanced data recovery margins in both single and double density. The loop is constructed of both digital and analog circuitry.

Figure 2-14. Phase Detector and Filter

The Voltage Controlled Oscillator (VCO) is a 74LS123 with both sections configured to trigger each other. The control voltage is applied to the resistors R3 and R4/5. An increase in voltage corresponds to an increase in frequency. IC 2A, a section of a 74LS123, also uses VX to provide this one-shot with a period which proportionally tracks the period of the VCO. See Figures 2-14 and 2-15.

A set of timing signals are generated from the VCO which are used by the Digital Phase Detector. IC's 1C and 3A are 74LS113s and are used to generate these signals. They are all clocked simultaneously to eliminated any skew in the generated signals.

Figure 2-15. VCO and Timing Generator

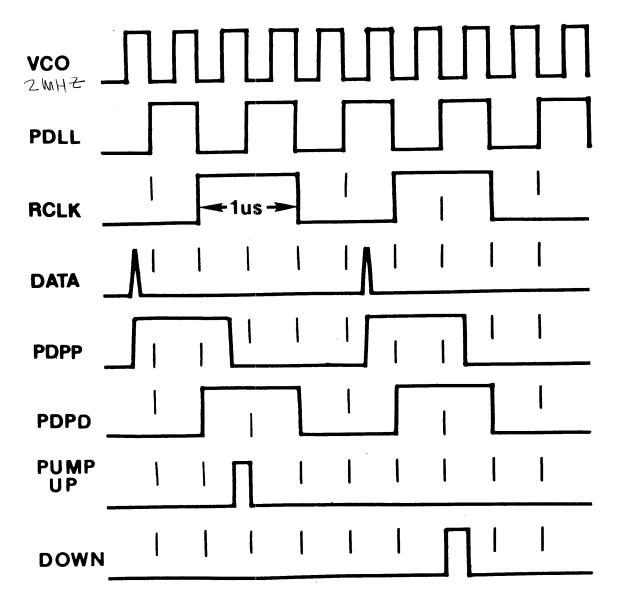

In the following discussion 8 inch operation is assumed (With 5 inch operation all timings are doubled). In double density (MFM), the incoming data stream contains bits which are separated by 2, 3, or 4 microseconds (wishful thinking!). Read Clock makes a transition every 1 us. The Phase-Locked Loop adjusts the VCO such that each data pulse is centered in the middle of a half-cycle of Read Clock (Window). More precisely, due to bit-shift, very few individual data pulses are centered. They tend to occur either a little early or late but the center of the spread in these pulses is centered in the window.

The signal PDLL (Phase Detector Lead/Lag) divides the window into early and late sections. PDNF (Phase Detector Normal Frame) is always true in double density. Its complement PDIF (Phase Detector Illegal Frame) is used in single density only. In single density, when the data pulses are separated by either 2 or 4 microseconds, every other 1 us frame of the phase detector is an Illegal Frame for single density operation. RCLK (Read Clock) is generated for both FM and MFM. Sections of ICs 3C, 3B, and 4A provide this switching

Figure 2-16. 8 Inch MFM Operation

logic. PDPD (Phase Detector Pulse Detected) indicates that during the last 1 us frame a data pulse was detected. This signal is maintained during the entire frame. PDPP (Phase Detector Pulse Present) is the output of a one-shot with a period of 1 us. It is triggered by an incoming data pulse. The falling edge of this signal occurs at the same place in the next frame as the data pulse occured that triggered the signal in the preceeding frame.

All these signals are used by the Phase Comparator which adjusts VX. The comparator provides Pump Up and Pump Down signals, where the period of the pump pulse is the same as the deviation of the incoming data pulse from the window's center. See Figure 2-15. This figure shows the internal phase signals, an early and late data pulse, and the corresponding pump pulses.

SECTION 3 CONSTRUCTION

# SECTION 3

#### BOARD ASSEMBLY

#### 3.1 INTRODUCTION

If you have purchased the JADE DOUBLE D Disk Controller as a kit, we strongly urge you to read this section in its entirety before attempting to assemble the board. This board is intended for those people who have had some prior experience with digital electronics and circuit board assembly. If you do not, it is highly recommended that you find an experienced person to help you with the assembly of this board.

Although there are about as many ways of assembling a board as the number of components factorial, if you will follow the assembly instructions STEP-BY-STEP, construction will be easier for you and much more pleasurable for both of us. It will help to mark the boxes as you complete each step.

Make sure you have the tools you will need to assemble this kit. For this board you will need the following: a soldering iron (25 watts maximum), ROSIN CORE solder (preferably 63/37), diagonal cutters, a small magnifying glass, a screwdriver, a lead former or a pair of needle-nose pliers, and a small tube of heat sink compound.

# 3.2 ASSEMBLY

- [] Check the parts recieved againsts the parts list. Take special care to correctly identify lookalike parts; resistors, capacitors, and diodes. If anything is missing from your kit, please call Jade's Customer Service Department and report the shortage immediately.

- USE EYE PROTECTION WHILE SOLDERING OR CUTTING WIRE

- [ ] When inserting IC sockets be sure to observe the pin 1 notch for proper alignment.

- [] Install 8-pin sockets at U4 and J4. Do not solder yet.

- [ ] Install 14-pin sockets at 1C, 1D, 1K, 1L, 1M, 2B, 2C, 2E, 2F, 2H, 2K, 2L, 2M, 3A, 3B, 3C, 3E, 3J, 4A, and 4B. Do not solder yet.

- [] Install 16-pin sockets at OL, OM, 1A, 1B, 1E, 2A, 3F, 3H, and 3M. Do not solder yet.

SECTION 3 CONSTRUCTION

[ ] Install 18-pin sockets at 4C, 4DL, 4DR, and 4E. Do not solder yet.

- [] Install 20-pin sockets at 1F, 1H, 3K, 3L, 4F, 4H, 4J, 4K, 4L, and 4M. Do not solder yet.

- [ ] Install 40-pin sockets at 1J and 2D. Do not solder yet.

- Place the flat styrofoam cover you recieved with your kit box firmly against the component side of the board. Turn the board over, holding the flat styrofoam piece tightly against the board. Press the board down, forcing the socktes into the styrofoam. Now solder the alternating corner pins of the IC sockets to hold them in place temorarily (pins 8 and 16 on a 16-pin socket, for instance).

- [ ] Turn the board over and very carefully inspect it to determine that all the IC sockets are down flat against the board. If you find any that are not down flat, melt the solder joints of the IC socket while pressing it down against the board.

- [ ] Now that all IC sockets are down firmly on the board, turn the board solder side up. Make sure all IC socket pins are sticking through the holes. IC sockets are very hard to remove after they are completely soldered in. Remove any socket not installed properly, straighten the pin and re-insert.

- [ ] Solder all IC pins.

NOTE: For the following steps the closest IC socket location for each part will be enclosed [IC#].

- [ ] Solder in the 1N748-750 diode at CR1 (4M).

- [ ] Install nine 1N270 diodes at the following locations:

```

[ ] CR2 (2L) [ ] CR5 (U4) [ ] CR6 (U4) [ ] CR7 (1A) [ ] CR8 (1A) [ ] CR9 (U4) [ ] CR23 (2B)

```

[ ] Install fourteen 1N914B diodes at the following locations:

```

CR3

(U4)

CR4

(U4)

CR11

] CR14

] CR17

CR12

(2B)

CR13

(1B)

CR14

U4)

] CR16 (2B)

1 CR15

(U4)

(2B)

(3M)

CR19 (1D)

] CR20 (4L)

CR18

1 CR24 (1D)

] CR21 (1B)

```

| [ | ]   | Install the 3.3K ohm 8-pin SIP resistor at RP1 (2F). Be careful to align pin 1.                                                                                         |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ | ]   | Install the 10K ohm trimmers at the following locations:                                                                                                                |

|   |     | [ ] R2 (TA) [ ] R5 (1B)                                                                                                                                                 |

| [ | )   | Be VERY CAREFUL in reading the resistor color codes as there are many different values used in this kit. If needed, use an ohm meter!                                   |

| [ | ]   | Install the 1.0K resistors (Brown-Black-Red) at the following locations:                                                                                                |

|   |     | [ ] R17 (3B) [ ] R19 (2M) [ ] R21 (3M)                                                                                                                                  |

| [ | ]   | Install the 4.7K resistors (Yellow-Purple-Red) at the following locations:                                                                                              |

|   |     | [ ] R8 (3A)       [ ] R14 (4A)       [ ] R22 (3B)         [ ] R23 (4K)       [ ] R24 (4L)       [ ] R25 (4M)         [ ] R27 (3A)       [ ] R39 (2A)       [ ] R40 (2A) |

| [ | ]   | Install four 10K resistors (Brown-Black-Orange) at the following locations:                                                                                             |

|   |     | [ ] R7 (4J) [ ] R16 (3B) [ ] R18 (3C) [ ] R36 (U4)                                                                                                                      |

| [ | j   | Install the 7.5K resistors (Purple-Green-Red) at the following locations:                                                                                               |

|   |     | [ ] R9 (OL) [ ] R15 (3A)                                                                                                                                                |

| [ | ]   | Install the 27K resistors (Red-Purple-Orange) at the following locations:                                                                                               |

|   |     | [ ] R2O (1A) [ ] R32 (1A) [ ] R38 (2A)                                                                                                                                  |

| [ | ]   | Install the 51K resistors (Green-Brown-Orange) at the following locations:                                                                                              |

|   |     | [ ] R29 (2A) [ ] R34 (U4)                                                                                                                                               |

| - | [ ] | Install the 30K resistors (Orange-Black-Orange) at the following locations:                                                                                             |

|   |     | [ ] R10 (OM) [ ] R35 (2A)                                                                                                                                               |

|   | [ ] | Install the 4.3K resistors (Yellow-Orange-Red) at the following locations:                                                                                              |

|   |     | [ ] R44 (2A) [ ] R45 (2A)                                                                                                                                               |

- [ ] Install the 5.1K resistors (Green-Brown-Red) at the following locations:

- [ ] R26 (4L) [ ] R52 (1A)

- [ ] Install the 33K resistor (Orange-Orange-Orange) at R28 (1A-1B).

- [ ] Install the 13K resistor (Brown-Orange-Orange) at R3O (1A).

- [ ] Install the 22 ohm resistor (Red-Red-Black) at R11 (1K-2K).

- [ ] Install the 240K resisttor (Red-Yellow-Yellow) at R12 (1M).

- [ ] Install the 300 ohm resistor (Orange-Black-Brown) at R13 (1L-2M).

- [ ] Install the 22K resistor (Red-Red-Orange) at R33 (1A).

- [ ] Install the 47K resistor (Yellow-Purple-Orange) at R31 (1A)

- [ ] Install the 20K resistor (Red-Black-Orange) at R37 (2A).

- [ ] Install the 470K resistor (Yellow-Purple-Yellow) at R41 (2A).

- Install the 390K resistor (Orange-White-Yellow) at R42 (2A).

- [ ] Install the 2.4K resistor (Red-Yellow-Red) at R43 (2A).

- [ ] Install the 150 ohm resistor (Brown-Green-Brown) at R46 (4M).

- [ ] Install the 2.0K resistor (Red-Black-Red) at R47 (U1).

- [ ] Install the 120 Ohm resistor (Brown-Red-Brown) at R48 (U1).

- [ ] Install the 82K resistor (Grey-Red-Orange) at R49. (2A).

- [] Install the 220 ohm resistor (Red-Red-Brown) at R51 (1K-1L).

- [ ] Install the 2.7K resistor (Red-Purple-Red) at R53 (U1),

- [] Install the 15 ohm 3 watt resistor (Brown-Green-Black at R54 (U2). Leave a 3/16" gap between the resistor and the PCB.

- [ ] Install the 1.2K ohm resistor (Brown-Red-Red) at R50 (1L).

- [ ] Install the 0.1 uf capacitors (104) at the following locations:

```

C11

C5 (OM)

C3 (1C)

C19

C13 (1E-2E)

C17

(2M)

C12

(1C)

C26

(4M)

C22

3A-4A)

(3D-4D)

C25

(3E)

C24

C23

(3C-4C)

C37

(1A)

C34

(U4)

(2C-3C)

C28

7 C40

C38 (1A)

```

- [] Install the 25 pf mica capacitors at the following locations:

- $\begin{bmatrix} \ \ \ \ \ \end{bmatrix} \begin{array}{c} C2 & (1B) \\ C10 & (2A-2B) \end{array} \quad \begin{bmatrix} \ \ \ \ \ \end{bmatrix} \begin{array}{c} C4 & (OL) \\ C14 & (OL-OM) \end{array} \quad \begin{bmatrix} \ \ \ \ \ \end{bmatrix} \begin{array}{c} C7 & (1A) \\ \end{array}$

- [] Install the 200 pf mica capacitors at the following locations:

- [ ] C6 (1A) [ ] C9 (1L-1M) [ ] C15 (1M) [ ] C18 (2A)

- [] Install the 6.8 uf 35 volt tantalum capacitors at the following locations. Observe polarity.

- [ ] C8 (4A) [ ] C31 (U1)

- [ ] Install the 10 uf 10 volt (106) tantalum capacitors at C29 (4A-4B). Observe polarity.

- [ ] Install the 4.7 uf 25 volt tantalum capacitors at the following locations. Observe polarity.

- [ ] C32 (U1) [ ] C41 (4B)

- [ ] Install the 10 pf mica capacitor at C1 (1A-1B).

- [] Install the 47 uf 6.3 volt tantalum capacitor at C16 (1M). Observe polarity.

- [ ] Install 0.022 uf (223) ceramic capacitor at C20 (3K-3L).

- [ ] Install the 100 pf mica capacitor at C21 (3L-3M).

Install the 22 uf 25 volt tantalum capacitor C27 (U3). Observe polarity. Install the 33 pf mica capacitor at C33 (1K-1L). Install the 0.01 uf ceramic capacitor at C35 (U4).Install the 1000 pf mica capacitor at C36 (U4). Install the 78M12 regulator at U1 (1A). Use the TO-5 mounting spacer. Install the 7805 regulator at U2 (3A-4A) using the heat sink and the #6 hardware. Use the needle-nose pliers to bend the 7805 leads before mounting it. Mount the regulator on the heat sink first, then solder. Install the 2N2907A transistors at U5 (2K-2L) and U8 (U1). Use two T0-18 spacers at this time. Install the 2N2222A transistor at U7 (U1). Use a TO-18 spacer when mounting. Install the 79L12 regulator at U6 (4B). part as shown in silkscreen. Install the 8.000 Mhz xtal at Y1 (3L). [ ] Install switch at S1 (3F-3H). Insert the DOUBLE D controller card into an S100 mainframe. Turn on the power switch an check the following voltages. U2 has +5 volt output. U1 has +12 volt output. U6 has -12 volt output. THE FOLLOWING STEPS ARE FOR 8" DRIVES. Install a 10K resistor (Brown-Black-Orange) at R1 (1A). Install a 18K resistor (Brown-Grey-Orange) at R3 (1A). Install a 15K resistor (Brown-Green-Orange) at R4 (1A). Install a 6.2K resistor (Blue-Red-Red) at R6 (OL).  $\begin{bmatrix} 1 \end{bmatrix}$ Install a jumper wire from "CLK" to "8" in the CLOCK SELECT BLOCK near ICs 2L-2M.

| [ | ] | THE FOLLOWING STEPS ARE FOR 5" DRIVES.                                                                                                 |

|---|---|----------------------------------------------------------------------------------------------------------------------------------------|

|   |   | [ ] Install a 24K resistor (Red-Yellow-Orange)                                                                                         |

|   |   | at R1 (1A).  [ ] Install a 39K resistor (Orange-White-Orange)                                                                          |

|   |   | at R3 (1A). [ ] Install a 36K resistor (Orange-Blue-Orange)                                                                            |

|   |   | at R4 (1A). [ ] Install an 8.2K resistor (Grey-Red-Orange)                                                                             |

|   |   | at R6 (OL).  [ ] Install a jumper wire from "CLK" to "5" in the CLOCK SELECT BLOCK near ICs 2L-2M.                                     |

| [ | ] | For use with a 16 bit address bus install a jumper from "M" to "S" in the ADDRESS MODE JUMPER BLOCK. In this mode IC 4B is not needed. |

| [ | ] | For Use with a 24 bit address bus install a jumper from "M" to "E" in the ADDRESS MODE JUMPED BLOCK. In this mode IC 4B is required.   |

| [ | ] | Insert the LM358 at U4.                                                                                                                |

| [ | ] | Insert the 74LS00 IC at 1D.                                                                                                            |

| [ | ] | Insert the 74LSO2 IC at 3C.                                                                                                            |

| [ | ] | Insert the 74LSO4 ICs at 1L and 2F.                                                                                                    |

| [ | ] | Insert the 7406 ICs at 1M and 2H.                                                                                                      |

| [ | ] | Insert the 74LS08 IC at 4A.                                                                                                            |

| [ | ] | Insert the 74LS10 IC at 2E.                                                                                                            |

| [ | ] | Insert the 74LS20 IC at 2C.                                                                                                            |

| [ | ] | Insert the 74LS21 IC at 2B.                                                                                                            |

| [ | ] | Insert the 74LS27 ICs at 3E and 3J.                                                                                                    |

| [ | ] | Insert the 74LS32 IC at 3B.                                                                                                            |

| [ | ] | Insert the 74LS74 IC at 2L.                                                                                                            |

| [ | ] | Insert the 74LS93 IC at 2M.                                                                                                            |

| [ | ] | Insert the 74LS113 ICs at 1C and 3A.                                                                                                   |

| [ | ] | Insert the 74LS123 ICs at 1A, 1B, 2A, OL, and OM.                                                                                      |

| [ | ] | Insert the 74LS240 ICs at 1F, 3K, and 3L.                                                                                              |

Insert the 74LS244 ICs at 1H, 4F, 4H, 4J, 4K, and 4L. Insert the 74LS273 IC at 4M. Insert the 7425 ICs at 1k and 2K. Insert the 7445 IC at 3M. Insert the 8131 ICs at 3F and 3H. Insert the 16-pin 150 ohm resistor pack at 1E. Insert the Z80A microprocessor at 2D. Insert the WD-1791-01 controller at 1J. [ ] Insert the 21141-3 static rams at 4C, 4DL, 4DR, and 4E. Inspect all inserted ICs for bent pins. Place DOUBLE D controller board in an extender board in an S100 mainframe. Open all switches in S1. Turn power switch on. Adjust trimmer R5 for a 2.0 mhz clock signal at IC 1B pin 12. (1.0 mhz for 5" configuration) Turn power switch off. Connect disk interface cable from controller to the disk drive. Observe pin 1 indications. Turn power switch on. Insert a preformatted single density diskette into the drive (DRIVE O) and close the door.

Adjust R2 for a 1.0 us output from one-shot 2A pin 5. (2.0 us output on 5" configuration)

Close switch TST\*. This will select drive O, turn

$[\ ]$  Open switch TST\*. Turn power switch off.

the motor control on, and load the head.

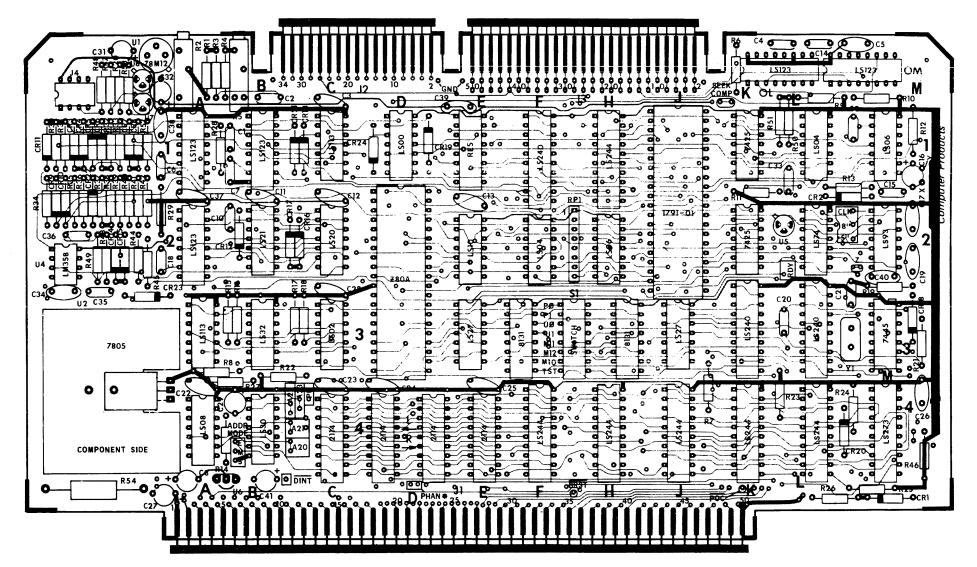

COMPONENT SIDE

#### JADE

Computer Products

| LTR | DESCRIPTION | APPROVED | DATE   |

|-----|-------------|----------|--------|

| Α   | PROTOTYPE   |          | 9.79   |

| С   |             | DD       | 2 · 80 |

IOD - 1200 - C SHEET 6 OF 7

| NUMBER OF SPECIES  | UF 85 JC 9-79 |       |   |        |                   |        |      |          |           |        |

|--------------------|---------------|-------|---|--------|-------------------|--------|------|----------|-----------|--------|

| TOBERAN ESON       | Charge C      |       |   | ĺ      | Computer Products |        |      |          |           |        |

| JEC MACCO AND IN   | APPROVED BY   |       |   | PC ART | wor               | RK     | (COM | P. SIDE) |           |        |

| A*A (ii() - (0)    | <b>├</b> ──   |       | T |        | ממ                | ROLLER | • :  |          |           |        |

| PRINTED SIRCUIT    | <b>-</b>      |       | 1 |        |                   | 0.0    | •    | COITT    |           | •      |

| DESIGN BY          | <b>_</b>      |       |   |        |                   | 1,171  |      | v1 NO    |           | 1 96 V |

|                    |               |       |   |        |                   | C      |      | IOD-1    | 1200      | C      |

| ENGINEERING        | NE KT         | SINC. |   |        |                   |        |      | 100      |           |        |

| TUSTIN CALIF 92680 | DRAM .        | ¥1;   |   |        | 16A.i 211         |        |      |          | SHELL 2 - | 7      |

#### JADE

Computer Products

|   | 4.5         | spence. | -A11   |

|---|-------------|---------|--------|

| Δ | OBS ISITEPE |         | 9.79   |

| 1 |             | 0.0     | 2 - 81 |

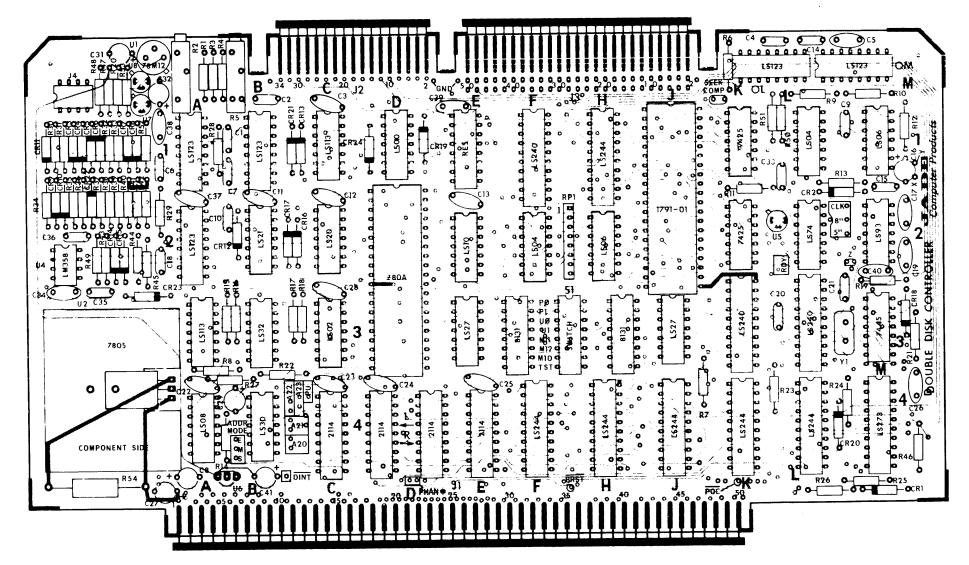

IOD - 1200 - C SHEET 6 OF 7

| The second secon | ν .   | 1.      |         | 9 79 | Computer Products |    |       |          |                               |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|---------|------|-------------------|----|-------|----------|-------------------------------|--|--|

| HATE STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 41 | дирн. н | vite B. |      | PC ART            |    |       |          |                               |  |  |

| PRINTED CIRCUIT DESIGN BY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |         |         |      | ו טט              | r1 |       | COLLET   | <b>\</b><br>T <sub>ni</sub> , |  |  |

| a ga gagi, dinga                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |         |         |      |                   | С  | IOD-1 | 200      | C                             |  |  |

| ENGINEERING<br>TUSTIN CALIF 92680                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |         |         |      | : Atr 2 1         |    |       | au i 1 4 | 7                             |  |  |

# JADE

NWOHE/SONE/REDIOS

10D-1200-C

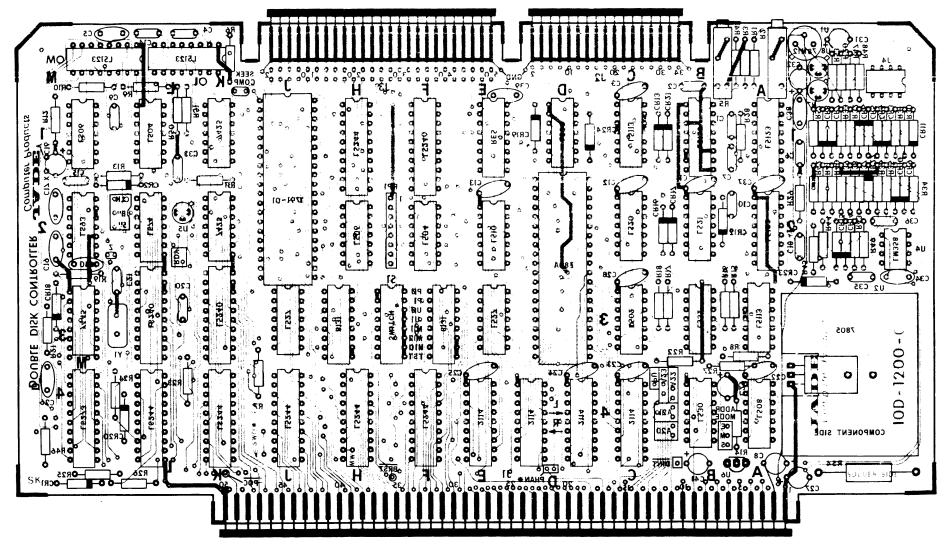

SHEET 6 OF 7

| 9.79 |            | PROTOTYPE | Α |

|------|------------|-----------|---|

| 08·V | <b>0</b> 0 |           | 3 |

| JADE Computer Products |                                             |       |        |           |  | 97.9 |                   |                  | The common Administration of the common and the com |

|------------------------|---------------------------------------------|-------|--------|-----------|--|------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E                      | PC ARTWORK (SOLDER SIDE) DD DISK CONTROLLER |       |        |           |  |      | ्राःअ <b>म</b> प∆ | l · ·            | PART STANFORM STANFOR |

| 1                      |                                             |       |        |           |  |      |                   |                  | PRINTED CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Č Ž                    | 200                                         | IOD-1 | )<br>3 |           |  |      | L                 |                  | DESIGN BY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7                      | n 2 1346                                    |       | 1      | 4.Att 2:1 |  |      | er.               | C TRHZ<br>Z-WAHG | ENGINEERING<br>TUSTIN, CALIF 92680                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# APPENDIX B

# PARTS LIST

| RESISTO                                                                                                 | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              | LOCAT                                   | CION-IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |