Programming

Reference

Manual

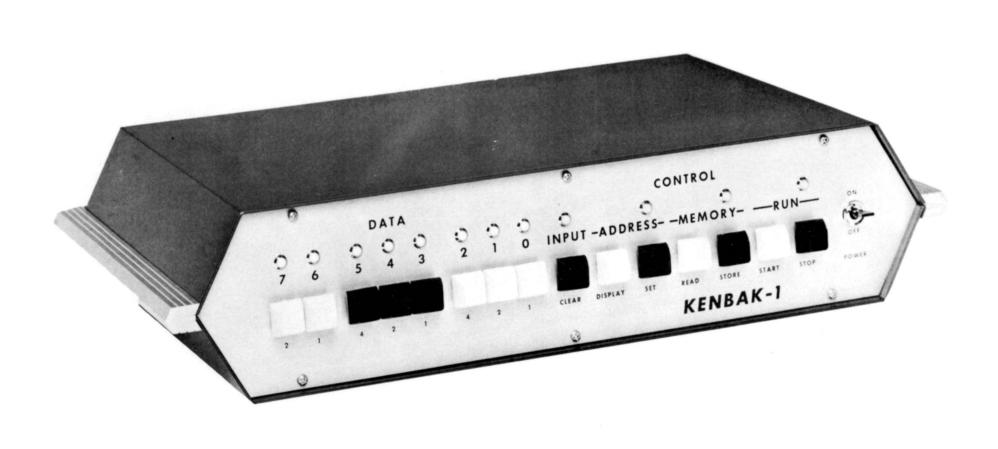

KENBAK-1

Computer

KENBAK

P.O.BOX 49324

LOS ANGELES, CA. 90049

frontispiece 4/1/71

#### Preface

This manual is a summary of the KENBAK-1 computer programming characteristics. The reader is assumed to be acquainted with the general theory of digital computers. Other manuals published by KENBAK have as their subjects the general theory of computers, programming of the KENBAK-1, and the maintenance and theory of operation of the KENBAK-1.

To correct errors or to clarify the presentation, revised pages will be issued from time to time. The list of current pages should be retained as it indicates the status of the manual. Pages are punched for a three ring binder so that the user may keep all of his material in one place with easy accessibility.

Questions and comments are welcomed since that provides the feedback which tells how well the job is being done.

Price: \$2.00

# Programming Reference Manual KENBAK-1 Computer

# List of Current Pages, Revision 0

| <u>Page</u> | <u>Dated</u> | <u>Page</u> | <u>Dated</u> | <u>Page</u> | Dated  |

|-------------|--------------|-------------|--------------|-------------|--------|

| PR-1        | 4-1-71       | PR-9        | 4-1-71       | PR-17       | 4-1-71 |

| PR-2        | 4-1-71       | PR-10       | 4-1-71       | PR-18       | 4-1-71 |

| PR-3        | 4-1-71       | PR-11       | 4-1-71       | PR-19       | 4-1-71 |

| PR-4        | 4-1-71       | PR-12       | 4-1-71       | PR-20       | 4-1-71 |

| PR-5        | 4-1-71       | PR-13       | 4-1-71       | PR-21       | 4-1-71 |

| PR-6        | 4-1-71       | PR-14       | 4-1-71       | PR-22       | 4-1-71 |

| PR-7        | 4-1-71       | PR-15       | 4-1-71       | PR-23       | 4-1-71 |

| PR-8        | 4-1-71       | PR-16       | 4-1-71       | PR-24       | 4-1-71 |

## Errata

For which no revised page was issued

NONE

# Programming Reference Manual KENBAK-1 Computer

# Table of Contents

|                                                           | Page  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------|-------|--|--|--|--|--|--|--|--|

| Introduction                                              | PR- 1 |  |  |  |  |  |  |  |  |

| Memory Structure and Addressing                           | PR- 1 |  |  |  |  |  |  |  |  |

| Special Memory Locations                                  |       |  |  |  |  |  |  |  |  |

| Number Representations                                    |       |  |  |  |  |  |  |  |  |

| Addressing Modes                                          | PR- 4 |  |  |  |  |  |  |  |  |

| Instructions                                              |       |  |  |  |  |  |  |  |  |

| ADD and SUB                                               | PR- 5 |  |  |  |  |  |  |  |  |

| LOAD and STORE                                            | PR- 6 |  |  |  |  |  |  |  |  |

| AND and OR                                                | PR- 7 |  |  |  |  |  |  |  |  |

| LNEG                                                      | PR- 8 |  |  |  |  |  |  |  |  |

| JUMPS (BRANCHES)                                          | PR- 9 |  |  |  |  |  |  |  |  |

| SKIPS                                                     | PR-10 |  |  |  |  |  |  |  |  |

| SET BITS                                                  | PR-11 |  |  |  |  |  |  |  |  |

| SHIFTS and ROTATES                                        | PR-12 |  |  |  |  |  |  |  |  |

| NOOP and HALT                                             | PR-13 |  |  |  |  |  |  |  |  |

| Symbolic Representation of Instructions                   | PR-14 |  |  |  |  |  |  |  |  |

| Register-to-Register Operations                           | PR-15 |  |  |  |  |  |  |  |  |

| Table Look Up                                             | PR-16 |  |  |  |  |  |  |  |  |

| Relative Operand Addressing                               | PR-16 |  |  |  |  |  |  |  |  |

| Input and Output                                          | PR-17 |  |  |  |  |  |  |  |  |

| Console Operations                                        | PR-18 |  |  |  |  |  |  |  |  |

| Power On-Off Switch                                       | PR-18 |  |  |  |  |  |  |  |  |

| Console Data Lamps                                        | PR-18 |  |  |  |  |  |  |  |  |

| Console Data Pushbuttons and Clear                        | PR-20 |  |  |  |  |  |  |  |  |

| Address Control Lamp, Address Display and Set Pushbuttons | PR-20 |  |  |  |  |  |  |  |  |

| Memory Control Lamp, Memory Read and Store Pushbuttons    | PR-21 |  |  |  |  |  |  |  |  |

| Start and Stop Pushbuttons                                | PR-21 |  |  |  |  |  |  |  |  |

| Lamp Tests P                                              |       |  |  |  |  |  |  |  |  |

| Example of Console Use                                    |       |  |  |  |  |  |  |  |  |

| Summary of Instruction Coding                             |       |  |  |  |  |  |  |  |  |

#### INTRODUCTION

The KENBAK-1 is a serial stored program general purpose digital computer with a memory of 256 eight bit bytes. Internally the machine is binary two's complement. Halt, No-op, and Shift instructions require one byte. All other instructions require two bytes which may start on either an odd or even address.

# MEMORY STRUCTURE AND ADDRESSING

Each of the 256 bytes of memory is addressable. The octal range of their addresses is 000 to 377 (decimal 000 to 255). Since  $2^8$  is equal to 256, one byte of memory can hold a complete address. The eight bits of a byte are always identified as:

| <u>b7</u> | b6 | <u>b5</u> | b4 | b3 | b2 | bl | <u>b0</u> | Binary to Octal Conversion |

|-----------|----|-----------|----|----|----|----|-----------|----------------------------|

| x         | x  |           |    |    |    |    |           | Octal group 100            |

|           |    | х         | х  | х  |    |    |           | Octal group 10             |

|           |    |           |    |    | х  | х  | х         | Octal group 1              |

where the most significant bit is b7 and the least significant bit is b0. Octal group 100 never assumes a value larger than 3.

#### SPECIAL MEMORY LOCATIONS

Nine memory locations are used for special purposes. They may be addressed and used as an operand location though the programmer must be aware that he may be interfering with the assigned special function. The special locations are:

| Octal Location | Purpose                               |

|----------------|---------------------------------------|

| 000            | A Register                            |

| 001            | B Register                            |

| 002            | X Register                            |

| 003            | P Register                            |

| 200            | Output Register                       |

| 201            | Overflow and Carry for the A Register |

| 202            | Overflow and Carry for the B Register |

| 203            | Overflow and Carry for the X Register |

| 377            | Input Register                        |

The A Register is the primary register of the arithmetic unit.

Operations that can be performed with it include Load, Store, Add,

Subtract, And, Or, Load Complement, Shifts and Rotates. The B Register is the secondary register of the arithmetic unit. Operations that can be performed with it include Load, Store, Add, Subtract, Shifts, and Rotates. The contents of the X Register are used in the Indexed address mode. Operations that can be performed with it include Load, Store, Add, Subtract. When not being used in Indexed addressing, the X Register can be used as an arithmetic register.

The A, B, and X Registers can all be used (singly, not jointly) to control the branch conditions. The testable conditions include Non-zero, Zero, Less than Zero, Positive (including zero), and Positive Non-zero.

The P Register is the Program Counter which shows the address of the next instruction to be executed.

The Output Register, location 200, controls the Console Data Lamps when the computer is in the Run state.

Locations 201, 202, and 203 contain the Overflow (OF) and Carry (CA) bits for the A, B, and X Registers, respectively.

b7 b6 b5 b4 b3 b2 b1 b0 0 0 0 0 0 CA OF

Each time that an Add or Subtract instruction is performed, the Overflow and Carry bits for the register are updated. They remain in this state until the next Add or Subtract operation to that register occurs. The remaining six bits in each word are always set to zero when the Overflow and Carry are updated. The Load Complement and the Shift instructions do not alter these words, nor do any other instructions.

Location 377 is the input location. Data from the Console Data Pushbuttons is placed here in both the Run and Halt states of the computer.

# NUMBER REPRESENTATIONS

Several choices exist for number representation including positive integer, signed integer, and signed fractional. The range of numbers that can be expressed in one byte in each mode is shown in the following table:

| Number Representation    | Decimal<br>Value_                       | Octal<br><u>Code</u> |     | Binar<br>Code |      |  |  |  |  |  |

|--------------------------|-----------------------------------------|----------------------|-----|---------------|------|--|--|--|--|--|

| Positive Integer         |                                         |                      |     |               |      |  |  |  |  |  |

| Largest positive number  |                                         |                      |     |               |      |  |  |  |  |  |

| Smallest number          | 0                                       | 000                  | 00  | 000           | 000. |  |  |  |  |  |

| Signed Integer           |                                         |                      |     |               |      |  |  |  |  |  |

| Largest positive number  | umber +127 177 01                       |                      |     |               |      |  |  |  |  |  |

| Smallest negative number | -128                                    | 200                  | 10  | 000           | 000. |  |  |  |  |  |

| Signed Fractional        |                                         |                      |     |               |      |  |  |  |  |  |

| Largest positive number  | Largest positive number +127/128 177 01 |                      |     |               |      |  |  |  |  |  |

| Smallest negative number | -128/128                                | 200                  | 1,0 | 000           | 000  |  |  |  |  |  |

|                          |                                         |                      |     |               |      |  |  |  |  |  |

The Jump (Branch) conditions of Positive, Negative, and Positive Non-zero assume one of the signed modes of number representation. The Jump conditions of Zero and Non-zero apply for all of the representations since 00 000 000 is the binary code for zero in all of them.

As detected by the computer, Overflow is based on the signed representations. Since the binary arithmetic is identical in all of these representations, the Carry bit is not affected by the programming choice for number representation. For positive integer representation the Carry is also the Overflow condition.

The range of quantities can be extended by using more than one byte.

#### ADDRESSING MODES

The Add, Subtract, Load, Store, Load Complement, And, and Or instructions have five addressing modes:

- 1. Constant, or Immediate

- 2. Memory

- 3. Indirect, or Deferred

- 4. Indexed

- 5. Indirect Indexed

In the Constant, or Immediate, mode of addressing, the operand is the contents of the second word of the instruction.

In the Memory mode of addressing, the second word of the instruction is the address of the operand.

In the Indirect addressing mode, the second word of the instruction is the address of the address of the operand.

In the Indexed mode of addressing, the contents of the second word of the instruction are added to the contents of the X Register to form the address of the operand.

In the Indirect Indexed mode of addressing, the contents of the second word of the instruction are used as an address pointer to the contents of another, second, location. The contents of this second location are added to the contents of the X Register to form the address of the operand.

In the Store instruction the operand address is where the data is stored. In Store Immediate instructions the data is stored in the second half of the instruction.

The Bit Manipulation instructions have only the Memory addressing mode.

The Jump or Branch instructions have Memory (called Direct) addressing or Indirect addressing.

#### INSTRUCTIONS

In the following pages, the individual instructions are discussed. It is assumed in each case that the instruction is in location p and (if it is a two byte instruction) in p+1.

#### ADDITION (ADD)

| First Byte |   |   |   |   |   |   |   |   |                   | Second Byte     |

|------------|---|---|---|---|---|---|---|---|-------------------|-----------------|

| Register   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Addressing Mode   | 7 6 5 4 3 2 1 0 |

| Α          | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | Immediate         |                 |

| В          | 0 | 1 |   |   |   | 1 | 0 | 0 | Memory            | Address or      |

| X          | 1 | 0 |   |   |   | 1 | 0 | 1 | Indirect          | Operand         |

|            |   |   |   |   |   | 1 | 1 | 0 | Indexed           |                 |

|            |   |   |   |   |   | 1 | 1 | 1 | Indirect, Indexed |                 |

The operand is specified or located according to the rules for the addressing mode. The operand and the contents of the designated register are added together and the sum is placed in the designated register. The operand is unchanged in the memory (unless the operand was in the designated register itself). The Carry and Overflow bits are updated in location 201 (for A), in 202 (for B), or in 203 (for X). The P Register is advanced by 2 and the next instruction is taken from p + 2.

#### SUBTRACTION (SUB)

| First Byte  |   |   |   |   |   |   |                       |   |                                                                 | Second Byte           |

|-------------|---|---|---|---|---|---|-----------------------|---|-----------------------------------------------------------------|-----------------------|

| Register    | 7 | 6 | 5 | 4 | 3 | 2 | 1                     | 0 | Addressing Mode                                                 | 7 6 5 4 3 2 1 0       |

| A<br>B<br>X | 0 | _ | 0 | 0 | 1 | 1 | 1<br>0<br>0<br>1<br>1 | 0 | Immediate<br>Memory<br>Indirect<br>Indexed<br>Indirect, Indexed | Address or<br>Operand |

The operand is specified or located according to the rules for the addressing mode. The operand is subtracted from the contents of the designated register and the difference is placed in the designated register. The operand is unchanged in the memory (unless the operand was in the designated register itself). The Carry (or Borrow) and the Overflow bits are updated in location 201 (for A), in 202 (for B), or in 203 (for X). The P Register is advanced by 2 and the next instruction is taken from p + 2.

### LOAD (LOAD)

| First Byte | <u> </u> |   |   |   |   |   |   |   |                   | Second Byte     |

|------------|----------|---|---|---|---|---|---|---|-------------------|-----------------|

| Register   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Addressing Mode   | 7 6 5 4 3 2 1 0 |

| Α          | 0        | 0 | 0 | 1 | 0 | 0 | 1 | 1 | Immediate         |                 |

| В          | 0        | 1 |   |   |   | 1 | 0 | 0 | Memory            | Address or      |

| X          | 1        | 0 |   |   |   | 1 | 0 | 1 | Indirect          | Operand         |

|            |          |   |   |   |   | 1 | 1 | 0 | Indexed           |                 |

|            |          |   |   |   |   | 1 | 1 | 1 | Indirect, Indexed |                 |

The operand is specified or located according to the rules for the addressing mode. The operand is placed in the designated register replacing the previous contents. The operand is unchanged in the memory. The P Register is advanced by 2 and the next instruction is taken from p+2.

## STORE (STORE)

| First Byte  |                                 | Second Byte           |

|-------------|---------------------------------|-----------------------|

| Register    | 7 6 5 4 3 2 1 0 Addressing Mode | 7 6 5 4 3 2 1 0       |

| A<br>B<br>X | 0 0 0 1 1 0 1 1                 | Address or<br>Operand |

The location to receive the data is determined by the addressing rules. The contents of the designated register are placed in this location replacing the previous contents. The contents of the register are unchanged. The P Register is advanced by 2 and the next instruction is taken from p+2.

| First Byte |          |   |   |   |   | Second Byte |   |   |                   |                 |

|------------|----------|---|---|---|---|-------------|---|---|-------------------|-----------------|

|            | <u>7</u> | 6 | 5 | 4 | 3 | 2           | 1 | 0 | Addressing Mode   | 7 6 5 4 3 2 1 0 |

|            | 1        | 1 | 0 | 1 | 0 | 0           | 1 | 1 | Immediate         |                 |

|            |          |   |   |   |   | 1           | 0 | 0 | Memory            | Address or      |

|            |          |   |   |   |   | 1           | 0 | 1 | Indirect          | Operand         |

|            |          |   |   |   |   | 1           | 1 | 0 | Indexed           | -               |

|            |          |   |   |   |   | 1           | 1 | 1 | Indirect. Indexed |                 |

The operand is specified or located according to the rules for the addressing mode. Each bit of the operand is Anded with the corresponding bit of the A Register, according to the truth table below, and the result is placed in the A Register replacing the previous contents. The operand is unchanged in the memory.

The P Register is advanced by 2 and the next instruction is taken from p + 2.

|                           | Re  | esult          |

|---------------------------|-----|----------------|

| Bits from<br>Two Operands | AND | (Inclusive) OR |

| 0 0                       | 0   | 0              |

| 0 1                       | 0   | 1              |

| 1 0                       | 0   | 1              |

| 1 1                       | 1   | 1              |

LOGICAL SUM (OR)

| First Byte |   |   |   |   |   |   |   |   |                   | Second Byte     |

|------------|---|---|---|---|---|---|---|---|-------------------|-----------------|

|            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Addressing Mode   | 7 6 5 4 3 2 1 0 |

|            | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | Immediate         |                 |

|            |   |   |   |   |   | 1 | 0 | 0 | Memory            | Address or      |

|            |   |   |   |   |   | 1 | 0 | 1 | Indirect          | Operand         |

|            |   |   |   |   |   | 1 | 1 | 0 | Indexed           | -               |

|            |   |   |   |   |   | 1 | 1 | 1 | Indirect, Indexed |                 |

The operand is specified or located according to the rules for the addressing mode. Each bit of the operand is Or-ed with the corresponding bit of the A Register, according to the truth table above (see AND), and the result is placed in the A Register replacing the previous contents. The operand is unchanged in the memory.

The P Register is advanced by 2 and the next instruction is taken from  $p \, + \, 2$ .

| First Byte |   |   |   |   |   |   |   |   |                   | Second Byte     |

|------------|---|---|---|---|---|---|---|---|-------------------|-----------------|

|            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Addressing Mode   | 7 6 5 4 3 2 1 0 |

|            | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | Immediate         |                 |

|            |   |   |   |   |   | 1 | 0 | 0 | Memory            | Address or      |

|            |   |   |   |   |   | 1 | 0 | 1 | Indirect          | Operand         |

|            |   |   |   |   |   | 1 | 1 | 0 | Indexed           | -               |

|            |   |   |   |   |   | 1 | 1 | 1 | Indirect, Indexed |                 |

The operand is specified or located according to the rules for the addressing mode. The A Register is loaded with the arithmetic complement (the value obtained by subtracting from zero) of the operand. This replaces the previous contents of the A Register. The operand is unchanged in the memory unless it had been specified as the contents of the A Register itself.

Overflow occurs if the operand was equal to -128 (10 00 000). In this case the result obtained is -128. This overflow is not detected nor is the A Register Overflow bit in location 201 altered by the LNEG instruction.

The P Register is advanced by 2 and the next instruction is taken from  $p \, + \, 2$ .

| JUMP | DIRE | CT   |          | (JPD) |

|------|------|------|----------|-------|

| JUMP | INDI | RECT |          | (JPI) |

| JUMP | AND  | MARK | DIRECT   | (JMD) |

| JUMP | AND  | MARK | INDIRECT | (JMI) |

| First Byte                                              |                       |                       | <br>   |        |                  |                  |   |                                                             | Second Byte                                                             |

|---------------------------------------------------------|-----------------------|-----------------------|--------|--------|------------------|------------------|---|-------------------------------------------------------------|-------------------------------------------------------------------------|

| A Register<br>B Register<br>X Register<br>Unconditional | 7<br>0<br>0<br>1<br>1 | 6<br>0<br>1<br>0<br>1 | 4      | 3      | 2<br>0<br>1<br>1 | 1<br>0<br>0<br>1 | 1 | Condition Non-zero Zero Negative Positive Positive Non-zero | 7 6 5 4 3 2 1 0  Target Address or Indirect Reference to Target Address |

| Jump<br>Jump and Mark                                   |                       |                       | 0<br>1 | 0<br>1 | Ļ                |                  | - | Direct Address (Me<br>Indirect Address                      | emory)                                                                  |

The "target" address is defined to be:

| Jump Direct or<br>Jump and Mark Direct     | The contents of the second byte of the instruction                                       |

|--------------------------------------------|------------------------------------------------------------------------------------------|

| Jump Indirect or<br>Jump and Mark Indirect | The address contained in the byte whose address is in the second byte of the instruction |

The Direct address mode is the same as the Memory address mode. The Indirect address mode for the Jump instructions is the same as the Indirect mode for the arithmetic and logic instructions.

The designated register (A, B, or X) is examined to determine if the Jump Conditions are met (true). A Non-zero condition in the register means at least one bit is a One. A Zero condition in the register means that all bits in the register are Zero. The Negative condition means that b7 (the most significant bit) is a One. The Positive condition means that b7 is a Zero. The Positive Non-zero condition means b7 is a Zero and at least one of the remaining seven bits is a One. The Jump Conditions can be forced to be true by the Unconditional specification.

If the Jump Conditions are true because the specified condition is true or because an Unconditional Jump is specified, then the next instruction is not taken from location p+2, but from the target address in the Jump instructions or from the target address plus one in the Jump and Mark instructions. If the Jump Conditions are not true, the next instruction is taken from p+2.

In the Jump and Mark instructions, the value p+2 is stored in the target address prior to executing the instruction in the location following the target address.

Notice that the instruction will not be a Jump instruction of any type unless bits 2, 1, and 0 of the first byte are either 011, 100, 101, 110, or 111 even if the Jump Conditions are Unconditional.

SKIP ON ZERO (SKP 0) SKIP ON ONE (SKP 1)

| First Byte |     |              |       |                 | Second Byte     |

|------------|-----|--------------|-------|-----------------|-----------------|

|            | 7 6 | 5 <b>4</b> 3 | 2 1 0 | Bit<br>Position | 7 6 5 4 3 2 1 0 |

|            | _1  |              | 0 1 0 |                 |                 |

| Skip on 0  | 0   | 0 0 0        |       | b0              |                 |

| Skip on 1  | 1   | 0 0 1        |       | <b>b1</b>       | Memory Address  |

|            |     | 0 1 0        |       | <b>b2</b>       |                 |

|            |     | 0 1 1        |       | b3              |                 |

|            |     | 1 0 0        |       | b4              |                 |

|            |     | 1 0 1        |       | <b>b</b> 5      |                 |

|            | 1   | 1 1 0        |       | b6              |                 |

|            |     | 1 1 1        |       | b7              |                 |

First the location in memory whose address is given in the second byte of the instruction is determined. Within these eight bits, the one is selected whose position corresponds to the three bit code in positions 5, 4, and 3 of the first byte of the instruction. If the instruction is Skip on Zero and the selected bit is a Zero or if the instruction is Skip on One and the selected bit is a One, then the next instruction is taken from p+4 and the next two locations in the "normal" instruction sequence are not used. Either a two byte instruction or two one byte instructions may be skipped. If the Skip Conditions are not met, then the next instruction is taken from p+2.

SET 0 (SET 0) SET 1 (SET 1)

| First Byte |     |       |       |                        | Second Byte     |

|------------|-----|-------|-------|------------------------|-----------------|

|            | 7 6 | 5 4 3 | 2 1 0 | Bit<br><u>Position</u> | 7 6 5 4 3 2 1 0 |

|            | 0   |       | 0 1 0 |                        | <u></u>         |

| Set to 0   | 0   | 0 0 0 |       | b0                     |                 |

| Set to 1   | 1   | 0 0 1 |       | bl                     | Memory Address  |

|            |     | 0 1 0 | 1     | b2                     |                 |

|            |     | 0 1 1 |       | b3                     |                 |

|            |     | 100   | •     | b4                     |                 |

|            |     | 101   |       | b5                     |                 |

|            |     | 1 1 0 | 1     | b6                     |                 |

|            |     | 1 1 1 |       | b7                     |                 |

The SET 0 instruction forces a single bit in the memory to a Zero. The SET 1 instruction forces a single bit in the memory to a One. The address of the memory location is contained in the second byte of the instruction. The bit within this word is determined by the bit code in positions 5, 4, and 3 of the first byte of the instruction. No other bit in the memory is changed except the designated one. The P Register is advanced by 2 and the next instruction is taken from location p+2.

| SHIFT LEFT   | (SFTL) |

|--------------|--------|

| SHIFT RIGHT  | (SFTR) |

| ROTATE LEFT  | (ROTL) |

| ROTATE RIGHT | (ROTR) |

| First Byte |   |   |   |   |   |   |   |   |          |

|------------|---|---|---|---|---|---|---|---|----------|

|            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |          |

| Right      | 0 |   |   |   |   | 0 | 0 | 1 |          |

| Left       | 1 |   |   | 0 | 1 |   |   |   | 1 Place  |

| Shift      |   | 0 |   | 1 | 0 |   |   |   | 2 Places |

| Rotate     |   | 1 |   | 1 | 1 |   |   |   | 3 Places |

| A Register |   |   | 0 | 0 | 0 |   |   |   | 4 Places |

| B Register |   |   | 1 |   |   |   |   |   |          |

Shifts and Rotates may be for 1, 2, 3, or 4 places. An n place Shift or Rotate is equal to performing a 1 place Shift or Rotate n times. The 1 place Shifts and Rotates are defined below.

|                |                   | <u>b7</u> | <u>b6</u> | <u>b5</u> | <u>b4</u> | <u>b3</u> | b2 | bl | <u>b0</u> |

|----------------|-------------------|-----------|-----------|-----------|-----------|-----------|----|----|-----------|

| SHIFT LEFT 1   | Original<br>After |           |           |           |           |           |    |    |           |

| ROTATE LEFT 1  | Original<br>After |           |           |           |           |           |    |    |           |

| SHIFT RIGHT 1  | Original<br>After |           |           |           |           |           |    |    |           |

| ROTATE RIGHT 1 | Original<br>After |           |           |           |           |           |    |    |           |

This Shift or Rotate is made to the A or B Register as specified. The P Register advances by one and the next instruction is taken from p + 1.

One byte instruction

One byte instruction

NO OPERATION (NOOP)

7 6 5 4 3 2 1 0 1 x x x x 0 0 0

The P Register is advanced by one and the next instruction is taken from location  $p\,+\,1$ .

HALT (HALT)

One byte instruction

7 6 5 4 3 2 1 0 0 x x x x 0 0 0

At the end of this instruction, the computer goes from the Run state to the Halt state. The P Register is advanced and ready to take the next instruction from location p+1.

#### SYMBOLIC REPRESENTATION OF INSTRUCTIONS

An instruction, including the operand address or specification, is represented symbolically in three parts. The first field is the basic operation such as ADD or SFTR. Preferred abbreviations for these operations were given with the instruction descriptions. The second field is the details of the basic operation, for example, "A" meaning to add to the A Register or B3 meaning to shift the B Register 3 places. The third field is the operand address except in the case of the Constant addressing mode which has a special representation illustrated below. Indirect addressing is indicated by the use of parentheses around the address. The Index addressing mode is indicated by ",X". The third field for the five addressing modes becomes:

Constant C = Value of Operand

Memory DATE

Indirect (DATE)

Indexed DATE, X

Indirect/Indexed (DATE), X

where DATE is the name of some location in memory. One byte instructions have no third field and may (Shifts and Rotates) or may not (Halt and Noop) have a second field.

#### REGISTER-TO-REGISTER OPERATIONS

All of these operations are produced by a single instruction using the Memory addressing mode. They are special cases of the previously discussed instructions which result from the addressability of the A, B, X, and P Registers.

| Operation                                                                                       | Symbolic                                                 | Rep                   | res                        | <u>entation</u>                                     |                            |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|----------------------------|-----------------------------------------------------|----------------------------|

| CLEAR A<br>CLEAR B<br>CLEAR X                                                                   | SUB A<br>SUB B<br>SUB X                                  | A<br>B<br>X           |                            |                                                     |                            |

| TRANSFER A TO B TRANSFER A TO X TRANSFER B TO A TRANSFER B TO X TRANSFER X TO A TRANSFER X TO B | LOAD B<br>LOAD X<br>LOAD A<br>LOAD X<br>LOAD A<br>LOAD B | A<br>B<br>B<br>X<br>X | or<br>or<br>or<br>or<br>or | STORE A<br>STORE B<br>STORE B<br>STORE X<br>STORE X | B<br>X<br>A<br>X<br>A<br>B |

| LEFT SHIFT A 1<br>LEFT SHIFT B 1<br>LEFT SHIFT X 1                                              | ADD A<br>ADD B<br>ADD X                                  | A<br>B<br>X           |                            |                                                     |                            |

This left shift operation is the same as produced by the instruction of the same name. When produced by adding the register to itself, Overflow and Carry are detected which they are not by the Left Shift instruction. The Carry bit is set if b7 was a One and is reset if b7 was a Zero. The Overflow bit is set if the original number was larger than 63 or smaller than -64. Otherwise the Overflow bit is reset.

| LOAD A NEG A | LNEG A | Α |

|--------------|--------|---|

| LOAD A NEG B | LNEG A | В |

| LOAD A NEG X | LNEG A | X |

The A Register is loaded with the complement (the value obtained by subtracting from 00 000 000) of the specified register. Overflow, undetected, occurs when the original number is -128 when the result produced is also -128.

| A + B TO A A - B TO A A + X TO A A - X TO A B + A TO B B - A TO B B + X TO B B - X TO B X + A TO X X - A TO X X - B TO X | ADD A SUB A ADD A SUB A ADD B SUB B ADD B SUB B ADD X SUB X ADD X SUB X | X<br>A<br>A<br>X<br>X<br>A<br>A |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------|

| A AND B TO A<br>A AND X TO A                                                                                             | AND A<br>AND A                                                          | B<br>X                          |

| A OR B TO A<br>A OR X TO A                                                                                               | OR A<br>OR A                                                            | B<br>X                          |

| JUMP TO A + 2<br>JUMP TO B + 2<br>JUMP TO X + 2                                                                          | STORE A<br>STORE B<br>STORE X                                           | P                               |

Storing a number n in the P Register under program control causes an unconditional branch or jump to location n+2.

#### TABLE LOOK UP

Using the contents of the A, B, or X Register as an Indirect address produces a result which has been called "table look up". The operation LOAD A (A)

replaces the address in the A Register by the contents of that address. Similar operations can be produced by the B and X Registers or by combinations of the A, B, and X Registers.

#### RELATIVE OPERAND ADDRESSING

Using the Indirect Indexed addressing mode with the P Register as the Indirect address location creates a condition which could be called "relative operand addressing". The operand address will be a "distance" from the instruction itself which is given by the contents of the X Register.

#### INPUT AND OUTPUT

Input from the Console Data Pushbuttons to the program and output from the program to the Console Data Lamps can occur while the computer is in the Run state. All input appears in location 377<sub>8</sub> whose contents may be tested with the Skip instructions or whose contents may be transferred to the A, B, or X Registers. It must be remembered that data will appear in location 377<sub>8</sub> while the operator is in the process of forming his input. If the input data is not to be used until the formation or entry is completed, one of the bits should be used as an interlock signal.

The contents of location  $200_8$  are continuously displayed in the Console Data Lamps when the computer is in the Run state. A transfer of data to  $200_8$  is equivalent to the output of that data to the Console Data Lamps. If the computer goes from the Run to the Halt state, the contents of location  $200_8$  are displayed until the operator makes another choice.

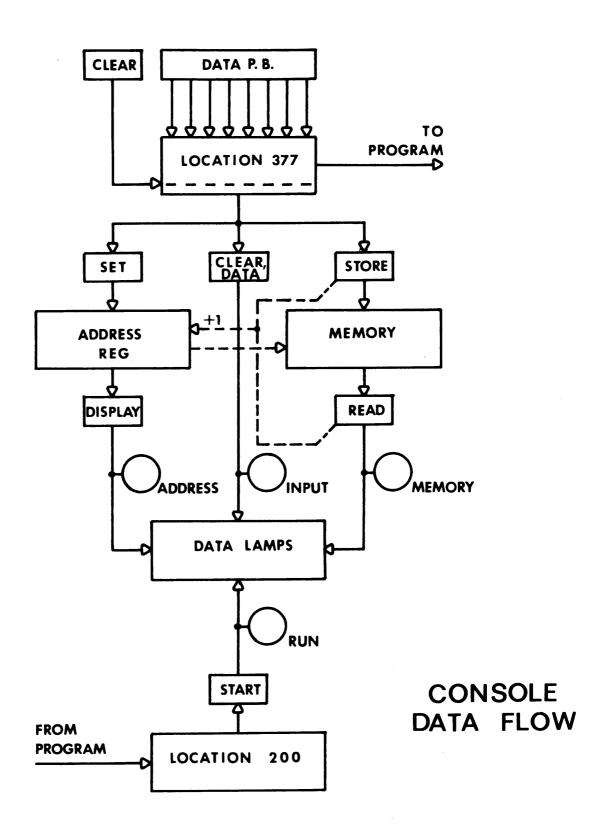

#### CONSOLE OPERATIONS

The Console switches and lamps provide the means to control the computer, to load programs and data, and to receive output (frontispiece).

## Power On-Off Switch

The Power Switch controls the line voltage to the computer.

Data in the memory is lost when power is turned off. When power is turned on, random data will appear in the memory. Since the computer uses very little power (40 watts), it can be left on without damage or significant expense.

No indicator light per se is used to indicate the power status. If any of the data and control lamps are on, then power must be on. If power is thought to be on and none of the data or control lamps are on, pushing the Clear Pushbutton will cause the Input Lamp to turn on if power is available. Also the Start, Read, Display, or the eight Data Pushbuttons can be used to test the power condition. The fan can also be heard when power is on.

When power is turned on, the Start Pushbutton should be depressed. If the computer stays in the Run state, then the Stop Pushbutton should also be depressed. These operations will initialize the internal control circuits.

#### Console Data Lamps

The eight Console Data Lamps receive their information from one of four sources as indicated by the Console Control Lamps, page PR-19. If the Input Lamp is On, the Console Data Lamps are displaying the contents of location  $377_8$  which is the location in memory where input is assembled. If the Address Lamp is On, the Console Data Lamps show the contents of the Address Register which is used for reading or storing data in the memory. If the Memory Lamp is On, the Console Data Lamps show the contents of a memory location which has been read. If the Run Lamp is On, or if none of the Control Lamps are On, the Console Data Lamps show the contents of location  $200_8$  which is assigned as the program output register.

Console Data Lamps Show

Contents of 377<sub>8</sub>

Contents of 2008

Contents of Address Register

Contents of Memory Location

When Control Lamp is On

Input

Run or None of the Control Lamps

Address

Memory

### Console Data Pushbuttons and Clear

The Clear Pushbutton erases the contents of location  $377_8$  to  $00\ 000\ 000$ . A Data Pushbutton sets the bit position in  $377_8$  which corresponds to its respective number. If a One is entered by mistake, Clear must be used to erase location  $377_8$  to  $00\ 000\ 000$  and the correct Ones must be re-entered. Between the entry of different bytes of information, Clear is used to erase the previous data.

Entry can occur during the Run state. Normally, the Console Data Lamps are displaying the contents of location  $200_8$  during the Run state. During the actual interval while the Clear or Console Data Pushbuttons are depressed, the Console Data Lamps will predominantly display the contents of location  $377_8$ . In the background, as a fainter light, the contents of location  $200_8$  will also be displayed. In the Run state, entry of data to location  $377_8$  must be accompanied by a stored program which will interpret and make use of the data.

In the Halt state, the data entered into  $377_8$  can be used to set the Address Register or it can be stored in the memory at locations determined by the Address Register.

# Address Control Lamp, Address Display and Set Pushbuttons

While the computer is halted, data may be entered or read from the memory where the address to be used is held in the Address Register.

Data is entered into the Address Register by the Address Set Pushbutton.

The source of this data is location 3778 which in turn is determined by the Clear and Console Data Pushbuttons. The contents of the Address Register may be caused to be displayed by the Address Display Pushbutton. This will be the next address. When reading or storing data in the memory, the contents of the Address Register are incremented by one for each depression of the Memory Read or Memory Store Pushbuttons.

When the computer goes into the Run state the value in the Address Register will be changed in an unspecified way.

# Memory Control Lamp, Memory Read and Store Pushbuttons

While the computer is in the Halt state, data may be examined (read) or be entered (stored) in the memory. This may be done one byte at a time. The memory location to be used is contained in the Address Register. For storing data, the source of the data is location 377<sub>8</sub>. In reading data, the Console Data Lamps will display the information. Each depression of the Read or Store Pushbutton will cause the Address Register to advance by one.

## Start and Stop Pushbuttons

After a program and data have been loaded into the memory, the computer can be made to go into the Run state by the Start Pushbutton. In the Run state, the computer is executing a stored program. The Run state will last until a Halt instruction is encountered or until the Stop Pushbutton is depressed.

The computer can be made to execute instructions one at a time, stopping after each instruction is finished. To do this, hold the Stop Pushbutton depressed and push and release Start. The Stop Pushbutton can then be released. The computer will have executed one and only one instruction.

If the P Register is examined while the computer is halted, it will show the address of the next instruction to be executed. Similarly, if the P Register is being loaded, it should be set with the address of the next instruction to be executed.

# Lamp Tests

To test whether a lamp is burned out push the Pushbutton in the table below. The lamp should light.

| To Test                                                                                                              | Push                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Lamp 0 Data Lamp 1 Data Lamp 2 Data Lamp 3 Data Lamp 4 Data Lamp 5 Data Lamp 6 Data Lamp 7 Input Address Memory | Data Pushbutton 0 Data Pushbutton 1 Data Pushbutton 2 Data Pushbutton 3 Data Pushbutton 4 Data Pushbutton 5 Data Pushbutton 6 Data Pushbutton 7 Clear Display (Address) Read (Memory) |

| Run                                                                                                                  | Start                                                                                                                                                                                 |

#### EXAMPLE OF CONSOLE USE

Load the program (all octal numbers)

|                                                                                                                       | Location Cont                                                                                                                              | <u>ents</u> <u>Symboli</u>                                                        | c Instruction                      |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------|

| LOOP                                                                                                                  |                                                                                                                                            | ADD B                                                                             | value of P Reg.<br>C=1             |

|                                                                                                                       |                                                                                                                                            | STORE B                                                                           | OUTPUT                             |

|                                                                                                                       |                                                                                                                                            | 14 JPD UI                                                                         | NC LOOP                            |

| OUTPUT                                                                                                                | 200 xx                                                                                                                                     | cx                                                                                |                                    |

| Steps:                                                                                                                |                                                                                                                                            |                                                                                   |                                    |

| 1. Power On 2. Start 3. Stop 4. Clear 5. Enter 003 6. Set (Address) 7. Clear 8. Enter 004 9. Store (Memory) 10. Clear | 11. Enter 10<br>12. Store<br>13. Clear<br>14. Enter 00<br>15. Store<br>16. Clear<br>17. Enter 13<br>18. Store<br>19. Clear<br>20. Enter 20 | 22. Cle<br>23. Ente<br>1 24. Stor<br>25. Cle<br>26. Ente<br>4 27. Stor<br>28. Dis | ar<br>er 344<br>ee<br>ar<br>er 004 |

Step 27 concluded the entry process. Step 28 is a double check that the Address Register has the correct value which in this case should be 012, the next address. To check the entry of the data, which is a good habit to get into, or in general, to examine memory proceed with

| 29. Clear                | 34. Read (should be 001) |

|--------------------------|--------------------------|

| 30. Enter 003            | 35. Read (should be 134) |

| 31. Set (Address)        | 36. Read (should be 200) |

| 32. Read (should be 004) | 37. Read (should be 344) |

| 33. Read (should be 103) | 38. Read (should be 004) |

To run the program

#### 39. Start

This program adds 1 to the B Register, puts the value of B out to location 200<sub>8</sub>, and hence the Data Lamps, and recycles or loops. The binary counting process should be in evidence on the Data Lamps though the lamps will be operating too fast in the lower order positions to observe the action in detail.

# SUMMARY OF INSTRUCTION CODING

| Instruction                      | First Byte Octal Digits                                  |                    |                                                        |                            |                                                    |                       |

|----------------------------------|----------------------------------------------------------|--------------------|--------------------------------------------------------|----------------------------|----------------------------------------------------|-----------------------|

|                                  | D                                                        |                    | -D-                                                    |                            | D                                                  |                       |

| Add, Sub,<br>Load, Store         | A Reg =<br>B Reg =<br>X Reg =                            | 0 1 2              | Add =<br>Sub =<br>Load =<br>Store =                    | 0<br>1<br>2<br>3           | Constant = Memory = Indirect = Indexed = Ind/Ind = | 3<br>4<br>5<br>6<br>7 |

| Or, And,<br>Lneg                 | 3                                                        |                    | Or = (Noop = And = Lneg =                              | 0<br>1)<br>2<br>3          | Constant = Memory = Indirect = Indexed = Ind/Ind = | 3<br>4<br>5<br>6<br>7 |

| Jumps                            | A Reg = B Reg = X Reg = Unc. =                           | 0<br>1<br>2<br>3   | JPD = JPI = JMD = JMI =                                | 4<br>5<br>6<br>7           | (≠0) =<br>(=0) =<br>(<0) =<br>(≥0) =<br>(>0) =     | 3<br>4<br>5<br>6<br>7 |

| Bit Test and<br>Manipulation     | Set to 0 = Set to 1 = Skip on 0 = Skip on 1 =            | 0<br>1<br>2<br>3   | Digit Valu<br>= Position                               |                            | 2                                                  |                       |

| Shifts, Rotates (one byte only)  | Right Shift = Right Rotates = Left Shift = Left Rotate = | 0<br>= 1<br>2<br>3 | A = B =plus 1 place = 2 places = 3 places = 4 places = | 0<br>4<br>1<br>2<br>3<br>0 | 1                                                  |                       |

| Miscellaneous<br>(one byte only) | Halt = 0 or<br>Noop = 2 or                               |                    | Any value                                              |                            | 0                                                  |                       |

| A B X ADD SUB LOAD STORE | 1<br>2<br>- 0 -<br>- 1 -<br>- 2 -<br>- 3 - | 0 0 0<br>0 0 1<br>0 0 2<br>0 0 3<br>2 0 0<br>3 7 7 |      | A B X P OUTPUT INPUT | PROGRAM REV<br>VERSION REV<br>PROGRAMMER<br>NOTES: | DATE                                             |

|--------------------------|--------------------------------------------|----------------------------------------------------|------|----------------------|----------------------------------------------------|--------------------------------------------------|

| OR A<br>NOOP<br>AND A    |                                            | roc                                                | DATA | SYMBOLIC ADDRESS     | CONTENTS                                           | COMMENTS                                         |

| LNEG A                   |                                            |                                                    |      |                      |                                                    |                                                  |

| IMMED                    | <b>3</b>                                   |                                                    |      |                      |                                                    | ·                                                |

| MEMORY                   | 4                                          |                                                    |      |                      |                                                    |                                                  |

| INDIRECT                 | <b>5</b>                                   |                                                    |      |                      |                                                    | <del></del>                                      |

| INDEXED                  | 6                                          |                                                    |      |                      |                                                    |                                                  |

| IND/XED                  |                                            |                                                    |      |                      |                                                    |                                                  |

| Α                        | 0                                          |                                                    |      |                      |                                                    |                                                  |

| В                        | 1                                          |                                                    |      |                      |                                                    |                                                  |

| X                        | 2                                          |                                                    |      |                      |                                                    |                                                  |

| UNC                      | 3                                          |                                                    |      |                      |                                                    |                                                  |

| JPD                      | <b>-4-</b>                                 |                                                    |      |                      |                                                    |                                                  |

| JPI                      | - 5 <del>-</del>                           |                                                    |      |                      |                                                    |                                                  |

| JMD                      | -6-<br>-7-                                 |                                                    |      |                      |                                                    |                                                  |

| JM I<br>≠ 0              | - <i>7</i> 3                               |                                                    |      |                      |                                                    |                                                  |

| ≠ 0<br>= 0               | <b>3</b>                                   |                                                    |      |                      |                                                    |                                                  |

| = 0<br>< 0               | _ <b>-</b> 5                               |                                                    |      |                      |                                                    | _                                                |

| > 0<br>≥ 0               | 6                                          |                                                    |      |                      |                                                    | <del></del>                                      |

| > 0<br>> 0               | <b>7</b>                                   |                                                    |      |                      |                                                    |                                                  |

| SET O                    | 0 B 2                                      |                                                    |      |                      |                                                    |                                                  |

| SET 1                    |                                            |                                                    |      |                      |                                                    |                                                  |

| SKIP 0                   | 2 B 2                                      |                                                    |      |                      |                                                    |                                                  |

| SKIP 1                   | 3 B 2                                      |                                                    |      |                      |                                                    | <del></del>                                      |

| B:BIT PO                 | SITION                                     |                                                    |      |                      |                                                    | _                                                |

| RT SFT                   | 0 - 1                                      |                                                    |      |                      |                                                    |                                                  |

| RT ROT                   | 1 - 1                                      |                                                    |      |                      |                                                    |                                                  |

| LFT SFT                  | 2 – 1                                      |                                                    |      |                      |                                                    |                                                  |

| LFT ROT                  | 3 — 1                                      |                                                    |      |                      |                                                    |                                                  |

| 1 PLC                    | <b>-1-</b>                                 |                                                    |      |                      |                                                    |                                                  |

| 2 PLC                    | -2-                                        |                                                    |      |                      |                                                    | <del></del>                                      |

| 3 PLC                    | <b>-3</b> -                                |                                                    |      |                      |                                                    |                                                  |

| 4 PLC                    | -0-                                        |                                                    |      |                      |                                                    |                                                  |

| B REG                    | +4                                         |                                                    |      |                      |                                                    |                                                  |

| NOOP                     | 200                                        |                                                    |      |                      |                                                    |                                                  |

| HALT                     | 000                                        | <b>}</b>                                           |      |                      |                                                    | <del>  -  </del>                                 |

| OF BO                    |                                            |                                                    |      |                      |                                                    | <del>  -</del>                                   |

| CA B1                    | 001                                        |                                                    | L    |                      |                                                    | <del>                                     </del> |

| A                        | 201                                        |                                                    |      |                      |                                                    |                                                  |

| B                        | 202                                        |                                                    |      |                      |                                                    |                                                  |