## **Operation and Maintenance Manual**

## Model 9100

# **Digital Tape Transport**

## KENNEDY

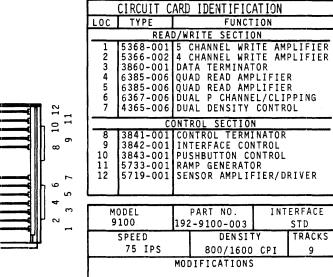

| ſ   | MODEL<br>9100 |     | PART NO.<br>2-9100-003 | INT | ERFACE<br>STD |   |

|-----|---------------|-----|------------------------|-----|---------------|---|

|     | SPEED         | 192 | DENSI                  | ſΥ  | TRACKS        | A |

|     | 75 IPS        |     | 800/1600               | CPI | 9             | ľ |

| - i | MODIFICATIONS |     |                        |     | l             |   |

|     |               |     |                        |     |               |   |

## CONTENTS

.

## SECTION I - APPLICATION DATA

| 1.1  | Introduction1-1                              |

|------|----------------------------------------------|

| 1.2  | Electrical and Mechanical Specifications 1-1 |

| 1.3  | Controls and Indicators1-5                   |

|      |                                              |

| 1.4  | Interface Connections1-7                     |

| 1.5  | Interface Signal Characteristics1-7          |

| 1.6  | Input Signal Description1-7                  |

| 1.7  | Output Signal Description1-7                 |

| 1.8  | Tape Motion Commands1-7                      |

| 1.9  | Interface Input Signals1-7                   |

|      | 1.9.1 Setup Commands1-7                      |

|      | 1.9.2 Tape Motion Commands1-10               |

|      | 1.9.3 Write Commands1-10                     |

|      | 1.9.4 Read Commands1-11                      |

|      | 1.9.5 Shutdown Commands1-11                  |

| 1.10 | Interface Output Commands1-11                |

|      | 1.10.1 Status Outputs1-11                    |

|      | 1.10.2 Read Outputs1-12                      |

| 1.11 | Station Select Switch1-12                    |

|      | Summary of Characteristics1-12               |

et.

## SECTION II - INSTALLATION AND OPERATION

| 2.1 | Installation                           |

|-----|----------------------------------------|

|     | 2.1.1 Inspection                       |

|     | 2.1.2 Mounting2-1                      |

|     | 2.1.3 Service Access                   |

|     |                                        |

|     | 2.1.4 Supplied Items/Required Items2-1 |

|     | 2.1.5 Intercabling                     |

|     | 2.1.6 Power Connections2-2             |

| 0 0 |                                        |

| 2.2 | Operation                              |

|     | 2.2.1 Interface                        |

|     | 2.2.2 Controls and Indicators2-2       |

|     | 2.2.3 Preliminary Procedures           |

|     |                                        |

|     | 2.2.4 Tape Threading                   |

|     | 2.2.5 Tape Loading2-3                  |

|     | 2.2.6 Placing Tape Unit On Line2-3     |

|     | 2.2.7 Tape Unloading and Rewind2-3     |

|     | 2.2.8 Power Shutdown                   |

|     |                                        |

#### **SECTION III - THEORY OF OPERATION**

| Introduction                            |

|-----------------------------------------|

| Tape Transport Control    3-1           |

| 3.2.1 Sequence Control                  |

| Write Operation                         |

| Read Operation                          |

| Test Panel                              |

| Tape Transport Control Adjustments3-5   |

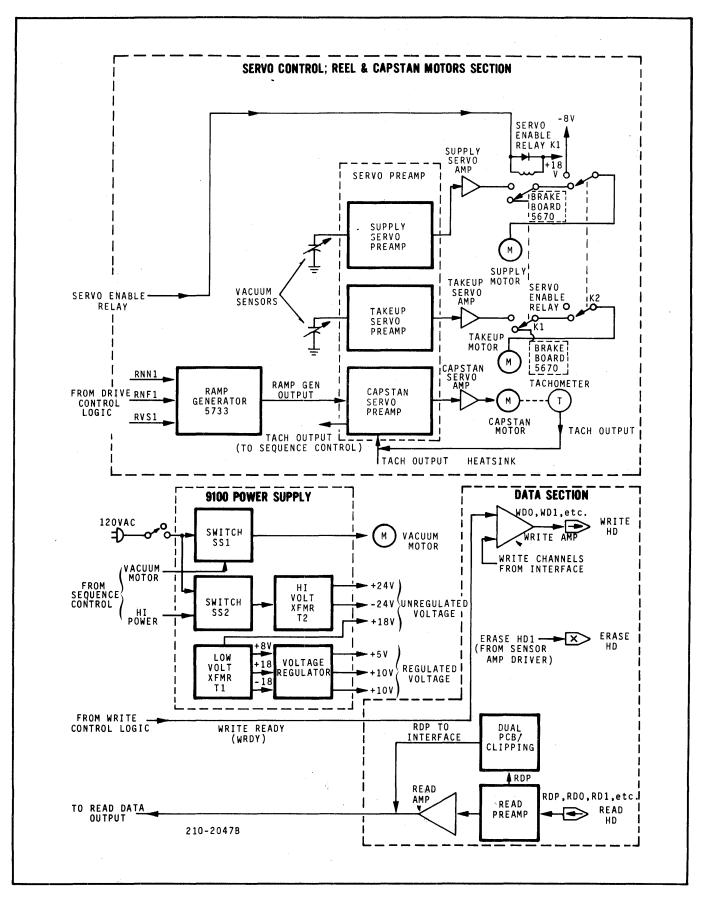

| Servo System                            |

| 3.7.1 Introduction                      |

| 3.7.2 Vacuum Sensors and Reel Servos3-5 |

| 3.7.3 Capstan Servo Amplifier           |

| 3.7.4 Servo System Adjustments3-6       |

| Data Section                            |

| 3.8.1 Introduction                      |

|                                         |

|     | 3.8.2 Write Electronics  | 3-6 |

|-----|--------------------------|-----|

|     | 3.8.3 Read Electronics   | 3-7 |

| 3.9 | Data Section Adjustments | 3-9 |

### SECTION IV - MAINTENANCE INSTRUCTIONS

i

| 4.1   | General                              | 4-1        |

|-------|--------------------------------------|------------|

| 4.2   | Preventive Maintenance               | 4-1        |

|       | 4.2.1 Daily Check                    | 4-1        |

|       | 4.2.2 Cleaning                       | 4-1        |

|       | 4.2.3 Visual Check                   |            |

| 4.3   | Routine Adjustment                   |            |

| 4.4   | Lubrication                          |            |

| 4.5   | Wear                                 |            |

| 4.5   | 4.5.1 Head Wear                      | 4-2        |

|       | 4.5.2 Guide Wear                     | 4-2        |

|       | 4.5.2 Guide wear                     | 4-2        |

|       | 4.5.3 Reel Hub Wear                  | 4-2        |

| 4.6   | Periodic Inspection                  |            |

| 4.7   | Test Panel Use                       | 4-2        |

|       | 4.7.1 Test Panel Use                 | 4-2        |

|       | 4.7.2 Operation                      | 4-5        |

| 4.8   | Hub O-Ring Adjustment                | 4-5        |

| 4.9   | Tape Path Mechanical Alignment       | 4-6        |

|       | 4.9.1 Reel Clearance Adjustment/     |            |

|       | Hub Replacement                      |            |

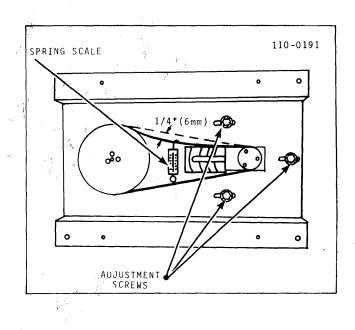

|       | 4.9.2 Capstan Parallelism            | 4-6        |

| 4.10  | Checking Supply Voltages             | 4-7        |

| 4.11  | Reel Servo Adjustment                | 4-7        |

|       | 4.11.1 Centering Adjustment          | 4-7        |

|       | 4.11.2 Gain Adjustments              | 4-7        |

| 4.12  | Vacuum Switch                        | 4-7        |

| 4.13  | Vacuum Column Adjustment             |            |

|       | Capstan Zero Adjustment              |            |

| 4.15  | EOT/BOT Sensor Adjustment            |            |

| 4.16  | Tape Speed Adjustment                | 4-9        |

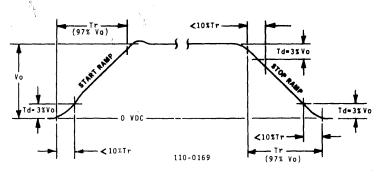

| 4.17  | Start/Stop Ramp Time Adjustment      | 4-9        |

| 4.18  | Rewind Speed                         | 4-10       |

| 4.19  | Read Level Adjustment                | 4-10       |

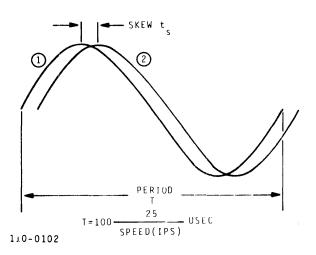

| 4.20  | Skew Adjustment                      | 4-10       |

| 1.20  | 4.20.1 Read Skew Adjustment          | 4-10       |

|       | 4.20.2 Write Skew Adjustment         |            |

| 4.21  | Head Face Shield Adjustment          |            |

| 4.22  | Blower Motor Belt Tension Adjustment | 4_11       |

| 4.23  | Troubleshooting                      | · · 4 - 11 |

| 4.20  | 4.23.1 High Error Rate               | 4 10       |

|       | 4.23.1 Angli Error Rate              |            |

|       | 4.23.2 Compatibility                 |            |

| 4 0 4 | 4.23.3 Other Malfunctions            |            |

| 4.24  | Parts Replacement                    |            |

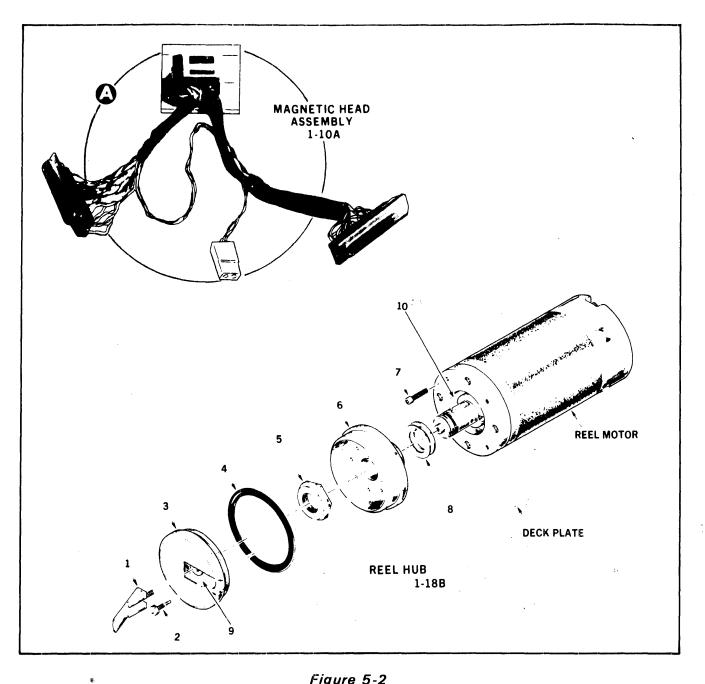

|       | 4.24.1 Hub Replacement               | 4-15       |

|       | 4.24.2 O-Ring Replacement            |            |

|       | 4.24.3 Reel Motor Replacement        | 4-15       |

|       | 4.24.4 Capstan Motor Replacement     |            |

|       | 4.24.5 Magnetic Head Replacement     |            |

|       | 4.24.6 EOT/BOT Sensor Replacement    | 4-15       |

|       | 4.24.7 Tape Cleaner Replacement      |            |

| 4.25  | Module Repair                        |            |

| 4.26  | Maintenance Tools                    |            |

## SECTION V - PARTS IDENTIFICATION

|     | Spare Parts Ordering Information5-1<br>In-Warranty Repair Parts Ordering |

|-----|--------------------------------------------------------------------------|

|     | Information                                                              |

| 5.3 | Export Orders                                                            |

|     | Illustrated Parts List                                                   |

|     | Field Kits                                                               |

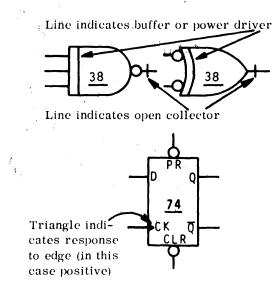

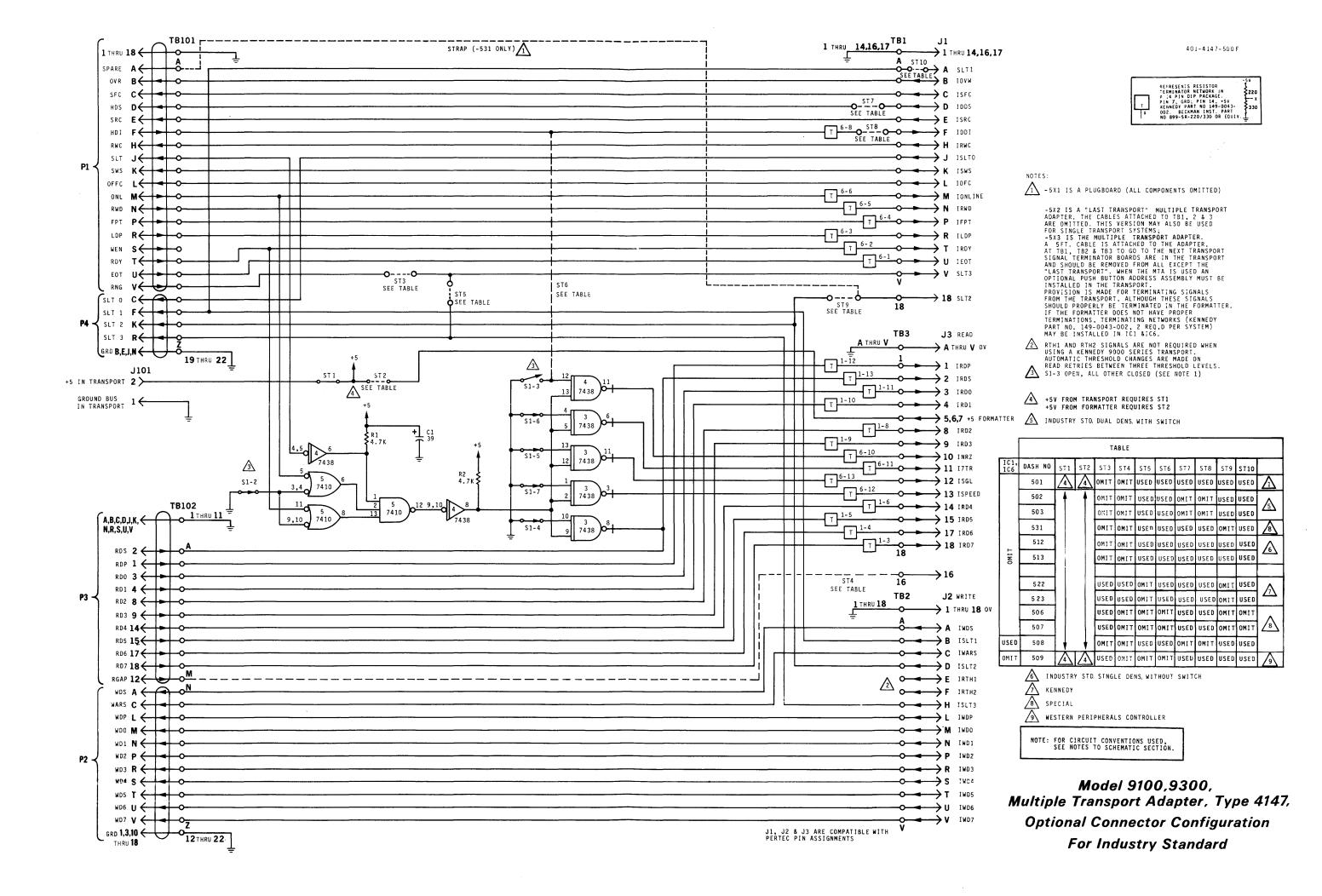

## SECTION VI – WIRING AND SCHEMATIC DIAGRAMS

| 1-1 | Outline and Installation1-3              |

|-----|------------------------------------------|

| 1-2 | Control Panel Controls and Indicators1-5 |

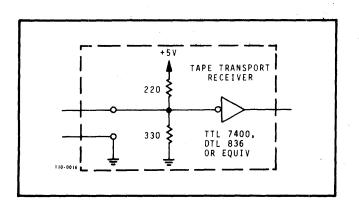

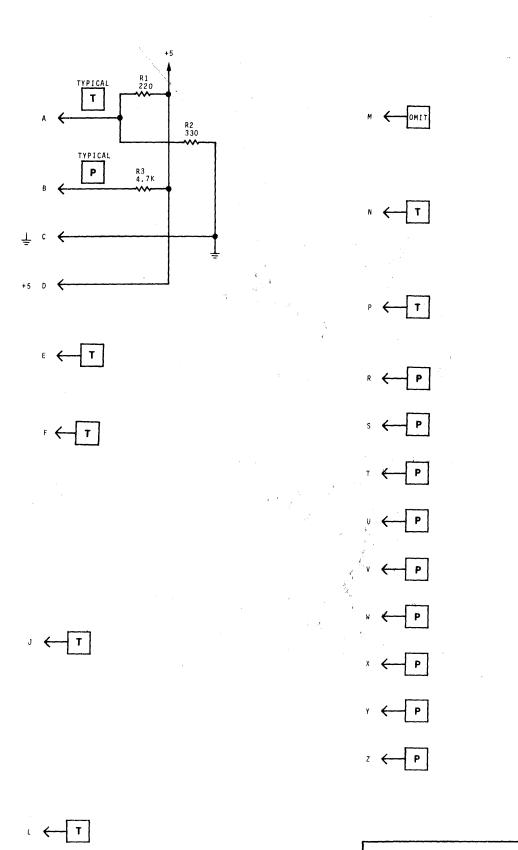

| 1-3 | Typical Receiver Circuit                 |

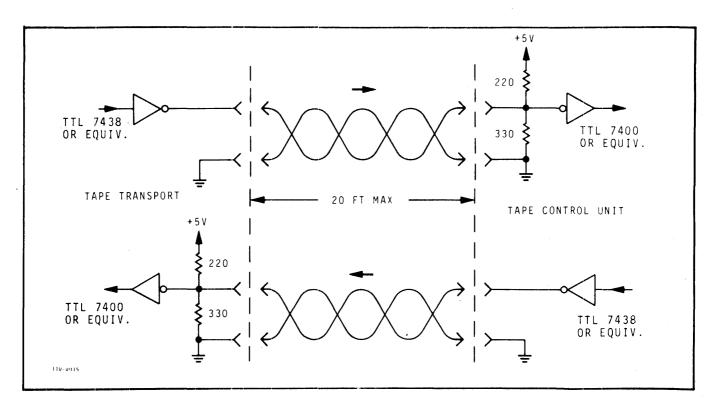

| 1-4 | Typical Interface Configuration1-8       |

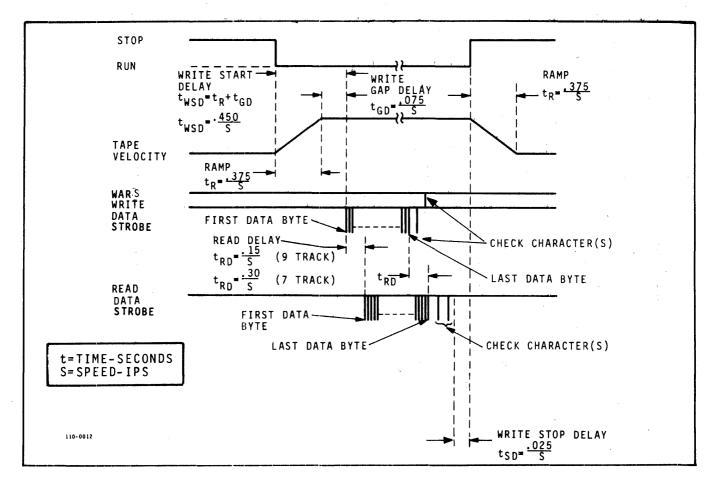

| 1-5 |                                          |

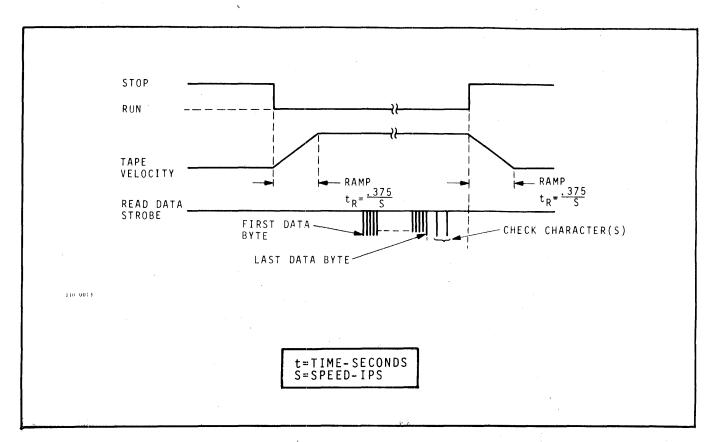

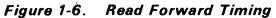

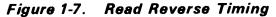

| 1-6 | Read Forward Timing1-9                   |

| 1-7 | Read Reverse Timing1-9                   |

| 1-8 | Summary of Interface Characteristics1-13 |

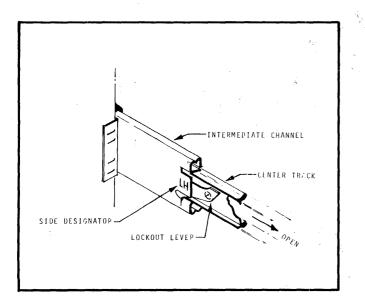

| 2-1 | Slide Identification                     |

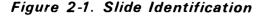

| 2-2 | Captive Screw Location                   |

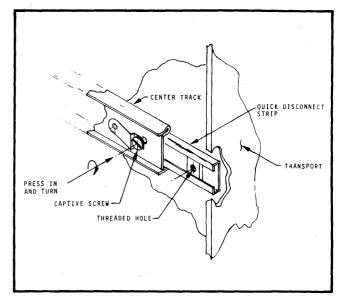

| 2-3 | Tape Threading Diagram2-2                |

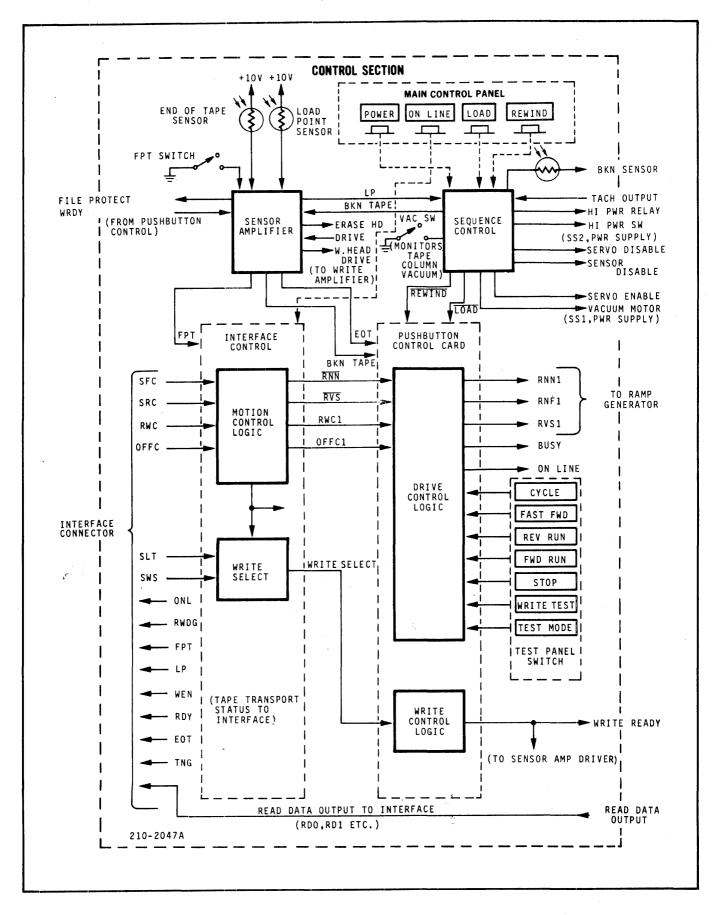

| 3-1 | Control Logic Block Diagram              |

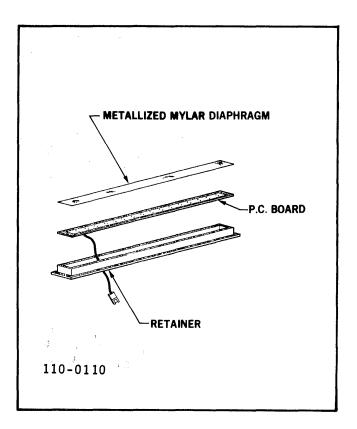

| 3-2 | Vacuum Sensor Assembly                   |

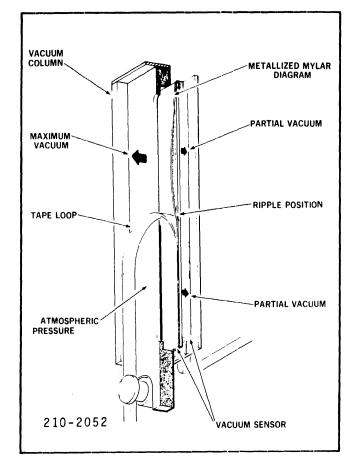

| 3-3 | Vacuum Sensor Operation                  |

| 3-4 | Write Data Section                       |

| 3-5 | Read Data Section                        |

| 4-1 | Opening of Head Shield4-1                |

| 4-1 | Test Panel Controls and Indicators4-4    |

| 4-4 |                                          |

# SECTION VII – GENERAL INFORMATION AND APPENDIX

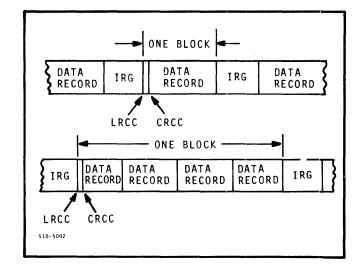

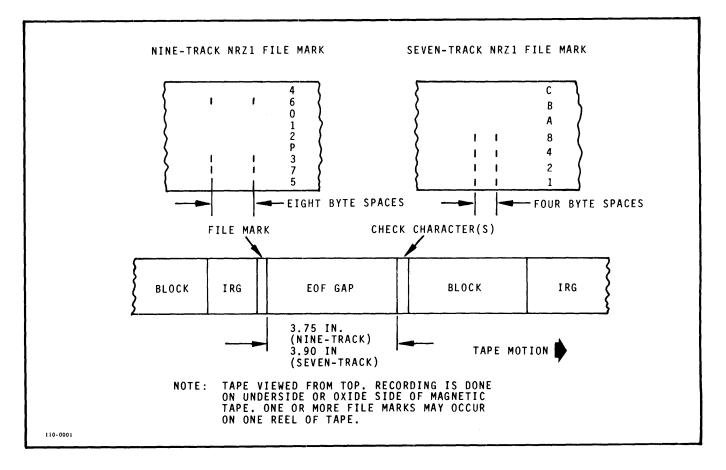

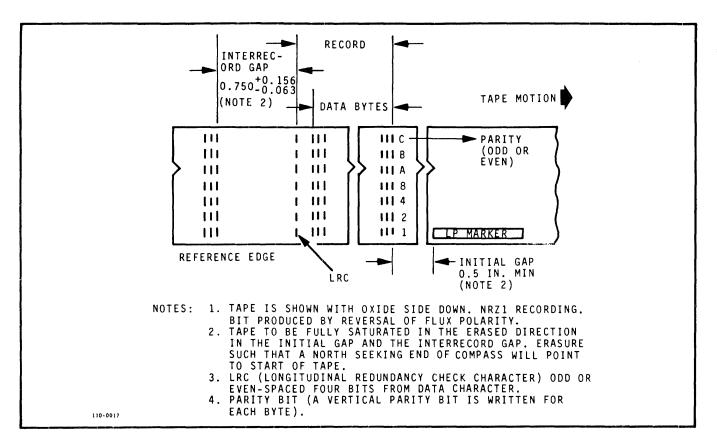

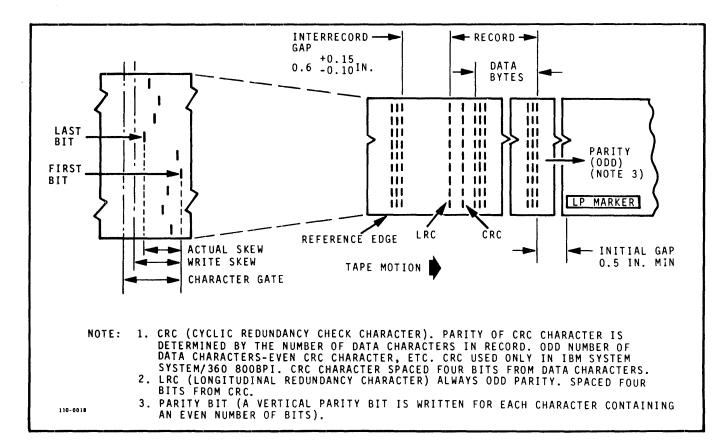

| Digital Recording on Magnetic Tape Using<br>NRZI Conventions and Format |

|-------------------------------------------------------------------------|

| Phase Encoded RecordingB-1                                              |

| Summary of Safety Precautions                                           |

| Recommended Tools/Test EquipmentC-1                                     |

## ILLUSTRATIONS

| 4-3 | Hub O-Ring Adjustment                     |

|-----|-------------------------------------------|

| 4-4 | Reel Hub Assembly                         |

| 4-5 | Capstan Parallelism Adjustment            |

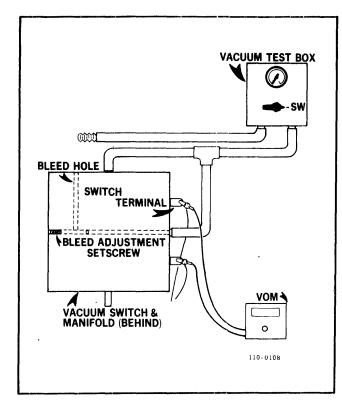

| 4-6 | Vacuum Switch Adjustment4-8               |

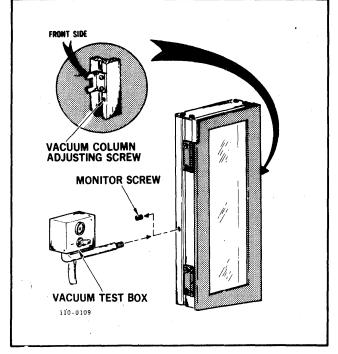

| 4-7 | Vacuum Column Adjustment4-8               |

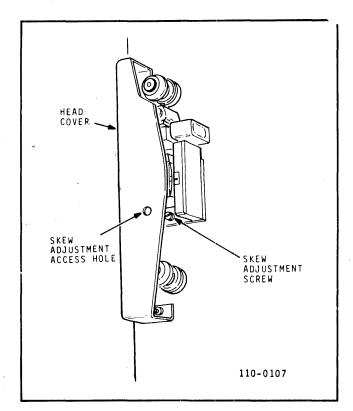

| 4-8 | Head Skew Adjustment                      |

| 4-9 | Blower Motor Belt Adjustment4-11          |

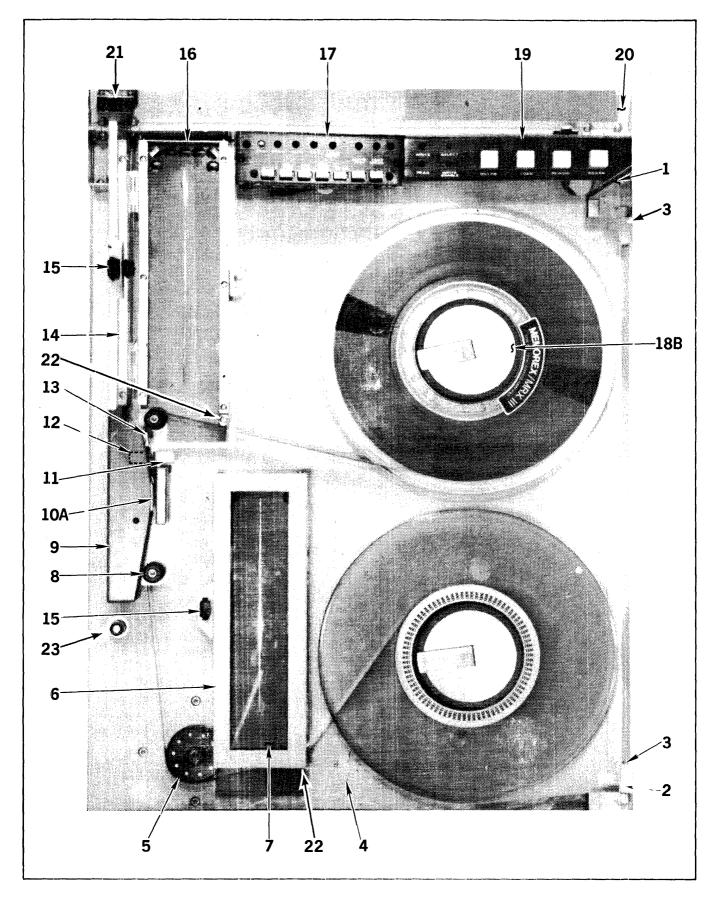

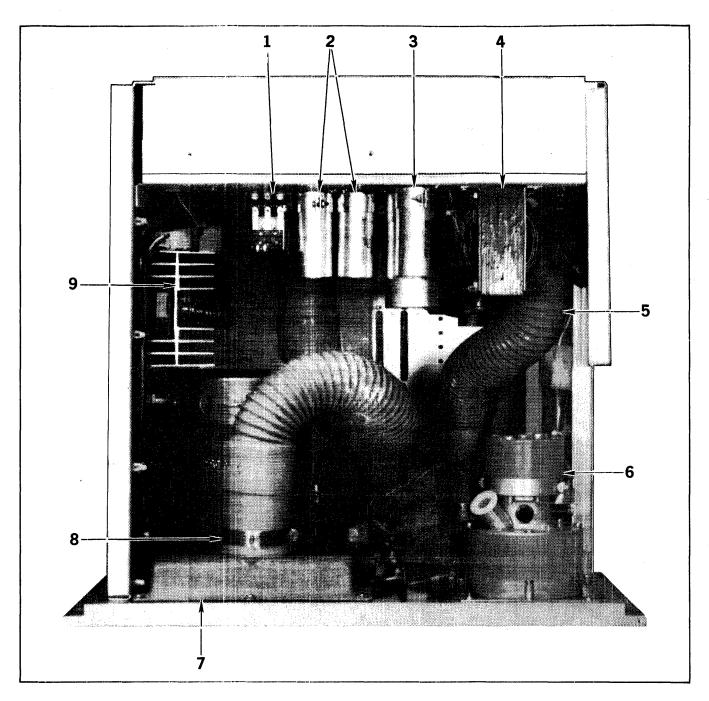

| 5-1 | Model 9100 Tape Transport: Front View5-2  |

| 5-2 | Parts Identification                      |

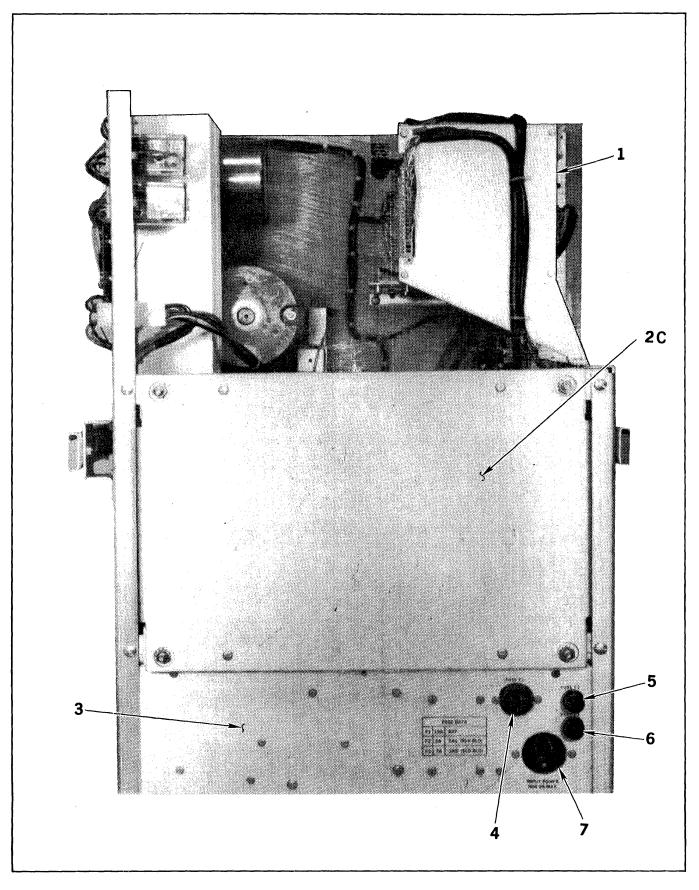

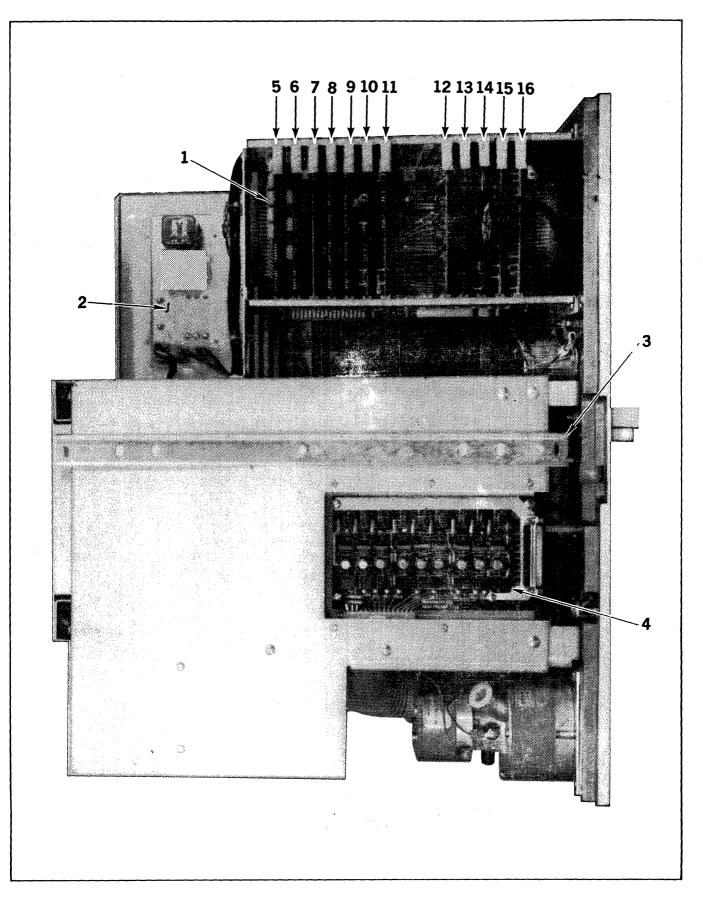

| 5-3 | Rear View: With Panel5-5                  |

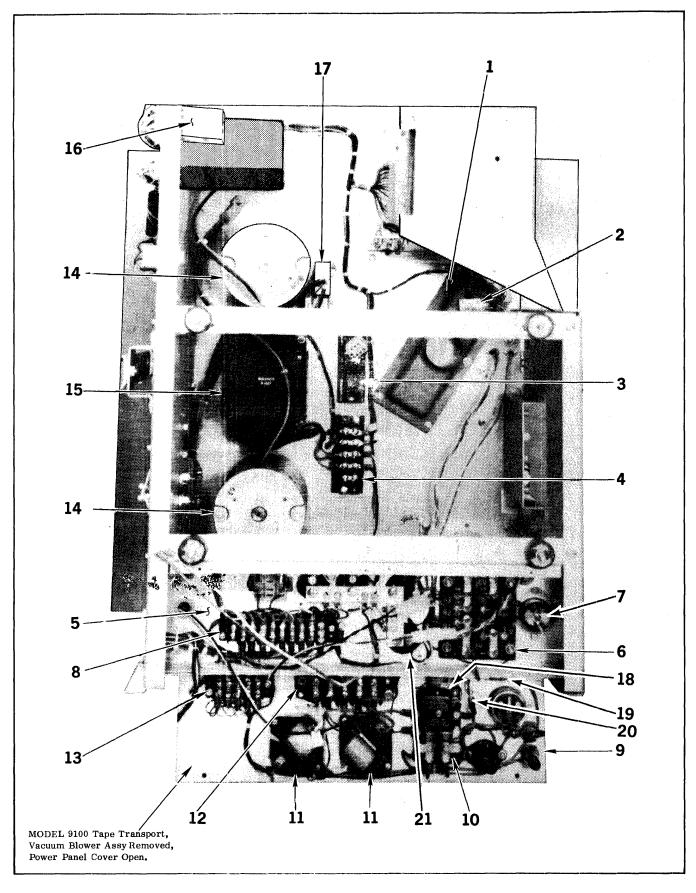

| 5-4 | Rear View: Without Panel                  |

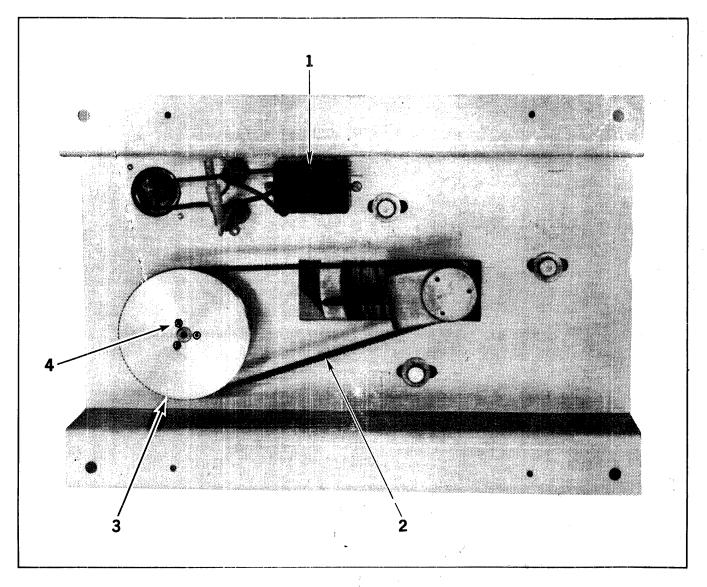

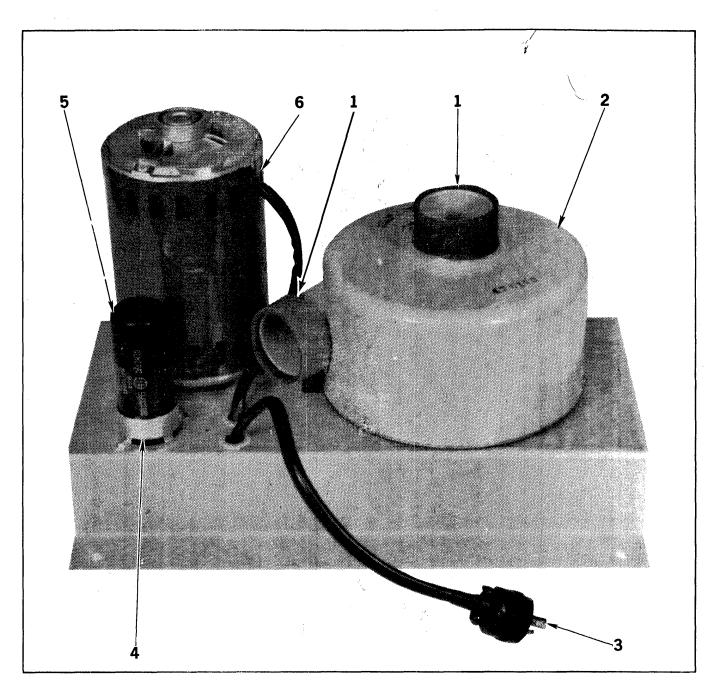

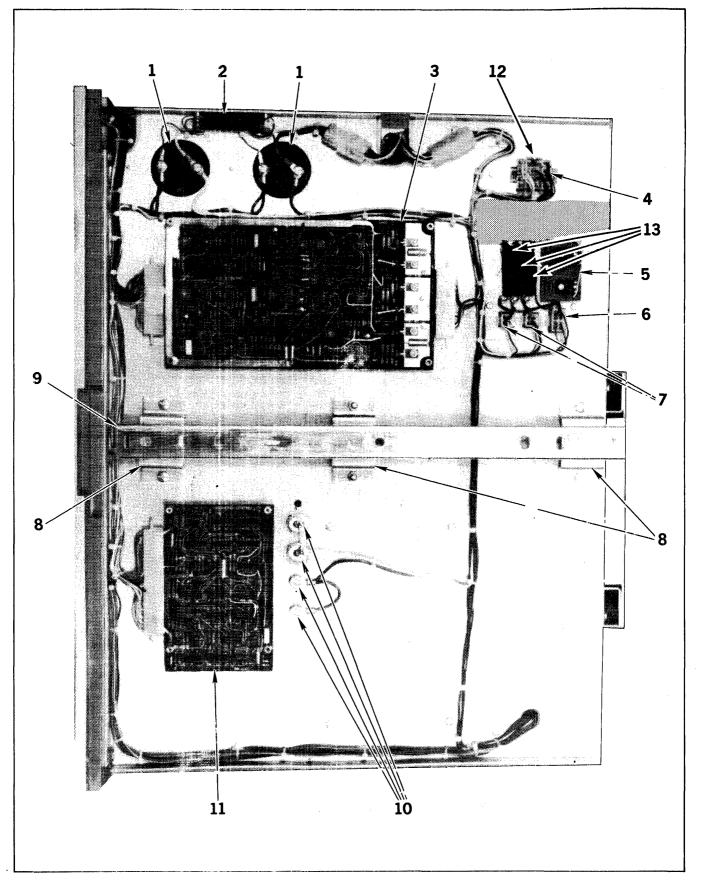

| 5-5 | Vacuum Blower Assembly: Bottom View5-8    |

| 5-6 | Vacuum Blower Assembly: Top View5-9       |

| 5-7 | Model 9100 Tape Transport:                |

|     | Bottom View                               |

| 5-8 | Model 9100 Tape Transport: Left Side5-11  |

| 5-9 | Model 9100 Tape Transport: Right Side5-12 |

## TABLES

## FCC NONCERTIFIED EQUIPMENT

<u>Warning</u>: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

# SECTION I APPLICATION DATA

### SECTION I

## APPLICATION DATA

## **1.1 INTRODUCTION**

The Kennedy Model 9100 is a synchronous digital magnetic tape unit that with proper external formatting control is capable of reading and writing IBM compatible tapes, and is used in applications requiring high reliability at moderate tape speeds. Typical applications include operation with mini computers as peripherals and high speed data collection systems.

The Model 9100 is equipped with the electronics necessary for reading and writing tapes and for controlling the tape motion. The head specifications and the mechanical and electrical tolerances of the Model 9100 meet the requirements for IBM compatibility. However, the formatting electronics, parity generator, cyclic redundancy check character(CRCC) generator, gap control, etc., are not included and must be provided by the tape control and formatter

#### **1.2 ELECTRICAL AND MECHANICAL SPECIFICATIONS**

in order to generate properly formatted IBM compatible tapes.

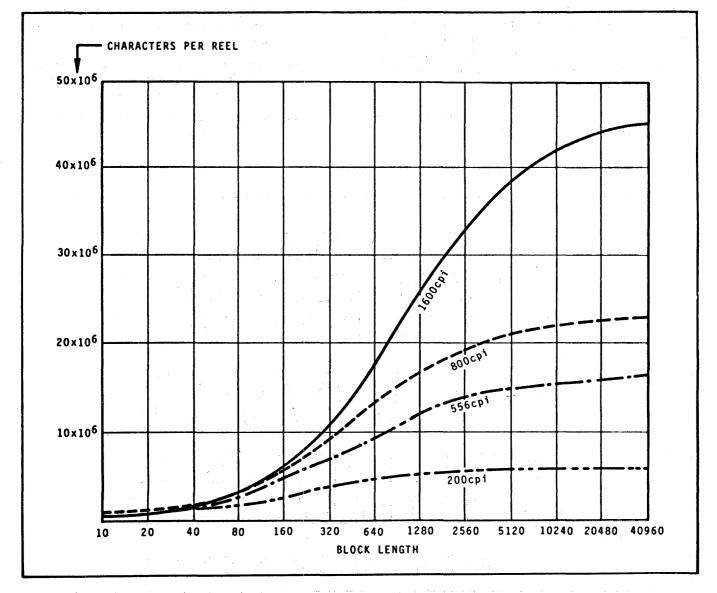

The standard Model 9100 is available in 7 or 9 track NRZI recording configurations, as well as the 9 track phase encoded configuration. Standard data recording densities are: 200/556 cpi or 556/800 cpi 7 track NRZI,800 cpi 9 track NRZI,1600 cpi 9 track phase encoded, 800/1600 cpi 9 track NRZI/ phase encoded, or 800/1600 cpi 9 track NRZI/ phase encoded, or 800/1600 cpi NRZI. A tape unit select switch is standard on 7 and 9 track models. A dual density switch is standard on 9 track dual density units.

The standard tape speed is 75 ips; however, tape speeds from 25-75 ips are available. The data transfer rate at 75 ips, 800 cpi is 60 kHz, or 120 kHz at 75 ips, 1600 cpi. Other options include power supply modification to accommodate foreign or dc line voltages, auto power restart, etc.

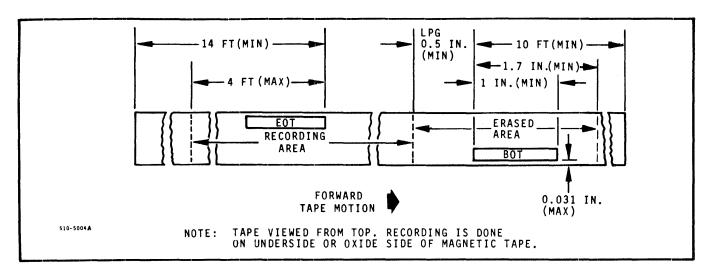

| Tape (computer grade)Width0.5 inch (1.27 cm)Thickness1.5 mil (0.038 mm)Tension8.0 ounces (227 gm)Reel diameterto 10.5 inches (26.6 cm)Capacity2400 feet (731.5 meters)Recl hub3.69 inches (9.37 cm) diaper IBM standards                                                                                                                                                                                                                | Erase headFull widthLoad point and end of tape reflective strip<br>detectionInfrared(IBM compatible)InfraredBroken tape detectionInfrared                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

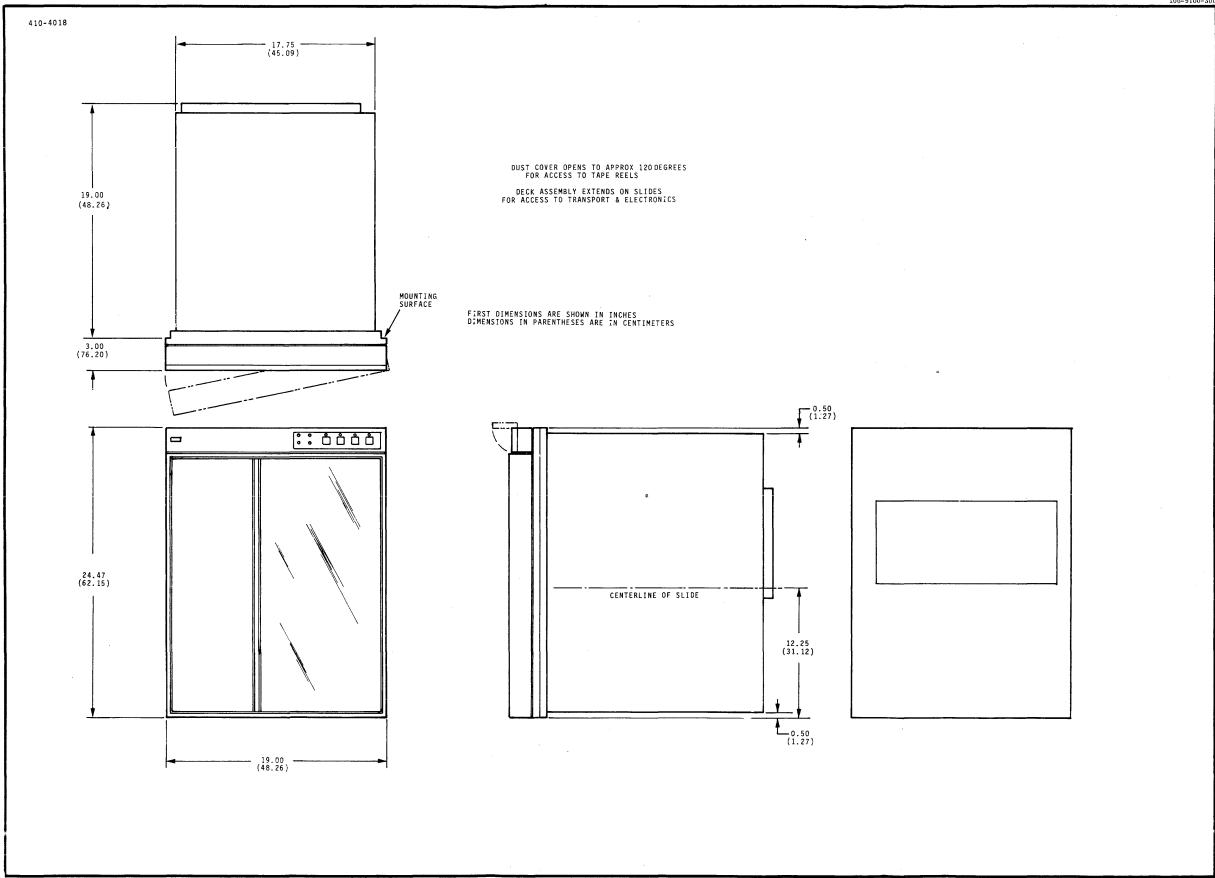

| Reel braking       Dynamic         Recording mode (IBM compatible)       NRZ1/PE         Tape drive       Single capstan         Tape speed       45-75 ips (114-190 cm/sec)         Instantaneous speed variation       ± 1%         Long term speed variation       ± 1%         Start/stop displacement       0.19 inch (0.476 cm)         Start/stop time @ 75 ips       5.0 ms         Rewind speed       200 ips (508 cm) nominal | Dimensions (see Figure 1-1)<br>Transport mounting (horizontal)<br>Standard 19-inch (48.26 cm) RETMA rack<br>Height 24.47 inches (62.15 cm)<br>Width 19.00 inches (48.26 cm)<br>Depth (from mounting surface)<br>19.0 inches (48.26 cm)<br>Depth (overall) 21.62 inches (54.91 cm)<br>Weight 150 pounds (67.95 kgm)<br>Shipping weight 200 pounds (75.43 kgm) |

| Magnetic head assembly<br>(Write to read gap displacement)<br>Dual gap 7 track read after write<br>Dual gap 9 track read after write<br>Dual gap 9 track read after write<br>Interchannel displacement error (measured<br>with IBM master skew tape PN 432362)<br>Write (maximum) 100 µinches (2.5 µm)<br>Read (maximum) 100 µinches (2.5 µm)                                                                                           | Operating environment<br>Ambient temperature                                                                                                                                                                                                                                                                                                                 |

Table 1-1. Electrical and Mechanical Specifications

106-9100-30CB

Figure 1-1. Model 9100 Outline and Installation Drawing

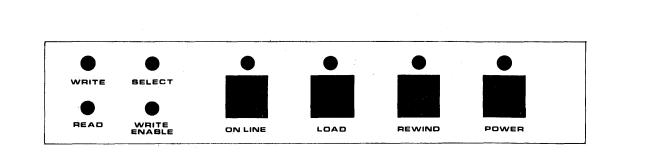

#### **1.3 CONTROLS AND INDICATORS**

WRITE INDICATOR. Illuminated when write status is selected.

READ INDICATOR. Illuminated when read status is selected.

SELECT INDICATOR. Illuminated when tape unit is on line and selected.

WRITE ENABLE INDICATOR. Illuminated whenever a reel with a write enable ring is mounted on the supply hub.

ON LINE. A momentary pushbutton, which functions as alternate action. When first activated the tape unit is placed in an on-line condition; when the tape unit is on line it can be remotely selected and will be ready if tape is loaded to or past the load point. When activated again it takes the tape unit off line. The indicator is illuminated in the on-line condition. LOAD. The momentary pushbutton activates the reel servos (tensions tape) and starts the load sequence. The indicator is illuminated when the reel servos are activated and tape is tensioned.

REWIND. The momentary pushbutton activates a rewind operation. This control is enabled only when tape is tensioned and unit is off line. The indicator is illuminated during either a local or remote rewind operation. Pressing the REWIND pushbutton at load point initiates the unload sequence.

## NOTE

LOAD and REWIND pushbuttons are disabled when the tape unit is on line.

POWER. The ON/OFF switch applies power to the tape transport.

## Figure 1-2. Control Panel Controls and Indicators

#### NOTE

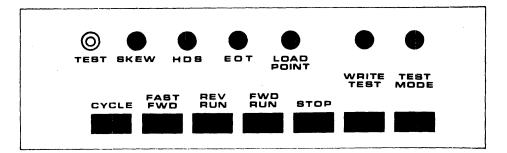

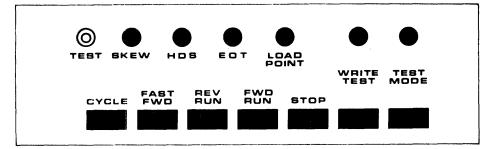

Tape transport must be off line and STOP pushbutton depressed before test panel can become functional.

TEST point and SKEW indicator. Indicator lights if tape skew exceeds the appropriate skew (read or write) gate setting. An oscilloscope test point is available for monitoring skew gate timing.

HDS indicator. Indicates that high density mode has been selected.

EOT indicator. Indicates when tape has reached or passed end of tape.

LOAD POINT indicator. Indicates when tape is at load point.

CYCLE pushbutton. An interlocked pushbutton which runs tape in alternating forward and reverse modes. Useful for making ramp or vacuum sensor adjustments. Depressing STOP pushbutton terminates this operation.

FAST FORWARD pushbutton. An interlocked pushbutton switch that allows tape unit to run forward at fast speed. Depressing STOP pushbutton or EOT marker terminates this operation.

REVERSE RUN pushbutton. An interlocked pushbutton switch that allows tape unit to run in reverse at normal speed. Depressing STOP pushbutton or load point marker terminates this operation.

FORWARD RUN pushbutton. An interlocked pushbutton switch that allows tape unit to proceed forward at normal speed. Depressing STOP pushbutton or EOT marker terminates this operation.

STOP pushbutton. An interlocked pushbutton switch that terminates all tape motion.

WRITE TEST pushbutton and indicator. A momentary pushbutton which programs 1's to be written on all channels to facilitate write skew adjustment. WRITE TEST remains active in FORWARD RUN mode only. (STOP pushbutton must be depressed and TEST MODE selected to actuate this feature.) The indicator remains illuminated while unit is in this mode.

TEST MODE pushbutton and indicator. A momentary pushbutton selects test mode and activates test panel. When indicator is illuminated, test panel is active. (Tape unit must be off line and STOP pushbutton depressed before test panel will function.)

## **Test Panel Controls and Indicators**

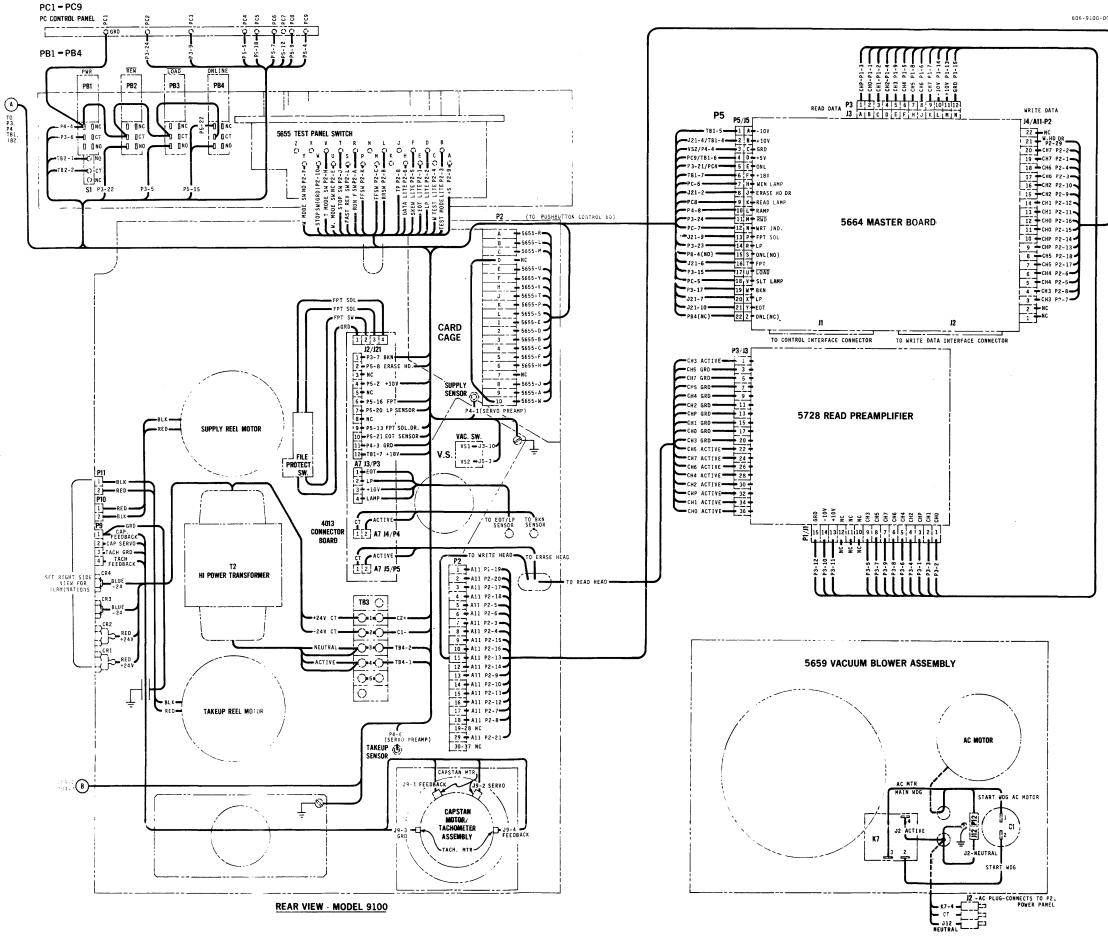

#### **1.4 INTERFACE CONNECTIONS**

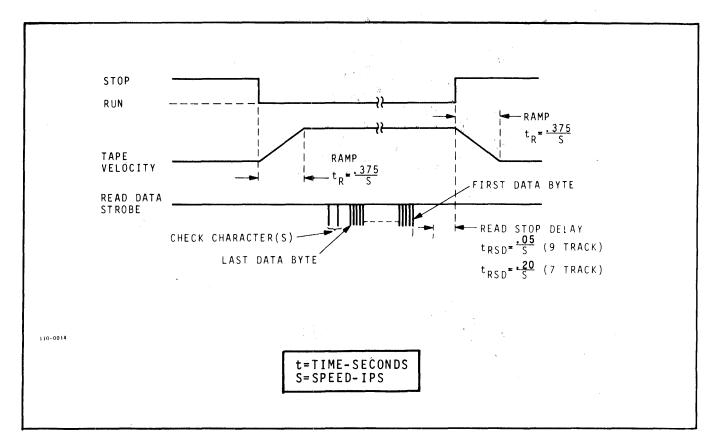

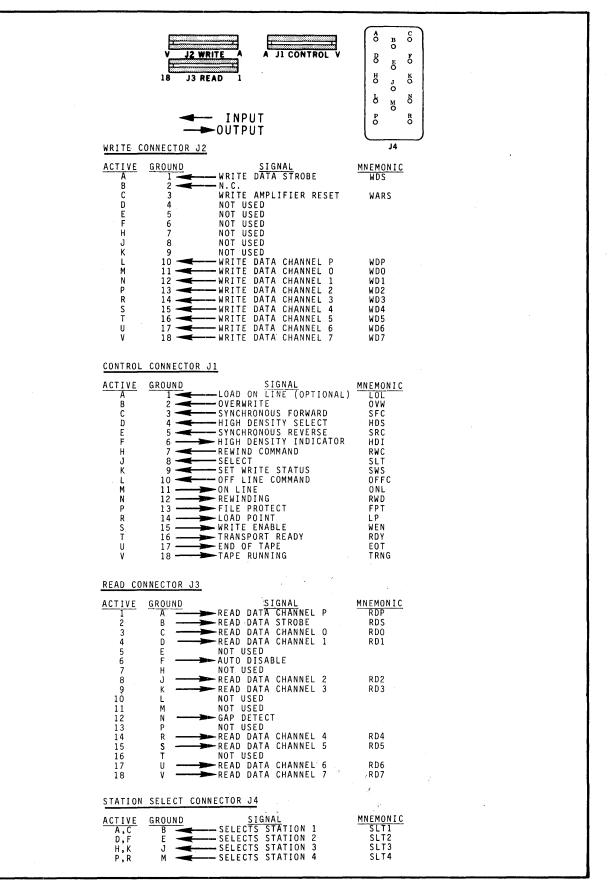

The interface connectors on the Model 9100 are designed for twisted pair inputs and outputs. For each active pin there is a ground pin. The mating interface connectors, three 36-pin edge connectors (PN 121-0096) are supplied with the tape unit.

#### **1.5 INTERFACE SIGNAL CHARACTERISTICS**

The tape unit responds to zero true inputs and provides zero true outputs. Each signal input is terminated in such a manner as to provide matching for twisted pair cables. See Figure 1-3. Each output line is driven with an open collector driver. For best results the typical interfacing circuit configurations shown in Figure 1-4 should be used. The recommended twisted pair cable will reduce the magnitude of intercable crosstalk. Unless otherwise specified all wires should be 24 AWG minimum, with a minimum insulation thickness of 0.01 inch. Each pair should have not less than one twist per inch and the input-output cables should not exceed 20 feet in length.

#### **1.6 INPUT SIGNAL DESCRIPTION**

The input receiver circuits, due to zero true current sinking logic design, will interpret a disconnected wire or removal of power at the transmitter as a logic 0 or false condition. The logic 1 or true state requires 25 ma current sink with less than 0.4v.

The logic 0 or false state will be 3v due to the input matching resistors (see Figure 1-3). The recommended input pulse width is 2 microseconds. The rise and fall times for pulses and levels must be less than 0.5 microsecond. Each input is enabled when the tape transport is on line and selected.

Figure 1-3. Typical Receiver Circuit

#### **1.7 OUTPUT SIGNAL DESCRIPTION**

Each output line is driven with an open collector current sinking logic driver which is capable of sinking up to 40 ma in the true state. All outputs are disabled (false) when the tape unit is not on line or not selected.

### **1.8 TAPE MOTION COMMANDS**

For maximum interface convenience, Model 9100 is configured to control tape motion and direction using the SYNCHRONOUS FORWARD command and SYN-CHRONOUS REVERSE command. The tape transport capstan servo accelerates the tape to the required speed with a linear ramp. The tape is also decelerated to a stop with a linear ramp. Start and stop occurs within the interrecord gaps. The ramp time is 5 ms for 75 ips and varies inversely with tape speed. The amount of tape travel during the ramp up or ramp down is always 0.19 inch.

These two factors are to be taken into consideration when writing and gapping. A delay is required before writing to insure that tape is up to speed and to allow read after write. Timing diagrams for pertinent commands to provide properly formatted tapes are shown in Figures 1-5 through 1-7.

Figure 1-5 shows the timing requirements for writing a block in a read after write system (dual gap head) in the write mode with read occurring immediately after writing. Figure 1-6 shows the timing requirements for reading a block in the forward direction. Figure 1-7 shows the timing requirements for reading a block on a read after write system in the reverse direction.

#### **1.9 INTERFACE INPUT SIGNALS**

All commands from and to the input/output connector are preconditioned by loading tape and placing the tape unit on line using the front panel controls. The next commands set up the recorder.

1.9.1 SETUP COMMANDS

#### TRANSPORT SELECT

| SLT Level | P1-J |

|-----------|------|

|-----------|------|

A level that when true enables all the interface drivers and receivers in the transport, thus connecting the transport to the controller. Transport must also be on line, and SLT must be true for entire sequence (until tape motion stops). The SLT level may be removed to disconnect the machine from the system. The read or write status will remain in the last established condition.

Figure 1-4. Typical Interface Configuration

Figure 1-5. Write Timing

## DATA DENSITY SELECT

| (Dual Density only) |       |      |

|---------------------|-------|------|

| DDS                 | Level | P1-D |

Used when the TRANSPORT DENSITY SELECT switch is in the remote position. When true, this level selects the high read density (dual density).

1.9.2 TAPE MOTION COMMANDS

OVERWRITE (OPTIONAL) OVW Level P1-B

A level that when true conditions appropriate circuitry in the transport to allow updating (rewriting) of a selected record. The transport must be in the write mode of operation to utilize the OVW feature.

| SYNCHRONOUS | FORWARD COMMAND |      |

|-------------|-----------------|------|

| SFC         | Level           | P1-C |

A level that when true, and the transport is ready and on line, causes tape to move forward at the specified speed. When the level goes false, tape motion ramps down and ceases.

#### SYNCHRONOUS REVERSE COMMAND

SRC

Level

P1-E

P1-H.

A level that when true, and the transport is ready and on line, causes tape to move in a reverse direction at the specified speed. When the level goes false, tape motion ramps down and ceases. If the load point marker is detected during a SRC, the SRC will be terminated. If a SRC is given when the tape is at load point, it will be ignored.

#### REWIND COMMAND

continue normally.

RWC

Pulse

A pulse input will rewind the tape past the load point and stop. The transport will then initiate a load forward sequence and return the tape to the load point marker. This input will be accepted only if the load point output is false. The transport may be taken off line while rewind is still in process. Rewind will

#### 1.9.3 WRITE COMMANDS

#### SET WRITE STATUS SWS Level P1-K

A level that must be true at the leading edge of a SFC (or RUN and FWD) when the write mode of operation is required, and must remain true for a minimum of 10  $\mu$ sec after the leading edge of the SFC (or RUN and FWD). SWS is sampled at the leading edge of the SFC (or RUN and FWD), toggling the read/write flip-flop to the appropriate state. Internal interlocks in the tape unit will prevent writing in the reverse direction, when the write enable ring is missing, when the tape unit is off line, when loading to load point, and during a rewind.

#### WRITE DATA INPUTS

| <u>Nine Track</u> | Seven Track |              |

|-------------------|-------------|--------------|

| WDP               | WDC         | P2-L         |

| WD0               |             | <b>P2-</b> M |

| WD1               |             | P2-N         |

| WD2               | WDB         | <b>P2-P</b>  |

| WD3               | WDA         | P2-R         |

| WD4               | WD8         | P2-S         |

| WD5               | WD4         | P2-T         |

| WD6               | WD2         | <b>P2-</b> U |

| WD7               | WD1         | <b>P2-</b> V |

Nine lines for nine-track operation, seven lines for seven-track operation. These are levels that if true at WDS time will result in a flux transition being recorded on tape (transport is in the write mode). Inputs must remain quiescent 0.1  $\mu$ sec beyond the trailing edge of the WDS pulse. The CRCC is written by providing the correct data character together with a WDS four character times after the last data character of the record.

The LRCC is written using the WARS signal. The LRCC can also be written by providing the correct data character together with a WDS. If the LRCC is written (DATA-WDS) in this manner a WARS should be given one character time after the LRCC to insure proper IRG erasure in case of data input error.

#### WRITE DATA STROBE

WDS

WARS

P2-A

A pulse of 1  $\mu$ sec nominal width for each character to be written. Writing occurs on the trailing edge of the WDS. WDS may be a 1  $\mu$ sec minimum, 1.5  $\mu$ sec maximum pulse. Data inputs must have settled for at least 0.1  $\mu$ sec before the leading edge of WDS and remain quiescent for at least 0.1  $\mu$ sec beyond the trailing edge.

Pulse

#### WRITE AMPLIFIER RESET

Pulse

P2-C

A pulse of 1  $\mu$ sec nominal width that, when true, resets the write amplifier circuits on the leading edge which is delayed internally by the write deskewing network. The purpose of this line is to enable writing of the longitudinal redundancy check character (LRCC) at the end of a record. This insures that all tracks are properly erased in an interrecord gap (IRG). In a seven-track system, the leading edge of the WARS pulse should be four character times after the leading edge of the WDS associated with the last data character in the block. In a nine-track system, the leading edge of the WARS pulse should be eight character times after the leading edge of the WDS associated with the last data character in the block (four character times after the CRCC is written).

#### 1.9.4 READ COMMANDS

The tape unit will always have read selected. When write is selected (SWS) the data just written will be read back using a high threshold level on the read amplifiers. When SWS is false the normal threshold is applied to the read amplifiers.

#### AUTOMATIC CLIPPING LEVEL DISABLE ACLD Level

When true this level overrides the automatic clipping level electronics and holds the read electronics in the normal clipping level. The switching between read and write clipping levels is not affected.

#### 1.9.5 SHUTDOWN COMMANDS

The use of a given magnetic tape unit may be terminated by an OFF LINE command. Once this command is given the tape unit may be returned to an interface command only by operating the front pahel ON LINE switch.

#### OFF LINE COMMAND OFF C Pulse P1-L

A level or pulse (minimum width 1  $\mu$ see) that resets the on-line flip-flop to the zero state, placing the transport under manual control. It is gated only by SELECT in the transport logic, allowing an OFFC to be given while a rewind is in progress. An OFFC should be separated from a rewind command by at least 2  $\mu$ sec.

### 1.10 INTERFACE OUTPUT SIGNALS

All output signals are enabled only when the tape transport is ON LINE and SELECTED.

#### 1.10.1 STATUS OUTPUTS

#### ON LINE

| ONT | · · · · | 134 87 |

|-----|---------|--------|

| ONL | Level   | P1-M   |

A level that is true when the on-line flip-flop is set. When true, the transport is under remote control. When false, the transport is under local control.

### TRANSPORT READY

RDY

Level P1-T

A level that is true when the tape transport is on tape; that is, when the initial load sequence is complete and the transport is not rewinding. When true, the transport is ready to receive a remote command.

#### HIGH DENSITY INDICATOR

| (Dual Density only) |       |       |

|---------------------|-------|-------|

| HDI                 | Level | P1- F |

A level that is true only when the high-density mode of operation is selected.

#### **FILE PROTECT**

| FPT |  | Level | P1- P |

|-----|--|-------|-------|

|     |  |       |       |

A level that is true when a reel of tape without a write-enable ring is mounted on the transport supply (or file) hub.

#### WRITE ENABLE

P3-6

| WEN Level | P1-S |

|-----------|------|

|-----------|------|

A level that is true when a reel of tape with a writeenable ring is mounted on the transport supply (or file) hub. Opposite of file protect.

#### LOAD POINT

| LDP |  |

|-----|--|

|-----|--|

| Level | P1-R |

|-------|------|

A level that is true when the load point marker is under the photosensor and the transport is not rewinding. After receipt of a SFC the signal will remain true until the load point marker leaves the photosense area.

#### TAPE RUNNING

This is a level that is true when tape is being moved under capstan control and remains true until tape motion has ceased. (Includes forward, reverse, and rewind tape motion.)

#### END OF TAPE

| EOT |  |

|-----|--|

|-----|--|

P1-U

A level that is true when the EOT marker is detected in the forward direction. Goes false when the EOT marker is detected in reverse (SRC or REWIND).

Level

| REWINDING |       |      |

|-----------|-------|------|

| RWD       | Level | P1-N |

A level that is true when the transport is engaged in a rewind operation or returning to the load point at the end of the rewind operation.

#### 1.10.2 READ OUTPUTS

Read outputs are present at all times. The high threshold level is selected internally when SWS is selected.

Pulse

#### **READ DATA STROBE**

RDS

P3-2

(Not used in phase encoded operation)

ration)

A pulse for each data character read from tape in NRZ1. The average time  $(\tau_1)$  between two read data strobes is

$$\tau_1 (\text{sec}) = \frac{1}{s \cdot d}$$

Read clock pulse width  $(t_w)$  is

$$t_{w} = \frac{1}{s \cdot d \cdot 32} = \frac{\tau}{32}$$

where

s = tape speed in inches per second

d = density characters per inch

The minimum time between consecutive read data strobes is less than this figure owing to skew and bit crowding effects. A guaranteed safe value for the minimum time is  $1/2 \tau_1$ .

#### **READ GAP DETECT**

**R**GAPLevelP3-12(Not used for phase encoded operation)

A level that is true approximately 20 character spacings after the last data byte (16 character spacings on seven-channel), and remains true until the first data byte of the subsequent data block. Note: This level will be true whenever tape motion is at rest.

#### READ DATA LEVEL (NRZ1 MODE)

| Nine Track | Seven Track |              |

|------------|-------------|--------------|

| RDP        | RDC         | P3-1         |

| RD0        |             | P3-3         |

| RD1        |             | P3-4         |

| R D2       | RDB         | <b>P3-</b> 8 |

| R D3       | RDA         | P3-9         |

| RD4        | RD8         | P3-14        |

| RD5        | RD4         | P3-15        |

| RD6        | RD2         | P3-17        |

| RD7        | RD1         | P3-18        |

Nine lines, nine track; seven lines, seven track. These lines may be strobed by either edge of the read clock and remain true for 1/64 of a character time following the trailing edge of the read clock. Note: A CRC character may be all zeros, which will not cause a read clock.

#### 1.11 STATION SELECT SWITCH

The station select unit on the front panel of the Model 9100 is wired as shown in Figure 1-8. When using the station select switch, disconnect the SELECT line connected to J1-J of the Model 9100.

#### 1.12 SUMMARY OF CHARACTERISTICS

Figure 1-8 shows the location of connectors and pin numbers with signal names.

#### 106-9101-300C

Figure 1-8. Summary of Interface Characteristics

## SECTION II

# INSTALLATION AND OPERATION

SECTION II

#### SECTION II

#### INSTALLATION AND OPERATION

#### 2.1 INSTALLATION

#### 2.1.1 INSPECTION

Prior to installation, inspect thoroughly for foreign material that may have become lodged in the vacuum columns, reel hubs, and other moving parts.

#### 2.1.2 MOUNTING

Physical dimensions and outline of the tape transport are shown in Figure 1-1. The transport requires 24.5 inches vertical mounting space on the standard 19 inch rack. The transport is mounted on a pair of slides which are attached to the rack. The slides are equipped with a lockout mechanism, shown in Figure 2-1, that prevents their overextension. The lockout mechanism is gravity activated, requiring each slide to be mounted on the side of the cabinet for which it was designed, as indicated on the slide. To ascertain that the slides are mounted correctly, open one slide (of the pair) and look for the letters RH (right hand) or LH (left hand) stamped directly above the lockout lever on the forward portion of the intermediate channel, as shown in Figure 2-1. The slide designated RH should be mounted on the right hand side of the cabinet when facing the unit. With the right and left hand slides securely fastened to the cabinet and in extended position, align the quick disconnect strips attached to the sides of the transport with the center track of the slides, as shown in Figure 2-2. Push transport towards cabinet until fully engaged.

#### CAUTION

To avoid personal injury and/or transport damage due to dropping of unit, secure transport in place by aligning captive screws on each slide with the respective threaded holes in the disconnect strips and tighten, as shown in Figure 2-2.

Figure 2-2. Captive Screw Location

#### 2.1.3 SERVICE ACCESS

Access to the plug-in cards and control electronics is available with the unit extended on slides from the sides. The voltage regulator and the servo power assembly are mounted on the inside of the heatsink on the side of the transport. The fuses, power connector, and interface connectors are also accessible from the rear of the unit. For servicing electronics, test points are provided by standoff pins on circuit boards and are identified by upper case letters near each test point.

#### 2.1.4 SUPPLIED ITEMS/REQUIRED ITEMS

All required items except the twisted pair interface cables are supplied with the unit. These required items and their part numbers include:

Empty 10.5 inch reel (113-0008-001)

Three 36 pin interface connectors (order three 121-0082-002)

Winchester Address Select Connector w/pin (121-0108-001; 121-0082-002)

Power Cord (121-9000-003)

Shipping Brace (291-4768-001) (Shipping brace should be removed before use and saved in case the machine is to be shipped in the future.)

Set of rack mount slides (128-0151-003)

#### 2.1.5 INTERCABLING

Installation of the tape transport requires fabrication of interconnection cables between the tape controller and the tape transport. The three 36 pin cable connectors that mate with the connectors on the units are supplied with the system.

The connector pin assignments are shown in Figure 1-8. Twisted pair cabling should be used to reduce intercable crosstalk. All wires should be 24 AWG minimum insulation thickness of 0.01 inch. Each pair should have no less than one twist per inch, and maximum cable length should not exceed 20 feet.

#### 2.1.6 POWER CONNECTIONS

#### CAUTION

Before connecting the unit to the power source, make certain the line voltage is correct (115 or 230 vac) and that proper fuses have been installed.

A detachable power cord is supplied with the tape unit. The power cord is 7.5 feet long and has a NEMA three-prong (two power, one chassis ground) plug for connection to the power source.

#### 2.2 OPERATION

#### 2.2.1 INTERFACE

Before placing the unit in operation, make certain that the interface connection procedures outlined in Section I have been performed.

#### 2.2.2 CONTROLS AND INDICATORS

Paragraph 1.3 lists the controls and indicators for the tape transport and describes the functions of each. The test panel controls are described in Section IV.

#### 2.2.3 PRELIMINARY PROCEDURES

Before placing the unit in operation, proceed as follows:

- a. Check the tape transport read/write head, erase head, capstan and idlers for any foreign material.

- b. Check for correct line voltage and make sure that correct fuses are installed (paragraph 2.1.5).

- c. Push primary power switch on control panel to ON position.

#### 2.2.4 TAPE THREADING

To thread the tape on the transport, proceed as follows:

- a. Raise the latch of the quick-release hub and place the tape file reel to be used on the supply hub (Figure 2-3) with the write enable ring side next to the transport deck.

- b. Hold the reel flush against the hub flange and secure it by pressing the hub latch down.

- c. Thread the tape along the path as shown on the threading diagram (Figure 2-3).

- d. Holding the end of the tape, wrap a few clockwise turns around the takeup reel hub.

Figure 2-3. Tape Threading Diagram

#### 2.2.5 TAPE LOADING

Pressing the LOAD pushbutton energizes the reel servos and initiates a load sequence. Tape advances to the load point marker and stops. If for some reason the load point marker is already past the sensor as, for example, when restoring power after a shutdown, tape continues to move for approximately 6 seconds and then initiates rewind automatically.

Once pressed, the LOAD switch is illuminated and remains illuminated until power has been turned off or tape is removed from the machine.

#### 2.2.6 PLACING TAPE UNIT ON LINE

After the tape is properly threaded and has been loaded and brought to the load point, press the ON LINE pushbutton and make certain the ON LINE indicator illuminates. (The REWIND pushbutton is disabled when the tape unit is on line.) On-line status enables the tape unit to be remotely selected and to perform all normal operations under remote control.

#### 2.2.7 TAPE UNLOADING AND REWIND

Provision is made in the 9000 series transports for rewinding a tape to load point under remote control. However, this operation may also be performed manually. Proceed as follows:

a. If the ON LINE indicator is illuminated, press the ON LINE pushbutton. The ON LINE indicator should extinguish when pressure is removed.

- b. Press the REWIND pushbutton. The tape will now rewind to the load point marker.

- c. After the tape has been positioned at the load point under remote or local control, press the REWIND pushbutton to rewind the tape past load point to the physical beginning of the tape.

#### NOTE

The rewind sequence cannot be stopped until the tape has rewound either to load point or until tape is rewound onto the supply reel after an unload sequence.

#### 2.2.8 POWER SHUTDOWN

A tape transport should not be turned off when tape is loaded and is past the load point marker. Kennedv 9000 series transports are designed to prevent physical damage to the tape in the event of power failure, and to minimize operator error which could destroy recorded data. In the event of power failure during tape unit operation, manually wind the tape forward several feet before restoring power. When power has been restored, press the LOAD pushbutton. If load point is not reached within 36 feet, the tape will rewind, searching for load point. If desired, the tape can then be advanced to the data block nearest the point at which the power failure occurred by initiating the appropriate control commands.

Although it is possible to develop procedures which would allow power shutdown between tape files and tape records this is not recommended. Where data files are short, it is preferable to use smaller tape reels.

## SECTION III

÷

# THEORY OF OPERATION

### SECTION III

## THEORY OF OPERATION

#### 3.1 INTRODUCTION

This section describes the Model 9100 tape transport at the functional block level. The description applies to the standard dual density 800/1600 cpi, nine track, 75 ips version. Detailed circuit descriptions are included in the schematic section of the manual.

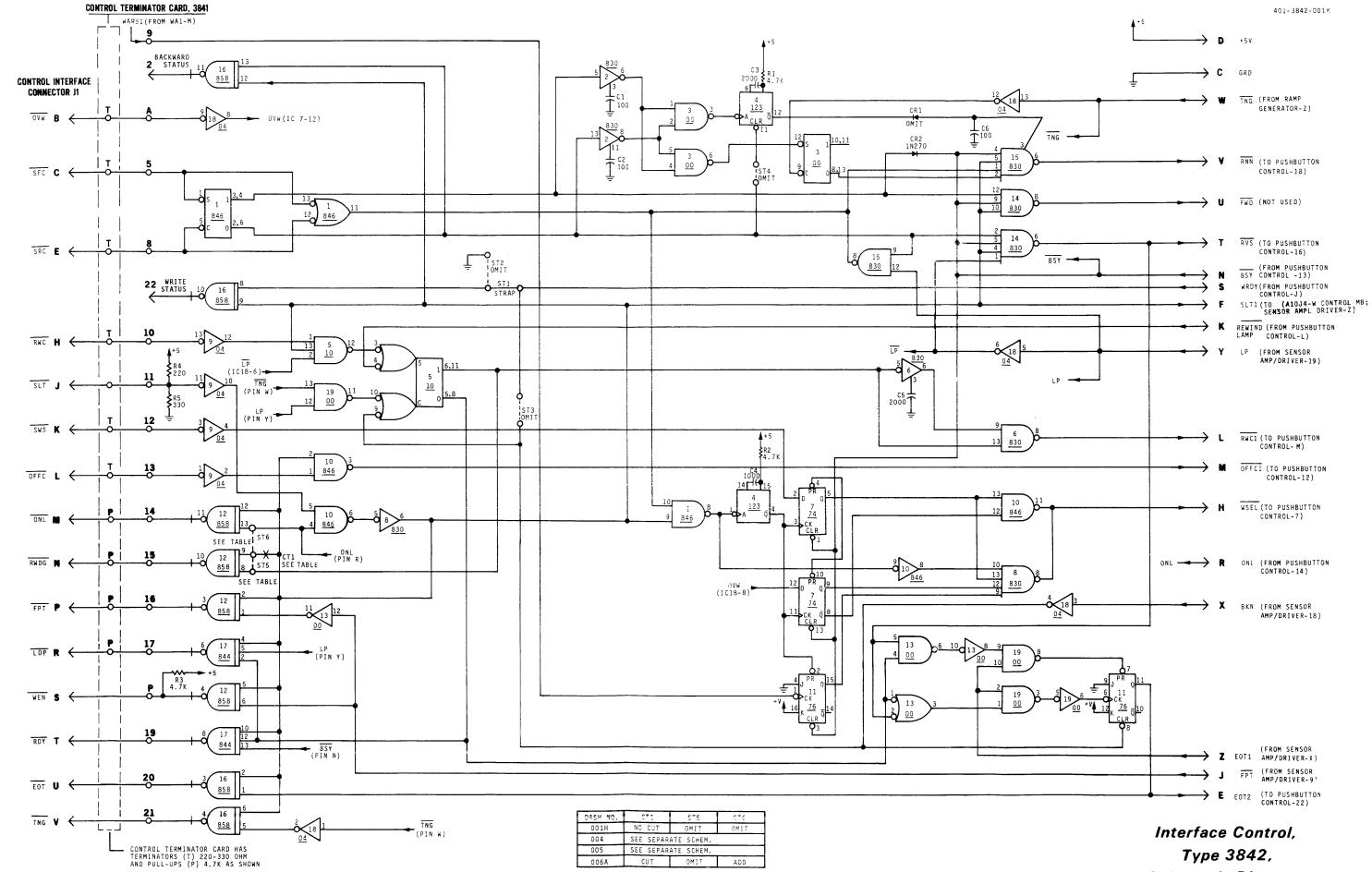

#### 3.2 TAPE TRANSPORT CONTROL

The circuit boards in the control section of the card cage control the tape transport by generating internal tape transport commands which are based upon commands from the interface, as well as status signals from the tape transport.

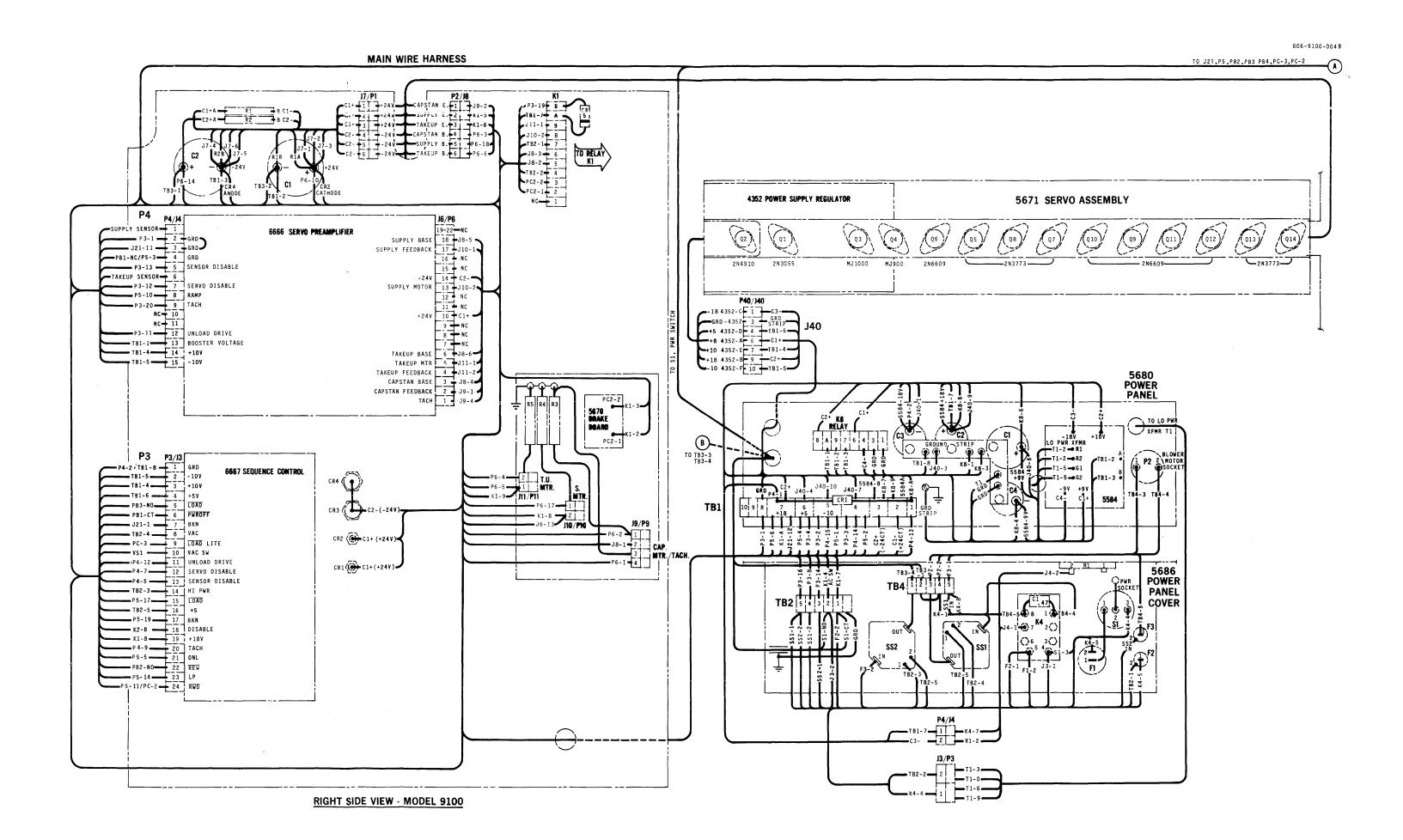

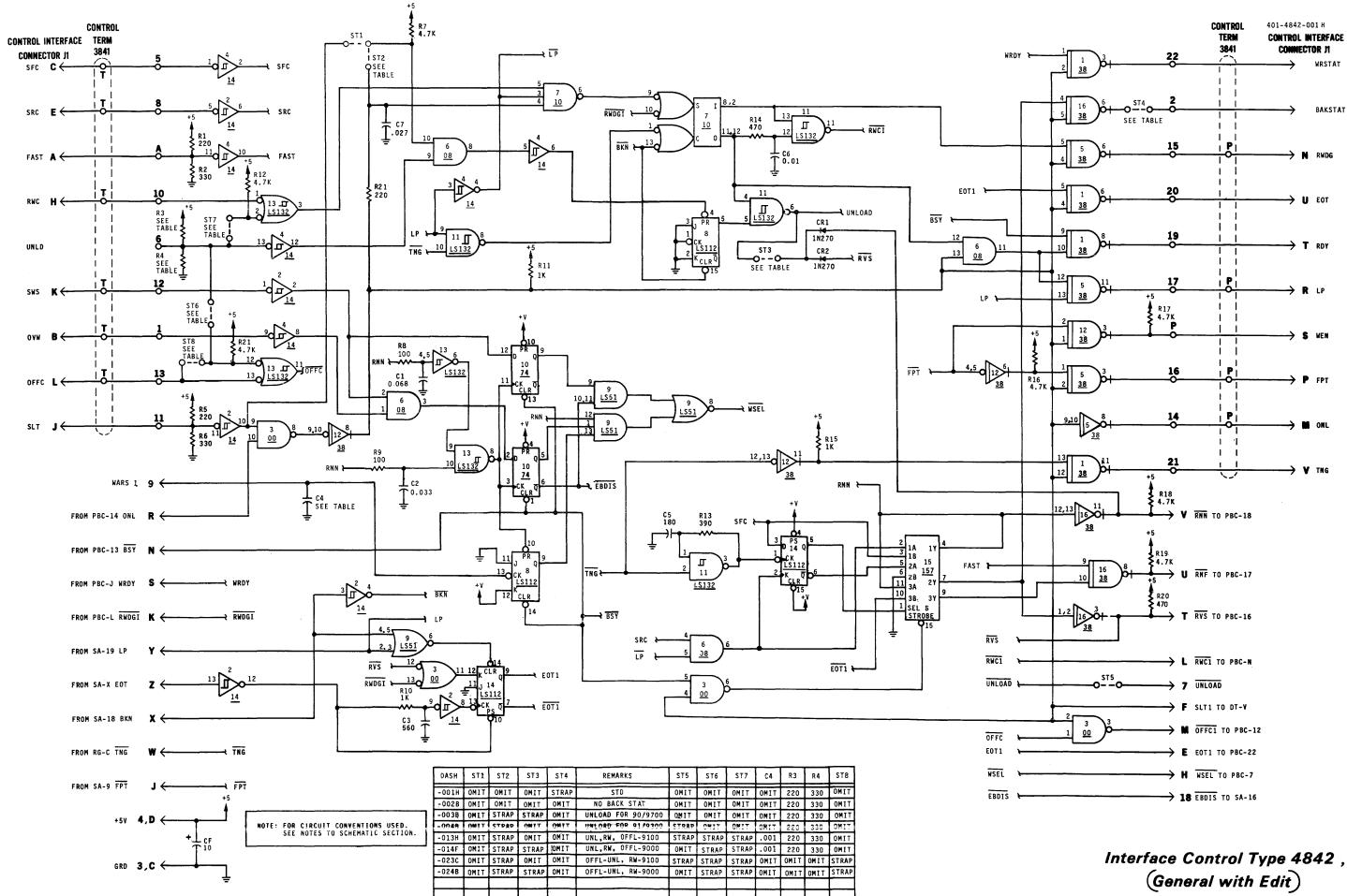

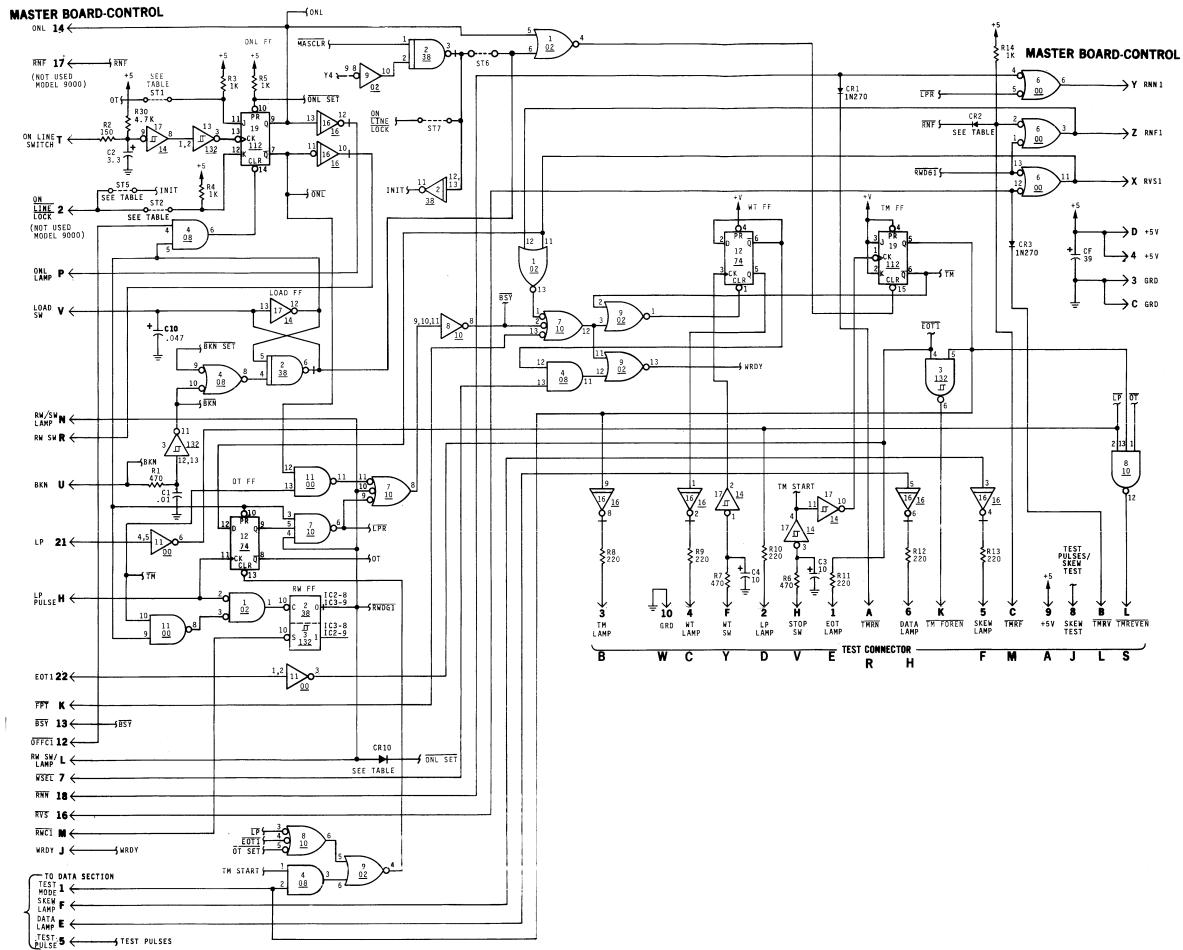

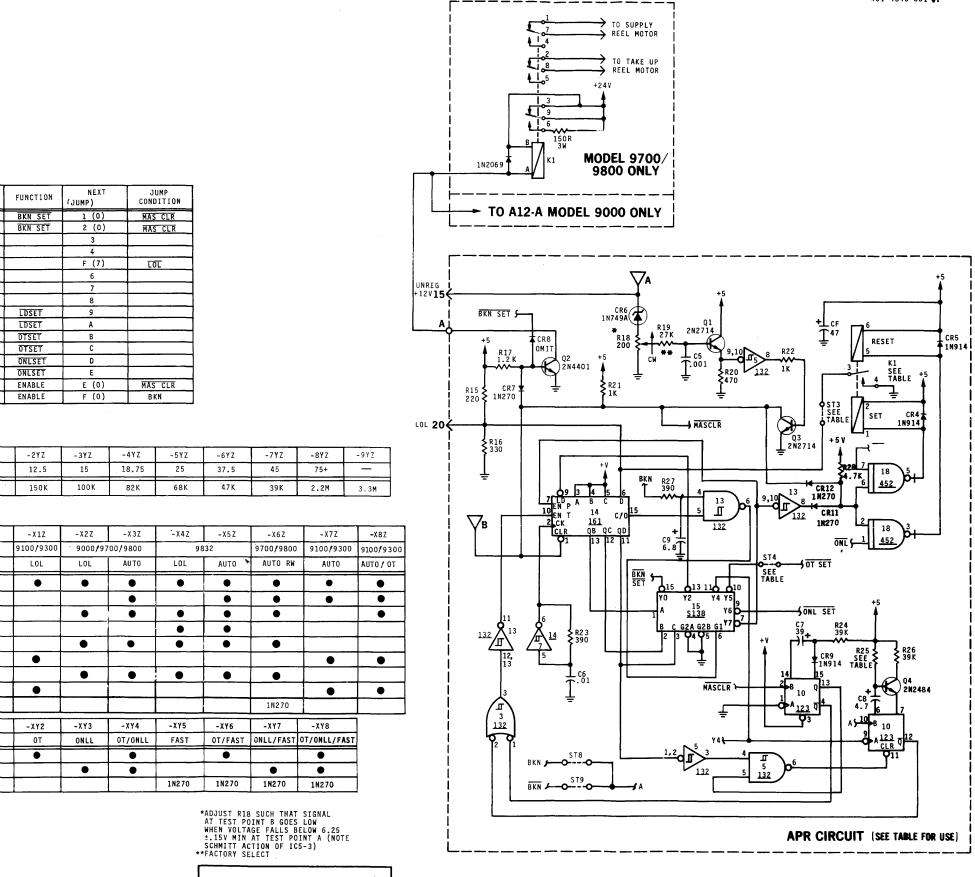

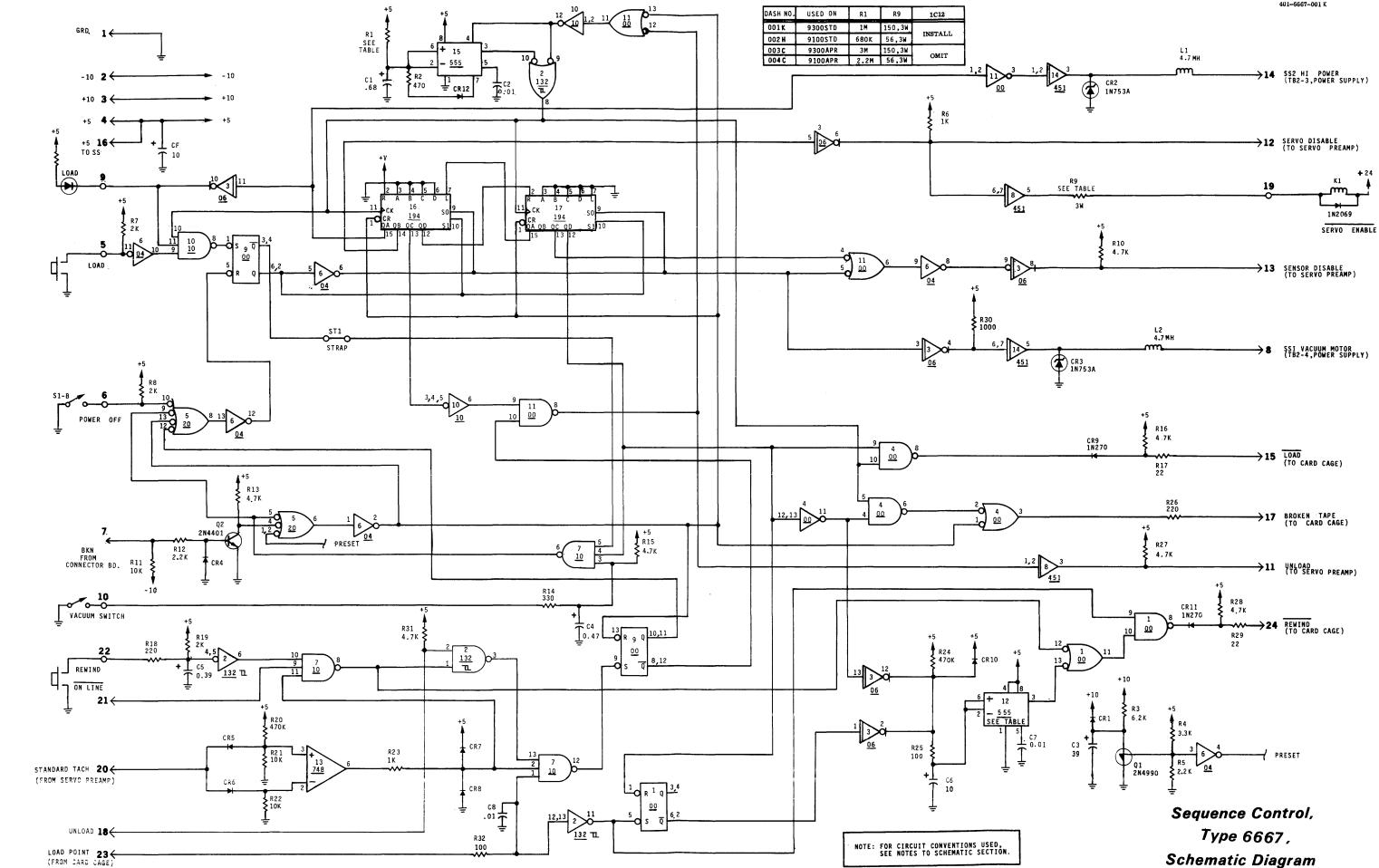

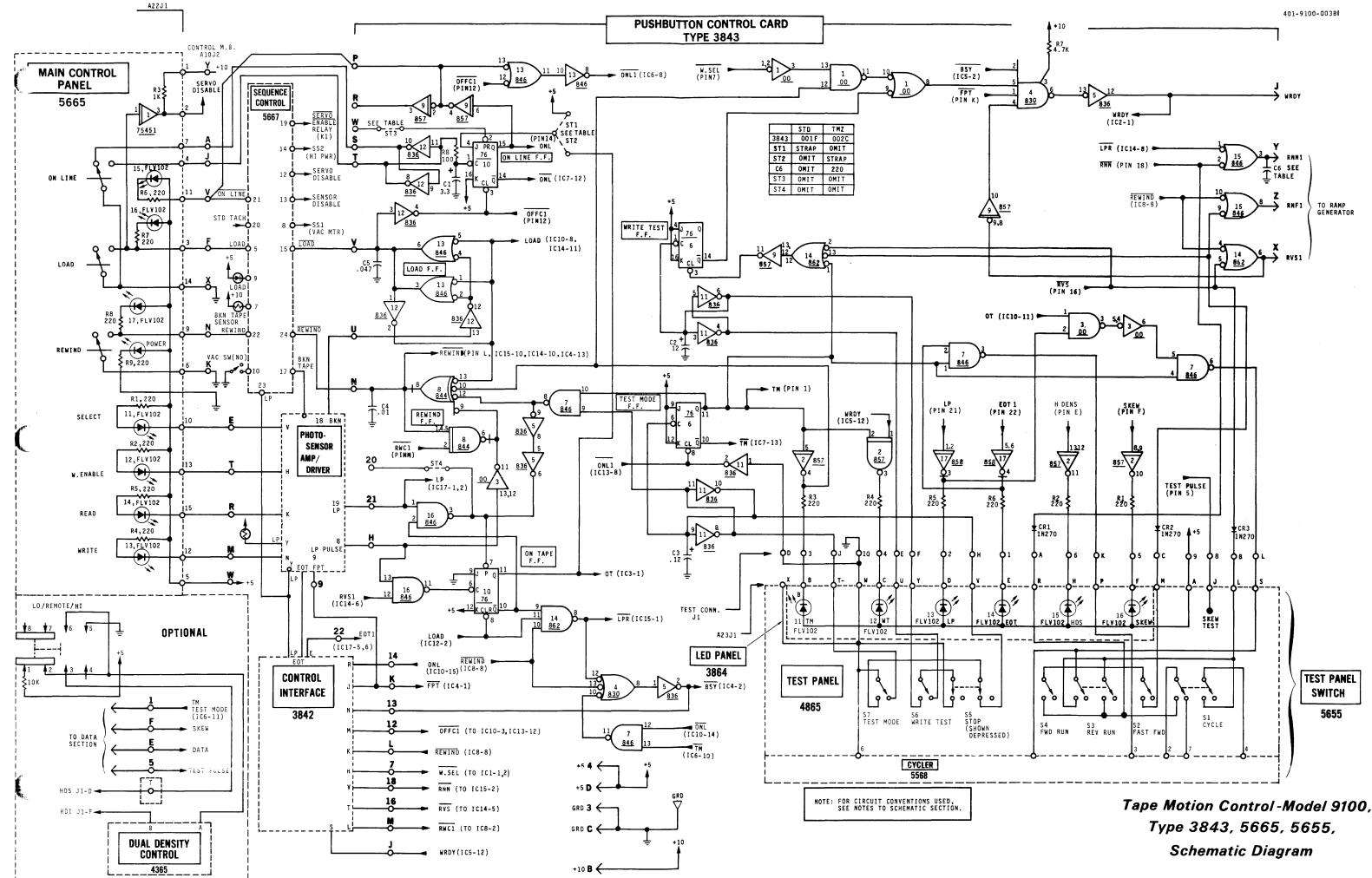

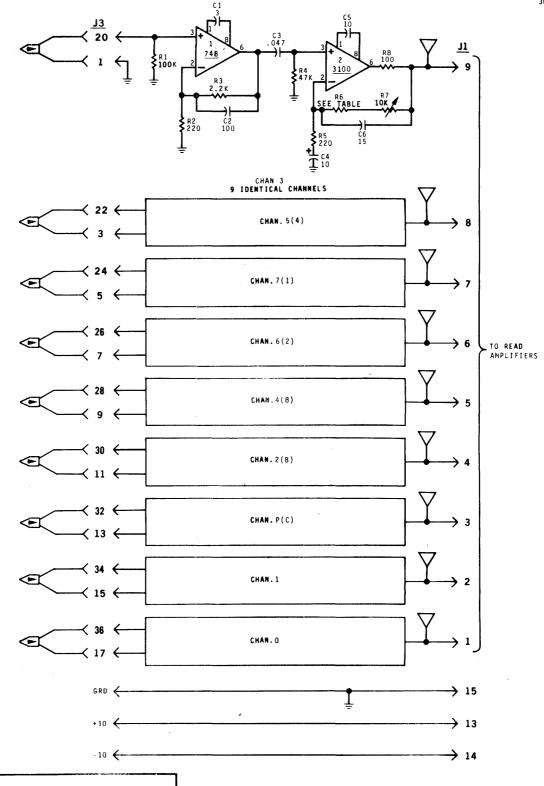

In the Model 9100, the following circuit boards control the tape transport:

Type 3841 Line Terminator Type 3842 Interface Control Type 3843 Pushbutton Control Type 5719 Sensor Amplifier/Driver Type 6667 Sequence Control Type 5733 Ramp Generator Type 6666 Servo Control

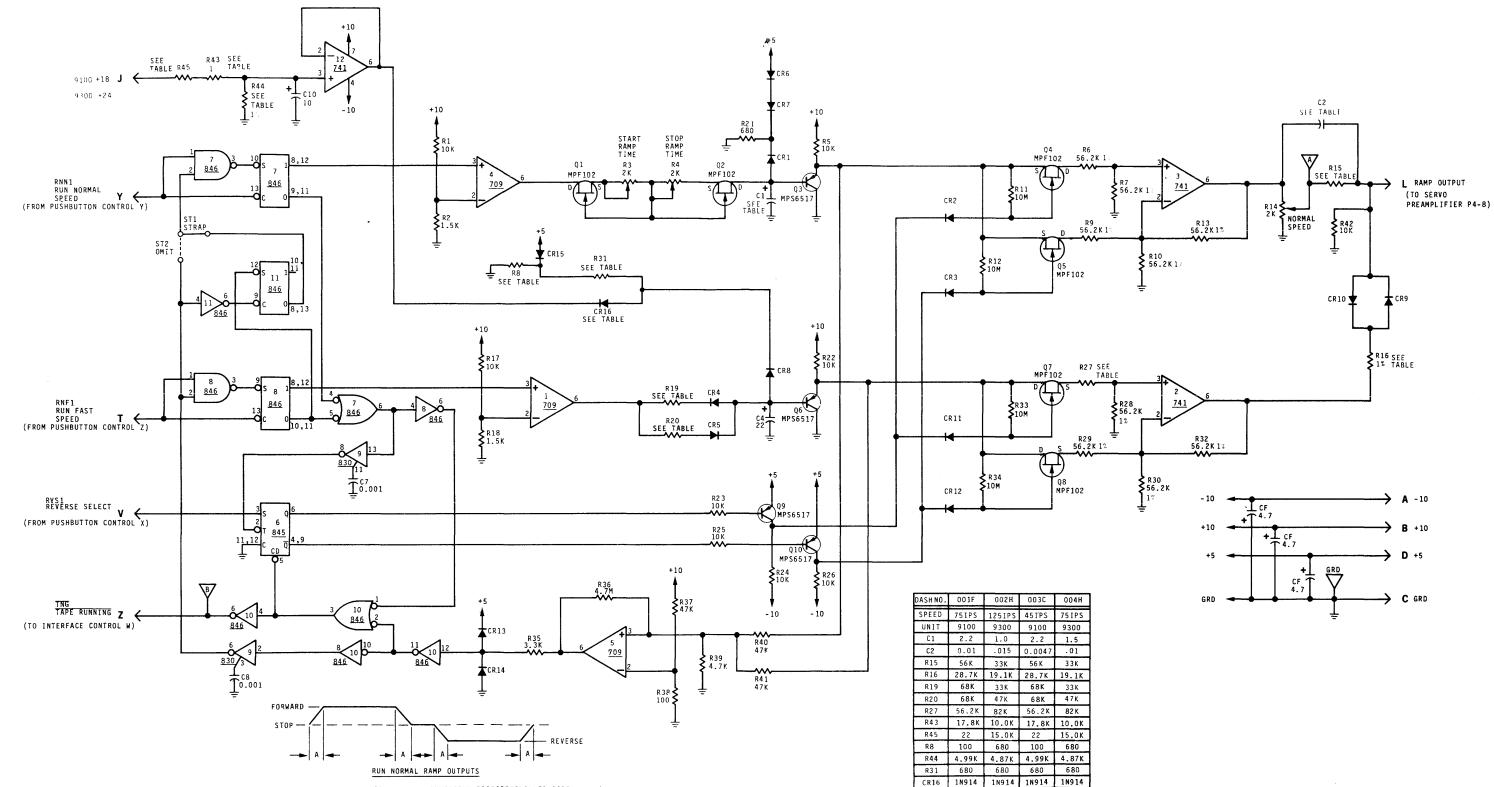

Figure 3-1 is a block diagram of the Model 9100. Tape commands from the interface connector are supplied to the interface control board which will generate internal tape transport commands if certain interlocks are satisfied. These tape transport commands are then supplied to the Pushbutton Control The Sequence Control and the Pushbutton board. Control also contain several interlocks which must be satisfied before the Pushbutton Control can encode the tape motion commands onto one of three command lines: RUN NORMAL (RNN1), RUN FAST (RNF1), and REVERSE SELECT (RVS1). These three command lines are supplied to the Ramp Generator, which provides linear ramp-up to speed and linear ramp-down to standstill in order to minimize tape stress and maintain accurate tape speeds. The output of the Ramp Generator is supplied to the capstan' servo preamplifier on the Type 5666 Servo Preamplifier board. The capstan servo uses the Ramp Generator output to control capstan motor current, while the capstan tachometer supplies a stabilizing feedback voltage to the capstan servo based on capstan motor speed.

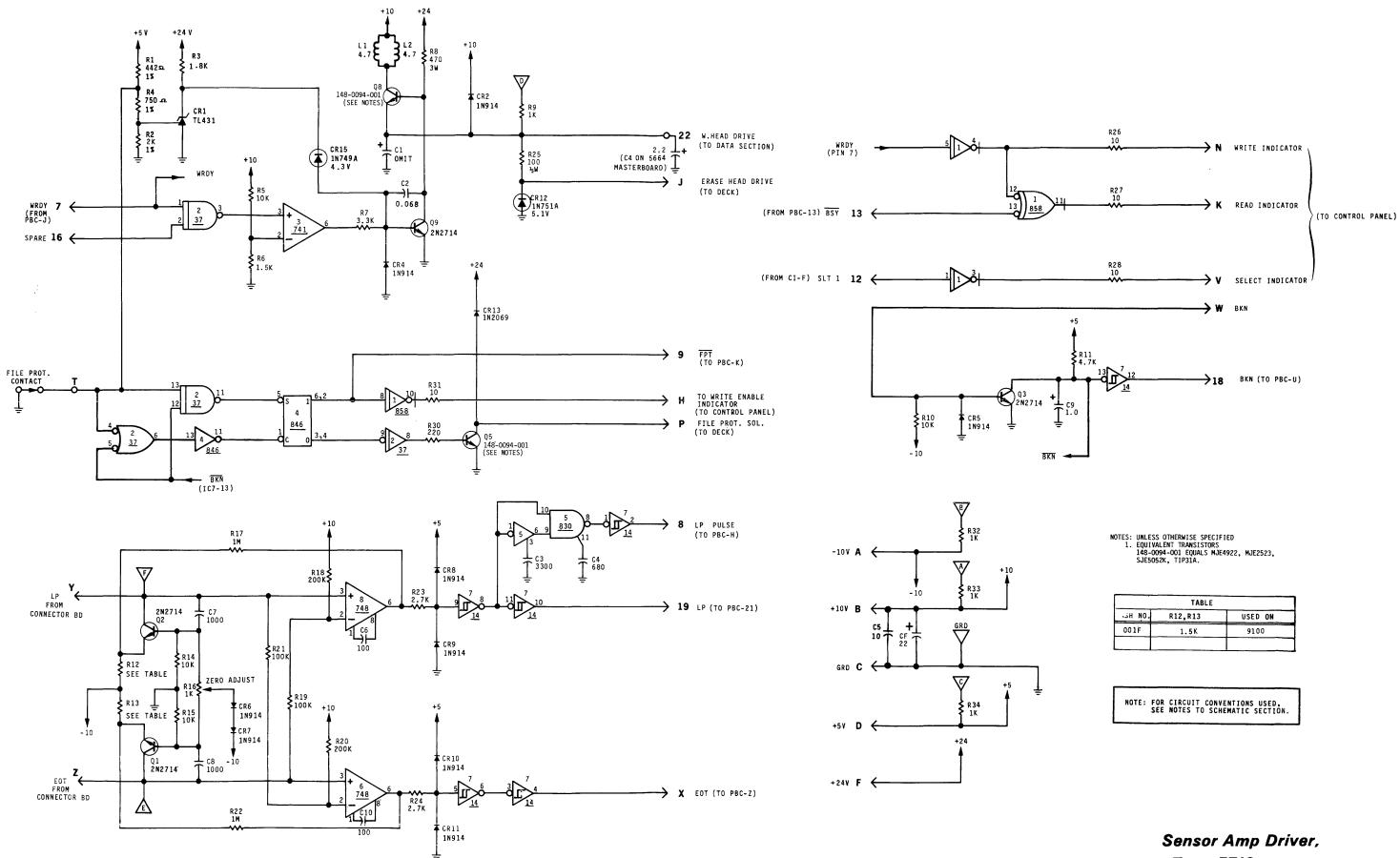

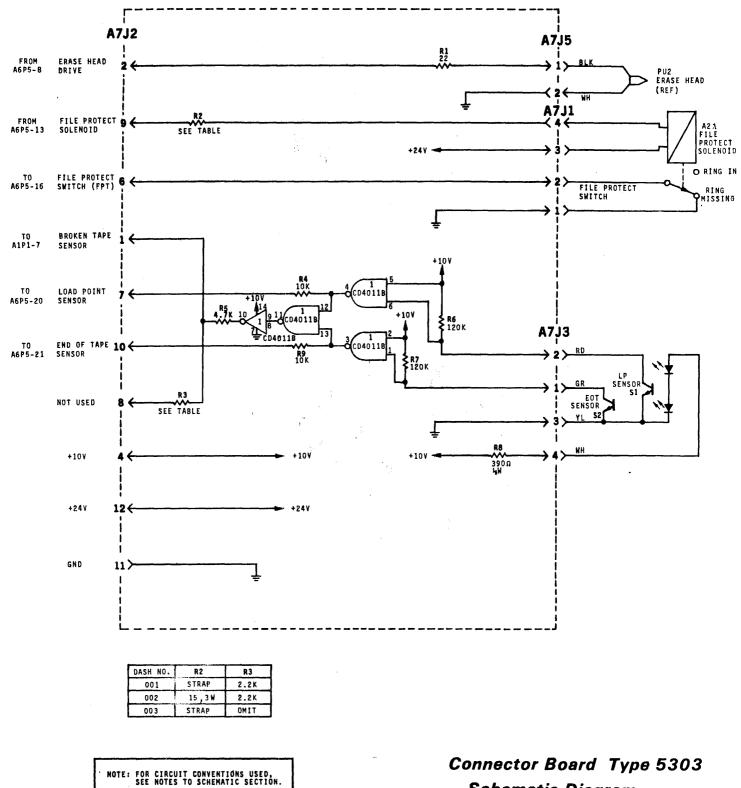

The Type 5719 Sensor Amplifier / Driver receives input from the file protect switch, load point sensor, and end of tape sensor. These signals are amplified and gated, then supplied to the Pushbutton Control and Sequence Control as tape transport status signals for controlling their interlocks.

The Type 3844 Sensor Amplifier/Driver module also contains the drivers for the WRITE, READ, and SELECT indicators on the main control panel.

#### 3.2.1 SEQUENCE CONTROL

Due to certain special sequencing requirements involved in controlling the tape transport, a special Sequence Control module has been developed for the Model 9100. Transport control pushbuttons on the main control panel connect directly to this board. In addition, broken tape, vacuum switch, and load point status signals are input to the Sequence Control board. Thus, when tape breaks or vacuum pressure drops, the Sequence Control will initiate the appropriate tape transport command to stop reel movement. Also, the sequencer will condition the actions caused by pressing the REWIND pushbutton dependent upon whether tape is in front of or past the load point marker.

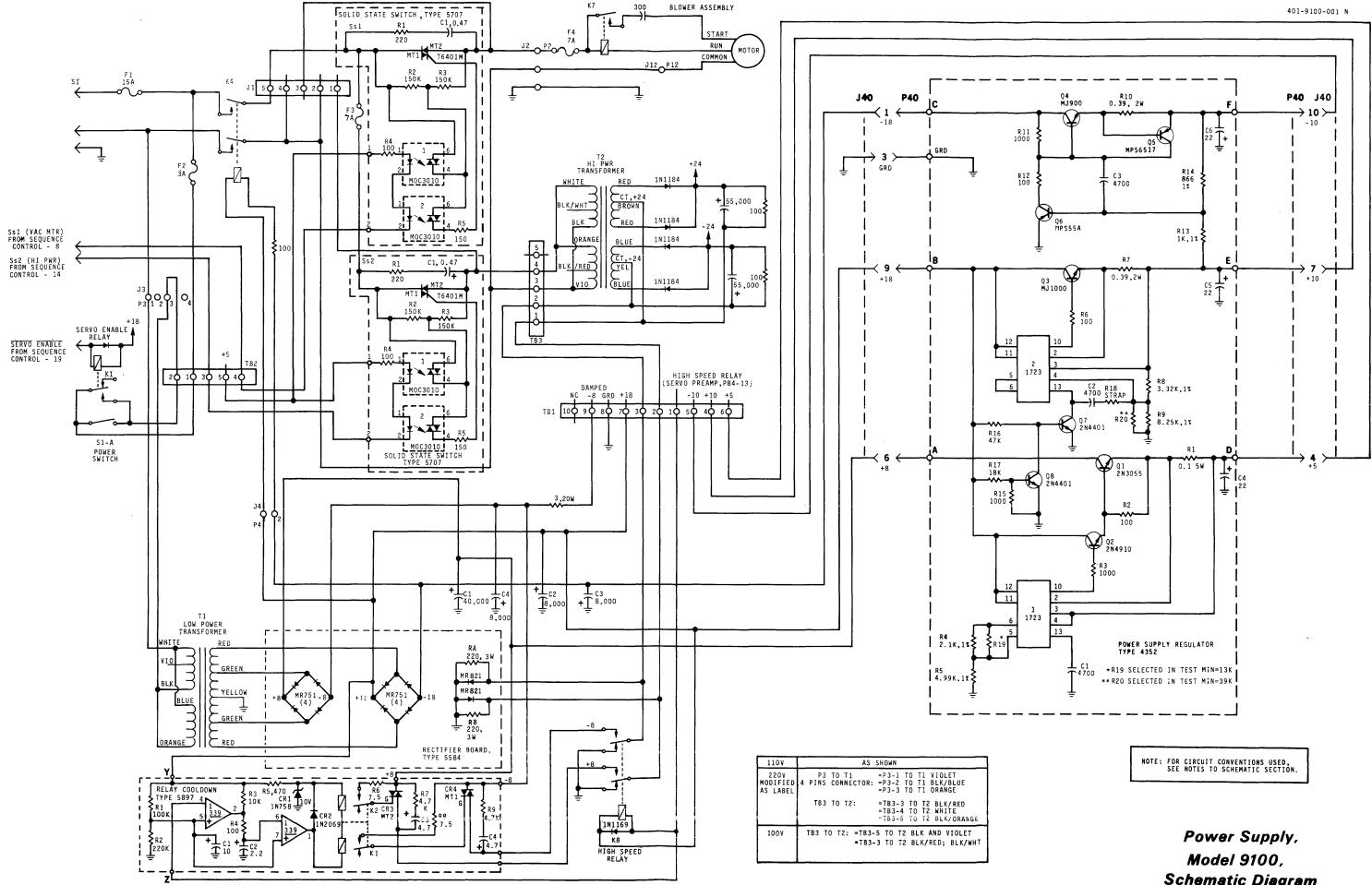

Four sequences are discussed: the POWER ON sequence, which occurs after the POWER pushbutton is pressed, the LOAD sequence, which follows the POWER ON sequence after the LOAD pushbutton is pressed, the UNLOAD sequence, which occurs when REWIND command is given and the tape is on the load point marker, and the POWER OFF sequence, when unit is loaded and power is turned off from the front panel.

#### 3.2.1.1 POWER ON Sequence

When the POWER pushbutton is pressed, the low power transformer and various regulated voltages are generated. The vacuum blower and high power transformer are enabled through main relay K4.

#### 3.2.1.2 LOAD Sequence

During this sequence, the vacuum blower motor is turned on, +24 vdc and -24 vdc is supplied to the electronics, servo relay K1 is actuated to enable reel motors and power latch, tape is tensioned and

Figure 3-1. Control Logic Block Diagram

Figure 3-1. Control Logic Block Diagram

drawn into the vacuum columns, and the reel servo loop is closed. At the completion of this sequence, the tape is properly tensioned. The capstan servo now receives the command to advance at normal speed to load point and then stops. If load point is not reached within 6 seconds after pressing the LOAD pushbutton, the sequencer will command the transport to rewind the tape, searching for load point. All operation is interrupted in case of broken tape or loss of vacuum as determined by the vacuum switch. In this instance BROKEN TAPE true signal will be supplied from the Sequence Control and all servos will be disabled immediately. An END OF TAPE true signal from the END OF TAPE sensor will not terminate a write operation. Instead, an EOT status is given to the interface, which should be used to generate a proper sequence to terminate writing.

#### 3.2.1.3 UNLOAD Sequence

During an unload operation, the tape is slowly and completely rewound onto the supply reel after it stops at load point during a normal rewind sequence.

To initiate the unload operation, the transport must be taken off line, either through an OFF LINE interface command or by pressing the ON LINE pushbutton. Next the REWIND pushbutton is pressed. This sets the unload flip-flop on the Sequence Control board, causing UNLOAD true to be output.

This connects the supply reel motor to -8 vdc instead of +24 vdc, opening the tape position servo loop. The takeup and supply reels now slowly rotate in reverse until the tape is completely rewound. When the physical end of tape is reached, BKN tape goes true and the unload sequence is terminated. Note that the POWER pushbutton is disabled during the entire unload operation.

#### 3.2.1.4 POWER OFF Sequence

When the POWER switch is shut off, the vacuum motor turns off immediately. The sequence is: vacuum switch off, sensor disable true (enabling the reels to remove tape from the vacuum chamber), servo disable true (applying braking signals to reels), all power then turned off.

#### 3.3 WRITE OPERATION

(Occurs after LOAD sequence is completed) The main pushbutton panel on the front of the tape deck is used to prepare the transport for operation. After power is turned on and the tape is properly threaded, the front panel LOAD pushbutton is pressed and the machine goes through the load sequence described above. Pressing the front panel ON LINE pushbutton now places the transport on line, preparing the transport to respond to interface commands as soon as they are available. When the transport is selected by a SLT true command from the interface, the Interface Control board's gates are enabled, allowing the transport to accept interface commands and return transport status signals to the interface.

Interlocks ensure that the transport writes data on tape only when the tape is properly loaded, the reel has a write enable ring, and the tape is moving forward at normal running speed. When SET WRITE STATUS from the interface goes true under these conditions, WRITE READY true is supplied to the Sensor Amplifier/Driver module. Here it turns on the write and erase head current drivers and illuminates the WRITE indicator on the front panel. WRITE READY and SELECT1 (combining ON LINE true and SELECT true) are also supplied to the data electronics card cage where they enable the write and read amplifier stages. With WRITE READY true, the interface supplies the properly formatted data to be written on tape.

#### 3.4 READ OPERATION

When the tape is properly loaded, not rewinding, and WRITE READY is false, a read operation is selected and the Sensor Amplifier/Driver module illuminates the front panel READ indicator. The read preamplifier and amplifier are now enabled to generate read signals back to the interface.

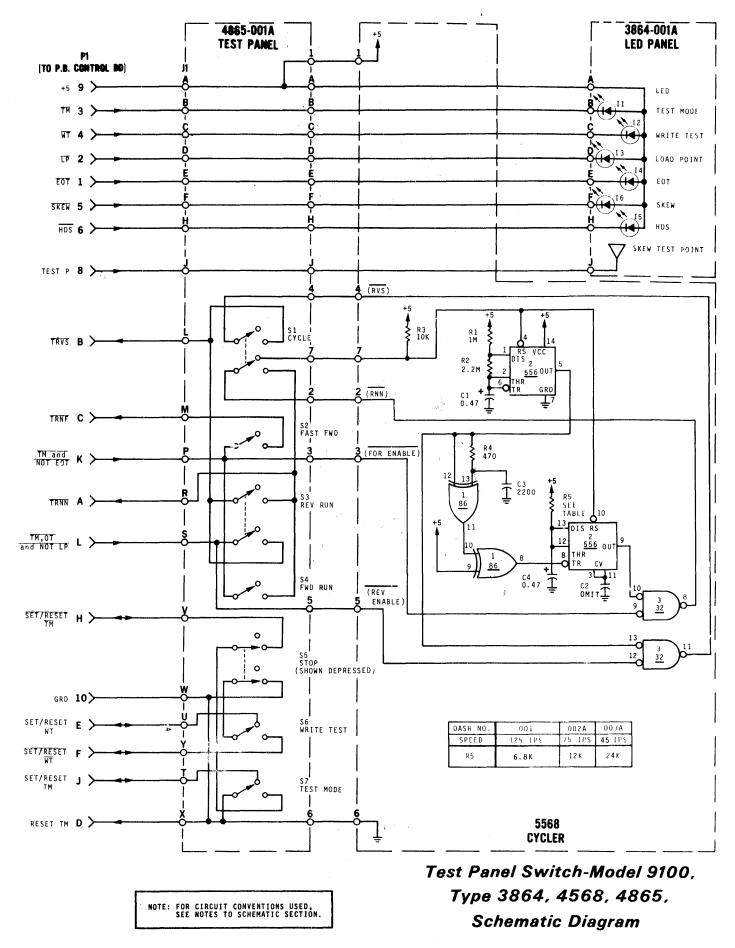

#### 3.5 TEST PANEL

The test panel is standard equipment in the Model 9100. Located next to the control panel, it is used to perform tests and adjustments on the tape transport while it is off line. This eliminates the need for many external test fixtures as well as saving valuable computer time.

The panel becomes operational only when the transport is off line, and the test panel STOP pushbutton is pressed. If these conditions are satisfied the test panel pushbuttons are enabled when the TEST MODE pushbutton is pressed. (The function of each test panel control and indicator is provided in Figure 4-2 of the maintenance section.)

Basically, the test panel is used for making skew, speed, ramp time, and servo system adjustments. Besides providing complete control over tape speed and direction, it can initiate a write test by generating a crystal controlled all-1 test pattern on the tape. The test panel also contains indicator lamps which illuminate when there is excessive skew, high density is selected, end of tape or load point is reached, or a write test is being performed. (The skew test indicates proper alignment of the read/write head.)

The test panel also contains a CYCLE pushbutton, which runs the tape forward and reverse continuously for making ramp time and reel servo adjustments.

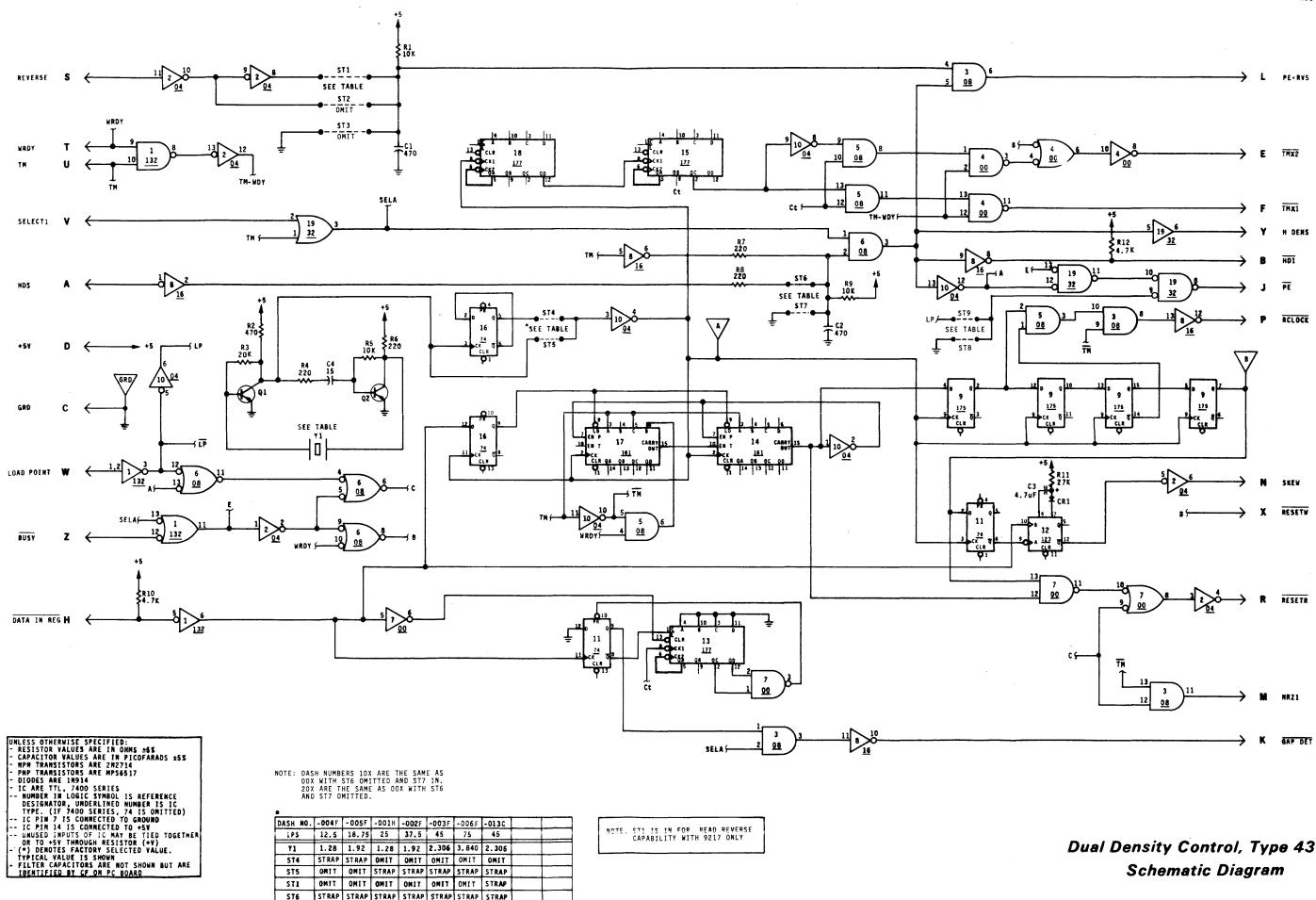

The logic circuitry required to translate test panel commands into tape transport commands is located on the Pushbutton Control card. The skew detect network for making skew tests is located on the Dual Density Control contained in the data section of the card cage.

#### 3.6 TAPE TRANSPORT CONTROL ADJUSTMENTS

The Kennedy tape transport requires few adjustments. These are preset at the factory and should not be changed unless there is strong reason to believe adjustment is required. The following adjustments are made on the control logic modules:

<u>Adjustment</u> Normal running speed Ramp-up time Ramp-down time End of tape/beginning of tape Location R14, Ramp Generator R3, Ramp Generator R4, Ramp Generator R16, Sensor/Amplifier Driver

The adjustment procedures are outlined in the maintenance section of the manual and in the circuit descriptions of the individual schematics.

#### 3.7 SERVO SYSTEM

#### 3.7.1 INTRODUCTION

The transport servo system advances the tape past the tape heads at a precisely controlled speed while maintaining a constant tape tension. The servo section is composed of three basic blocks: the takeup and supply vacuum sensors, takeup and supply reel servos, and the capstan motor servo.

#### 3.7.2 VACUUM SENSORS AND REEL SERVOS

When the machine is running forward normally, tape loops form approximately half way up the takeup and supply vacuum columns. (This position will vary depending on tape direction and speed. However, tape loop position should not fluctuate once established in any given mode.) Two specially designed tape sensors are positioned behind the tape loops to maintain the tape loop position while the tape is in motion. These sensors are variable capacitors. Each capacitor consists of a plated PC board covered with flexible, metallized mylar. The edges of the board are 5/1000 inch thicker than the copper center, forming a long groove (see Figure 3-2). Several holes are drilled through the board. The grooved area is covered with metallized plastic, mylar side down to form a dielectric. Wires are connected to the metallized covering and the copper plate to form a capacitor. The sensor is then mounted to a hollow metal chamber to form the base of the column.

When the Model 9100 is turned on and forward mode is selected, the vacuum pump attached to the back of the vacuum chamber draws the tape upward into the tape chamber (see Figure 3-3). A high vacuum exists above the tape in the enclosed portion of the chamber. No vacuum exists at the open end of the tape chamber. A partial vacuum is present in the vacuum chamber behind the tape sensor.

Since there are holes drilled in the sensor, the difference in pressure thus created presses the metallized mylar covering against the copper plate over the area below the tape loop. Thus the capacitance of the sensor changes as the tape loop moves in the column.

Figure 3-2. Vacuum Sensor Assembly

## Figure 3-3. Vacuum Sensor Operation: Cross Section View

The tape loop sensors are connected to an oscillator as the frequency control element. Any capacitance increase caused by the tape loop moving up the column decreases the output frequency of the oscillator and vice versa. This output frequency is integrated and filtered, and dc zeroed in to develop a dc motor control voltage. Thus the torque of the reel motors is controlled to centralize the tape loops within the vacuum columns during operation.

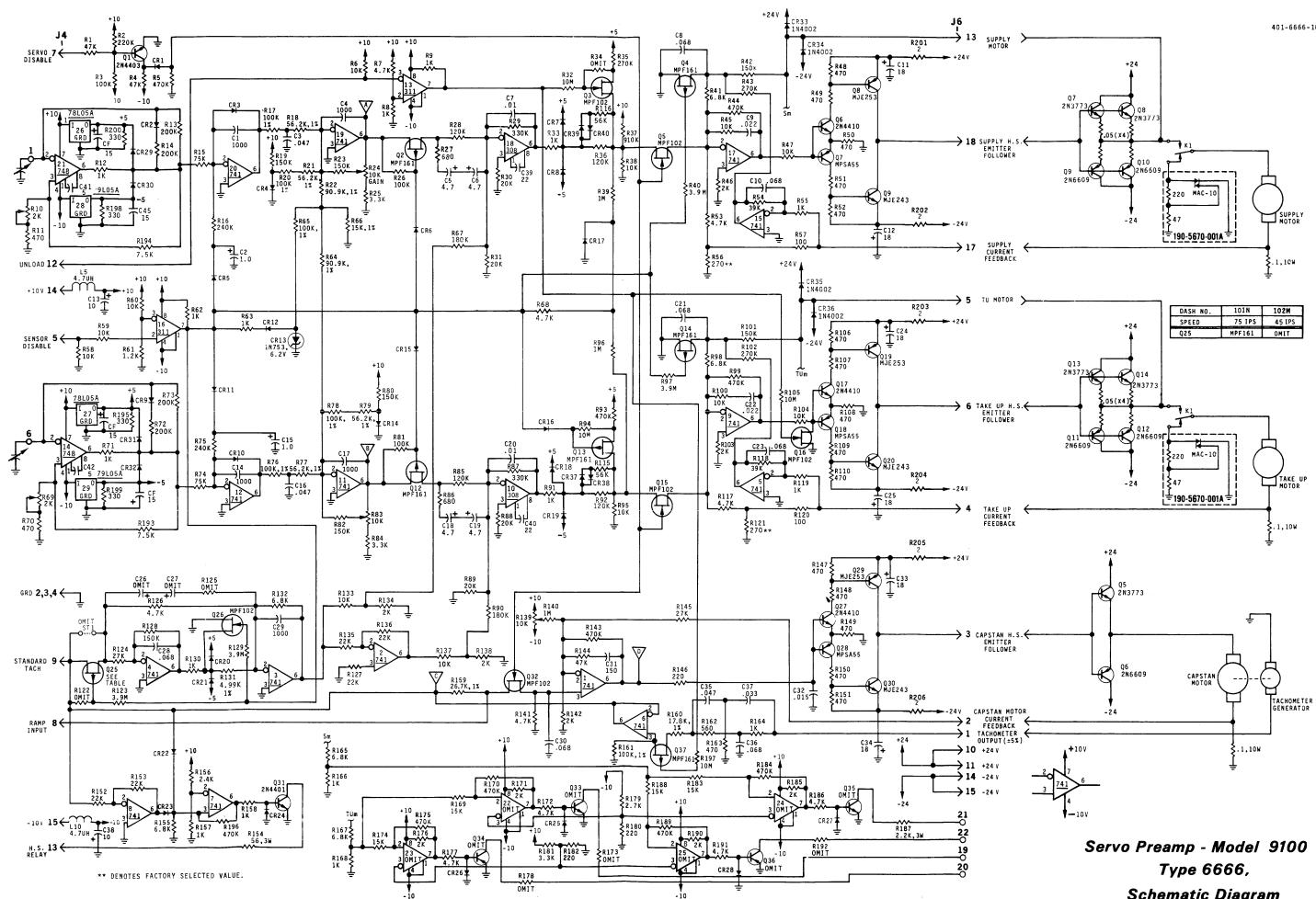

#### 3.7.3 CAPSTAN SERVO AMPLIFIER

A RUN NORMAL, RUN FAST, or REVERSE signal from the Ramp Generator is decoded and then supplied to the Capstan Servo Amplifier on the Type 6666 Servo board. This capstan servo can be disabled by SERVO DISABLE true from the Sequence Control. Motor speed is kept constant by feedback from a tachometer mounted to the capstan motor. This feedback is compared to the Ramp Generator input. Any difference voltage caused by motor speed deviation is amplified to develop a corrective voltage for returning the motor to proper speed. A sampling of tachometer output is also directed to the Sequence Control.

#### 3.7.4 SERVO SYSTEM ADJUSTMENTS

These adjustments are preset in the factory and should not be changed unless there is strong reason to believe adjustment is required. Adjustment procedures are outlined in the maintenance section of the manual and in the circuit description of the servo system schematic.

Adjustment: R4, R54 Frequency Controls

Function: varies basic frequency of oscillators to control speed of reel motors

Location: Type 6666 Servo Preamplifier

Adjustment: R17, R65 Gain Potentiometers

Function: eliminates tape loop overshoot when tape direction is changed

Location: Type 6666 Servo Preamplifiers

Adjustment: R115 Capstan Servo Zero

Function: eliminates capstan creep when tape is stopped

Location: Type 6666 Servo Preamplifier

### 3.8 DATA SECTION

#### 3.8.1 INTRODUCTION

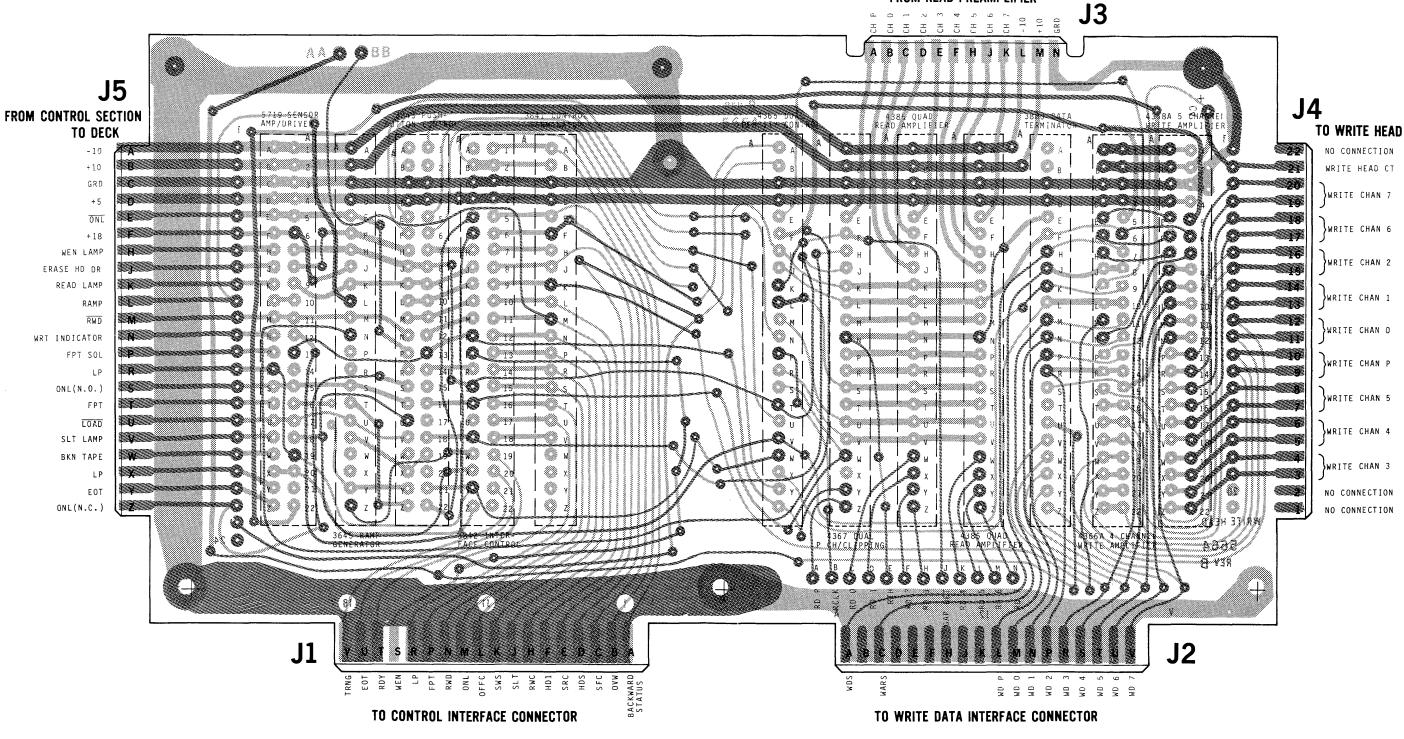

The data section includes read/write amplifiers and interface cards containing output drivers and timing controls. Block diagrams are shown in Figures 3-4 and 3-5.

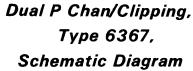

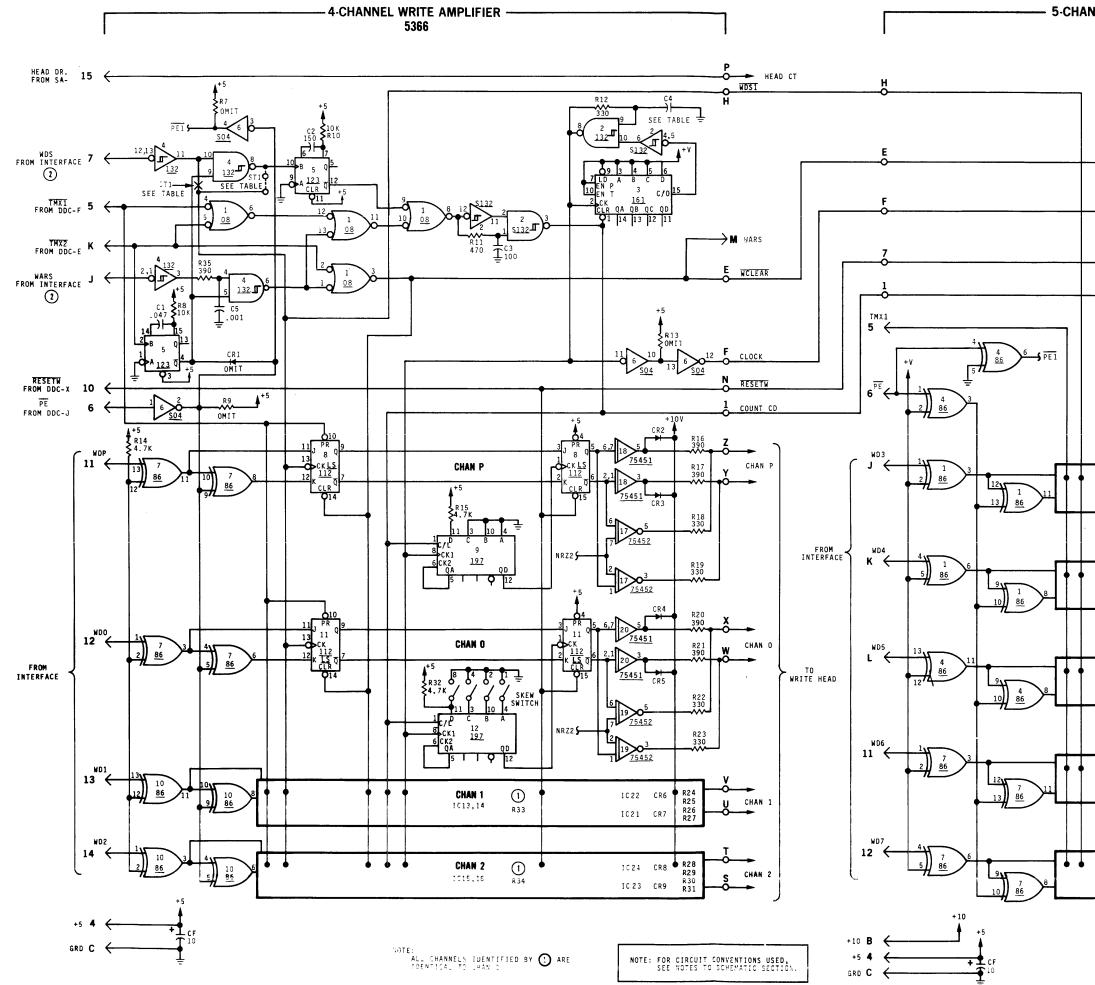

The data section consists of seven circuit cards that plug into the data masterboard. These include a Dual Density Control, a Dual P Channel/Clipping Control, a pair of Quad Read Amplifier modules, a Four Channel Write Amplifier card, a Five Channel Write Amplifier card, and a Data Terminator card.

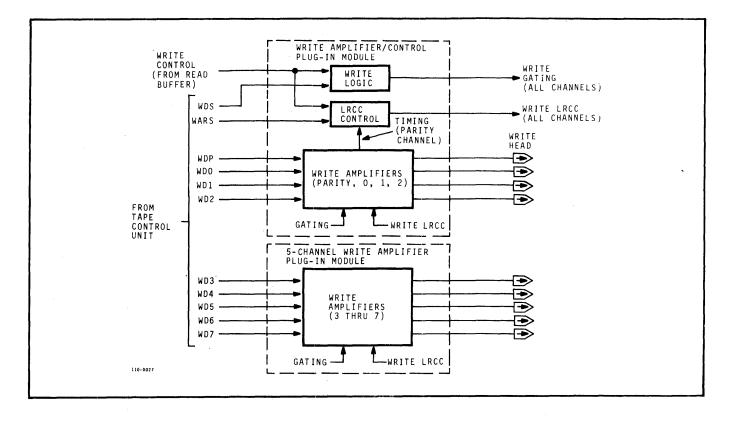

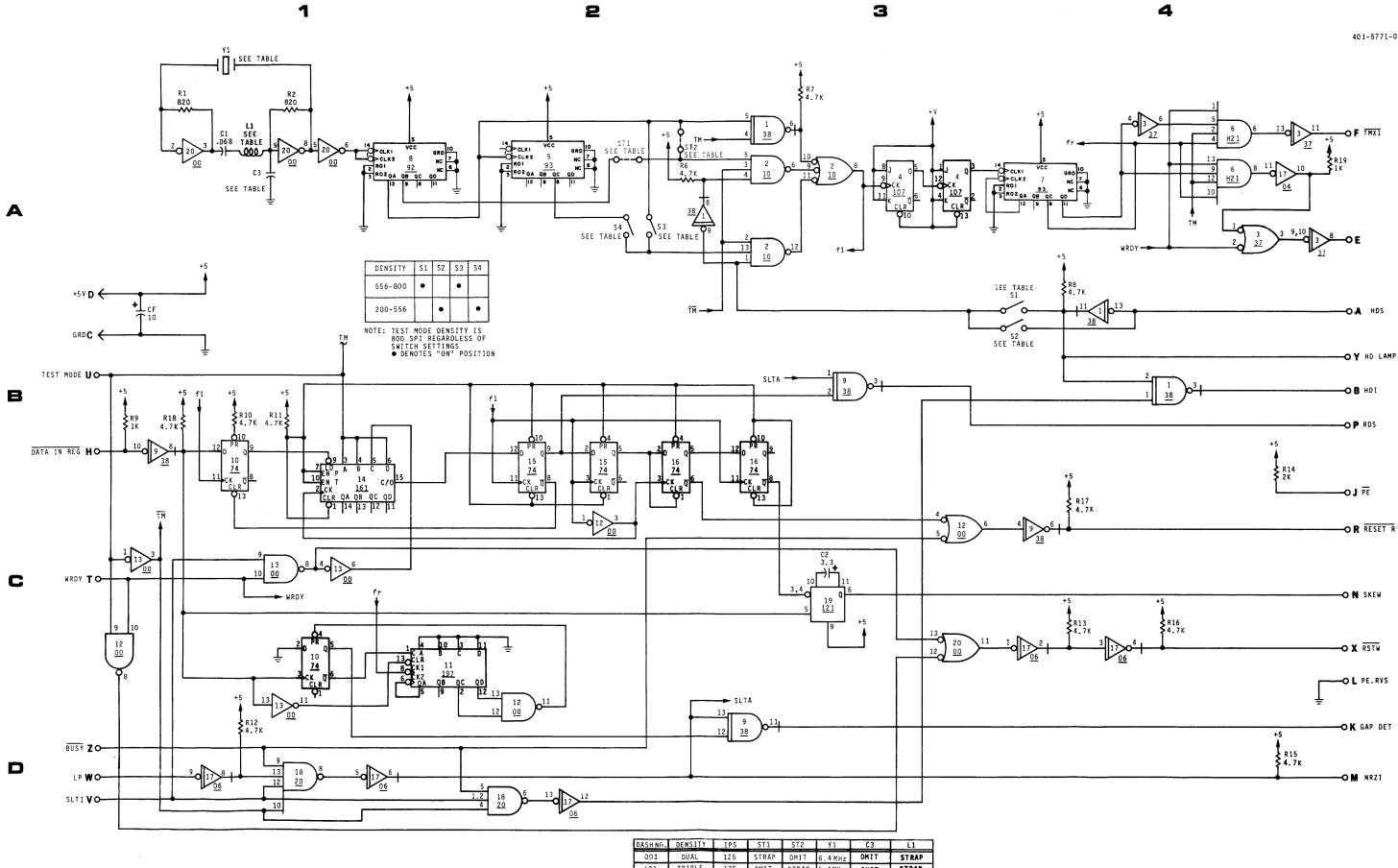

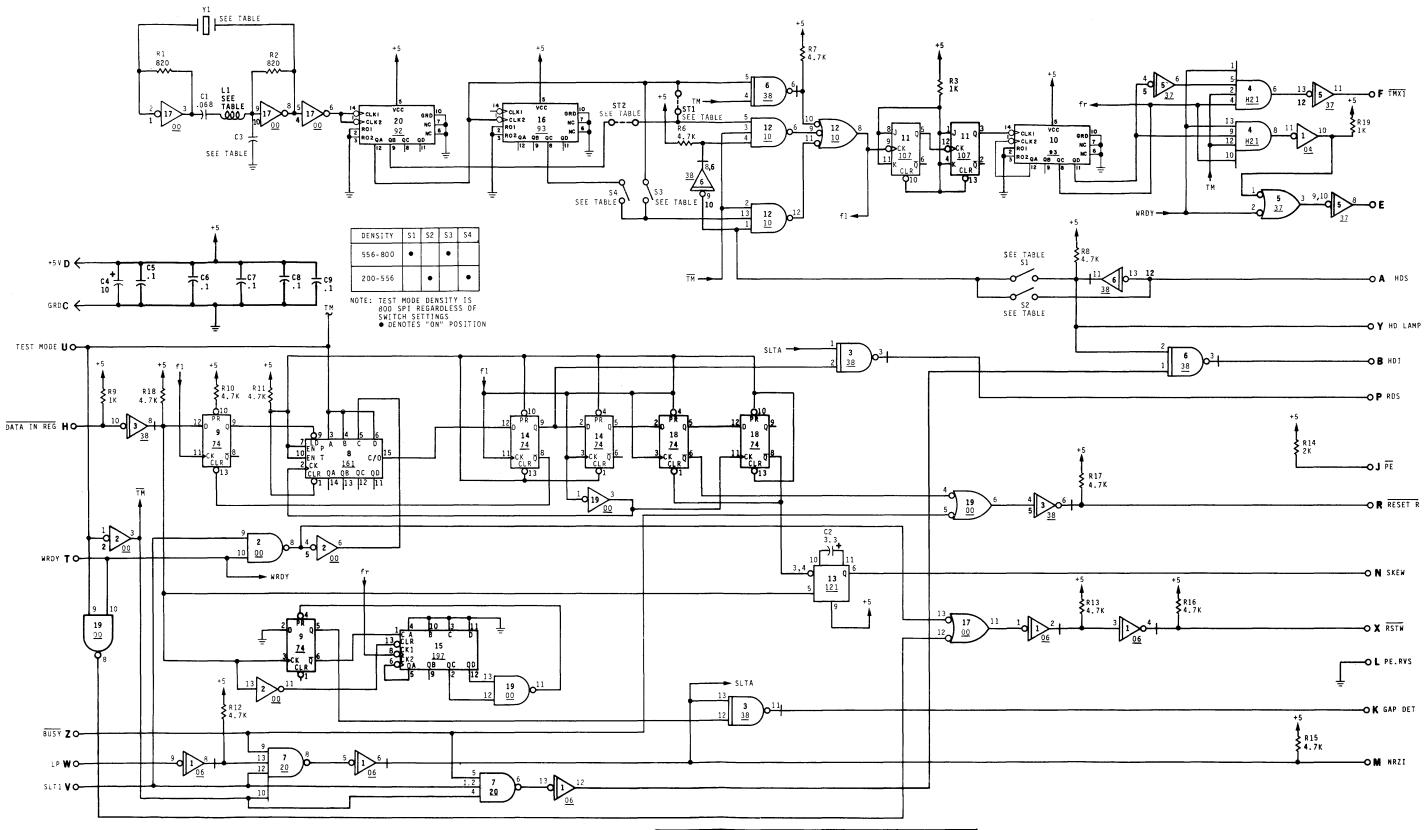

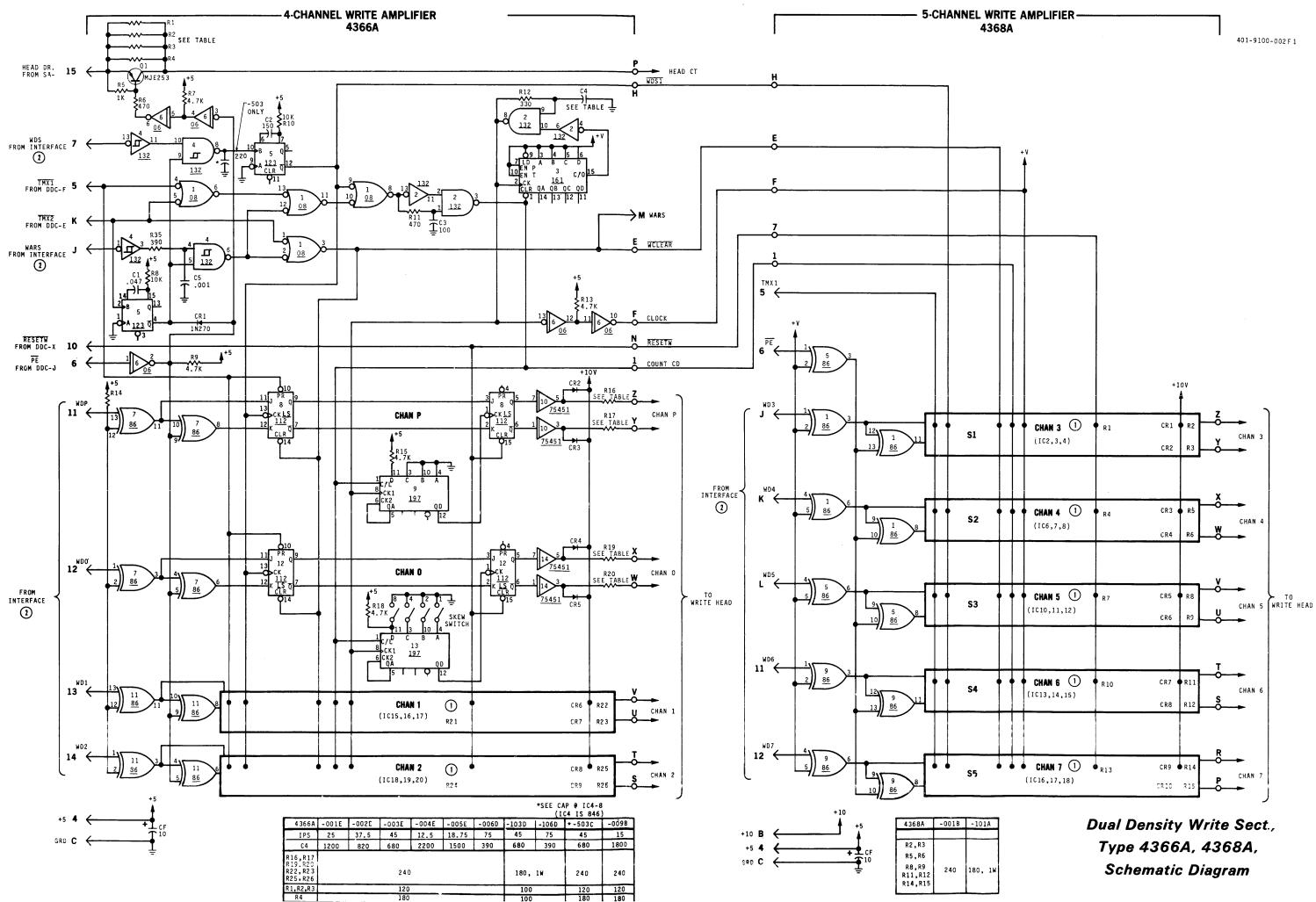

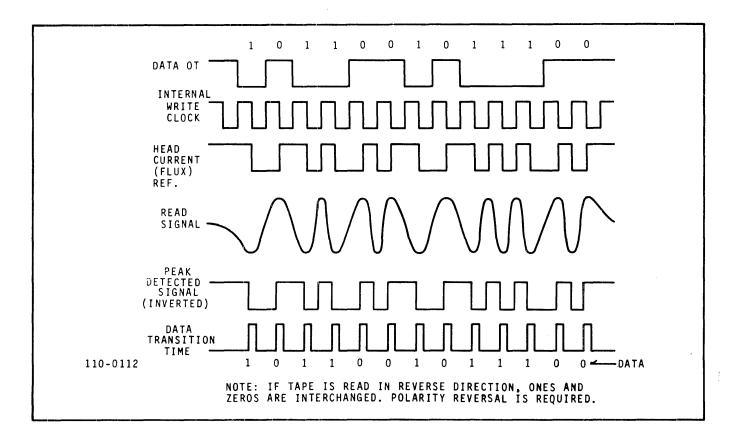

#### 3.8.2 WRITE ELECTRONICS (Figure 3-4)

A write amplifier channel is provided for each tape channel. Four of these channels and the circuitry typical of all write amplifiers are contained on Type 4366 Write Amplifier. The five remaining write amplifier stages are located on Type 4368 Write Amplifier. These cards plug into the masterboard, from which the necessary head connections are made. (Two of the channels on the Type 4366 Write Amplifier are not used in seven-track operation.)

Each write amplifier channel consists of an input buffer, a digitally adjustable deskewing circuit, a clocked flip-flop, and a write head driver. The skew characteristics of each read/write head are tested at the factory and the write amplifier switches are

Figure 3-4. Write Data Section

set to compensate for the skew, using channel P as the fixed reference channel. (Normally the write deskew switch settings should never be changed. When a new head is installed the factory furnishes a label displaying the new deskew switch settings required to compensate for the characteristics of the new head.)

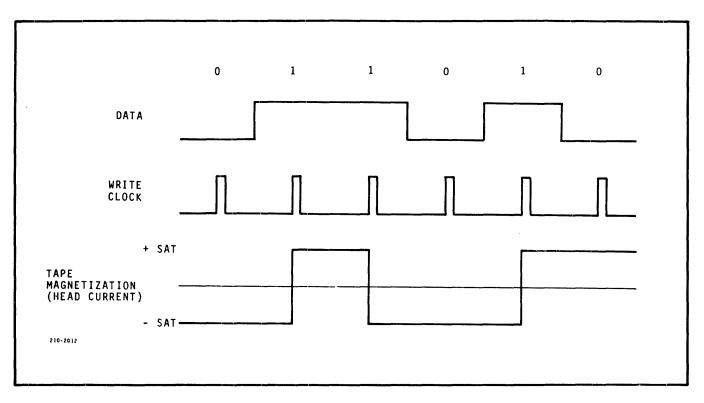

The write electronics section also includes the write data strobe buffer which clocks the write amplifier flip-flops, and a write amplifier reset circuit to clear all write amplifier flip-flops. The write amplifier reset is used to write the longitudinal redundancy check character. During a write test mode, initiated by the test panel with the recorder off line, the write electronics generates an all-1 test pattern on tape derived from a crystal controlled reference frequency  $F_R$ , supplied from the module in the read electronics. The test pattern can be used to test write deskewing as well as other functions of the data electronics.

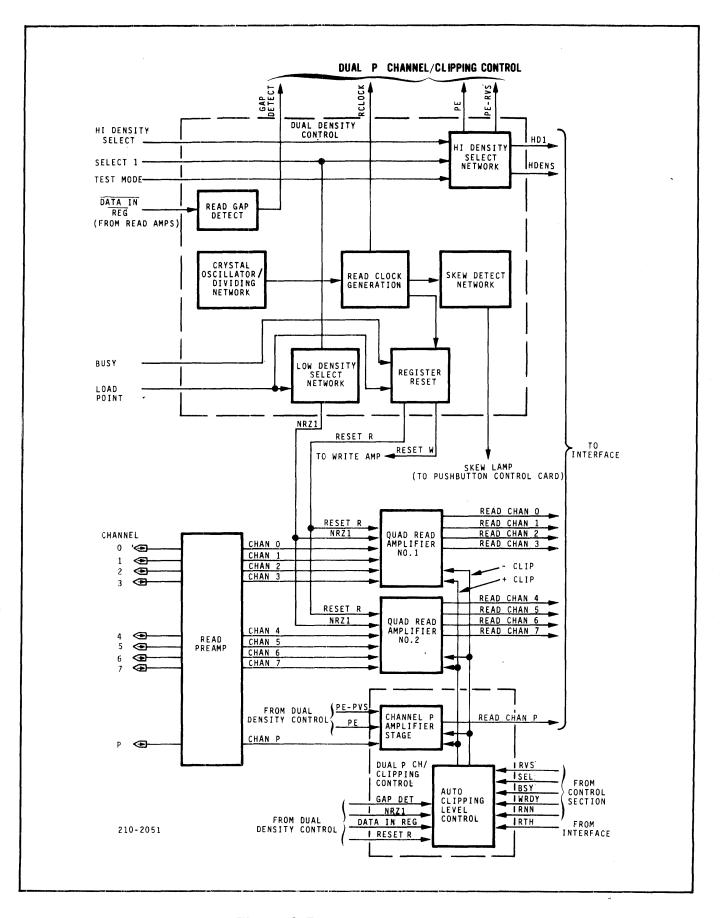

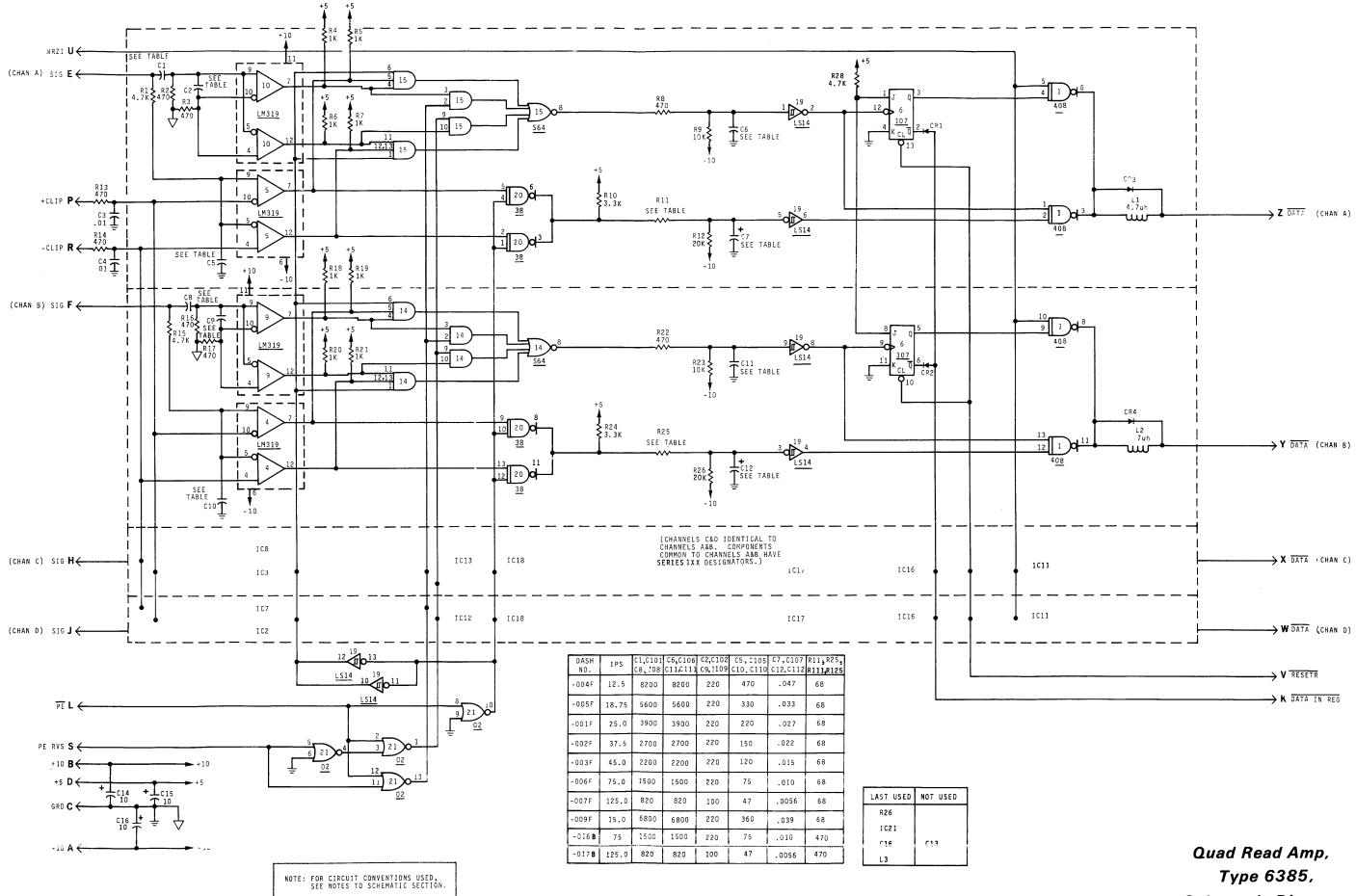

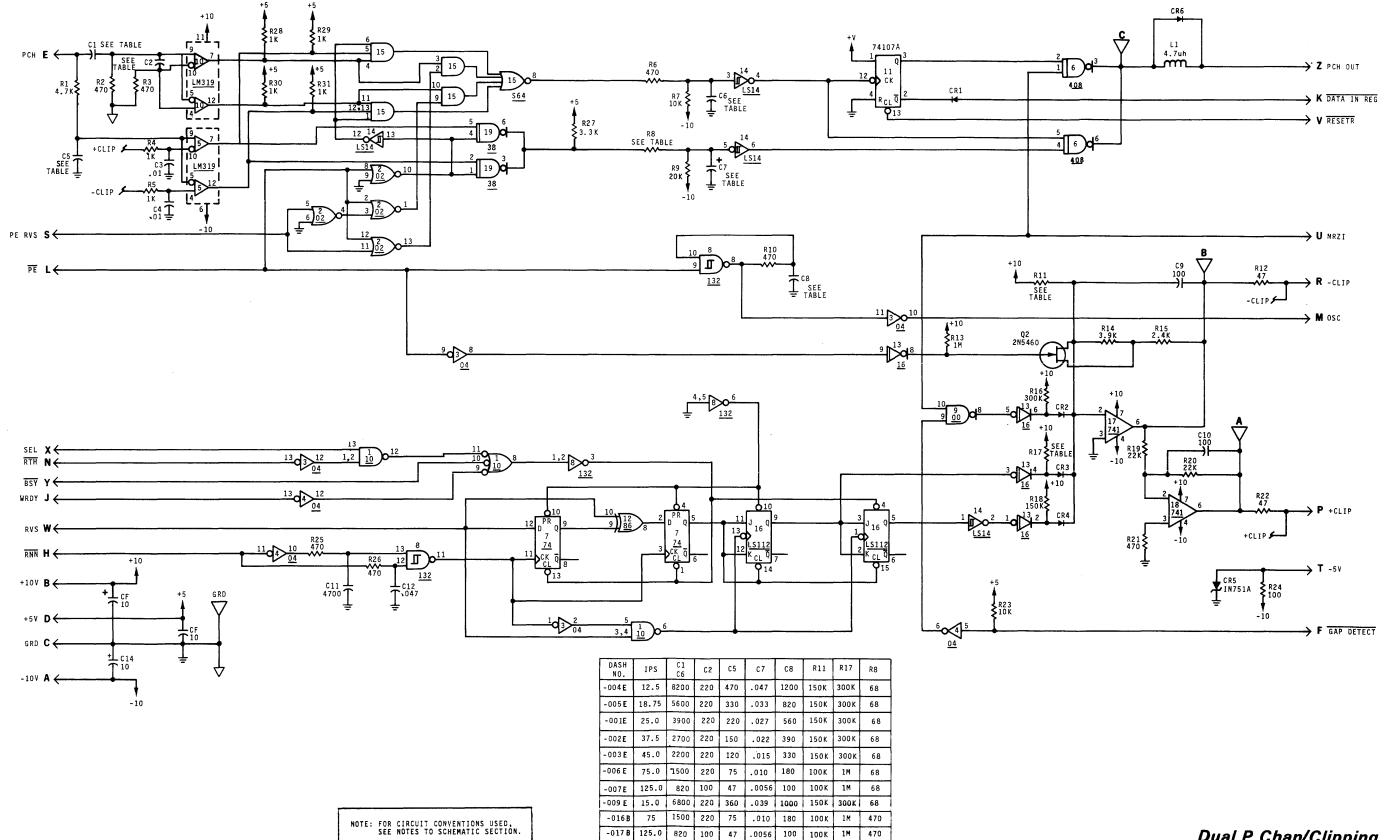

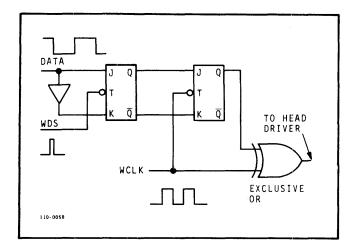

#### 3.8.3 READ ELECTRONICS (Figure 3-5)

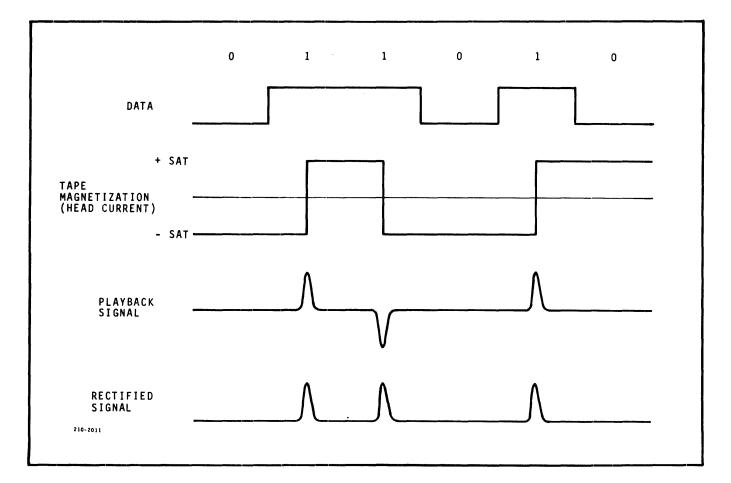

The function of the read electronics is to convert the data recovered from the tape into digitized wave forms, deskew, and supply it to the interface with its respective read clock. The read electronics also detect the interrecord gap and excessive skew. The components comprising the read section include the magnetic read head, the Read Preamplifier module, Read Amplifier/Clipping Control module, and a pair of Quad Read Amplifier modules. Figure 3-5 is a functional block diagram of the read section, showing the general signal flow between the cards. A detailed circuit description of each circuit card accompanies the schematic of the card.

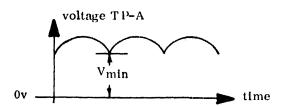

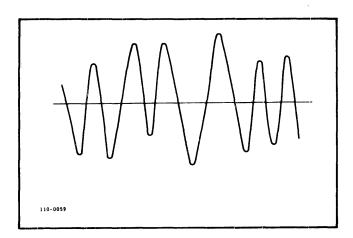

Low level analog signals on the order of tens of millivolts are supplied from the read head to the Read Preamplifier module. They are linearly amplified to an output voltage (adjusted by a potentiometer for each read preamplifier stage) of approximately 8 volts peak to peak during 800 cpi NRZ1 read operation. The amplified analog signals are then supplied to the nine read amplifier stages, eight of which are located on the Quad Read Amplifiers. (Channel P is directed to the Read Amplifier stage includes a peak detection circuit, a filtering network, an output data register, and a pulse generator.

The analog signals from the preamplifier are detected only when they exceed the positive or negative clipping levels provided by the Dual P Channel/Clipping

Figure 3-5. Read Data Section

Control module. They are then rectified and peak detected, with the resulting digitized wave forms containing negative-going transitions corresponding to the peaks of the input analog signals, e.g., one bits in the NRZ1 code. The digitized wave forms are supplied to a filtering network which eliminates spurious pulses between transitions. The data of each channel is then stored in a register which generates DATA IN REGISTER to the Dual Density Control.

The Dual Density Control card supplies a READ CLOCK output to clock the data registers of all nine channels simultaneously, supplying the data character to the interface.

When an error is detected, and the transport is commanded by the interface to reread a block, the read amplifier clipping levels are switched automatically by the Dual P Channel/Clipping Control module to maximize the recoverability of marginally recorded data. First the clipping levels are lowered to recover possible partial dropouts. If the block is still in error, the clipping levels are switched to higher levels to eliminate possible baseline spikes.

The Dual Density Control module contains circuitry common to all nine channels. It generates the read clock and detects excessive skew, as well as detecting the interrecord gap and providing the interlocks necessary for 800 or 1600 cpi density selection. The Dual Density Control also supplies reference frequencies to the Write Amplifier modules in order to generate the write test pattern.

In the phase encoded mode, the analog signal with its two main frequency components is amplified, peak detected, and digitized. Threshold detection for PE mode is identical to NRZ1 threshold detection, except for the absence of RCLK and RGAP outputs to the interface. The output of each channel represents its respective flux change.

## 3.9 DATA SECTION ADJUSTMENTS

The following adjustments are made in the data electronics section:

| Adjustment                  | Location         |

|-----------------------------|------------------|

| Read preamplifier amplitude | Type 5728 Read   |

|                             | Preamplifier     |

| Skew alignment              | Read/write head, |

|                             | write amplifiers |

The adjustments are preset at the factory and should not be changed unless there is strong reason to believe that readjustment is required. The adjustment procedures are described in the circuit description of the Read Preamplifier and Write Amplifier schematics.

# SECTION IV

## MAINTENANCE INSTRUCTIONS

#### SECTION IV

### MAINTENANCE INSTRUCTIONS

### 4.1 GENERAL

Kennedy Company tape transports are highly reliable precision instruments which will provide years of trouble-free performance when properly maintained. A planned program of routine inspection and maintenance is essential for optimum performance and reliability. The units require very few adjustments and these should not be performed unless there is strong reason to believe they are required. All electrical adjustments are preset at the factory and should not require readjustment except after long periods of time.

#### 4.2 PREVENTIVE MAINTENANCE

To assure continuing trouble-free operation a preventive maintenance schedule should be kept. The items involved are few and simple but very important to proper tape transport operation. The frequency of vary performance will somewhat with the environment and degree of use of the transport so a rigid schedule applying to all machines is difficult to define. The recommended periods below apply to units in constant operation in ordinary environments. They should be modified if experience shows other periods are more suitable.

#### 4.2.1 DAILY CHECK

Visually check the machine for cleanliness and obvious misadjustment. If items in the tape path show evidence of dirt or oxide accumulation, clean thoroughly.

#### 4.2.2 CLEANING

All items in the tape path must be kept scrupulously clean. This is particularly true of the head and guides. The inside of the dust cover must not be allowed to accumulate dirt since transfer to the tape will cause malfunction.

In cleaning it is important to be thorough yet gentle and to avoid certain dangerous practices.

#### 4.2.2.1 Head Cleaning

Oxide or dirt accumulations on the head surfaces are removed using a mild organic solvent and a swab. Q tips are convenient for this use but must be used with caution. Be sure the wooden portion does not contact head surfaces.

An ideal solvent is 1.1.1 trichlorothane contained in Kennedy K21 maintenance kit. However, others such as isopropyl alcohol will do. DO NOT USE: acetone or lacquer thinner, aerosol spray cans, or rubbing alcohol.

Do not use an excess of any solvent, and be extremely careful not to allow solvent to penetrate ball bearings of idler rollers, capstan motor, etc., since it will destroy their lubrication.

4.2.2.2 Tape Path Cleaning

#### CAUTION

Do not attempt to clean the mylar sensors in columns or allow solvent to contact the element. Dirt and oxide will not impede the sensor operation.

Other items in the tape path should be cleaned at the same time as the magnetic head. These include columns, idler rollers, tape guides, capstan, and tape cleaner surface.

The techniques are similar to those outlined above for head cleaning.

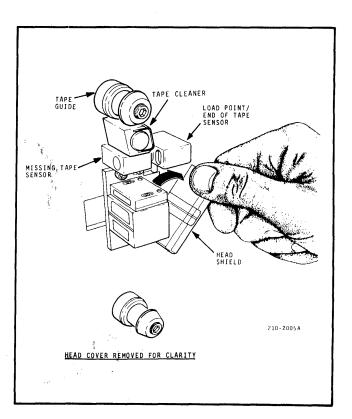

Figure 4-1. Opening of Head Shield

#### 4.2.2.3 Other Cleaning

A vacuum cleaner is recommended for removing accumulations of dust inside the dust cover or elsewhere in the unit. Compressed air may be used if caution is exercised to avoid blowing dirt into bearings. Antistatic cleaners are available for cleaning the plexiglass dust cover window.

#### 4.2.3 VISUAL CHECK

Check visually to determine if all appears to be right with the machine. It is helpful to run tape forward and reverse observing smooth tape motion, proper vacuum operation, etc.

#### 4.3 ROUTINE ADJUSTMENT

There are no routine adjustments. Need for adjustment will be manifest if malfunction occurs. Under normal circumstances adjustment will be more likely to cause trouble than prevent it.

#### 4.4 LUBRICATION

No bearing lubrication is required. All bearings are lubricated for life and introduction of oil may destroy their lubrication.

#### 4.5 WEAR

Magnetic tape is an abrasive and in time wear will be noted on items over which the oxide surface slides.

#### 4.5.1 HEAD WEAR

Head wear is generally signaled by an increase in error rate. Confirmation is a sizable increase in output voltage at the read head as measured at the read preamplifier. When the head becomes worn it must be replaced. Head replacement procedure is described in paragraph 4.24.5.

Worn heads usually can be resurfaced at least once if returned to the factory. This is more economical than replacement with a new head. Consult Section V for details of head return.

#### 4.5.2 GUIDE WEAR

Guides wear principally at the point of contact with the front guide surface. Although guides are ceramic, in time grooves will appear. Since guides are symmetrical it is only necessary to loosen the guide mounting screw, rotate the guide, and tighten to present an unworn surface to the tape.

#### 4.5.3 REEL HUB WEAR

Quick release hubs are adjustable to assure a firm clamping action. They are designed to make it impossible to mount a reel in a wrong or cocked position. If the locking action should become weak, the hub may be adjusted as described in paragraph 4.8. O-ring clamps used in the hub may tend to hang up after long periods of use. This can be corrected as follows:

- a. Remove O-ring from hub.

- b. Clean thoroughly with mild solvent.

- c. Lubricate ring with silicone grease. Wipe off as thoroughly as possible, leaving a light lubricating film.

- d. Snap O-ring back in place.

#### 4.6 PERIODIC INSPECTION

At regular intervals, approximately every two months, it is advisable to make a more thorough check of machine operating parameters. This will ensure that no progressive degradation will go unnoticed. The test panel facilitates making these checks, allowing control of tape motion off line for test purposes as well as providing useful indicators and test signals. The test panel connector plugs into a connector on the control electronics. It does not require that interface cables be disconnected. Using the test panel or other appropriate means, the following should be checked periodically.

> Tape speed Ramp times Read level Skew Photosensor adjustment Capstan and reel servo adjustment

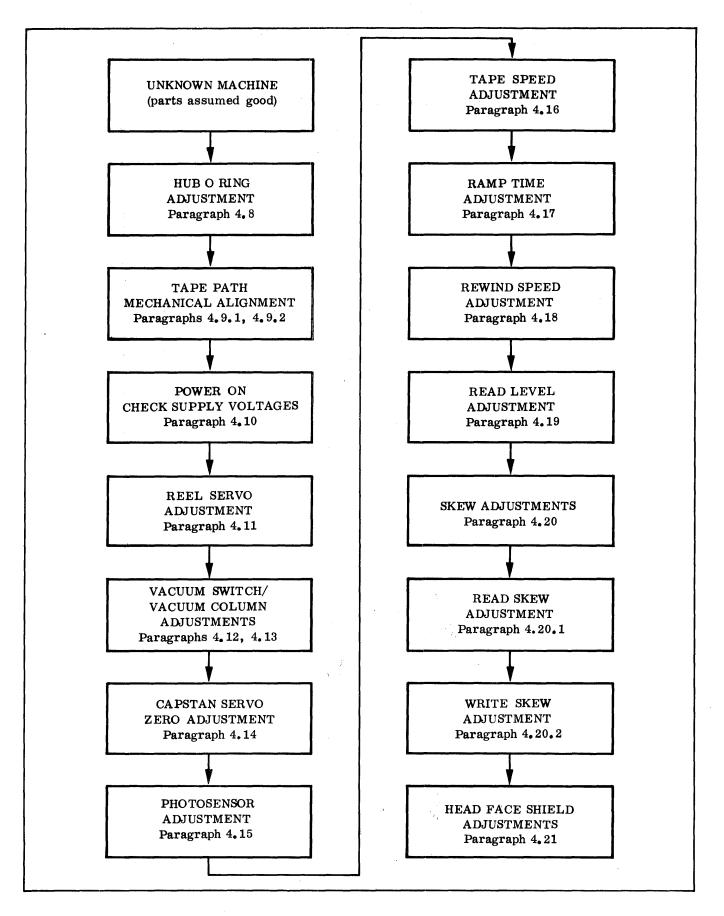

Procedures for checking these and other items are given in this section and a suggested sequence of adjustments is shown in Table 4-1.

#### 4.7 TEST PANEL USE

#### 4.7.1 TEST PANEL USE

The test panel is standard equipment in the Model 9100. Located next to the control panel, it is used to perform tests and adjustments on the tape transport while it is off line. This eliminates the need for many external test fixtures as well as saving valuable computer time.

The function of each test panel control and indicator is provided in Figure 4-2.

Basically, the test panel is used for making skew, ramp time and servo adjustments. Besides providing

Table 4-1. Adjustment Sequence

#### NOTE

Tape transport must be off line and STOP pushbutton depressed before test panel can become functional.

TEST point and SKEW indicator. Indicator lights if tape skew exceeds the appropriate skew (read or write) gate setting. An oscilloscope test point is available for monitoring skew gate timing.

HDS indicator. Indicates that high density mode has been selected.

EOT indicator. Indicates when tape has reached or passed end of tape.

LOAD POINT indicator. Indicates when tape is at load point.

CYCLE pushbutton. An interlocked pushbutton which runs tape in alternating forward and reverse modes. Useful for making ramp or vacuum sensor adjustments. Depressing STOP pushbutton terminates this operation.

FAST FORWARD pushbutton. An interlocked pushbutton switch that allows tape unit to run forward at fast speed. Depressing STOP pushbutton or EOT marker terminates this operation.

REVERSE RUN pushbutton. An interlocked pushbutton switch that allows tape unit to run in reverse at normal speed. Depressing STOP pushbutton or load point marker terminates this operation.

FORWARD RUN pushbutton. An interlocked pushbutton switch that allows tape unit to proceed forward at normal speed. Depressing STOP pushbutton or EOT marker terminates this operation.

STOP pushbutton. An interlocked pushbutton switch that terminates all tape motion,

WRITE TEST pushbutton and indicator. A momentary pushbutton which programs 1's to be written on all channels to facilitate write skew adjustment. WRITE TEST remains active in FORWARD RUN mode only. (STOP pushbutton must be depressed and TEST MODE selected to actuate this feature.) The indicator remains illuminated while unit is in this mode.

TEST MODE pushbutton and indicator. A momentary pushbutton selects test mode and activates test panel. When indicator is illuminated, test panel is active. (Tape unit must be off line and STOP pushbutton depressed before test panel will function.)

## Figure 4-2. Test Panel Controls and Indicators

complete control over tape speed and direction, it can initiate a write test by generating a crystal controlled all-1 test pattern on the tape. The test panel also contains indicator lamps which illuminate when there is excessive skew, high density is selected, end of tape or load point is reached, or a write test is being performed. (The skew test indicates proper alignment of the read/write head.)

The test panel contains a CYCLE pushbutton. When pressed, it runs the tape forward and reverse continusously to facilitate ramp time and reel servo adjustments.

#### 4.7.2 OPERATION

Pressing the TEST MODE pushbutton activates the test panel if the Model 9100 is off line with the STOP pushbutton on the control panel depressed. The test panel is turned off by either pressing the TEST MODE pushbutton to release it or by pressing the ON LINE pushbutton on the control panel.

#### 4.8 HUB O RING ADJUSTMENT (FIG. 4-3.)

Object: to lock tape reel firmly to the hub.

If the tape reel is loose with hub locked, check the condition of the neoprene O-ring. This O-ring expands when the locking latch is depressed to secure reel to hub.

- **4.8.1** If the O-ring is not worn, but the reel won't seat firmly:

- a. Loosen hub setscrew until the inner hub turns freely.

- b. With hub latch up, rotate inner hub clockwise while restraining the outer hub. This will exert more pressure on the O-ring when the latch is depressed.

- c. Place reel on hub and lock latch to determine whether more or less tightening is required.

#### NOTE

There are several holes in the bottom of the outer hub to accommodate the hub setscrew. Therefore, after adjustent is correct, the hub must be turned slightly until the setscrew fits into one of these holes.

- d. After the correct setting is found, retighten the hub setscrew.

- 4.8.2 If O-ring requires replacement:

- a. Loosen setscrew until inner hub turns freely.

- b. Unscrew inner hub from hub assembly.

Figure 4-3. Hub O-Ring Adjustment

- c. Replace worn O-ring with new O-ring (Kennedy PN 125-0030-006). Prior to installation the new O-ring should be lubricated with silicone grease and wiped, leaving a light lubricating film.

- d. Replace inner hub and readjust O-ring pressure according to paragraph 4.8.1.

## 4.9 TAPE PATH MECHANICAL ALIGNMENT

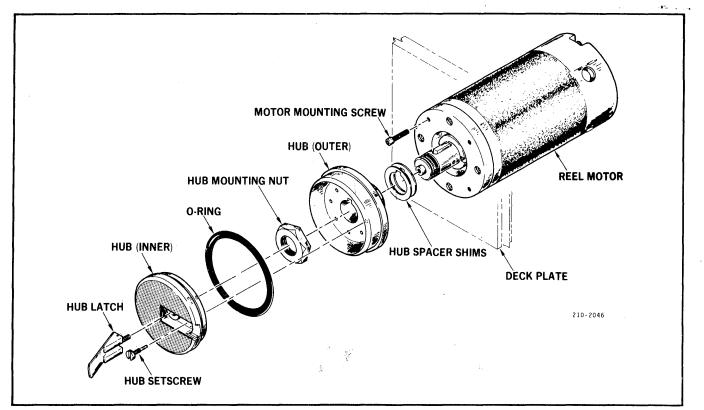

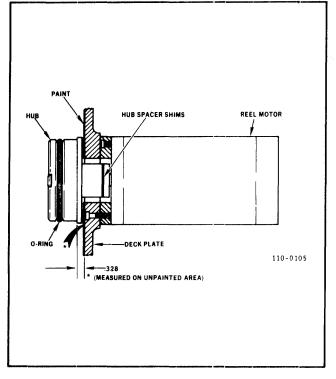

4.9.1 REEL CLEARANCE ADJUSTMENT/ HUB REPLACEMENT (Figures 4-3, 4-4)

Object: To maintain the proper tape path across the top of the hub reel mounting flange and the unpainted area on the deck plate (see Figure 4-3). This measurement should be made with a vernier caliper. A special shim kit, Kennedy PN 198-0100-001) is available for spacing the hub assembly properly.

Procedure:

- a. Loosen hub setscrew and unscrew inner hub.

- b. Insert special spanner wrench (Kennedy PN 154-0042-001) into setscrew holes to stabilize hub. Then remove the hub mounting nut with a socket wrench. Slide remaining portion of the hub assembly off the motor shaft.

- c. Add or remove shims as required to obtain 0.328 inch distance from reel flange to the unpainted portion of the deck plate.

- d. Reassemble hub assembly. Tighten nut to 20 + -5 in./lb torque.

Figure 4-4. Reel Hub Assembly

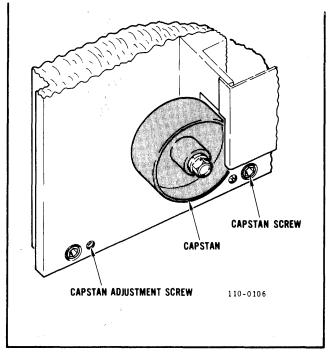

## 4.9.2 CAPSTAN PARALLELISM

The tape should not travel laterally (ride in or out) on the capstan in the forward or reverse mode. To check, observe the tape on the capstan while the machine is in CYCLE mode.

## Adjustment Procedure

Object: to eliminate any lateral tape movement on the capstan during operation.

- a. With tape stopped, loosen capstan screws (see Figure 4-5).

- b. Back off both capstan adjustment setscrews until they no longer touch the capstan motor mounting plate.

- c. Retighten both capstan adjustment setscrews until they press lightly against the capstan motor mounting plate.

- d. Place machine in CYCLE test mode. Observe tape position on the capstan. If tape moves OUTWARD, tighten both adjustment screws equally until OUTWARD lateral movement ceases. If tape moves INWARD, loosen both adjustment screws equally until inward lateral movement ceases.

- e. Retighten capstan setscrews and recheck. If lateral tape movement has been eliminated, adjustment is complete. Otherwise, repeat adjustment procedure.

Figure 4-5. Capstan Parallelism Adjustment

## 4.10 CHECKING SUPPLY VOLTAGES

Here is a list of supply voltages and their test points in the Model 9100.

- +24v case of Q27, Q28, Q31, Q32, Q35 (MJ802), heatsink (+26v under light load)

- -24v case of Q29, Q30, Q33, Q34, Q36 (MJ4502), heatsink (-26v under light load)

- +10v (+0.5,-0.2v) Sensor Amplifier/Driver, test point A

- -10v (+/-0.8) Sensor Amplifier/Driver, test point B

- +5v (+/-0.25) Sensor Amplifier/Driver, test point C

#### NOTE

- (1) Use chassis ground when making voltage measurements.

- (2) Make certain power is switched OFF when removing or replacing circuit boards.

If the voltages are not correct, the trouble is either in the power supply or due to an overload on the power supply. Removing each circuit board while monitoring supply voltage can help isolate the cause of any overload. Also, be sure to check the power supply for burned, open, or shorted components. The power supply is protected against short circuits in its regulated voltage circuitry.

#### 4.11 REEL SERVO ADJUSTMENT

4.11.1 CENTERING ADJUSTMENT (R10, Supply Servo; R69, Takeup Servo)

Object: to center tape in both vacuum columns when tape is stopped.

#### NOTE

Tape loops must be in both vacuum columns during adjustment.

#### Procedure:

- a. Load tape and advance it to load point.

- b. Adjust R10 on the servo preamp until tape loop is center in the supply vacuum column. (Note: While adjusting, make certain tape loops remain within both vacuum columns.)

- c. Repeat steps a and b to adjust R69, the takeup servo zero adjustment. When completed, both reels should be stationary, with the tape centered in both vacuum columns.