# Model 9220

## **Embedded Formatter**

#### FCC CERTIFIED COMPUTER EQUIPMENT

<u>Warning</u>: This equipment generates and uses radio frequency energy and if not installed and used in accordance with the instruction manual may cause harmful interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment.

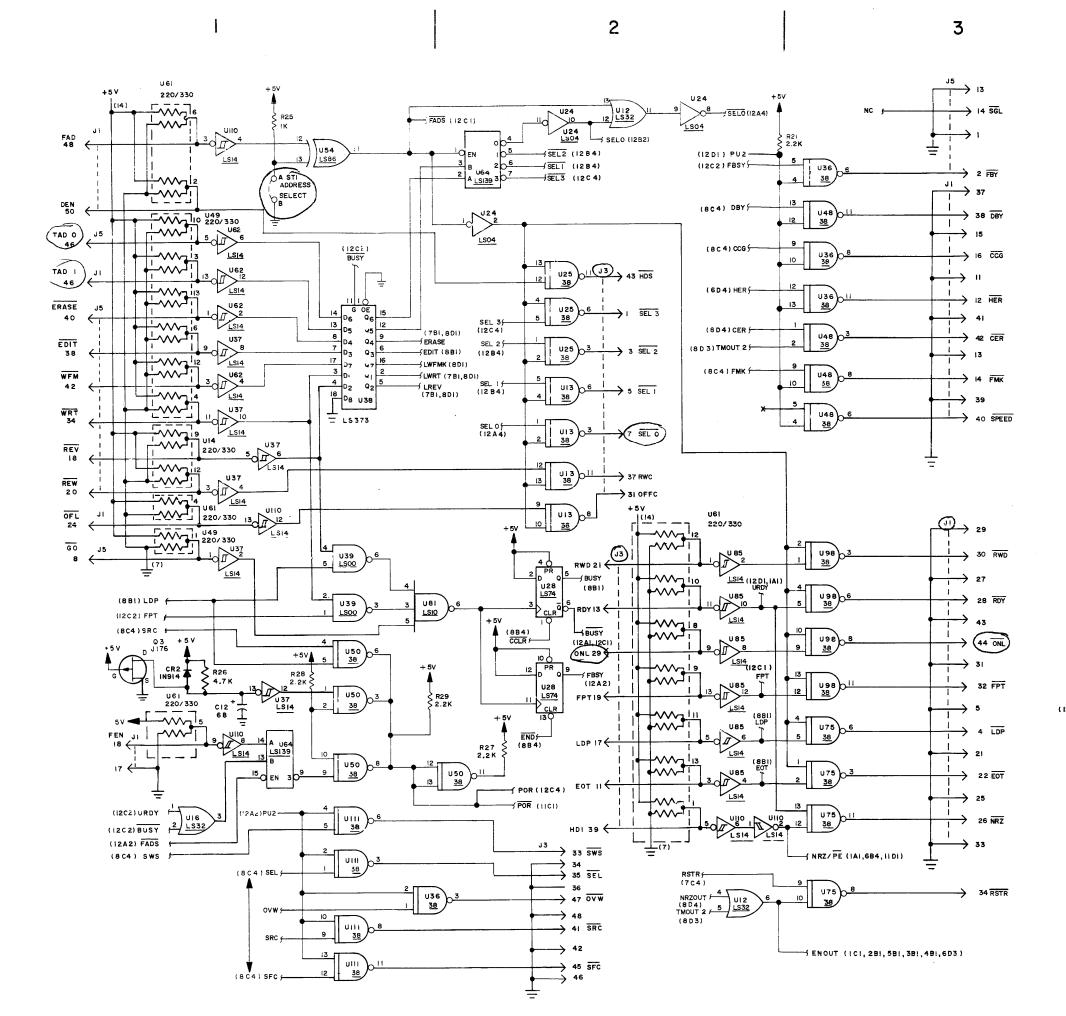

Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### 1.0 INTRODUCTION

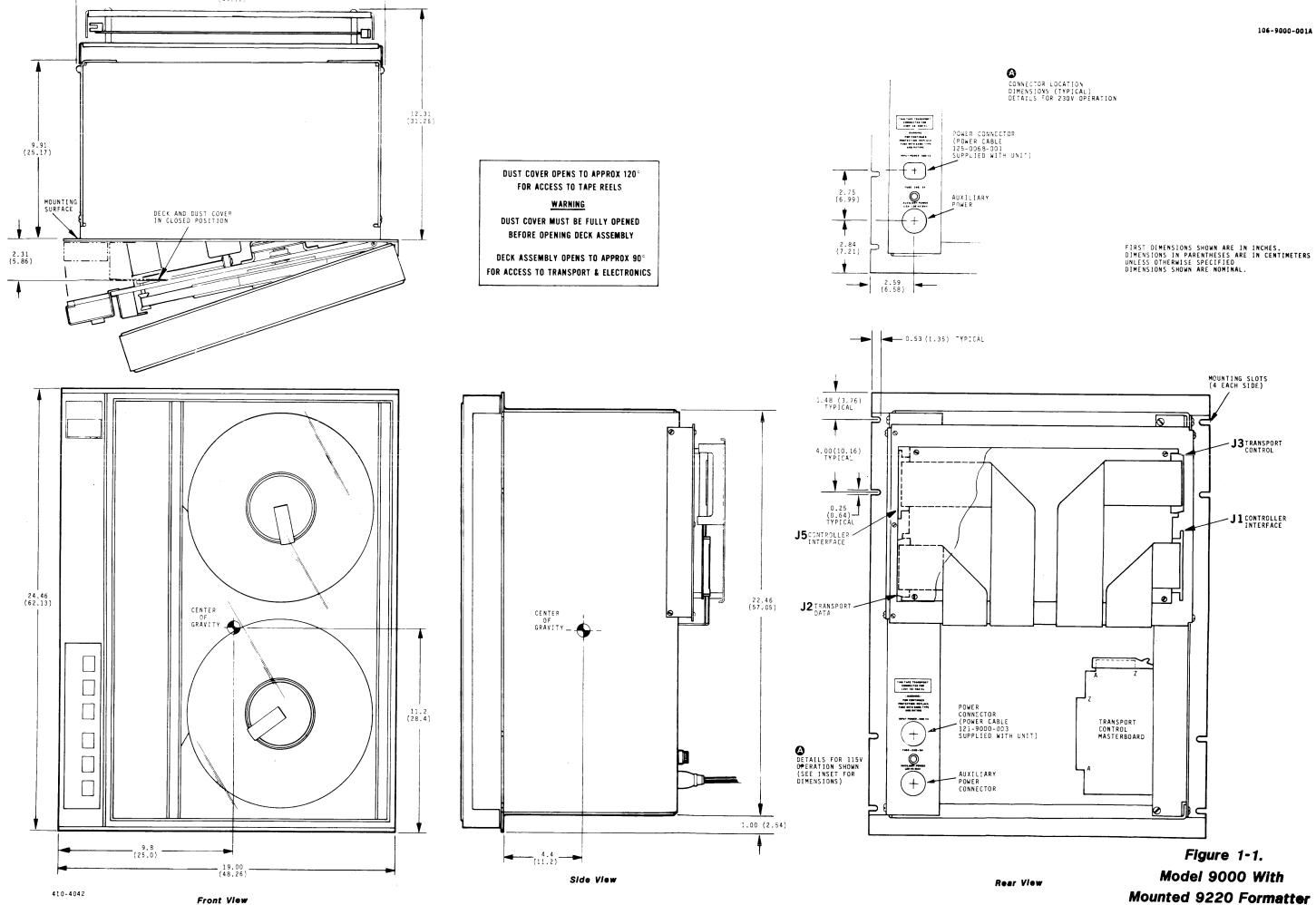

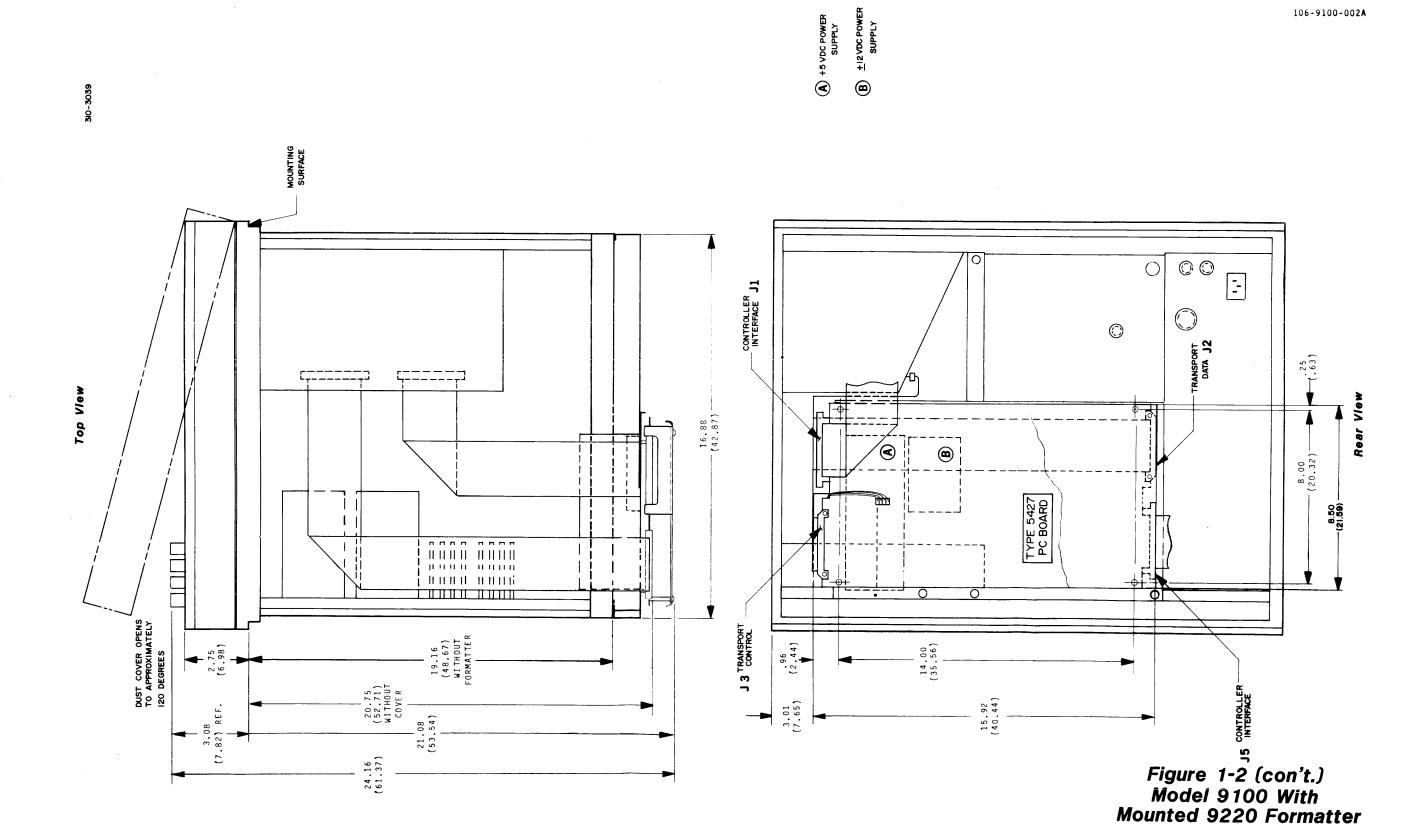

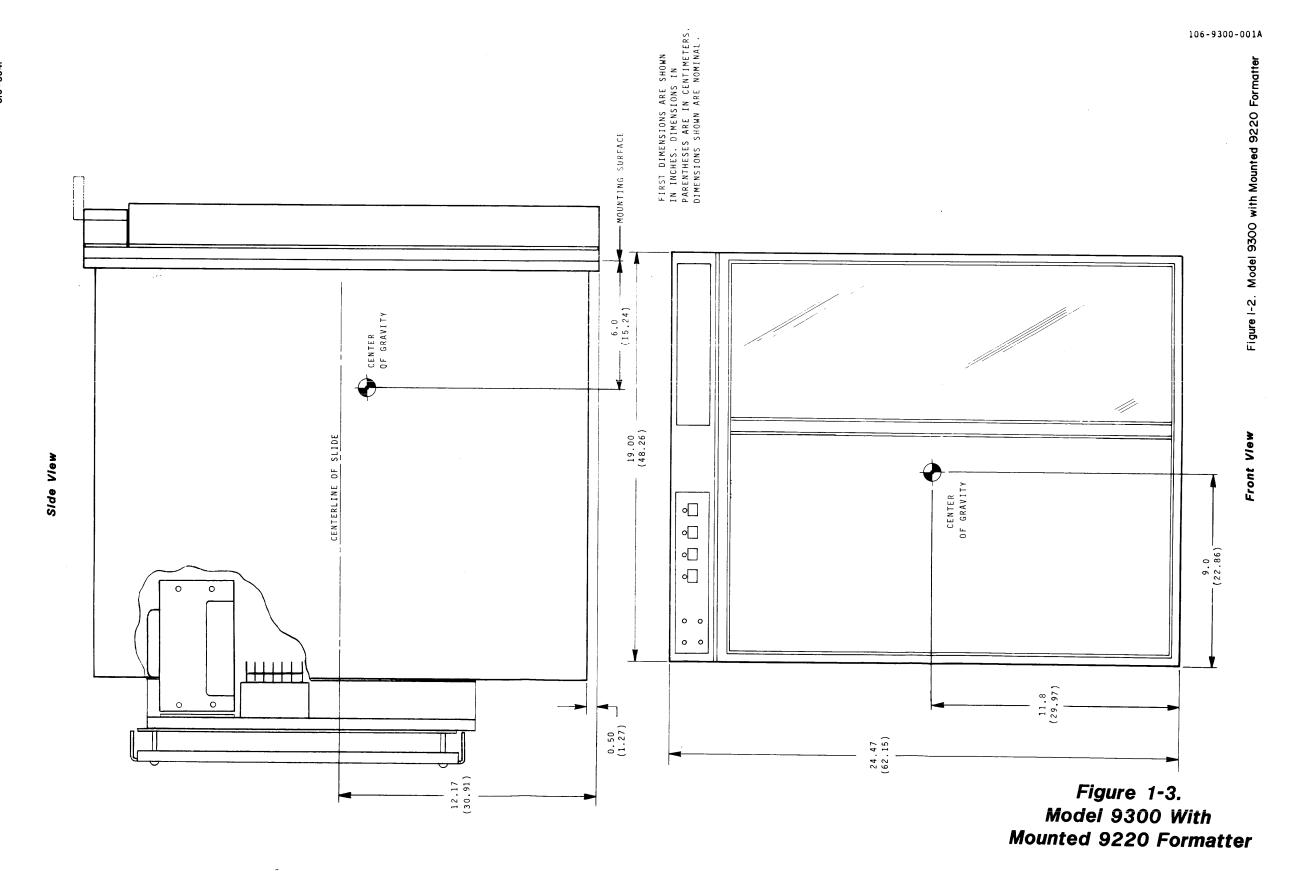

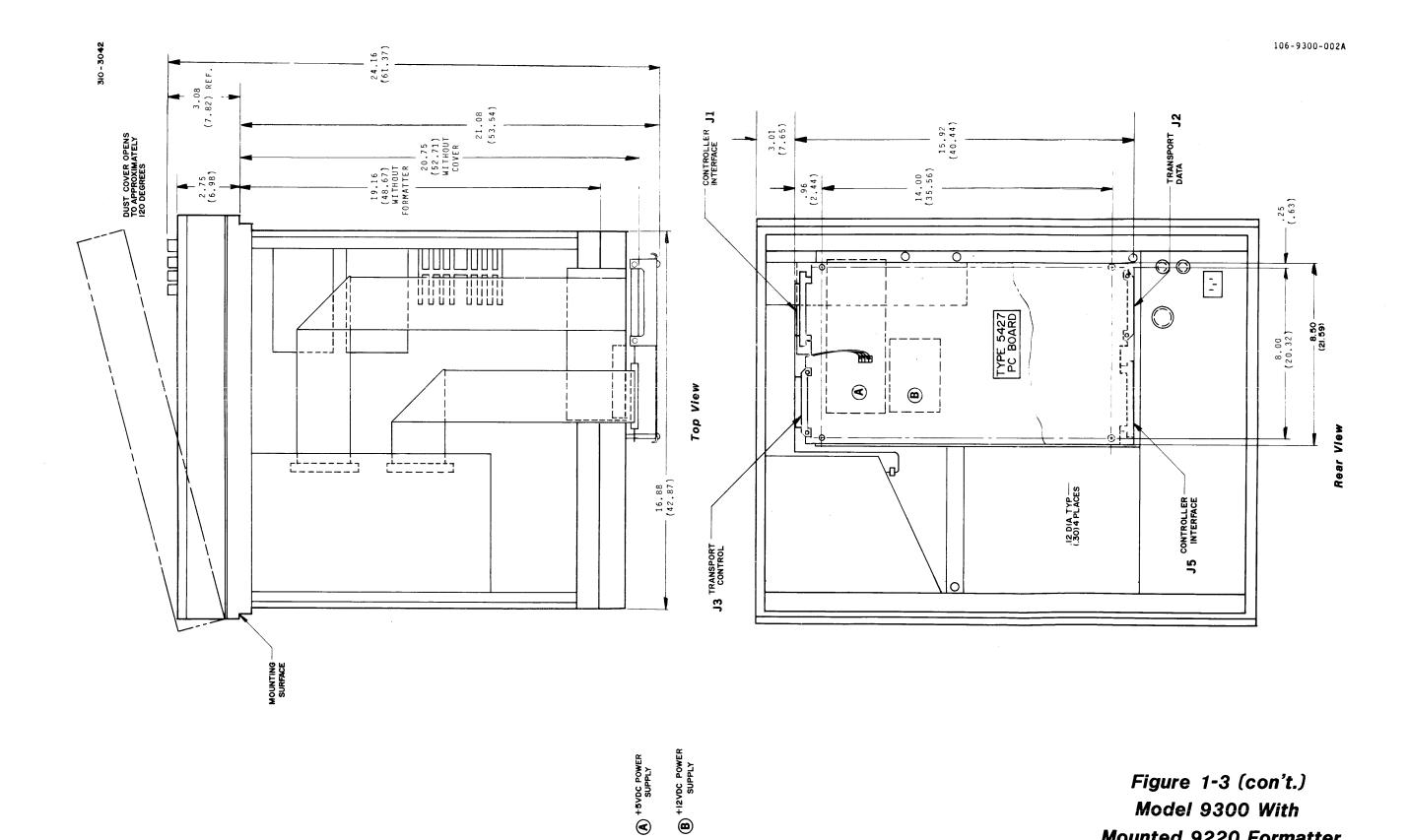

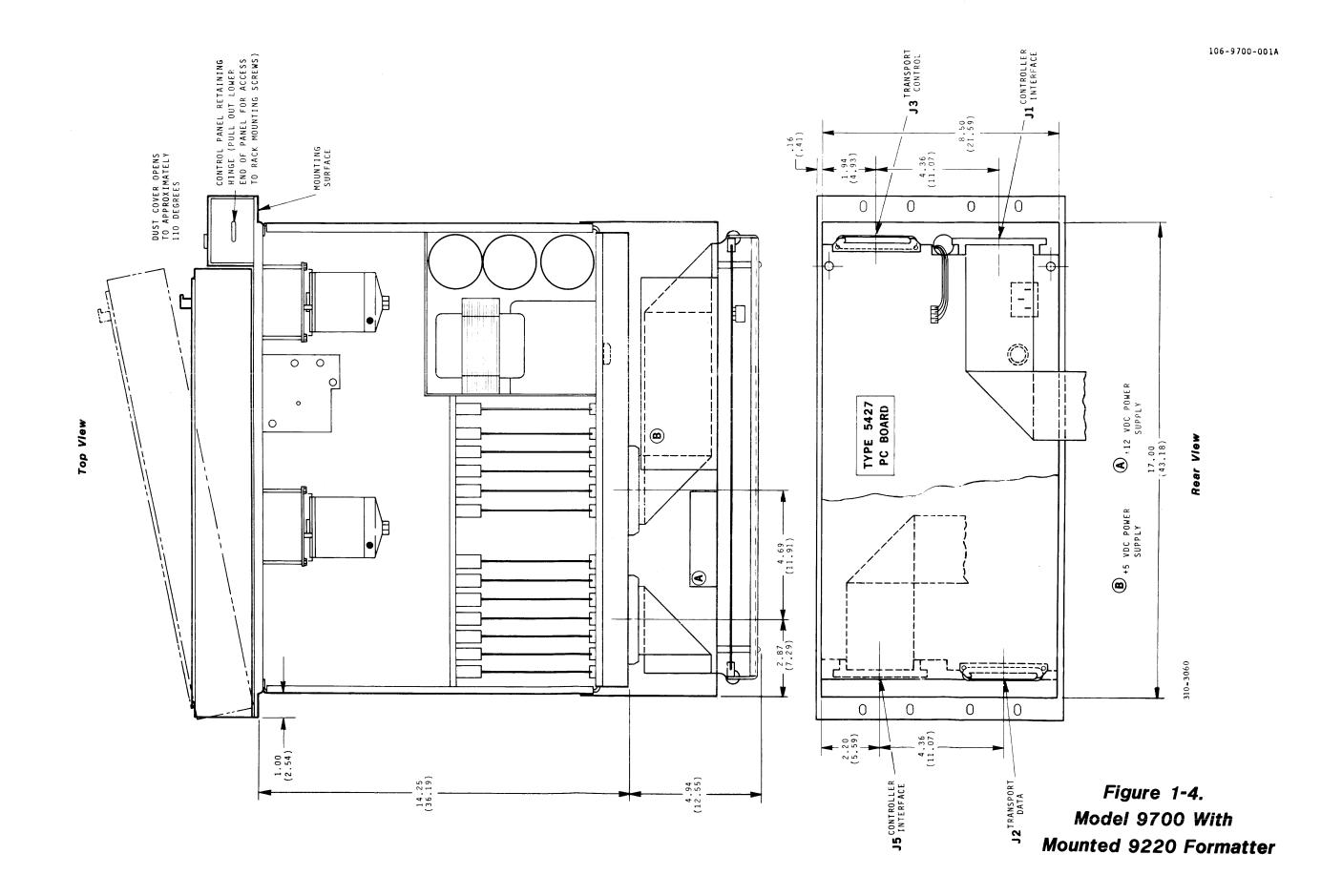

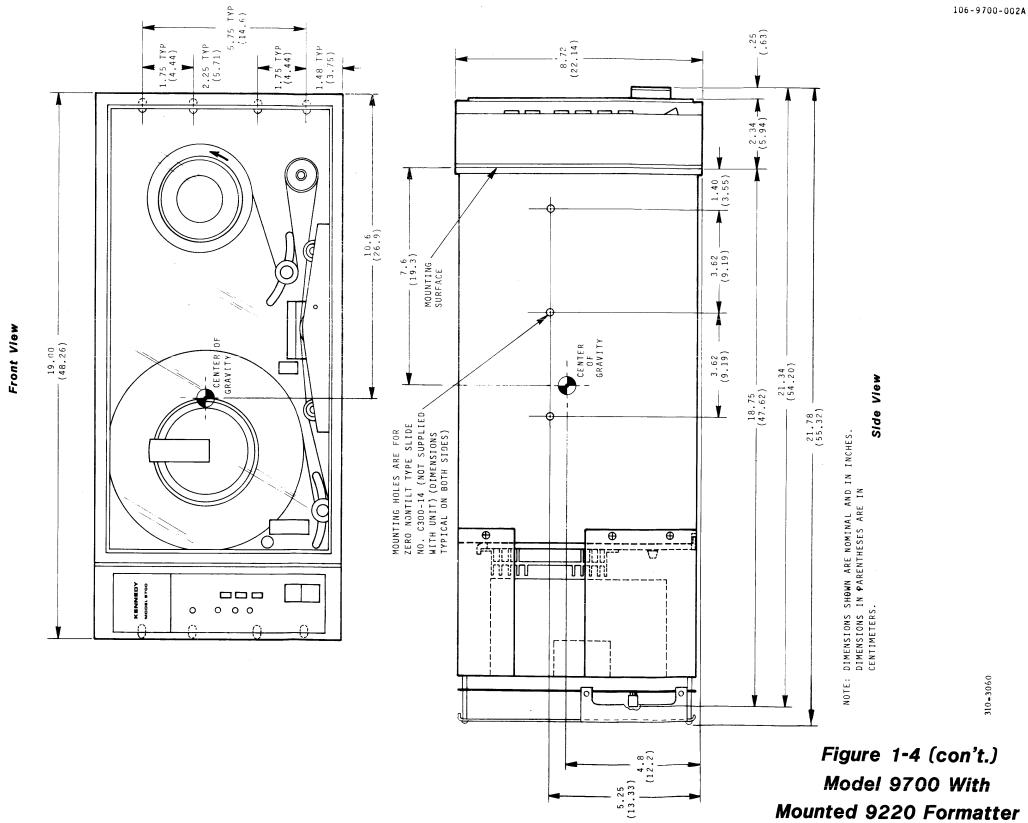

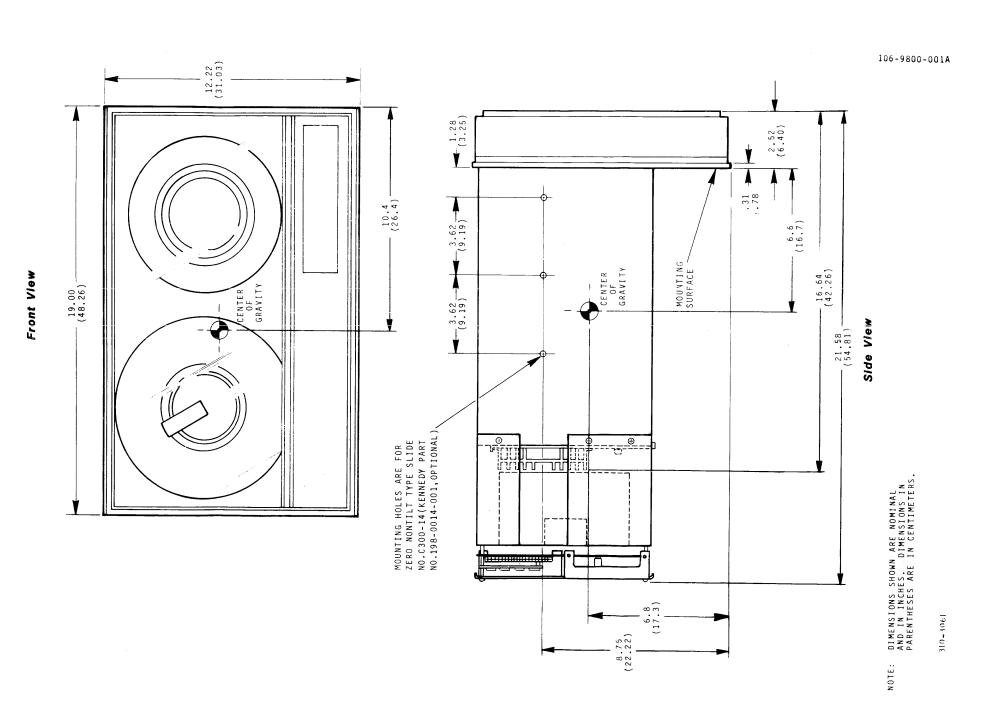

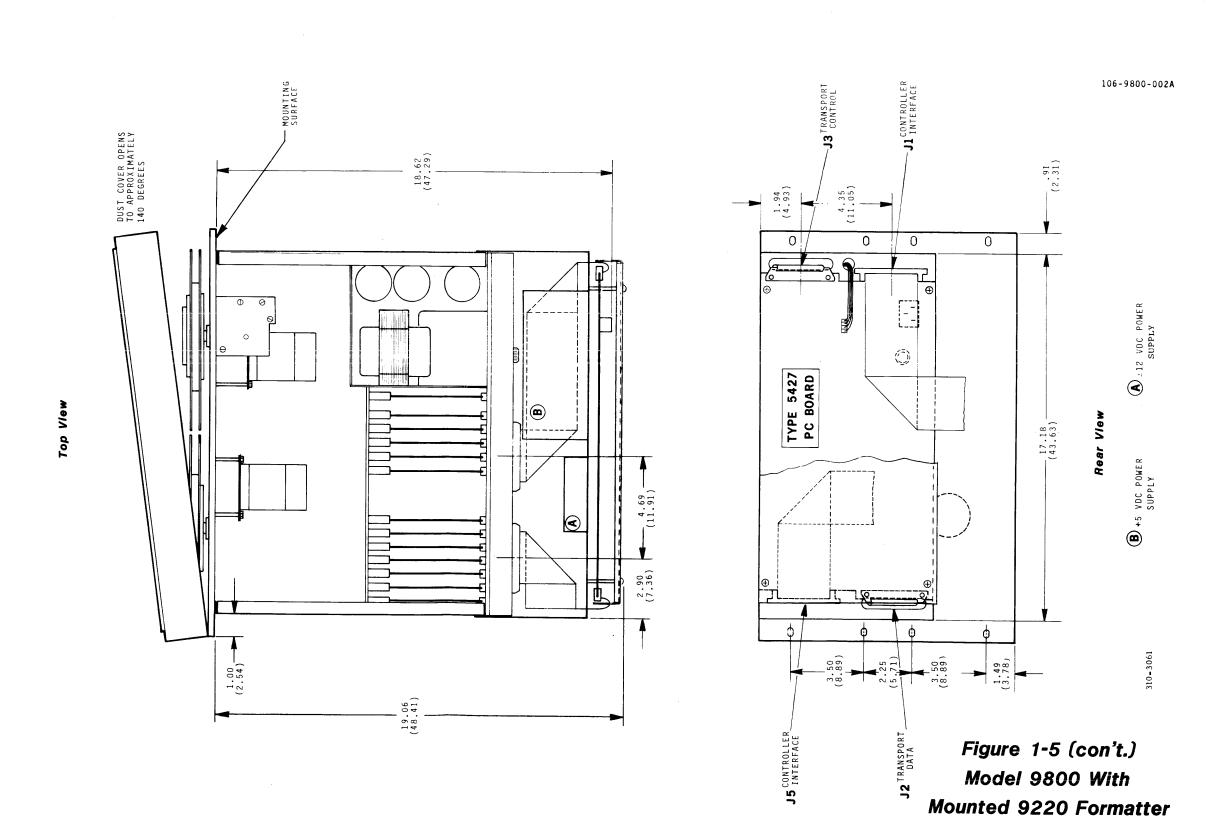

These application notes are provided for the user or system designer and contain information necessary to interface and install the Kennedy 9X00F tape subsystems. Figures 1-1 through 1-5 illustrate the outline and installation drawings of the 9000 Series with the mounted 9220 formatter.

#### 1.1 GENERAL DESCRIPTION

There are five models in the Kennedy tape subsystem line: Models 9000F, 9800F, 9700F, 9100F and 9300F. Seven tape speeds are available from 12.5 ips to 125 ips. Refer to the configuration table and operational specifications given in section 2 for reel size and tape speeds available for each model.

The Kennedy 9X00F consists of a digital synchronous tape transport and embedded formatting control electronics. The control electronics meet all requirements for reading and writing ANSI/IBM compatible 800 cpi NRZI and 1600 cpi PE formats.

#### 1.2 STANDARD FEATURES

- 1. Industry compatible formatter interface

- 2. Signature analysis formatter design

- 3. Offline customer engineering test panel

- 4. Marginal skew check

- 5. Read-after-write shortened skew gate

- 6. Crystal controlled timing

- 7. LED indicators

- 8. Switch selectable addressing

- 9. Quick release hubs

- 10. Modular transport design

- 11. Simplified tape loading

- 12. Variable capacitance tape location detector (Models 9100F/9300F only)

#### 1.3 RELATED DOCUMENTS

- 1. ANSI X3.22 Recorded Magnetic Tape for information interchange (800 cpi, NRZI)

- 2. ANSI X3.39 Recorded Magnetic Tape for information interchange (1600 cpi, PE)

- 3. ANSI X3.40 Unrecorded Magnetic Tape for information interchange (800 cpi, NRZI and 1600 cpi, PE)

- 4. Embedded Formatter Product Specification PN 102-0022-001

- 5. Model 9X00F Operation and Maintenance Manual

- 6. Model 9000 Product Specification PN 102-0025-001

- 7. Model 9000 Operation and Maintenance Manual PN 193-9000-000

- 8. Model 9700 Product Specification PN 102-0026-001

- 9. Model 9700 Operation and Maintenance Manual PN 193-9701-000

- 10. Model 9800 Product Specification PN 102-0027-001

- 11. Model 9800 Operation and Maintenance Manual PN 193-9801-000

- 12. Model 9100 Product Specification PN 102-0019-001

- 13. Model 9100 Operation and Maintenance Manual PN 193-9100-000

- 14. Model 9300 Product Specification PN 102-0020-001

- 15. Model 9300 Operation and Maintenance Manual PN 193-9300-000

Mounted 9220 Formatter

A +5VDC POWER SUPPLY

Figure 1-3 (con't.) Model 9300 With Mounted 9220 Formatter

Figure 1-5.

Model 9800 With

Mounted 9220 Formatter

#### 2.0 SPECIFICATIONS

Although all Kennedy tape subsystems feature a common electrical interface, the various models are uniquely packaged. This section provides mechanical and electrical information to interface 9X00F series Kennedy subsystems with any computer system.

#### 2.1 MECHANICAL SPECIFICATION

Tables 2-1 and 2-2 are summaries of operational specifications for Kennedy tape subsystems. When integrating into a system, it should be noted that the units utilize convection cooling as the sole means of heat dissipation (except Model 9300) and that heat sinks are oriented for vertical transport mounting. A fan is provided in Model 9300 for heat dissipation. The operating range of the units is consistent with normal environments; however, care must be taken when enclosing the units to provide adequate air flow to assure that operating temperature limits will not be exceeded.

In the case of horizontally mounted units, it is suggested that forced air cooling be utilized.

All necessary mounting and interfacing hardware are provided as an installation kit with each unit. Figures 2-1 through 2-5 provide details for rack mounting and installing the various units.

# 2.2 OPERATIONAL SPECIFICATION (MODELS 9100F/9300F)

| 9100                                                             | 9300                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9 track 800 cpi, 1600 cpi,<br>800/1600 cpi                       | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9 Read-after-Write                                               | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NRZI/PE IBM Compatible                                           | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 75 ips                                                           | 125 ips                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| +/-3%                                                            | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| +/-1%                                                            | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 150m inches max 800 cpi<br>200m inches max 556 cpi               | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5 ms +/-0.5 ms at 75 ips<br>Inversely proportional to tape speed | 3 ms +/-0.3 ms at 125 ips                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0.1875 +/-0.0125 inch                                            | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Internally Timed                                                 | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Internally or Externally Generated Internally Generated          | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8.0 oz                                                           | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10.5 inch 2400 feet, 1.5 mil<br>0.5 inch wide tape               | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Single Capstan 180° wrap                                         | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vacuum Column<br>Capacitive                                      | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 200 ips nominal                                                  | 300 ips nominal                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TTL                                                              | Same                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                  | 9 track 800 cpi, 1600 cpi, 800/1600 cpi  9 Read-after-Write  NRZI/PE IBM Compatible  75 ips  +/-3%  +/-1%  150m inches max 800 cpi 200m inches max 556 cpi  5 ms +/-0.5 ms at 75 ips Inversely proportional to tape speed  0.1875 +/-0.0125 inch  Internally Timed  Internally Generated Internally Generated  8.0 oz  10.5 inch 2400 feet, 1.5 mil 0.5 inch wide tape  Single Capstan 180° wrap  Vacuum Column Capacitive  200 ips nominal |

| Model                 | 9100                                         | 9300   |

|-----------------------|----------------------------------------------|--------|

| Subsystem Interface   | TTL Industry Compatible low true             | Same   |

| Physical Dimensions   | 9100                                         | 9300   |

| Mounting              | Standard EIA rack                            | Same   |

| Weight                | 155 lb                                       | 170 lb |

| Power                 | 115 vac +/-10% 48-60 Hz<br>750 watts maximum | Same   |

| Operating Temperature | +2° to 50°C                                  | Same   |

| Altitude              | 0 to 4000 feet                               | Same   |

| Humidity              | 15 to 95% noncondensing                      | Same   |

| Options Available     | High altitude kit, special paint,<br>230 vac | Same   |

Table 2-1

Operational Specification, Models 9100F/9300F

### 2.3 OPERATIONAL SPECIFICATION (MODELS 9000F/9800F/9700F)

| Model                              | 9000 .                                                                             | 9800                                                                               | 9700                                                                               |

|------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Data Density                       | 9 track, 800 cpi,<br>1600 cpi, 800/1600 cpi                                        | 9 track, 800 cpi,<br>1600 cpi, 800/1600 cpi                                        | 9 track 800 cpi,<br>1600 cpi, 800/1600 cpi                                         |

| Number of Tracks                   | 9 Read-after-Write                                                                 | 9 Read-after-Write                                                                 | 9 Read-after-Write                                                                 |

| Format                             | NRZI/PE IBM<br>Compatible                                                          | NRZI/PE IBM<br>Compatible                                                          | NRZI/PE IBM<br>Compatible                                                          |

| Tape Velocity                      | 10-45 ips                                                                          | 10-37.5 ips                                                                        | 10-37.5 ips                                                                        |

| Instantaneous<br>Speed Variation   | +/-3%                                                                              | +/-3%                                                                              | +/-3%                                                                              |

| Long Term<br>Speed Variation       | +/-1%                                                                              | +/-1%                                                                              | +/-1%                                                                              |

| Interchannel<br>Displacement Error | 150m in., max 800 cpi<br>200m in., max 556 cpi                                     | 150m in., max 800 cpi<br>200m in., max 556 cpi                                     | 150m in, max 800 cpi<br>200m in., max 556 cpi                                      |

| Read Data                          | NRZI 9 output levels<br>with Read Strobe<br>PE 9 output levels<br>with Read Strobe | NRZI 9 output levels<br>with Read Strobe<br>PE 9 output levels<br>with Read Strobe | NRZI 9 output levels<br>with Read Strobe<br>PE 9 output levels<br>with Read Strobe |

| Start/Stop Time                    | 15 ms +/-1 ms at 125 ips<br>inversely proportional<br>to tape speed                | 15 ms +/-1 ms at 125 ips<br>inversely proportional<br>to tape speed                | 15 ms +/-1 ms at 125 ips<br>inversely proportional<br>to tape speed                |

| Start/Stop<br>Displacement         | 0.1875 +/-0.0125"                                                                  | 0.1875 +/-0.0125"                                                                  | 0.1875 +/-0.0125"                                                                  |

| Gaps                               | Internally timed                                                                   | Internally timed                                                                   | Internally timed                                                                   |

| Parity (VRC)                       | Internally or                                                                      | Internally or                                                                      | Internally or                                                                      |

| CRC/LRC                            | externally generated Internally generated                                          | externally generated Internally generated                                          | externally generated<br>Internally generated                                       |

| Tape Tension                       | 8.0 (+/-0.5) oz                                                                    | 8.0 (+/-0.5) oz                                                                    | 8.0 (+/-0.5) oz                                                                    |

| Reel Size                          | 10.5", 2400 ft<br>1.5 mil 0.5" wide tape                                           | 8.5 ", 1200 ft<br>1.5 mil 0.5" wide tape                                           | 7", 600 ft<br>1.5 mil 0.5" wide tape                                               |

|                                    |                                                                                    |                                                                                    |                                                                                    |

| Model                           | 9000                                                                   | 9800                                | 9700                                |

|---------------------------------|------------------------------------------------------------------------|-------------------------------------|-------------------------------------|

| Drive System                    | Single Capstan<br>180 wrap                                             | Single Capstan<br>180 wrap          | Single Capstan<br>180 wrap          |

| Servo Buffer Arm<br>Positioning | Electromagnetic                                                        | Electromagnetic                     | Electromagnetic                     |

| Rewind Speed                    | 150 ips nominal                                                        | 120 ips nominal                     | 120 ips nominal                     |

| Electronics                     | TTL                                                                    | TTL                                 | TTL                                 |

| Subsystem Interface             | TTL Industry<br>Compatible low true                                    | TTL Industry<br>Compatible low true | TTL Industry<br>Compatible low true |

| Physical Dimensions             | 9000                                                                   | 9800                                | 9700                                |

| Mounting                        | Standard EIA rack                                                      | Standard EIA rack                   | Standard EIA rack                   |

| Weight                          | 90 lb                                                                  | 45 lb                               | 35 lb                               |

| Power                           | 115 vac +/-10%<br>48-400 Hz<br>UL approved                             | 115/230 vac +/-10%<br>48-500 Hz     | 115/230 vac +/-10%<br>48-500 Hz     |

| Operating Temperature           | +2° to 50°C                                                            | +2° to 50°C                         | +2° to 50°C                         |

| Altitude                        | 0 to 30,000 feet                                                       | 0 to 30,000 feet                    | 0 to 30,000 feet                    |

| Humidity                        | 15 to 95% noncondensing                                                | 15 to 95%<br>noncondensing          | 15 to 95% noncondensing             |

| Options                         | 37.5, 45 ips switch<br>selectable addressing<br>special paint, 230 vac | 25, 37.5 ips<br>special paint       | 25, 37.5 ips<br>special paint       |

Table 2-2 Operational Specification, Models 9000F/9800F/9700F

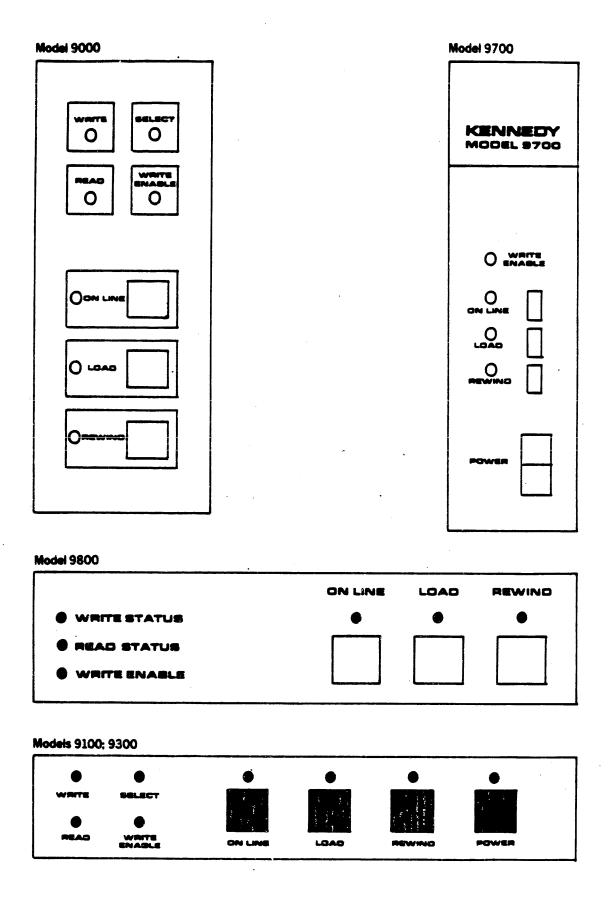

#### 3.1 CONTROLS AND INDICATORS

An illustration of controls and indicators on the series 9X00 transports is shown in figure 3-1. These local controls and indicators are utilized to prepare the transports for operation and to monitor key functions. They are described only to provide greater familiarization with the units.

#### **3.1.1 POWER**

On Models 9100 and 9300, there is a momentary pushbutton switch/indicator which connects line voltage to the power transformer. Models 9000, 9700 and 9800 utilize a power switch only. When power is on: all power supplies are established; all motors are open-circuited (low value resistors are connected across the reel motors), and a reset signal is applied to key control flip-flops.

#### 3.1.2 LOAD

The momentary pushbutton activates the reel servos (tensions tape) and starts the load sequence. Tape runs forward at normal speed to the reflective foil load point marker, then stops. The indicator is illuminated when the reel servos are activated and tape is tensioned.

#### 3.1.3 ONLINE

A momentary pushbutton, which functions as alternate action. When first activated the tape unit is placed in an online condition; when the tape unit is online it can be remotely selected and will be ready if tape is loaded to or past the load point tape marker. When activated again it takes the tape unit offline. The indicator is illuminated in the online condition.

#### 3.1.4 REWIND

This momentary pushbutton activates a rewind operation. This control is enabled only when tape is tensioned and unit is offline. The indicator is illuminated during either a local or remote rewind operation.

Enabling this control causes tape to rewind at the specified speed. On reaching the load point marker, the rewind operation ceases and the load sequence is automatically entered, positioning the tape approximately 0.19 inch beyond the load point marker.

If the REWIND control is depressed and released when tape is at load point (LOAD indicator illuminated), tape rewinds off the takeup reel and tension is lost.

LOAD and REWIND pushbuttons are disabled when the tape unit is online.

#### 3.1.5 READ

Illuminates when tape unit is online, selected and read selected. (This indicator is not available on Model 9700.)

#### 3.1.6 WRITE

Illuminates when tape unit is online, selected and write status selected. Write enable signal must also be true, indicating a tape with a write enable ring mounted on the transport.

#### 3.1.7 SELECT

Illuminates when tape unit is online and selected.

#### 3.1.8 WRITE ENABLE

Write enable is an indicator which is illuminated whenever power is ON and a reel of tape with a write enable ring installed is mounted on the transport.

#### 3.1.9 UNIT SELECT SWITCH

This rotary selector switch is utilized in applications requiring addressing one of several transports. Activating the SLT line corresponding to the address (0-3 or 1-4) selected causes the transport to be selected. This feature is optional on Models 9000, 9700 and 9800, but is standard on Models 9100/9300.

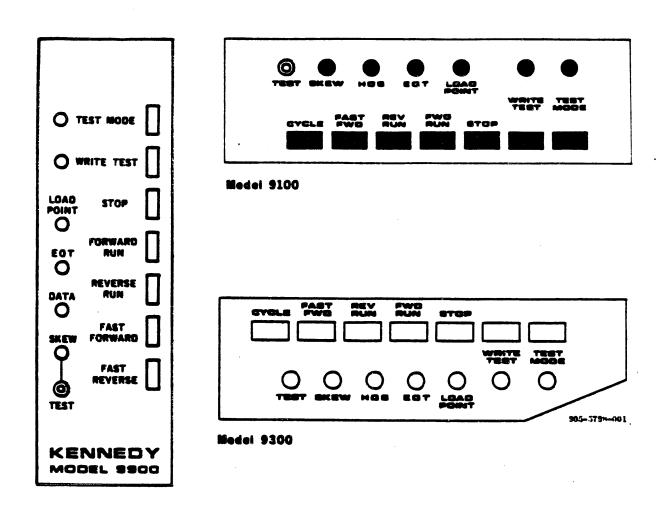

#### 3.2 TEST PANEL

Models 9000, 9100 and 9300 contain test panels which provide a means of exercising, testing and adjusting the tape transport while it is offline, eliminating the need for a separate test fixture or for the use of valuable computer time. (Test panels are optional in models 9700 and 9800.) The test panel can initiate forward and reverse tape motions at either normal or high tape speeds. It can also initiate a write test, generating a crystal controlled all-1s test pattern on tape. The test panel also provides indicators for load point, end of tape and data available. An additional indicator monitors excessive skew and is used to align the read/write head in conjunction with an 800 cpi skewmaster tape. When the head is properly aligned and the data is written on tape properly the SKEW indicator is extinguished.

The controls and interlocks for the test panel are located on the Pushbutton Control card. The skew detect network is located on the Delay Timing module in the read logic section of the transport. The test panel becomes operational only when the transport is offline with the test panel STOP pushbutton depressed. If these conditions are satisfied the test panel pushbuttons are enabled when the TEST MODE pushbutton is pressed.

Figure 3-2 illustrates the test panel of various transports.

Figure 3-1. Control Panel Controls and Indicators

#### 3.2.1 TEST POINT AND SKEW INDICATOR

Indicator lights if tape skew exceeds the appropriate skew (read or write) gate setting. An oscilloscope test point is available for monitoring skew gate timing.

#### 3.2.2 HDS

Indicates that high density mode has been selected. Replaces data LED used with single density units.

#### 3.2.3 EOT

Indicates that tape has reached or passed the reflective end of tape marker.

#### 3.2.4 LOAD POINT

Indicates that tape is at load point.

#### 3.2.5 CYCLE (9100/9300 TRANSPORTS ONLY)

An interlocked pushbutton which runs tape in alternating forward and reverse modes. Useful for making ramp or vacuum sensor adjustments. Depressing STOP pushbutton terminates this operation.

#### 3.2.6 FAST FORWARD

An interlocked pushbutton switch that allows tape unit to run forward at fast speed. Depressing STOP pushbutton or advancing tape to EOT marker terminates this operation.

#### 3.2.7 REVERSE RUN

An interlocked pushbutton switch that allows tape unit to run in reverse at normal speed. Depressing STOP pushbutton or rewinding tape to load point marker terminates this operation.

#### 3.2.8 FORWARD RUN

An interlocked pushbutton switch that allows tape unit to proceed forward at normal speed. Depressing STOP pushbutton or advancing tape to EOT marker terminates this operation.

#### 3.2.9 STOP

An interlocked pushbutton switch that terminates tape motion.

#### 3.2.10 WRITE TEST

A momentary pushbutton which programs 1s to be written on all channels to facilitate write skew adjustment. WRITE TEST remains active in FORWARD RUN mode only. (STOP pushbutton must be depressed and TEST MODE selected to actuate this feature.) The indicator remains illuminated while unit is in this mode.

#### 3.2.11 TEST MODE

This momentary pushbutton selects test mode and activates test panel. When indicator is illuminated, test panel is active. (Tape unit must be offline and STOP pushbutton depressed before test panel will function.)

### 3.2.12 FAST REVERSE (9700/9800/9000 ONLY)

An interlocked pushbutton switch that allows tape unit to run in reverse at specified speed. Depressing STOP pushbutton or rewinding tape to BOT marker will terminate this operation.

#### 3.2.13 DATA

Indicates when data is being processed by read/write electronics.

#### 3.3 OPTIONS

When incorporated in series 9X00 tape transports the type 4843 pushbutton control module allows use of several factory installed optional features. These functions are determined by optional straps and use of components.

#### 3.3.1 AUTO POWER RESTART

With the standard APR option, this circuitry continually monitors the line voltage and whether the tape unit is online or offline. If the external voltage falls below the minimum value required by the tape unit, this option will force the unit into an offline state and issue a BROKEN TAPE command. When the input power level returns to an acceptable value, the APR circuitry will do one of two things, depending on whether the deck was online before the power failure: (1) nothing, if the unit was in an offline state, or (2) load, advance tape several inches and place the unit online if it was previously in an online state.

#### 3.3.2 ON TAPE (OT)

With this option the tape unit cannot be placed online until a reel of tape is loaded and positioned at or past the BOT tab.

Medel 9000; Medel 9900 Test Bez

Figure 3-2

Test Panel Controls and Indicators

#### 4.0 INTERFACE DESCRIPTION

### 4.1 INTERFACE SIGNAL CHARACTERISTICS

Signals from the controller to the 9X00F must conform to the following specifications:

Levels:

Low = True = 0V

High = False = +3V (approx.)

Pulses:

Low = True = 0V

High = False = +3V (approx.)

Minimum Pulse Width:

1.0 microsecond

Total edge transmission delay to be no greater than 200 nanoseconds over 20 foot cable

All output signals from the Model 9X00F are driven by open collector type line drivers capable of sinking up to 36 ma (25 standard unit loads) in the low true state. Open lines will result in false signal levels.

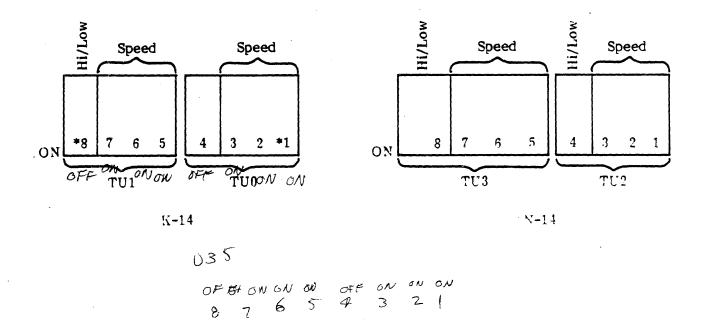

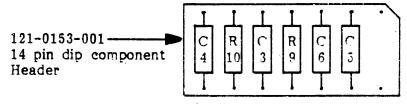

Configuration switches are provided for speed selection. Two speeds may be selected in multidrive phase encoded formatter systems A or B. Any four of seven available NRZI speeds may be selected. Switch settings are given in table 4-5. Component values for the VCO filter are given in table 4-6.

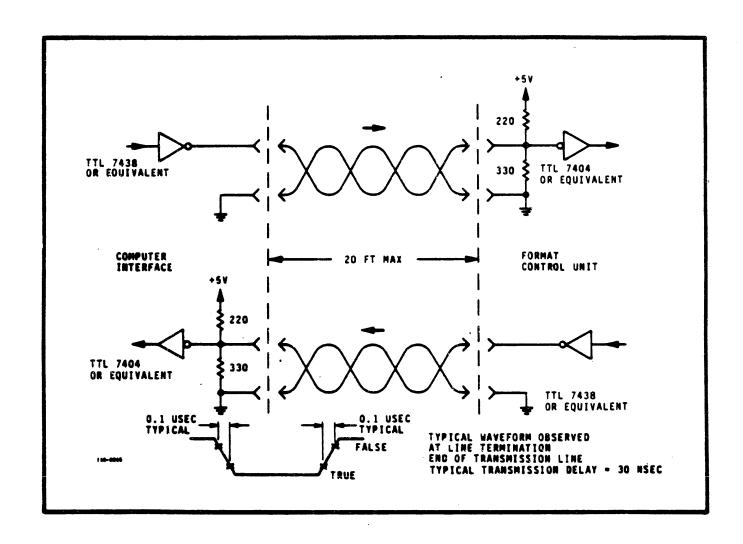

Typical line driver and receiver circuits are shown below in figure 4-1. Twisted pair or ribbon cables with alternate wire ground are required for all inputs and outputs. The maximum recommended length for controller to formatter cables is 20 feet (Pertec compatible). Connector pin assignments and cross reference to 100 pin edge connector are provided in tables 4-1 and 4-3.

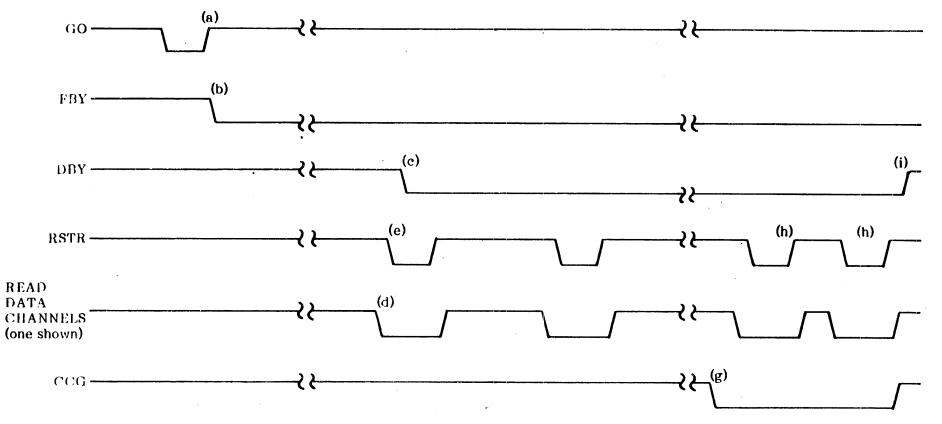

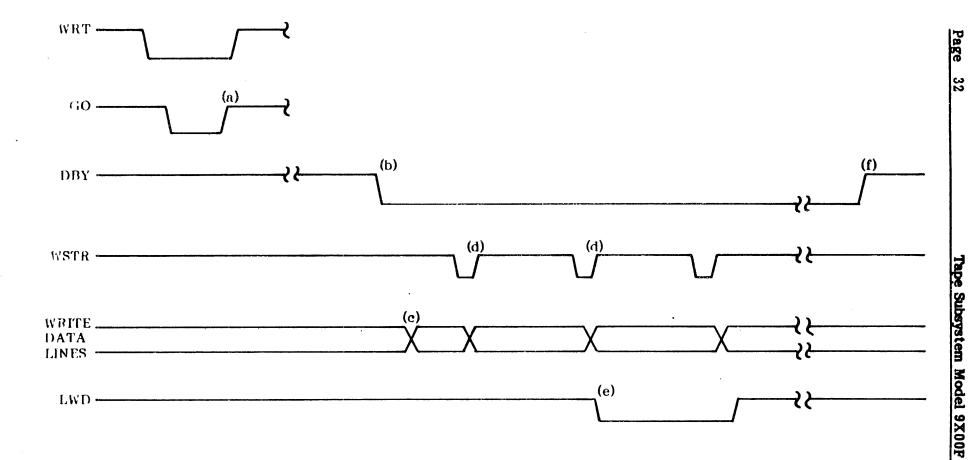

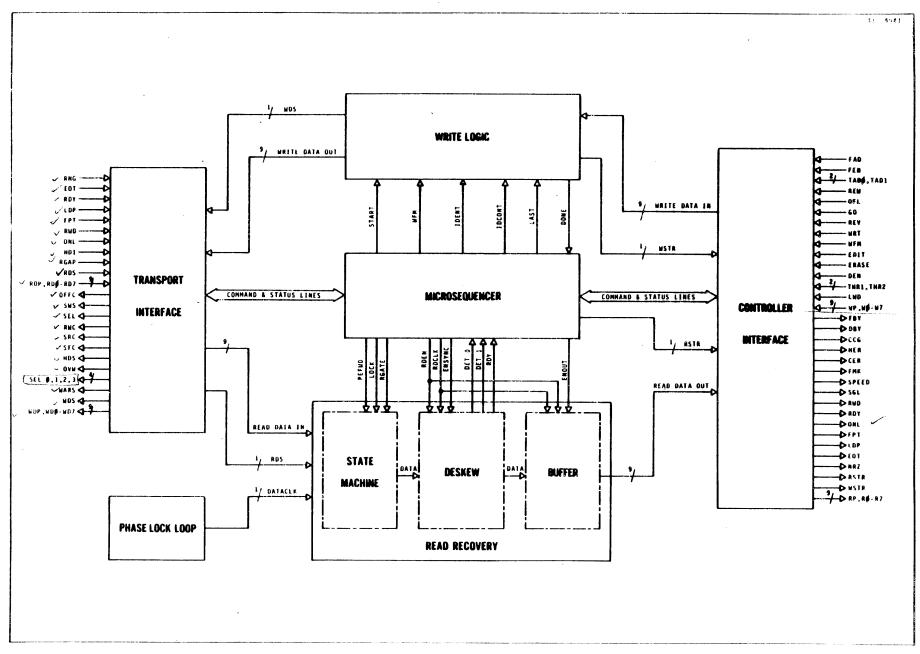

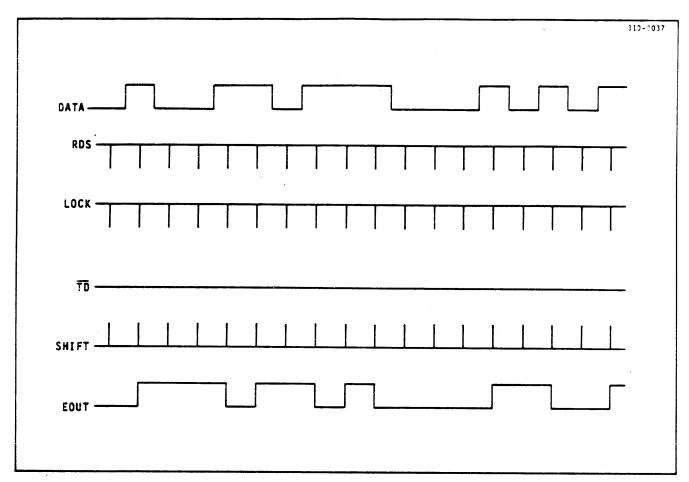

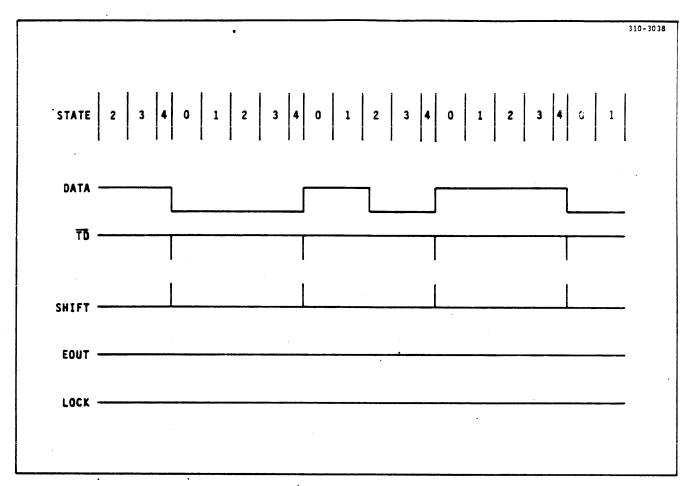

Typical write and read interface timing diagrams are shown in figures 5-1 and 5-2. Commands for Model 9X00F are shown in table 4-2.

### 4.2 INTERFACE INPUT SIGNALS (CONTROLLER TO FORMATTER)

The following paragraphs describe the specifications and functions for each input signal required from the controller to the formatter interface inputs of Model 9X00F. Under the signal name are listed the connector and active pin designation for the input signal line, and the mnemonic designation of the line. An I/O signal list is provided in table 4-1.

FORMATTER ADDRESS FAD

D Level

**B48**

A level which selects one of two formatters. FAD false selects formatter address 0; FAD true selects formatter address 1. The formatter addresses are determined by an address switch on the formatter PCBA. Normally, the formatter must be selected in order to perform any formatter operations. FAD is not latched on go pulse.

Figure 4-1

Typical Interface Configuration

| Mnemonic                                                                       | Level<br>or<br>Pulse                                                                                                                          |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                |                                                                                                                                               |

| FAD TAD0, TAD1 GO REV WRT WFM EDIT ERASE REW DEN OFL LWD FEN WP, W0-W7         | L<br>P<br>L<br>L<br>L<br>P<br>L<br>P<br>L<br>L                                                                                                |

|                                                                                |                                                                                                                                               |

| FBY DBY HER CCG IDENT CER FMK WSTR RSTR RSTR RP, R0-R7 RDY RWD LDP ONL FPT EOT | LLPLLPPPLLLLLLLLLL                                                                                                                            |

|                                                                                | FAD TAD0, TAD1 GO REV WRT WFM EDIT ERASE REW DEN OFL LWD FEN WP, W0-W7  FBY DBY HER CCG IDENT CER FMK WSTR RSTR RP, R0-R7 RDY RWD LDP ONL FPT |

Table 4-1

Input/Output Signal List

TRANSPORT ADDRESS TADO, TAD1

Levels

J5-46; J1-46

The status of these lines determines which of up to four transports are selected by the formatter. The following lists define the tape transport addresses produced as a result of the various TAD0, TAD1.

| TAD0 | TAD1 | ADDRESS |

|------|------|---------|

| 0    | 0    | SLT0    |

| 0    | 1    | SLT1    |

| 1    | 0    | SLT2    |

| 1    | 1    | SLT3    |

Transport addresses are latched by the formatter on go pulse.

#### INITIATE COMMAND

GO

Pulse

J5-8

A pulse which initiates any command specified by the command lines described in the following paragraphs. Information on the command lines is copied in the formatter on the trailing edge of the GO pulse. FBY is set true when the GO pulse is given with the formatter and the selected transport ready.

NOTE: Command lines must be stable 0.5 microsecond before and after.

| (X = Asserted)         | Rev/Fwd | WRT/Rd | WFM | Edit | Erase |

|------------------------|---------|--------|-----|------|-------|

| Read Forward           |         |        |     |      |       |

| Read Reverse           | X       |        |     |      |       |

| Read Reverse (Edit)    | X       |        |     | X    |       |

| Write                  |         | X      |     | ••   |       |

| Write (Edit)           |         | X      |     | X    |       |

| Write File Mark        |         | X      | X   | •• . |       |

| Erase (Variable)       |         | X      |     |      | X     |

| Erase (Fixed)          |         | X      | X   |      | X     |

| Space Fwd Block        |         |        |     |      | X     |

| Space Rev Block        | X       |        |     |      | X     |

| Space Fwd File         |         |        | X   |      | X     |

| Space Fwd File (w/STB) |         | •      | X   |      |       |

| Space Rev File         | X       |        | X   |      | X     |

| Space Rev File (w/STB) | X       |        | X   |      |       |

Table 4-2

Command Table

#### COMMAND LINES

The levels on these lines issue a command to the formatter on the trailing edge of the GO pulse. The REV, WRT, WFM, EDIT, ERASE and DEN levels must be held steady from 0.5 microsecond prior to the edge to 0.5 microsecond following the trailing edge of the GO pulse.

REVERSE

REV

Level

J5-18

A level which initiates reverse tape motion when true. When false, this level specifies forward tape motion.

WRITE

WRT

Level

J5-34

Write mode is specified when this level is true; read mode is specified when this level is false.

WRITE FILE MARK

WFM

Level

J5-42

When this level and WRT are true, the formatter will write a file mark on the tape.

EDIT

**EDIT**

Level

J5-38

EDIT true and REV true modify the read reverse stop delay to optimize head positioning for a subsequent edit operation. When the EDIT level is true and WRT is true, the OVW (overwrite) line is activated and the selected transport operates in the edit mode.

**ERASE**

ERASE

Level

J5-40

ERASE true and WRT true cause the formatter to execute a dummy write command. The formatter will issue a normal write command but no data will be recorded. A length of tape, as defined by LWD, will be erased. When ERASE, WRT/READ and the WFM command lines are true approximately 3.75 inches (9.52 cm) of tape will be erased.

**DENSITY SELECT**

DEN

Level

J1-50

When true, this optional level selects the lower of two possible data transfer packing densities. When this level is false, the higher packing density is selected. This line is not latched by formatter on GO pulse. Also, to be used only with transport in remote density select. Formatter density will be slaved off transport status.

REWIND

REW

Pulse

J5-20

A pulse which causes the transport to rewind to load point. This pulse is directly routed to the transport and does not cause the formatter to go busy.

OFFLINE COMMAND

OFL

**Pulse**

J1-24

This pulse causes the transport to go offline without causing the formatter to go busy.

LAST WORD

LWD

Level

J5-4

When this level is true during a write or erase command, it indicates that the next character to be strobed into the formatter is the last character of the record. LWD goes true when the last data character is placed on the interface lines.

FORMATTER ENABLE

FEN

Level

J1-18

When false, this level causes all formatters in the system to revert to the quiescent state. This line may be used to disable the formatters if controller power is lost or to clear formatter logic when illegal commands or unusual conditions occur.

WRITE DATA PARITY AND WRITE DATA LINES

WP. W0-W7

Levels

(refer to pin list)

These lines are present in both NRZI and PE formatters and will be defined for each application.

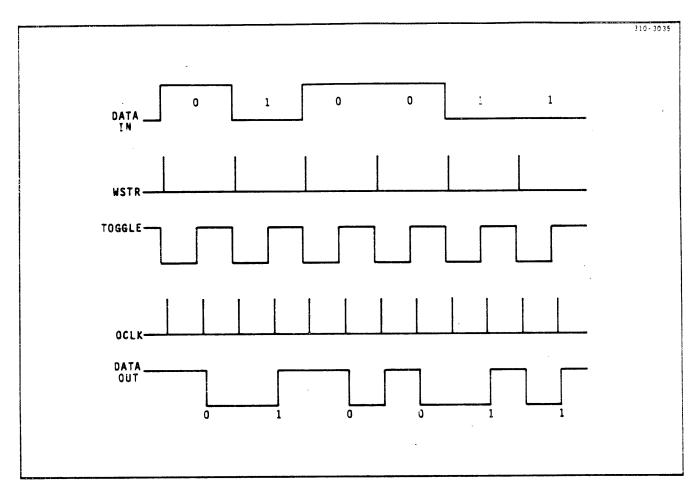

#### (1) NRZI Formatter

These 9 lines transmit write data from the controller to the formatter. Lines WP, W0-W7 are utilized for 9-channel operation.

For 9-channel operation the 8 data bits appearing on W0-W7 are written onto the corresponding channels on tape; W7 corresponds to the least significant bit of the character.

Line WP is optional and is utilized only if it is required to write the parity bit specified by the customer. When this option is not employed the formatter generates odd parity internally on the basis of data contained on W0-W7.

The first character of a record should be available on these lines within one character period after DBY goes true and remain until the trailing edge of the first WSTR is issued by the formatter.

The next character of information must then be placed on these lines within one-half of a character period.

Subsequent characters of a record are processed in this manner until LWD is set true by the controller when the last character is transmitted.

#### (2) PE Formatter

The 8 write data lines (9 in the case of external parity option) are utilized to transmit write data from the controller to the formatter. W0 corresponds to the most significant bit and W7 to the least significant bit of each character.

The first character of a record should be available on these lines less than 40 character periods after DBY goes true and remain until the trailing edge of the first WSTR is issued by the formatter. The next character of information must then be placed on these lines within one-half of a character period.

Subsequent characters of a record are processed in this manner until LWD is set true by the controller when the last character is transmitted.

#### 4.3 INTERFACE OUTPUTS (FORMATTER TO CONTROLLER)

Pins J1-16 - J1-15 output the CHECK CHARACTER GATE for NRZI mode and the IDENTIFICATION for PE mode. The controller must allow for this signal when combination NRZI/PE formatting is used. All pulse widths are 1 microsecond wide (minimum).

FORMATTER BUSY

FBY

Level

J5-2

The level goes true on the trailing edge of GO when a command is issued by the controller. FBY will remain true until tape motion ceases.

DATA BUSY

DBY

Level

J1-38

This level goes true when the tape is up to speed, has traversed the IBG, and the formatter is about to write data or look for a read signal on the tape. DBY remains true until data transfer is completed and the appropriate post record delay is completed. DBY goes false when the capstan starts to decelerate the tape. New commands may be issued 0.5 microsecond after DBY goes false.

HARD ERROR

HER

Pulse

J1-12

(NRZI Mode)

When true, this pulse indicates a read error. This line will be true during read operations when one or more of the following occurs:

- (1) Longitudinal parity error

- (2) Improper record format

- (3) CRCC parity error

- (4) Vertical parity error on a data character.

In all cases except a vertical parity error, HER will be pulsed after the complete record has been read. In the case of a vertical parity error, the HER line will be pulsed when a read strobe (RSTR) pulse is issued for the character in error. DBY goes false after all error information has been transferred to the controller.

CORRECTED ERROR

CER

Pulse

J1-42

(PE Mode only)

When true, this pulse indicates that a single track dropout has been detected and the formatter is performing an error correction.

HARD ERROR

HER

**Pulse**

J1-12

(PE Mode)

When true, this pulse indicates that an uncorrectable read error has occurred and that the record should either be reread or rewritten. Here is a table illustrating the possible HER/CER signal combinations, together with their meaning:

| Signal Sta | ates . |                                                                 |

|------------|--------|-----------------------------------------------------------------|

| HER        | CER    |                                                                 |

| 0          | 0 =    | No Error Detected                                               |

| 0          | 1 =    | Single Channel Error                                            |

| 1          | 0 =    | Postamble, VRC ERROR or: Multiple Channel Errors                |

| 1          | 1 =    | Excessive Skew or: Single Channel Failure w/Postamble VRC Error |

HER/CER valid during RDS.

. . . .

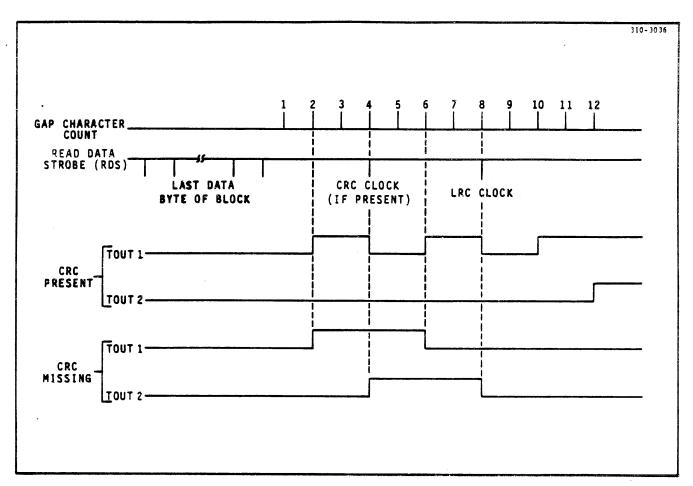

CHECK CHARACTER GATE

CCG

Level

J1-16

(NRZI Mode only)

This level is set true by the NRZI formatter when the read information being transmitted to the controller is a cyclic redundancy check character (CRCC) or a longitudinal redundancy check character (LRCC). When data characters are transmitted, CCG goes false. Data and check information can be distinguished by gating READ STROBE (RSTR) with CCG or its inverse. After leaving load point, J1-16 should be used only when  $\overline{NRZ}/PE$  status indicates NRZI mode.

# \* IDENTIFICATION IDENT

(PE Mode)

Level

J1-16

When true, this level identifies PE tapes. PE tapes are detectable in the read forward mode from load point by the presence of an identification burst on the parity channel. Use with NRZ line.

FILE MARK

Pulse

J1-14

File mark is pulsed when a file mark is detected on the tape during a read operation or during a write file mark operation in a read-after-write transport. The FMK line will be pulsed after a complete file mark record has been read. Error conditions should be ignored when a file mark is detected.

#### TRANSPORT STATUS AND CONFIGURATION LINES

These lines indicate the status and configuration of the selected transport to the controller after being gated with the formatter address signal, FAD. The low true transport status lines are: READY (RDY), ONLINE (ONL), REWINDING (RWD), FILE PROTECT (FPT), LOAD POINT (LP) and END OF TAPE (EOT).

Transport configuration lines are NRZ/PE, 7TK/9TK and LOW/HIGH. Refer to pin list for location.

WRITE STROBE

WSTR

Pulse

J1-36

This line pulses each time a data character is written onto tape. WSTR samples the write data lines WP, W0-W7 from the controller and copies this information character by character into the formatter write logic. The first character should be available prior to the first write strobe pulse and succeeding characters should be set up within half a character period after the trailing edge of each write strobe pulse. The write strobe is also active during variable length erase commands; however, the data being copied into the formatter will have no meaning.

READ STROBE

**RSTR**

Pulse

J1-34

This line consists of a pulse for each character of read information to be transmitted to the controller. These signals should be used to sample the read data lines RDP, RD0-RD7.

In NRZI formatters, the transmission of CRC and LRC data characters will be flagged by the check character gate (CCG) signal as described under HARD ERROR (HER).

READ DATA LINES

RP, R0-R7

Levels

(see pin list)

In the NRZI formatter, RP and R0-R7 are utilized for 9-channel operation; in PE formatters the 9 PE channels are assigned to RP, R0-R7.

Each character read from tape is made available by parallel sampling the read lines with READ STROBE. Since the data remains on the read data lines for a full character period, the corresponding RSTR pulses are timed to occur after approximately the center of the character period.

#### EMBEDDED FORMATTER INTERFACE PIN LIST AND CROSS REFERENCE TO 100 PIN CONNECTOR (J101)

| 1 2                                            | T/C                                                                    |                                                                                                                                 | CROSS REFERENCE TO 100 PIN C                                                                                                                                                                                                                                                                                                     | ONNECTOR (J                                                                                             | 101)                                    |                                                                                                                                                                                                                |

|------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| it of                                          | TE /                                                                   | A Conne                                                                                                                         |                                                                                                                                                                                                                                                                                                                                  |                                                                                                         |                                         | 9219 J101                                                                                                                                                                                                      |

| consider or                                    | Sig                                                                    | Gnd                                                                                                                             | Signal Name                                                                                                                                                                                                                                                                                                                      | Mnemonic                                                                                                | In/Out                                  | Sig Gnd                                                                                                                                                                                                        |

| · -                                            | 2                                                                      | 1                                                                                                                               | Formatter Busy                                                                                                                                                                                                                                                                                                                   | FBY                                                                                                     | Out                                     | B22/B23                                                                                                                                                                                                        |

|                                                | 4                                                                      | 3                                                                                                                               | Last Word                                                                                                                                                                                                                                                                                                                        | LWD                                                                                                     | In                                      | B13/B14 🗸                                                                                                                                                                                                      |

|                                                | 6                                                                      | 5.                                                                                                                              | Write Data 4                                                                                                                                                                                                                                                                                                                     | W4                                                                                                      | In                                      | B19/B20                                                                                                                                                                                                        |

|                                                | 8                                                                      | <b>7</b> ·                                                                                                                      | Initiate Command                                                                                                                                                                                                                                                                                                                 | GO                                                                                                      | In                                      | A3/A2 ✓                                                                                                                                                                                                        |

|                                                | 10                                                                     | 9.                                                                                                                              | Write Data ()                                                                                                                                                                                                                                                                                                                    | W O                                                                                                     | In                                      | B16/B17                                                                                                                                                                                                        |

|                                                | 12                                                                     | 11                                                                                                                              | Write Data 1 Single                                                                                                                                                                                                                                                                                                              | W1                                                                                                      | In                                      | A16/A17                                                                                                                                                                                                        |

|                                                | 14                                                                     | 13                                                                                                                              | Single \ com                                                                                                                                                                                                                                                                                                                     | SGL                                                                                                     | Out                                     | A33/A32                                                                                                                                                                                                        |

| -                                              | - 16                                                                   | 15                                                                                                                              | (+5v)                                                                                                                                                                                                                                                                                                                            | +5V                                                                                                     | Out                                     | A48, 49, 50 -                                                                                                                                                                                                  |

|                                                | /18                                                                    | 17                                                                                                                              | Reverse/Forward                                                                                                                                                                                                                                                                                                                  | REV                                                                                                     | In                                      | B4/B5 -                                                                                                                                                                                                        |

|                                                | 20                                                                     | 19                                                                                                                              | Rewind                                                                                                                                                                                                                                                                                                                           | REW                                                                                                     | In                                      | B12/B11 🗸                                                                                                                                                                                                      |

|                                                | 22                                                                     | 21                                                                                                                              | Write Data Parity                                                                                                                                                                                                                                                                                                                | WP                                                                                                      | In                                      | A15/A14                                                                                                                                                                                                        |

|                                                | 24                                                                     | 23                                                                                                                              | Write Data 7                                                                                                                                                                                                                                                                                                                     | W7                                                                                                      | In                                      | A21/A20 -                                                                                                                                                                                                      |

|                                                | 26                                                                     | 25                                                                                                                              | Write Data 3                                                                                                                                                                                                                                                                                                                     | W 3                                                                                                     | In                                      | A18/A17 -                                                                                                                                                                                                      |

|                                                | 28                                                                     | 27                                                                                                                              | Write Data 6                                                                                                                                                                                                                                                                                                                     | W6                                                                                                      | ln                                      | B21/B20 ~                                                                                                                                                                                                      |

|                                                | 30                                                                     | 29                                                                                                                              | Write Data 2                                                                                                                                                                                                                                                                                                                     | W 2                                                                                                     | In                                      | B18/B17 ~                                                                                                                                                                                                      |

|                                                | 32                                                                     | 31                                                                                                                              | Write Data 5                                                                                                                                                                                                                                                                                                                     | W5                                                                                                      | In                                      | A19/A20~                                                                                                                                                                                                       |

|                                                | 34                                                                     | 33                                                                                                                              | Write Data 3                                                                                                                                                                                                                                                                                                                     | WRT                                                                                                     | In .                                    | A4/A5 ~                                                                                                                                                                                                        |

|                                                | 36                                                                     | 35<br>35                                                                                                                        | Read Threshold Level 2 (not used)                                                                                                                                                                                                                                                                                                | THR2                                                                                                    | In                                      | B9/B8 ~                                                                                                                                                                                                        |

|                                                | 38                                                                     | 37                                                                                                                              | Edit                                                                                                                                                                                                                                                                                                                             | EDIT                                                                                                    | In                                      | A6/A5 ~                                                                                                                                                                                                        |

|                                                | 40                                                                     | 39                                                                                                                              | Erase .                                                                                                                                                                                                                                                                                                                          | ERASE                                                                                                   | In                                      | B7/B8 ~                                                                                                                                                                                                        |

|                                                | 40                                                                     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |                                                                                                         |                                         |                                                                                                                                                                                                                |

|                                                |                                                                        | 41                                                                                                                              | Write File Mark                                                                                                                                                                                                                                                                                                                  | WFM                                                                                                     | In<br>In                                | Doi: DO                                                                                                                                                                                                        |

|                                                | 44                                                                     | 43                                                                                                                              | Read Threshold Level 1 (not used)                                                                                                                                                                                                                                                                                                | THR1                                                                                                    | In<br>*                                 | A7/A8 ~                                                                                                                                                                                                        |

| -                                              | ~ 46<br>48                                                             | 45                                                                                                                              | Transport Address 0                                                                                                                                                                                                                                                                                                              | TAD0                                                                                                    | In<br>Out                               | A1/A2                                                                                                                                                                                                          |

| Ŷ                                              |                                                                        | 47                                                                                                                              | Read Data 2                                                                                                                                                                                                                                                                                                                      | R2                                                                                                      | Out                                     | 13037 500                                                                                                                                                                                                      |

| ( 0                                            | 50                                                                     | 49                                                                                                                              | Read Data 3                                                                                                                                                                                                                                                                                                                      | R3                                                                                                      | Out                                     | A39/A38                                                                                                                                                                                                        |

|                                                |                                                                        |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |                                                                                                         |                                         |                                                                                                                                                                                                                |

| $\mathcal{L}$                                  | J1 (                                                                   | B Conne                                                                                                                         | ctor)                                                                                                                                                                                                                                                                                                                            |                                                                                                         |                                         | 9219 J101                                                                                                                                                                                                      |