# HYBRID COMPUTER SYSTEM REQUEST FOR PROPOSAL

JANUARY 1966

Lockheed

MISSILES & SPACE COMPANY

A GROUP DIVISION OF LOCKHEED AIRCRAFT CORPORATION

# LOCKHEED MISSILES & SPACE COMPANY

HYBRID COMPUTER

ANALOG SECTION

# INSTRUCTIONS TO BIDDERS

Bidders must respond to all numbered items. If Bidder wishes to take exception to any requirement, he may do so provided he includes a section of his proposal labled EXCEPTIONS and clearly indicates which item or items where he has taken an exception.

Bidders are to provide price breakdowns for all two digit numbered items in Sections 1, 2, 3, and 4.

Bidders are to provide their own guaranteed specifications whice are called for in Section 5, and must provide the information on the forms provided in Section 10. Other specification information will be considered only if the Method of Measurement is clearly defined. It is requested that if other specification information is included, that the formats in Section 10 be used where applicable.

Bidders proposals must contain a clear description of all aspects of their computer systems and peripheral equipment. It is requested that where possible the descriptions follow the outline in Sections 1 through 4.

Additional options will be considered if bidder clearly shows that there will be no reduction in computing capability and what advantage the option would provide to Lockheed Missiles and Space Company.

Any computing element proposed must be available for demonstration and testing under system operating conditions at any time after receipt of proposals.

# STATEMENT OF REQUIREMENTS:

The intent of this procurement is to purchase five identical analog computer systems containing all solid state computing components of the highest static accuracy and best dynamic performance.

- 1.0 Minimum Complement of computing components for each of five analog computer systems:

- 1.1 Analog computer console and cabinets completely wired with all necessary power supplies and operating controls.

- 1.1.1 Console shall contain an overload indicator system.

- 1.1.2 Console shall contain an oscilloscope display system.

- 1.1.3 Console shall contain a Rate Test feature.

- 1.1.4 Console shall contain a temperature controlled capacitor oven.

- 1.1.5 Console shall contain a shielded analog patch bay.

- 1.1.6 Console shall contain an Electronic Digital VoltMeter.

- 1.1.7 Console shall contain a transistor VoltMeter.

- 1.1.8 Console shall contain a reference voltage system. Voltage may be any level. The reference system will be capable of being slaved to any one of the four other consoles.

- 1.1.9 Console shall contain a reference divider system capable of local and remote operation. Remote mode must be capable of accepting inputs from a digital computer or an automatic set up device.

- 1.1.10 Console shall have a mode control system capable of local and remote operation. Remote mode must be capable of accepting inputs from any other analog computer, either one of two digital computers, or an automatic set up device.

- 1.1.11 Console shall contain an addressing system that can select any computing component. Addressing system must be capable of local and remote operation. Remote mode must be capable of accepting address from either one of two digital computers or an automatic set up device.

- 1.1.12 Console shall contain a power supply monitor system capable of reading all the power supplies in the analog computer system on the EDVM, TVM or oscilloscope.

# 1.2 60 Integrators

- 1.2.1 Each capable of summer, integrator or high gain operation.

- 1.2.2 Each having the capability of at least six input resistors, 3 providing gains of one, and 3 providing gains of 10 when a normal feedback resistor is used.

- 1.2.3 Each having the capability of a selection of an integration time constant of one second, one hundred milliseconds, ten milliseconds and one millisecond, when used with a standard gain of one input resistor.

- 1.2.4 One third or more of the integrators should have the capability of selecting an integration time constant of ten seconds when used with a standard gain of one input resistor.

- 1.2.5 Each having the capability of electronic switching mode control for Initial Condition, Hold and Operate modes.

- 1.2.6 Each having the capability of independent mode control for Initial Condition, Hold, and Operate modes.

- 1.2.7 Each having the capability of holding the input network's summing junction to zero volts in the Pot Set and Initial Condition modes.

- 1.2.8 Each having the initial condition summing junction available on the patchboard.

- 1.2.9 Each having the capability of having the initial rate from the input summing junction available for readout in the initial condition and static check modes.

#### 1.3 60 Summers

- 1.3.1 Each capable of summer or high gain operation.

- 1.3.2 Each having the capability of at least six input resistors,3 providing gains of one, and 3 providing gains of 10 when a normal feedback resistor is used.

- 1.3.3 Each having the capability of holding the input network's summing junction to zero volts in the Pot Set mode.

#### 1.4 240 Potentiometers

- 1.4.1 20 Potentiometers are to be three terminal manual set with a ground connection to be made by a bottle plug.

- 1.4.2 All potentiometers except the three terminal are to be servo set.

- 1.4.3 All potentiometers except the three terminal are to be phase shift compensated.

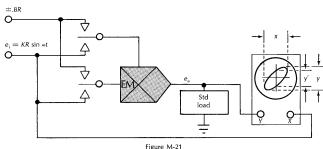

#### 1.5 90 Electronic Multipliers

1.5.1 Approximately one half of the multipliers should be class 2, accepting +x and +y from low impedances source and providing a low impedance output.

- 1.5.2 Approximately one forth of the multipliers should be class 3, accepting +x and -y from a low impedance source and providing a low impedance output, or accepting +x and +y from a low impedance source and providing a current output. The patchboard configuration should be such that the programmer has the option for either mode of class 3 operation as well as providing for division and square root modes.

- 1.5.3 Approximately one forth of the multipliers will normally be associated with the Electronic Resolvers, but will be available as multipliers as a programmer option when resolvers are not used.

#### 1.6 6 Electronic Resolvers

- 1.6.1 Each resolver shall be capable of polar to rectangular conversion of 2 two dimensional vectors.

- 1.6.2 Each resolver shall be capable of rectangular to polar conversion of a two dimensional vector.

- 1.6.3 Each resolver shall be capable of continuous resolution in both the polar to rectangular and rectangular to polar modes.

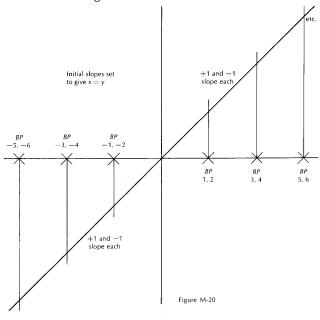

# 1.7 24 Stored Program Dioded Function Generators

- 1.7.1 Each function generator shall be set by a pre-programmed device such as a card, special board, or digital computer.

- 1.7.2 Each function generator shall have at least ten segments plus a parallax adjustment.

- 1.7.3 Both the breakpoints and slope shall be adjustable.

- 1.7.4 Each function generator should be class 1, accepting x from a low impedance source and providing f(x) as a low impedance output.

- 1.7.5 Pairs of function generators, by a programmer option, may be combined for twenty segment operation.

#### 1.8 30 Feedback Limiters

- 1.8.1 Each limiter must be adjustable over the entire reference voltage range.

- 1.8.2 Each limiter shall provide hard limiting for summers and integrators.

## 1.9 30 Comparators

1.9.1 Each comparator will have its output and complemented output available in the logic area.

#### 1.10 30 Electronic Switches

1.10.1 Each switch shall be capable of being controlled by any logic signal in the logic area.

- 1.10.2 Each switch shall be capable of switching voltages over the entire reference voltage range.

- 1.11 24 Relays

- 1.11.1 Each relay shall be double pole double throw.

- 1.11.2 Each relay shall be capable of being set by any logic signal in the logic area.

- 1.12 15 Function Switches1.12.1 Each function switch shall be single pole triple throw.

- 1.13 200 Analog Trunks

- 1.14 250 Logic Units

- 1.14.1 A logic unit is defined as a gate, flip flop, one shot, each stage of a shift register, each binary stage of a counter, etc.

- 1.14.2 Each logic unit will have both true and complemented outputs available.

- 1.14.3 The logic may be either synchronous or asynchronous, but if the latter, a clock must be available at the patchboard.

- 1.14.4 The logic board will have at least 100 trunk lines.

- 1.15 10 Analog Patchboards

1.15.1 Analog patchboards are to provide shielding for patch cords.

- 1.17 10 Logic Patchboards

- 1.18 500 Logic Patching Elements

1.18.1 Logic patching elements are patch cords, bottle plugs and multiples.

- 1.19 1 DC to low frequency noise generator.

- 1.20 1 High frequency noise generator

- 2.0 Peripheral Equipment:

- 2.1 15 Eight Channel Strip Chart Recorders

- 2.1.1 Must be capable of slaving with the analog computer mode control.

- 2.1.2 Must be capable of operating the analog computer mode control.

- 2.2 15 X-Y Plotters

- 2.2.1 Each must be capable of plotting over a 10 x 15 inch range.

- 2.2.2 Pen operation must be capable of being slaved to the analog computer mode control.

- 2.3 2 Automatic Set up and Checkout Devices

- 2.3.1 Must be capable of setting all servo set pots.

- 2.3.2 Must be capable of reading all computing components.

- 2.3.3 Must be capable of activating the computer mode control.

- 2.3.4 Read and store all potsetting in a suitable form for reprogramming the computer.

- 2.4 1 Analog Patchboard Storage System

- 2.4.1 Must be capable of holding all of the analog patchboards in a fully wired condition.

- 2.5 l Logic Patchboard Storage System

- 2.5.1 Must be capable of holding all of the logic patchboards in a fully wired condition. Can be incorporated with Item 2.4.

- 2.6 l Patch Cord Storage System

- 2.6.1 Must be capable of holding all of the patch cords, both analog and logic.

- 2.6.2 Shall be arranged in such a manner to facilitate patching either analog or logic patchboards.

# 3.0 Spares and Test Equipment:

- 3.1 1 Test Rack

- 3.1.1 Capable of testing and calibrating all computing elements to original specifications, operating in the same system environment as the computer system.

- 3.1.2 Capable of testing and calibrating all logic elements to original specifications, operating in the same system environment as the logic system.

- 3.1.3 Test rack may use spare computing components to implement the above tests.

- 3.2 l Reference Divider System

- 3.2.1 System must provide two voltages simultaneously, one to be used as an input, the other to be used as a nulling voltage.

- 3.2.2 System must be capable of dividing reference by .001% steps.

- 3.2.3 System must have preprogramming capability for selecting standard test and calibration voltages.

- 3.2.4 System must be portable.

- 3.3 1 Lot Spare Computing Elements

- 3.3.1 Shall include EDVM, power supplies, reference, amplifier networks, and approximately one or two percent of the plug in spare components, but at least two of each type of computing element or card.

- 3.4 1 Lot Spare Parts

- 3.4.1 Shall include at least two each of each type of resistor, capacitor, diode, transistor and relay that are used in the computer system.

#### 4.0 Options:

- 4.1 Delete one computer console as described in Item 1.

- 4.2 Delete 3 eight channel recorders, 3 X-Y plotters as described in Items 2.1 and 2.2

- 4.3 Delete 1 automatic set up and checkout device as described in Item 2.3.

- 4.4 Substitute a parallel entry keyboard for both the addressing and reference divider systems.

- 4.5 Substitute electronic digital attenuators for all of the servo set potentiometers.

# 5.0 Required Specifications:

- 5.1 Drift

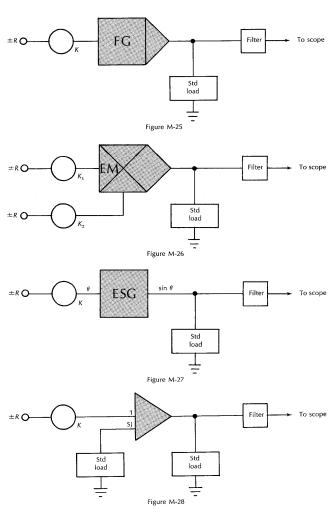

- 5.1.1 Arbitrary Electronic Function Generator

- 5.1.2 Electronic Multiplier

- 5.1.3 Electronic Sinusoid Generator

- 5.1.4 Integrator Amplifier

- 5.1.5 Summing Amplifier

- 5.1.6 SCI Method of Measurement

- 5.1.7 Format for results 10.1.

- 5.2 Error, Total

- 5.2.1 Electronic Multiplier

- 5.2.1.1 SCI Method of Measurement

- 5.2.1.2 Format for results 10.2.1

- 5.2.2 Combination Amplifier

- 5.2.2.1 SCI Method of Measurement for Summing Amplifier with the combination amplifier in the summing mode.

- 5.2.2.2 Format for results 10.2.2

- 5.2.3 Summing Amplifier

- 5.2.3.1 SCI Method of Measurement

- 5.2.3.2 Format for results 10.2.2

- 5.3 Frequency Response, Amplitude

- 5.3.1 Combination Amplifier

- 5.3.1.1 SCI Method of Measurement for amplifier with the combination amplifier in the summing mode.

- 5.3.2 Summing Amplifier

- 5.3.2.1 SCI Method of Measurement for amplifier.

- 5.3.3 Arbitrary Electronic Function Generator

- 5.3.3.1 SCI Method of Measurement

- 5.3.4 Electronic Multiplier

5.3.4.1 SCI Method of Measurement

- 5.3.5 Electronic Sinusoid Generator

5.3.5.1 SCI Method of Measurement

- 5.3.6 Format for results 10.3.

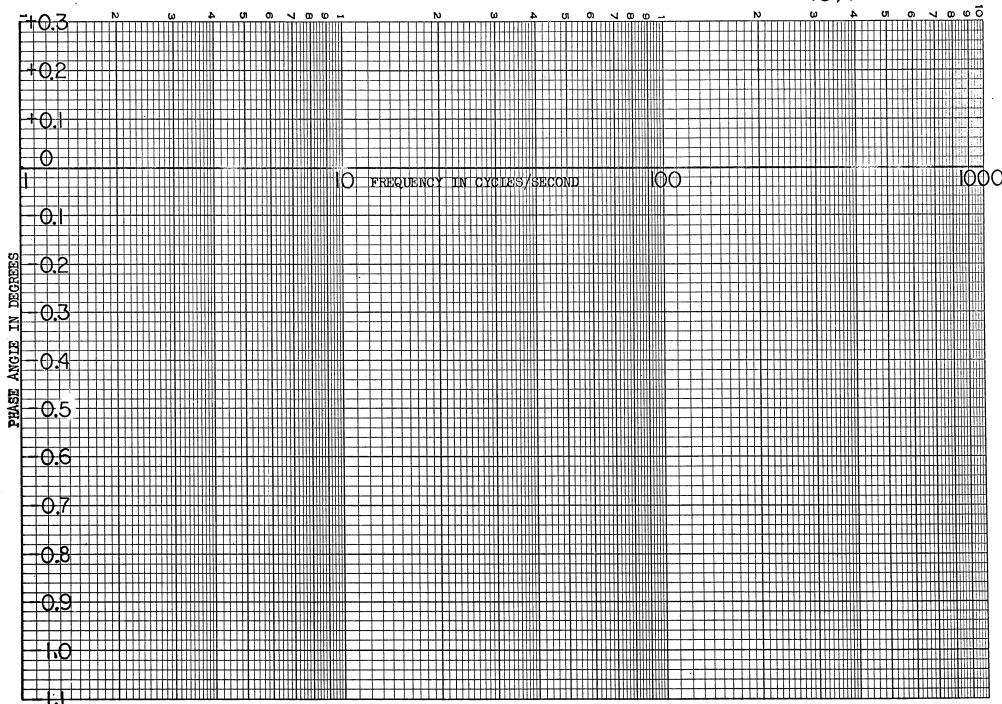

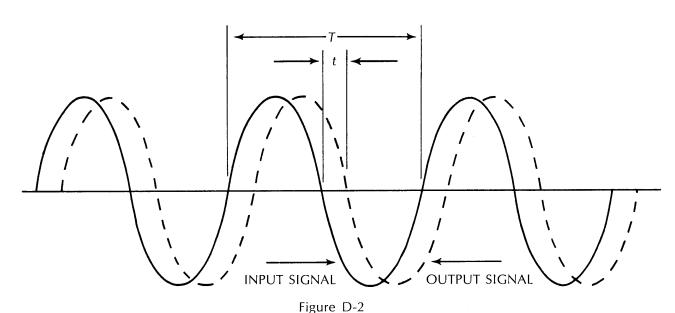

- 5.4 Frequency Response, Phase

- 5.4.1 Combination Amplifier

5.4.1.1 SCI Method of Measurement for amplifier with the combination amplifier in the summer mode.

- 5.4.2 Summing Amplifier

5.4.2.1 SCI Method of Measurement for amplifier

- 5.4.3 Arbitrary Electronic Function Generator

5.4.3.1 SCI Method of Measurement

- 5.4.4 Electronic Multipliers

5.4.4.1 SCI Method of Measurement

- 5.4.5 Electronic Sinusoid Generator

5.4.5.1 SCI Method of Measurement

- 5.4.6 Format for results 10.4.

- 5.5 Noise

- 5.5.1 Arbitrary Electronic Function Generator

- 5.5.2 Electronic Multiplier

- 5.5.3 Electronic Sinusoid Generator

- 5.5.4 Summing Amplifier

- 5.5.5 SCI Method of Measurement

- 5.5.6 Format for results 10.5.

- 5.6 Recovery Time, Overload

- 5.6.1 Arbitrary Electronic Function Generator

- 5.6.2 Electronic Multiplier

- 5.6.3 Electronic Sinusoid Generator

- 5.6.4 Summing Amplifier

- 5.6.5 SCI Method of Measurement

- 5.6.6 Format for results 10.6.

- 5.7 Response, Transient

- 5.7.1 Arbitrary Electronic Function Generator

- 5.7.2 Electronic Multiplier

- 5.7.3 Electronic Sinusoid Generator

- 5.7.4 Summing Amplifier

- 5.7.5 SCI Method of Measurement

- 5.7.6 Format for results 10.7.

- 5.8 Response, Transient, Under Capacitive Loading

- 5.8.1 Summing Amplifier

- 5.8.2 SCI Method of Measurement

- 5.8.3 Format for results 10.8.

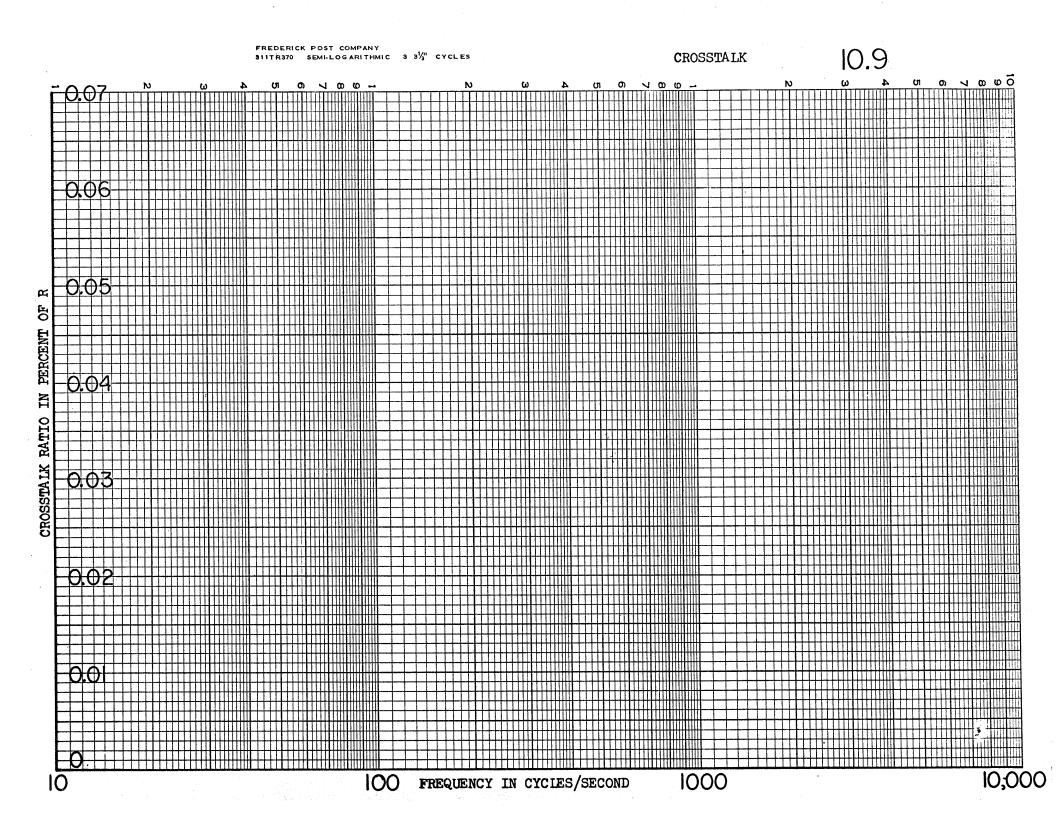

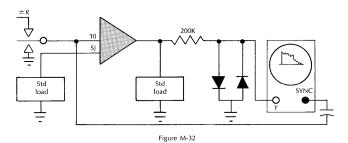

- 5.9 Crosstalk, Patchboard Amplifiers

- 5.9.1 Method of Measurement 9.1

- 5.9.2 Format for results 10.9.

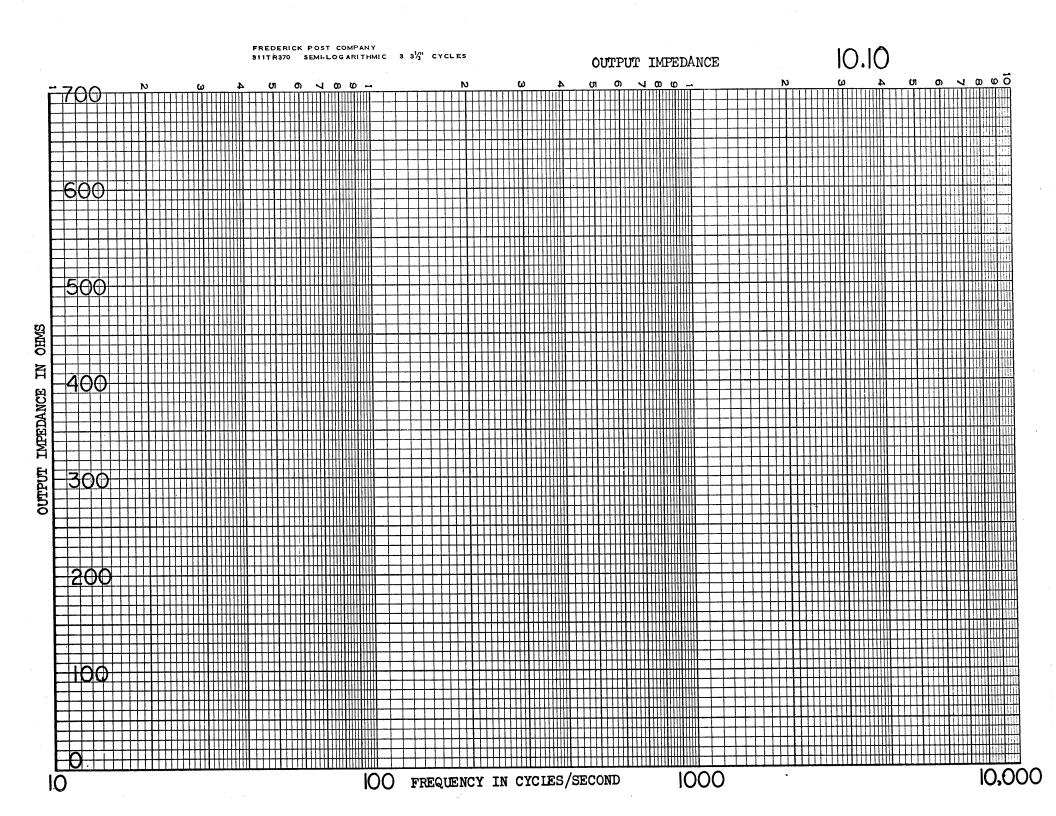

- 5.10 Output Impedance

- 5.10.1 Combination Amplifiers

- 5.10.2 Summing Amplifier

- 5.10.3 Method of Measurement 9.2

- 5.10.4 Format for results 10.10.

- 5.11 Velocity Limit

- 5.11.1 Combination Amplifier

- 5.11.2 Summing Amplifier

- 5.11.3 Method of Measurement 9.3

- 5.11.4 Format for results 10.11

- 6.0 Computer System's Environmental Requirements:

- 6.1 Bidders shall submit dimensioned drawings showing the physical size of all consoles, cabinets and peripheral devices. Drawing will indicate the location of airconditioning intakes and exhausts, power cords, and other external cable requirements.

- 6.2 Bidders shall submit a suggested arrangement of a computer system including the arrangement of the peripheral equipment.

- 6.3 Bidders will indicate the clearances required for maintenance access to the computer system and the peripheral equipment.

- 6.4 Bidders shall submit floor loading data for the computer system.

- 6.5 Bidders shall submit electrical power requirements for computer system and peripheral equipment.

- 6.6 Bidders shall submit airconditioning requirements for the computer system and peripheral equipment. Data will include the volume and temperature of the intake air and the temperature of the exhaust air.

- 6.7 Bidders shall submit any additional facility requirements for the installation or operation of the computer systems and peripheral equipment.

- 7.0 Successful bidder shall provide five (5) copies of maintenance procedures and maintenance manuals for all computing components and peripheral equipment.

#### 8.0 Inspection and Delivery

- 8.1 Successful bidder shall notify Lockheed Missiles and Space Company at least two weeks in advance of a date for inspection of the computer systems at the bidder's plant.

- 8.2 Successful bidder shall provide space and test equipment for representatives of Lockheed Missiles and Space Company to inspect and test the computer system prior to shipment.

- Shipment of the computer systems can be made only after successfully meeting specifications. Meeting of specifications is to be determined by Lockheed Missiles and Space Company.

- 8.4 Shipment is to be F.O.B. Lockheed Missiles and Space Company, Sunnyvale, California.

- 8.5 Bidder shall submit a delivery date based on receipt of purchase order.

- 8.6 Bidder shall provide a plan to compensate IMSC in the event bidder is unable to meet his delivery date.

# 9.0 Method of Measurement:

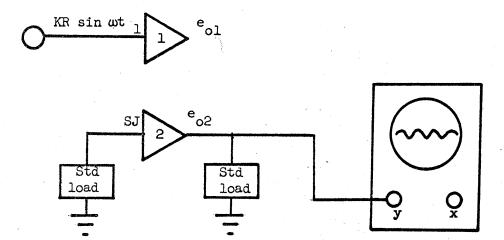

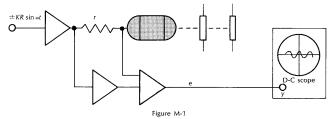

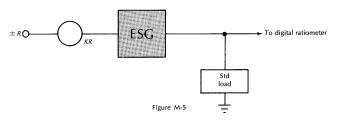

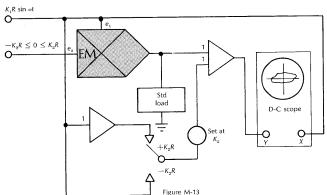

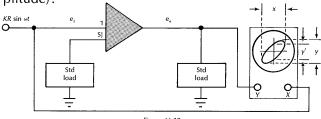

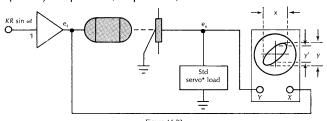

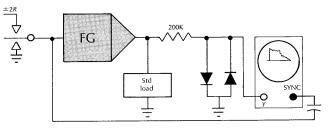

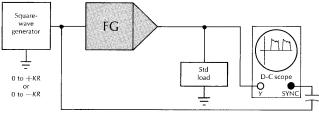

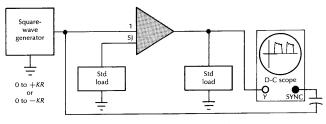

9.1 Cross Talk, Amplifier

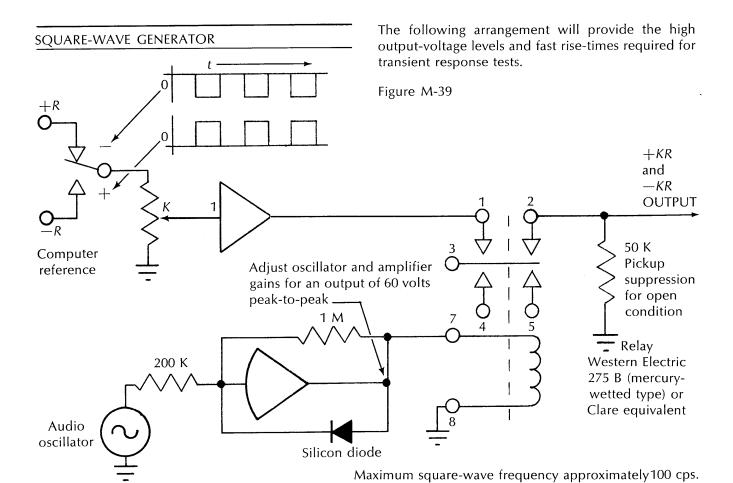

The following circuit is recommended for measurement of amplifier cross talk. Worse case results for any combination of amplifiers on the patchboard should be given as the crosstalk specifications.

Cross talk ratio =  $\frac{e_{o2}}{KR}$

Suggested values of K is 1.0

R = Reference voltage.

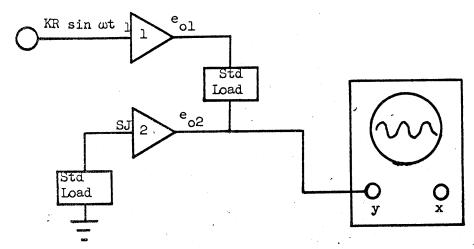

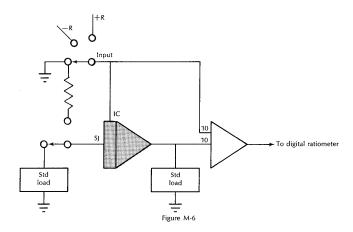

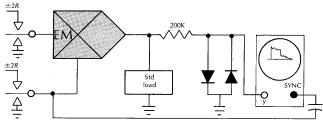

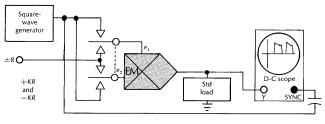

# 9.2 Output Impedance

The following circuit is recommended for measurement of amplifier output impedance.

Output Impedance =

$$\frac{e_{o2 \text{ Max}} R_L}{KR - e_{o2 \text{ Max}}}$$

Where  $\mathbf{R}_{\mathbf{L}}$  is the value of the standard output load in ohms. Suggested value of K is 1.0.

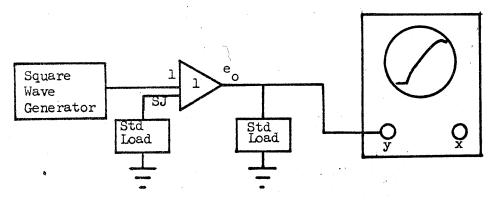

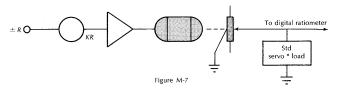

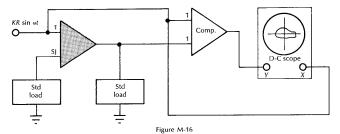

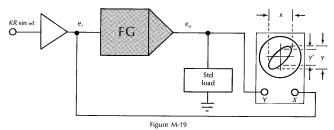

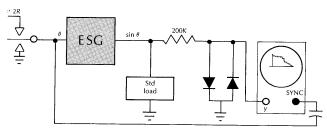

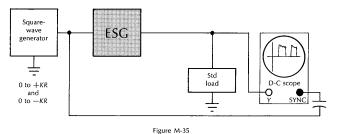

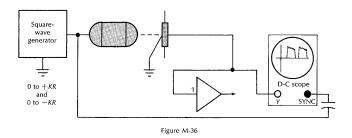

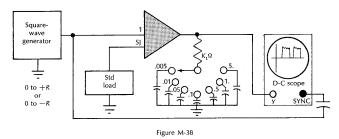

# 9.3 Velocity Limit

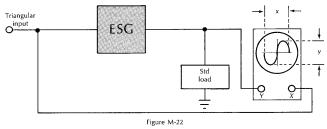

Velocity limit can be measured by the circuit shown below:

Recommended value of K is 1.0. The frequency of the square wave generator and the time scale of the oscilloscope should be adjusted to give the best resolution of the output slope.

Velocity limit =

$$\frac{.8 \text{ KR}}{\text{t}.9\text{eo}^{-\text{t}}.\text{lec}}$$

Where t see is the time required for e to reach .9 KR and t leo is the time required for e to reach .1 KR.

SCI square wave generator may be used.

# 10.0 Format for Specifications

| 10.1 | Drift    |            |          |                |                                                                                                                                                                                                                                  |

|------|----------|------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 10.1.1   | Arbitrary  | Electro  | nic Function ( | Generator                                                                                                                                                                                                                        |

|      |          |            |          | Microvolts/ho  | our                                                                                                                                                                                                                              |

|      |          |            |          | % R/hour       | 4                                                                                                                                                                                                                                |

|      | 10.1.2   | Electronic | : Multip | lier           |                                                                                                                                                                                                                                  |

|      | •        |            |          | Microvolts/ho  | our                                                                                                                                                                                                                              |

|      |          |            |          | %R/hour        |                                                                                                                                                                                                                                  |

|      | 10.1.3   | Electronic | Sinuso   | id Generator   | en de la companya de<br>La companya de la co |

|      |          |            |          | Microvolts/ho  | our                                                                                                                                                                                                                              |

|      |          |            | ·        | %R/hour        |                                                                                                                                                                                                                                  |

|      | 10.1.4   | Integrator | · Amplif | ier            |                                                                                                                                                                                                                                  |

|      |          | 10.1.4.1   | Hold M   | ode            | •                                                                                                                                                                                                                                |

|      |          |            |          |                | Microvolts/second                                                                                                                                                                                                                |

|      |          |            | , ´      |                | %R/second                                                                                                                                                                                                                        |

|      |          | 10.1.4.2   | Operat   | e Mode         |                                                                                                                                                                                                                                  |

|      |          |            |          |                | Microvolts/second                                                                                                                                                                                                                |

|      |          |            |          |                | %R/second                                                                                                                                                                                                                        |

|      | 10.1.5   | Summing Am | plifier  |                |                                                                                                                                                                                                                                  |

|      |          |            | ····     | Microvolts/hou | ır                                                                                                                                                                                                                               |

|      |          |            |          | %R/hour        |                                                                                                                                                                                                                                  |

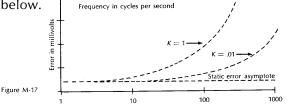

| 10.2 | See Grap | hs         | -        |                |                                                                                                                                                                                                                                  |

| 10.3 | See Grap | hs         |          |                |                                                                                                                                                                                                                                  |

| 10.4 | See Grap | h <b>s</b> |          | •              |                                                                                                                                                                                                                                  |

- 10.5 Noise

Photo-oscillograms with y-axis calibrations in peak to peak millivolts and as a percentage of R. SCI filter cut off frequencies.

- 10.6 Recovery Time, Overload

Photo-oscillograms with x-axis calibrations in time.

- 10.7 Response, Transient

Photo-oscillograms for K equal to 0.1 and 0.8.

- 10.8 Response, Transient, under Capacitive loading.

Photo-oscillograms.

- 10.9 See Graphs.

- 10.10 See Graphs.

- 10.11 Velocity Limit

Photo-oscillograms with the x-axis calibrated in time and the y-axis calibrated in percent of R. In addition, photo-oscillograms should be marked with the velocity limit value.

# LOCKHEED MISSILES AND SPACE COMPANY

HYBRID COMPUTER

INTERFACE SECTION

# INDEX

| 1.0 | Title       | <b>e</b>                        |  |  |  |  |

|-----|-------------|---------------------------------|--|--|--|--|

| 2.0 | Purp        | ose                             |  |  |  |  |

| 3.0 | Gene        | ral Description                 |  |  |  |  |

| 4.0 | Inte        | nterface Philosophy             |  |  |  |  |

|     | 4.1         | General                         |  |  |  |  |

|     | 4.2         | Pure Digital Mode               |  |  |  |  |

|     | 4.3         | Pure Analog Mode                |  |  |  |  |

|     | 4.4         | Hybrid Mode                     |  |  |  |  |

|     | 4.5         | Control                         |  |  |  |  |

| 5.0 | Data        | Transmission                    |  |  |  |  |

|     | 5.1         | General                         |  |  |  |  |

|     | 5.2         | ADC Requirements                |  |  |  |  |

|     | <b>5.</b> 3 | ADC System Specifications       |  |  |  |  |

|     | 5.4         | DAC Requirements                |  |  |  |  |

|     | 5.5         | DAC System Specifications       |  |  |  |  |

|     | 5.6         | Isolation                       |  |  |  |  |

|     | 5.7         | Checkout Panel                  |  |  |  |  |

|     | <b>5.</b> 8 | Operational Configuration       |  |  |  |  |

| 6.0 | Gene        | ral Purpose Logic               |  |  |  |  |

| •   | 6.1         | Logic Complement                |  |  |  |  |

|     | 6.2         | Patchboard Terminations         |  |  |  |  |

|     | 6.3         | Logic Compatibility             |  |  |  |  |

|     | 6.4         | Synchronous Logic               |  |  |  |  |

| 7.0 | Disc        | rete Trunks                     |  |  |  |  |

|     | 7.1         | General                         |  |  |  |  |

|     | 7.2         | Analog-Interface Trunks         |  |  |  |  |

|     | 7.3         | Interface-Interface Trunks      |  |  |  |  |

| 8.0 | Free        | Priority Interrupts             |  |  |  |  |

|     | 8.1         | General                         |  |  |  |  |

|     | 8.2         | Description                     |  |  |  |  |

| 9.0 | Free        | Discretes                       |  |  |  |  |

|     | 9.1         | General                         |  |  |  |  |

|     | 9.2         | Parallel and Individual Control |  |  |  |  |

9.3 One Shots

| 10.0 | Funct                 | ional Control                              |  |  |

|------|-----------------------|--------------------------------------------|--|--|

|      | 10.1                  | General                                    |  |  |

|      | 10.2                  | Digital Access Selection                   |  |  |

|      | 10.3                  | Addressing An Analog Computer              |  |  |

| •    | 10.4                  | Busy Status and End of Operation Interrupt |  |  |

|      | 10.5                  | Address Selection                          |  |  |

|      | 10.6                  | DVM Readout                                |  |  |

|      | 10.7                  | Setting Pots                               |  |  |

|      | 10.8                  | Mode Control                               |  |  |

| 11.0 | Cabli                 | ng                                         |  |  |

|      | 11.1                  | General                                    |  |  |

|      | 11.2                  | ADC Channels                               |  |  |

|      | 11.3                  | DAC Channels                               |  |  |

|      | 11.4                  | Discrete Trunks                            |  |  |

| 12.0 | Insta                 | allation Requirements                      |  |  |

| 13.0 | Docum                 | cumentation Requirements                   |  |  |

| 14.0 | Software Requirements |                                            |  |  |

#### 1.0 Title:

Lockheed Missiles and Space Company, Hybrid Computer Interface Section

#### 2.0 Purpose:

The purpose of this request for proposal (RFP) is to set forth the functional description of an interface system to connect the digital and analog computers defined in the following two RFP's:

- Lockheed Missiles and Space Company Hybrid Computer, Digital Section

- Lockheed Missiles and Space Company Hybrid Computer, Analog Section

# 3.0 General Description:

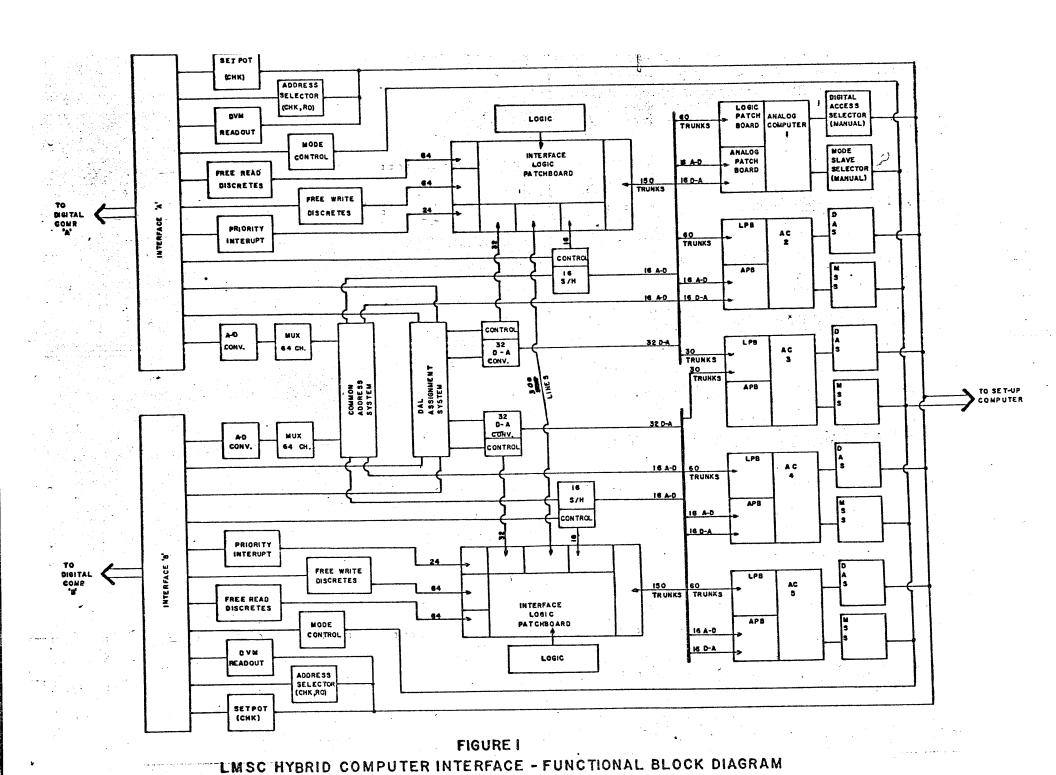

The proposed interface equipment (Figure 1) shall be installed at IMSC, Sunnyvale, California in Building 181 as a linkage system between analog and digital computers which will be delivered during 1966.

The digital section of the hybrid computing system is described in the RFP entitled IMSC Hybrid Computer, Digital Section. The analog section of the computing system is described in the RFP entitled IMSC Hybrid Computer, Analog Section. The digital section will consist of two medium sized digital computers or their equivalent. The analog section will consist of five analog computers (with general purpose logic units) and two small digital set-up computers.

The proposed linkage equipment will be composed of two identical interface systems denoted in Figure 1 as 'A' and 'B'. Both interface systems will be distinct and independent of each other and capable of simultaneously operating as part of separate hybrid computer simulations.

The proposed linkage system will be flexible in that analog to digital channels and digital to analog channels and general purpose logic not used in one interface subsystem can be used in the other. Each of the two interface systems will have capability for both high accuracy high speed data transmission, and effective control and monitoring of an independent hybrid simulation.

# . 4.0 Interface Philosophy:

#### 4.1 General

The following operational philosophies shall dictate the overall design and construction of the Hybrid Computer interface described in this request.

4.2 Pure Digital Mode

The hybrid interface system shall not interfer nor restrict either of the digital computers from operating in its normal digital mode, independent of the interface and all other computers.

- Pure Analog Mode

The hybrid interface system shall not interfer nor restrict any combination

of the analog computers from operating in their normal analog mode,

independent of the interface and all other computers.

- 4.4 Hybrid Mode

The hybrid interface system shall be composed of two identical, distinct, and independent interface systems, 'A' and 'B'. These interface systems shall be constructed such that the following modes of operation can be performed.

- 4.4.1 Each of the two interface systems shall be designed and constructed such that unused analog-to-digital and digital-to-analog conversion channels (ADC, DAC) and unused general purpose logic in one interface system can be used by the other interface system (See: 5.2.2 and 5.4.11).

- 4.4.2 Component failure (e.g., power supply, disconnected cable, etc.) in one interface system shall not interfer nor restrict the standard operation of the other interface system. (The word 'standard' refers to an interface system that does not utilize unused equipment in the other interface system).

- 4.4.3 Two hybrid computing systems can be mechanized and operated simultaneously and completely independent of one another.

- 4.4.4 One group of analog computers, one interface system, and one digital computer can be delivered to IMSC where they will be checked out, and operated both independently and as a hybrid computing unit. The remaining computing equipment can be assembled and checked out at another location (e.g. vendor's factory). The interface vendor shall state the change in cost and physical size of the complete interface system if this operational philosophy

(4.4.4) is recinded.

## 4.5 Control

The area of control involves all those functions of the linkage equipment which involve the controllability of the interface system from the digital computer, analog computer, and from the interface logic patch panel. This request indicates what functions must be controlled, but the implementation of these controls is a direct function of the particular analog and digital computers and is left up to the system designer. It will be the responsibility of the vendor to furnish a satisfactory operating system.

This document should be used only to determine the functional capabilities and not be used as a specification for equipment design. The responsibility for linking the equipment to the analog computer and to the digital computer is the responsibility of the vendor. In evaluating the proposed system, Lockheed will be interested in the command structure utilized by the digital computer in controlling the interface. The execution times of these commands will be evaluated and must be contained in the proposal. Every effort should be made by the vendor to implement the functional capability of the equipment with off the shelf design and equipment.

## 5.0 Data Transmission System:

#### 5.1 General

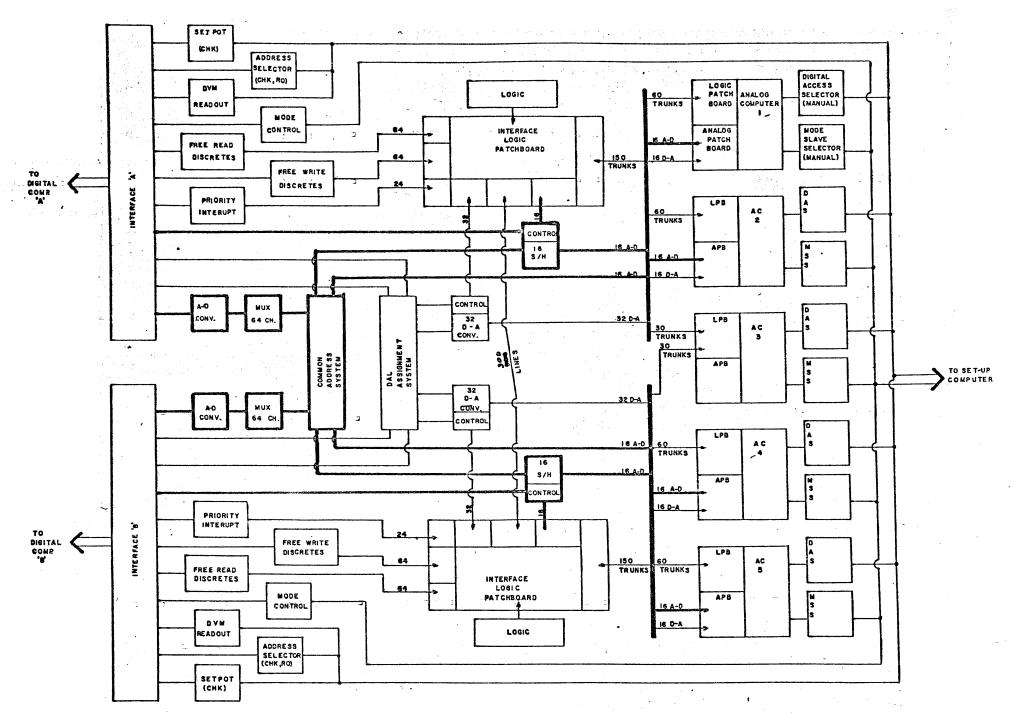

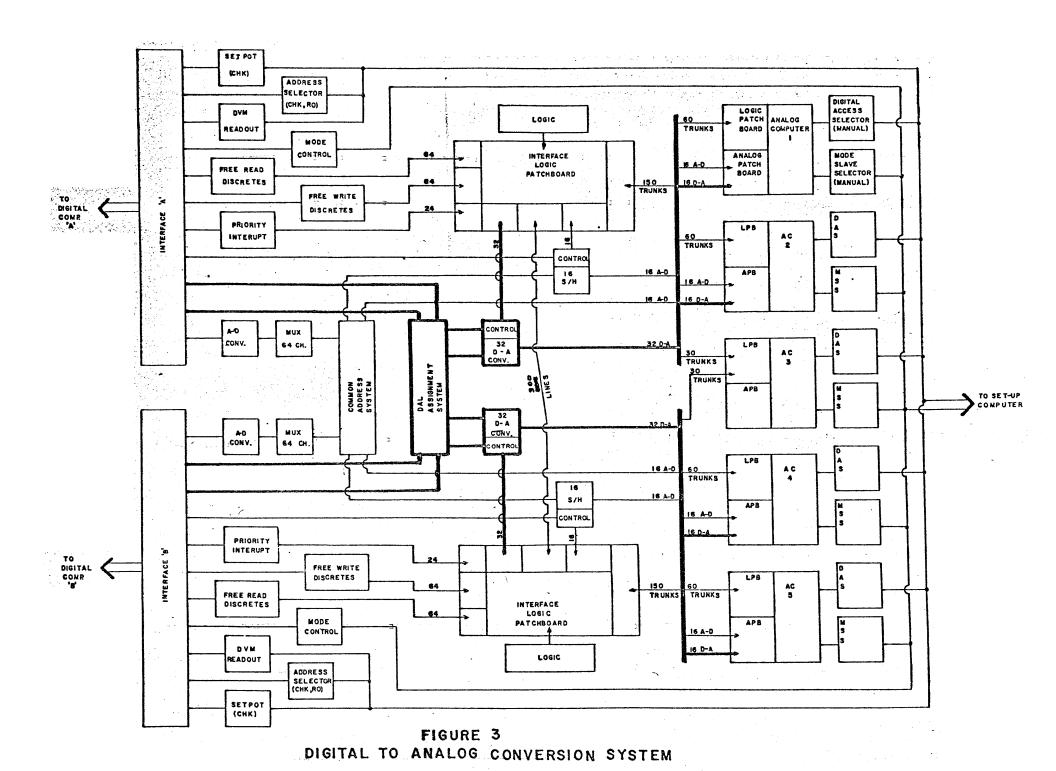

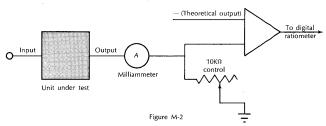

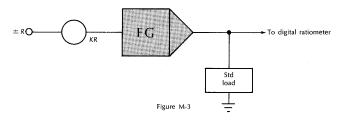

- 5.1.1 The transmission and processing of continuous data signals between the analog and digital computers shall be accomplished in each of the two interface systems by the analog-to-digital and the digital-to-analog systems. Analog computer signals shall be digitized and sent to the digital computer via the Analog-to-Digital Conversion (ADC) system (Figure 2). Digital-to-analog signals shall be processed and transmitted to the analog computer via the Digital-to-Analog Conversion (DAC) system (Figure 3).

- 5.1.2 Control of the ADC sample and hold amplifiers and the DAC output registers shall be governed by the digital computers. However, the system shall be designed such that the two interfaces will have the capability to override and synchronize control by appropriate patching of general purpose logic on the interface patchboards.

- 5.1.3 A switching arrangement shall be incorporated within the hybrid DAC interface system to provide switching control of unused DAC and/or ADC channels in one interface system to the other interface system.

- 5.1.4 The discussion and description of the ADC and DAC systems that follow, place a lower limit, not an upper limit, on the characteristics and capabilities of the data transmission system's components. The primary concern of this request is to obtain two independent and flexible sets of ADC and DAC systems that can reliably transmit data between the analog and digital computers at a maximum THROUGH-PUT rate, with a maximum THROUGH-PUT accuracy and resolution, and with a minimum amount of noise and distortion.

FIGURE 2

ANALOG TO DIGITAL CONVERSION SYSTEM

#### 5.2 ADC Requirements:

- Each of the two ADC systems (Figure 2) shall include cabinets, chassis, and associated power supplies wired and with all the necessary cabling to the digital and analog computers and:

- 5.2.2 The hybrid interface shall contain a total of 64 ADC channels -- 32 with sample and hold amplifiers, 32 without sample and hold amplifiers. The vendor is requested to supply a unit or modular price with his proposal for ease of modification.

- 5.2.3 The ADC channels will be commetted to the analog computers' patchboards as shown in Figure 2. Each of the four analog computers (Numbers 1,2,4,5) will be connected to 16 different ADC channels; 8 channels containing sample and hold amplifiers, 8 channels without sample and hold amplifiers.

- 5.2.4 All ADC channels shall accept analog voltages from the analog patchboards that will range from plus to minus 100 volts. The vendor shall discuss a method by which his proposed ADC system can detect analog input voltages that exceed 100 volts.

- 5.2.5 All ADC channels will be constructed such as not to degrade the analog computers' operation by excessive loading.

- 5.2.6 The two ADC systems shall be independent such that a malfunction or power shutdown in one interface system will not affect the standard (See: 4.4.2) operation of the other.

- 5.2.7 Interface 'A' shall contain the 32 ADC channels connected to analog computers numbered 1 and 2. Interface 'B' shall contain the remaining 32 ADC channels connected to analog computers numbered 4 and 5.

- 5.2.8 Each interface system shall be able to random and sequentially monitor all ADC channels independently of one another. The vendor should describe the operational modes of his proposed ADC system in detail.

- 5.2.9 It is desirable that each of the two interfaces contain a multiplexer and address system such that the 64 ADC channels can be expanded up to 96 channels after delivery of the hybrid interface system.

The vendor is requested to describe the expansion capability of his proposed ADC systems. He will include two supplementary

- prices in his quotation: The price per additional ADC channel with a sample and hold amplifier; the price per additional ADC channel without a sample and hold amplifier.

- 5.2.10 The ADC resolution shall be 14 bits (13 bits plus sign) or more. If the vendor has the capability of furnishing an ADC system(s) with a resolution exceeding 14 bits, he should document, price and include that system(s) as an option to the 14 bit ADC system. If the vendor has a preference for one ADC system over another (e.g. resolution), he should state his preference within his proposal and discuss his reasons.

- 5.2.11 The control of the 16 sample and hold amplifiers in each of the two ADC interface systems shall be connected to their corresponding Interface Logic Patchboards (Figure 2) in such a way as to allow signals from the logic patchboards to override and synchronize sample and hold commands originating in the digital computers. The vendor is expected to include a complete description of his proposed sample and hold control system in his proposal. Desirable features of this system would be: If no patching is made to a sample and hold control hole on the logic patchboard, then the sample and hold amplifier represented by that patchboard hole would respond directly to sample and hold commands emanating from the digital computer. A 'disable' signal patched into the hole would delay execution of the digital computers' command until the signal from the logic patchboard changed to 'enable'.

- 5.2.12 An ADC sample and hold selection switch (manual) shall be included within the hybrid interface system by which an operator could distribute the control of the sample and hold amplifiers between the two digital computers. The switch should functionally operate as follows: If an operator manually positions the switch between numbers n and n+1; Sample and hold amplifiers numbered up to and including n would be under control of digital computer 'A', (digital computer 'B' could monitor the output of the sample and hold amplifiers, but it could not control the amplifiers); sample and hold amplifiers numbered n+1 and greater would be assigned to digital computer 'B' (digital computer 'A' could monitor the output

of the sample and hold amplifiers, but it could not control the amplifiers). Standard ADC system operation would be achieved when the switch was positioned between numbers 16 and 17 (See: 4.4.2)

# 5.3 ADC System Specifications

## 5.3.1 General

The manufacturer shall include the following specifications in his description of his proposed ADC system. In these specifications ADC THROUGH-PUT and S/H shall be defined as:

- ADC THROUGH-PUT: From the analog computer's patchboard to the digital computer's memory.

- S/H: Sample and Hold or Track and Store amplifier.

# 5.3.2 ADC THROUGH-PUT rate 1:

This rate shall specify the speed at which 16 ADC channels with sample and hold amplifiers (S/H) can be sequentially addressed and their voltages digitized and transferred to one of the digital computer's memory storage. The ADC THROUGH-PUT rate shall be commensurate with the THROUGH-PUT accuracy 1. The rate shall be derived under the following conditions:

- S/H amplifiers have previously been placed in their hold (store) mode;

- S/H amplifiers are connected to the first through the sixteenth multiplexer channels;

- The multiplexer shall start with its first channel and advance sequentially to its sixteenth channel;

- S/H amplifiers connected to even numbered multiplexer channels will represent maximum analog output voltages of the opposite polarity as those connected to odd numbered multiplexer channels. (e.g. Chan 1, +100V; Chan 2, -100V; Chan 3, +100V; ...; Chan 16 -100V).

# 5.3.3 ADC THROUGH-PUT rate 2:

This rate shall specify the speed at which the information on the 17th through the 32nd multiplexer channels (without S/H amplifiers) can be sequentially addressed, digitized and placed in the digital computer's memory storage. The ADC THROUGH-PUT rate shall be commensurate with the THROUGH-PUT accuracy 2. The rate shall be derived under the following conditions:

- The sixteen analog input channels without S/H amplifiers shall be connected to the 17th through the 32nd multiplexer channels;

- The voltages from the analog patchboard on the sixteen direct lines of the multiplexer shall alternate between plus and minus peak analog output voltages (e.g. Chan 17, +100V; Chan 18, -100V; Chan 19, +100V; ...; Chan 32, -100V).

#### 5.3.4 ADC THROUGH-PUT accuracy 1:

This value shall specify the accuracy with which the ADC system can transpose an analog voltage on the analog computer's patchboard (via a S/H amplifier, multiplexer and ADC) into a digitized number and store it within the digital computer's memory. ADC THROUGH-PUT accuracy shall include errors from all contributing sources (e.g. S/H amplifier; ADC resolution; component off-set, gain, linearity; allowable settling times), and shall be that error which is associated with the ADC THROUGH-PUT rate 1. The value shall be specified as a percent of the peak analog output voltage (e.g. ±0.03% of 100 volts).

## 5.3.5 ADC THROUGH-PUT accuracy 2:

With two exceptions, this specification shall be the same as that described in ADC THROUGH-PUT accuracy 1. Exceptions: The S/H amplifier is not included in the signal line; the error shall be commensurate with ADC THROUGH-PUT rate 2.

#### 5.3.6 S/H Recovery Time:

The length of time necessary for the sample and hold amplifier to change from a state where it is holding (storing) a voltage representing the plus or minus peak analog output voltage to the sample (track) mode where it is accurately tracking the peak analog voltage of the opposite polarity. The accuracy of the track-mode shall be commensurate with the ADC THROUGH-PUT accuracy 1.

## 5.3.7 S/H Decay:

This characteristic represents the maximum voltage decay (droop) experienced by any of 16 sample and hold amplifiers from the time they were placed into the hold (store) mode to the time the last S/H amplifier was sequentially addressed and ; its voltage digitized. The initial value of voltage stored on the 16 S/H amplifiers shall correspond to the peak analog output voltage (e.g. 100 volts). The S/H decay shall be specified as a percent of the peak analog output voltage (e.g. 0.005% of 100 volts).

#### 5.4 DAC Requirements:

- Each of the two DAC systems (Figure 3) shall include cabinets, chassis, and associated power supplies wired and with all the necessary cabling to both the digital and analog computers and:

- 5.4.2 The hybrid interface shall contain a total of 64 double buffered DAC channels. The vendor is requested to supply a unit or modular price with his proposal for ease of modification.

- 5.4.3 The DAC channels will be terminated on the analog computers' patchboards as shown in Figure 3. Each of the four analog computers (numbers 1,2,4,5) will be connected to 16 different DAC channels.

- 5.4.4 All DAC channels shall be referenced to the analog reference voltage supplies of their respective analog computers. The interface must be designed such that the DAC systems do not draw an excessive amount of current from the analog computers' reference supplies.

- 5.4.5 All DAC channels shall be able to output voltages to the analog computers' patchboards that range from plus to minus 100 volts. The DAC output amplifiers will be expected to drive the same loads as the analog amplifiers. Any significant dissimilarities in electrical characteristics between the DAC output amplifiers and the analog amplifiers shall be noted by the vendor.

- 5.4.6 The two DAC systems shall be independent such that a malfunction or power shutdown in one interface system will not affect the standard (See 4.4.2) operation of the other.

- 5.4.7 Interface 'A' shall contain the 32 DAC channels connected to analog computers numbered 1 and 2. Interface 'B' shall contain the 32 DAC channels connected to analog computers numbered 4 and 5.

- 5.4.8 It is desirable that each of the two DAC systems have the capability of expanding in number of channels after delivery of the hybrid interface system. The vendor is requested to describe the expansion capability of his proposed system. He should include the unit or modular price required for this expansion.

- The DAC resolution shall be 14 bits (13 bits plus sign) or more.

If the vendor has the capability of furnishing an DAC system(s)

with a resolution exceeding 14 bits, he shall document, price

and include that system(s) as an option to his 14 bit DAC system.

- If the vendor has a preference for one DAC system over another (e.g. resolution, buffers) he should state his preference within his proposal and discuss the reasons for his preference.

- interface systems shall be connected to their corresponding interface logic patchboards in such a way as to allow signals from the logic interface patchboards to override and synchronize output register transfer commands originating in the digital computers. The vendor is expected to include a complete description of his proposed output register control system within his proposal. Desirable features of this system would be: If no patching is made to an output register control hole on the logic interface patchboard, then the output register represented by that patchboard hole would respond directly to output register transfer commands emanating from the digital computer. A 'disable' signal patched into the hole would delay execution of the transfer command until the signal changed to 'enable'.

- 5.4.11 A DAC assignment switch (manual) shall be included within the hybrid interface system which will enable an operator to assign the DAC channels associated with each of the two digital computers. The position of this switch will determine which of the two digital computers can send input data into a DAC's input register and send control commands to the DAC's output register. The vendor is expected to include a complete description of this control system in his proposal. The switch should have the following characteristics: If an operator manually positions the DAC assignment switch between numbers n and n+1; DAC channels numbered up to and including n would be assigned to digital computer 'A' (digital computer 'B' could neither send data nor control commands); DAC channels numbered n+1 and greater would be assigned to digital computer 'B' (digital computer 'A' could neither send data nor control commands). Standard operation would be achieved when the switch was positioned between numbers 32 and 33 (See: 4.4.2).

# 5.5 DAC System Specifications:

5.5.1 General

The manufacturer shall include the following specifications in his

description of his proposed DAC system. In these specifications, DAC THROUGH-PUT shall be defined as:

• DAC THROUGH-PUT: From digital computer memory storage to analog computer patchboard.

#### 5.5.2 DAC Amplifier settling time 1:

Length of time necessary for one DAC output amplifier to change from a plus or minus peak analog output voltage to a peak output voltage of the opposite polarity (e.g. from -100V to +100V). The settling time shall be sufficient to provide the DAC THROUGH-PUT accuracy.

5.5.3 DAC Amplifier settling time 2:

Length of time necessary for one DAC output amplifier to change from a plus or minus peak analog output voltage to 99% of the peak voltage of the same polarity (e.g. from -100V to -99V). The settling time shall be sufficient to provide the DAC THROUGH-PUT accuracy.

5.5.4 DAC THROUGH-PUT signal-to-noise ratio:

This figure shall represent the ratio of the noise amplitude on the

DAC channel measured at the analog patchboard to the peak analog output voltage (e.g. +0.005% of 100 volts).

5.5.5 DAC THROUGH-PUT accuracy:

This value shall include errors from all contributing sources (e.g. DAC resolution; component off-set, gain error, linearity error; allowed settling time) and shall be that error associated with the specified DAC THROUGH-PUT rates. The value shall be specified as a percent of the peak output voltage (e.g. +0.01% of 100 volts).

#### 5.5.6 DAC THROUGH-PUT rate 1:

The length of time required to change 32 DAC channels assigned to one digital computer from a plus or minus peak analog voltage output to a peak amplitude output of the opposite polarity. The length of time shall include the time necessary to sequentially load the DAC input registers from the digital memory, the updating of the output registers in unison, and the DAC output amplifiers' settling time. The allowed settling time shall be commensurate with that used in deriving the DAC THROUGH-PUT accuracy.

#### DAC THROUGH-PUT rate 2: 5.5.7

With one exception, this specification is the same as the procedure for DAC THROUGH-PUT rate 1. Exception, the DAC output voltage to the analog patchboard shall retain the same polarity and be commanded to change from 100% to 99% of a peak value (e.g. +100V to +99V).

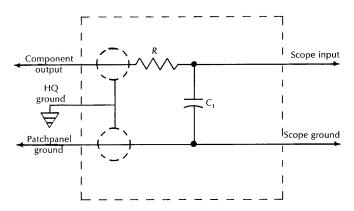

#### \_5.6 Isolation:

The vendor shall describe and evaluate the effectiveness of the techniques he will utilize to minimize noise and distortion in his proposed data transmission system (e.g. analog-interface-digital ground loops, cross talk).

#### Checkout Panel: 5.7

It would be desirable if the vendor's interface system contained a checkout panel by which the interface and analog computer sections of a hybrid simulation could be statically checked and trouble shot without the use of the digital computers. If available and practical, the vendor should include in his proposal a description of the control panel's functions for evaluation and consideration. The checkout panel should provide for:

- Digital values to be loaded into the DAC registers.

- . Digital values to be read out of the ADC registers.

#### Optional Configuration: 5.8

More than one data transmission system configuration may be acceptable since there are trade-offs between the data transmission system's characteristics (i.e., settling time versus rate versus accuracy versus resolution). If a trade-off enhances one or more ADC or DAC system characteristic (e.g., greater THROUGH-PUT accuracy, rate, resolution), without violating the minimum requirements, the vendor should note the option and document the associated specifications.

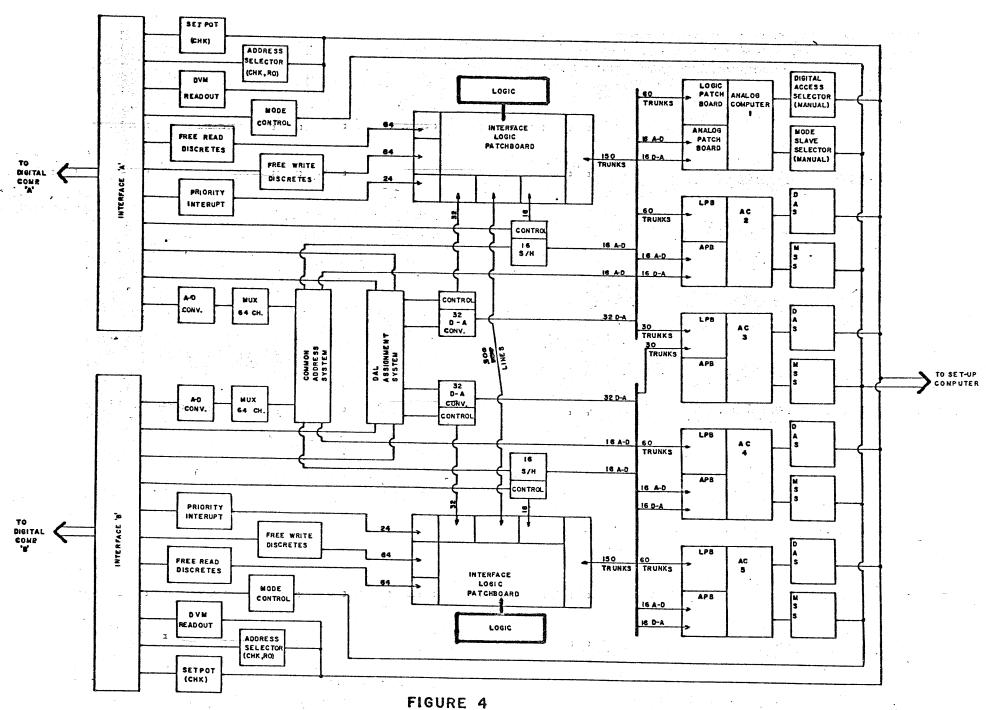

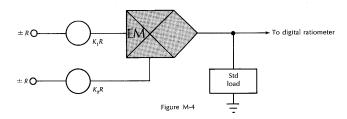

# 6.0 General Purpose Logic:

General purpose logic will be added to the hybrid interface system to supplement the logic contained on the analog computers' logic patchboards (Figure 4). This logic with its associated patchboards will be supplied with the hybrid computer interface. Logic will be divided into two groups each associated with one of the two digital computers. The logic power supplies, cables and associated components will be made as independent as possible so that a malfunction or a

GENERAL PURPOSE INTERFACE LOGIC

power shutdown on one of the logic complements will not interfer with the operation of the other.

#### 6.1 Logic Complement:

Each of the two interface systems will contain 2 patchboards, an assortment of patch leads and the following logic complement:

- l clock (1-2 MC)

- 36 decode down counters

- 80 flip flops

- 10 one shots

- 10 differentiators

- 200 two-input 'AND' gates

- 50 five-input 'AND' gates

- 10 line drivers

All logic outputs will have the capability of driving at least 8 other logic units. The logic complement should be optionally priced so that the complement can be easily modified.

### 6.2 Patchboard Terminations:

Each interface patchboard will contain the discrete and interrupt information from its associated digital computer, the outputs and inputs from its associated general purpose interface logic, trunk lines between the two logic interface patchpanels and discrete trunk lines to three of the analog computers (figure 5). The complements of logic signals should be available and as much bussing as possible as determined by the interface patchboard size selected by the vendor. Both interface patchbays should be designed identically so that patchboards wired for interface 'A' can be run on interface 'B'.

#### 6.3 Logic Compatibility:

- 6.3.1 The trunks between the interface logic patchboards and the interface logic shall be designed so that logic from one logic complement can be patched and used as part of the other logic complement (Figure 5).

- 6.3.2 The logic on the interface patchboards should be compatible with the logic on the analog computers' logic patchboard. If it is not compatible, then signal conditioning for a 150 bi-directional signal (level changers) will be provided on each of the two interface patchboards. If bi-directional signal conditioning is

- not a practical approach, then a 100 input and a 100 output signal conditioning unit (level changers) shall be supplied for each of the two interface systems.

- 6.3.3 All computer discretes will be terminated on their respective interface logic patchboards. This will include control lines (9.0) status lines (9.0), and interrupt lines (8.0). These lines will originate at the interface of the digital computer and shall be compatible with the logic levels of the general purpose interface logic.

- 6.4 Synchronous Logic:

The vendor will discuss the problems of synchronous and asynchronous patchable logic. He will discuss how logic and clock information will be synchronized between analog computers and the interface systems between slaved analog computers, between interfaces, between combinations of each, especially when independent problems share the same logic patchboards. The vendor should state his ability to provide both synchronous and asynchronous logic. He should include within his quotation the prices for both types of logic.

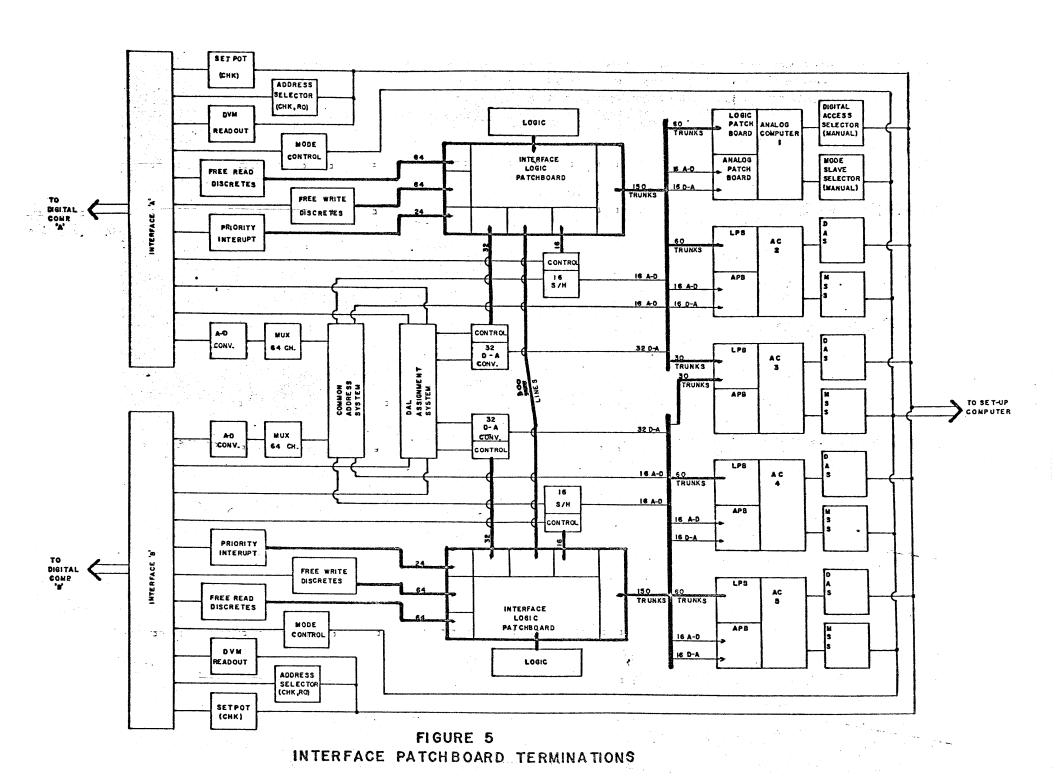

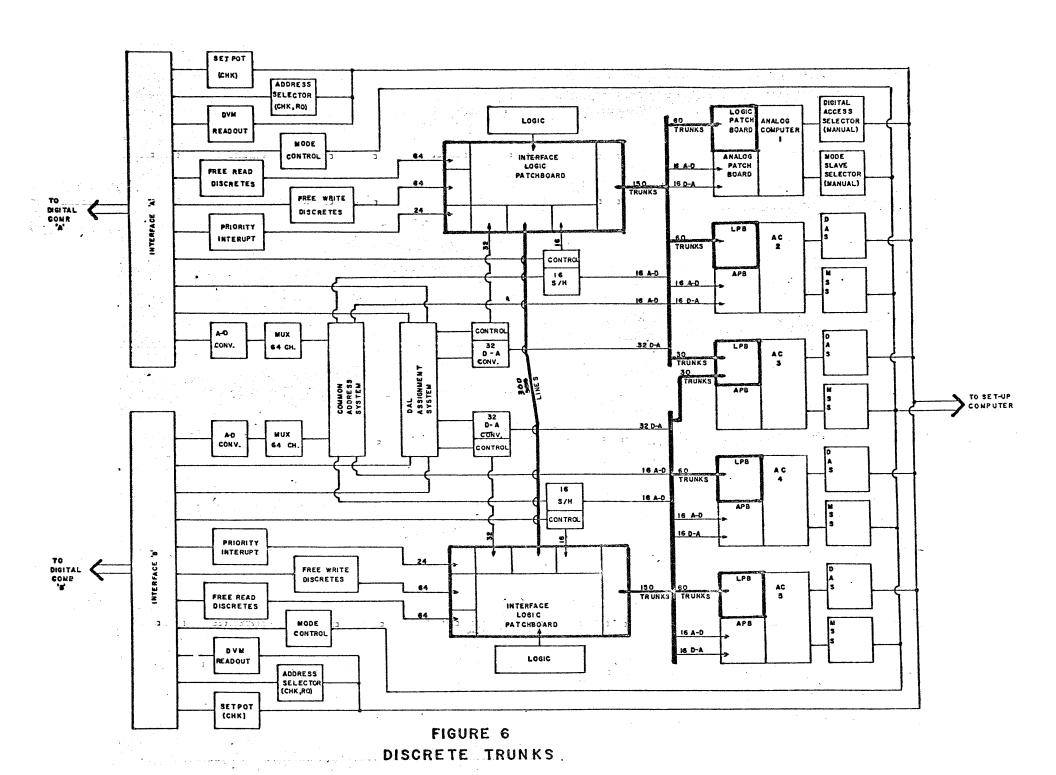

## 7.0 Discrete Trunks:

- 7.1 General:

- Interface systems 'A' and 'B' shall be able to transmit discrete signals from one interface logic patchboard to another and to the analog logic patchboards through a system of general purpose discrete-trunk lines (Figure 6). The trunk lines shall be arranged and/or constructed such that crosstalk does not degrade the overall hybrid system's performance.

- 7.2 Analog-Interface Trunks:

- Each interface system shall have 150 general purpose discrete trunk lines which will be connected from its interface logic patchboard to three of the five analog computers. Interface 'A' will have 60 of its 150 lines connected to the analog logic patchboard of analog computer number 1, 60 lines connected to analog computer 2, and 30 lines connected to analog computer 3. Interface 'B' will have 60 of its 150 discrete trunk lines connected to the logic patchboard of analog computer number 5, 60 lines connected to analog computer 4, and 30 lines connected to analog computer 5. All lines shall terminate in well defined patchboard locations and in such a way that all analog logic patchboards are similar and interchangeable.

Interface logic patchboards shall be similar and interchangeable with one another. The vendor shall submit a modular or unit price for these lines with his regular quotation to facilitate ease of modification.

#### 7.3 Interface-Interface Trunks:

The two interface logic patchboards will be connected to one another by 300 general purpose discrete lines (Figure 6). These lines will be terminated in well defined locations on each of the two interface's patchboards such that their patchboards are interchangeable. The vendor shall include a modular or unit price for these lines with his regular quotation for ease of modification.

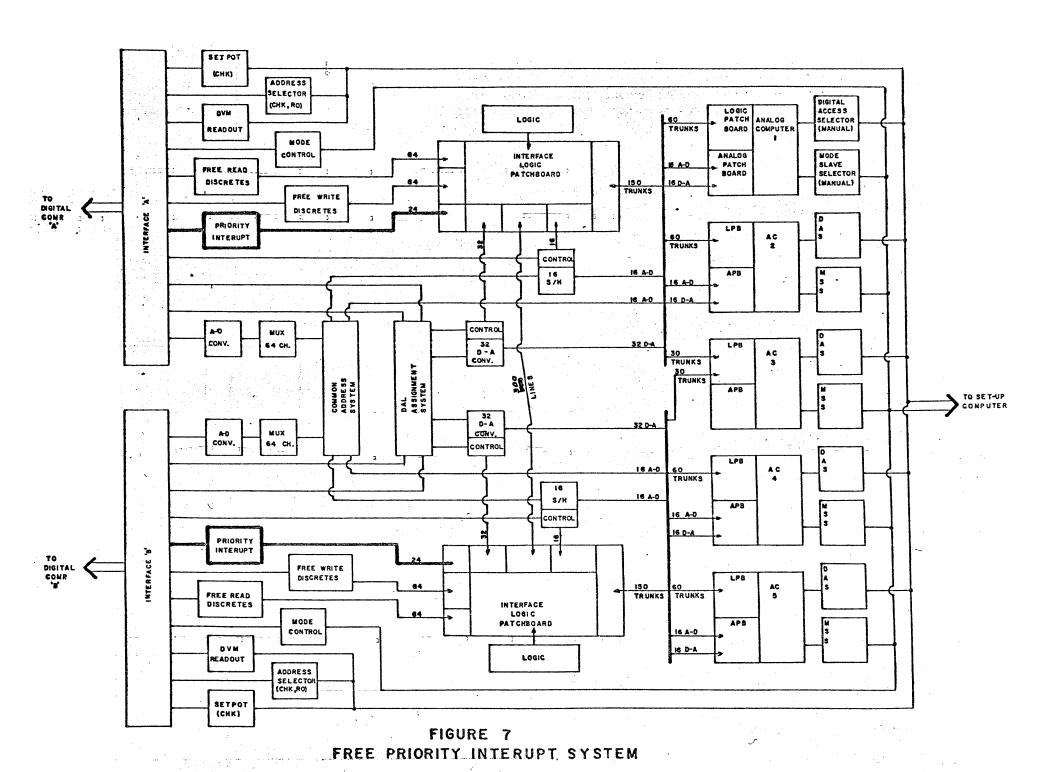

## 8.0 Free Priority Interrupts:

#### 8.1 General:

The interrupt portion of the interface equipment is of vital importance in evaluating the vendor's proposal. It is the responsibility of the interface vendor to insure that this hybrid computer system has two independent priority interrupt systems - one for each digital computer (Figure 7). Due to the vital nature of this system, complete specifications of the command functions and the operational registers must accompany the proposal for evaluation. Both 'A' and 'B' interfaces will have 24 non-assigned (free) interrupts that are connected on their respective logic interface patchboards. The interrupt logic levels shall be compatible with the logic levels of the general purpose interface logic.

#### 8.2 Description:

The operation of the interrupt system will depend greatly on the digital computer selected for the hybrid computing system. The interrupt characteristics desired in this proposal are described as if the interrupt capability had to be designed within the interface system. The following interrupt scheme is a suggested method of handling interrupts. The interrupt control of the interface system will be used by the digital computer to allow interrupts of higher priority to be processed while disallowing interrupts of lower priority. This system will be effected by an interrupt register and an interrupt mask register. The interrupt mask register will allow a bit set in the interrupt register to be transmitted to the digital computer on its associated interrupt line. If the bit is zero in the mask register, transmission will be disallowed. The interrupt register will be set by a signal from the analog computer and is reset by the digital computer.

The digital computer may reset the interrupt register or each bit selectively. The interrupt register will continue to drive its associated interrupts through the mask register until reset by the digital computer even if the controlling signal from the analog computer or interface logic disappears.

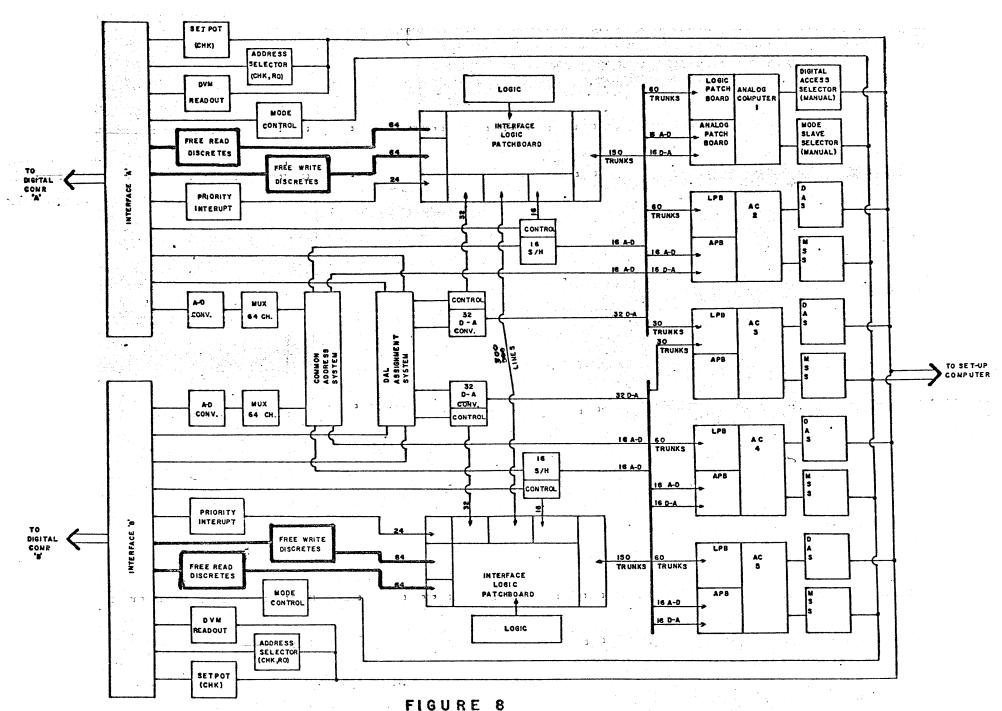

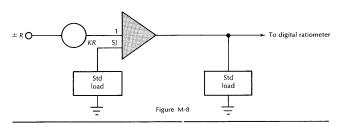

#### 9.0 Free Discretes:

#### 9.1 General:

The two interface systems will each contain 64 read and 64 write discrete lines (Figure 8). The lines will be terminated in well defined locations on the interface patchboards in such a way as to allow the interface patchboards to be interchanged. These read and write sense and control lines will be able to be sensed and selected by the digital computer. The manner in which these discrete lines are implemented will be determined by the selection of the digital computer. If the digital computer has the capability of selecting control lines and of sensing individual discrete lines then the interface will merely contain the logic required for signal conditioning these signals for the interface patchboard in the flipflops required for storage of these lines. If a digital computer is selected without this capability, then the interface must contain the decoding of channel commands required to implement the selection and sensing of control lines.

#### 9.2 Parallel and Individual Control:

A desirable feature would be the division of the read-write discrete lines into two groups - one which would be controlled by parallel transfer and the other which would allow individual sensing and select. The parallel transfer would appear on the interface patchboard as a input and a output register. The individual lines would appear on the patchboard as simple control and discrete lines.

#### 9.3 One Shots:

A desirable feature for the control lines would be the ability for patching automatic reset. In this mode of operation, by placing the plug in the interface patchboard, the flipflops storing the control line would be reset generating a pulse signal at the interface patchboard. The pulse should be at the length and levels required for satisfactory operation with the logic on the interface patch panel.

FREE READ & WRITE DISCRETE SYSTEMS

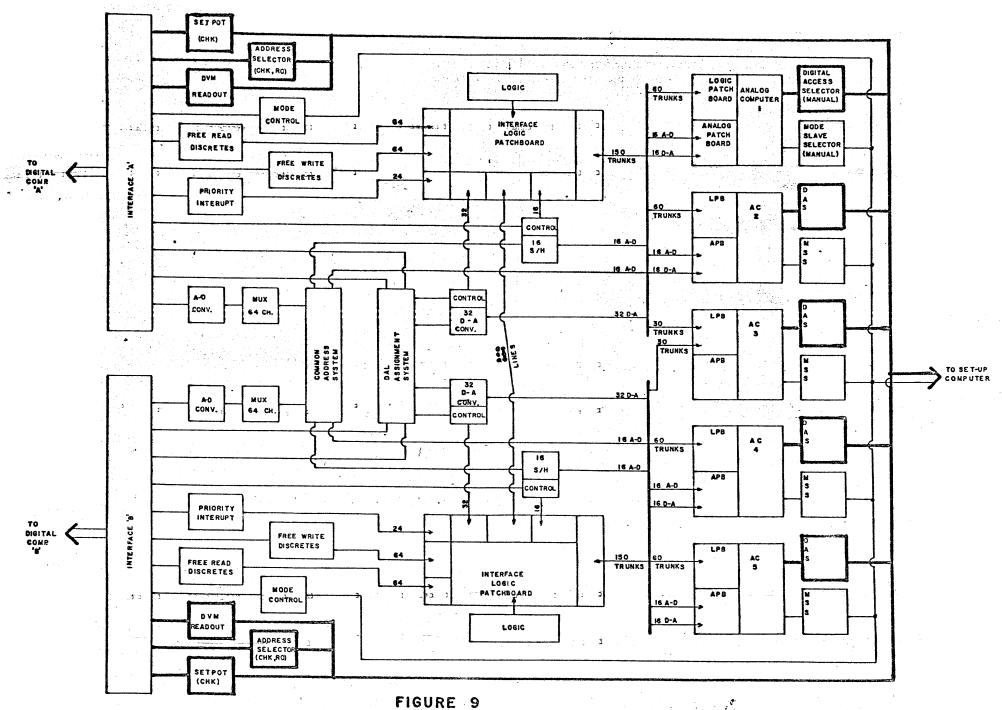

#### 10.0 Functional Control:

#### 10.1 General:

The control section of the interface will allow the digital computer to perform set-up, control, and monitoring functions within the analog computer. These functions are:

- DVM Readout (Figure 9)

- Set Pot (Figure 9)

- Address Select (Figure 9)

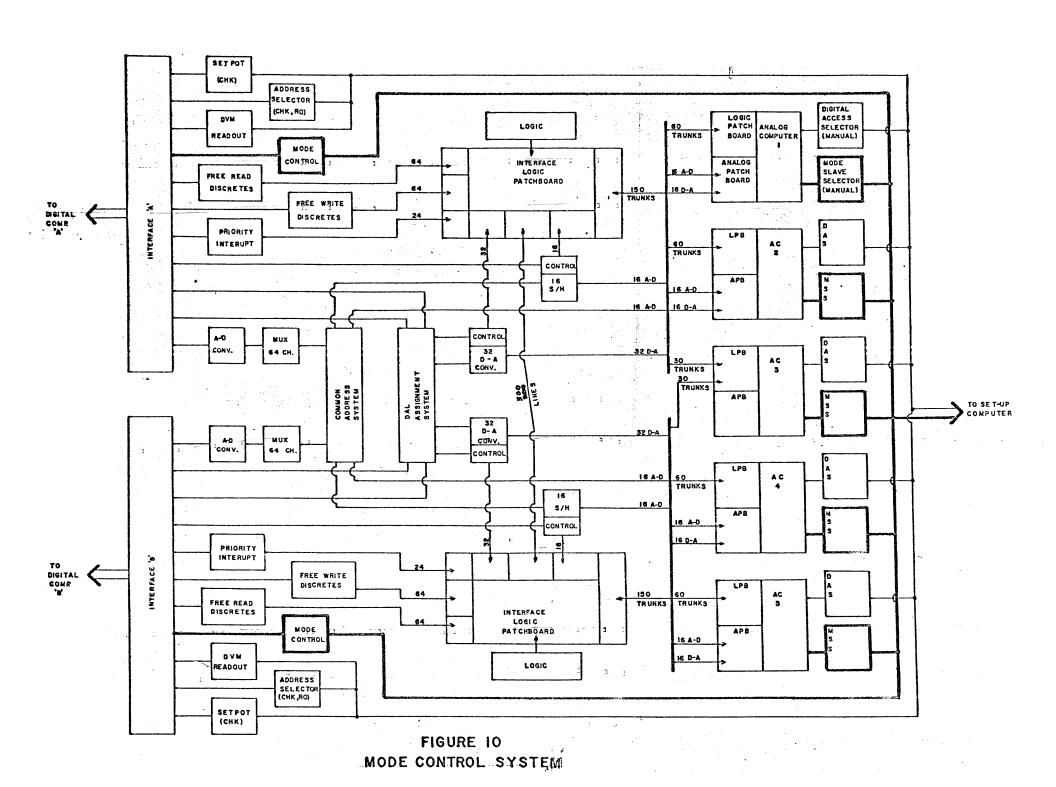

- Mode Control (Figure 10)

A dual channel controller from the digital computers with access up to five analog consoles will be furnished. Both digital computers will be able to operate in parallel with any of the analog consoles.

#### 10.2 Digital Access Selection:

A digital access selector switch will be installed on each analog computer (Figure 9). This switch will allow communication from digital Computer 'A' only; allow access from digital computer 'B' only; allow access from both digital computers; or allow access from neither digital computer. An additional switch position will allow complete isolation of the analog computer from the interface controller and allow direct access by a small digital set-up computer.

## 10.3 Addressing an Analog Computer:

The digital computer will be able to address an analog computer by sending an address selection code to the interface controller. When the address for the analog computer is received, the interface will determine whether the digital access selection switch is in the proper position to allow access by that digital computer. A check will also be made to see if the analog computer is currently reserved by the other digital control interface. If the analog computer is not reserved and the digital address selection is allowed, the analog computer will be reserved by the addressing computer until a release command is sent by the digital computer. Any attempts to address the analog computer by the other digital computer will be rejected until this release command is sent. However, the other digital computer may communicate with any of the other analog computers whose digital access selection switch allows its addressing. If the controller rejects a digital computer, status information will be furnished so that the digital computer may determine the reason for the rejection.

ADDRESS SELECTOR, DVM READOUT & SETPOT SYSTEMS

10.4 Busy Status and End of Operation Interrupt:

If the operation selected by the digital computer cannot take place within the speed required for the digital computer to execute a further command, this function will cause the activation of a busy sense line. This busy sense line will stay set until the operation is completed. The hybrid computer programmer will also have the option of selecting an interrupt on end of operation. This interrupt will allow the digital processor to continue on other calculations and be interrupted when the slower function requested of the analog computer is completed. All functions on the analog computer of which the controller cannot complete at computer speed, will utilize this busy and interrupt on end of operation signals.

#### 10.5 Address Selection:

The digital computer, through the controller, will be able to select any computing component on the analog computer's patchboard that can be selected by the analog computer's address selection system (Figure 9).

10.6 DVM Readout:

The computer may readout any analog component of the analog patchboard which has been previously selected by an address select command (Figure 9). The DVM readout may be selected with or without an interrupt on the end of the operation.

#### 10.7 Setting Pots:

The digital computer may set a pot on the analog computer whose address has been previously selected (Figure 9). This action will incorporate a command to place the pot in the check submode. The operation may take place with or without interrupt on the end of operation. The controller will raise the busy status line as long as the operation is taking place. Before dropping the status line or generating an interrupt to end of operation, a error set pot status bit will be set if the pot could not be set within the required tolerance.

#### 10.8 Mode Control:

The interface will be able to slave to the mode of a master analog computer or the analog computers will be able to slave to the interface. Status information as to the mode of the master analog computer or the interface will be available to the digital computers. The digital computer will be able to control all the modes of the analog computer when the analog

computers are slaved to the interface (e.g. run, hold, initial condition, pot set, rate test, status test). The selection of the slaving of each analog computer will be under control of a manual mode slave selector switch located on each of the five analog computers (Figure 10). The functions of this switch are a supplement to the analog computer's own mode slaving system.

#### 11.0 Cabling:

#### 11.1 General:

The interface vendor shall assume responsibility for the construction and installation of all cables (e.g. control, power and data transmission), necessary to integrate each of the two interface systems into the desired hybrid computing system.

#### 11.2 ADC Channels:

16 ADC channels from interface 'A' (8 with, 8 without S/H amplifiers) shall be cabled to analog computer 1 (Figure 2). The remaining channels will be cabled to analog computer 2. These channels will be terminated in a well defined location on the analog logic patchboards. ADC channels from interface 'B' shall be cabled and terminated to analog computers 4 and 5 in the same fashion.

#### 11.3 DAC Channels:

16 DAC channels from interface 'A' shall be cabled to analog computer 1 (Figure 3). The remaining 16 channels will be cabled to analog computer 2. These channels will terminate in a well defined patchboard location. The DAC channels from interface 'B' shall be cabled and terminated to analog computers number 4 and 5 in the same fashion.

### 11.4 Discrete Trunks:

60 trunk lines from interface logic patchboard 'A' shall be cabled to (Figure 6) analog computer 1, 60 to analog computer 2, and 30 to analog computer 3 (Figure 6). These lines will be terminated in a well defined location on the analog logic patchboards.

The trunk lines from interface logic patchboard 'B' shall be cabled and terminated to analog computers 3, 4 and 5 in the same fashion: 60 trunks to analog computer 5, 60 trunks to analog computer 4, and 30 trunks to analog computer 3.

#### 12.0 Installation Requirements:

The hybrid computer installation will be on a false floor with ducted air

conditioning to the computers equipment cabinets. Three phase 115 volt, 60 cycle power is available. The vendor will furnish installation information for all equipments and including:

- Any unique equipment or requirements

- e Floor loading

- Power Requirements

- Suggested Layouts

- Layout Restrictions

- Air conditioning and environmental requirements

- Maintenance and space requirements

- Dimensions and floor cutouts for each cabinet

- Maximum and desired cable lengths.

#### 13.0 Documentation Requirements:

The vendor shall deliver to IMSC two complete sets of interface documents at the same time he delivers the interface. Each set shall contain complete and accurate manuals on: Wiring and installation schematics; maintenance and operational procedures.

#### 14.0 Software Requirements:

Software will be required to satisfactorily demonstrate the effective operation of the interface system. The vendor is referred to the software requirements outlined in the digital section of the RFP entitled "IMSC Hybrid Computer, Digital Section". Effective interface diagnostic and maintenance routines will be evaluated as part of the system's total capability and are a very desirable feature. A proposal by the vendor whereby the acceptance software would encompass sophisticated interface, diagnostics and maintenance routines, would be given due consideration by Lockheed.

# LOCKHEED MISSILES AND SPACE COMPANY

HYBRID COMPUTER

DIGITAL SECTION

### INDEX

- Title 1.0 2.0 Purpose 3.0 4.0 4.1 4.2 4.3 4.4

- Introduction

- Digital Computer Hardware

- Processors

- 4.1.1 Floating Point

- 4.1.2 Interrupts

- 4.1.3 Control and Status Lines

- 4.1.4 Core Addressing

- 4.1.5 Time Sharing Hardware

- Internal Clock 4.1.6

- Memory Requirements

- Data Channels

- Peripherals

- 4.4.1 Card

- 4.4.2 Printers

- Tape Units 4.4.3

- 4.4.4 Punch

- 4.4.5 System Control and Checkout Consoles

- 4.4.6 Optional Capability

- 4.5 Mass Memory

- 4.6 Interface

- 4.6.1 Vendor's Ability

- 4.6.2 System Responsibility

- Installation Requirements 4.7

- Software Introduction 5.0

- 5.1 Requirements

- Hybrid Requirements 5.1.1

- Scientific Digital Computation 5.1.2

- Integrated Software 5.1.3

- Operational Philosophy 5.2

- Basic Operating System 5.2.1

- Time Sharing Software 5.2.2

- 5.2.3 Maintenance in a Time Sharing Mode

### 5.3 Software Packages

- 5.3.1 Executive

- 5.3.1.1 Job Processing

- 5.3.1.2 Input-Output Organization

- 5.3.1.3 Priority Interrupt Handling

- 5.3.1.4 Time Shared Processing

- 5.3.1.5 Program Debugging Aids

- 5.3.2 Hybrid Executive

- 5.3.3 Hybrid Debugging

- 5.3.4 Request Package

- 5.3.5 Fortran IV

- 5.3.6 Assembler

- 5.3.7 Real Time Fortran

- 5.3.8 Simulation Languages

- 5.3.9 Analog Program Check

- 5.3.10 Computer Diagnostic

- 5.3.11 Interface Diagnostic

- 5.3.12 Analog Computer Diagnostic

- 5.3.13 Installation and Checkout

- 5.3.14 Acceptance Tests

- 5.3.15 Disc Oriented Software

- 6.0 Exhibits

- 6.1 Fortran Compilations

- 6.2 Library Routines

- 7.0 Card Keypunch

- 8.0 Bidders Instructions

- 8.1 Costs and Technical Response

- 8.2 Prices for Procurement Options

- 8.3 Personnel Associated with Contract

#### 1.0 Title:

Lockheed Missiles and Space Company, Hybrid Computer Digital Section.

#### 2.0 Purpose:

The purpose of this RFP is to set forth the requirements of the Digital Section of the Hybrid Computational Facility for Lockheed Missiles and Space Company, Sunnyvale, California. This section of the proposal will deal with the digital computer and its peripheral equipment. This section will also contain the software which is required for the hybrid facility.

#### 3.0 Introduction:

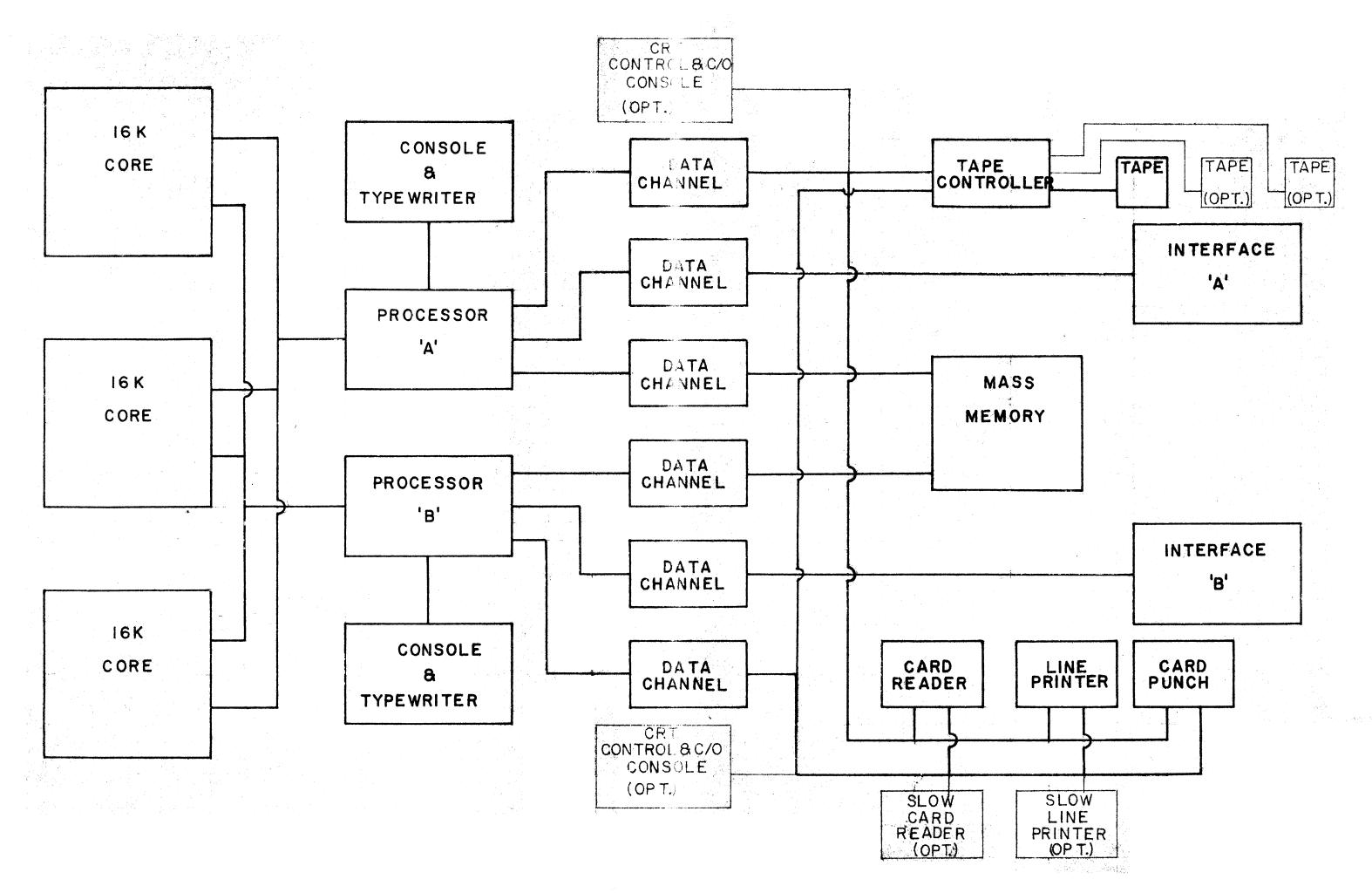

The Hybrid Computer Laboratory will contain two medium sized digital computers and a number of analog consoles. The equipment is expected to solve hybrid, pure digital, and pure analog problems.

The computer system is described in Figure D-1. The system may be divided and operated as two independent systems, or combined to form one large computational system. In the early stages of system operation, the system will operate in a number of fixed configurations. As system capability is increased, the system will become an integrated computational system where equipment allocation is under program control.

The Digital Section of this proposal involves furnishing the digital computer and associated digital peripheral equipment which will be integrated into an operational hybrid system. The requirements of this system have been evaluated and are presented.

Alternate implementations of this capability will be evaluated, if presented, if they are within the framework of the operational philosophy and fulfill the system requirements.

#### 4.0 Digital Computer Hardware:

#### 4.1 Processors

The computer's main frame will consist of two medium speed computers. Alternate configurations of a large processor may be presented. These computers will be evaluated according to their capability of performing high speed scientific computations and their ability to be systemized in a hybrid environment. A secondary consideration of importance will be the effectiveness of their operation as a time shared system.

#### 4.1.1 Hardware Floating Point

The system will be required to have hardware floating point with an accuracy of at least ten decimal digits. The computer will be

evaluated on its speed in operating on floating point numbers with the following minimum requirements: floating add, 20 microseconds, floating subtract 20 microseconds, floating multiply, 30 microseconds, and floating divide, 30 microseconds. The speed of the floating point arithmetic unit will be evaluated by the instruction timing, execution time of standard arithmetic routines, and execution time of a Fortran compiled program.

#### 4.1.2 Interrupts

Each compute module must contain a multi-level interrupt system. This system will contain the interrupts required for controlling the standard peripherals plus 24 free interrupts for the analog computer interface. Interrupts will be supplied with the ability to arm or disarm each selectively under program control. The vendor will comment on each of the following subjects:

- 1. Interrupt expansion

- 2. Interrupt priorities

- 3. The effect of shared core on the interrupt system.

#### 4.1.3 Control and Status Lines

The digital computer will be evaluated on its ability to directly control external status and control lines. Optional pricing should be included for such lines as may be required for the vendor furnishing the computer interface.

#### 4.1.4 Core Addressing

The manufacturer will discuss the method by which each processor is addressing the 48K of memory specified in Section 4.2. If the memory addressing scheme is non-standard, a complete documentation is required of the effect of this non-standard memory addressing on the vendor's software.

#### 4.1.5 Time Sharing Hardware

The ability of the computer to be utilized as a time shared system will be discussed. Hardware features such as memory protection and dynamic relocation will be discussed.

#### 4.1.6 Internal Clock:

Each processor will contain an internal clock.

#### 4.2 Memory Requirements

The memory requirements of the digital system are 48K of 24 bit memory or its equivalent. The memory cycle time will be two microseconds or less.

The memory size was calculated on the basis that, (one) computer instructions are stored per memory word, and (two), storage cells are required for floating point numbers. The floating point numbers will be of the accuracy required for ten decimal digits. The maximum memory module size is 16K with each processor having independent access.

#### 4.3 Data Channels

Each compute module will contain a data channel for the standard peripherals, and a data channel for the mass memory. Additional data channels will be required for the analog interface as determined by its vendor. The vendor shall indicate the variety of standard data channels available for interfacing.

## 4.4 Peripherals

The digital computer peripherals will be specified in this section. The peripheral speeds are indicated as a minimum requirement.

#### 4.4.1 Card Reader

The system will contain a card reader which is accessible to either computer. This card reader will have the capability of reading a standard IRM card at the rate of at least 800 cards per minute. Optional pricing will also be included in the proposal for a high speed card reader on Computer A, and a low speed card reader on Computer B.

#### 4.4.2 Printers