# VIP-640A/VIP-1024A VIDEO DIGITIZER BOARDS for the VMEbus TECHNICAL MANUAL 268-MH-01 Rev. 0 February 10, 1987

| 4 | PR  | OGRAMMING 4 -                    | 1          |

|---|-----|----------------------------------|------------|

|   | 4.1 | The Memory Map                   | 1          |

|   | 4.2 | Pixel Access                     | 1          |

|   | 4.3 | LUT Access                       | 4          |

|   | 4.4 | CRTC Access                      | 5          |

|   | 4.5 | Video Keying                     | 5          |

|   | 4.6 | Video Adjustments                | 7          |

|   | 4.7 | Registers and Lookup Tables      | 8          |

|   |     | 4.7.1 Control Register 0         | L <b>O</b> |

|   |     | 4.7.2 Control Register 1         | l 1        |

|   |     | 4.7.3 Mask Register              | l <b>2</b> |

|   |     | 4.7.4 Status Register            | L <b>3</b> |

|   |     | 4.7.5 Snapshot Register          | <b>[4</b>  |

|   |     | 4.7.6 Video Gain Register        | L <b>4</b> |

|   |     | 4.7.7 Video Offset Register      | 15         |

|   | 4.8 | SY6845E CRT Controller           | 16         |

|   |     | 4.8.1 CRTC Address Register      | ۱7         |

|   |     | 4.8.2 CRTC Status Register       | ۱7         |

|   |     | 4.8.3 CRTC Data Register         | ٤١         |

|   |     | 4.8.4 Pan Control                | L8         |

|   |     | 4.8.5 Scroll Control             | 18         |

|   | 4.9 | SY6845E CRT Controller           | 19         |

|   |     | 4.0.6 SV6845F Internal Registers | 1 Q        |

# VIP-640A/VIP-1024A VIDEO DIGITIZER BOARDS

for the VMEbus

TECHNICAL MANUAL

268-MH-01

Rev. 0

February 10, 1987

| This Manual Is Valid For The Following Products |               |               |  |  |

|-------------------------------------------------|---------------|---------------|--|--|

| Name                                            | Hardware I.D. | Firmware I.D. |  |  |

| VIP-640A                                        | REV. 1        |               |  |  |

| VIP-1024A                                       | REV. 1        |               |  |  |

|                                                 |               |               |  |  |

MATROX Electronic Systems Limited 1055 St Regis Blvd., Dorval, Quebec Canada H9P 2T4

Tel.: (514) 685-2630 Telex: 05-822798

# Contents

| 1 | INT  | RODUCTION              | 1 - 1  |

|---|------|------------------------|--------|

| 2 | SPE  | CIFICATIONS            | 2 – 1  |

| 3 | FUI  | NCTIONAL DESCRIPTION   | 3 - 1  |

|   | 3.1  | Master/Slave Operation | 3 - 2  |

|   | 3.2  | Board Control          | 3 - 3  |

|   | 3.3  | Input and Conversion   | 3 - 4  |

|   | 3.4  | Input Lookup Table     | 3 - 5  |

|   | 3.5  | Frame Buffer           | 3 - 6  |

|   | 3.6  | The Bit Mask           | 3 - 7  |

|   | 3.7  | Frame Grabbing         | 3 - 7  |

|   | 3.8  | Video Modes            | 3 - 8  |

|   |      | 3.8.1 Normal Mode      | 3 - 8  |

|   |      | 3.8.2 Zoom Mode        | 3 - 10 |

|   | 3.9  | Video Output           | 3 - 10 |

|   | 3.10 | Video Keying           | 3 - 10 |

|   | 3.11 | Output Lookup Tables   | 3 - 11 |

| Ļ | PR  | OGRAMMING 4 - :                  | L |

|---|-----|----------------------------------|---|

|   | 4.1 | The Memory Map                   | 1 |

|   | 4.2 | Pixel Access                     | 1 |

|   | 4.3 | LUT Access                       | 4 |

|   | 4.4 | CRTC Access                      | 5 |

|   | 4.5 | Video Keying                     | 5 |

|   | 4.6 | Video Adjustments                | 7 |

|   | 4.7 | Registers and Lookup Tables      | 8 |

|   |     | 4.7.1 Control Register 0         | 0 |

|   |     | 4.7.2 Control Register 1         | 1 |

|   | •   | 4.7.3 Mask Register              | 2 |

|   |     | 4.7.4 Status Register            | 3 |

|   |     | 4.7.5 Snapshot Register          | 4 |

|   |     | 4.7.6 Video Gain Register        | 4 |

|   |     | 4.7.7 Video Offset Register      | 5 |

|   | 4.8 | <b>SY6845E CRT Controller</b>    | 6 |

|   |     | 4.8.1 CRTC Address Register      | 7 |

|   |     | 4.8.2 CRTC Status Register       | 7 |

|   |     | 4.8.3 CRTC Data Register         | 8 |

|   |     | 4.8.4 Pan Control                | 8 |

|   |     | 4.8.5 Scroll Control             | 8 |

|   | 4.9 | SY6845E CRT Controller           | 9 |

|   |     | 4.9.6 SY6845E Internal Registers | 9 |

| 5 | STI | RAPS 5 -                                  | 1   |

|---|-----|-------------------------------------------|-----|

|   | 5.1 | Strap Notation                            | . 1 |

|   | 5.2 | Status Bit                                | . 1 |

|   | 5.3 | Board Address Selection                   | . 2 |

|   |     | 5.3.1 Addressing Mode                     | · 2 |

|   |     | 5.3.2 Memory Space                        | · 2 |

|   |     | 5.3.3 Page and Register Address Selection | · 2 |

|   | 5.4 | Master and Slave Setup                    | - 4 |

|   | 5.5 | Sync Selection                            | - 4 |

|   |     | 5.5.1 Input Sync Source                   | - 5 |

|   |     | 5.5.2 Composite Sync Type                 | - 5 |

|   |     | 5.5.3 Output Channel Sync Polarity 5 -    | - 5 |

|   |     | 5.5.4 Feedback Channel Input Impedance    | - 5 |

|   | 5.6 | Camera Connector                          | - 5 |

|   |     | 5.6.1 Pixel Clock                         | - 5 |

|   |     | 5.6.2 Vertical Sync                       | - 6 |

|   |     | 5.6.3 Sync                                | - 6 |

|   | 5.7 | Factory-Set Straps                        | - 6 |

|   |     | 5.7.1 Expansion Strap                     | - 6 |

|   |     | 5.7.2 Configuration Straps                | - 7 |

|   | 5 è | Stran Summary 5 -                         | _ & |

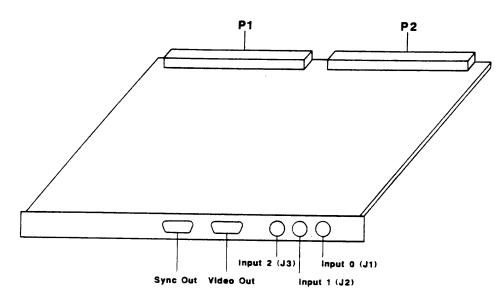

| 6 | CO   | CONNECTORS   |                                                   |              |  |  |

|---|------|--------------|---------------------------------------------------|--------------|--|--|

|   | 6.1  | Extern       | nal Connectors                                    | 6 - 2        |  |  |

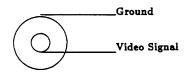

|   |      | 6.1.1        | Video Input 0 (J1), Input 1 (J2) and Input 2 (J3) | 6 - 2        |  |  |

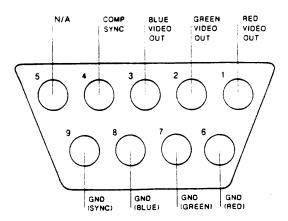

|   |      | 6.1.2        | Video Output (J4)                                 | 6 - 2        |  |  |

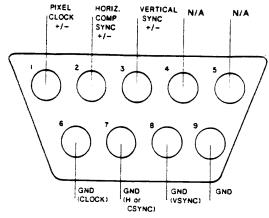

|   |      | 6.1.3        | Camera (J5)                                       | 6 – 3        |  |  |

|   | 6.2  | VMEb         | ous Board Connectors (P1 and P2)                  | 6 – 3        |  |  |

|   |      | 6.2.1        | Sync-Bus                                          | 6 - 5        |  |  |

| 7 | MA   | INTE         | NANCE AND WARRANTY                                | 7 – 1        |  |  |

| A | INS  | TALL.        | ATION                                             | <b>A</b> – 1 |  |  |

| В | DAT  | ra sh        | EETS                                              | B - 1        |  |  |

| C | NOI  | MINA         | L GAIN AND OFFSET                                 | C - 1        |  |  |

| D | INI: | <b>FIALI</b> | ZATION EXAMPLE                                    | <b>D</b> – 1 |  |  |

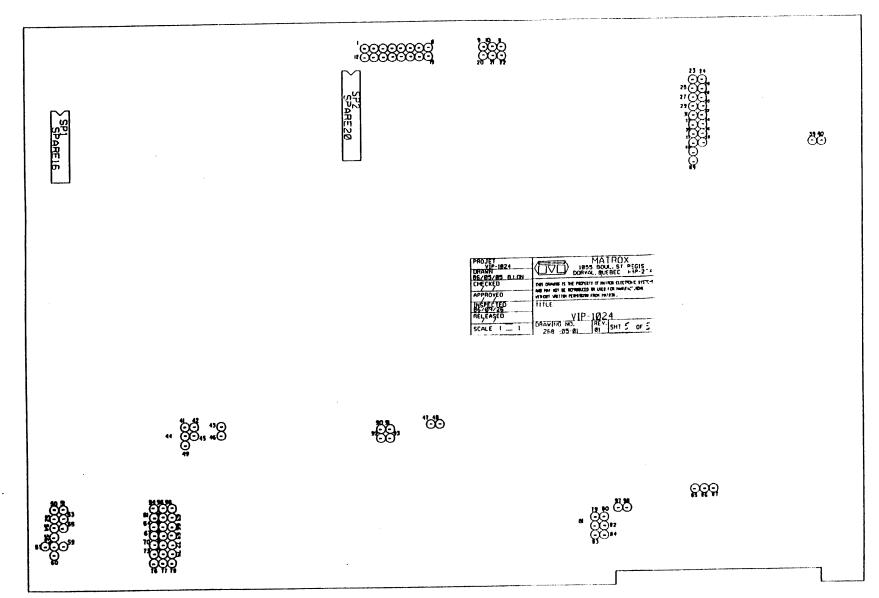

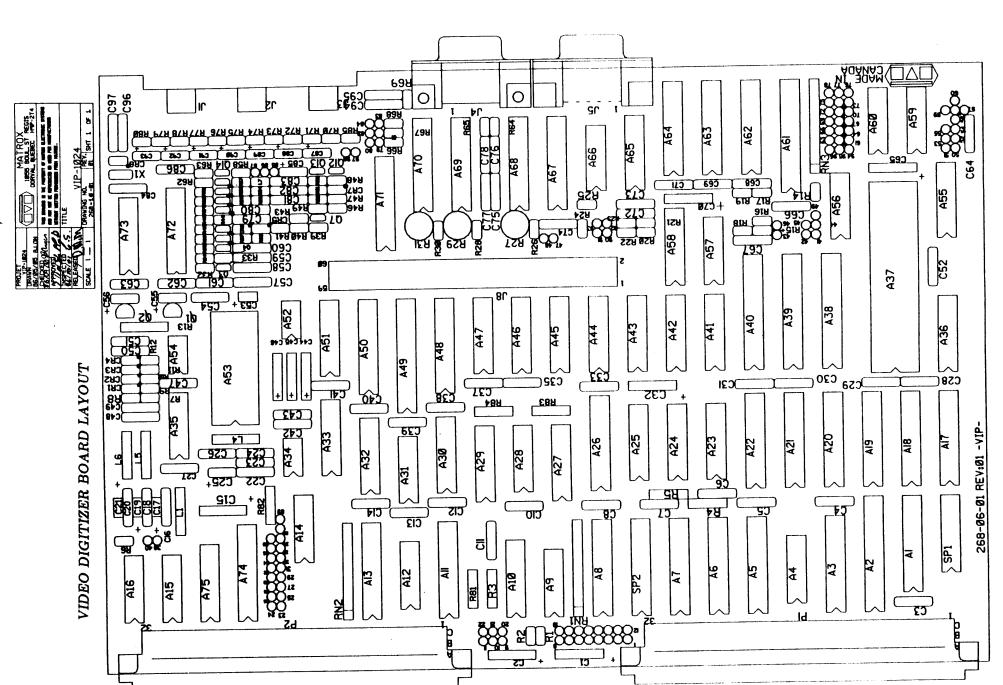

| E | VID  | EO D         | IGITIZER BOARD LAYOUT                             | E - 1        |  |  |

| F | REE  | FEREN        | NCES                                              | F - 1        |  |  |

# List of Figures

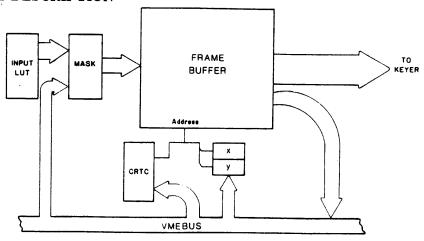

| 3.1 | BLOCK DIAGRAM OF VIP                          | 3 - 1  |

|-----|-----------------------------------------------|--------|

| 3.2 | THREE BOARDS COMBINED FOR RGB OPERATION       | 3 - 2  |

| 3.3 | INPUT SECTION                                 | 3 - 4  |

| 3.4 | INPUT SIGNAL ADJUSTMENT                       | 3 - 5  |

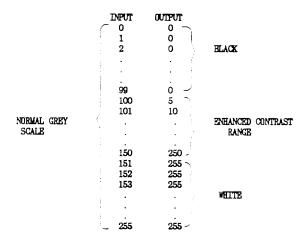

| 3.5 | INPUT LUT CONFIGURED FOR CONTRAST ENHANCEMENT | 3 - 5  |

| 3.6 | FRAME BUFFER                                  | 3 - 6  |

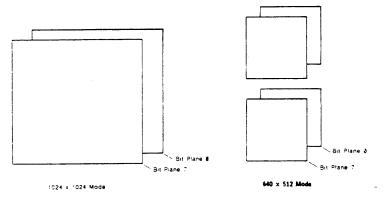

| 3.7 | VIP-1024 VIDEO MODES                          | 3 - 7  |

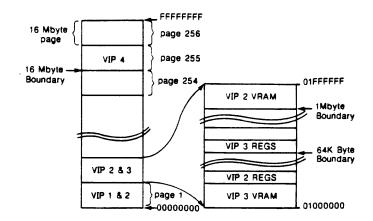

| 4.1 | SAMPLE MEMORY MAP FOR 4 BOARDS                | 4 - 2  |

| 4.2 | PIXEL DATA ACCESS                             | 4 - 2  |

| 4.3 | LUT DATA ACCESS                               | 4 - 3  |

| 4.4 | VIDEO KEYING                                  | 4 - 5  |

| 4.5 | KEYING AND OUTPUT SECTION                     | 4 - 6  |

| 4.6 | INPUT SIGNAL ADJUSTMENT                       | 4 - 7  |

| 4.7 | EXAMPLE OF OFFSET AND GAIN ADJUSTMENTS        | 4 - 8  |

| 5.1 | STRAP LOCATIONS                               | 5 - 10 |

| 6.1 | CONNECTOR LAYOUT                              | 6 – 1  |

| 6.2 | INPUT VIDEO CONNECTOR                         | 6 - 2  |

#### LIST OF FIGURES

| 6.3 | OUTPUT VIDEO CONNECTOR  | 6 – 2 |

|-----|-------------------------|-------|

| 6.4 | OUTPUT CAMERA CONNECTOR | 6 - 3 |

# List of Tables

| 2.1 | FRAME BUFFER AND DISPLAY SPECIFICATIONS | - 2 |

|-----|-----------------------------------------|-----|

| 3.1 | FRAME BUFFER AND DISPLAY INFORMATION    | - 9 |

| 3.2 | GREY LEVEL - COLOR TRANSFORMATION       | 11  |

| 4.1 | KEYING CONTROL                          | - 6 |

| 4.2 | REGISTER AND LUT OFFSETS 4              | - 8 |

| 4.3 | VIP-1024A REGISTER SUMMARY              | 19  |

| 4.4 | VIP-640A REGISTER SUMMARY               | 20  |

| 5.1 | STRAP SUMMARY Part One                  | - 8 |

| 5.2 | STRAP SUMMARY Part Two                  | - 9 |

| 6.1 | P2 CONNECTOR PIN SIGNAL NAMES 6         | - 4 |

#### LIST OF TABLES

## Chapter 1

# INTRODUCTION

The VIP-640A and VIP-1024A are real-time video frame-grabbers for the VMEbus and are configured as VME slave modules. The VIP can grab picture frames from a video input on a single or continuous basis and send them to a CRT while performing instructions on frame storage, video keying, color enhancement, and pixel clarification from a host. This manual provides all of the information required to install and operate the two versions of the VIP.

An overview of the boards' specifications and features is provided in Chapter 2 and a more detailed description of the VIP's capabilities may be found in the functional description in Chapter 3. Chapter 4 is dedicated to programming, and provides information that the programmer must have in order to write access routines. Chapter 5 outlines the VIP's strap options and Chapter 6 gives the pin assignments for all of the board's connectors. Chapter 7 provides information on maintenance and warranty. Appendix A gives a brief installation procedure. Appendix B contains the CRTC data sheets. A "nominal gain and offset" algorithm is listed in Appendix C. Appendix D contains an initialization program written in Whitesmith C. A layout of the main board can be found in Appendix E. A list of reference sources is given in Appendix F.

This manual contains all the information required to install and operate both versions of your VIP. However, if you do have problems, feel free to telephone our Applications Engineering Department. They will be happy to answer any questions you may have.

## INTRODUCTION

# Chapter 2

# **SPECIFICATIONS**

#### **SPECIFICATIONS**

## • Display Specifications:

| MODEL     | DESCRIPTION                                                                |

|-----------|----------------------------------------------------------------------------|

|           | NORMAL MODE                                                                |

|           | 1024 	imes 1024 	imes 8-bit Frame Buffer                                   |

|           | 640 	imes 512 (European)/480 (U.S.) display and grab resolution            |

|           | 2 display image areas stored                                               |

| VIP-640A  | ZOOM MODE                                                                  |

|           | 1024 	imes 1024 	imes 8-bit Frame Buffer                                   |

|           | $320 	imes 256 \; 	ext{(European)/240 (U.S.)} \; 	ext{display resolution}$ |

|           | 12 display image areas stored                                              |

|           | NORMAL MODE                                                                |

|           | 1024 	imes 1024 	imes 8-bit Frame Buffer                                   |

|           | 512 	imes 512 (European)/480 (U.S.) display and grab resolution            |

|           | 4 display image areas stored                                               |

| VIP-1024A | ZOOM MODE                                                                  |

|           | 1024 	imes 1024 	imes 8-bit Frame Buffer                                   |

|           | $256 	imes 256 	ext{ (European)/240 (U.S.) display and grab resolution}$   |

|           | 16 display image areas stored                                              |

Table 2.1: FRAME BUFFER AND DISPLAY SPECIFICATIONS

#### • Bus:

- Double-height VMEbus

- All signals in accordance with VMEbus specification

- A32 or A24, D16 slave

- supervisor or non-privileged access

#### • Special Functions:

- Operates in continuous grab or snapshot mode

- Software provides switching between four video sources (three external and one internal feedback)

- Software vertical and horizontal pans with 16 line and 8 pixel resolution respectively

- Software enabled video keying on any pattern written into the least significant bit of the frame buffer

- Write mask to allow the user to mask off any or all of the bit planes in the frame buffer

- Software controlled offset and gain of input signal for optimization of dynamic range of A/D converter

- Input and output video lookup tables

- Software selectable lookup table maps

- Video bus through P2 connector for expansion and to gen-lock multiple boards together for true RGB input

#### • Video Sync:

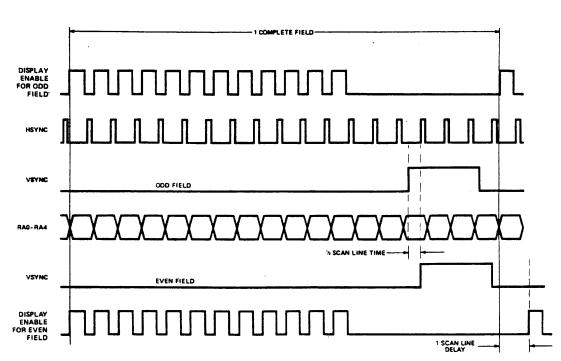

- Software switch between video sync rates for American EIA RS-170 (VIP-1024A only) or RS-330 (60Hz, 525 lines) and European CCIR (50Hz, 625 lines) TV standards

- Software selectable internal sync generator (block or serrated for the VIP-1024A; block sync only for the VIP-640A) or PLL on external sync source

- Input for external synchronization (NB: it is not possible to synchronize the VIP to an external block sync source.)

- Provide vertical and horizontal or composite sync and pixel clock on J5 connector

#### **SPECIFICATIONS**

#### • Video Timing:

- Active Video: 51.2μs

- Horizontal Sync Frequency: 15.75kHz

- Horizontal Sync Width: 4.8μs

- Vertical Sync Frequency: 60Hz (American) 50Hz (European)

- Vertical Sync Width: 190.5 µs

- All these parameters (except vertical sync width) can be changed if block sync is selected.

#### • Memory Access:

- Word (2 pixels) or byte (1 pixel) access to video RAM

- Direct access to the video RAM through a 1 Megabyte window on VMEbus

- Address of video RAM window can be strap-selected

- Fully transparent memory in both display and grab modes

- Simultaneous display of memory while digitizing

#### • Register Access:

- Direct access to the registers through a 64 Kbyte window in standard or extended address space

- Word or byte access to all devices except the LUTs which are accessible through byte access

#### • Connectors:

- Three BNC connectors for RGB input

- One female DB9 connector for RGB output with separate sync and composite sync available on all channels

- One male DB9 connector with sync and pixel clock for camera

- 36 signals defined on P2 for expansion or gen-lock

#### • Power Requirements:

- VIP-640A 16.14W  $\pm 10\%$

- \* +5VDC 2.85A ±10%

- \* +12VDC 85mA ±10%

- \* -12VDC 40mA ±10%

- VIP-1024A 16.14W  $\pm 10\%$

- \* +5VDC 2.85A ±10%

- \* +12VDC 85mA ±10%

- \* -12VDC 40mA ±10%

#### • Dimensions:

- Standard VMEbus double-height board

- \* 160mm (6.299in) deep

- \* 233.35mm (9.187in) high

- \* 20.32mm (0.8 in) thick

- \* 373.4sq cm (57.9sq in) in area

#### • Environment:

- 5°C to 46°C operating temperature

- 8% to 80% relative humidity; non-condensing

#### • Storage:

- -40°€ to 60°C

- 5% to 100% relative humidity; non-condensing

#### **SPECIFICATIONS**

## Chapter 3

# FUNCTIONAL DESCRIPTION

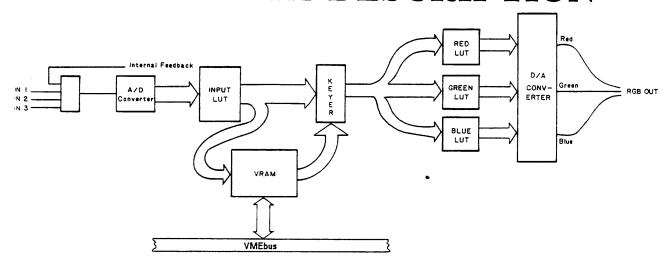

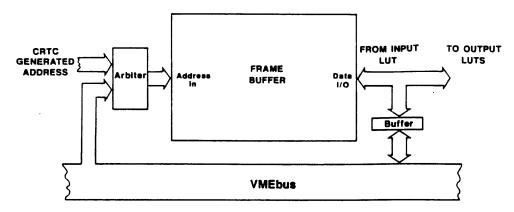

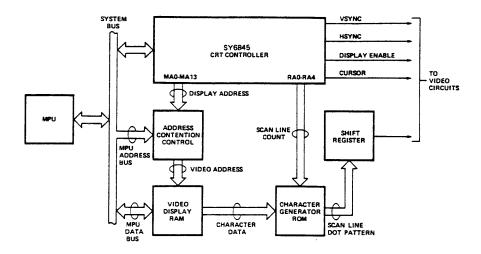

Figure 3.1: BLOCK DIAGRAM OF VIP

The VIP is a plug-in video frame grabber-digitizer board for the VMEbus. It has a resolution of  $512 \times 512/480$  or  $640 \times 512/480$  pixels (depending on model) in normal (non-zoom) mode with eight bits per pixel and a power consumption of approximately 17W. The VIP is capable of operating in a continuous or single frame grab mode and has built-in video keying capabilities as well. Frames which have been stored in the on-board frame buffer can be loaded into the system memory or onto disk. Conversely, video data, as well as lookup table data, can be written to the VIP by the system CPU. The VIP has one input and three output lookup tables, each of which has eight maps to choose from. There are three input ports and an RGB output as well as an internal feedback channel. The operation of the VIP is illustrated in Figure 3.1.

#### 3.1 Master/Slave Operation

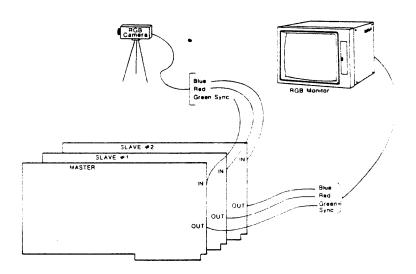

Up to four VIP boards can be combined, one master and three slaves, to simultaneously process information. To implement a Master/Slave setup, one VIP is strapped as master and one, two, or three others are configured as slaves (see section on strapping). This type of setup can be used to separately process the signals of an RGB input and produce a real color (as opposed to a pseudo-color) RGB output. An example of an RGB setup is shown in Figure 3.2. Synchronization signals are transmitted via the sync bus which must interconnect pins 1 through 5 of Rows A and C on connector P2. A fourth board may be used for another spectral input or for other purposes.

(Boards not drawn to scale.)

Figure 3.2: THREE BOARDS COMBINED FOR RGB OPERATION

#### 3.2 Board Control

The user controls the board by accessing a number of registers and direct access lookup tables (LUTs). This section gives a brief overview of these resources. More detailed descriptions are provided in the following sections.

- Input Lookup Table: 2K bytes, 8-bit wide, write-only, divided into eight 256 byte LUTs selected through Control Register 0

- Red Lookup Table: 2K bytes, 8-bit wide, write-only, divided into eight 256 byte red LUTs selected through Control Register 0

- Green Lookup Table: 2K bytes, 8-bit wide, write-only, divided into eight 256 byte green

LUTs selected through Control Register 0

- Blue Lookup Table: 2K bytes, 8-bit wide, write-only, divided into eight 256 byte blue LUTs selected through Control Register 0

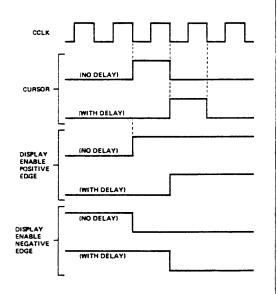

- CRTC Data Register: an 8-bit read/write data port to CRTC internal registers.

- CRTC Address Register: A 5-bit register used to set the address of the internal CRTC register to be accessed through the CRTC data register.

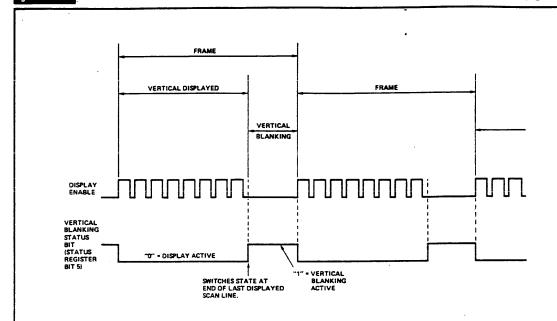

- CRTC Status Register: a 1-bit register used to read the status of the CRTC.

- Video Offset Register: an 8-bit write-only register used to set the offset of the input video before it reaches the A/D converter.

- Video Gain Register: an 8-bit write-only register used to set the gain of the input video during conversion.

- Control Register 0: an 8-bit write-only register used for miscellaneous control functions.

- Control Register 1: an 8-bit write-only register used to select the input source and type as well as some output processing options.

- Mask Register: an 8-bit write-only register used to define a mask to select which bitplanes can be overwritten in the frame buffer.

- Status Register: A 4-bit read-only register indicating the vertical blanking interval, master or slave configuration of the board, and video grabber status.

- Snapshot Register: A 0-bit read/write register used to trigger the digitizing of a single frame.

#### 3.3 Input and Conversion

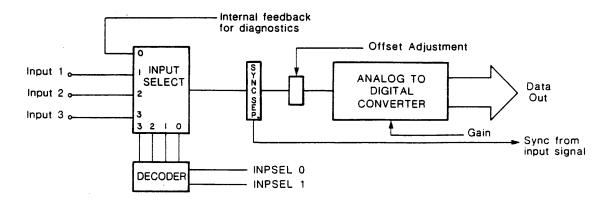

Figure 3.3: INPUT SECTION

The user inputs video to the VIP via any one of 4 software selectable inputs. The VIP may be synchronized to the video source or the video source may be synchronized to the VIP. When the VIP is to be synchronized to the video source, the user supplies composite sync as part of the video signal at the selected input or as a separate signal at input 2 (a strap determines which mode is used). Note that the VIP can only be used with an external sync source that supplies serrated vertical sync pulses. When the video source is to be synchronized to the VIP, the VIP-1024A is strapped to generate either block or serrated sync while the VIP-640A only generates block sync. This internally generated sync is then output to the video source via J5.

In addition to vertical sync, J5 provides a pixel clock and horizontal or composite sync for cameras that may need these extra signals. The polarity of these signals is strap selectable. The sync signal, generated internally or externally, is routed via a sync separator to a phase locked loop that generates all of the video timing signals required by the VIP.

After the video signal drives the sync separator, it is subject to an adjustable DC offset voltage (see Figure 3.4), which, along with adjustable gain, allows the user to center any portion of the video signal in the analog-to-digital converter's operating range. These two controls are similar to the brightness and contrast controls on a television, and allow the user to digitize only that part of the video that is of interest to him.

After the signal has been adjusted, it is processed by an A/D converter. It is then digitized in real time, producing 8-bit codes that are used as indices or addresses to the input lookup table which provides resulting pixel data. This pixel data is then stored in the frame buffer or is output to the CRT.

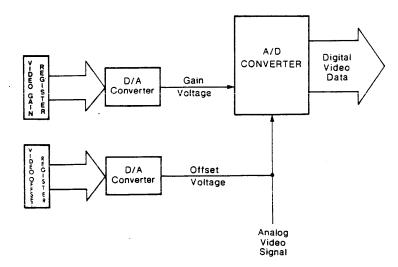

Figure 3.4: INPUT SIGNAL ADJUSTMENT

#### 3.4 Input Lookup Table

An input lookup table is provided to enable the user to manipulate the video data as it is taken from the A/D converter. The input LUT can be loaded from the VMEbus and is subdivided into eight individual 256 byte maps. This allows the user to load eight discrete sets of data into the LUT in order to modify or manipulate the current frame. The input LUT maps the

Figure 3.5: INPUT LUT CONFIGURED FOR CONTRAST ENHANCEMENT

incoming data to values set up by the user, and can be used as an image processing device when it is loaded with the appropriate data. Figure 3.5 illustrates a LUT map set up for contrast enhancement. In this example the lighter greys will exit the LUT as white and the darker greys as black. The middle greys (values 100 to 150) have their grey range expanded so that their values will represent the full range of greys from black to white. This technique is used to isolate details in what would otherwise be an almost continuous field of grey.

#### **FUNCTIONAL DESCRIPTION**

Figure 3.6: FRAME BUFFER

#### 3.5 Frame Buffer

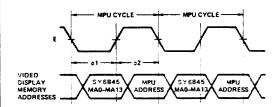

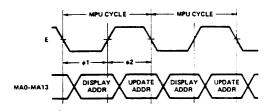

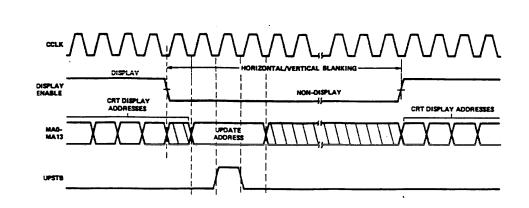

The VIP is shipped with 1MB of memory mapped VRAM (video RAM) for the frame buffer, a memory used to store frame grab data. Both the system bus and the CRT Controller have simultaneous transparent access to the frame buffer. This simultaneous transparent access is achieved by giving the CRT Controller access to the frame buffer when the controlling clock signal is high and giving access to other processes when the clock is low. Starting at a user supplied address in the frame buffer, the CRTC sends pixel data to the output LUT's in a continuous scan. The starting address is the address of the pixel that the user wants located in the upper left corner of the display. As the CRTC always sends the same number of pixels for each output scan line, it is possible, by loading a different starting address into the CRTC, to affect horizontal and vertical scrolling in the output video signal with eight pixel and sixteen line precision. (See also the SY6845E data sheets in Appendix B.) This gives the ability to pan both vertically and horizontally, which is particularly useful because of the VIP-1024A's 1024 × 1024 storage area and 512 × 512 display area, and the VIP-640A's 1024 × 1024 storage area and 640 × 512 display area.

#### 3.6 The Bit Mask

Data that is written from the bus to the VIP pass through a bit mask. This mask is set up through software and enables the user to selectively write data from the host to any or all of the eight bit-planes of the frame buffer. For example, if bit 0 of the mask register is set to 1 no data will be written into bit-plane 0 of the frame buffer. This applies to data from the bus as well as video input data.

This mask can be used to load different images into each individual bit plane in the frame buffer, allowing the user to form graphics and text overlays on protected planes by using the output LUTs to distinguish the overlay from the rest of the frame buffer. The mask can prevent writing from the digitizing port. The mask is also useful when setting up the frame buffer with the appropriate values in the least significant bit in each pixel which has a special function for video keying (See Sections 3.10 and 4.5).

#### 3.7 Frame Grabbing

When in frame grabbing mode, an A/D converter grabs a frame pixel-by-pixel from the selected input port, digitizes it, and sends it on to the LUT. Each pixel is mapped to a new value corresponding to the entries in the LUT. Finally, the frame buffer stores the pixel information.

There are two image aquisition modes: continuous grab mode, and snapshot mode. Continuous grab mode continually digitizes and updates the frame buffer with video data from the inputs. Frames are continuously digitized and stored in this buffer. Snapshot mode allows one frame to be grabbed beginning at the first VSYNC following the snapshot request. In both modes the display is at no time inhibited. This allows simultaneous display of the frame buffer while grabbing is in progress. Also, a continuous grab may be stopped, in effect freezing the last frame aquired.

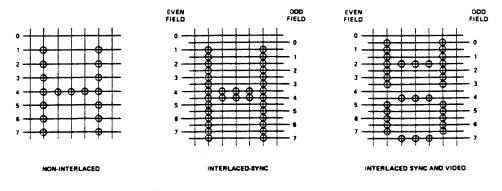

Figure 3.7: VIP-1024 VIDEO MODES

#### 3.8 Video Modes

#### 3.8.1 Normal Mode

The VIP-1024A incorporates a  $1024 \times 1024$  pixel frame buffer with a display area consisting of a  $512 \times 512/480$  window in this buffer. This window may be panned and scrolled throughout the entire frame buffer. In QUADBUF mode the frame buffer is divided into 4 quadrants, with each the size of the display window. This division allows the user to rapidly switch between the images stored in each quadrant. The pan and scroll functions used in the QUADBUF mode wraparound within the viewed quadrant.

The VIP-640A also incorporates a 1024 × 1024 pixel frame buffer, but with a display area consisting of a 640 × 512/480 window in this buffer. This display window can be panned and scrolled throughout the frame buffer allowing two complete images to be stored. QUADBUF mode can be employed on the VIP-640A if the user enables this feature and reduces the horizontal display width to 512 pixels by modifying register R1 of the CRTC. This reduction in width retains the square pixel aspect while it also allows rapid switching between images. Note that QUADBUF is not normally used with the VIP-640A because of the required reduction in display width.

Both versions of the VIP can be panned horizontally and vertically by changing the starting address in the CRTC. The video mode is selected using various bits in the control registers. In 1024 by 1024 mode the frame buffer wraps as a whole, in 512 by 512 mode, or 640 by 512 mode, each of the frame buffers is completely independent of the others.

| MODEL     | DESCRIPTION                                                                            |

|-----------|----------------------------------------------------------------------------------------|

|           | NORMAL MODE                                                                            |

|           | $1024 \times 1024 \times 8$ -bit Frame Buffer                                          |

|           | 640 	imes 512 (European)/480 (U.S.) display and grab resolution                        |

|           | 2 display image areas stored                                                           |

| VIP-640A  | ZOOM MODE                                                                              |

|           | $1024 \times 1024 \times 8$ -bit Frame Buffer                                          |

|           | $320 	imes 256 \; 	ext{(European)}/240 \; 	ext{(U.S.)} \; 	ext{display resolution}$    |

|           | 12 display image areas stored                                                          |

|           | NORMAL MODE                                                                            |

|           | 1024 	imes 1024 	imes 8-bit Frame Buffer                                               |

|           | 512 	imes 512 (European)/480 (U.S.) display and grab resolution                        |

|           | 4 display image areas stored                                                           |

| VIP-1024A | ZOOM MODE                                                                              |

|           | 1024 	imes 1024 	imes 8-bit Frame Buffer                                               |

|           | $256 	imes 256 	ext{ (European)}/240 	ext{ (U.S.)} 	ext{ display and grab resolution}$ |

|           | 16 display image areas stored                                                          |

|           |                                                                                        |

Table 3.1: FRAME BUFFER AND DISPLAY INFORMATION

#### 3.8.2 Zoom Mode

The VIP zoom function allows the aquisition and display of images in 2x Zoom Mode. This Zoom Mode is enabled by rewriting the CRTC parameters and setting bit 6 of Control Register 0. It can be used to enlarge a portion of a previously grabbed image or to grab images with reduced resolution.

When an image is grabbed in the normal display mode, the user can then utilize the Zoom Mode to display an enlarged view of the grabbed image. He can then scroll and pan to view other parts of the enlarged image.

The Zoom Mode halves the number of pixels grabbed (and displayed) both horizontally and vertically. Images grabbed in Zoom Mode occupy one quarter of the memory space required by normally grabbed images. In Zoom Mode the VIP-1024A can store 16 images while the VIP-640A can store 12 (of which 4 are stored in the unused portion of the Frame Buffer).

Continuous grabbing in different Frame Buffer areas allows up to 16 video frames to be stored dynamically during aquisition. This may be used for negative time event recording or simple animation sequences.

#### 3.9 Video Output

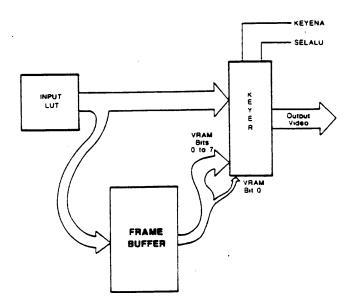

There are two sources of data for output from the VIP: the frame buffer and the video input. The user can select the output to come from either the frame buffer or the input LUT. Alternatively, the output can be dynamically switched between these two sources using Video Keying.

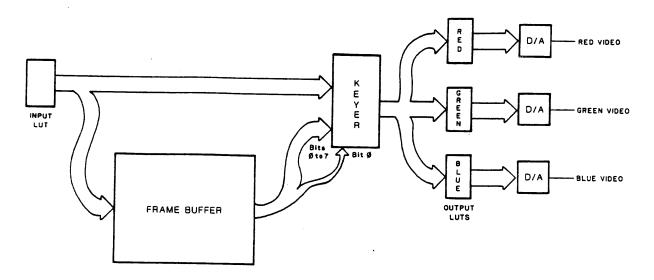

#### 3.10 Video Keying

When video keying is selected, the video input does not go into the frame buffer but passes through to the video output. As each pixel of the input image enters the VIP, the keyer, on a pixel by pixel basis, tests the least significant bit of the corresponding pixel in the frame buffer. When this bit is set to 0, the pixel from the input LUT is sent to the output LUTs, otherwise the frame buffer pixel is sent. This results in the contents of the frame buffer being displayed where the user has set the least significant bit to 1 and the input LUT being displayed elsewhere, giving the ability to overlay video, text or graphics onto the input video signal. Video Keying is described in greater detail in Section 4.5.

#### 3.11 Output Lookup Tables

| Input | Red | Green | Blue | Output |

|-------|-----|-------|------|--------|

| 100   | 0   | 0     | 255  | blue   |

| 101   | 255 | 0     | 0    | red    |

| 102   | 0   | 255   | 0    | green  |

| 103   | 100 | 100   | 100  | grey   |

Table 3.2: GREY LEVEL - COLOR TRANSFORMATION

The 8-bit output of the keyer is sent to the three output LUTs. Each LUT receives all eight bits, and then, using one of its eight maps, generates a new value. Separate values, for the red, green, and blue output signals, allow the user to have access to 256 shades of grey or 16.7 million colors (maps are loaded with appropriate intensities). The colors that are produced by a single board are pseudo-colors. This means that the colors do not represent what the camera sees but rather represent the level of intensity. The user can assign very different colors to greys which are very close – allowing the user to distinguish details with much greater ease than when the output is in greys only. An example is illustrated in Table 3.2.

The output of each LUT is sent to a digital to analog converter. These D/A converters produce, in real time, the three analog signals for the RGB output. The output of these converters can be strapped for block or serrated sync (VIP-1224A only). This sync can be individually disabled on each video output channel by selecting the appropriate strap.

#### FUNCTIONAL DESCRIPTION

# Chapter 4

# **PROGRAMMING**

This chapter provides information necessary to write access routines. It is loosely divided into two sections. The first section contains descriptions of how to utilize the various functions of the board. The second section contains information on the various registers available to the user.

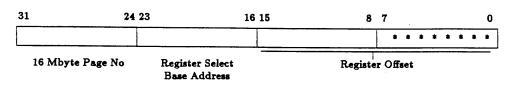

#### 4.1 The Memory Map

With 32-bit addressing, the maximum addressable memory space is 4 Gbytes. With 24-bit addressing, the maximum addressable memory space is 16M bytes. Extended 32-bit (A32) or standard 24-bit (A24) addressing modes are strap-selectable. In A32 mode, the VIP decoder must find the Video RAM and the register map in the same 16 Mbyte page (strap selected). One page of 1 Mbyte (strap selected) is decoded as direct access Video RAM. One section of 64 Kbytes is decoded as register and LUT locations. It is not necessary, however, to strap all system VIP boards into the same page (see Figure 4.1). Remember that all intervening memory space is usable and anything inadvertently written to a VIP board in the course of loading or running a program will be lost to the program and will randomly affect the board.

#### 4.2 Pixel Access

The frame buffer can be loaded with a frame grab from the video input or the video bus, and it can be both written to and read from the system bus.

#### **PROGRAMMING**

Figure 4.1: SAMPLE MEMORY MAP FOR 4 BOARDS

Figure 4.2: PIXEL DATA ACCESS

The in-bus host accesses the frame buffer by using X and Y addressing in the following format:

| Buffer Selection | BY        | $\mathbf{B}\mathbf{X}$ |           |           |           |           |           |               |            |            |

|------------------|-----------|------------------------|-----------|-----------|-----------|-----------|-----------|---------------|------------|------------|

| Address Bit      | A19       | A18                    |           |           |           |           |           |               |            |            |

|                  |           |                        |           |           |           |           |           |               |            |            |

| Y Location       | <b>Y9</b> | <b>Y8</b>              | <b>Y7</b> | <b>Y6</b> | <b>Y5</b> | <b>Y4</b> | <b>Y3</b> | $\mathbf{Y2}$ | <b>Y</b> 1 | Y0         |

| Address Bit      | A19       | A17                    | A16       | A15       | A14       | A13       | A12       | A11           | A10        | A9         |

| -X Location      | X9        | X8                     | X7        | X6        | X5        | X4        | X3        | X2            | X1         | X0         |

| Address Bit      | A18       | A8                     | A7        | A6        | A5        |           | <b>A3</b> | <b>A2</b>     | <b>A</b> 1 | <b>A</b> 0 |

If word access is used, then 2 pixels are written at the same time. The high byte is placed in the even numbered pixel locations (A0=0) and the low byte is placed in the odd numbered pixel locations (A0=1). The frame buffer may be regarded in two ways. If only one buffer of  $1024 \times 1024$  is defined, then a tenth bit is added to each coordinate by changing the two buffer selection bits BY and BX to coordinates Y9 and X9 respectively. All access to the frame buffer is by direct addressing.

Frame grabbing is accomplished by using either a snapshot grab or a continuous grab. A snapshot grab stores a single video frame and is accomplished by reading from or writing to the Snapshot Register. A continuous grab is initiated by writing a 1 to the CONFGR bit in Control Register 1. The VIP then, starting at the beginning of the next frame, grabs one frame after another into the frame buffer until the user writes a 0 to CONFGR, at which point the VIP terminates the current frame and stops grabbing. For both types of frame grab, the FGRACT bit in the Status Register indicates when frame grabbing is active.

The VIP has a mask register to mask access to selected bit-planes in the display buffer. It masks access from both the system bus and the frame grabbing process and allows the user to selectively write to any combination of the 8 bit-planes.

For further information on these commands refer to Section 4.7 Registers and Lookup Tables.

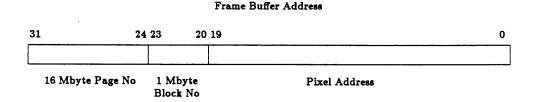

Figure 4.3: LUT DATA ACCESS

#### 4.3 LUT Access

The VIP has four lookup tables: one input and three output. The input LUT allows the user to manipulate data as it is taken from the A/D converter. Each of the three output LUTs can be used to control one of the primary colors (red, green, and blue) in the RGB output signal.

Each LUT is a 2 Kbyte static RAM subdivided into eight individual 256 byte tables. This allows the user to load eight sets of data into each LUT. The user selects the map to be used with the control bits LUTSL0, LUTSL1 and LUTSL2 in Control Register 0.

The currently selected 256 byte tables from all LUTS are mapped onto the VMEbus, from which they can be written to but not read. Modification of the lookup tables is by direct access from the in-bus host CPU to the tables' addresses as outlined in Section 4.7 and Table 4.2. Thus, of the eleven bits used to address any given lookup table, the high order 3 bits are ignored and only the low order 8 bits representing values 00 - FF are used by the decoder. The particular 256 byte block within the LUT's offset is selected by the 3 MSB bits supplied by LUTSL0, LUTSL1, and LUTSL2 of Control Register 0. For more information on this selection process see Section 4.7.1 Control Register 0.

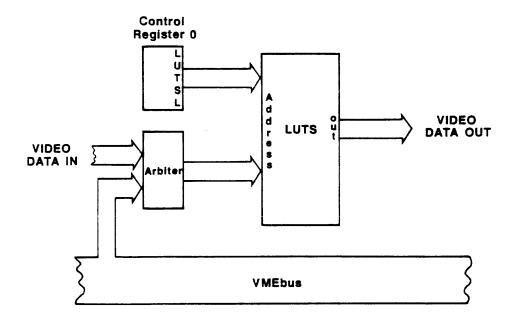

Figure 4.4: VIDEO KEYING

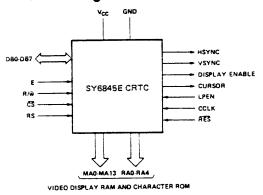

#### 4.4 CRTC Access

The VIP uses a SY6845E CRT controller. Control parameters are loaded into the CRTC using two registers: the CRTC Data Register and the CRTC Address Register. The CRTC Status Register is used to read the chip's status. Additional information on the SY6845E can be found in Appendix B while additional information on the registers used to access the CRTC is given in Section 4.8. Furthermore, if block sync is enabled on the VIP-1024A (always enabled on the VIP-640A), the CRTC may be reprogrammed for any format consistent with a 10 MHz pixel rate used in the 256 × 256 display mode.

#### 4.5 Video Keying

The VIP is capable of keying the frame buffer contents over the input video signal and outputing the resulting combined video. Keying is controlled by the three bits: KEYENA, SELALU, and the least significant bit in each pixel (Key Bit), as shown in Table 4.1. As you can see, when SELALU and KEYENA are 1, the Key Bit determines whether the output video comes from the input LUT or from the frame buffer. The bit mask can be used to set up the keying bit-plane without affecting the other planes. Note, however, that since one of the frame buffer's 8 bit-planes is used for the key, the number of colors that you can key onto the input video is 128 and not the 256 that can normally be produced by output from the frame buffer. For more information see Section 4.7.2

Figure 4.5: KEYING AND OUTPUT SECTION

| SELALU | KEYENA | KEY BIT | OUTPUT SOURCE |

|--------|--------|---------|---------------|

| 0      | 0      | 0       | input LUT     |

| 0      | 0      | 1       | input LUT     |

| 0      | 1      | 0       | input LUT     |

| 0      | 1      | 1       | input LUT     |

| 1      | 0      | 0       | frame buffer  |

| 1      | 0      | 1       | frame buffer  |

| 1      | 1      | 0       | input LUT     |

| 1      | 1      | 1       | frame buffer  |

Table 4.1: KEYING CONTROL

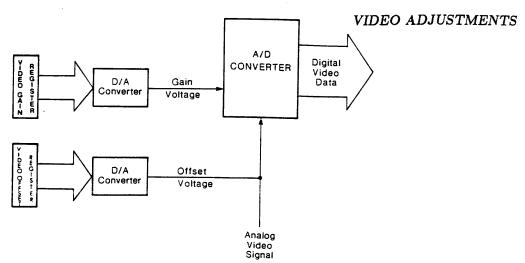

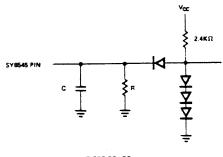

Figure 4.6: INPUT SIGNAL ADJUSTMENT

### 4.6 Video Adjustments

The VIP provides two registers for the adjustment of the gain and offset of the input analog-to-digital converter (Figure 4.6). The offset adjustment is a DC voltage that is applied to the input analog signal in order to clamp the black level to 0V. These two adjustments have the same effect as the brightness (gain) and contrast (offset) controls on a household television receiver.

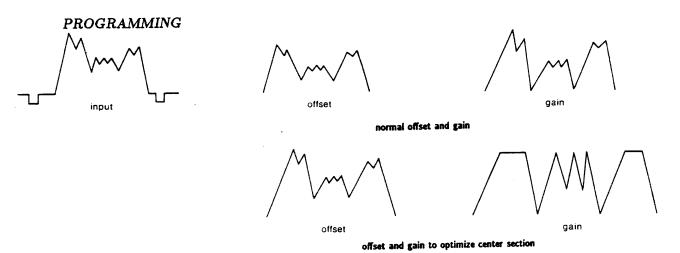

The use of these two adjustments is illustrated in Figure 4.7. The analog-to-digital converter's gain and offset parameters are adjusted either to optimize digitization of a specific portion of the video signal or to ensure maximum conversion range for specific video inputs.

In order to optimize conversion range, the following procedure is used. A black level signal is repeatedly digitized while the offset value is decremented until this level corresponds to a to a digital value of 00H. This yields the value for the offset parameter.

Using the previous offset value, a white level signal is digitized repeatedly while decrementing the gain until the white level corresponds to a digital value of FFH. The resulting parameters are valid as long as the characteristics of the video input signal do not change.

The most effective algorithm for this procedure is a binary search of the 256 possible values of the offset and gain. This results in a maximum of seven passes to determine each parameter. A summary of an algorithm to set the nominal gain and offset may be found in Appendix C.

Figure 4.7: EXAMPLE OF OFFSET AND GAIN ADJUSTMENTS

| RESOURCE                      | ACC      | MODE        | RANGE ALLOCATED              | USED             |

|-------------------------------|----------|-------------|------------------------------|------------------|

| Input lookup table            | W        | В           | 0000 - 07FF                  | 256 <sup>1</sup> |

| Red lookup table              | w        | В           | 0800 - 0FFF                  | 256              |

| Green lookup table            | W        | В           | 1000 - 17FF                  | 256              |

| Blue lookup table             | w        | В           | 1800 - 1FFF                  | 256              |

| N / A                         | "        | _           | 2000 - 27FF                  |                  |

| Control Register 0            | w        | B/W         | 2800 - 28FF                  | low byte         |

| Control Register 1            | w        | B/W         | 2900 - 29FF                  | low byte         |

| Mask Register                 | w        | B/W         | 2A00 - 2AFF                  | low byte         |

|                               | R        | B/W         | 2B00 - 2BFF                  | low byte         |

| Status Register               | R/W      | B/W         | 2C00 - 2CFF                  |                  |

| Snapshot Register             | 10, 11   | 2,          | 2D00 - 2FFF                  |                  |

| N / A                         | R/W      | B/W         | 3000 - 33FF                  | low byte         |

| CRTC Address/Status Register  | R/W      | B/W         | 3400 - 37FF                  | low byte         |

| CRTC Data Register            | w        | B/W         | 3800 - 3BFF                  | low byte         |

| Video Gain Register           | w        | B/W         | 3C00 - 3FFF                  | low byte         |

| Video Offset Register         | W        | D/ W        | 4000 - FFFF                  | 10 2,10          |

| N / A                         | <u></u>  | <u> </u>    |                              | nth.             |

| ACC: Method by which the reso | urce ma  | y be access | sed i.e. Read of Write of Do | otn.             |

| MODE: Manner by which the re  | source I | may be acc  | essed i.e. Byte or Word.     |                  |

Table 4.2: REGISTER AND LUT OFFSETS

# 4.7 Registers and Lookup Tables

There are 9 memory mapped registers and 4 lookup tables in the VIP. They occupy a 64 KByte user-strapped memory space on the VMEbus. The addresses specified in Table 4.2 are offsets from the Register Base Address assigned to the registers and LUT's on the VMEbus when the board is strapped. The operation and the functions of the VIP are controlled by the system CPU through read and write accesses to the VIP's internal registers and lookup tables. Registers are used for miscellaneous control functions such as input and output processing options, bit-plane access, board status, processing status, etc. They are also used for specific functions such as setting the video gain and offset, accessing the CRTC, snapshot enable, etc. For more information concerning the LUTs refer to Section 3.4

$<sup>^1256</sup>$  of 2048 bytes accessable at a time, selected by LUTSEL 0.1.2

#### REGISTERS AND LOOKUP TABLES

and Section 3.11. The following diagrams show register and LUT addressing for the VIP.

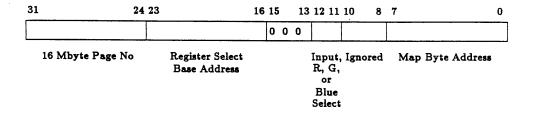

#### Register Address

\* Don't Care

## Lookup Table Address

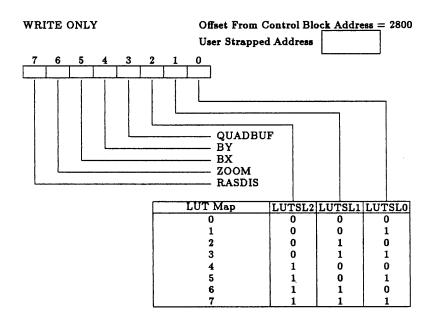

#### 4.7.1 Control Register 0

Note: all bits in this register are set to the default value (0) upon power-up (cold reset).

- Bits 0,1,2: LUTSL0, LUTSL1, and LUTSL2. Write a 0 or a 1 to each of these bits to select the corresponding set of lookup table maps used for grab or display. Write only.

- Bit 3: QUADBUF. Use this bit to set the display format. Write a 1 to this bit to select 4 independent 512 × 512 frame buffers. Write a 0 to this bit to select one 1024 × 1024 frame buffer. The QUADBUF mode is not normally used with the VIP-640A because of the reduction in horizontal display width.

- Bit 4: BY. Use this bit along with BX to select the quadrant of the display memory to be displayed when in  $4 \times 512 \times 512$  mode. Not normally used with the VIP-640A as explained above. (Used with VIP-1024A when QUADBUF=1; set to 0 on VIP-640A.)

- Bit 5: BX. Use this bit along with BY to select the quadrant of the display memory to be displayed when in  $4 \times 512 \times 512$  mode. Not normally used with the VIP-640A as explained above. (Used with VIP-1024A when QUADBUF=1; set to 0 on VIP-640A.)

- Bit 6: ZOOM. Use this bit to enable or disable the Zoom function. Set this bit to 1 to enable Zoom, or set it to 0 to disable Zoom.

- Bit 7: RASDIS. Write a 1 to this bit to prohibit video memory refresh. Write a 0 to this bit to enable a video memory refresh. This bit should always be set to 0 except when switching between internal and external synchronization.

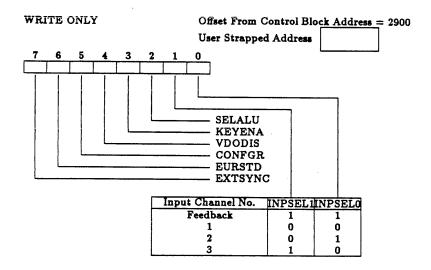

#### 4.7.2 Control Register 1

Bits 0 and 1: INPSEL0 and INPSEL1. These two bits are used to select the input source according to the table above.

Bit 2 and 3: SELALU and KEYENA. These two bits are used to determine the source of the video output. The following table shows the keying and LUT options selected by the bit values of SELAU, KEYENA, and the Key Bit. The Key Bit is the least significant bit of each pixel in the frame buffer.

| SELALU | KEYENA | KEY BIT | OUTPUT SOURCE |

|--------|--------|---------|---------------|

| 0      | 0      | 0       | input LUT     |

| 0      | 0      | 1       | input LUT     |

| 0      | 1      | 0       | input LUT     |

| 0      | 1      | 1       | input LUT     |

| 1      | 0      | 0       | frame buffer  |

| 1      | 0      | 1       | frame buffer  |

| 1      | 1      | 0       | input LUT     |

| 1      | 1      | 1       | frame buffer  |

Bit 4: VDODIS. Write a 1 to this bit to disable the video output. Write a 0 to enable the video output.

Bit 5: CONFGR. Write a 1 to this bit to enable continuous frame grabbing. Write a 0 to disable continuous frame grabbing. In the frame grab mode video frames are continuously grabbed, digitized and then stored in the video memory. The frame grab active bit in the status register is set to 0 after the continuous grab operation is disabled and a complete frame has been grabbed.

#### PROGRAMMING

- Bit 6: EURSTD. Write a 1 to this bit to select the European TV standard of 50Hz and 625 lines. Write a 0 to select the American TV standard of 60Hz and 525 lines.

- Bit 7: EXTSYNC Write a 1 to this bit to select external sync and to use the PLL to lock onto the horizontal sync in the video signal at the selected video input. Write a 0 to this bit to select a master (internal) sync and to make the on board crystal oscillator available.

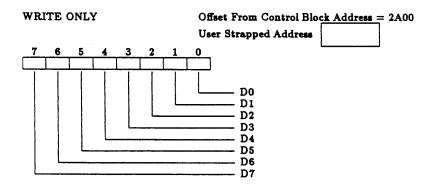

#### 4.7.3 Mask Register

Use this register to define a mask to selectively control write access to the different bit-planes in the frame buffer. This allows the user to set up the data in the frame buffer for video overlaying. Writing FF<sub>16</sub> to this mask will mask write operations to all bit-planes in the frame buffer.

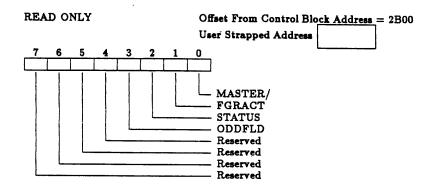

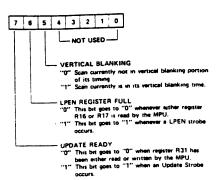

#### 4.7.4 Status Register

- Bit 0: MASTER/. When the VIP is configured as a slave, this bit is 1. When the board is configured as a master then this bit is 0.

- Bit 1: FGRACT. This bit is set to 1 when frame grabbing is active. It is set to 1 immediately after the snapshot strobe to indicate that the frame grabbing process has started and is reset to 0 once the complete frame has been grabbed. This bit is also set during continuous frame grabbing.

Note: This bit is cleared on system reset.

- Bit 2: STATUS. This bit reflects the state of the strap 43-46. It is 0 when 43-46 is IN and 1 when 43-46 is OUT.

- Bit 3: ODDFLD. Bit 3 is 1 when the display frame is in an odd field. Bit 3 is 0 when the display frame is in an even field.

Bits 4-7: reserved.

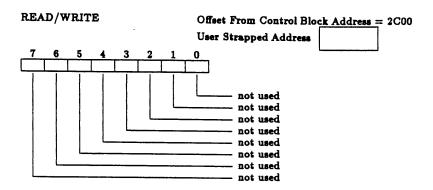

#### 4.7.5 Snapshot Register

Make an access to this 0-bit read/write register to enable the video digitizer to take a snapshot of the next frame. This register has no effect on continuous grabbing mode.

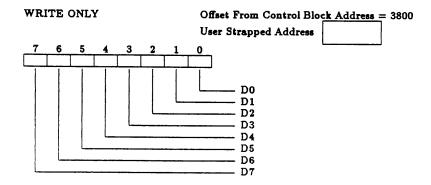

#### 4.7.6 Video Gain Register

This 8-bit register is used to control the video gain through the A/D converter. The gain can be set for 256 levels by loading these bits with values  $00_{16}$  through  $FF_{16}$ . This register is used in conjuction with the Video Offset Adjust Register to adjust the input signal. See Section 4.6 for detailed instructions on this register's use.

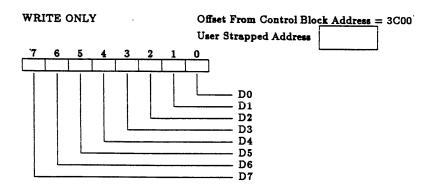

## 4.7.7 Video Offset Register

This 8-bit register is used to clamp the input analog video signal to a 5V reference level for the A/D converter. There are 256 different offset levels from  $00_{16}$  to  $FF_{16}$ .  $00_{16}$  represents 5.98V offset, and  $FF_{16}$  an offset of 4.26V. See Section 4.6 for instructions on this register's use.

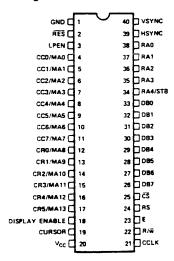

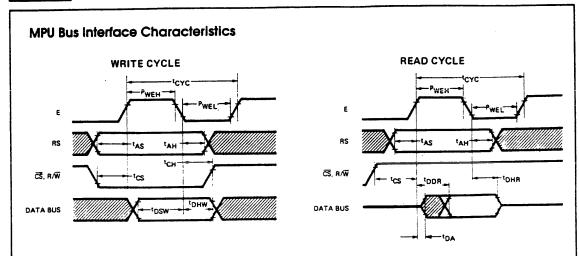

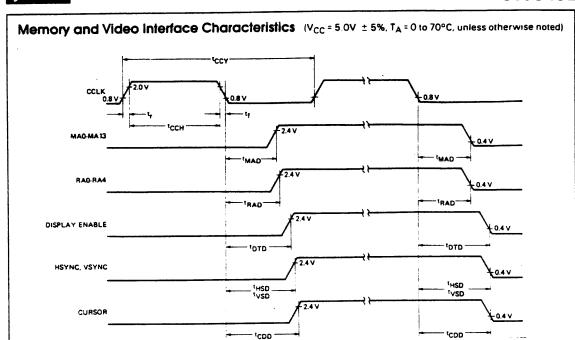

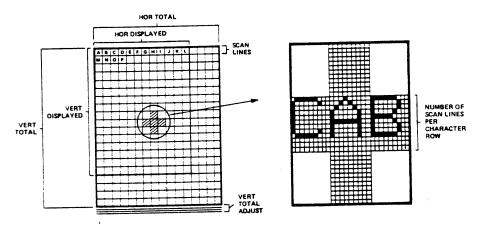

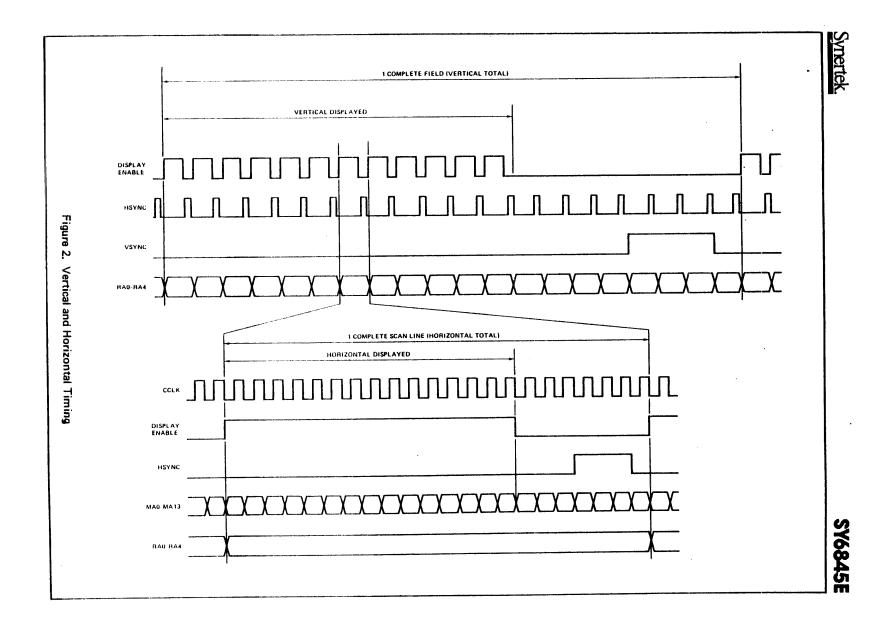

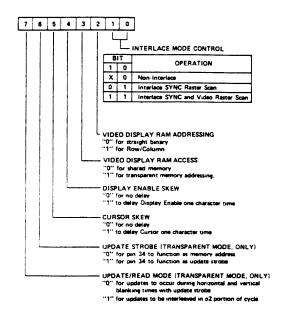

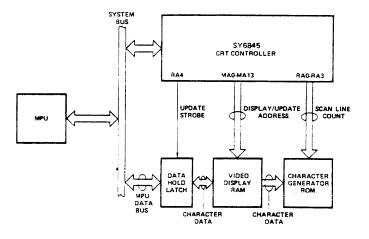

#### 4.8 SY6845E CRT Controller

The SY6845E CRT Controller has 22 accessible internal registers which are used to define and control the raster scan CRT display. One of these registers, the Address Register, is used as a pointer for the Data Register which is used to load the other 20 (since the Status Register is directly accessable) registers.

In order to load any of the other registers, first load the Address Register with the necessary pointer. Then load the Data Register with the data to be placed in the selected register. Likewise, the user can read the internal registers (if applicable) by writing their address to the Address Register and then reading the Data Register. For further explanation see the SY6845E data sheets in Appendix B.

Note: The SY6845E is capable of generating sync frequencies other than 50Hz and 60Hz. It is strongly recommended that the CRTC be loaded as specified in this manual. See Table 4.3. For information on other frequencies, contact our Applications Engineering Department.

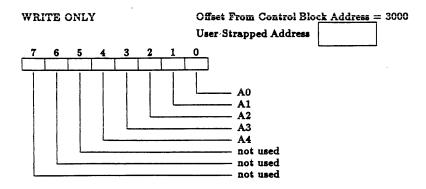

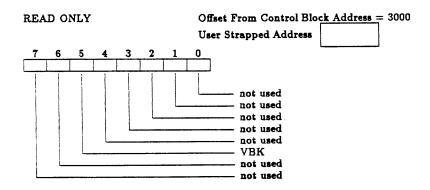

#### 4.8.1 CRTC Address Register

This 5-bit register is used as a pointer to the CRT controller's internal registers when initializing the CRT controller for use. Only the five least significant bits are used.

#### 4.8.2 CRTC Status Register

This 1-bit register holds the same place in memory as the CRTC Address Register. It is used to determine when the scan is in its vertical blanking period.

Bits 0-4: not used.

Bit 5: VBK. Bit 5 is 1 when the scan is in its vertical blanking period.

Bits 6,7: not used

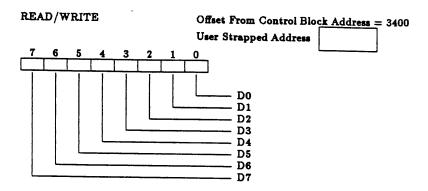

#### 4.8.3 CRTC Data Register

This 8-bit register is used in conjunction with the CRTC Address Register to indirectly load data to or read data from the CRT controller's internal registers.

#### 4.8.4 Pan Control

Pan control is achieved through register 13 of the CRTC. In order to access this register, it is necessary to write  $D_{16}$  into the CRTC Address Register. Panning is by 8 pixels (one character) at a time and is absolute with a continuous wrap around effect. Therefore, if the upper left hand corner of the screen is at coordinates (0,0) in the frame buffer, writing a one into the CRTC Data Register will move the screen right by 8 pixels and writing a two will move the screen right by 16 pixels. However, if the upper left hand corner of the screen is at coordinates (6,5), then writing a one to the data register will move the screen left 40 pixels.

#### 4.8.5 Scroll Control

Scroll control is achieved through register 12 of the CRTC. In order to access this register, it is necessary to write  $C_{16}$  into the CRTC Address Register. Scrolling is by 16 pixels (one character) at a time and is absolute with a continuous wrap around effect. Therefore, if the upper left hand corner of the screen is at coordinates (0,0) in the frame buffer, writing a  $1_{16}$  into the CRTC Data Register will move the screen down by sixteen pixels and writing a  $2_{16}$  will move the screen down by 32 pixels. However, if the upper left hand corner of the screen is at coordinates (0,4), then writing a one to the data register will move the screen up 48 pixels.

## 4.9 SY6845E CRT Controller

## 4.9.6 SY6845E Internal Registers

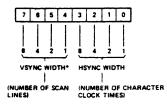

The following two tables list the SY6845E internal registers and the values that you must load these registers with for the North American (U.S.) video standard and the European video standard. Included are values for both the Normal Mode (Non-Zoom Mode) and the Zoom Mode.

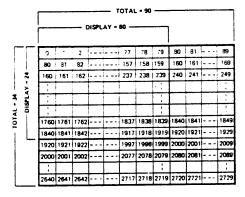

| Reg<br>Addr | Reg<br>No. | Register Type                      | Unit               | I/O<br>Type    | US<br>Std | Eur<br>Std | ZOOM<br>Mode<br>US Std | ZOOM<br>Mode<br>Eur Std |

|-------------|------------|------------------------------------|--------------------|----------------|-----------|------------|------------------------|-------------------------|

| 0           | R0         | Horisontal Total                   | Char               | Write          | 51        | 52         | 28                     | 30                      |

| 1           | R1         | Horizontal Displayed               | Char               | Write          | 40        | 40         | 20                     | 20                      |

| 2           | R2         | Horizontal Sync Position           | Char               | Write          | 42        | 43         | 20                     | 21                      |

| 3           | R3         | Vertical and Horizontal Sync Width | Char/ Scan<br>Line | Write          | 4E        | 8E         | 47                     | 87                      |

| 4           | R4         | Vertical Total                     | Char Row           | Write          | 1F        | 26         | 0F                     | 12                      |

| 5           | R5         | Vertical Total Adjust              | Scan Line          | Write          | 06        | 00         | 06                     | 00                      |

| 6           | R6         | Vertical Displayed                 | Char Row           | Write          | 1E        | 20         | 0F                     | 0F                      |

| 7           | R7         | Vertical Sync Position             | Char               | Write          | 1E        | 23         | OF                     | 11                      |

| 8           | R8         | Mode Control                       |                    | Write          | 07        | 07         | 05                     | 05                      |

| 9           | R9         | Scan Line                          | Scan Line          | Write          | 0F        | 0F         | 0F                     | 0F                      |

| A           | R10        | Cursor Start                       | Scan Line          | Write          | XX        | XX         | XX                     | XX                      |

| В           | R11        | Cursor End                         | Scan Line          | Write          | XX        | XX         | XX                     | XX                      |

| C           | R12        | Displayed Start<br>Address (H)     | _                  | Write          | 00        | 00         | 00                     | 00                      |

| D           | R13        | Displayed Start<br>Address (L)     | _                  | Write          | 00        | 00         | 00                     | 00                      |

| E           | R14        | Cursor Position (H)                | _                  | Read/<br>Write | xx        | xx         | XX                     | xx                      |

| F           | R15        | Cursor Position (L)                | _                  | Read/<br>Write | XX        | xx         | xx                     | XX                      |

| 10          | R16        | Light Pen Register (H)             |                    | Read           | XX        | XX         | XX                     | XX                      |

| 11          | R17        | Light Pen Register (L)             | _                  | Read           | XX        | XX         | XX                     | XX                      |

| 12          | R18        | Update Location (H)                | -                  | Write          | XX        | XX         | XX                     | XX                      |

| 13          | R19        | Update Location (L)                |                    | Write          | XX        | XX         | XX                     | XX                      |

| 1F          | R31        | Dummy Location                     |                    |                | XX        | XX         | XX                     | XX                      |

Table 4.3: VIP-1024A REGISTER SUMMARY

#### **PROGRAMMING**

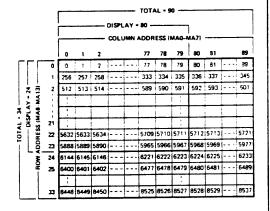

| Reg<br>Addr | Reg<br>No. | Register Type                                    | Unit      | I/O<br>Type    | US<br>Std | Eur<br>Std | ZOOM<br>Mode<br>US Std | ZOOM<br>Mode<br>Eur Std |

|-------------|------------|--------------------------------------------------|-----------|----------------|-----------|------------|------------------------|-------------------------|

| 0           | R0         | Horizontal Total                                 | Char      | Write          | 51        | 52         | 30                     | 30                      |

| 1           | R1         | Horizontal Displayed                             | Char      | Write          | 40        | 40         | 28                     | 27                      |

| 2           | R2         | Horizontal Sync Position Vertical and Horizontal | Char      | Write          | 42        | 43         | 2A                     | 28                      |

| 3           | R3         | Vertical and Horizontal Sync Width               | Char/Scan | Write          | 4E        | 8E         | 47                     | 88                      |

| 4           | R4         | Vertical Total                                   | Char Row  | Write          | 1F        | 26         | 0F                     | 12                      |

| 5           | R5         | Vertical Total Adjust                            | Scan Line | Write          | 06        | 00         | 06                     | 0A                      |

| 6           | R6         | Vertical Displayed                               | Char Row  | Write          | 1E        | 20         | 0F                     | 10                      |

| 7           | R7         | Vertical Sync Position                           | Char      | Write          | 1E        | 23         | 0F                     | 11                      |

| 8           | R8         | Mode Control                                     |           | Write          | 07        | 07         | 05                     | 05                      |

| 9           | R9         | Scan Line                                        | Scan Line | Write          | 0F        | 0F         | 0F                     | 0F                      |

| A           | R10        | Cursor Start                                     | Scan Line | Write          | XX        | XX         | XX                     | XX                      |

| В           | R11        | Cursor End                                       | Scan Line | Write          | XX        | XX         | XX                     | XX                      |

| С           | R12        | Displayed Start<br>Address (H)                   |           | Write          | 00        | 00         | 00                     | 00                      |

| D           | R13        | Displayed Start Address (L)                      | _         | Write          | 00        | 00         | 00                     | 00                      |

| E           | R14        | Cursor Position (H)                              |           | Read/<br>Write | XX        | XX         | xx                     | xx                      |

| F           | R15        | Cursor Position (L)                              | _         | Read/<br>Write | XX        | XX         | xx                     | XX                      |

| 10          | R16        | Light Pen Register (H)                           | <u> </u>  | Read           | XX        | XX         | XX                     | XX                      |

| 11          | R17        | Light Pen Register (L)                           |           | Read           | XX        | XX         | XX                     | XX                      |

| 12          | R18        | Update Location (H)                              | _         | Write          | XX        | XX         | XX                     | XX                      |

| 13          | R19        | Update Location (L)                              |           | Write          | XX        | XX         | XX                     | XX                      |

| 1F          | R31        | Dummy Location                                   |           |                | XX        | XX         | XX                     | XX                      |

Table 4.4: VIP-640A REGISTER SUMMARY

# Chapter 5

# **STRAPS**

# 5.1 Strap Notation

User configured straps select or control several functions on the VIP. This chapter describes those functions and indicates what the different strap options are. All straps on the board are made by tying together numbered wire wrap pins. When a particular strap is referred to, it is done so by giving the numbers of the two pins that are to be tied together to form the strap. In some cases the pin numbers are followed by an IN or OUT suffix to indicate whether the pins are to be strapped or left free.

#### 5.2 Status Bit

This strap determines the logic level read at bit 2 in the Status Register and it is meant to be user defined. The user may want to use it to tell the system CPU something about the VIP's current strap configuration. For example, we can use this strap to inform the host CPU that something else is using the Video-Bus.

STATUS = 0 43-46 IN STATUS = 1 43-46 OUT

#### 5.3 Board Address Selection

The number of Video Digitizer Boards that can be installed into the system is dependant upon the number of boards which can be connected on the same Sync-Bus. It is necessary, however, for each board to have a different base address. In 32-bit addressing, the user can include the VIP boards in the same 16 Mbyte page arranging them so that no memory space overlaps, or they can select a different 16 Mbyte page for one or more VIPs. For an example of this see Figure 4.1. In 24-bit addressing mode there is only one 16 Mbyte page so all VIPs must be in the same page.

#### 5.3.1 Addressing Mode

The following straps select the addressing mode.

Supervisor mode only 62-63 OUT Supervisor or non-privileged 62-63 IN

#### 5.3.2 Memory Space

The following straps select either a 16 Mbyte (24-bit address) or 4 Gbyte (32-bit address) memory space.

Address Size Address Space Strap

24-bit address 16 Mbyte 65-66 IN

32-bit address 4 Gbyte 65-66 OUT

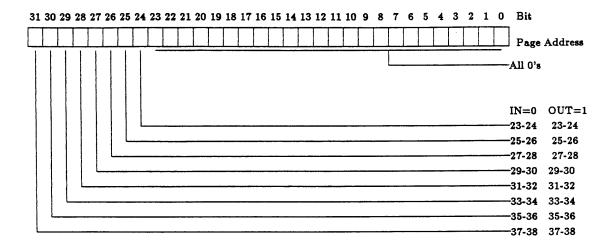

#### 5.3.3 Page and Register Address Selection

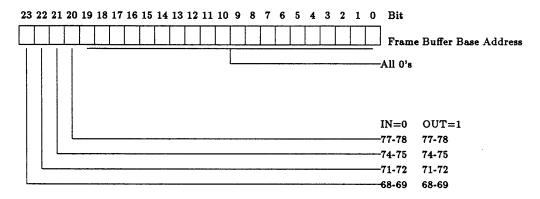

There are three sets of straps. One set determines the 16 Mbyte page for the VIP's location. Another set determines the 1 Mbyte block for the Video RAM and a third set determines the 64K block for the Registers and LUT's. In A32 mode, the VIP decoder must find the Video RAM and the register map in the same strap selected 16 Mbyte page. Thus note that in the following diagrams, the page of both the register access block and the VRAM is dependant upon the page that the high order eight bits of the 32-bit address have been strapped to on the VIP. With 24-bit addressing, this does not apply.

#### 16 Mbyte Page Selection

If your system uses a 32-bit address use the straps in the following diagram to select the 16 Mbyte page that the VIP is to be located in.

#### Register Access Block

The following diagram shows how to strap the position of the VIP's register access block on any 64 Kbyte boundary in the 16 Mbyte page selected by the page select straps.

#### 1 Mbyte Frame Buffer Boundary Selection

The following diagram shows how to strap the VIP's frame buffer on any 1 Mbyte boundary in the 16 Mbyte page selected by the page select straps.

## 5.4 Master and Slave Setup

The following straps determine whether the VIP is a master (controls the video bus) or a slave. Refer to Section 6.2.1 for information on the Sync-Bus.

Master 39-40 IN 47-48 OUT Slave 39-40 OUT 47-48 IN

# 5.5 Sync Selection

The following straps select various sync options. See Section 3.3 for input sync description. Note that block sync (RS 330) must not be selected when the board is in external sync mode.

|                                    | OPTION | IN    | OPTION | $\mathbf{OUT}$ |

|------------------------------------|--------|-------|--------|----------------|

| Input channel sync type            | RS170  | 42-45 | RS330  | 42-45          |

| Composite sync on output red gun   | YES    | 83-84 | NO     | 83-84          |

| Composite sync on output green gun | YES    | 81-82 | NO     | 81-82          |

| Composite sync on output blue gun  | YES    | 79-80 | NO     | 79-80          |

#### 5.5.1 Input Sync Source

When the VIP is taking its sync from an external source, that sync can be combined with the video on the currently selected video input or it can be a separate composite sync signal on channel 2 (green input), with one of the other inputs selected to input video. The following straps most be used to select one mode or the other.

Sync combined with video 85-86 IN 86-87 OUT Separate sync on channel 2 (green) 85-86 OUT 86-87 IN

#### 5.5.2 Composite Sync Type

The following straps allow you to select the type of sync at the output of the VIP-1024A. The VIP-640A must always be strapped for RS330 sync.

RS170 51-53 IN 53-55 OUT (VIP-1024A only) RS330 51-53 OUT 53-55 IN

#### 5.5.3 Output Channel Sync Polarity

Active High 50-52 IN 52-54 OUT Active Low 50-52 OUT 52-54 IN

#### 5.5.4 Feedback Channel Input Impedance

The following strap determines whether an internal 75 ohm termination impedence will be connected to the feedback channel input. It is used only if no load is connected to the green video output.

Internal Termination Impedence In Place 97-98 IN

Internal Termination Impedence Absent 97-98 OUT

#### 5.6 Camera Connector

#### 5.6.1 Pixel Clock

The following straps set the polarity of the Pixel Clock.

#### **STRAPS**

Active high 70-73 IN 73-76 OUT Active low 70-73 OUT 73-76 IN

#### 5.6.2 Vertical Sync

The following straps set the polarity of the vertical sync at the output.

Active high 64-67 IN 61-64 OUT Active low 64-67 OUT 61-64 IN

#### 5.6.3 Sync

The following straps select the type and polarity of the sync that is provided at pin 2 of J5.

|                             | <b>58-60</b> | 56-58 | 57-58 | 58-59 |

|-----------------------------|--------------|-------|-------|-------|

| Active high composite sync  | IN           | OUT   | OUT   | OUT   |

| Active low composite sync   | OUT          | IN    | OUT   | OUT   |

| Active high horizontal sync | OUT          | OUT   | IN    | OUT   |

| Active low horizontal sync  | OUT          | OUT   | OUT   | IN    |

# 5.7 Factory-Set Straps

#### 5.7.1 Expansion Strap

The following straps are provided for eventual expansion but in the meantime they must be positioned as follows:

| 9-10 | 10-11 | 20-21 | 21-22 | 41-44 | 44-49 |

|------|-------|-------|-------|-------|-------|

| IN   | OUT   | IN    | OUT   | OUT   | IN    |

# 5.7.2 Configuration Straps

The straps connected to pins 88 through 96 are factory configured as follows and should not be changed.

| VIP-640A  | VIP-1024A |

|-----------|-----------|

| 88-89 IN  | 88-89 OUT |

| 90-91 IN  | 90-92 IN  |

| 92-93 IN  | 91-93 IN  |

| 95-96 IN  | 95-96 IN  |

| 94-95 OUT | 94-95 OUT |

# 5.8 Strap Summary

| Pin | Name                        | Connecting Pin |

|-----|-----------------------------|----------------|

| 1   | Register Base Addr Sel A16  | 12             |

| 2   | '' A17                      | 13             |

| 3   | '' A18                      | 14             |

| 4   | '' A19                      | 15             |

| 5   | '' A20                      | 16             |

| 6   | '' A21                      | 17             |

| 7   | '' A22                      | 18             |

| 8   | '' A23                      | 19             |

| 9   | Expansion Strap             | 10             |

| 10  | 6.6                         | 9              |

| 11  | **                          |                |

| 12  | Register Base Addr Sel A16  | 1              |

| 13  | · · A17                     | 2              |

| 14  | · A18                       | 3              |

| 15  | '' A19                      | 4              |

| 16  | '' A20                      | 5              |

| 17  | '' A21                      | 6              |

| 18  | ** A22                      | 7              |

| 19  | '' A23                      | 8              |

| 20  | Expansion Strap             | 21             |

| 21  | • • •                       | 20             |

| 22  | **                          |                |

| 23  | VIP Base Address Sel A24    | 24             |

| 24  | ** A24                      | 23             |

| 25  | '' A25                      | 26             |

| 26  | '' A25                      | 25             |

| 27  | '' A26                      | 28             |

| 28  | 11 A26                      | 27             |

| 29  | '' A27                      | 30             |

| 30  | · · A27                     | 29             |

| 31  | · · A28                     | 32             |

| 32  | '' A28                      | 31             |

| 33  | · · A29                     | 34             |

| 34  | '' A29                      | 33             |

| 35  | '' A30                      | 36             |

| 36  | '' A30                      | 35             |

| 37  | '' A31                      | 38             |

| 38  | · · A31                     | 37             |

| 39  | Master Select               | 40             |

| 40  | 11                          | 39             |

| 41  | Expansion Strap             |                |

| 42  | RS170/RS330 Input Sync Type | 45             |

| 43  | STATUS                      | 46             |

| 44  | Expansion Strap             | 49             |

Table 5.1: STRAP SUMMARY Part One

| Pin      | Name                                  | Connecting Pin |

|----------|---------------------------------------|----------------|

| 45       | RS170/RS330 Input Sync Type           | 42             |

| 46       | STATUS                                | 43             |

| 47       | Slave Select                          | 48             |

| 48       | Diave Delect                          |                |

| 49       | Expansion Strap                       | 47             |

|          |                                       | 44             |

| 50       | Output Channel Sync Polarity/High     | 52             |

| 51       | Composite Sync Type/RS170             | 53             |

| 52       | Output Channel Sync Polarity High/Low | 50 or 54       |

| 53       | Composite Sync Type RS170/RS330       | 51 or 55       |

| 54       | Output Channel Sync Polarity/Low      | 52             |

| 55       | Composite Sync Type/RS330             | 53             |

| 56       | Active Low Composite Sync             | 58             |

| 57       | Active High Horisontal Sync           | 58             |

| 58       | High/Low Composite/Horizontal Sync    | 60,56,57,or59  |

| 59       | Active Low Horizontal Sync            | 58             |

| 60       | Active High Composite Sync            | 58             |

| 61       | Active Low Vertical Sync              | 64             |

| 62       | Supervisor/Non-privileged             | 63             |

| 63       | Supervisor/Non-privileged             | 62             |

| 64       | Active Low/High Vertical Sync         | 61 or 67       |

| 65       | Address Select 24/32                  | 66             |

| 66       | ••                                    | 65             |

| 67       | Active High Vertical Sync             | 64             |

| 68       | VRAM Base Address A23                 | 69             |

| 69       | '' A23                                | 68             |

| 70       | Active High Pixel Clock               | 73             |

| 71       | VRAM Base Address A22                 | 72             |

| 72       | '' A22                                | 71             |

| 73       | Pixel Clock High/Low                  | 70 or 76       |

| 74       | VRAM Base Address A21                 | 75             |

| 75       | 11                                    | 74             |

| 76       | Active Low Pixel Clock                | 73             |

| 77       | VRAM Base Address A20                 | 78             |

| 78       | 11                                    | 77             |

| 79       | Output Composite Sync/Blue            | 80             |

| 80       | 11                                    | 79             |

| 81       | Output Composite Sync/Green           | 82             |

| 82       | 2 aspas composise pluci dicen         | 81             |

| 83       | Output Composite Sync/Red             | 84             |

| 84       | Ogshas combourse plucited             | 83             |

| 85       | Input Sync Source Select              | 86             |

| 86       | Input Sync Source                     | 85 or 87       |

| 87       | Input Sync Source Green               | 86             |

| 88       | factory pin                           | 89             |

| 89       | factory pin                           | 1              |

| 1        | •                                     | 88             |

| 90       | factory pin                           | 91 or 92       |

| 91<br>92 | factory pin<br>factory pin            | 90 or 93       |

| 1 :      |                                       | 90 or 93       |

| 93       | factory pin                           | 91 or 92       |

| 94       | factory pin                           | 95             |

| 95       | factory pin                           | 94 or 96       |

| 96       | factory pin                           | 95             |

| 97       | 75 ohm internal termination           | 98             |

| 98       | 75 ohm internal termination           | 97             |

Table 5.2: STRAP SUMMARY Part Two

Figure 5.1: STRAP LOCATIONS

# Chapter 6

# **CONNECTORS**

Figure 6.1: CONNECTOR LAYOUT