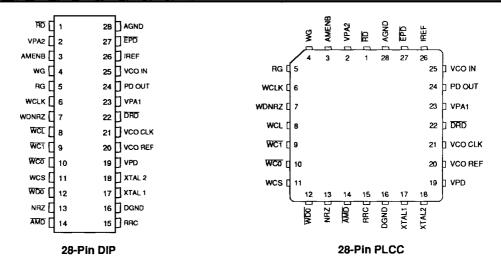

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

#### REFERENCE OSCILLATOR

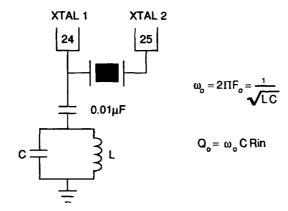

An internal reference oscillator generates the standby reference for the PLL. For the 32D5321/5322 and the 32D535/5351, a series resonant crystal of twice the data rate should be used between XTAL1 and XTAL2. For the 32D5362, the series resonant crystal should be selected at three times the data rate. If a crystal oscillator is not desired, then an external TTL compatible reference may be applied to XTAL1, leaving XTAL2 open.

If it is desired to operate a crystal at a non-fundamental or harmonic frequency, then the following network is suggested:

The typical input impedance looking into XTAL1 is approximately Rin =  $250\Omega$ . It is recommended to design the value of Qo at approximately 10 to 15. Therefore, a resonant frequency of Fo = 20 MHz would result in L  $\cong$  0.16  $\mu$ H and C  $\cong$  380 pF.

#### ATTENUATOR CIRCUIT

If a crystal oscillator is not desired, then an external TTL Compatiable reference may be applied to XTAL1 leaving XTAL2 open. It is required, however that the TTL signal be attenuated then A.C. coupled into XTAL1 using the following network:

TTL CLOCK INPUT

$$0.1 \, \mu\text{F}$$

XTAL:

The signal amplitude into XTAL1 should be attenuated to approximately 1.0 to 2.0 Vp-p; this will insure that the transients associated with TTL switching characteristics won't couple into the data synchronizer and degrade performance.

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

#### LOOP FILTER

The performance of the data synchronizer is directly related to the selection of the loop filter. The loop filter characteristics should be optimized for:

#### (A) Fast Acquisition

The ability of the loop to quickly obtain lock when the input signal to the Phase Detector is switched between the reference oscillator (crystal) and the Read Data (RD). Fast acquisition implies a large loop bandwidth so that it can quickly respond to changes at the input.

#### (B) Data Margin

The ability of the loop to ignore bit shifts (jitter) and maintain a well centered window about the data pulse train. In general, it is not desirable to allow the loop to respond to a single shifted bit as this would cause the subsequent bit to be poorly centered within its window and possibly cause an error. This requirement implies a small loop bandwidth reducing the sensitivity to high frequency jitter.

#### (C) Data Tracking

The ability to respond to instantaneous changes in phase and frequency of the data. This can be a result of such phenomena as disk rotational speed variations which cause changes in the characteristics of the incoming data stream. In general, this requirement is consistent with that of fast acquisition, however, this depends upon the application.

Although the loop performance characteristics place conflicting requirements on the loop bandwidth, the architecture of the Silicon Systems chip family significantly simplifies the design by minimizing the "step in phase" and "step in frequency" encountered when switching the Phase Detector input reference signal. A zero phase restart technique is employed to minimize the initial phase error while the standby reference oscillator keeps the VCO at the center frequency during non-read modes.

One approach in determining the initial loop filter selection is to consider the requirements imposed during acquisition. This includes both acquiring lock to the crystal reference in non-read modes, as well as locking to the preamble field prior to decoding data. The format of the sector will dictate which of these two criteria imposes the tightest restriction on acquisition.

The requirements for acquiring lock to the crystal oscillator are application specific and usually depend upon the length of the Write Splice gap. Therefore, the design approach employed in this analysis will be based upon the requirements during acquisition to the preamble field. The length (in time) of the preamble field is set by the data synchronizer's locking sequence. Knowing this length in time, and that our initial phase error is less than 0.5 radians, we can determine an acceptable loop bandwidth ( $\omega$ n) and damping factor ( $\zeta$ ). One possible loop filter configuration is as follows:

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

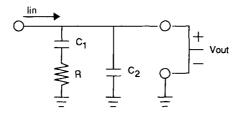

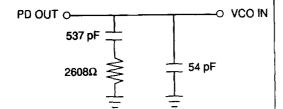

The role of C1 is as an integrating element. The larger this capacitance, the longer the acquisition time; the smaller the capacitance, the greater the ability to track high frequency jitter. The resistor R reduces the phase shift induced by C1. The capacitor C2 will suppress high frequency transients and will have minimal effect on the loop response if it is small relative to C1 (typically C2 = C1/10)

The loop filter transfer function is:

$$F(s) = \frac{Vout}{lin} = \frac{1 + sRC_1}{sC_1(1 + sC_2 R + C_2/C_1)}$$

If C2 << C1, then:

$$F(s) = \frac{Vout}{lin} = \frac{1 + sRC_1}{sC_1}$$

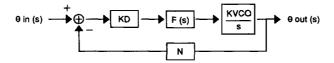

The overall block diagram for the phaselock loop can be described as:

Where:

KD = Phase Detector gain [A/rad]

F(s) = Loop filter impedance [V/A]

KVCO/s = VCO control gain [rad/s V]

N = The ratio of the reference input frequency to the VCO output frequency

The closed loop transfer function is

$$T(s) = \frac{\theta \text{out}(s)}{\theta \text{in}(s)} = \frac{G(s)}{1 + GH(s)} = \frac{KD \cdot KVCO[(1 + sRC_1)/C_1]}{s^2 + s[N \cdot KD \cdot KVCO \cdot R] + \frac{N \cdot KD \cdot KVCO}{C_1}}$$

by putting the characteristic equation (denominator) in the form of:  $s^{2} + 2s \zeta \omega n + \omega n$

we can solve for ωn and ζ to get:

$$\omega_{\text{n}}^{2} = \frac{N \cdot \text{KD} \cdot \text{KVCO}}{\text{C1}} \qquad \zeta = \frac{N \cdot \text{KD} \cdot \text{KVCO} \cdot \text{R}}{2\omega_{\text{n}}}$$

Now we can solve for R. C1 and C2:

$$C1 = \frac{N \cdot KD \cdot KVCO}{^{2}} \qquad R = \frac{2\zeta \omega n}{N \cdot KD \cdot KVCO} \qquad C_{2} = \frac{C_{1}}{10}$$

where:  $\omega n = loop$  bandwidth and,  $\zeta = loop$  damping factor

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

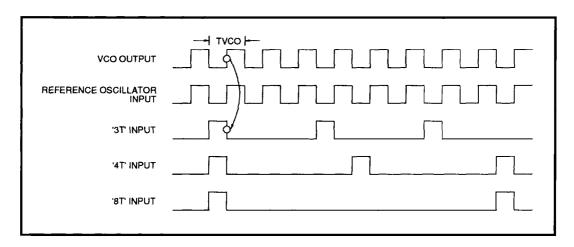

Because of the nature of Run Length Limited (RLL) codes, the Phase Detector will only be enabled during a data pulse. This technique allows the VCO to run at a center frequency with period, TVCO, equal to one encoded data bit cell time.

Figure 1 represents the relationship between the VCO output when locked to various Phase Detector input signals.

FIGURE 1: Relationship of VCO Output to Phase Detector Input

The average amplitude of the Phase Detector gain depends upon the Phase Detector input signal. When the PLL is locked to the reference oscillator, the Phase Detector is continuously enabled and the gain is at its maximum. When the PLL is tracking data and the input is an "8T" pattern, then the Phase Detector gain is at its minimum. The following indicates the value of "N" for various input conditions:

| N = 1.0   | for θin = reference oscillator                             |

|-----------|------------------------------------------------------------|

| N = 0.33  | for θin = 3T (100) preamble field (maximum data frequency) |

| N = 0.25  | for θin = 4T (1000) preamble field                         |

| N = 0.125 | for θin = 8T (minimum data frequency)                      |

Throughout this analysis the PLL has been considered as a continuous time system. In actuality the characteristics of the Phase Detector result in a sampled data system. By utilizing an integrating loop filter to average and smooth the Phase Detector charge pump output pulses, this analogy should be reasonable.

Determining an acceptable amount of phase error after locking to the preamble field depends upon the system requirements. In addition, it may be necessary to consider the effects of frequency steps in applications where motor speed control tolerances are significant. Generally, an acceptable amount of error is defined to be that amount which when added to all other timing error contributors, results in the data being within its timing window by the required margin.

In general, it is desirable to have the loop damping factor " $\zeta$ " between 0.5 and 1.0 during acquisition. For a high gain, second-order loop this results in minimal noise bandwidth.

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

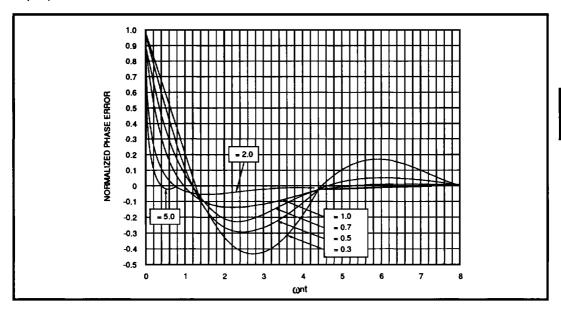

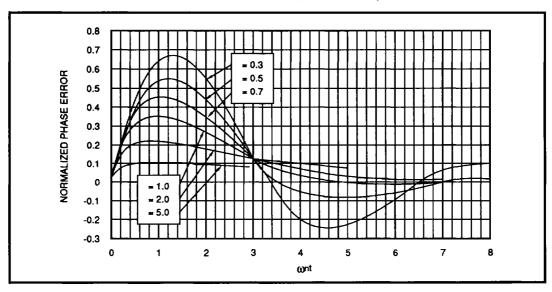

Figure 2 represents the phase error's response in time to a transient step in phase as a function of the loop bandwidth and damping factor. Figure 3 indicates the response of the VCO control voltage to compensate for this step in phase.

FIGURE 2: Transient Phase Error  $\theta e(t)$  Due To a Step In Phase  $\Delta \theta$

FIGURE 3: Transient Phase Error  $\theta e(t)$  Due to a Step in Frequency  $\Delta \omega$

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

#### APPLICATION OF THE SSI 32D5321/5322

#### 10 Mbit/s Soft Sector Example

For a data rate of 10 Mbit/s the SSI 32D5321/5322 requires a series resonant crystal of twice the data rate or 20 MHz. In the Soft Sector mode the PLL locking sequence allows the VCO to be within a determined amount of error after 38 x '3T' (100) bit groups. At 10Mbit/s each data bit cell time, TVCO, is equal to 50 ns. This results in:

$$tmax = (38) (3) (50 ns) = 5.7 \mu s$$

Therefore, the PLL has 5.7 µs to settle to within an acceptable amount of error before tracking and decoding data. Because the SSI 32D5321/22 employs a zero phase restart technique, the initial phase error is less than 8% TORC (0.5rad) or:

$\theta e < (0.08)(100 \text{ ns})$

θe < 8 ns

In general, it is desirable to have the loop damping factor " $\zeta$ " between 0.5 and 1.0 during acquisition. For a high gain, second-order loop this results in minimal noise bandwidth. For this example we will let  $\zeta = 0.7$ .

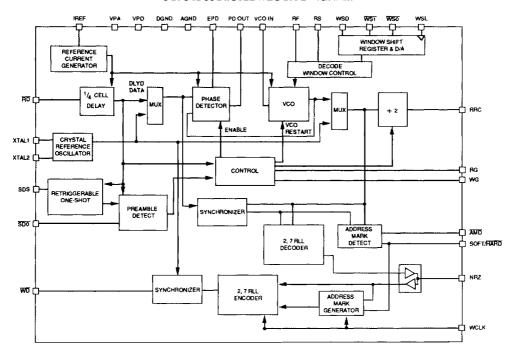

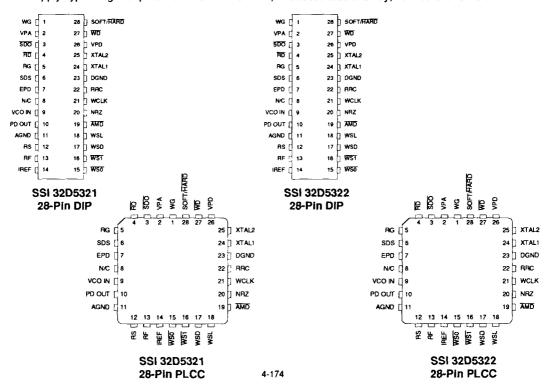

#### SSI 32D5321/5322 BLOCK DIAGRAM

4-172 0790

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

As shown in Figure 2, with  $\zeta = 0.7$ , our initial transient phase error will be at most 22% of its original value at ont = 2.3, 7.5% at ont = 4.0, etc. For this example we want the final phase error to be less than 1% of its original level. This results in a  $\omega$ nt between 5 and 6. To simplify the results, let  $\omega$ nt = 5.7.

Now,

$$\omega_{nt} = 5.7$$

and  $t_{max} = 5.7 \,\mu s$

$\therefore \omega_{nt} = 1.0 \cdot 10^6 \,\text{rad/s}$

with  $\zeta = 0.7$

Since we are evaluating the loop response during acquisition to the '3T' preamble, N = 0.33.

Now we have all the information required to calculate the loop filter component values.

#### For the SSI 32D5321:

the SSI 32D5321:

$$RR = \frac{40.67}{10 \text{ Mbs}} - 0.5 = 3.567 \text{ k}\Omega$$

$$\omega_{\text{n}} = 1.0 \cdot 10^6 \text{ rad/s}$$

$$\zeta = 0.7$$

$$KD(typ) = 0.309/(RR+500) = 7.6 \cdot 10^{-5} \text{ A/rad}$$

$$KVCO(typ) = 0.17\omega_{\text{o}} = 0.17(2\pi)/\text{To} = 2.14 \cdot 10^7 \text{ rad/s V}$$

$$N = 0.33$$

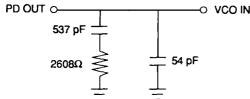

$$R = \frac{2 \zeta \omega n}{N \cdot KD \cdot KVCO} = 2608 \Omega$$

$$C_1 = \frac{N \cdot KD \cdot KVCO}{\omega n^2} = 537 \text{ pF}$$

$$C_2 = \frac{C_1}{10} = 54 \text{ pF}$$

RR =

$$\frac{43.86}{10 \text{ Mbs}}$$

- 1.2 = 3.186 kΩ

ωn = 1.0 • 10° rad/s

$\zeta$  = 0.7

KD(typ) = 0.309/(RR+500) = 8.38 • 10-5 A/rad

KVCO(typ) = 0.17ωo = 0.17(2π)/To = 2.14 • 10° rad/s V

$$N = 0.33$$

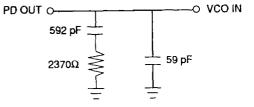

$$R = \frac{2\zeta \omega n}{N \cdot KD \cdot KVCO} = 2.37 \text{ k}\Omega$$

$$C_1 = \frac{N \cdot KD \cdot KVCO}{\omega n^2} = 592 \text{ pF}$$

$$C_2 = \frac{C_1}{10} = 59 \text{ pF}$$

This loop filter configuration and its component values should be considered a starting point. The final value of on depends upon the system requirements and can certainly be optimized for a specific application. In the table below, we have listed some suggested external component values for several common data rates.

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

#### 32D5321

| DATA RATE | DAMPING LOCK TIM | LOCK TIME |     | BANDWIDTH $\omega n \left(\frac{rad}{sec}\right)$ | EXTERNAL COMPONENT VALUES |        |        |       |                     |                     |

|-----------|------------------|-----------|-----|---------------------------------------------------|---------------------------|--------|--------|-------|---------------------|---------------------|

| (Mbit/s)  | FACTOR,ζ         | tmax (μs) | ωnt |                                                   | RR(KΩ)                    | Cd(pF) | Rd(KΩ) | R(ΚΩ) | C <sub>1 (pF)</sub> | C <sub>2 (pF)</sub> |

| 7.5       | 0.7              | 7.5       | 5.0 | 6.67 x 10 <sup>5</sup>                            | 4.92                      | 100    | 11.0   | 3.1   | 680                 | 68                  |

| 10.0      | 0.7              | 5.7       | 5.7 | 1.0 x 10 <sup>6</sup>                             | 3.57                      | 82     | 10.0   | 2.7   | 510                 | 51                  |

#### 32D5322

| DATA RATE | DAMPING LOCK | LOCK TIME |     | BANDWIDTH                                               | EXTERNAL COMPONENT VALUES |        |        |       |                     |                     |

|-----------|--------------|-----------|-----|---------------------------------------------------------|---------------------------|--------|--------|-------|---------------------|---------------------|

| (Mbit/s)  | FACTOR,ζ     | tmax (μs) | ωnt | $\omega n \left( \frac{\text{rad}}{\text{sec}} \right)$ | RR(KΩ)                    | Cd(pF) | Rd(KΩ) | R(KΩ) | C <sub>1 (pF)</sub> | C <sub>2 (pF)</sub> |

| 7.5       | 0.7          | 7.5       | 5.0 | 6.67 x 10 <sup>5</sup>                                  | 4.64                      | 100    | 13.0   | 2.94  | 710                 | 71                  |

| 10.0      | 0.7          | 5.7       | 5.7 | 1.0 x 10 <sup>6</sup>                                   | 3.19                      | 100    | 10.0   | 2.37  | 590                 | 59                  |

| 15.0      | 0.7          | 3.8       | 5.7 | 1.5 x 10 <sup>6</sup>                                   | 1.72                      | 100    | 6.49   | 1.43  | 654                 | 65                  |

#### LAYOUT CONSIDERATIONS

As with other high frequency analog devices the SSI 32D5321/22 requires care in layout. The designer should keep analog signal lines as short as possible and well balanced. Use of a ground plane is recommended, along with supply bypassing to separate the SSI 32D5321/22, and associated circuitry, from other circuits on the PCB.

0790

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

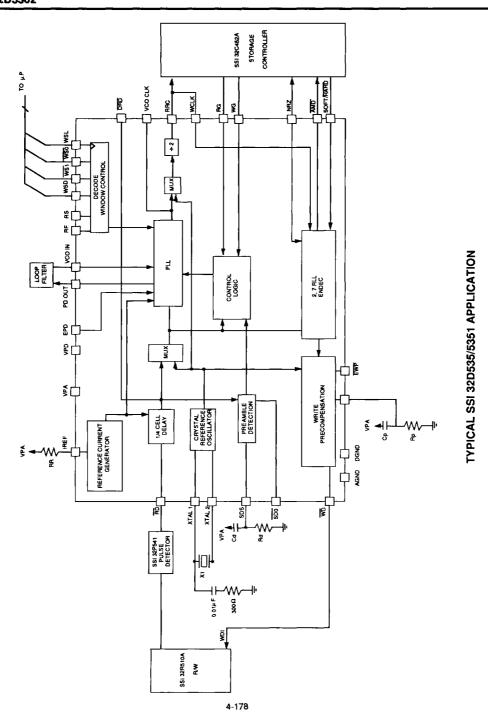

#### **APPLICATION OF THE SSI 32D535/5351**

#### 10 Mbit/s Soft Sector Example:

For a data rate of 10 Mbit/s the SSI 32D535/5351 requires a series resonant crystal of twice the data rate or, 20 MHz. In the Soft Sector mode the PLL locking sequence allows the VCO to be within a determined amount of error after 38 x '3T' (100) bit groups. At 10 Mbit/s each data bit cell time, TVCO, is equal to 50 ns. This results in:

$$tmax = (38)(3)(50 \text{ ns}) = 5.7 \,\mu\text{s}$$

Therefore, the PLL has 5.7 µs to settle to within an acceptable amount of error before tracking and decoding data. Because the SSI 32D535 employs a zero phase restart technique, the initial phase error is less than 8% TORC (0.5rad) or:

$$\theta_e < (0.08)(100 \text{ ns})$$

$\theta_e < 8 \text{ ns}$

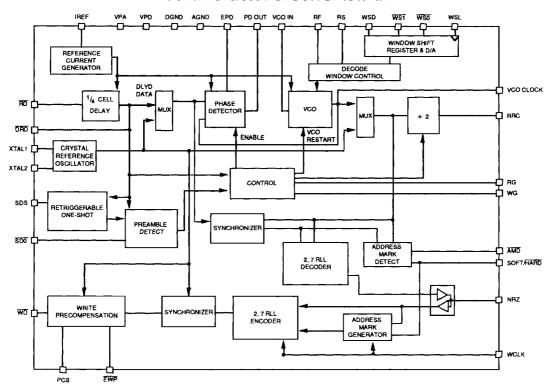

#### SSI 32D535/5351 BLOCK DIAGRAM

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

In general, it is desirable to have the loop damping factor " $\zeta$ " between 0.5 and 1.0 during acquisition. For a high gain, second-order loop this results in minimal noise bandwidth. For this example we will let  $\zeta = 0.7$ .

As shown in Figure 2, with  $\zeta=0.7$ , our initial transient phase error will be at most 22% of its original value at  $\omega_{nt}=2.3$ , 7.5% at  $\omega_{nt}=4.0$ , etc. For this example we want the final phase error to be less than 1% of its original level. This results in a  $\omega_{nt}$  between 5 and 6. To simplify the results, let  $\omega_{nt}=5.7$ .

This loop filter configuration and its component values should be considered a starting point. The final value of on depends upon the system requirements and can certainly be optimized for a specific application. In the table below, we have listed some suggested external component values for several common data rates.

Now,

$$\omega nt = 5.7$$

and

$$t_{max} = 5.7 \, \mu s$$

$$\therefore \omega n = 1.0 \cdot 10^6 \, rad/s$$

with

$$\zeta = 0.7$$

Since we are evaluating the loop response during acquisition to the '3T' preamble, N = 0.33.

Now we have all the information required to calculate the loop filter component values.

#### For the SSI 32D535:

RR =

$$\frac{40.67}{10 \text{MB}}$$

- 0.5 = 3.567 k $\Omega$

$\omega_{\text{n}}$  = 1.0 • 10<sup>6</sup> rad/s

$\zeta$  = 0.7

KD(typ) = 0.309/(RR+500) = 7.6 • 10<sup>-5</sup> A/rad

KVCO(typ) = 0.17 $\omega_{\text{n}}$  = 0.17(2 $\pi$ )/T0 = 2.14 • 10<sup>7</sup> rad/s V

N = 0.33

R =  $\frac{2\zeta\omega_{\text{n}}}{\text{N•KD•KVCO}}$  = 2608 $\Omega$

$$C_1 = \frac{\text{N} \cdot \text{KD} \cdot \text{KVCO}}{\omega \text{n}^2} = 537 \text{pF} \qquad C_2 = \frac{C_1}{10} = 54 \text{ pF} \qquad C_1 = \frac{\text{N} \cdot \text{KD} \cdot \text{KVCO}}{\omega \text{n}^2} 356 \text{pF} \qquad C_2 = \frac{C_1}{10} = 36 \text{pF}$$

$$PD \text{ OUT} \bigcirc \qquad \bigcirc \text{VCO IN} \qquad PD \text{ OUT} \bigcirc \qquad \bigcirc \text{VCO IN}$$

#### For the SSI 32D5351:

RR=

$$\frac{76}{DR}$$

- 1.75 = 5.85 k $\Omega$

$\omega_n$  = 1.0 • 10<sup>6</sup> rad/s

$\zeta$  = 0.7

KD(typ) = (0.34/RR+900) = 5.04 • 10<sup>-5</sup> A/rad

KVCO(typ) = 0.17 $\omega$ 0 = 0.17(2 $\pi$ )/T0 = 2.14 • 10<sup>7</sup> rad/s V

N = 0.33

$$R = \frac{2\zeta\omega_n}{N \cdot KD \cdot KVCO} = 3935\Omega$$

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

This loop filter configuration and its component values should be considered a starting point. The final value of ωn depends upon the system requirements and can certainly be optimized for a specific application. In the table below, we have listed some suggested external component values for several common data rates.

#### 32D535

| DATA RATE | DAMPING  | LOCK TIME |     | BANDWIDTH $\omega n \left(\frac{rad}{sec}\right)$ | EXTERNAL COMPONENT VALUES |        |               |       |          |          |

|-----------|----------|-----------|-----|---------------------------------------------------|---------------------------|--------|---------------|-------|----------|----------|

| (Mbit/s)  | FACTOR,ζ | tmax (μs) | ωnt |                                                   | RR(KΩ)                    | Cd(pF) | $Rd(K\Omega)$ | R(ΚΩ) | C 1 (pF) | C 2 (pF) |

| 7.5       | 0.7      | 7.5       | 5.0 | 6.67 x 10 <sup>5</sup>                            | 4.92                      | 100    | 11.0          | 3.0   | 687      | 69       |

| 10.0      | 0.7      | 5.7       | 5.7 | 1.0 x 10 <sup>6</sup>                             | 3.57                      | 82     | 10.0          | 2.7   | 510      | 51       |

#### 32D5351

| DATA RATE | DAMPING LOCK TIME |            |     | BANDWIDTH (rad)       | EXTERNAL COMPONENT VALUES |        |        |       |                     |                     |

|-----------|-------------------|------------|-----|-----------------------|---------------------------|--------|--------|-------|---------------------|---------------------|

| (Mbit/s)  | FACTOR,ζ          | t max (μs) | ωnt |                       | RR(KΩ)                    | Cd(pF) | Rd(KΩ) | Β(ΚΩ) | C <sub>1 (pF)</sub> | C <sub>2 (pF)</sub> |

| 10.0      | 0.7               | 5.7        | 5.7 | 1.0 x 10 <sup>6</sup> | 5.85                      | 100    | 10.0   | 3.94  | 356                 | 36                  |

| 15.0      | 0.7               | 3.8        | 5.7 | 1.5 x 10 <sup>6</sup> | 3.32                      | 100    | 6.49   | 2.46  | 379                 | 38                  |

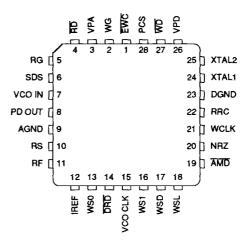

| <b>EWP</b> | 1  | 32 | SOFT/HARD |

|------------|----|----|-----------|

| WG         | 2  | 31 | PCS       |

| VPA        | 3  | 30 | ₹ WD      |

| SDO (      | 4  | 29 | ] VPD     |

| RD         | 5  | 28 | ] N/C     |

| RG         | 6  | 27 | XTAL2     |

| SDS        | 7  | 26 | ] XTAL1   |

| EPD        | 8  | 25 | DGND      |

| VCO IN     | 9  | 24 | RRC       |

| PD OUT     | 10 | 23 | WCLK      |

| AGND [     | 11 | 22 | NRZ       |

| RS         | 12 | 21 | AMD       |

| RF         | 13 | 20 | WSL       |

| IREF       | 14 | 19 | WSD       |

| WSO (      | 15 | 18 | WS1       |

| DRD        | 16 | 17 | VCO CLK   |

|            |    |    |           |

32 LEAD SOW, DIP

28 Pin PLCC

NOTE: Does not include the following pins which are available on the 32-Pin packages

- \$D0

- EPD

- SOFT/HARD (internally pulled up high)

st be used in soft sector applications only

So must be used in soft sector applications only.

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

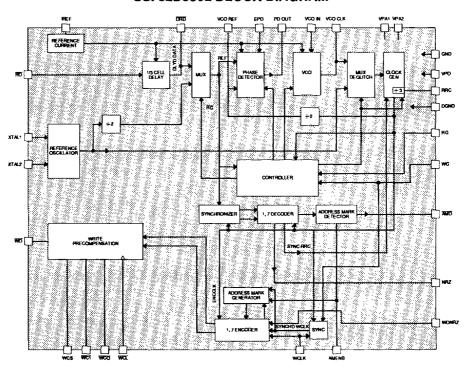

#### **APPLICATION OF THE SSI 32D5362**

#### 15 Mbit/s Soft Sector Example

For a data rate of 15 Mbit/s the SSI 32D5362 requires a serial resonant crystal of three times the data rate or 45 MHz. In the Soft Sector mode the PLL locking sequence allows the VCO to be within a determined amount of error after 16 x '3T' (100) bit groups. At 15Mbit/s each data bit cell time, TVCO, is equal to 44.4 ns. This results in:

$$tmax = (16) (3) (44.4 ns) = 2.1 \mu s$$

Therefore, the PLL has 2.1 µs to settle to within an acceptable amount of error before tracking and decoding data. Because the SSI 32D536 employs a zero phase restart technique, the initial phase error is less than 16% TORC (1.0rad) or:

$$\Delta \theta e < (0.16)(66.7 \text{ ns})$$

$\Delta \theta e < 10.7 \text{ ns}$

In general, it is desirable to have the loop damping factor " $\zeta$ " between 0.5 and 1.0 during acquisition. For a high gain, second-order loop this results in minimal noise bandwidth. For this example we will let  $\zeta \approx 0.7$ .

#### SSI 32D5362 BLOCK DIAGRAM

0790 4-179

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

As shown in Figure 2, with  $\zeta=0.7$ , our initial transient phase error will be at most 22% of its original value at  $\omega nt=2.3$ , 7.5% at  $\omega nt=4.0$ , etc. For this example we want the final phase error to be less than 15% of its original level. This results in a  $\omega nt$  between 3 and 4. To simplify the results, let  $\omega nt=3.2$ . This results in a maximum final phase error of 1.6 ns.

Now,

$$\omega_{n}t = 3.2$$

and

$$tmax = 2.1 \,\mu s$$

$$\therefore \omega_{n} = 1.5 \cdot 10^{6} \, rad/s$$

with

$$\zeta = 0.7$$

Since we are evaluating the loop response during acquisition to the '3T' preamble, N = 0.33.

Now we have all the information to calculate the loop filter component values.

RR =

$$3873\Omega$$

$\omega n = 1.5 \cdot 10^6 \text{ rad/s}$

$\zeta = 0.7$

KD(typ) =  $0.57/(RR+530) = 1.3 \cdot 10^4 \text{ A/rad}$

KVCO(typ) =  $\frac{0.20(2\pi)}{2\text{To}} = 2.83 \times 10^7$

N =  $0.33$

which results in:

This loop filter configuration and its component values should be considered a starting point. The final value of on depends on the system requirements and can certainly be optimized for a specific application. In the following table we have listed some suggested external component values for two common data rates:

| DATA RATE | DAMPING LOCK TIME |           |     | BANDWIDTH<br>(rad)                        | EXTERNAL COMPONENT VALUES |      |                     |                     |  |  |

|-----------|-------------------|-----------|-----|-------------------------------------------|---------------------------|------|---------------------|---------------------|--|--|

| (Mbit/s)  | FACTOR, ζ         | tmax (µs) | ωnt | $\omega n \left( \frac{rad}{sec} \right)$ | RR(kΩ)                    | R(Ω) | C <sub>1</sub> (pF) | C <sub>2</sub> (pF) |  |  |

| 10        | 0.7               | 3.2       | 3.2 | 1.0 x 10 <sup>6</sup>                     | 6.96                      | 2957 | 470                 | 47                  |  |  |

| 15        | 0.7               | 2.1       | 3.2 | 1.5 x 10 <sup>6</sup>                     | 3.87                      | 1729 | 540                 | 54                  |  |  |

4-180

0790

#### .

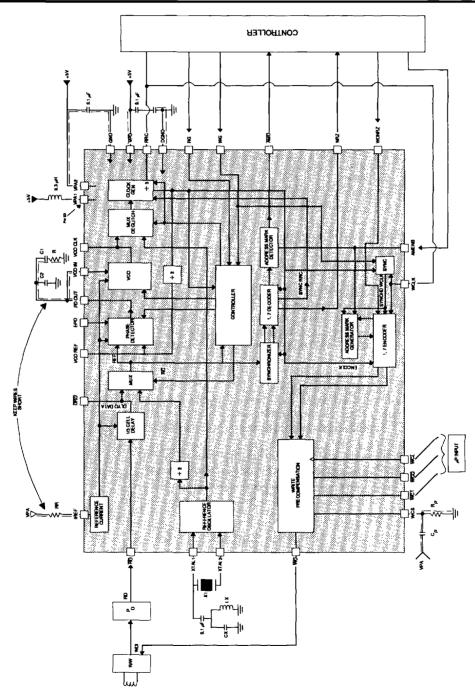

# FIGURE 5: Typical Application

# Data Synchronizer Family Application Notes

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

4-181

SSI 32D5321/5322 SSI 32D535/5351 SSI 32D5362

#### LAYOUT CONSIDERATIONS

As with other high frequency devices the SSI 32D5362 requires care in layout. The designer should keep analog signal lines as short as possible and well balanced. Use of a ground plane is recommended, along with supply bypassing to separate the SSI 32D5362 and associated circuitry, from other circuits on the PCB. It is also recommended that an inductor  $(0.3\,\mu\text{H})$  be placed in series with the analog supply which supports the VCO circuitry (VPA1, Pin 23). This additional filtering has been shown effective in eliminating VCO jitter, which can degrade window margin performance.

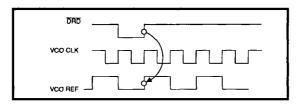

#### **TEST POINTS**

The SSI 32D5362 provides three (3) test points which can be utilized to evaluate window margin characteristics.

- (a) DRD, delayed read data the positive edges represent the data bit position

- (b) VCO REF, the VCO reference which represents the input to the Phase Detector, synchronizer, and 1,7 decoder

- (c) VCO CLK, the VCO clock output which represents the output of the VCO

The following figure describes the relationship between the various test points:

FIGURE 6: Test Point Relationships

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680, (714) 731-7110, FAX: (714) 731-5457