# 7200 Processing Unit

Reference Manual 2903.002

# **Preliminary Information**

This manual precedes initial release publications and therefore may undergo substantial revision.

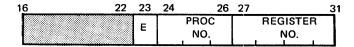

# Computer System Products

## **Preliminary Edition October 1972**

Requests for copies of Memorex publications should be made to your Memorex representative or to the Memorex branch office serving your locality.

$\frac{\partial f_{k+1}}{\partial t} = \frac{1}{|k|^{2}} \left( \frac{1}{|k|^{2}} + \frac{1}{|k|^{2}} \right) = \frac{1}{|k|^{2}} \left( \frac{1}{|k|^{2}} + \frac{1}{|k|^{2}} \right) = \frac{1}{|k|^{2}} \left( \frac{1}{|k|^{2}} + \frac{1}{|k|^{2}} + \frac{1}{|k|^{2}} \right)$

A readers' comments form is provided at the back of this publication. If the form has been removed, comments may be addressed to the Memorex Corporation, Publications Dept., Santa Clara, California 95052.

# 7200 PROCESSING UNIT REFERENCE (MRX/40 SYSTEM)

# **PREFACE**

This publication covers the 7200 Processing Unit (for MRX/40 data-processing systems). It describes the functional characteristics, data formats, operating routines, and the System Control Panel. Each machine instruction is detailed, with a brief example.

The publication is intended to aid programmers, system engineers, and data-processing managers and operators in better understanding and using the system.

Appendices provide further details of machine formats and instructions.

September, 1972

# **TABLE OF CONTENTS**

| Section |                                         | Page | Section                           | Page |

|---------|-----------------------------------------|------|-----------------------------------|------|

| 1       | GENERAL DESCRIPTION                     | 1-1  | Compare Instructions              | 4-3! |

|         |                                         |      | Control Instructions              | 4-4  |

|         | Introduction                            | 1-1  | Data Conversion Instructions      | 4-4: |

|         | Processor State Concept                 | 1-1  | Data Transfer Instructions        | 4-50 |

|         | General                                 | 1-1  | Shift Instructions                | 4-5  |

|         | Consecutive-Cycle Mode                  | 1-2  | Floating-Point Instructions       | 4-6  |

|         | Major-Cycle Timing                      | 1-2  | Data Format                       | 4-6  |

|         | Processing-Unit Organization            | 1-2  | Normalization                     | 4-6  |

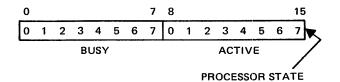

|         | Processor States                        | 1-2  | Zero Representation               | 4-63 |

|         | Processor State 0                       | 1-5  | Arithmetic Exceptions             | 4-63 |

|         | Processor State 2                       | 1-5  | Floating-Point Register           | 4-64 |

|         | Processor State 3                       | 1-6  | System Instructions               | 4-70 |

|         | Processor State 4                       | 1-6  | Extended File Register            | 4-70 |

|         | Processor States 5, 6, and 7            | 1-6  | Control Register (C)              | 4-7: |

|         | Main Storage                            | 1-6  | Privileged Mode Register (PM)     | 4-7  |

|         | Alterable Control Memory                | 1-6  | Boundary Crossing Register (BC)   | 4-7! |

|         | Arithmetic-Logical Unit                 | 1-6  | Register Option                   | 4-7  |

|         | Register File                           | 1-6  | Control Instructions              | 4-76 |

| 2       | FUNCTIONAL CHARACTERISTICS              | 2-1  | 5 SYSTEM OPERATING PROCEDURES     | 5-1  |

|         | Main Storage Addressing                 | 2-1  | Introduction                      | 5-1  |

|         | Binary Representation                   | 2-1  | Controls and Indicators           | 5-1  |

|         | Arithmetic                              | 2-1  | Operator Group                    | 5-1  |

|         | Single-Precision Addition               | 2-3  | Programmer Group                  | 5-4  |

|         | Single-Precision Subtraction            | 2-3  | Maintenance Group                 | 5-7  |

|         | Double-Precision                        | 2-3  | System Activity Display Group     | 5-7  |

|         | Information Formats                     | 2-3  | Communications Activity Group     | 5-8  |

|         |                                         |      | Operating Procedures              | 5-8  |

| 3       | INSTRUCTION TYPES                       | 3-1  | Modes of Operation                | 5-8  |

|         |                                         |      | Breakpoint Facility               | 5-9  |

|         | Generalized Instruction Formats         | 3-1  | Switching Power On and Off        | 5-9  |

|         | Addressing Modes                        | 3-2  | Loading Control Storage from Disc | 5-10 |

|         | Immediate Addressing                    | 3-2  | Power On Condition                | 5-10 |

|         | Direct Addressing                       | 3-2  | Reset/Load Condition              | 5-11 |

|         | Indirect Addressing                     | 3-3  | Loading Control Storage from      |      |

|         | Implementation                          | 3-3  | Card Reader                       | 5-11 |

|         | Indexing                                | 3-3  | Power On Condition                | 5-11 |

|         | -                                       |      | Reset/Load Condition              | 5-12 |

| 4       | MACHINE INSTRUCTIONS                    | 4-1  | Loading Main Storage from Disc    | 5-12 |

|         |                                         |      | Loading Main Storage from         |      |

|         | Introduction                            | 4-1  | Card Reader                       | 5-13 |

|         | Source and Object Format Interpretation | 4-1  | Reading Main Storage              | 5-13 |

|         | General-Purpose Instructions            | 4-4  | Preconditions                     | 5-13 |

|         | Arithmetic Instructions                 | 4-4  | Procedure                         | 5-13 |

|         | Bit-Oriented Instructions               | 4-18 | Writing Main Storage              | 5-13 |

|         | Boolean Logic Instructions              | 4-21 | Preconditions                     | 5-13 |

|         | Branching Instructions                  | 4-26 | Procedure                         | 5-14 |

## TABLE OF CONTENTS (Continued)

| Section                                           | Page         | Section                                       | Page        |

|---------------------------------------------------|--------------|-----------------------------------------------|-------------|

| Reading Registers of Register Files Preconditions | 5-14<br>5-14 | APPENDIX A - INSTRUCTION SUMMARY AND EXTENDED | <b>A</b> -1 |

| Procedure                                         | 5-14         | MNEMONIC CODES                                |             |

| Loading Registers of Register Files Preconditions | 5-14<br>5-14 |                                               |             |

| Procedure                                         | 5-15         | APPENDIX B — EBCDIC AND ASCII CODES           | B-1         |

| Reading Registers of Register Option              | 5-15         | APPENDIX B - EBCDIC AND AGOIT CODES           |             |

| Preconditions                                     | 5-15         |                                               |             |

| Procedure                                         | 5-1 <b>5</b> | A DITUMETIC                                   | C-1         |

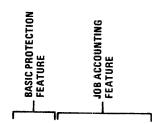

| Loading Registers of Register Option              | 5-16         | APPENDIX C - HEXADECIMAL ARITHMETIC           | <b>C</b> -1 |

| Preconditions                                     | 5-16         |                                               |             |

| Procedure                                         | 5-16         |                                               |             |

| Reading Shared Resources Registers                | 5-16         | APPENDIX D — MACHINE LANGUAGE                 | D-          |

| Preconditions                                     | 5-16         | INSTRUCTION TIMING                            |             |

| Procedure                                         | 5-16         | FORMULAS                                      |             |

| Executing Programs                                | 5-16         |                                               |             |

| Precondition                                      | 5-16         |                                               |             |

| Procedure                                         | 5-16         |                                               |             |

# LIST OF FIGURES

| Figure |                                                 | Page |

|--------|-------------------------------------------------|------|

| 1-1    | 7200 Processing Unit Architecture               | 1-3  |

| 1-2    | 7200 Processing Unit Block Diagram              | 1-4  |

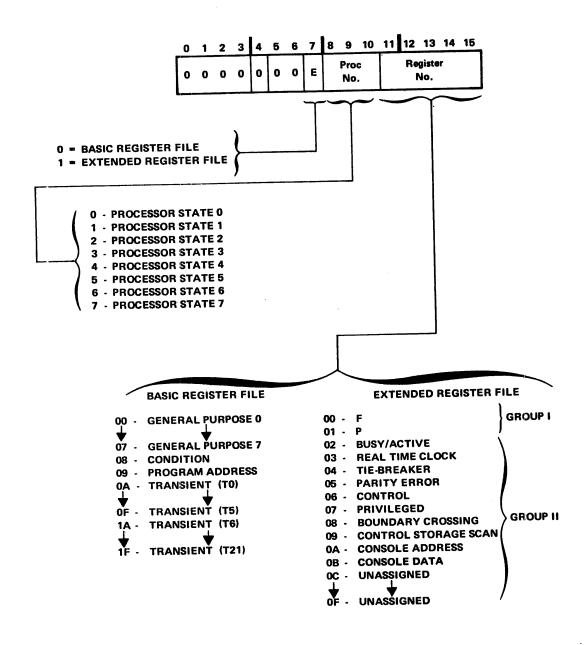

| 1-3    | Register File Layout                            | 1-8  |

| 1-4    | Condition Register Assignments                  | 1-8  |

| 2-1    | Single-Precision Fixed-Point Format             | 2-3  |

| 2-2    | Double-Precision Fixed-Point Format             | 2-4  |

| 3-1    | Register-to-Register Instruction Addressing     | 3-4  |

| 3-2    | Immediate-Register Instruction Addressing       | 3-5  |

| 3-3    | Memory-to-Register Instruction Addressing       | 3-6  |

| 3-4    | Direct-Register Instruction Addressing          | 3-6  |

| 3-5    | Memory-to-Memory Instruction Addressing         | 3-7  |

| 3-6    | Pre-Indexing with BCH Instruction               | 3-8  |

| 3-7    | Post-Indexing with B Instruction                | 3-8  |

| 3-8    | Memory-to-Memory Instruction with Post-Indexing | 3-9  |

## LIST OF FIGURES (Continued)

| Figure |                                                             | Page |

|--------|-------------------------------------------------------------|------|

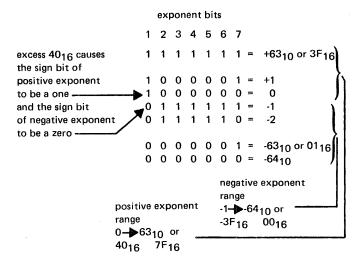

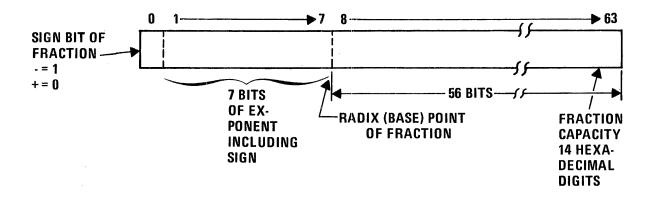

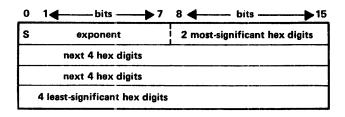

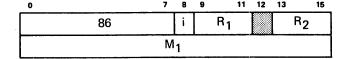

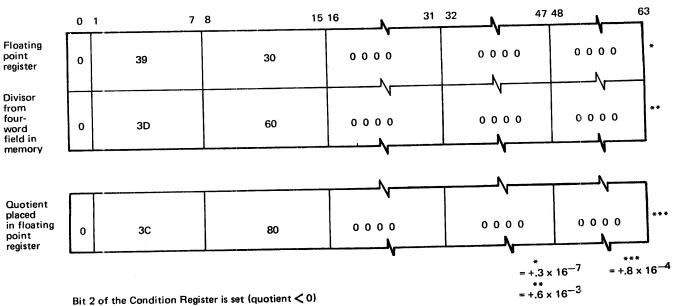

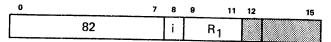

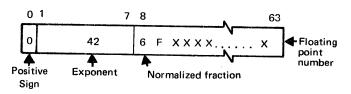

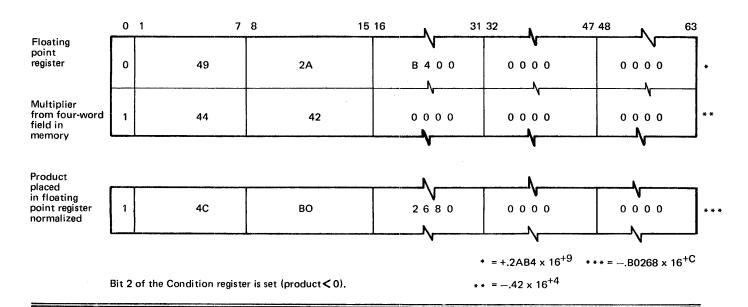

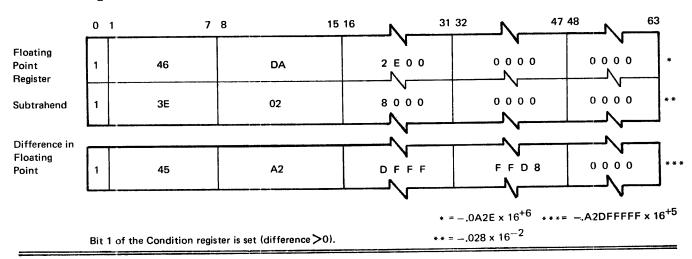

| 4-1    | Floating-Point Data Format                                  | 4-63 |

| 4-2    | Floating-Point Register Format                              | 4-64 |

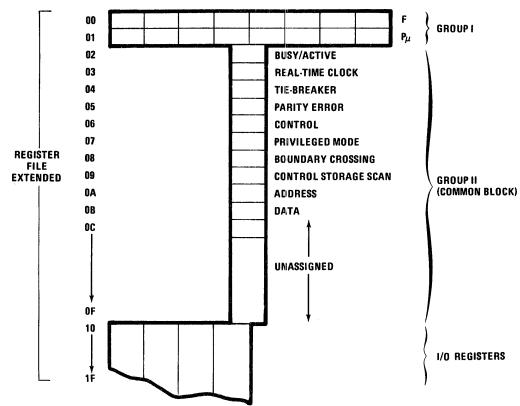

| 4-3    | Extended Register File Structure                            | 4-71 |

| 4-4    | Register Option Address Structure                           | 4-76 |

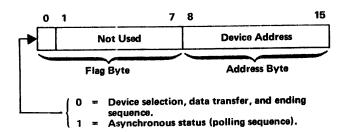

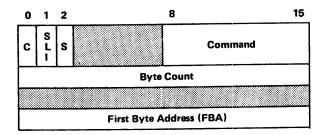

| 4-5    | INP Instruction in Basic Data Channel Operation             | 4-85 |

| 4-6    | OUT Instruction in Basic Data Channel Operation             | 4-85 |

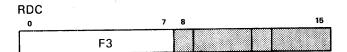

| 4-7    | Relationship, Line Parameter Table and Line Exit Jump Table | 4-87 |

| 5-1    | MRX/40 and 50 System Control Panel                          | 5-2  |

| 5-2    | Register File Address Format                                | 5-15 |

| 5-3    | Register File and Associated Register Addresses             | 5-18 |

| 5-4    | Format: Registers of Register Option                        | 5-19 |

| 5-5    | Addresses: Registers of Register Option                     | 5-19 |

# LIST OF TABLES

| Table |                        | Pag |

|-------|------------------------|-----|

| 2-1   | EBCDIC Character Codes | 2-5 |

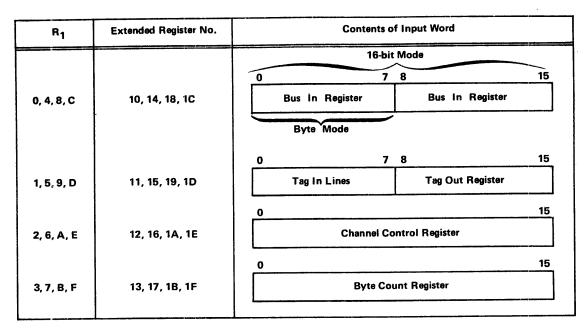

| 4-1   | Extended Register File | 4.7 |

## 1. GENERAL DESCRIPTION

#### INTRODUCTION

The MEMOREX 7200 Processing Unit is the major component in an I/O-oriented, business data-processing system. Its basic repertoire of 159 instructions provides a powerful facility for both business data-processing and scientific problem-solving.

The 7200 is a byte (8 bit)-oriented processing unit. In addition to single-precision operations in bytes and words (16 bits), the basic instruction set accommodates problems requiring double-precision (32-bit) solutions. An optional set of ten floating-point instructions is available to extend the scientific capabilities of the system.

A wide range of storage sizes, peripheral devices, and integrated adapters affords maximum flexibility in tailoring a system to meet a user's specific need. MRX/40 is supported by an unusually comprehensive operating system developed by Memorex. This extensive programming systems support permits the user to concentrate on his application, rather than on the functions of the system. The combination of hardware and software capability provides a price/performance level normally associated with more costly data processing systems. The result is a more efficient and economical data-processing system for the user.

Several characteristics distinguish the MRX/40 computer systems:

- Advanced architecture

- Wide range of peripheral devices

- Extensive communications support

- Comprehensive programming systems support

#### PROCESSOR STATE CONCEPT

#### **GENERAL**

Data processing systems divide their time between input/output operations and arithmetic/logical functions. This conflict of interest usually causes large periods of system time to be dominated by input/output functions. Obviously, while this domination exists, hardware such as that dedicated to arithmetic/logical functions stands idle. This results in uneconomical time-versus-hardware usage.

To avoid this uneconomical usage, the 7200 Processing Unit divides its running time into segments called *major cycles*. These time segments are cyclically assigned to one of eight *processor states*. For each state, a group of hardware registers holds information relating to the operation currently being performed by that state. A processor state and its associated group of registers, then, constitute a resource that is "dedicated" to the solution of a particular problem. In order to effect this solution, each processor state shares with the other states the use of the common (or "shared") resources of the computer.

Because only one processor state is active for a given time segment, the shared resources (principally, the arithmetic/logical unit and main storage) need concentrate on but one task during each major cycle.

By assigning specific types of tasks to individual processor states, as well as by allocating major cycles sequentially to each state that is waiting to execute the next segment of its task, and finally by never granting a processor state two consecutive major cycles if another state is awaiting its turn, the processing unit ensures that the system will not be bound up by either computation or input-output activities.

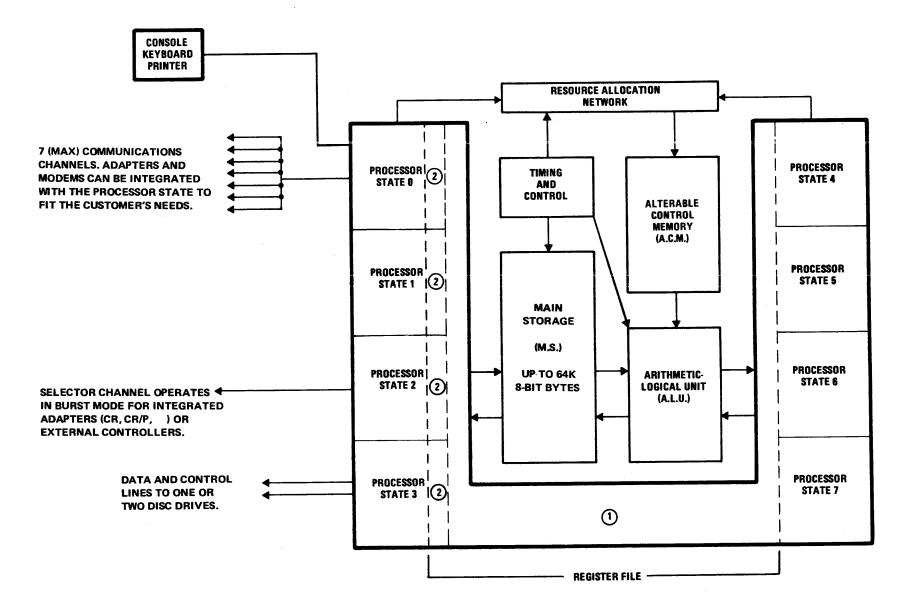

Figure 1-1 shows the arrangement of the dedicated resources with respect to major-cycle assignments. If all processor states have tasks to do, the first major cycle is given to state 0, the second to state 1, and so on. When processor state 7 has had its turn (using major cycle 8), the scanning sequence begins again: cycle 9 is assigned to state 0, cycle 10 to state 1, and so on. If processor state 1 had no task to perform, state 2 would receive cycle 2, with state 7 receiving cycle 7. Then, during the second scan, state 2 would receive cycle 9.

In each scan, the I/O processor states are given precedence. This is because those states communicate with peripheral equipment, and normally handle that communication on a "can't wait" basis. Processor states that do not operate under such time constraints are assigned lower-order positions in the scanning sequence.

A software-controlled priority mode is provided for those instances when an I/O processor state can't wait for its normal turn in the sequence. If that situation occurs, the Resource Allocation Network — which assigns the major cycles — grants the I/O processor state an out-of-sequence major cycle. This decision is made at the end of each major cycle; the action is similar to that of a system operating under a priority-interrupt scheme. It is this tailoring of the Resource Allocation Network around the I/O requirements that makes the MRX/40 system so well suited for file management and data inquiry-retrieval applications.

#### **CONSECUTIVE-CYCLE MODE**

As implied earlier, the major cycles are equitably distributed among the processor states requesting access to shared resources. To prevent a monopoly of the shared resources, the Resource Allocation Network does not normally give two successive major cycles to the same processor states.

For those relatively infrequent cases where only one processor state is requesting access, the Resource Allocation Network may be directed to give that state consecutive cycles. This is accomplished through a bit in the Control register.

Specific information for setting up the consecutive-cycle mode is given under the discussion of the Control register in Section 4.

The Job Accounting option keeps track of the number of major cycles the Resource Allocation Network grants to each of the processor states.

#### MAJOR-CYCLE TIMING

Every major cycle consists of a number of 200-nanosecond "minor cycles", during which time individual micro instructions ( $\mu$ I's) are executed. References to main storage are also made during the major cycle.

The length of each major cycle — and consequently the number of minor cycles contained within it — depends upon whether or not a main storage reference is made. The resultant variations in major-cycle length are shown below.

| Function                                                    | Minor<br>Cycles | Length<br>(Micro-<br>seconds) |

|-------------------------------------------------------------|-----------------|-------------------------------|

| Execute instructions                                        | 8               | 1.6                           |

| Read or write<br>Main Storage;<br>execute instruc-<br>tions | 9               | 1.8                           |

#### PROCESSING-UNIT ORGANIZATION

A simplified block diagram of the 7200 Processing Unit is shown in Figure 1-2. The processor states gain access to the shared resources via the Resource Allocation Network, the function of which was implied earlier. Descriptions of other elements in the diagram follow. Information for the systems programmer about the inter-relationships of these components is contained in Section 4 of this manual.

#### **PROCESSOR STATES**

All eight processor states have equal capacity to perform logical, arithmetic, and bit-manipulative operations. Moreover, processor states 0 through 4 utilize special hardware that enable them to accomplish specific tasks. Because of this specificity, it is convenient to assign a name to each processor state according to its prime dedicated task:

- Processor State 0: Communications

- Processor State 1: Not assigned

- Processor State 2: Selector Channel

| Integrated<br>Adapters<br>Extended<br>Registers | IXA  ON SOLUTIONS  COMMUNICATIONS | BASIC DATA<br>CHANNEL | CARD RDR  CARD R/P  TA  CHANNEL  OPTION  CHANNEL  OPTION | INTEGRATED FILE ADAPTER  DIRECT ACCESS STORAGE | A<br>COMM<br>I/O<br>IXA<br>ns<br>RDR<br>R/P | BBREVIATIONS  = Communic = Input/Outp = Console Ad = Nanosecone = Reader = Reader | ut<br>lapter<br>d                          |                      |

|-------------------------------------------------|-----------------------------------|-----------------------|----------------------------------------------------------|------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------|----------------------|

|                                                 |                                   |                       |                                                          | OPERATIN                                       | G SYSTEM                                    |                                                                                   |                                            |                      |

| Main<br>Storage                                 | COMMUNICATIONS<br>1/0<br>Routines |                       | UNIT RECORD AND MAGNETIC TAPE 1/0 ROUTINES               | DISC<br>I/O<br>ROUTINES                        | CONTROL<br>PROGRAM                          |                                                                                   | USER<br>OGRA<br>AND<br>RANSIENT OPERATIONS | NG                   |

| Registers                                       | GENERAL<br>REGISTERS              | GENERAL<br>REGISTERS  | GENERAL<br>REGISTERS                                     | GENERAL<br>REGISTERS                           | GENERAL<br>REGISTERS                        | GENERAL<br>REGISTERS                                                              | GENERAL<br>REGISTERS                       | GENERAL<br>REGISTERS |

| Major Cycle 1  Major Cycle 2                    | PROCESSOR<br>STATE 0              | PROCESSOR<br>STATE 1  | PROCESSOR                                                |                                                |                                             |                                                                                   |                                            |                      |

| Major Cycle 3  Major Cycle 4                    |                                   |                       | STATE 2                                                  | PROCESSOR<br>STATE 3                           |                                             |                                                                                   | -                                          |                      |

| Major Cycle 5  Major Cycle 6                    |                                   |                       |                                                          |                                                | PROCESSOR<br>STATE 4                        | PROCESSOR<br>STATE 5                                                              |                                            |                      |

| Major Cycle 7                                   |                                   |                       |                                                          |                                                |                                             |                                                                                   | PROCESSOR<br>STATE 6                       | PROCESSOR<br>STATE 7 |

| Major Cycle 8                                   |                                   |                       |                                                          |                                                |                                             | <del></del>                                                                       |                                            | JIAIL /              |

- (1)80 REGISTERS SHARED BY ALL EIGHT PROCESSOR STATES, 10 PER STATE:

- EIGHT GENERAL-PURPOSE REGISTERS

- ONE CONDITION REGISTER

- ONE PROGRAM ADDRESS REGISTER

- (2) SPECIAL INTERNAL REGISTERS FOR IMPLEMENTING I/O FUNCTIONS

Processor State 3: Disc

Processor State 4: Executive

• Processor States 5, 6, 7: General Purpose

#### **Processor State 0**

This processor state contains an integrated communications adapter (ICA) to provide serial data communication over as many as 7 communications lines for both synchronous and asynchronous terminals utilizing switched networks and dedicated or local lines. An integrated console adapter, for service to the console keyboard/printer, is also attached to Processor State 0.

Each communications line is controlled by a line adapter that is field-modifiable through interchangeable printed-circuit boards to accommodate a wide variety of customer applications.

The ICA can communicate with local or remote devices operating with seven-level-plus-parity or eight-level codes in the following speeds.

| Asynch                           | ronous                      | Synchronous                                                 |                                                      |

|----------------------------------|-----------------------------|-------------------------------------------------------------|------------------------------------------------------|

| Baud<br>(bits/sec)               | Characters/<br>sec          | Baud<br>(bits/sec)                                          | Characters/<br>sec                                   |

| 110<br>150<br>300<br>600<br>1200 | 10<br>15<br>30<br>60<br>120 | 600<br>1200<br>1800<br>2000<br>2400<br>3600<br>4800<br>9600 | 75<br>150<br>225<br>250<br>300<br>450<br>800<br>1200 |

Three methods of operation are provided:

- 1. Operating a local terminal over lines up to 50 feet in length (no modem required).

- 2. Communicating, via a common-carrier-provided data set or customer-provided modem, with a remote terminal using a compatible modem.

- Communicating, via an internal modem and a common-carrier-provided data access arrangement, with a remote terminal using a compatible modem.

The asynchronous line adapters are full-duplex, permitting two-way simultaneous operation. In addition, when an adapter is supplemented by a suitable modem, a split-speed provision permits operating the primary channel at 1200 baud and the secondary channel at 150 baud. This mode allows either channel to be transmitting while the other channel receives. Echoplex is also supported; in this mode, the received message is transmitted back to the sending station, allowing the sending terminal to monitor the performance of the transmission line.

These line adapters feature the ability, under program control, to determine the speed of a remote terminal, to select a speed, to automatically answer, or to indicate a lost-data condition. Information may be coded in seven levels plus programmable parity, or in eight levels.

The asynchronous line adapters provide a subset of EIA standard RS-232-C interface (Data Transmission Configuration Interface Type L).

The synchronous line adapters are half duplex. However, when connected to a full-duplex facility, they permit two-way alternate message transfer without line turn around delay. Synchronous communications are provided for Basic or Code Transparent EBCDIC or ASCII.

The synchronous line adapters provide a subset of EIA standard RS-232-C interface (Data Transmission Configuration Interface Type D).

#### **Processor State 2**

This processor state controls data transfers to and from peripheral devices using integrated adapters, or to and from external controllers via the selector channel feature. An integrated card reader adapter (IRCA) provides control for a 1000-, 600-, or 300-card-per-minute reader; an integrated reader/punch adapter (IRPA) provides control for a 500/120 card-per-minute reader/punch.

In addition to the adapters, Processor State 2 can handle up to seven IBM\* 360/370-compatible external controllers via the selector channel option. Parity is generated and checked for all transmissions to or from the external controllers.

Processor State 2 is capable of various modes of data transfer under control of different I/O Driver programs. It also can handle active devices in a controlled order of priority, as well as performing diagnostic testing operations.

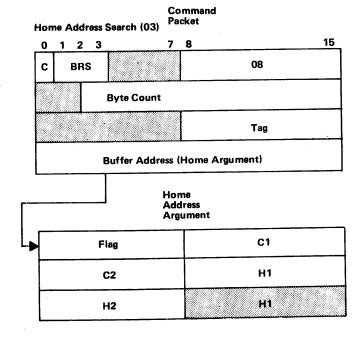

#### **Processor State 3**

This processor state contains an integrated file adapter (IFA) with direct interface to the disc drives. It controls communication between main storage and one or two MEMOREX 3664 Disc Drives.

The IFA decodes commands to initiate these drive functions:

- Positioning read/write heads to a specific location on the disc surface (seek) and selecting a read/write head

- Locating a particular record or part of a record on the disc surface (search)

- Writing a record or part of a record

- Reading a record or part of a record

Seek operations may be performed concurrently. All other operations are non-concurrent and may be performed only on a selected drive.

Each record appears in fields of information separated by gaps. The disc processor can write count and data fields and read count, key and data fields. Command chaining is permitted; however, any attempt to read, write or search across a track boundary will result in an error condition. \*Tradename — International Business Machines

#### **Processor State 4**

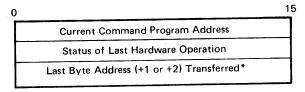

This processor state is used by the operating system to monitor and control system operations. Unique functions performed by the operating system in this state are as follows:

- 1. Assigning the execution of programs to other processor states.

- 2. Assigning I/O operations within those programs to the cognizant I/O processor state.

- 3. Supplying time-of-day information when requested by the various programs.

- 4. Periodically reading the interval timer, and updating the time-of-day clock accordingly.

- 5. Initiating error-isolation and error-correction routines when needed.

Items 2 and 3 are effected in response to the Service Request, a processing-unit instruction issued by the

general-purpose processor state requesting the information. (Certain instructions, including all of those directly relating to I/O, are "restricted", and cannot be executed by the general-purpose states.)

#### Processor States 5, 6, and 7

These are general-purpose processor states which may be assigned to execute user programs. Assigning one of these to a user program dedicates eight general-purpose registers, a condition register, and a program address register for exclusive use of that program. The assigning of general-purpose processor states to user programs is a function of the system's control program.

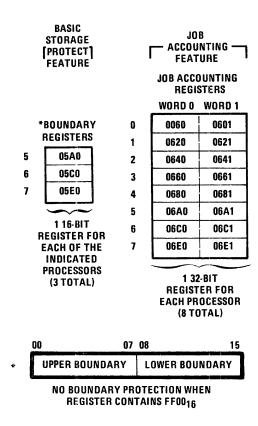

#### **MAIN STORAGE**

The 7200 Processing Unit provides byte addressability for up to 64K bytes of main storage (MS). Boundary protection during write references to storage is inherent for processor states 5, 6, and 7. Minimum storage size offered is 16K bytes.

#### **ALTERABLE CONTROL MEMORY**

The word-addressable ACM stores micro-instructions. There are 65 micro-instructions, used to form microprograms that implement execution of the processing unit instructions, control integrated I/O adapters, and control of certain special operations such as data entry or read-out from the System Control Panel.

#### ARITHMETIC-LOGICAL UNIT

Mathematical computations, Boolean functions (masking, for example), and data-shifting operations are handled by the ALU. Shifts of up to 15 binary positions may be made in a single pass through the 32-bit shift network. The existing ALU hardware readily accommodates double-precision and floating-point operations.

#### **REGISTER FILE**

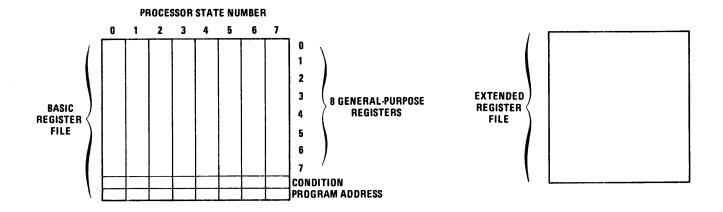

All the registers associated with the various processor states are called, collectively, the register file.

The purpose of the register file is to hold information

pertinent to the operations currently being executed by the processor states. As mentioned earlier, the performance of a task by one processor state — executing a user application program, for example, or transferring 100 words to a disc — involves many brief periods of activity, each separated by wider spaces of dormancy during which other states are active. During each active period, the less time spent obtaining the operands, the better. The register file offers just such a means of rapid retrieval. Its access time is roughly one-seventh that of main storage.

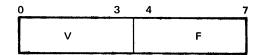

The register file is divided into two functional areas, as shown in Figure 1-3. The first comprises the basic registers, of which each processor state has a set. The Basic register file is associated with the execution of processor state programs; its component parts are as follows:

- General Registers used as the programmer desires: as index, base, transient, or working registers. (Exception: zero cannot be used as an index register; specifying it as an index modifier indicates no indexing.)

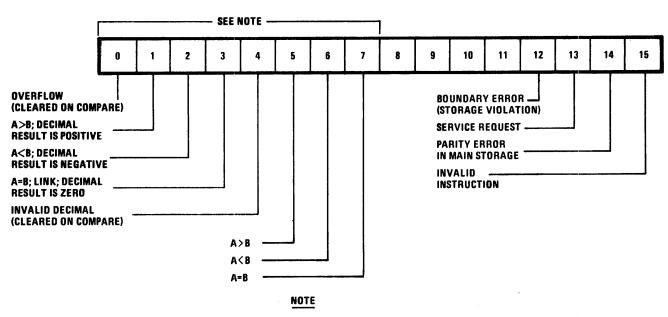

- Condition Register records conditions resulting from instruction execution (results equal, for example). The specific conditions are detailed below.

- Program Address Register contains the address of the instruction currently being executed by the associated processor state.

All registers in the Basic register file are addressable. A processor state may have access to any register within its own set (represented by the columns under the processor number in Figure 1-3) through use of the general-purpose machine-language instructions.

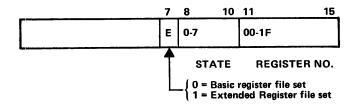

The Extended register file contains the I/O-related registers, the common block registers, and internal control registers which are used in conjunction with special-purpose functions, such as I/O data transfer and operating system control. The Extended registers have limited addressability. Some are addressable only by privileged instructions, and others only by restricted instructions.

A complete description of the Extended registers — their usage and functions — is in Section 4 under the heading System Instructions.

The Condition register records conditions resulting from the execution of both the basic instruction repertoire and the optional floating-point instructions. Twelve bits within the register record the resulting conditions. Figure 1-4 shows the conditions recorded for the basic instructions and their positions within the register.

- Bit 0 This bit position set indicates that arithmetic overflow occurred during an add, subtract or divide instruction. Being set during a Zero and Add, Add Packed Decimal or Subtract Packed Decimal instruction, it indicates that significant data within the field was lost. This bit position is always cleared following a Compare instruction.

- Bit 1 This bit position set following a Compare instruction indicates that the first operand R1 is greater than the second operand R2, as explained by the note in Figure 1-4. This position is also set for decimal arithmetic instructions when the result is positive.

- Bit 2 This bit position set following a Compare instruction indicates that the first operand R1 is less than the second operand R2 (note in Figure 1-4). This position is also set for decimal arithmetic instructions when the result is negative.

- Bit 3 This bit position set following a Compare instruction indicates that the two operands tested are identical. For decimal arithmetic instructions, it indicates that the result is zero. This position is also set for the non-decimal arithmetic instructions when a carry-out from adder bit position 0 occurs (link condition).

- Bit 4 This bit position is set during a packed decimal instruction if an EBCDIC character other than 0-9 is found in the unpacked field, or if a hex representation other than a letter A through F is found in the sign portion of the lowest-order byte. This position is always cleared following a Compare instruction.

- Bit 5 This bit position set following a Compare instruction indicates that the first operand R1 is greater than the second operand R2 (note on Figure 1-4).

- Bit 6 This bit position set following a Compare instruction indicates that the first operand R1 is less than the second operand R2 (note on Figure 1-4).

- Bit 7 This bit position set following a Compare instruction indicates that the two operands tested are identical.

Figure 1-3. Register File Layout

BIT GROUPS 0-3 AND 4-7 ARE BOTH SET AFTER ANY OF THE COMPARE INSTRUCTIONS. INTERPRETATION, WHETHER LOGICAL (MAGNITUDE ONLY) OR ARITHMETIC (SIGNED VALUES), DEPENDS UPON THE INSTRUCTION, AS FOLLOWS:

| INSTRUCTION                             | PURPOSE                                               | 0-3        | 4-7        |

|-----------------------------------------|-------------------------------------------------------|------------|------------|

| CMPX ) CBY CBYM )                       | MAGNITUDE ONLY,<br>BYTE-ORIENTED                      | LOGICAL    | LOGICAL    |

| CMPK<br>CMPF                            | ARITHMETIC, PACKED DECIMAL ARITHMETIC, FLOATING POINT | ARITHMETIC | ARITHMETIC |

| CMP, CMPD, CMPI, CMPI, CMPM, CMPT, CMPT | ARITHMETIC, WORD-ORIENTED                             | ARITHMETIC | LOGICAL    |

Figure 1-4. Condition Register Assignments

- Bits 8-11 Reserved

- Bit 12 This bit position is set when a processor attempts to read from or write into main storage beyond its boundary limits invoked at the time.

- Bit 13 This bit position is set during the execution of a Service Request instruction.

- Bit 14 This bit position is set whenever a parity error is detected on a word (instruction or operand) read from main storage.

- Bit 15 This bit position is set when an undefined operation code is translated, or when an unprivileged processor attempts to execute a restricted or privileged instruction, or when a privileged processor attempts to execute an instruction that is restricted to another processor.\*

Generally, the hardware writes into the Condition register in 4-bit hexadecimal groups. For example, if the result of a decimal arithmetic operation were positive, bit positions 1 and 5 would be set and positions 0, 2-4, 6 and 7 would be cleared. Bit positions 8-15 would be unchanged. On the other hand, for a *Compare* instruction that resulted in arithmetic and logical equality, 0-2 and 4-6 would be cleared, while 3 and 7 would be set. Bit positions 8-15 would be unchanged.

It is important to note that in the second instance, bit position 1 is cleared and no longer represents the result of the decimal arithmetic operation. This means that the Condition register must be examined before another instruction that can affect it is executed, or the prior condition indication will be lost.

In the *Instruction Descriptions*, Section 4, any instruction that affects the Condition register will stipulate which bits are affected. It assumes, then, that other bits are unchanged.

<sup>\*</sup>The terms "privileged" and "restricted" are defined in Section 4.

## 2. FUNCTIONAL CHARACTERISTICS

#### MAIN STORAGE ADDRESSING

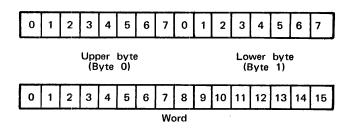

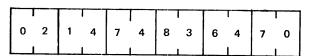

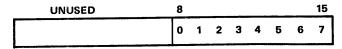

The MEMOREX processing unit is a 16-bit, fixed-point, machine. The basic memory unit is an 8-bit byte; two bytes are contained in each 16-bit main storage word. The word and byte relationship, with their respective bit positions, is shown below.

For instructions, addressing must always be by words; however, the instructions themselves may deal with word-length (16-bit) or byte-length (8-bit) operands.

Though instructions vary in length, they must begin at a word address in main storage. The lowest-order bit of word addresses are not used; thus, all word addresses are even.

Byte-length operands may be in either byte of a storage word. Therefore, in byte-oriented instructions the lowest-order bit of the address is used to select the byte; the upper byte with an even address and the lower byte with an odd address.

#### **BINARY REPRESENTATION**

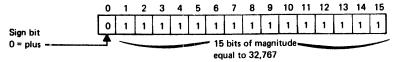

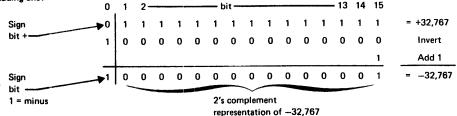

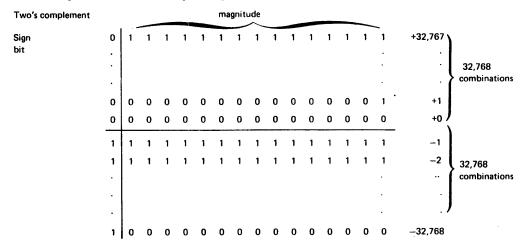

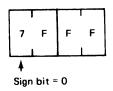

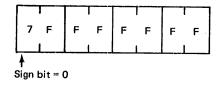

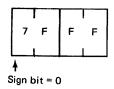

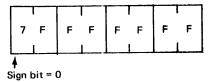

The arithmetic operands within the 7200 are either 16 or 32 bits represented in conventional signed binary notation. The highest-order bit specifies the sign, while the remaining bits specify the value of the operand. Positive operands are represented in true binary form with a 0 in the sign-bit position. Negative operands are represented in the two's complement form with a 1 in the sign bit.

#### **ARITHMETIC**

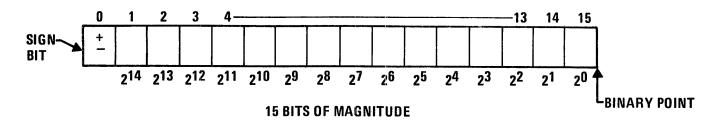

The 7200 performs both single-precision (16-bit) and clouble-precision (32-bit) addition and subtraction. The single-precision, fixed-point data format contains a 15-bit integer value and a sign bit (Figure 2-1).

The largest positive number that can be expressed in a signed 16-bit word either in storage or in a register is +32,767:

The two's complement representation for negative numbers is formed by inverting the positive binary representation and adding one:

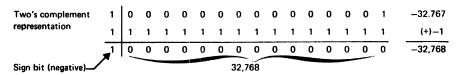

This -32,767 value, is however, one less in absolute value than the largest negative number that can be expressed in a signed 16-bit word. The largest negative number is formed by adding (-1) to -32,767.

Although the same quantity of both positive and negative numbers can be represented in a signed 16-bit machine, the two's complement usage causes the positive and negative range of numbers to be offset by one number:

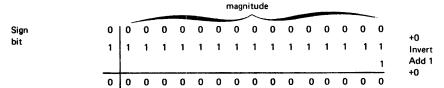

As a result of the offset there is one positive and one negative number which cannot be represented in its opposite form. The value zero can only be expressed as a positive number, which is apparent when we attempt to generate the two's complement representation for positive zero.

The same is true with negative 32,768, which can only be expressed as a negative value in single-precision notation.

|             |   |   |   |   |   |   |   | magı | nitud  | le |   |   |   |   |   |   |                 |

|-------------|---|---|---|---|---|---|---|------|--------|----|---|---|---|---|---|---|-----------------|

|             |   | _ |   |   | - | _ |   |      | $\sim$ |    |   |   |   |   |   | _ |                 |

| Sign<br>bit | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0      | 0  | 0 | 0 | 0 | 0 | 0 | 0 | <b>-32,768</b>  |

| bit         | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1    | 1      | 1  | 1 | 1 | 1 | 1 | 1 | 1 | Invert<br>Add 1 |

|             | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0      | 0  | 0 | 0 | 0 | 0 | 0 | 0 | -32,768         |

Figure 2-1. Single-Precision Fixed-Point Format

#### SINGLE-PRECISION ADDITION

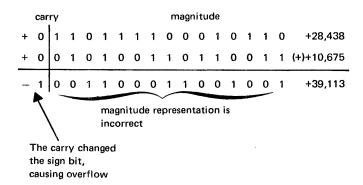

When both operands have like signs, the resulting sum may be too large to express in fifteen bits of magnitude. In this case a carry will propagate from the magnitude field into the sign bit position, causing the sign to change — this is overflow, recorded in the Condition register. In this example two positive numbers are added, resulting in a sum too large for the magnitude field. The resultant overflow sum is an incorrect negative value.

In this example, two positive numbers are added, resulting in a sum too large for the magnitude field. The resultant overflow sum is an incorrect negative value.

The addition of two operands with unlike signs cannot generate overflow since the result is the difference between the two, and it will be less than or equal to the larger operand.

#### SINGLE-PRECISION SUBTRACTION

Single-precision subtraction of two operands with unlike signs can result in overflow. Of course, overflow will only occur when the result is too large to express in 15 bits of magnitude. Overflow cannot occur when like-signed values are subtracted, because the adder result is really the difference between the two operands.

#### **DOUBLE-PRECISION**

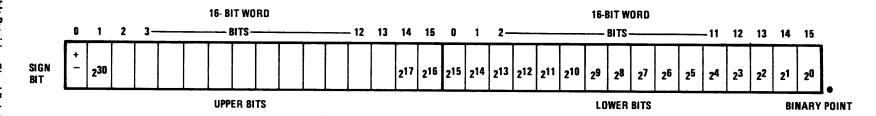

Double-precision, fixed-point operands contain a 31-bit integer value and one sign bit. A 32-bit operand resides in two adjacent storage locations or two adjacent file registers (Figure 2-2).

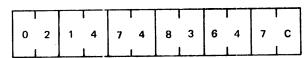

#### INFORMATION FORMATS

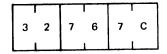

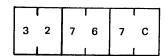

The 16-bit registers and main storage words within the 7200 facilitate the usage of hexadecimal notation. Hexadecimal numbering requires four binary places to represent each of the 16 different symbols within the system: decimal digits 0-9 and letters A-F. Thus, each 16-bit word or register can contain four hexadecimal symbols representing values from zero to 32,767<sub>10</sub>.

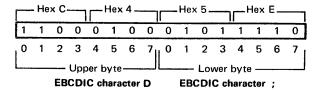

The hexadecimal symbols are also used to represent characters within the Extended Binary-Coded Decimal Interchange Code (EBCDIC). Each EBCDIC character, 8 bits long, comprises two hexadecimal symbols. Although 8 bits provide 256 possible variations, not all are used. The EBCDIC characters do represent the digits *0-9*, letters of the alphabet, all punctuation and arithmetic symbols (such as + -;>=), and special graphic and control symbols as shown in Table 2-1.

Each EBCDIC character (letter, digit or symbol) is represented in one byte (two hex symbols) as shown below.

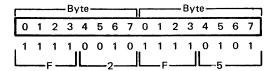

Since the decimal digits 0.9 can be represented in four bits and each EBCDIC character requires an entire byte, bits 0.3 are always 1111<sub>2</sub> (the hexadecimal character F) for those digits. As an example; the number 25 represented in EBCDIC code occupies two bytes.

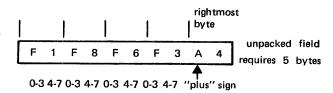

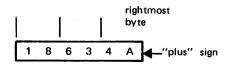

The numeric fields in EBCDIC, unpacked decimal fields, require a byte for each decimal digit. In an unpacked decimal field, bits 0-3 are always F<sub>16</sub> except in the byte containing the least significant decimal digit of the field.

In that byte, bits 0-3 indicate the sign of the entire decimal field. The hexadecimal letters used to indicate the sign are these:

Plus:

A,F, C, or E

Minus:

B or D

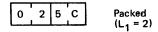

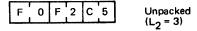

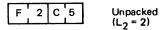

An unpacked decimal field can be packed to occupy a fewer number of bytes, by removing bits 0-3 of each EBCDIC digit except in the one containing the sign. The sign character is moved to the rightmost byte of the new packed field. The example below shows the number +18,634<sub>10</sub> in an unpacked decimal field and then in a packed decimal field.

packed field requires 3 bytes

If an unpacked field with an odd number of digits is packed, no portion of the resulting packed field is unused. If a even-number unpacked field is packed, the leftmost four bits of the resulting packed field are zeros.

Table 2-1. EBCDIC Character Codes (Bits 4-7)

|            |   |      | 0000 | 1<br>0001 | 2<br>0010 | 3<br>0011 | 4<br>0100 | 5<br>0101 | 6<br>0110 | 7<br>0111 | 8<br>1000 | 9<br>1001 | A<br>1010 | B<br>1011 | C<br>1100 | D<br>1101 | E<br>1110 | F<br>1111 |

|------------|---|------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|            | 0 | 0000 | NUL  | зон       | STX       | ETX       | PF        | нт        | LC        | DEL       |           |           | SMM       | VT        | FF        | CR        | so        | SI        |

|            | 1 | 0010 | DLE  | DC1       | DC2       | ТМ        | RES       | NL        | BS        | IL.       | CAN       | EM        | СС        | CU1       | IFS       | IGS       | IRS       | IUS       |

|            | 2 | 0010 | DS   | sos       | FS        |           | BYP       | LF        | ЕТВ       | ESC       |           |           | SM        | CU2       |           | ENQ       | ACK       | BEL       |

|            | 3 | 0011 |      |           | SYN       |           | PN        | RS        | UC        | EOT       |           |           |           | CU3       | DC4       | NAK       |           | SUB       |

|            | 4 | 0100 | SP   |           |           |           |           |           |           |           |           |           | ¢         |           | <         | (         | +         |           |

|            | 5 | 0101 | &    |           |           |           |           |           |           |           |           |           | ı         | \$        | *         | )         | ;         |           |

|            | 6 | 0100 |      | 1         |           |           |           |           |           |           |           |           |           | ,         | %         | _         |           | ?         |

| (Bits 0-3) | 7 | 0111 |      |           |           |           |           |           |           |           |           |           | :         | #         | @         | ,         | =         | "         |

|            | 8 | 1000 |      | а         | b         | С         | d         | е         | f         | g         | h         | i         |           |           |           |           |           |           |

|            | 9 | 1001 |      | j         | k         | ı         | m         | n         | 0         | р         | q         | r         |           |           |           |           |           |           |

|            | A | 1010 |      |           | s         | t         | u         | ٧         | w         | ×         | У         | z         |           |           |           |           |           |           |

|            | В | 1011 |      |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |

|            | С | 1100 |      | Α         | В         | С         | D         | E         | F         | G         | Н         | ı         |           |           | ,         |           |           |           |

|            | D | 1101 |      | J         | κ         | L         | М         | N         | 0         | Р         | Q         | R         |           |           |           |           |           |           |

|            | E | 1110 |      |           | s         | т         | U         | ٧         | w         | x         | Υ         | z         |           |           |           |           |           |           |

|            | F | 1111 | 0    | 1         | 2         | 3         | 4         | 5         | 6         | 7         | 8         | 9         |           |           |           |           |           |           |

(B

# 3. INSTRUCTION TYPES

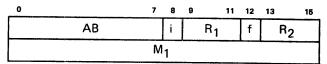

Every instruction consists minimally of a two-byte (16-bit) base instruction word. This base instruction word comprises two parts: an 8-bit operation code which tells the computer what to do with data; and two fields that specify, in general, the sending and receiving locations of the operand or operands used in the instruction.

Often, the base instruction word is not sufficient to provide all the information needed for certain operations. In such instances, it is augmented by adding a second, or a third, and sometimes even a fourth word. The repertoire, then, comprises 2-byte, 4-byte, 6-byte, and 8-byte instructions (two bytes in a word). This is the first consideration in determining the instruction type.

An instruction operand may be located in one of three places: in the instruction itself ("immediate" operand), in a register ("register" operand), or in main storage ("memory" operand). Operand location provides the second factor to be considered when determining the type of an instruction. Considering byte length and operand location, the repertoire may be divided into six basic instruction types:

- 1. Register/Register (2-byte)

- 2. Immediate/Register (2-byte)

- 3. Memory/Register (4-byte)

- 4. Direct/Register (4-byte)

- 5. Memory/Memory (6-byte)

- 6. Memory/Memory, extended (8-byte)

These six types are explained below.

## **GENERALIZED INSTRUCTION FORMATS**

Although a variety of formats are used to express the 159<sup>†</sup> instructions in the repertoire, better than 80% of them fall into one of the six types listed above. The following delineates the formats for these six basic types.

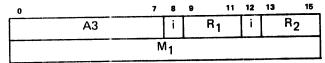

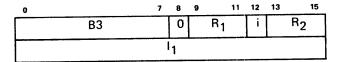

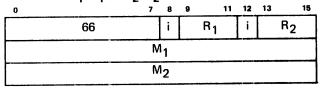

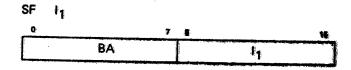

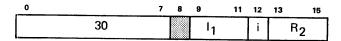

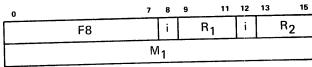

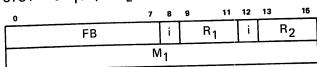

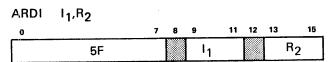

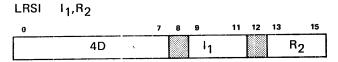

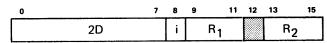

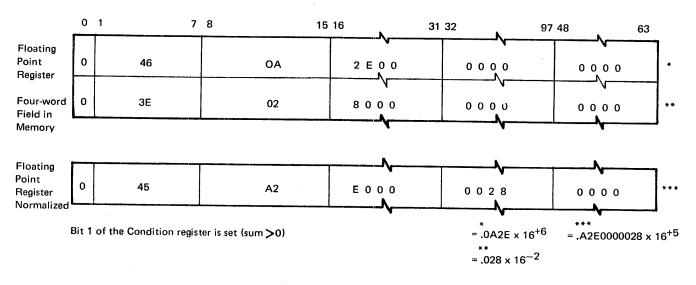

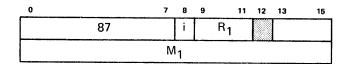

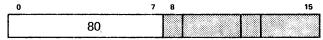

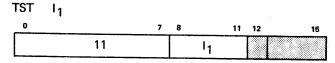

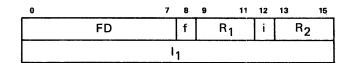

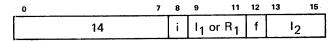

## 1. Register/Register (2-byte instruction)

| 8 | 4              | 4              |

|---|----------------|----------------|

| F | R <sub>1</sub> | R <sub>2</sub> |

F: The basic operation code

R<sub>1</sub>: A field specifying the location of the first operand. (A register number.)

R<sub>2</sub>: A field usually specifying the location of the results of the operation. If the operation involves two operands, this also specifies the location of the second operand.

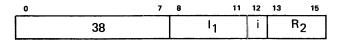

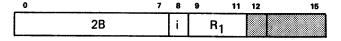

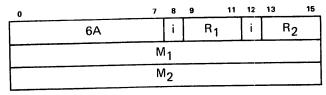

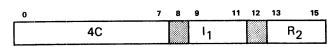

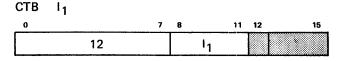

## 2. Immediate (2-byte instruction)

| 8 | 4  | 4  |

|---|----|----|

| F | lη | 12 |

F: The basic operation code

I<sub>1</sub>: A 4-bit quantity, the absolute value of which is used as the first operand.

R<sub>2</sub>: A field usually specifying the location of the results of the operation. If the operation involves two operands, this also specifies the location of the second operand.

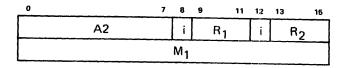

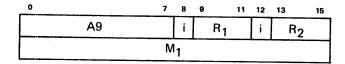

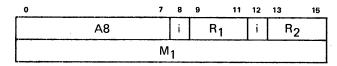

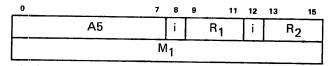

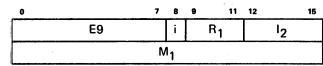

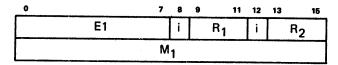

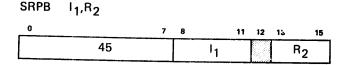

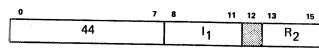

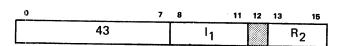

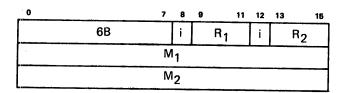

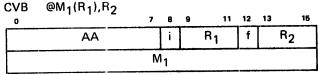

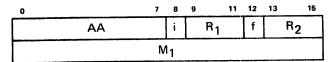

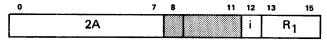

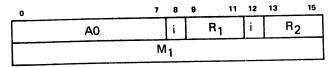

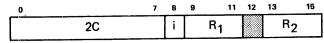

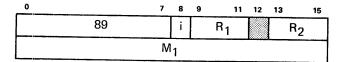

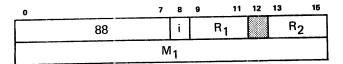

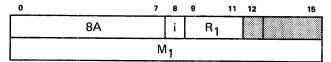

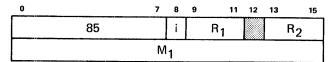

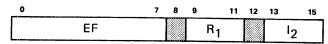

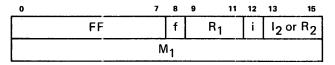

#### 3. Memory/Register (4-byte instruction)

| F              | R <sub>1</sub> | R <sub>2</sub> |  |  |  |  |  |  |

|----------------|----------------|----------------|--|--|--|--|--|--|

| M <sub>1</sub> |                |                |  |  |  |  |  |  |

F: The basic operation code

M<sub>1</sub>: An address specifying the location of the first operand.

<sup>&</sup>lt;sup>†</sup>Does not include 10 for the floating-point option.

- R<sub>1</sub>: A register number, the contents of which may be used to modify the first operand address (see Indexing).

- R<sub>2</sub>: A field usually specifying the location of the results of the operation. If the operation involves two operands, this also specifies the location of the second operand.

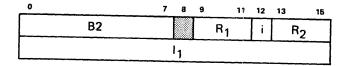

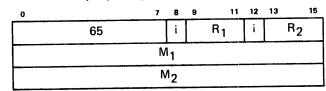

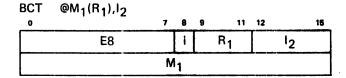

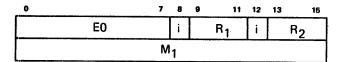

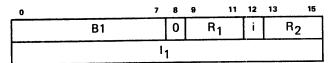

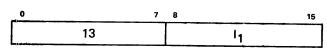

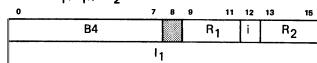

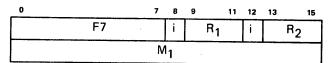

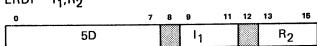

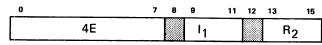

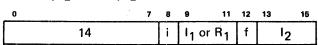

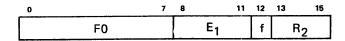

- 4. Direct (4-byte instruction)

| F  | R <sub>1</sub> | R <sub>2</sub> |

|----|----------------|----------------|

| 11 |                |                |

- F; The basic operation code

- I1: A 16-bit quantity, the absolute value of which is used as the first operand.

- R<sub>1</sub>: A register number, the contents of which may be used to modify the first operand (see Indexing).

- R2: A field usually specifying the location of the results of the operation. If the operation involves two operands, this also specifies the location of the second operand.

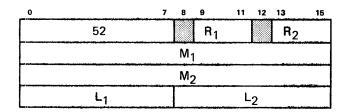

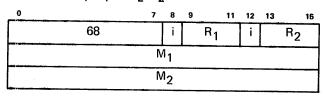

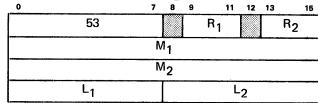

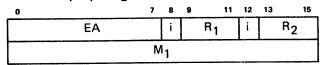

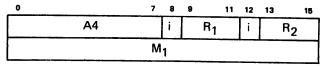

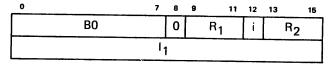

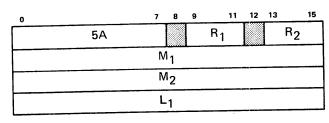

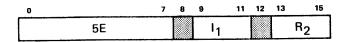

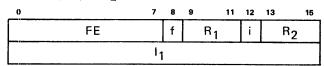

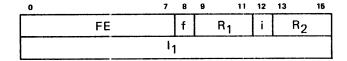

- 5. Memory/Memory (6-byte instruction)

| F              | R <sub>1</sub> | R <sub>2</sub> |  |  |  |  |  |

|----------------|----------------|----------------|--|--|--|--|--|

| M <sub>1</sub> |                |                |  |  |  |  |  |

| М              | 2              |                |  |  |  |  |  |

- F: The basic operation code

- M1: The first operand address

- M<sub>2</sub>: The second operand address; usually specifies the location of the results of the operation.

- R<sub>1</sub>, Two register numbers, the respective R<sub>2</sub>: contents of which may be used to modify the first operand address and the second operand address (see Indexing).

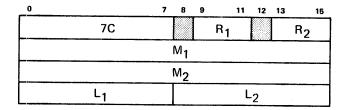

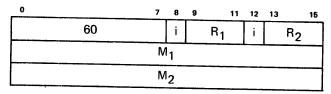

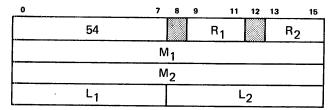

- Memory/Memory, extended (8-byte instruction)

| F              | R <sub>1</sub> | R <sub>2</sub> |  |  |  |  |  |

|----------------|----------------|----------------|--|--|--|--|--|

| M <sub>1</sub> |                |                |  |  |  |  |  |

| M <sub>2</sub> |                |                |  |  |  |  |  |

| L <sub>1</sub> | L              | 2              |  |  |  |  |  |

This instruction type deals with fields of operands, rather than single operands. F,  $R_1$ ,  $R_2$ ,  $M_1$ , and  $M_2$  are as explained under 5, above. The field length, in bytes, of the first operand is given by  $L_1$ ; that of the second operand is given by  $L_2$ .

As stated above, the foregoing are generalized formats only. Individual differences will be detailed in the instruction descriptions.

#### ADDRESSING MODES

Three addressing modes are available by which to obtain the operands used by an instruction: immediate, direct, and indirect.

#### **IMMEDIATE ADDRESSING**

Immediate addressing covers those cases where the operand is contained in the instruction word itself. Examples of "immediate" operands are:

- raw data

- shift count

- skip count

- a hexadecimal value indicating a bit position (in a register) that is to be tested, set, or cleared.

- an External Register number

- a processor number

#### **DIRECT ADDRESSING**

Direct addressing means that the related field of the instruction ( $R_1$  or  $M_1$ ;  $R_2$  or  $M_2$ ) specifies an address at which the operand may be found; the instruction specifies the location of the operand directly.

#### **INDIRECT ADDRESSING**

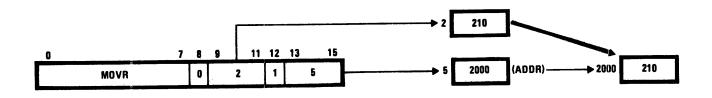

Indirect addressing means that the related field of the instruction  $(R_1 \text{ or } M_1; R_2 \text{ or } M_2)$  specifies a location that contains the address of the operand. That is, the instruction specifies the location of the operand indirectly.

#### **IMPLEMENTATION**

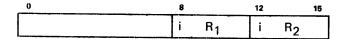

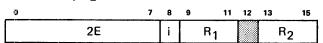

Direct and indirect addressing are indicated by the highest-order bits (designated "i") in the two R fields of the base instruction word.

For example, if bit 8 is 0, the register indicated by the lower three bits of the  $R_1$  field (or the 16-bit address stored in the  $M_1$  field if this is a multi-word instruction) contains the operand. On the other hand, if bit 8 is 1, the indicated register contains the operand address; if this were a multi-word instruction,  $M_1$  would contain a 16-bit memory location the **contents** of which would stipulate the address of the operand. These rules apply equally to the bit-12 address-mode designator.

Direct addresses may be even or odd, depending upon the instruction. Indirect addresses must always be even; whether the final operand address, located at the "indirect" address, is even or odd depends upon the instruction.

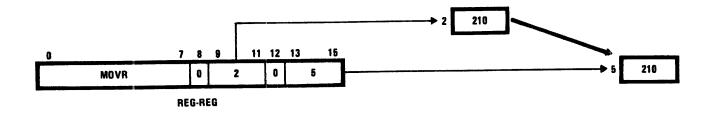

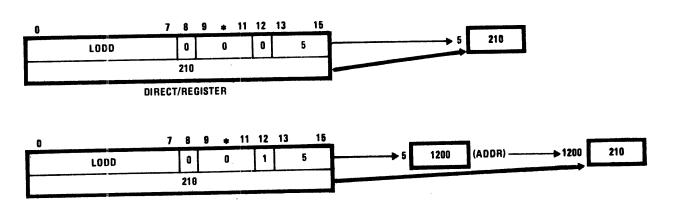

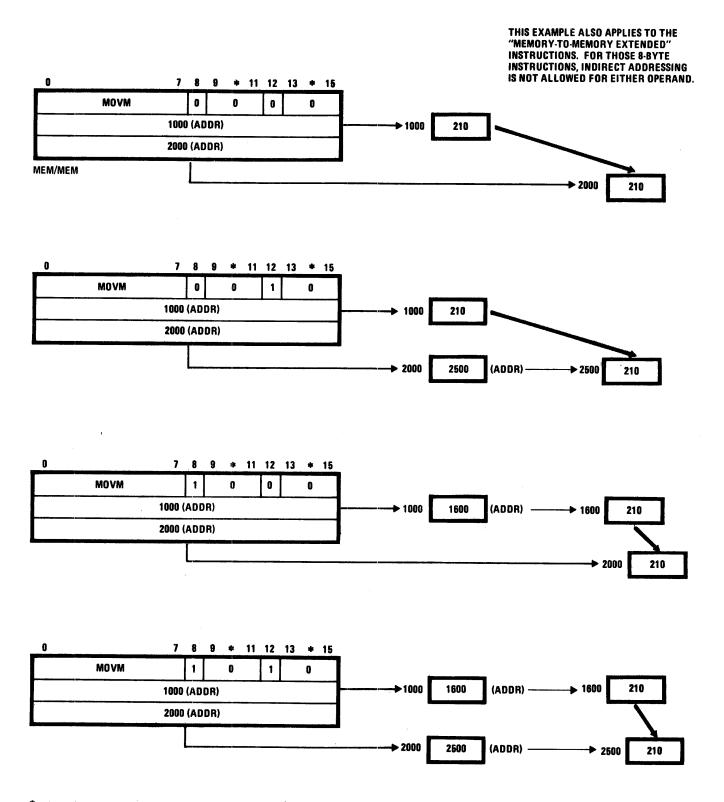

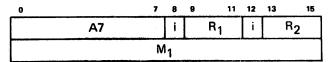

Figures 3-1 through 3-5 show the addressing schemes available for each instruction type, using all possible combinations of the two 'i' designators. Note that as each format is titled, the basic instruction type name is manifested for the case where both bit 8 and bit 12 are 0. In each example, when bit 8 or bit 12 is 1, the additional manipulation of indirect addressing is required.

These figures do not give the complete addressing story, for there are still the indexing (or address modification) situations to consider. This is the subject of the next section, Indexing.

#### **INDEXING**

Indexing consists of adding to the value of an instruction's M field (or the contents of the address specified therein) the contents of the register indicated in the corresponding R field of the base instruction word. Indexing cannot apply to the 2-byte instructions because those instructions do not have an M field.

Indexing will occur in an instruction whenever the R field for the indexable M address contains a register number other than zero (that is, 1-7). If the R field (bits 9-11 for  $R_1$ ; bits 13-15 for  $R_2$ ) contains a zero, no indexing for the related M address field is performed.

The terms "pre-indexing" and "post-indexing" define at what point in the instruction execution the indexing occurs. If the register contents are added to the value of the *M* field, it is called pre-indexing. If the register contents are added to the **contents** of the address specified by the M field, it is called post-indexing.

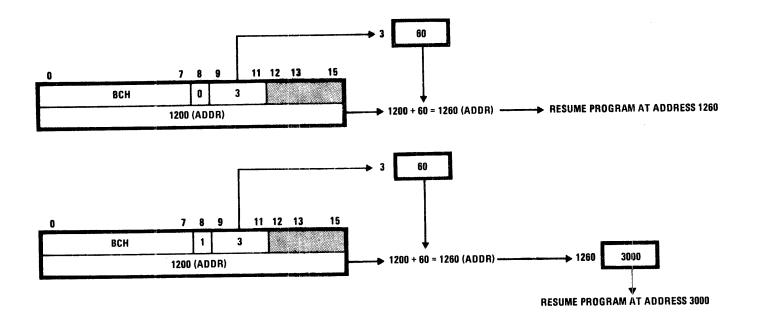

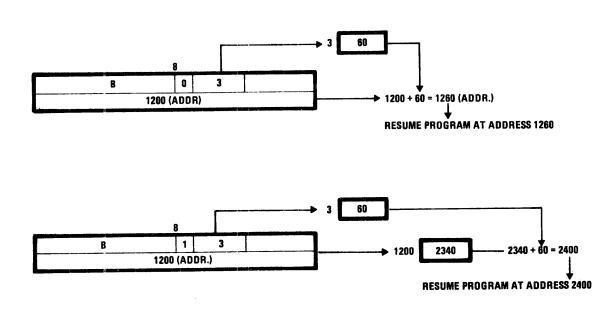

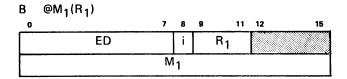

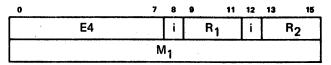

In the instruction repertoire, only one instruction (BCH) uses pre-indexing. Figure 3-6 shows how pre-indexing applies to that instruction. Figure 3-7 shows a similar instruction, B, using post-indexing. Figure 3-8 uses one of the previously defined examples to show another example of post-indexing. In the Machine Instructions section, indexing is always indicated when it is valid. Except for the BCH instruction, which uses pre-indexing, post-indexing is assumed when indexing is indicated.

It should be pointed out that, as the examples show, the two indexing methods differ only for the indirect addressing mode. That is, post-indexing must operate on the contents of the M field for the direct addressing mode (inasmuch as the "indirect" address doesn't exist), and in this respect is identical to pre-indexing.

The foregoing discussion has dwelt on address modification. But indexing may also be used to modify an operand. This fact bears repeating, for although indexing most frequently refers to address modification, operand modification is possible — albeit only for the second operand of direct-type instructions as evidenced previously in Item 4, under *Generalized Instruction Formats*.

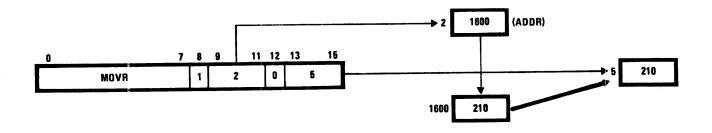

Figure 3-1. Register-to-Register Instruction Addressing

An important indexing consideration is this possibility: Indexing can attempt to produce an operand address greater than the 16-bit capacity of the adder. This condition occurs when the operand address, M, and the modifying value in the indexing register result in a overflow sum greater than  $65,535_{10}$  or FFFF<sub>16</sub>. If such happens, significance beyond 16 bits is lost; the remaining 16-bit sum is the operand address utilized by the instruction.

Of course, this condition can also occur when indexing an operand itself (the / field) rather than the operand address. No error indication is recorded when the above condition occurs,

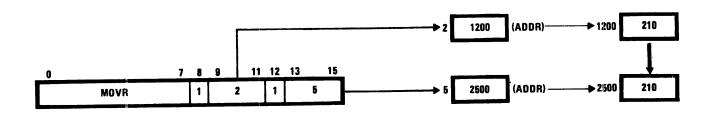

Figure 3-2. Immediate-Register Instruction Addressing

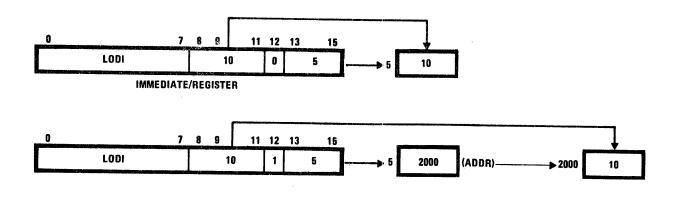

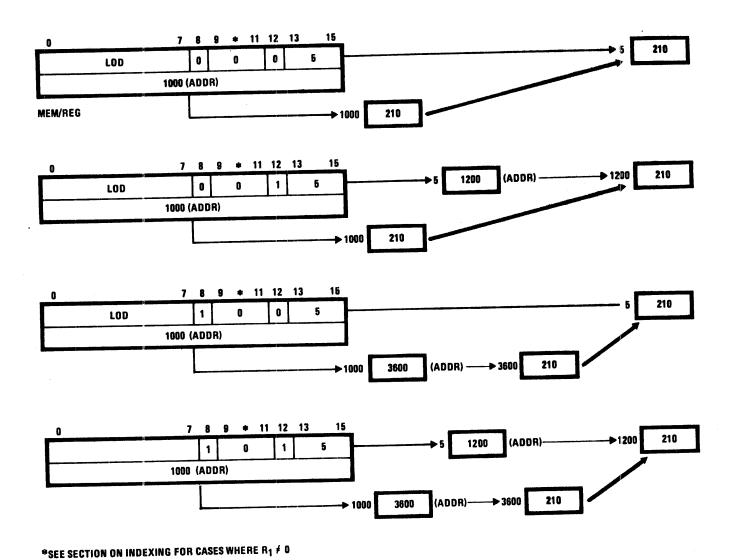

Figure 3-3. Memory-to-Register Instruction Addressing

<sup>\*</sup>SEE SECTION ON INDEXING FOR CASES WHERE R1 # 0

Figure 3-4. Direct-Register Instruction Addressing

<sup>\*</sup>SEE SECTION ON INDEXING FOR CASES WHERE  $R_1$ ,  $R_2 \neq 0$

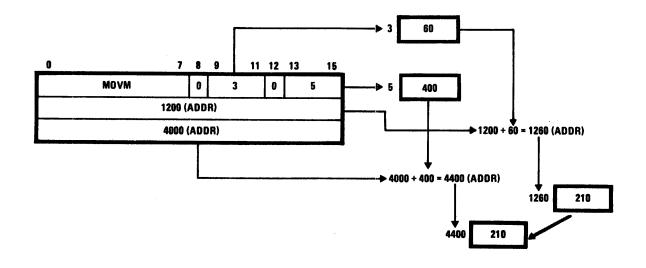

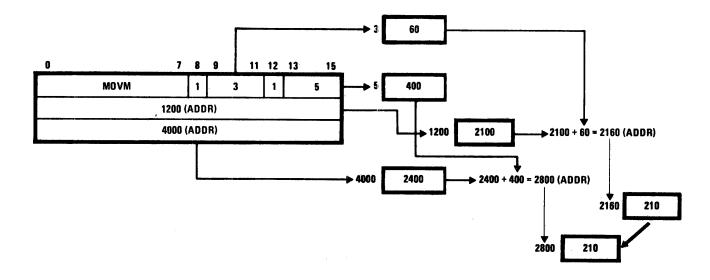

Figure 3-5. Memory-to-Memory Instruction Addressing

The BCH instruction causes an unconditional jump (or branch) to the address stipulated. If the  $R_1$  field were 0, 1200 would be the new address (or, if Bit 8 were a 1, the new address would be stipulated by the contents of location 1200). Because  $R_1$  is not 0, the contents of the indicated register are added to the value of the M-field. The state of Bit 8 then indicates whether or not an additional storage reference is needed to obtain the final "jump to" address.

Figure 3-6. Pre-Indexing With BCH Instruction

THE B INSTRUCTION ALSO PERFORMS AN UNCONDITIONAL JUMP, BUT USES POST-INDEXING. NOTE THAT B AND BCH (FIGURE 3-8) PERFORM IDENTICALLY WHEN BIT 8 IN BOTH INSTRUCTIONS IS A 0 (DIRECT ADDRESSING). THE INSTRUCTIONS DIFFER, HOWEVER, WHEN BIT 8 IN BOTH IS A 1 (INDIRECT ADDRESSING).

Figure 3-7. Post-Indexing With B Instruction

FOR OTHER VALUES OF THE ADDRESS-MODE DESIGNATORS (BITS 8 AND 12), COMBINE THE APPROPRIATE PARTS OF THESE EXAMPLES.

Figure 3-8. Memory-to-Memory Instruction With Post-Indexing

# 4. MACHINE INSTRUCTIONS

#### INTRODUCTION

The MRX/40/50 System machine instruction set is divided into two major categories: general-purpose instructions and system instructions. General-purpose instructions are the instructions needed to solve most data processing problems using a defined software system. System instructions are specialized instructions used to interpret and alter a software system.

Within these two major categories, the instructions are divided into functional groups, and these functional groups are listed in alphabetical order, as shown in the following table.

# General-Purpose Instructions System Instructions

Arithmetic

Control

1/0

**Bit-Oriented**

Boolean Logic

Roolegu rodk

Branching

Compare

Control

**Data Conversion**

**Data Transfer**

Shift

**Optional: Floating Point**

The instructions in each functional group are listed alphabetically by mnemonic. This rule holds for all instructions except for logical pairs or groups of instructions — these instructions are listed alphabetically according to the first instruction of the pair. For instance, PAKX (Pack) will be followed by UNPX (Unpack), and SB (Skip Back Unconditional) will be followed by SF (Skip Forward Unconditional).

Remember the following rules when reading the machine instruction descriptions.

- 1. The address of a memory field refers to the leftmost byte of that field.

- A word is defined as two bytes; the bit positions in a word are numbered left to right, 0-15.

- 3. The operand fields of the instructions may be fixed or variable in length. Fixed-length operand fields may be one byte, one word (2 bytes), or two words (4 bytes in length. Variable-length fields may range from 0-65.535 bytes.

- 4. Most instructions must address even bytes in memory; the rest can address even or odd bytes. The instructions which can address even or odd bytes are identified by a bullet following the instruction name (such as, Compare Packed Decimal e).

- 5. The effective address of a field in memory is defined as the final address of the field derived from all specified addressing techniques. If no optional addressing techniques are used, the effective address is in the M field, otherwise, the effective address is a result of indexing, indirect addressing, or both.

# **SOURCE AND OBJECT FORMAT INTERPRE- TATION**

The source and object formats of the operands are defined using the following symbols.

| Op Code | The operation codes are p | resented |

|---------|---------------------------|----------|

|         | in hexadecimal (00 throu  | igh FF). |

R A general register number, 0-7. The register may be used as a sending or receiving field (0-7), or as an index register (1-7 only).

E Extended register,0-15. (For RDX and WRX only.)

M A memory address, 0-65,535.

An immediate value; the value varies depending on the instruction.

The value may represent an amount used in an arithmetic operation, a shift count, a skip count, or a bit number.

i

@

L A field length, usually 0-255, but longer for some instructions. For certain instructions the length of an operand field may be defined in the instruction. The length specified in the instruction overrides any previous field length definition, but is only in effect for that instruction.

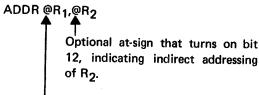

An at-sign (@) in a source operand indicates indirect addressing, an optional feature. For the instructions in which a register is a sending or receiving field, the at-sign indicates indirect addressing for R<sub>1</sub> or R<sub>2</sub>. If a field in memory is the sending or receiving field, the at-sign indicates indirect addressing of M<sub>1</sub> or M<sub>2</sub>.

() Index registers and field lengths are optional; they are enclosed in parentheses in a source operand. A source operand using both an indexing and a field length specification would be represented like this:  $M_1(L_1,R_1)$ . The comma in the parentheses must not only be coded when both the length and index register are used, but also if either one of them is used, as follows:  $M_1(L_1)$  or  $M_1(R_1)$ . This enables the assembler to distinguish between the two specifications in parentheses.

Bits 8 and 12 of the object instructions are used in almost every instruction to convey information to the computer concerning that instruction. If these bits are not interpreted in any way, they are shaded; otherwise, the following symbols are used to define bits 8 and 12.

i Indirect addressing indicator; for direct addressing i=0, for indirect addressing i=1. Indirect addressing is indicated by the programmer.

f A sub-function indicator; indicates a function that the operation code alone cannot do. Function bits are set by the assembler.

1,0 If bit 8 or 12 must be a 1 or a 0 for a particular instruction, the bit will be shown as a 1 or 0. These bits are set by the assembler; if the wrong bit state appears in the object instruction, a no-operation occurs.

An R, M, I, or L in source operand 1 is identified as  $R_1$ ,  $M_1$ ,  $I_1$ , or  $L_1$ ; in source operand 2 they are identified as  $R_2$ ,  $M_2$ ,  $I_2$ , or  $L_2$ . These symbols are numbered so that they can be referred to easily (distinguishing between  $R_1$  and  $R_2$  in the same instruction) and to make clear the location of these fields in the object format.

The two major operand fields must be separated by a comma; no blanks are allowed anywhere in the operand fields.

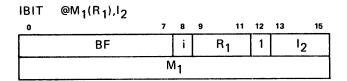

The following examples show how the source and object formats of the machine instructions are illustrated in this section. The at-sign and any designations in parentheses (field length and index registers) are almost always optional; if any of these designations are not optional, this fact will be noted. Data flow is usually operand 1 to operand 2, unless stated otherwise.

# **EXAMPLE 1: Add Register-Register**

Optional at-sign that turns on bit 8, indicating indirect addressing of R<sub>1</sub>.

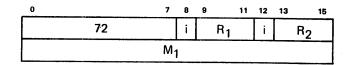

| 0       | 7 | 8 | 9              | 11 | 12 | 13             | 15 |

|---------|---|---|----------------|----|----|----------------|----|

| OP CODE |   | i | R <sub>1</sub> |    | i  | R <sub>2</sub> |    |

$R_1$  and  $R_2$  are in the same relative position in the object format.

The variations of this instruction are shown in the following diagram; depending on the use of indirect addressing, data flow may be register to register, memory to register, register to memory, or memory to memory.

$$ADDR \begin{cases} R_1 \\ @R_1 \end{cases} R_2$$

$$R_2$$

$$R_2$$

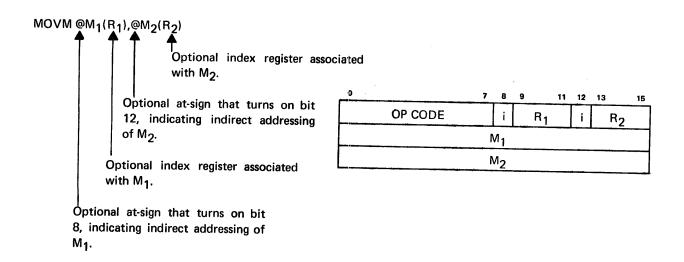

# **EXAMPLE 2: Move Memory-Memory**

The variations of this instruction are shown in the following diagram. Data flow is always memory to memory, but there are many ways in which the addressing options can be used.

Since each operand can be expressed either of four ways, there are  $4 \times 4 = 16$  variations of this instruction.

# **GENERAL-PURPOSE INSTRUCTIONS**

#### **ARITHMETIC INSTRUCTIONS**

| Mnemonic | Name                       |

|----------|----------------------------|

| ADD      | Add Memory-Register        |

| ADDD     | Add Direct                 |

| ADDI     | Add Immediate              |

| ADDK     | Add Packed Decimal •       |

| ADDM     | Add Memory-Memory          |

| ADDR     | Add Register-Register      |

| ADDT     | Add Two-Word               |

| DIV      | Divide Memory-Register     |

| DIVD     | Divide Direct              |

| DIVI     | Divide Immediate           |

| DIVK     | Divide Packed Decimal •    |

| DIVM     | Divide Memory-Memory       |

| DIVR     | Divide Register-Register   |

| MPY      | Multiply Memory-Register   |

| MPYD     | Multiply Direct            |

| MPYI     | Multiply Immediate         |

| MYPK     | Multiply Packed Decimal •  |

| MPYM     | Multiply Memory-Memory     |

| MPYR     | Multiply Register-Register |

| SUB      | Subtract Memory-Register   |

| SUBD     | Subtract Direct            |

| SUBI     | Subtract Immediate         |

| SUBK     | Subtract Packed Decimal •  |

| SUBM     | Subtract Memory-Memory     |

| SUBR     | Subtract Register-Register |

| SUBT     | Subtract Two-Word          |

| ZADK     | Zero and Add ●             |

The following rules apply to binary addition and subtraction.

- The Overflow bit (bit 0) in the Condition register is set if the results of a binary add or subtract exceed the limits of a signed one-word or two-word result field. Specifically, overflow is indicated if the results are greater than 2<sup>n-1</sup>-1 or if the results are less than -2<sup>n-1</sup> (where n=16 or 32 bits).

- The Link bit (bit 3) in the Condition register is set if the results of a binary add or subtract exceed the limits of an unsigned one-word or two-word result field. Specifically, link is indicated if the results are greater than 2<sup>n</sup>-1 for an add (where n=16 or 32 bits).

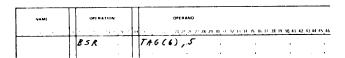

# Add Memory - Register

ADD @M<sub>1</sub>(R<sub>1</sub>),@R<sub>2</sub>

FUNCTION: Performs a binary addition of a one-word field in memory and a one-word field in a general register or in memory.

OPERAND 1: A one-word field in memory. Addressing options to the base address  $M_1$  include indexing, indirect addressing, or a combination of both.

OPERAND 2: A one-word field in the general register specified by R<sub>2</sub>, or in memory if indirect addressing is used.

RESULTS: The sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1, 2, and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than 65,535.

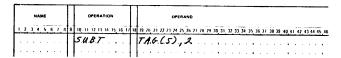

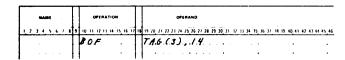

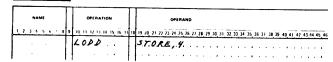

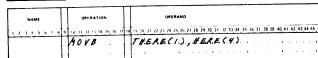

# **EXAMPLE**

| NAMI        |   |    | OPERA   | 110%  |        |      | _  | ór | ERAND | <br>    | _  |      | _    | _  |    |      | _    | _  | _  |      | _   |      |

|-------------|---|----|---------|-------|--------|------|----|----|-------|---------|----|------|------|----|----|------|------|----|----|------|-----|------|

| to the con- | 1 |    | 11 31 1 | 15 10 | II. 12 |      |    |    |       | PI 41 3 | 17 | 11.3 | 4 35 | 36 | 31 | 38 3 | 9 40 | 41 | 47 | 43 6 | 4 4 | 5 46 |

|             |   | A. | DD      |       |        | TA.C | 50 | 3) | ,.7   | <br>,   |    |      |      | ,  |    |      |      |    |    |      |     |      |

|             | ł |    |         |       | •      |      |    |    |       |         |    |      |      |    |    |      |      |    |    |      |     |      |

The field identified by TAG(5) is added to the contents of register 7; the sum will be in register 7.

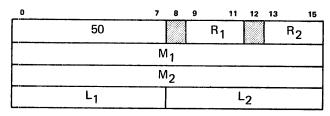

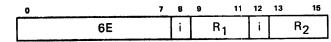

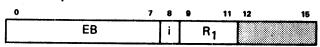

### **Add Direct**

ADDD 11(R1),@R2

FUNCTION: Performs a binary addition of a one-word immediate value and a one-word field in a general register or in memory.

OPERAND 1: A 16-bit immediate signed value in the second word of the instruction; the value may range from -32,768 to +32,767.

Indexing may be specified for operand 1. In this case, the value of operand 1 is derived by adding the I<sub>1</sub> value and the general register contents specified by R<sub>1</sub>; no check for overflow or link is made during the indexing.

OPERAND 2: A one-word field in the general register specified by R<sub>2</sub>, or in memory if indirect addressing is used.

RESULTS: The sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1, 2, and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than 65,535.

# **EXAMPLE**

|  |   | , | N | AM | 11 |  | <br>I |   | _   |   | OP | 'E R | IA | rto | N  | - |      | Ī | Ī  |    |    |   |   |   | o | PER | 41 | ю  |   |   |    |    |     |      |     | _     |   |     |    |    |    |    |    |    |    |    |    | _  |

|--|---|---|---|----|----|--|-------|---|-----|---|----|------|----|-----|----|---|------|---|----|----|----|---|---|---|---|-----|----|----|---|---|----|----|-----|------|-----|-------|---|-----|----|----|----|----|----|----|----|----|----|----|

|  | , | _ |   | :  | 4  |  | <br>1 | 4 | 111 |   |    | 1/ 1 | 1  | 11  | 15 | 1 | . 1. | 1 | +- | -  |    | ~ | - | _ | _ | 1.0 | -  | _  | - | - | 24 | 10 | -11 | . 1. | 1 1 | <br>1 | 5 | 11. | 1/ | 18 | 19 | 10 | 41 | 47 | 43 | 44 | 45 | 46 |

|  |   |   |   |    |    |  | ŀ     | ł | A   | L | 1. | 2    | 0  |     |    |   |      |   | 1  | ٠. | 5. | 0 | ( | 4 |   | ٠,  | 1  | ۲. | 3 |   |    |    | •   |      |     |       |   |     |    |    |    |    |    |    |    |    | •  |    |

|  |   |   |   |    |    |  | ı     | 1 |     |   |    |      |    |     |    | • |      | 1 | 1  |    | •  |   |   |   |   |     | •  |    |   |   |    |    |     |      |     |       | • |     |    |    |    | •  |    |    |    |    |    |    |

The immediate value of 150 is modified by the contents of register 2 and added to the contents of register 3; the sum will be in register 3.

If register 2 contains a value of 4, and register 3 contains a value of 10, the operation will add 150 + 4 + 10; the result of 164 will be in register 3.

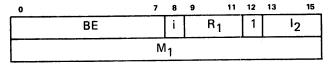

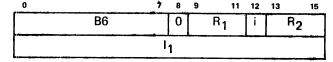

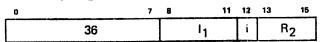

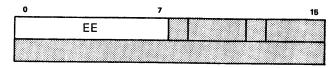

# Add Immediate

ADDI I<sub>1</sub>,@R<sub>2</sub>

| 0 7 | 8 | 11 | 12 | 13 | 15 |

|-----|---|----|----|----|----|

| 32  |   | 11 | i  | R  | 2  |

FUNCTION: Performs a binary addition of a 4-bit immediate value and a one-word field in a general register or in memory.

OPERAND 1: A 4-bit unsigned value located in bits 8-11 of the instruction; the I<sub>1</sub> value may range from 0-15. The I<sub>1</sub> value is added to bit positions 12-15 of operand 2; bits 0-11 are zeros.

OPERAND 2: A one-word field in the general register specified by R<sub>2</sub>, or in memory if indirect addressing is used.

RESULTS: The sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1, 2, and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than 65,535.

# **EXAMPLE**

| <b></b>       | * | ***     |        |         | ~   | ~   | **** | *** | *** |    |      |       |      | -   |      |    |    |      |    | ~    |      |     | -          | -   | -   |      |     | -    |    | -         |

|---------------|---|---------|--------|---------|-----|-----|------|-----|-----|----|------|-------|------|-----|------|----|----|------|----|------|------|-----|------------|-----|-----|------|-----|------|----|-----------|

| NAMI          |   | OF      | PERATI | ON      | 1   | 1   |      |     |     | OF | PERA | ND    |      |     |      |    |    |      |    |      |      |     |            |     |     |      |     |      |    |           |

| 2 1 1 5 1 2 8 | 9 | 10 () 1 | 2341   | 1 25 16 | J,  | , s | м    | 71  | ni  | ., | 1.75 | 7ti . | ,, , | 8 2 | 4 30 | 31 | 37 | 31 : | и: | is 3 | 16 3 | , 3 | <b>8</b> 3 | 9 4 | 0 4 | 1 42 | 2 4 | 3 44 | 45 | <b>46</b> |

|               |   | ADI     | I      |         |     |     |      |     |     |    |      |       |      |     |      |    |    |      |    |      |      |     |            |     |     |      |     |      |    |           |

|               |   |         |        |         | - 1 | l   |      | ٠.  |     |    |      |       |      |     |      |    |    |      |    |      |      |     |            |     |     |      |     |      |    |           |

The immediate value of 10 is added to the field at the memory address specified in register 4; the sum will be at this address.

#### Add Packed Decimal •

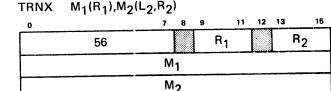

ADDK  $M_1(L_1,R_1),M_2(L_2,R_2)$

<u>FUNCTION</u>: Performs a signed decimal addition, proceeding from right to left, of the two packed decimal fields in memory. The field lengths L<sub>1</sub> and L<sub>2</sub> may vary from 0-255 bytes.

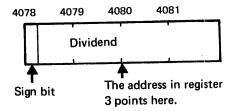

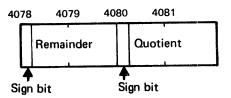

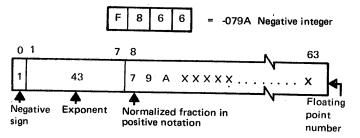

<code>OPERAND 1:</code> A packed decimal field in memory. The field length, 0-255 bytes, is specified in the  $L_1$  field of the instruction. The operand address indicated by  $M_1$  may be indexed, but indirect addressing is not allowed. The effective address points to the most significant bytes of the decimal field.