# MRX/40/50 Systems 7200/7300 Computers Product Description

#### FOR MEMOREX INTERNAL USE ONLY

# COMPANY CONFIDENTIAL

This product description contains confidential information of the Memorex Corporation and is intended for internal distribution only.

Document 2999.001 March 1972

# FOR INTERNAL USE ONLY

#### PREFACE

This document describes hardware aspects of the MEMOREX 7200/7300 Computers at the design level of March, 1972. It completely replaces the previous versions.

This product description contains information for programmers, engineers, field support and marketing personnel, and other Memorex personnel concerned with a general overview of the processor's capabilities of the computer; discuss its functional characteristics and principles of operation, including instruction descriptions, and describe the System Control Panel and its use.

It is recognized that changes are occurring, and potential changes are being evaluated; present and future inaccuracies will be treated in later publications.

The Product Description is intended to serve as a source of official information for Memorex personnel until it is supplanted by the series of 7200 and 7300 Computer manuals now being generated. Comments may be sent to the Publications Department, Midwest Operations, Memorex Corporation, 9200 Science Center Drive, Minneapolis, Minnesota, 55428, for use in preparing these future publications.

# SPECIAL MRX MARKETING EDITION

This abridged edition of the 7200/7300 computers Product Description has been prepared from more extensive Memorex internal development documentations.

# SECTIONAL TABLE OF CONTENTS

| I. GENERAL   | DESCRIPTION                                            | 1 - 1 |

|--------------|--------------------------------------------------------|-------|

| II. FUNCTIO  | NAL DESCRIPTION                                        | 2-1   |

| III. MACHINE | INSTRUCTIONS                                           | 3-1   |

| IV. (Not Ind | cluded in This Version)                                | -     |

| V. SYSTEM    | CONTROL PANEL                                          | 5-1   |

|              | COMPARISON OF 7200/7300 PERFORMANCE<br>CHARACTERISTICS | A-1   |

| APPENDIX B:  | MNEMONIC CODE TO HEX CODE                              | B-1   |

| APPENDIX C:  | MACHINE LANGUAGE INSTRUCTION TIMING FORMULAS           | C-1   |

2999.001

# SECTION I GENERAL DESCRIPTION

# TABLE OF CONTENTS

# GENERAL DESCRIPTION

| INTRODUCTION                | 1-1   |

|-----------------------------|-------|

| ARCHITECTURE                | 1-2   |

| PERIPHERAL DEVICES          | 1-3   |

| COMMUNICATIONS SUPPORT      | 1-3   |

| PROGRAMMING SYSTEMS SUPPORT | 1 - L |

# SECTION I GENERAL DESCRIPTION

#### INTRODUCTION

An overview of the MRX/40/50 data-processing systems is provided in Section 1 of this product description. The remainder of this manual is devoted to the detailed description of the functional and logical characteristics of the MEMOREX 7200 and 7300 computers. Appendix A tabulates the performance differences between the 7200 and 7300. While peripheral devices are referred to throughout, they are not discussed in detail.

The MRX/40 and 50 are low-cost communications-oriented systems with large data base capacity. A wide range of storage sizes, peripheral devices, and integrated adapters affords maximum flexibility in tailoring a system to meet a user's specific need. MRX/40/50 are supported by an unusually comprehensive operating system developed by Memorex. This extensive programming systems support permits the user to concentrate on his application, rather than on the functions of the system. The combination of hardware and software capability provides a price/performance level normally associated with more costly data processing systems. The result is a more efficient and economical data-processing system for the user.

Several characteristics distinguish the MRX/40/50 computer systems:

- Advanced architecture

- Wide range of peripheral devices

- Extensive communications support

- Comprehensive programming systems support

1-1 2999.001

#### ARCHITECTURE

The MEMOREX 7200 and 7300 offer advanced hardware design at all levels, from monolithic circuit components to architecture. The use of monolithic components produces a high-speed machine cycle. Miniaturized circuits permit the concentration of great computational power in a physically small cabinet. They also reduce the number of required components, thus decreasing the potential sources of hardware failure; the result is a high degree of reliability. The 7200/7300 printed-circuit boards are packaged and arranged by function, which makes fault isolation and correction faster.

Main storage is implemented through the use of metal-oxide semi-conductors (MOS) which allow for greater packing density of components and lower memory costs. Storage sizes of the 7200/7300 range from 16K to 128K bytes (each byte contains 8 bits plus a parity bit).

The 7200 and 7300 are microprogrammed computers. All machine language instructions are implemented through the use of microprogramming instructions residing in Control Storage. These micro-instructions perform within the much shorter cycle time of Control Storage. Microprograms, automatically loaded at Initial Program Load (IPL) time, are provided by Memorex; they reside as a small reserved portion of a disc pack and require no user intervention or maintenance.

The design of the 7200/7300 computers is such that certain portions of the hardware are dedicated to specific functions such as communications input-output, direct-access input-output, and arithmetic functions. A full set of eight general registers is dedicated for each such use by the operating system. Three additional sets of eight general registers are dedicated for user programs. The use of these various hardware functions is controlled by the operating system which interfaces to a hardware-controlled priority network.

The 7200/7300 incorporate integrated adapters for control of disc storage, communications, card readers, and card punches. Their use eliminates the need for large external control units, and thus provides for a lower-cost system.

7200/7300 computer features include these:

- Alterable Control Storage (4K words)

- Up to 128K bytes of Main Storage

- Error Correction Code (ECC) option for Main Storage

- Job Accounting Aids

- Interval Timer

- Storage Protection

- Relocation and Protection

- Integrated Console Adapter (standard)

- Integrated Communications Adapter (ICA) servicing up to 15 communications channels

- Integrated File Adapter (IFA) for up to eight MEMOREX 3664 disc drives.

- Integrated adapters for the following:

- up to 1000 cpm card readers (80-column)

- up to 500/120 cpm reader/punch (80-column)

- Printer attachment for up to 1200 lpm printer

- Up to two selector channels for supporting external control units.

#### PERIPHERAL DEVICES

An unusually wide range of peripheral devices to solve a variety of application needs can be accommodated by the MRX/40/50 systems:

- Card equipment (80-column cards).

- Printers may range in speed up to 1200 lines per minute.

- From one to eight disc drives may be used, each with a capacity of 14 or 28 megabytes. This adds up to a potential of 224 million bytes of on-line storage.

- Magnetic tape transfer rates may be up to 60 kilobytes per second.

#### COMMUNICATIONS SUPPORT

The MRX/40/50 systems have low-cost communications hardware, combined with simplified communications software. Up to 15 communications lines are provided for operations in asynchronous or synchronous modes. Other features include autocall, autoanswer, speed selection, autopoll, station select, and synchronous transparency.

1-3

For terminals, the user may choose from the MEMOREX 1200 series or certain IBM\* and Teletype\* terminals. Networks ranging from small to relatively large may be configured for the MRX/40/50.

A logical-level macro language is provided to handle both asynchronous and synchronous transmissions. Included are the standard functions such as READ, WRITE, GET, PUT, and code translate. Messages are queued in memory. A special communications monitor controls multiple terminals and multiple transactions for the user-written application programs.

#### PROGRAMMING SYSTEMS SUPPORT

The MRX/40/50 systems are supported by a level of programming systems normally only available with large-scale systems. The operating system provided for the MRX/40/50 is a comprehensive multi-programming system which includes the following features:

- Cataloged job control statements

- Input spooling

- Output spooling

- Complete data management

- Extensive utility programs

- High-performance disc sort

- Advanced library facilities

- Modular systems generation

- IBM\* System/360 Model 20 compatibility

Four major programming languages are available for MRX/40/50: Assembler, ANSI COBOL, RPG II and FORTRAN IV. The Assembler language has complete macro capability. COBOL includes many significant extensions. The RPG II language is designed so that most IBM 360/20 and System/3 programs will recompile and execute without modification. All languages include the ability to exit to assembler language subroutines, and programs can be segmented.

1-4

<sup>\*</sup>Tradenames, International Business Machines Corporation and the Teletype Corporation.

# SECTION II FUNCTIONAL DESCRIPTION

### TABLE OF CONTENTS

# FUNCTIONAL DESCRIPTION

| INTRODUCTION<br>SYSTEM ARCHITECTURE                                                                                                  | 2-1<br>2-1                                  |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Input/Output Computer Hardware Priority Storage Protection Computer Options                                                          | 2-3<br>2-3<br>2-4<br>2-5<br>2-5             |

| Job Accounting Relocation and Protection                                                                                             | 2-5<br>2-5                                  |

| Relocation<br>Protection<br>Control                                                                                                  | 2-6<br>2-6<br>2-6                           |

| Error Correction Code Option                                                                                                         | 2-9                                         |

| DATA REPRESENTATION                                                                                                                  | 2-9                                         |

| Hexadecimal Representation EBCDIC Representation Binary Representation Zoned Decimal Format Packed Decimal Representation Addressing | 2-9<br>2-10<br>2-13<br>2-14<br>2-16<br>2-17 |

| Immediate Data Indexing Direct Addressing Indirect Addressing                                                                        | 2-17<br>2-17<br>2-18<br>2-20                |

| MACHINE INSTRUCTION FORMATS                                                                                                          | 2-23                                        |

|                                                                                                                                      |                                             |

| FIGURE TITLES                                                                                                                        |                                             |

| Figure 2-1. System Architecture Figure 2-2. Generating Relocation Address Figure 2-3. Storage Access Protection Matrix               | 2-2<br>2-7<br>2-8                           |

i

2999.001

# SECTION II FUNCTIONAL DESCRIPTION

#### INTRODUCTION

This section contains information intended to provide program implementation understanding for the MRX/40/50 system (MEMOREX 7200 and 7300 computers respectively). It does so by further explaining the system architecture (hardware and software concept and relationship) and describing data and instruction formats, storage addressing, and principles pertinent to program implementation.

#### SYSTEM ARCHITECTURE

Data processing systems divide their time between input/output operations and arithmetic/logical functions. This conflict of interest usually causes large periods of system time to be dominated by input/output functions. Obviously, while this domination exists, hardware such as that dedicated to arithmetic/logical functions stands idle. This results in uneconomical time-versus-hardware usage.

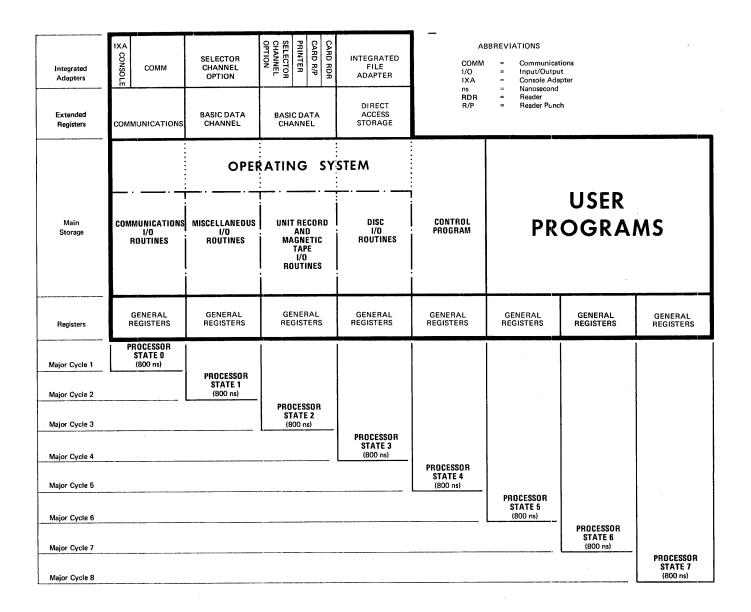

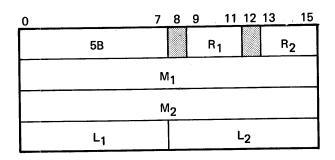

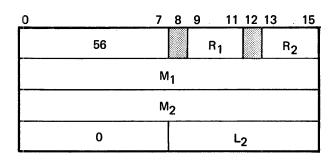

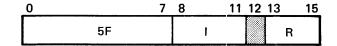

To avoid this uneconomical usage, the 7300 computer employs a multiplex technique which divides one complete *machine* cycle into eight segments called 'major cycles'. Along with this time division, a design concept is implemented dedicating those resources (hardware) which are function oriented to one of these time segments. Figure 2-1 illustrates this combination of one *major cycle* and a particular set of dedicated resources as a 'processor state'. These *processor states* are

2-1

#### FOR MEMOREX INTERNAL USE ONLY

Figure 2-1. System Architecture

functionally oriented and during the time they exist have exclusive access to what is termed "shared resources". Shared resources are those elements of hardware, such as an arithmetic section, which are common to all processors.

#### Input/Output

The first consideration in any data-processing system is how well it can transmit or receive data. As shown in Figure 2-1, the 7300 computer has functionally oriented integrated adapters and hardware as described by the following paragraphs.

• There is an integrated communications adapter capable of controlling up to 15 independent communications lines. These communications lines are connected through the adapter to the communications processor.

The integrated adapter (IXA) for the system console also uses the communications processor.

- There are two basic data channel processors.

- The card reader, card reader/punch, and printer connect to the basic data channel via their respective adapters. Up to seven external control units connect to the basic data channel via the first selector channel option.

- 2. Up to eight additional external control units may be attached to the second selector channel.

- To accommodate disc storage devices, an integrated file adapter is provided connecting up to eight disc drives to the disc processor.

#### Computer Hardware

Each of the four input/output processors has a set of general registers. These registers are used by the input/output routines for their respective function.

Four additional sets of general registers are illustrated in Figure 2-1. One of these register sets is dedicated to the control programs of the operating system. The remaining three sets of general registers are dedicated to executing user programs.

Hardware timing for the 7300 computer divides the total computer cycle into eight segments (major cycles). During each major cycle, specific functionally dedicated resources (hardware) perform in conjunction with shared resources to become a processing entity. Figure 2-1 illustrates this period of time as a "processor state". One of these major cycles is allotted to each processor state.

#### Priority

As previously mentioned, the hardware machine timing is divided into major cycles, allocated one cycle per processor state. Figure 2-1 illustrates the first major cycle being allocated to processor state 0 (communications processor). In other words, for that cycle the computer is operating the communications hardware. During the next major cycle, processor state 1 (a multi-device processor) hardware is in operation. This continues through processor states 2, 3, 4, 5, 6, and 7.

If, as the diagram shows, all processor states have work to perform of equal priority, these cycles occur sequentially. Processor states performing high-speed input-output operations need priority over those performing lower-speed input-output or general computational functions. For this purpose, a priority scheme is provided to take care of any 1/0 processor state that needs major cycles sooner than its normal turn in the sequence. This priority scheme can be adjusted at the end of each major cycle; that is, every major cycle a test is made to see if the normal priority (sequential processor-state operation) is to be followed, or if an 1/0 processor should be given an out-of-sequence cycle. This action is similar to that of a system that operates on a priority-interrupt system.

#### Storage Protection

This feature provides main storage protection for each of the processor states 5, 6, and 7. A register designated Upper Bounds (UB) and Lower Bounds (LB) is provided for each of these processor states. These registers are accessible only by processor state 4.

Upper and Lower Bounds values are set up by the control program (processor state 4). Each writing access attempted by an instruction executing under processor states 5, 6, or 7 is then checked by the Storage Protection hardware against the UB and LB values for that processor state. If the address falls outside the bounds values, writing is prevented and the control program detects a problem program addressing error.

#### Computer Options

The following paragraphs describe optional features of the 7300 computer.

#### JOB ACCOUNTING

This option comprises eight 32-bit registers, one for each processor state, and an incremental adder. Each time a processor state gets a major cycle, the hardware automatically increases the contents of the associated Job Accounting register by 1. A job accounting register may be read at any time, but any attempt to write into it will reset it to zero.

#### RELOCATION AND PROTECTION

The Relocation and Protection feature provides three functions:

- Allows for relocation of programs without instruction modification

- 2. Extends the addressing capability of the system from 65K to up to one-million bytes

- 3. Provides a comprehensive storage protection scheme for all processor states.

This feature is implemented through the use of a Segment Relocation Table, Protection Matrix, Segment Tag File, and Address Mode Register.

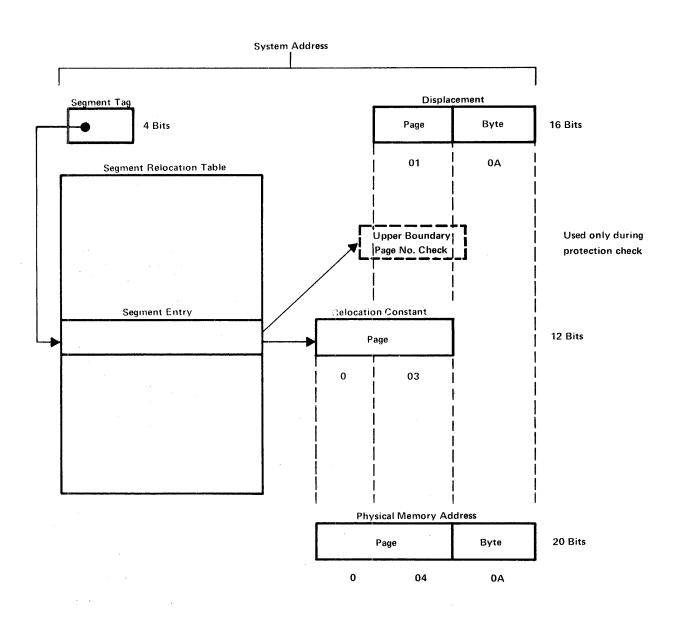

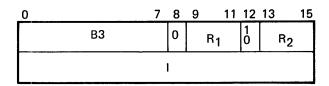

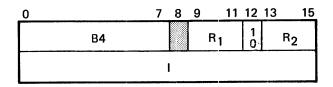

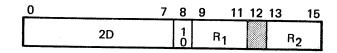

Relocation. Each processor state has a hardware "segment tag" associated with its program address (P) register and with each of its general registers. This segment tag identifies an entry in the Segment Relocation Table, from which a relocation constant or lower boundary page number of the storage segment (or block) is obtained. Each entry in the Segment Relocation Table also contains an upper boundary number for that segment.

The effective address presented by each processor to the relocation and protection hardware is called the system address. The 20-bit system address consists of two parts: a 4-bit Segment Number and a 16-bit displacement within the segment. The displacement consists of an 8-bit Page Number (identifying blocks of 256 bytes each) and an 8-bit byte displacement.

The relocation and protection hardware uses the segment tag for access to the appropriate entry in the Segment Relocation Table. The 16-bit displacement is then added to the relocation constant to form the physical memory address used in the instruction. (The 8-bit displacement is never altered. Figure 2-2.)

The general rule for obtaining a Segment Number is this: if there is a general register involved in the formation of the address, its associated segment tag is used; if there is no general register so involved, the segment tag associated with P-Register is supplied.

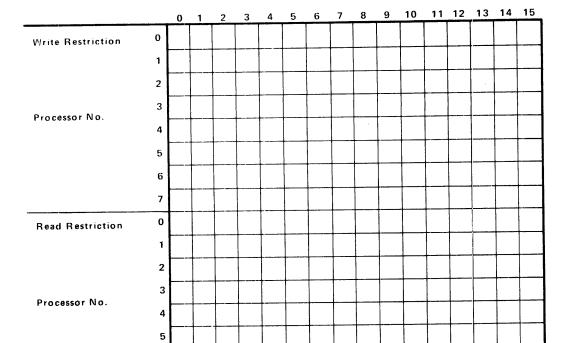

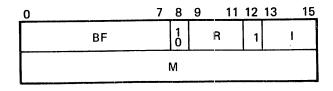

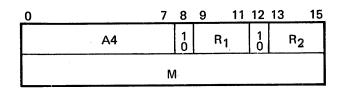

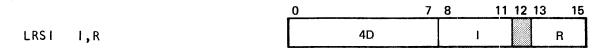

Protection. Storage may be divided into a maximum of 16 segments; access to each is controlled through the Protection Matrix. This matrix is organized as shown in Figure 2-3. Each processor has two rows assigned to it; one for READ and one for WRITE. Access by a processor state for READ or WRITE to a specific segment is allowed only if the bit is 0 in the column for the correct segment corresponding to the row for that processor state.

If access is to be permitted, a check is also performed by the relocation and protection hardware to assure that the page number of the system address displacement does not exceed the "upper bounds" entry in the Segment Relocation Table for that segment. "Upper bounds" is the maximum page number which may be addressed within that segment. If the bounds is exceeded, the instruction will not be executed and a condition code will be set for the processor state.

Control. Control of the Relocation and Protection feature is supported through special machine language instructions and the Address-Mode Register. Access to these is controlled by the control program (processor state 4).

2-6 2999.001

Figure 2-2. Generating Relocation Address

SEGMENT NUMBER

Figure 2-3. Storage Access Protection Matrix

6

2999.001

#### ERROR CORRECTION CODE OPTION

The Error Correction Code (ECC) option corrects single-bit errors, and detects but does not correct double-bit errors made during a storage reference. In either case, an entry is made in the ECC Error Log register.

#### DATA REPRESENTATION

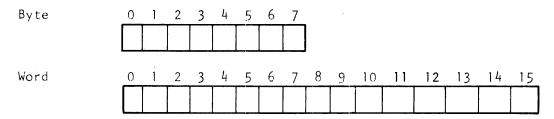

The basic unit of memory for the MEMOREX 7300 processor is an 8-bit byte. The bytes in memory are numbered from 0 to a maximum of 131,072 (128K). The computer transfers two bytes at a time into or out of memory; these two bytes are treated as a unit, called a word. The bits in a byte or word are numbered left to right from 0 through 7 or 0 through 15, respectively.

Data can be represented in any of the following formats: hexadecimal, EBCDIC, binary, and zoned or packed decimal.

#### Hexadecimal Representation

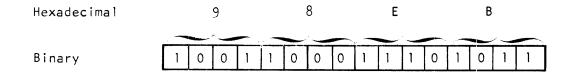

Hexadecimal notation is a system in which four bits are used to represent the decimal values, 0-15. Since the hexadecimal system implies 16 different numbering symbols, this system uses digits 0-9 and letters A, B, C, D, E, and F for decimals 10, 11, 12, 13, 14, and 15, respectively.

Each hexadecimal symbol has a corresponding 4-bit pattern. This system uses every possible combination of the four bits (16 combinations).

For example, the value of each of four bits is shown, representing the equivalents of  $2^3$ ,  $2^2$ ,  $2^1$ , and  $2^0$ .

| 8  | 4  | 2  | 1  |  |

|----|----|----|----|--|

| 23 | 22 | 21 | 20 |  |

|   | Bi | inary | / |             |

|---|----|-------|---|-------------|

| 0 | 1  | 0     | 1 | 4 + 1 = 5   |

| 1 | 0  | 1     | 0 | 8 + 2 = A   |

| 1 | 1  | 1     | 1 | 8+4+2+1 = F |

The following table shows the correlation between decimal, hexadecimal, and binary notation.

| <u>Decimal</u> | <u>Hexadecimal</u> | Binary |

|----------------|--------------------|--------|

| 0              | 0                  | 0000   |

| 1              | 1                  | 0001   |

| 2              | 2                  | 0010   |

| 3              | 3                  | 0011   |

| 4              | 4                  | 0100   |

| 5              | 5                  | 0101   |

| 6              | 6                  | 0110   |

| 7              | 7                  | 0111   |

| 8              | 8                  | 1000   |

| 9              | 9                  | 1001   |

| 10             | Α                  | 1010   |

| 11             | В                  | 1011   |

| 12             | С                  | 1100   |

| 13             | D                  | 1101   |

| 14             | E                  | 1110   |

| 15             | F                  | 1111   |

Using hexadecimal notation, a direct conversion from binary to hexadecimal, or vice-versa, is very easily made.

#### **EBCDIC** Representation

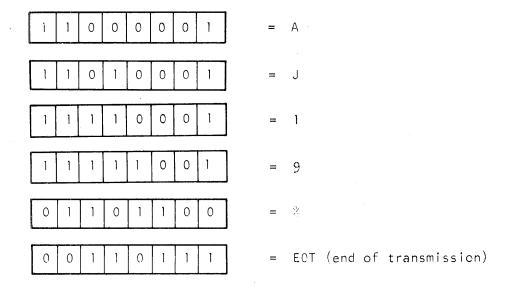

Extended Binary-Coded-Decimal Interchange Code is a system that uses an 8-bit code to represent 256 possible characters (256 possible variations of eight bits). The EBCDIC system not only represents digits 0-9, but also the letters of the alphabet (upper and lower case), all punctuation and arithmetic symbols (such as +-; >=), and some special graphic and control symbols (such as SMM-start of manual message, and EOT-end of transmission).

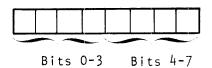

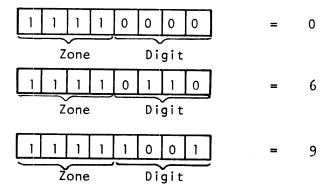

Each character (letter, digit, or other symbol) is represented in one byte (eight bits). The byte is divided into two portions of four bits each:

Some examples of EBCDIC characters and their corresponding 8-bit codes are:

Numeric fields in EBCDIC are in a zoned decimal format.

The following chart shows the entire set of EBCDIC symbols with the hexadecimal equivalents of the zone and digit portions.

Bits 4-7 Hexadecimal and Binary Representation

|   |   |      | 0   | 1           | 2           | 2           | J.         |            |     |     | _    |      |        |     |     | ·   |     |      |

|---|---|------|-----|-------------|-------------|-------------|------------|------------|-----|-----|------|------|--------|-----|-----|-----|-----|------|

|   |   |      | ı   |             |             | 3           | 4          | 5          | 6   | 7   | 8    | 9    | А      | В   | С   | D   | Ε   | F    |

|   | 0 | 0000 | NUL | 0001<br>SOH | 0010<br>STX | 0011<br>ETX | 0100<br>PF | 0101<br>HT |     |     | 1000 | 1001 |        |     |     |     |     | 1111 |

|   |   |      | NOL | 30n         | 317         | EIX         | PF         | н          | LC  | DEL |      |      | SMM    | ۷T  | FF  | CR  | S0  | SI   |

|   | 1 | 0001 | DLE | DC 1        | DC2         | ТМ          | RES        | NL         | BS  | 1 L | CAN  | ЕМ   | СС     | CUI | IFS | IGS | IRS | IUS  |

|   | 2 | 0010 | DS  | SOS         | FS          |             | ВҮР        | LF         | ETB | ESC |      |      | SM     | CU2 |     | ENQ | ACK | BEL  |

|   | 3 | 0011 |     |             | SYN         |             | PN         | RS         | UC  | EOT |      |      |        | CU3 | DC4 | NAK |     | SUB  |

|   | 4 | 0100 | SP  |             |             |             |            |            |     |     |      |      | ¢      |     | <   | (   | +   | ı    |

|   | 5 | 0101 | ક   |             |             |             |            |            |     |     |      |      | !<br>• | \$  | *   | )   | ;   | ~    |

|   | 6 | 0110 | -   | /           |             |             |            |            |     |     |      |      |        | ^   | %   | _   | >   | ?    |

| 1 | 7 | 0111 |     |             |             |             |            |            |     |     |      |      | :      | #   | 0   | ı   | =   | 11   |

| n | 8 | 1000 |     | a           | ь           | С           | d          | е          | f   | g   | h    | i    |        |     |     |     |     |      |

|   | 9 | 1001 |     | j           | k           | 1           | m          | n          | 0   | р   | q    | r    |        |     |     |     |     |      |

|   | Α | 1010 |     |             | S           | t           | u          | V          | W   | ×   | У    | z    |        |     |     |     |     |      |

|   | В | 1011 |     |             |             |             |            |            |     |     |      |      |        |     |     |     |     |      |

|   | С | 1100 |     | Α           | В           | С           | D          | E          | F   | G   | Н    | ı    |        |     |     |     |     |      |

|   | D | 1101 |     | J           | К           | L           | М          | N          | 0   | Р   | Q    | R    |        |     |     |     |     |      |

|   | E | 1110 |     |             | S           | Т           | U          | V          | W   | Х   | Υ    | Z    |        |     |     |     |     |      |

|   | F | 1111 | 0   | 1           | 2           | 3           | 4          | 5          | 6   | 7   | 8    | 9    |        |     |     |     |     |      |

Bits 0-3 Hexadecimal and Binary Representation

#### Binary Representation

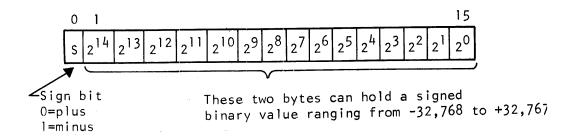

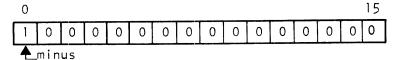

A word (two bytes) in a signed binary format has a sign bit (bit 0) and 15 bits in which to hold a value (bits 1-15). The value of each bit increases from right to left by a power of two.

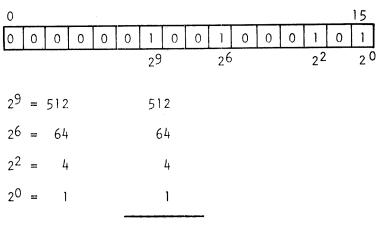

To determine the decimal value of a binary field, the decimal equivalents are added for each bit position that is on (1).

581 = decimal value of field

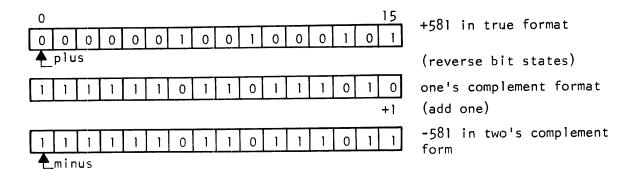

Positive numbers are in the format described in the preceding text; each bit position stands for a specific value. Negative numbers are in a two's complement form. The two's complement of a value is formed by reversing the state of each bit (this is the one's complement form) and then adding 1 to the entire field(this is the two's complement form).

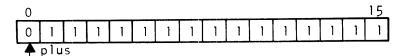

The highest possible number in two's complement form is +32,767.

The lowest possible number in two's complement form is -32,768.

Zoned Decimal Format

In the zoned decimal format, each digit 0-9 is held in one byte. Bits 4-7 of a byte hold the digit 0-9 in the standard binary format; this is called the digit portion of a byte. Bits 0-3 of a byte are always  $1111_{16}$ ; this is called the zone portion of the byte.

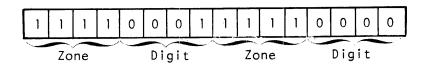

Since each digit requires a byte, a three-digit field requires three bytes, a seven-digit field requires seven bytes, and so forth. The number 10 would occupy two bytes.

The digit portions equal 1 and 0, or 10.

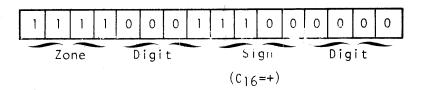

All numeric fields must have a sign, and in the zoned decimal format the first four bits (0-3) of the rightmost byte are used to hold a sign. A hexadecimal C is a plus sign, and a hexadecimal D is a minus sign. The number +10 would appear as follows:

In the zoned decimal format, a byte is required to hold each digit, 0-9. The zone portion of each byte is unused (except for the sign in the rightmost byte). These zoned decimal fields can be packed into a fewer number of bytes if these zones are removed; thus a packed or unzoned decimal format. In the packed format, the 4-bit sign is moved to the last four bits of the rightmost byte.

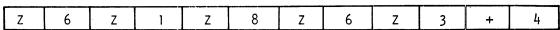

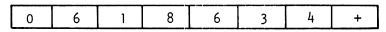

The following illustration shows the number 18,634 in a zoned format and a packed (unzoned) format. Note the difference in placement of the sign. For easier interpretation, the actual bit patterns are not shown.

#### Zoned

| Z    | 1     | Z    | 8     | Z    | 6     | Z    | 3     | +    | 4     |

|------|-------|------|-------|------|-------|------|-------|------|-------|

| Zone | Digit | Zone | Digit | Zone | Digit | Zone | Digit | Sign | Digit |

#### Packed

| 1 | 8        | 6 | 3 | 4 | + |

|---|----------|---|---|---|---|

|   | <u> </u> |   |   | L |   |

Digit Digit Digit Digit Sign

If a field with an odd number of digits is packed, no portion of the packed field is unused. If a field with an even number of digits is packed, however, the first four bits of the packed field are unused, and are filled with zeros.

In the last example, 18,634 was converted from a five-byte zoned field to a three-byte packed field. For the number 618,634, the zoned field requires six bytes and the packed field four bytes. The zoned and packed fields would appear as follows. The unused portion of the leftmost byte of the packed field is considered zero.

#### Zoned

Zone Digit Zone Digit Zone Digit Zone Digit Sign Digit

#### Packed

Zero Digit Digit Digit Digit Digit Sign

In packed decimal format, there are several 4-bit patterns for plus and minus. The following 4-bit patterns, identified in hexadecimal notation, indicate plus or minus.

Plus: F, A, C, E, 0, 2, 4, 6, 7, or 8

Minus: B, D, 1, 3, 5, or 9

#### Addressing

The data involved in an instruction can be in one of three places: in the instruction itself, in a general register, or in main storage. If the data is in the instruction, there really is no addressing; if it is in a general register, the programmer simply provides the register number. But if the data is in main storage, there are several techniques for defining the location of that data to the computer. The following material discusses the basic addressing techniques and how these techniques are combined. For ease of presentation, all numbers in the object formats in this section are decimal numbers.

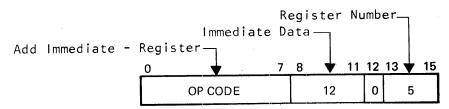

#### IMMEDIATE DATA

Data held in the instruction is called immediate data, since it is immediately available to the computer; there is no addressing involved.

The immediate value 12 (decimal) will be added to the contents of general register 5. (Bit 12 is 0, indicating direct addressing of register 5.)

Note: Bits 8 and 12 have a special use for many instructions, this is described in the discussions of direct and indirect addressing in this section.

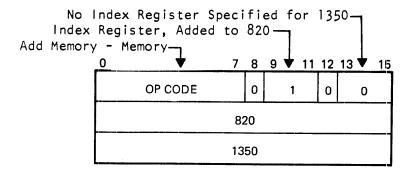

#### TNDEXING

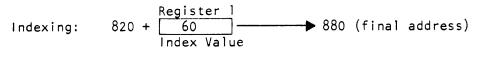

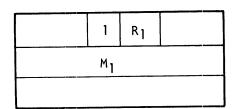

Indexing is an addressing technique in which a memory address is added to the contents of a general register (1-7) to form the address of data used in the instruction. A general register used for indexing is called an index register.

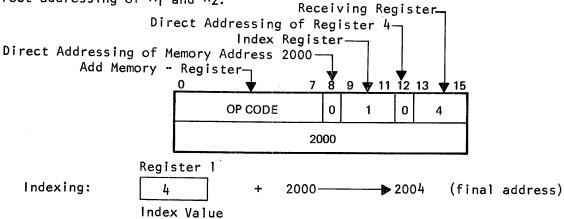

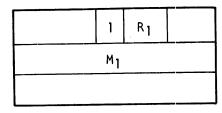

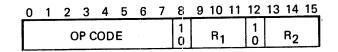

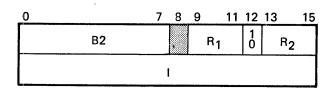

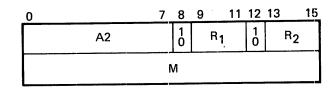

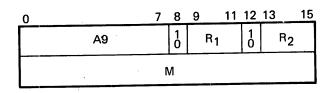

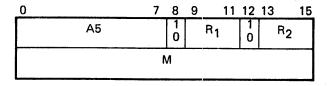

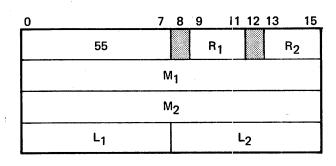

Indexing is optional for most of the 4-, 6-, and 8-byte instructions. For instructions that allow indexing the first register indicated  $(R_1)$  in an instruction is associated with the first memory address  $(M_1)$ , and the second register  $(R_2)$  is associated with the second memory address  $(M_2)$ . The following example, shows how indexing applies to a 6-byte instruction. Instruction contents in this and subsequent examples are expressed in decimal.

Addition: 880

$$27$$

+ 1350  $143$   $\longrightarrow$  1350  $170$  Data

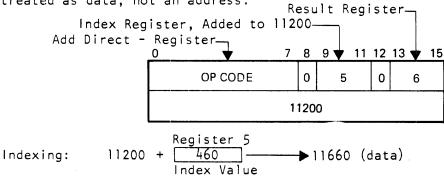

Several instructions use indexing to form a value used in the instruction rather than to form an address. These instructions add an immediate value to the contents of the index register; the result is treated as data, not an address.

#### DIRECT ADDRESSING

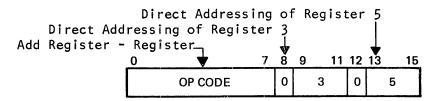

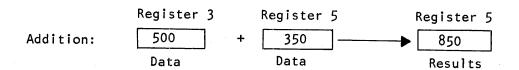

A direct address is one (a memory address or a register number) that is either the final address of the data used in the instruction, or an address used for indexing. A direct address is not the address of a second address.

Direct addressing is indicated by bits 8 and 12 for instructions in which this technique applies. If the bit is 0 (off), direct addressing is indicated.

In this example, bits 8 and 12 are off. This indicates that the registers identified in the instruction contain the data used in the operation.

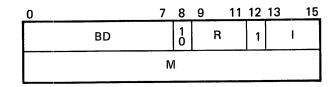

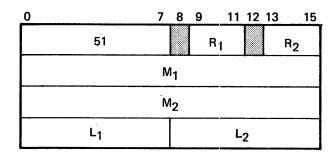

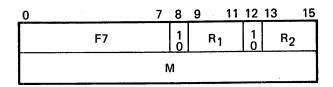

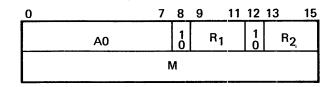

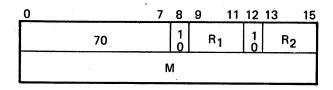

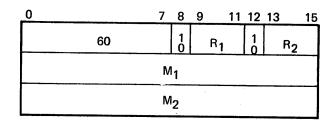

Direct addressing applies to register numbers and memory addresses. For 2-byte instructions, bit 8 is associated with  $R_1$  (identified in bits 9-11) and bit 12 is associated with  $R_2$  (identified in bits 13-15). For 4-byte instructions, bit 8 is associated with  $M_1$  (identified in bits 16-31) and bit 12 is associated with  $R_2$ .  $R_1$  in these instructions is used as an index register, and direct or indirect addressing does not apply to index registers. For 6-byte instructions, bit 8 is associated with  $M_1$  and bit 12 is associated with  $M_2$  (identified in bits 32-47). The 8-byte instructions all use direct addressing - it is a requirement.

The following 4-byte instruction shows an example of indexing and direct addressing of  $M_1$  and  $R_2$ .

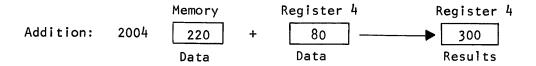

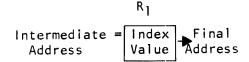

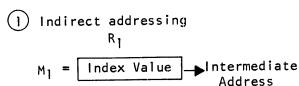

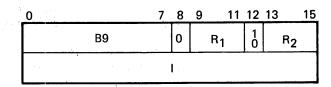

An indirect address (memory address or a register number) is the address of a second address. This second address may be the final address of the data used in the instruction, or it may be an address used for indexing. The second address must always be a memory address; it cannot be a register number. An indirect memory address must be an even-numbered address; the final address may be even or odd-numbered, depending on the instruction used.

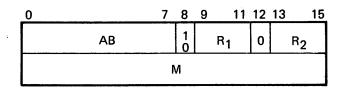

Indirect addressing is indicated by bits 8 and 12 for instructions in which this technique applies. If the bit is 1 (on), indirect addressing is indicated. In the following example, bit 8 is on (1) indicating that the register identified in bits 9-11 contains a memory address, and at that memory address is the data used in the instruction. Bit 12 is off (0) indicating that the register identified in bits 13-15 contains data, not an address of data. The data flow in the example is memory to register.

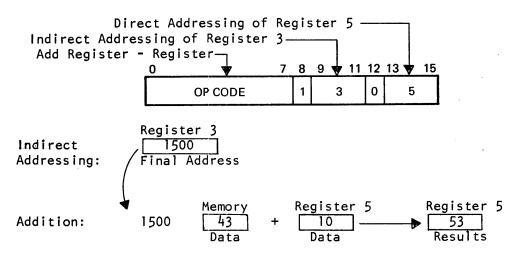

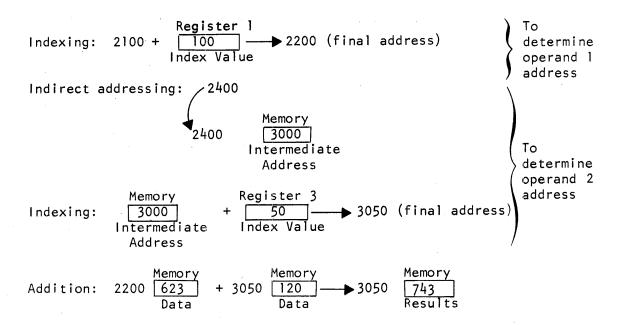

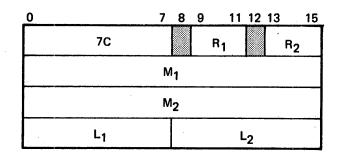

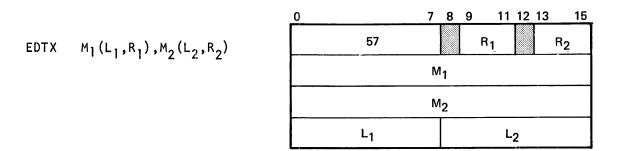

Indirect addressing applies to register numbers and memory addresses in the same way that direct addressing does. Bits 8 and 12 are associated with R1 and R2 for 2-byte instructions, with M1 and R2 for 4-byte instructions, and with M1 and M2 for 6-byte instructions. Indirect addressing is not allowed for 8-byte instructions. The following example of a 6-byte instruction shows how indirect addressing works in combination with indexing.

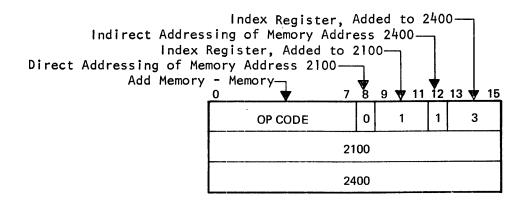

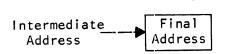

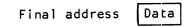

In the preceding example, to determine the operand 2 address, the indirect addressing was resolved, then the indexing was done. This technique is called post-indexing, because the indexing is done after the indirect addressing is resolved. Almost all instructions in which indirect addressing and indexing are allowed use the post-indexing technique. Very few instructions use a pre-indexing technique, in which the indexing is done before the indirect addressing is resolved. The following example shows how post-indexing and pre-indexing differ.

POST-INDEXING

mined by these steps:

Indirect addressing Memory

(2) Indexing

(3) Final address

Final address Data

The address of the operand is deter- The address of the operand is determined by these steps:

Indexing

Memory

(3) Final address

Note: Bits 8 and 12 in the object instructions are used as indicator bits; they indicate something to the computer that the operation code alone cannot do. These bits are not always used to indicate direct or indirect addressing; sometimes they tell the computer more about the operands or the operation itself. When used in such a manner, these bits are called function indicators; they may be turned on by the assembler in some cases and by the programmer in other cases. Function bits are clearly defined for each instruction that uses them in the section Machine Instructions.

All programs used in the computer, whether system, utility, or application programs, have one thing in common: when they are executed they reside in main storage as a series of machine instructions. Machine instructions can be directly executed by the computer; they are the result of a translation of source instructions. The source instructions are in a format that can be easily interpreted by a programmer; the object (machine) instructions are in a format that is easily interpreted by the machine. The following material describes the machine instructions in their object format, as they would appear in main storage.

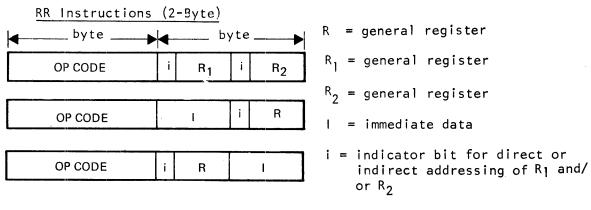

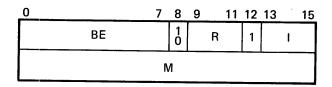

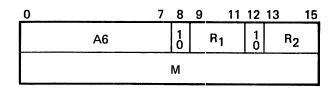

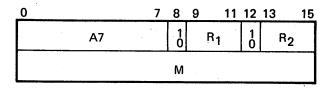

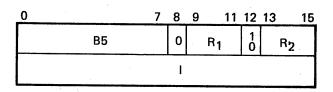

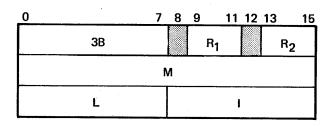

There are four basic machine instruction formats.

- RR Register-to-Register

- RX Register-to-Indexed Storage

- XX Indexed Storage-to-Indexed Storage

- SS Storage-to-Storage

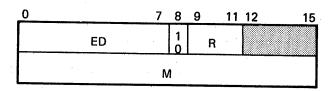

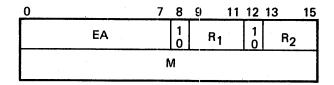

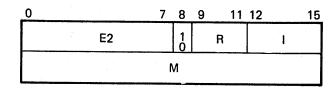

The machine instructions are divided into these four categories on the basis of the instruction length (2, 4, 6, or 8 bytes of 8 bits each) and the type of operations they perform. The most common variations of each type of instruction are illustrated in the following diagrams.

Data flow is 1 --- 2

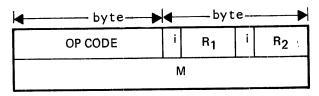

### RX Instructions (4-Byte)

| OP CODE | i | R | l |

|---------|---|---|---|

|         | M |   |   |

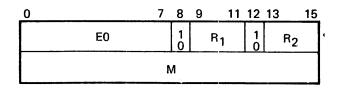

| OP CODE | R <sub>1</sub> | i | R <sub>2</sub> |

|---------|----------------|---|----------------|

|         | ı              |   |                |

$R_1$  = general register for indexing of M or I

$R_2$  = general register

M = memory address

l = immediate data

i = indicator bit, for direct or indirect addressing of M or  $R_2$

Data flow is usually 1 → 2

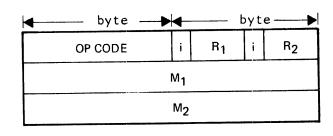

# XX Instructions (6-Byte)

$R_1 = general register for indexing of M_1$

$R_2$ = general register for indexing of  $M_2$

$M_1 = memory address$

$M_2$ = memory address

i = indicator bit, for direct or indirect addressing of  $\rm M_1$  or  $\rm M_2$

Data flow is 1 → 2

#### SS Instructions (8-Byte)

| byte-          | <b>4</b> I     | oyte ——        |  |  |  |  |  |

|----------------|----------------|----------------|--|--|--|--|--|

| OP CODE        | R <sub>1</sub> | R <sub>2</sub> |  |  |  |  |  |

| M <sub>1</sub> |                |                |  |  |  |  |  |

|                | M <sub>2</sub> |                |  |  |  |  |  |

| L <sub>1</sub> | L <sub>2</sub> | 2 .            |  |  |  |  |  |

$R_1$  = general register for indexing of  $M_1$

$R_2$  = general register for indexing of  $M_2$

$M_1 = memory address$

$M_2$  = memory address

$L_1 = field length$

$L_2$  = field length

Data flow is  $l \longrightarrow 2$

An operation code in the first byte of each instruction tells the computer what type of operation to perform. This code is most easily represented as a two-digit hexadecimal number, each digit representing four bits. For instance, an *Add Register - Register* operation would have the following source and object representation. (The object format uses hexadecimal numbers in this example.)

The operation code tells the computer what to do with the data, while the rest of the instruction is concerned with identifying the location or address of the data to be used in the instruction.

# SECTION III MACHINE INSTRUCTIONS

# TABLE OF CONTENTS

# MACHINE INSTRUCTIONS

| INTRODUCTION                 | 3-1  |

|------------------------------|------|

| ARITHMETIC INSTRUCTIONS      | 3-6  |

| BIT-ORIENTED INSTRUCTIONS    | 3-39 |

| BOOLEAN LOGIC INSTRUCTIONS   | 3-48 |

| BRANCHING INSTRUCTIONS       | 3-64 |

| COMPARE INSTRUCTIONS         | 3-93 |

| DATA CONVERSION INSTRUCTIONS | 3-10 |

| DATA TRANSFER INSTRUCTIONS   | 3-12 |

| NO OPERATION                 | 3-14 |

| SERVICE REQUEST              | 3-14 |

| SHIFT INSTRUCTIONS           | 3-15 |

# SECTION III MACHINE INSTRUCTIONS

#### INTRODUCTION

This section describes the regular set of machine instructions. The restricted (Control and I/O) instructions are described in  $\underline{\text{Section}}$  IV, Theory of Operations (not included in this version).

The instructions are grouped by function in the following order:

- 1. Arithmetic

- 2. Bit-Oriented

- 3. Boolean Logic

- 4. Branching

- 5. Compare

- 6. Data Conversion

- 7. Data Transfer

- 8. No Operation

- 9. Service Request

- 10. Shift

Within each group, the individual instructions are arranged alphabetically by name. Each instruction description includes the source format, the object format, a discussion of the operation involved, and an example. The following rules apply to the instruction descriptions.

- Most instructions must address even bytes in memory; the rest can address even or odd bytes. The instructions which can address even or odd bytes are identified by a bullet following the instruction name (such as, Compare Packed Decimal ●).

- The address of a memory field refers to the leftmost byte of that field.

- A word is defined as two bytes (8 bits in a byte); the bit positions in a word are numbered left to right (0-15).

- The operand fields of the instructions may be fixed or variable in length. Fixed-length operand fields may be one byte, one word (2 bytes), or two words (4 bytes) in length. Variable-length fields may range from 0-255 bytes.

- The operand fields for some instructions are contained in two registers or two words; however, only one register or word is addressed by the instruction. If the address of the operand is R, the operand may be at R and R+1 (plus one register) or R and R-1 (minus one register). For example: if R=5, the operand field may be in 5 and 6 or 4 and 5.

- If the address of the operand is M, the operand may be at M and M+1 (plus one word) or M and M-1 (minus one word). For example: if M=1324, the operand field is a four-byte field occupying locations 1324, 1325, 1326, and 1327 (for M and M+1) or 1322, 1323, 1324, and 1325 (for M and M-1).

- The Overflow bit (bit 0) in the Condition register is set if the results of a binary add or subtract exceed the limits of a signed one-word or two-word result field. Specifically, overflow is indicated if results  $> 2^{n-1}-1$  or results  $< -2^{n-1}$  (where n=16 or 32 bits).

- The Link bit (bit 3) in the Condition register is set if the results of a binary add or subtract exceed the limits of an unsigned one-word or two-word result field. Specifically, link is indicated if results  $> 2^{n}-1$  for an add (where n=16 or 32 bits), or if operand  $1 \ge 0$  operand 2 for a subtract.

The source and object formats of the operands are defined using the following symbols.

| OP Code | The | operation  | codes       | are | presented | in | hexadecimal |

|---------|-----|------------|-------------|-----|-----------|----|-------------|

|         | (00 | through FF | ´) <b>.</b> |     |           |    |             |

R A general register number, 0-7. The register may be used as a sending or receiving field or as an index register.

M A memory address, 0-65,535.

An immediate value; the value varies depending on the instruction. The value may represent an amount used in an arithmetic operation, a shift count, a skip count, or a bit number.

L A field length, usually 0-255, but longer for some instructions. For certain instructions the length of an operand field may be defined in the instruction. The length specified in the instruction overrides any previous field length definition, but is only in effect for that instruction.

An R, M, I, or L in source operand 1 is identified as  $R_1$ ,  $M_1$ ,  $I_1$ , or  $I_1$ ; in source operand 2 they are identified as  $R_2$ ,  $M_2$ ,  $I_2$ , or  $I_2$ . If there is only one operand, no number is used (R, M, I, or L). These symbols are numbered so that they can be referred to easily (distinguishing between  $R_1$  and  $R_2$  in the same instruction) and to make clear the location of these fields in the object format.

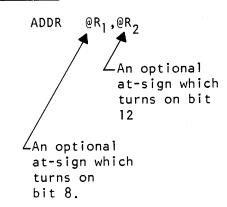

An at-sign (@) in a source operand indicates indirect addressing, an optional feature. For the instructions in which a register is a sending or receiving field, the at-sign indicates indirect addressing for  $\mathsf{R}_1$  or  $\mathsf{R}_2$ . If a field in memory is the sending or receiving field, the at-sign indicates indirect addressing of  $\mathsf{M}_1$  or  $\mathsf{M}_2$ .

Index registers and field lengths are optional; they are enclosed in parentheses in a source operand.

The two major operand fields are separated by a comma.

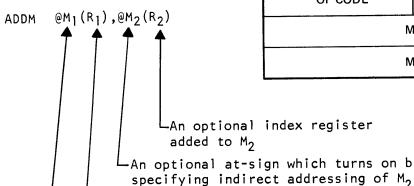

The following examples show how the source and object formats are illustrated. The at-sign and any designations in parentheses are almost always optional; if any of these designations are not optional, this fact will be noted. Data flow is usually operand 1 to operand 2, unless otherwise stated.

Data flow is 1 to 2.

The variations of this instruction are as follows: data flow may be register to register, register to memory, memory to register, or memory to memory, depending on the use of indirect addressing.

$$ADDR \begin{cases} R_1 & R_2 \\ R_1 & R_2 \end{cases}$$

There are  $2 \times 2 = 4$  possible variations of this instruction.

#### EXAMPLE 2

-An optional index register added to Mo -An optional at-sign which turns on bit 12,

-An optional index register added to M<sub>1</sub>

An optional at-sign which turns on bit 8, specifying indirect addressing of M<sub>1</sub>

The data flow of this instruction is always memory to memory. Any variation of operand 1 can be used with any variation of operand 2.

Timing formulas for all instructions are included as a part of Appendix C to this document.

# ARITHMETIC INSTRUCTIONS

| Mnemonic Code | <u>Name</u>                     |

|---------------|---------------------------------|

| ADDD          | Add Direct                      |

| ADDI          | Add Immediate                   |

| ADDM          | Add Memory - Memory             |

| ADD           | Add Memory - Register           |

| ADDK          | Add Packed Decimal •            |

| ADDR          | Add Register - Register         |

| ADDT          | Add Two-Word                    |

| DIVD          | Divide Direct                   |

| DIVI          | Divide Immediate                |

| DIVM          | Divide Memory - Memory          |

| DIV           | Divide Memory - Register        |

| DIVK          | Divide Packed Decimal           |

| DIVR          | Divide Register - Register      |

| MPYD          | Multiply Direct                 |

| MPYI          | Multiply Immediate              |

| MPYM          | Multiply Memory - Memory        |

| MPY           | Multiply Memory - Register      |

| MPYK          | Multiply Packed Decimal         |

| MPYR          | Multiply Register - Register    |

| SUBD          | Subtract Direct                 |

| SUBI          | Subtract Immediate              |

| SUBM          | Subtract Memory - Memory        |

| SUB           | Subtract Memory - Register      |

| SUBK          | Subtract Packed Decimal $ullet$ |

| SUBR          | Subtract Register - Register    |

| SUBT          | Subtract Two-Word               |

| ZADK          | Zero and Add                    |

3-6

2999.001

ADDD  $I(R_1), @R_2$

<u>FUNCTION</u>: Performs a binary addition of a one-word immediate value\* and a one-word field in a general register or in memory.

OPERAND 1: A 16-bit immediate signed value in bits 16-31 of the instruction; the value may range from -32,768 to +32,767.

\*Indexing may be specified for operand l. In this case, operand l is derived by adding the I value and the general register contents specified by  $R_{\parallel}$ ; no check for overflow or link is made during the indexing.

$\frac{\text{OPERAND 2}}{\text{in memory}}$ : A one-word field in the general register specified by  $R_2$  or

<u>RESULTS</u>: The resulting sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1-2 and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than 65,535.

EXAMPLE: ADDD 15000(2),3

The immediate value of 15,000 is modified by the contents of register 2 and added to the value in register 3. The sum remains in register 3.

If @ (indirect addressing) is specified, register 3 contains a memory address.

Add Immediate

ADDI I,@R

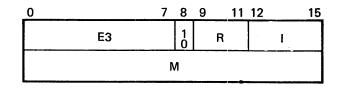

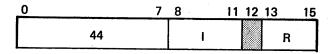

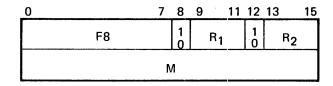

| 0  | 7 | 8 | 11 | 12     | 13 | 15 |

|----|---|---|----|--------|----|----|

| 32 |   |   | ļ  | 1<br>0 | R  |    |

<u>FUNCTION</u>: Performs a binary addition of a 4-bit immediate value and a one-word field in a general register or in memory.

$\underline{\text{OPERAND }}_1$ : A 4-bit unsigned value located in bits 8-11 of the instruction; the value may range from 0-15. The I value is added to operand 2 in bit positions 12-15 with bits 0-11 zeros.

OPERAND 2: A one-word field in the general register specified by R or in memory if indirect addressing is used, bit 12=1.

<u>RESULTS</u>: The resulting sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1-2 and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than 65,535.

EXAMPLE: ADDI 10,@4

The immediate value of 10 is added to the operand at the memory address specified in register 4, at which address the sum is also placed.

If @ (indirect addressing) is not specified, the register contains an operand and subsequent sum, rather than an operand address.

Add Memory - Memory

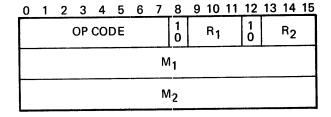

ADDM  $@M_1(R_1), @M_2(R_2)$

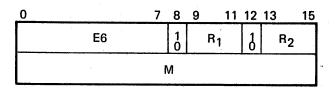

| 0              |    | 7 | 8  | 9              | 11 | 12     | 13             | 15 |

|----------------|----|---|----|----------------|----|--------|----------------|----|

|                | 62 |   | 10 | R <sub>1</sub> |    | 1<br>0 | R <sub>2</sub> |    |

| M <sub>1</sub> |    |   |    |                |    |        |                |    |

|                |    | M | 2  |                |    |        |                |    |

FUNCTION: Performs a binary addition of two one-word fields in memory.

<u>OPERAND 1</u>: A one-word field in memory. Addressing options to the base address  $M_1$  include indexing  $(R_1)$ , indirect addressing (bit 8=1), or a combination of both.

OPERAND 2: Same as operand 1 except use  $M_2$ ,  $R_2$ , and bit 12=1.

<u>RESULTS</u>: The resulting sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1-2 and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than 65,335.

EXAMPLE: ADDM @HERE(3),@TAG(2)

<code>@HERE(3)</code> identifies a 16-bit operand which is added to another operand identified by @TAG(2). The subsequent sum is located at the address specified at @TAG(2).

ADD  $@M(R_1), @R_2$

<u>FUNCTION</u>: Performs a binary addition of a one-word field in memory and a one-word field in a general register or in memory.

<u>OPERAND 1</u>: A one-word field in memory. Addressing options to the base address M include indexing  $(R_1)$ , indirect addressing (bit 8=1), or a combination of both.

$\underline{\text{OPERAND 2}}$ : A one-word field in the general register specified by  $R_2$  or in memory if indirect addressing is used, bit 12=1.

<u>RESULTS</u>: The resulting sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1-2 and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than 65,535.

#### EXAMPLE: ADD TAG(5),7

A 16-bit operand identified by TAG(5) is added to the contents of register 7.

Although not specified in the example, @ (indirect addressing) can be applied to both operators.

ADDK  $M_1(L_1,R_1), M_2(L_2,R_2)$

| 0              |                | 7 | 8 | 9 | 11             | 12 13 | 15             |

|----------------|----------------|---|---|---|----------------|-------|----------------|

|                | 52             |   |   |   | R <sub>1</sub> |       | R <sub>2</sub> |

| M <sub>1</sub> |                |   |   |   |                |       |                |

| M <sub>2</sub> |                |   |   |   |                |       |                |

|                | L <sub>1</sub> |   |   |   | Į              | -2    |                |

$\overline{\text{FUNCTION}}\colon$  Performs a signed decimal addition, proceeding from right to left, of the two packed decimal fields in memory. The field lengths L\_1 and L\_2 may vary from 0-255 bytes.

$\frac{\text{OPERAND 1}}{\text{bytes, is}}$ : A packed decimal field in memory. The field length, 0-255 bytes, is specified in the L  $_{l}$  field of the instruction. The operand address indicated by M  $_{l}$  may be indexed (R  $_{l}$ ), but indirect addressing is not allowed. The effective address points to the most significant bytes of the decimal field.

$\frac{\text{OPERAND 2}}{\text{bytes}}$ : A packed decimal field in memory. The field length, 0-255 bytes, is specified by the L $_2$  value in the instruction. The operand address indicated by M $_2$  may be indexed (R $_2$ ), but indirect addressing is not allowed. The effective operand address points to the most significant bytes of the decimal field.

RESULTS: The resulting decimal sum resides at the operand 2 location. The following conditions can occur, depending on the values of  $L_1$  and  $L_2$ .

- If L  $_1$  is greater than L  $_2$  and the difference between L  $_1$  and L  $_2$  contains significant data, bit 0 of the Condition register is set.

- If  $L_1 = 0$  and  $L_2 = 0$ , bit 3 of the Condition register is set.

- If  $L_1 = 0$ , an add of zero is assumed.

- If L<sub>2</sub> is greater than L<sub>1</sub>, zeros are used to make up the difference in field lengths.

The Condition register is also affected as follows:

- Bit 0 is set if significant data is lost; bits 1-7 are cleared.

- Bits 1 and 5 are set if results are plus; bits 0, 2-4, and 6-7 are cleared.

- Bits 2 and 6 are set if results are minus; bits 0-1, 3-5, and 7 are cleared.

- Bits 3 and 7 are set if results are zero; bits 0-2, and 4-6 are cleared.

EXAMPLE: ADDK FIELD2(10,5),FIELD1(12,6)

A 10-byte packed field identified by FIELD2(10,5) is added to a 12-byte packed field identified by FIELD1(12,6). Had the field lengths been reversed (that is, trying to add the larger field to the smaller) and the overlap contains significant (non-zero) bytes, bit 0 of the Condition register is set to indicate lost data (an incorrect add).

Add Register - Register

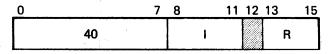

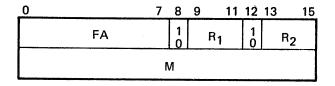

ADDR @R<sub>1</sub>,@R<sub>2</sub>

| 0  | 7 | 8      | 9              | 11 | 12     | 13 1           | <u>5</u> |

|----|---|--------|----------------|----|--------|----------------|----------|

| 22 |   | 1<br>0 | R <sub>1</sub> |    | 1<br>0 | R <sub>2</sub> |          |

<u>FUNCTION</u>: Performs a binary addition of two one-word fields; either field may be in a general register or in memory.

$\underline{\text{OPERAND 1}}\colon$  A one-word field in the general register specified by R\_1 or in memory if indirect addressing is used, bit 8=1.

$\underline{\text{OPERAND 2}}$ : A one-word field in the general register specified by R<sub>2</sub> or in memory if indirect addressing is used, bit 12=1.

<u>RESULTS</u>: The resulting sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than +32,767 or less than -32,768.

- Bits 1-2 and 4-7 are cleared.

- Bit 3 (link) is set if the result is more than 65,535.

EXAMPLE: ADDR @4,@1

In this example, both source operands specify indirect addressing; therefore, register 4 and register 1 contain memory addresses of operands. The operation adds the operand found through register 4 to the operand found through register 1 (sum remains at the latter location).

Add Two-Word

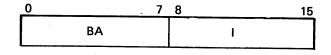

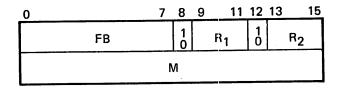

ADDT  $@M(R_1), @R_2$

| 0  | 7 | 8 | 9 11           | 12 | 13             | 15 |  |

|----|---|---|----------------|----|----------------|----|--|

| 72 |   | 0 | R <sub>1</sub> | 10 | R <sub>2</sub> |    |  |

| M  |   |   |                |    |                |    |  |

<u>FUNCTION</u>: Performs a binary addition of a two-word field in memory and a two-word field in two general registers or in memory.

<u>OPERAND 1</u>: A two-word field in memory at the effective address. Addressing options to the base address M include indexing  $(R_1)$ , indirect addressing (bit 8=1), or a combination of both.

<u>OPERAND 2</u>: A two-word field located in two general registers (the most significant bits in the register specified by  $R_2$  and the least significant bits in the register  $R_2+1$ ) or in memory at the address if indirect addressing is used, bit 12=1. (Note: If register 7 is specified by  $R_2$ , the most significant bits are in register 7 and the least significant bits are in register 0.)

The effective address points to the most significant word of the operand.

<u>RESULTS</u>: The resulting sum resides at the operand 2 location. The Condition register is affected as follows:

- Bit 0 (overflow) is set if the result is greater than  $+2^{31}-1$  or less than  $-2^{31}$ .

- Bits 1-2 and 4-7 are cleared.

- Bit 3 (link) is set if the result is greater than  $+2^{32}-1$ .

EXAMPLE: ADDT TAG(1),5

TAG(1) identifies a two-word field which is added to the contents of registers 5 and 6. The two word sum remains in registers 5 and 6.

Although not used in this example, @ can precede each operator to specify indirect addressing.

Divide Direct

DIVD  $I(R_1)$ , @R<sub>2</sub>

$\overline{\text{FUNCTION}}$ : Performs a binary division; the divisor is a one-word immediate value\*, and the dividend is a two-word field in two general registers or in memory.

OPERAND 1: The divisor; a 16-bit immediate signed value in bits 16-31 of the instruction; the value may range from -32,768 to +32,767.

\*Indexing may be specified for operand 1. In this case, operand 1 is derived by adding the I value and the general register contents specified by R<sub>I</sub>; no check for overflow or link is made during the indexing.

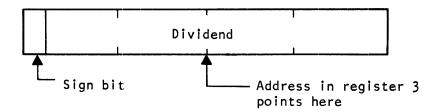

OPERAND 2: The dividend; a 32-bit signed value contained in a two-word field.

If direct addressing is used (bit 12=0), the least significant bits are in the register specified by  $R_2$  and the most significant bits are in the register  $R_2$ -1. (Note: If register 0 is specified by  $R_2$ , the least significant bits of the dividend are in register 0 and the most significant bits are in register 7.)

If indirect addressing is used (bit 12=1), the least significant bits are in memory at the effective address and the most significant bits at the effective address -2.

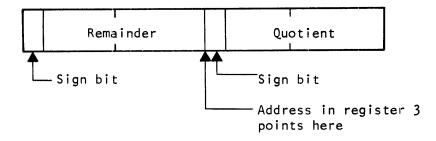

<u>RESULTS</u>: The quotient, a 16-bit signed value, resides at the  $R_2$  register or the effective address of the operand 2 location. The remainder, a 16-bit signed value, resides at the  $R_2$ -l register or effective address -2 of the operand 2 location; the remainder always has the same sign as the dividend.

The Condition register is affected as follows:

- Bit 0 (overflow) is set if the resulting quotient is greater than +32,767 or less than -32,768.

- Bit 0 (overflow) is set if the divisor is 0; the operands are unchanged.

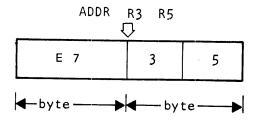

EXAMPLE: DIVD -32255(4),@3

The instruction specifies a binary divide in which the divisor is formed by adding -32,255 to the contents of register 4, and the dividend is found at the address specified in register 3.

As shown in the following illustration, the address specified in register 3 points to the third byte of the 32-bit dividend. This is the 4-byte field in memory that holds the dividend.

After the division, the quotient (including sign bit) is placed in the third and fourth bytes and the remainder (also with sign bit) is placed in bytes one and two. Thus, for subsequent operations, the quotient can be found at the address as specified in register 3. This is the same field after the divide operation.

Divide Immediate

DIVI I,@R

| 0 | ,  | 7 | 8 | 11 | 12 | 13 | <u> 15</u> |

|---|----|---|---|----|----|----|------------|

|   | 39 |   |   | ı  | 0  | R  |            |

<u>FUNCTION</u>: Performs a binary divide; the divisor is a 4-bit immediate value, and the dividend is a two-word field in two general registers or in memory.

OPERAND 1: The divisor is a 4-bit unsigned value in bits 8-11 of the instruction; the value is always positive and may range from 0-15.

OPERAND 2: The dividend; a 32-bit signed value contained in a two-word field.

If direct addressing is used (bit 12=0), the least significant bits are in the register specified by  $R_1$  and the most significant bits are in the register R. (Note: If register 0 is specified by R, the least significant bits of the dividend are in register 0 and the most significant bits are in register 7.)

If indirect addressing is used (bit 12=1), the least significant bits are in memory at the effective address and the most significant bits at the effective address -2.

RESULTS: The quotient, a 16-bit signed value, resides at the R register or the effective address of the operand 2 location. The remainder, a 16-bit signed value, resides at the R-l register or effective address -2 of the operand 2 location; the remainder always has the same sign as the dividend.

The Condition register is affected as follows:

- Bit 0 (overflow) is set if the resulting quotient is greater than +32,767 or less than -32,768.

- Bit 0 (overflow) is set if the divisor is 0; the operands are unchanged.

## EXAMPLE: DIVI 14,@1

Divides a 32-bit field (31 bits plus sign) by 14. The divisor is an absolute value in the instruction, and the dividend is located in memory according to the method described under DIVD. The quotient is stored at the address specified in register 1.

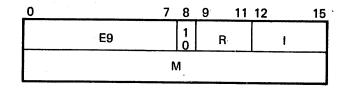

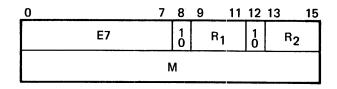

DIVM  $@M_1(R_1), @M_2(R_2)$

| 0  | 7 | 8 | 9              | 11 | 12 | 13             | 15 |

|----|---|---|----------------|----|----|----------------|----|

| 69 |   | 1 | R <sub>1</sub> |    | 10 | R <sub>2</sub> |    |

|    | M | 1 |                |    |    |                |    |

|    | M | 2 |                |    |    |                |    |

<u>FUNCTION</u>: Performs a binary division; the divisor is a one-word field in memory, and the dividend is a two-word field in memory.

<u>OPERAND 1</u>: The divisor; a 16-bit signed value in a one-word field in memory. Addressing options to the base address M<sub>1</sub> include indexing ( $R_1$ ), indirect addressing (bit 8=1), or a combination of both.

<u>OPERAND 2</u>: The dividend; a 32-bit signed value in memory at the effective address and the effective address -1. Addressing options to the base address  $M_2$  include indexing  $(R_2)$ , indirect addressing (bit 12=1), or a combination of both. The effective operand 2 address points to the least significant bits of the dividend.

RESULTS: The quotient, a 16-bit signed value, resides at the effective address of the operand 2 location. The remainder, 16-bit signed value, resides at the effective address -2 of the operand 2 location. The remainder always has the sign of the dividend.

The Condition register is affected as follows:

- Bit 0 (overflow) is set if the resulting quotient is greater than +32,767 or less than -32,768.

- Bit O (overflow) is set if the divisor is zero; the operands are unchanged.

#### EXAMPLE: DIVM @HERE(6),@TAG(4)

TAG(4) and HERE(6) are locations each containing an address of an operand. The operand identified by @TAG(4) is divided by the operand identified by @HERE(6). The dividend is a four-byte field; the address of the dividend, @TAG(4), points to the third byte of the four-byte field. After the division, this address points to the quotient; this address minus two bytes points to the remainder.

DIV @M(R<sub>1</sub>),@R<sub>2</sub>

<u>FUNCTION</u>: Performs a binary division; the divisor is a one-word field in memory, and the dividend is a two-word field in two general registers or in memory.

$\underline{\text{OPERAND 1}}$ : The divisor; a 16-bit signed value in a one-word field in memory. Addressing options to the base address M include indexing (R<sub>1</sub>), indirect addressing (bit 8=1), or a combination of both.

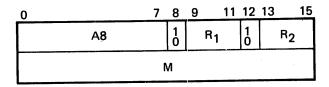

OPERAND 2: The dividend; a 32-bit signed value contained in a two-word field.

If direct addressing is used (bit 12=0), the least significant bits are in the register specified by  $R_2$  and the most significant bits are in the register  $R_2$ -1. (Note: If register 0 is specified by  $R_2$ , the least significant bits of the dividend are in register 0 and the most significant bits are in register 7.)

If indirect addressing is used (bit 12=1), the least significant bits are in memory at the effective address and the most significant bits are at the effective address - 2.

RESULTS: The quotient, a 16-bit signed value, resides at the R2 register or the effective address of the operand 2 location. The remainder, a 16-bit signed value, resides at the R2-1 register or effective address - 2 of the operand 2 location; the remainder always has the same sign as the dividend.

The Condition register is affected as follows:

- Bit 0 (overflow) is set if the resulting quotient is greater than +32,767 or less than -32,768.

- Bit 0 (overflow) is set if the divisor is 0; the operands are unchanged.

$E_4 = 0$  if divisor = 0  $E_4 = 1$  if divisor  $\neq 0$

EXAMPLE: DIV TAG(4),@2

Register 2 contains the address (see DIVD) of the dividend (32-bit operand), and TAG(4) identifies the divisor (16-bit operand). The quotient is at the address in register 2, and the remainder is at that address minus two bytes.

Although not shown in the example, @ (indirect addressing) can be specified for the divisor also.

Divide Packed Decimal

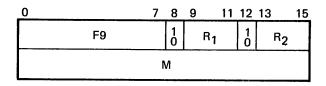

$\overline{\text{FUNCTION}}$ : Operand two, the dividend, is divided by operand one, the divisor, and replaced by the quotient and remainder.

OPERANDS: The quotient field is placed leftmost in the operand two, dividend field. The remainder field is placed rightmost in the same field and has a size equal to the length code,  $L_1$ , of the divisor. The quotient and remainder occupy the entire dividend field, thus the address of the dividend, operand two, is the address of the quotient. The size of the quotient field is  $L_2$ - $L_1$ .

The length code,  $L_1$ , of the divisor must not exceed 127 (253 digits and sign) or be greater than or equal to the length code,  $L_2$ , of the dividend. Otherwise, overflow occurs and the operation is not performed. Also, a length code of zero for the divisor or zero divisor field contents causes overflow and operation suppression. The range of  $L_1$  is 1-127, the range of  $L_2$  is 2-255. The divisor, dividend, quotient and remainder are all signed packed decimal fields right-aligned. The sign of the quotient is determined by the rules of algebra. The sign of the remainder has the same value as the dividend sign. Sign validity checking is not performed. The following rules apply:

plus: hex 0,2,4,6,7,8,A,C,E,F

minus: hex 1,3,5,9,B,D

The preferred sign; plus, X'C', and minus, X'D', are generated. A minus zero quotient or remainder is forced to plus.

The operand fields remain unchanged if overflow occurs.

RESULTS: The operand fields may not overlap. Invalid digits cause undefined results. The following condition register settings can occur:

| Bits 0-7  | Condition                                                                              |

|-----------|----------------------------------------------------------------------------------------|

| 1000 0000 | Overflow, $L_1 > 127$ ; $L_1 \ge L_2$ , $L_1 = 0$ ; or; divisor field contents of zero |

| 0100 0100 | The quotient is greater than zero                                                      |

| 0010 0010 | The quotient is less than zero                                                         |

| 0001 0001 | The quotient is equal to zero                                                          |

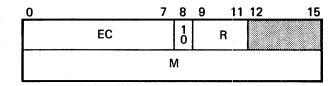

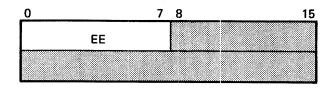

0 7 8 9 11 12 13 15 29 1 R<sub>1</sub> 1 R<sub>2</sub>

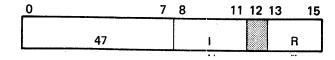

DIVR @R<sub>1</sub>,@R<sub>2</sub>

<u>FUNCTION</u>: Performs a binary division; the divisor is a one-word field in a register or in memory, and the dividend is a two-word field in two adjacent registers or in memory.

$\underline{\text{OPERAND 1}}$ : The divisor; a 16-bit signed value in the general register specified by  $R_1$  or in memory if indirect addressing is used, bit 8=1.

OPERAND 2: The dividend; a 32-bit signed value contained in a two-word field.

If direct addressing is used (bit 12=0), the least significant bits are in the register specified by  $R_2$  and the most significant bits are in the register  $R_2-1$ . (Note: If register 0 is specified by  $R_2$ , the least significant bits of the dividend are in register 0 and the most significant bits are in register 7.)

If indirect addressing is used (bit 12=1), the least significant bits are in memory at the effective address and the most significant bits are in the effective address - 2.

<u>RESULTS</u>: The quotient, a 16-bit signed value, resides at the  $R_2$  register or the effective address of the operand 1 location. The remainder, a 16-bit signed value, resides at the  $R_2$ -1 register or effective address - 1 of the operand 2 location; the remainder always has the same sign as the dividend.

The Condition register is affected as follows:

- Bit 0 (overflow) is set if the resulting quotient is greater than +32,767 or less than -32,768.

- Bit 0 (overflow) is set if the divisor is 0; the operands are unchanged.

EXAMPLE: DIVR @1,@3

A binary divide is performed on a 32-bit (31 plus sign bit) dividend residing at the address specified in register 3. The 16-bit divisor resides at a location specified in register 1; the quotient is stored at the address in register 3; the remainder is stored at that address minus two bytes.

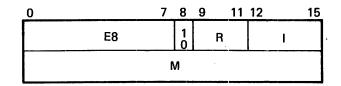

MPYD  $I(R_1), @R_2$

| 0 |    | 7 | 8 | 9              | 11 | 12 | 13 |                | 15 |

|---|----|---|---|----------------|----|----|----|----------------|----|

|   | B8 |   | 0 | R <sub>1</sub> |    | 1  |    | R <sub>2</sub> |    |

|   |    |   | l |                |    |    |    | -              |    |

<u>FUNCTION</u>: Performs a binary multiplication of a one-word immediate value\* and a one-word field in a general register or in memory.

OPERAND 1: The multiplier; a 16-bit immediate signed value in bits 16-31 of the instruction; the value may range from -32,768 to +32,767.

\*Indexing may be specified for operand 1. In this case, operand 1 is derived by adding the 1 value and the general register contents specified by R1; no check for overflow or link is made during the indexing.

$\underline{\text{OPERAND 2}}$ : The multiplicand; a one-word field in the general register specified by R<sub>2</sub> or in memory if indirect addressing is used, bit 12=1.

<u>RESULTS</u>: The product, a 32-bit signed value, resides at the operand 2 location. If operand 2 is in a register, the least significant bits of the product are in the register specified by  $R_2$  and the most significant bits are in register  $R_2$ -1. (Note: If register 0 is specified by  $R_2$ , the least significant bits are in register 0 and the most significant bits are in register 7.) If operand 2 is in memory, the least significant bits of the product are at the effective address and the most significant bits are at the effective address - 2.

EXAMPLE: MPYD 16101(3),@1

A 16-bit (includes sign) multiplicand at the address in register 1 is multiplied by the sum of 16,101 and the contents of register 3. The 32-bit (includes sign bit) product is stored at the address in register 1 minus two bytes.

Multiply Immediate

0 7 8 11 12 13 15 MPYI I,@R

FUNCTION: Performs a binary multiplication of a 4-bit immediate value and a one-word field in a general register or in memory.

OPERAND 1: The multiplier; a 4-bit unsigned field located in bits 8-11 of the instruction; the value is always positive and may range from 0-15.

OPERAND 2: The multiplicand; a one-word field in the general register specified by R or in memory if indirect addressing is used, bit 12=1.

<u>RESULTS</u>: The product, a 32-bit signed value, resides at the operand 2 location. If operand 2 is in a register, the least significant bits of the product are in the register specified by R and the most significant bits are in register R-1. (Note: If register 0 is specified by R, the least significant bits are in register 0 and the most significant bits are in register 7.) If operand 2 is in memory, the least significant bits of the product are at the effective address and the most significant bits are at the effective address - 2.

EXAMPLE: MPYI 15,@6

The multiplicand located at the address specified in register 6 is multiplied by 15. The subsequent product is stored at the address in register 6 minus two bytes.

MPYM  $@M_1(R_1), @M_2(R_2)$

| 0  | 7  | 8  | 9              | 11 | 12     | 13             | 15 |

|----|----|----|----------------|----|--------|----------------|----|

| 68 |    | 10 | R <sub>1</sub> |    | 1<br>0 | R <sub>2</sub> |    |

|    | IV | 11 |                |    |        |                |    |

|    | IV | 12 |                |    |        |                |    |

$\overline{\text{FUNCTION}}$ : Performs a binary multiplication of two one-word fields in memory.

$\underline{\text{OPERAND 1}}$ : The multiplier; a one-word field in memory. Addressing options to the base address M<sub>1</sub> include indexing (R<sub>1</sub>), indirect addressing (bit 8=1), or a combination of both.

$\underline{\text{OPERAND 2}}\colon$  The multiplicand; a one-word field in memory. Addressing options to the base address M2 include indexing (R2), indirect addressing (bit 12=1), or a combination of both.

RESULTS: The product; a 32-bit signed value. The least significant bits reside at the operand 2 effective address, and the most significant bits reside at the operand 2 effective address - 2.

EXAMPLE: MPYM @FRRD(5),@TTM(2)

The location of the multiplicand is defined by @TTM(2), and the location of the multiplier by @FRRD(5). The 32-bit product is stored at the operand 2 address minus two bytes.

Multiply Memory - Register

MPY  $@M(R_1), @R_2$

FUNCTION: Performs a binary multiplication of a one-word field in memory and a one-word field in a general register or in memory.

OPERAND 1: The multiplier; a one-word field in memory. Addressing options to the base address M include indexing  $(R_1)$ , indirect addressing (bit 8=1), or a combination of both.

OPERAND 2: The multiplicand; a one-word field in the general register specified by R2 or in memory if indirect addressing is used, bit 12=1.

<u>RESULTS</u>: The product, a 32-bit signed value, resides at the operand 2 location. If operand 2 is in a register, the least significant bits of the product are in the register specified by R2 and the most significant bits are in register  $R_2$ -1. (Note: If register 0 is specified by  $R_2$ , the least significant bits are in register 7.) If operand 2 is in memory, the least significant bits of the product are at the effective address and the most significant bits are at the effective address - 2.

EXAMPLE: MPY @FRRD(2),@1