112/114 8" OEM Disc Drives Technical Manual

#### Publication Number 112/114.60-00

#### January 1983 edition

This manual is subject to change by Memorex at any time without notice and is provided on an as-is basis to the customer. The data in this manual is up-to-date relative to the edition date and Memorex makes no warranty, expressed or implied, with regard to its accuracy of completeness.

The information in this publication is subject to periodic revisions and to updates by Publications Bulletins. A bulletin is identified as Publication Number 112/114.60-00XX, where "XX" equals "01" for the first bulletin released.

To request copies of this publication or any bulletin, send a Supplies Requisition (form number 7020) using the publication number, to: Memorex Corporation, Marketing Distribution Center, San Tomas at Central Expressway, Santa Clara, California 95052.

A readers' comments form is provided at the back of this publication. If the form has been removed, please send comments to Memorex Corporation, Department 6313, M/S 14-32, San Tomas at Central Expressway, Santa Clara, California 95052.

# Copyright © 1983 MEMOREX CORPORATION ALL RIGHTS RESERVED

### **Preface**

This manual is for customer engineers who handle 112/114 disk drives. It describes how to operate, handle and maintain the equipment.

This manual consists of the following ten sections.

Section 1: General Description

Section 2: Operation

Section 3: Installation and Checkout

Section 4: Theory of Operation

Section 5: Troubleshooting

Section 6: Maintenance

Section 7: Spare Parts

Section 8: IC Detail

Section 9: Parts List (To Be Supplied)

Section 10: Schematics

## **Table of Contents**

|            |                                              | Page |

|------------|----------------------------------------------|------|

| 1.         | GENERAL DESCRIPTION                          | 1-1  |

| 1.1        | GENERAL                                      | 1-1  |

| 1.1.1      | General                                      | 1-1  |

| 1.1.2      | Features                                     | 1-1  |

| 1.2        | SPECIFICATIONS                               | 1-2  |

| 1.2.1      | Environmental Condition of Installation Site | 1-2  |

| 1.2.2      | Power Source Specifications                  | 1-3  |

| 1.2.3      | Performance                                  | 1-6  |

| 1.2.4      | Reliability                                  | 1-7  |

| 1.3        | EXTERNAL APPEARANCE                          | 1-8  |

| 2.         | OPERATION                                    | 2-1  |

| 2.1        | GENERAL                                      | 2-1  |

| 2.2        | POWER ON/OFF SEQUENCE                        | 2-1  |

| 3.         | INSTALLATION AND CHECKOUT                    |      |

| 3.<br>3.1  | GENERAL                                      |      |

| 3.1        | UNPACKING                                    |      |

| 3.2<br>3.3 | VISUAL INSPECTION                            | 3-1  |

| 3.4        | MOUNTING                                     |      |

| 3.4.1      | Installation in Locker                       | 3-3  |

| 3.4.2      | Securing for Transportation                  | 3-4  |

| 3.4.3      | Service Area                                 | 3-5  |

| 3.5        | CABLES                                       | 3-6  |

| 3.5.1      | Cable and connector Specifications           | 3-6  |

| 3.5.2      | Cable Connections                            | 3-7  |

| 3.6        | SWITCH ARRANGEMENT                           | 3.9  |

| 3.6.1      | Drive Select (Device Number Selection)       | 3-9  |

| 3.6.2      | Seek Complete                                | 3-9  |

| 3.6.3      | Sector/Byte Clock                            | 3-10 |

| 3.6.4      | Sector During the Generation of Index        | 3-10 |

| 3.6.5      | Write/Read Data, Write/PLO Clock             | 3-11 |

| 3.6.6      | Assigning the Number of Sectors              | 3-11 |

| 3.6.7      | Delay SKC                                    | 3-14 |

| 3.6.8      | Controlling the Basic Drive Select Signals   | 3-15 |

| 3.6.9      | Timing Margin Measurement Switch             | 3-15 |

|            | Timing Specification Selection               | 3-16 |

| 3.6.11     | Media Error                                  | 3-17 |

| 4.         | THEORY OF OPERATION                          | 4-1  |

| 4.1        | GENERAL                                      | 4-1  |

| 4.2        | OPERATION OF MECHANICAL PORTION              | 4-1  |

| 4.2.1      | Disk Enclosure                               | 4-1  |

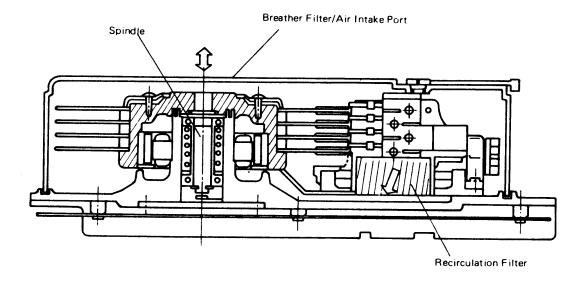

| 4.2.2      | Spindle                                      | 4-2  |

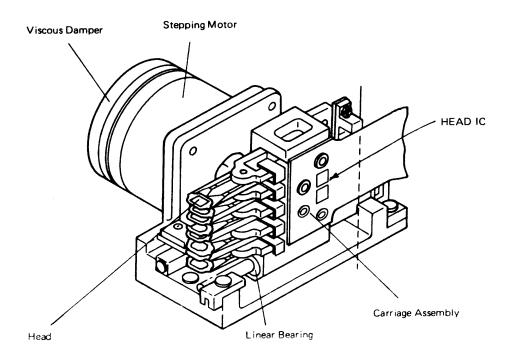

| 4.2.3      | Carriage Assembly                            | 4-3  |

| 4.2.4      | Air Circulation in DE                        | 4-4  |

| 4.3        | MAGNETIC HEADS AND RECORDING MEDIA           | 4-5  |

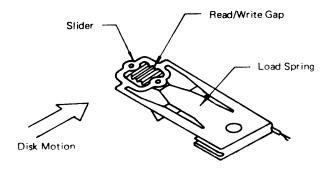

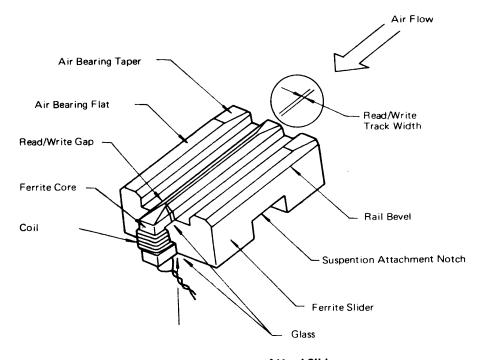

| 4.3.1      | Magnetic Heads                               | 4-5  |

| 4.3.2      | Recording Media (Magnetic Disk)              | 4-6  |

| 4.3.3      | Head and Surface Configuration               | 4-6  |

| 4.3.4      | Clock Track Format                           | 4-6  |

| 4.4        | FORMAT                                       | 4-8  |

| 4.4.1      | General                                      | 4-8  |

| 4.4.2      | Track Format                                 | 4-8  |

| 4.4.3      | Detail of The Format                         | 4-8  |

|                |                                              | Pag        |

|----------------|----------------------------------------------|------------|

| 4.5<br>4.5.1   | INTERFACE                                    |            |

| 4.5.1<br>4.5.2 | General                                      |            |

| 4.5.3          | Signal Lines                                 |            |

| 4.5.4          | Timing Specifications                        |            |

| 4.5.5          | Format Timing Specification                  |            |

| 4.5.6          | Driver/Receiver                              |            |

| 4.5.7          | Pin Assignment in Connector                  |            |

| 4.6            | ELECTRIC CIRCUIT OPERATION                   |            |

| 4.6.1          | Block Diagram                                | 4-1        |

| 4.6.2          | Start/Stop Circuit                           | 4-1        |

| 4.6.3          | DC Spindle Motor Driving Circuit             | 4-2        |

| 4.6.4          | DC Spindle Motor Controller                  |            |

| 4.6.5          | Unit Select Operation                        |            |

| 4.6.6          | SEEK Control                                 |            |

| 4.6.7          | Stepper Driving Circuit                      |            |

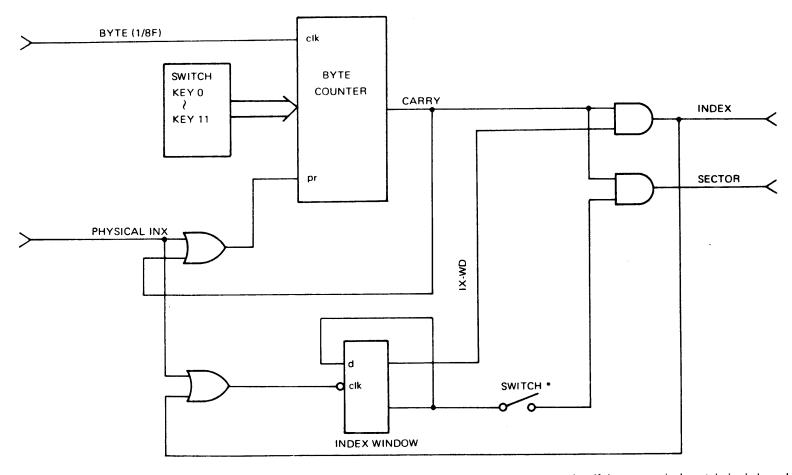

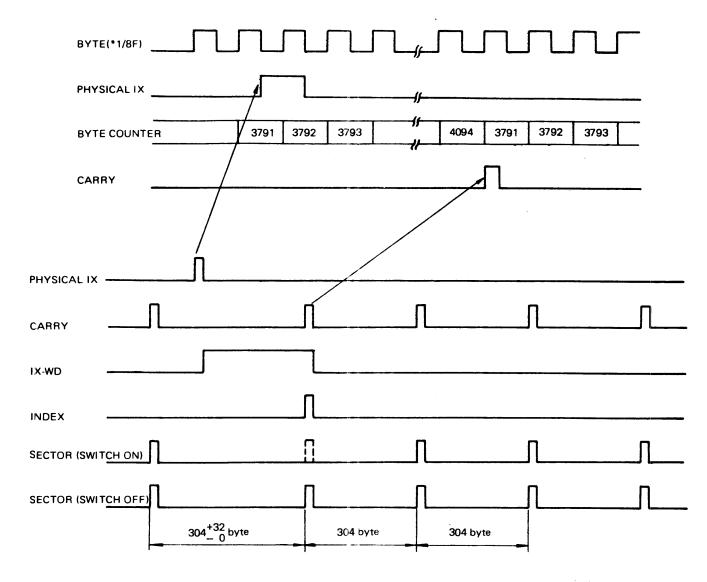

| 4.6.8          | Index and Sector Generation Circuit          |            |

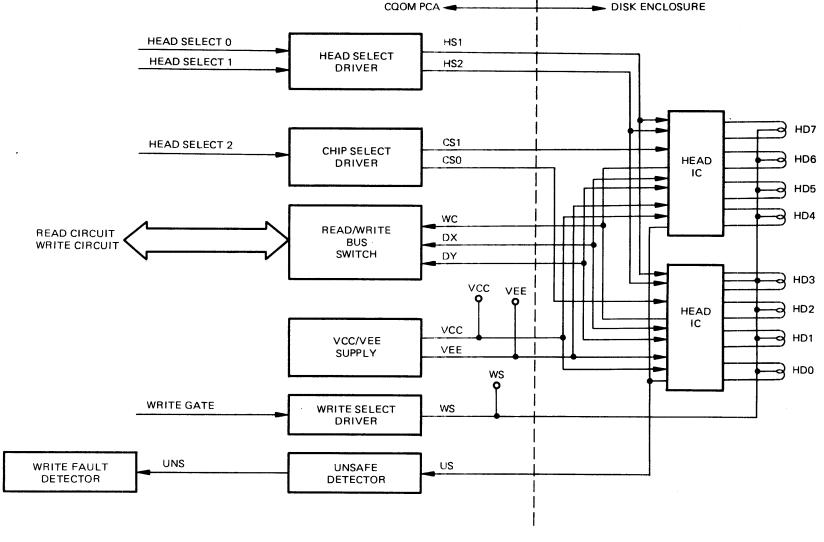

| 4.6.9          | Read/Write Circuit                           |            |

| 5.             | TROUBLESHOOTING                              |            |

| 6.             | MAINTENANCE                                  |            |

| 6.1            | GENERAL                                      |            |

| 6.2            | CHECK OF THE CONTROL CIRCUIT                 |            |

| 6.2.1          | General                                      | 6-1        |

| 6.2.2          | Confirming the Switch Settings               | 6-1        |

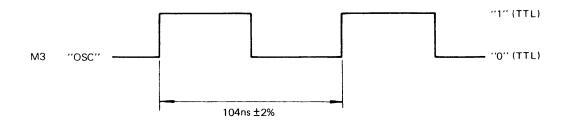

| 6.2.3          | Check of Standard Frequency Oscillator       |            |

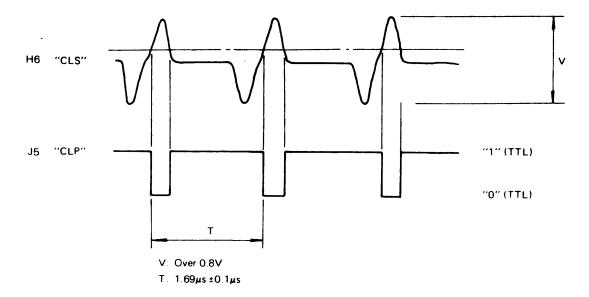

| 6.2.4<br>6.2.5 | Check of Clock Signal                        | 6-2        |

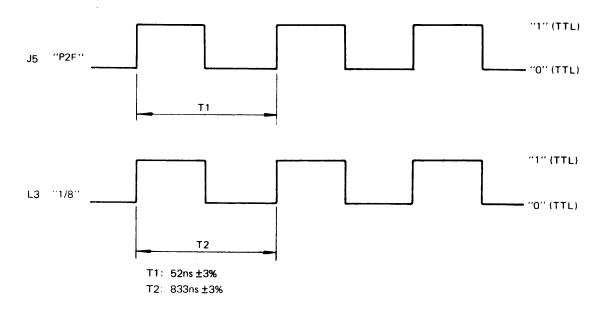

| 6.2.6          | Inspection of PLO Circuit                    |            |

| 6.2.7          | Inspection of VFO Circuit                    |            |

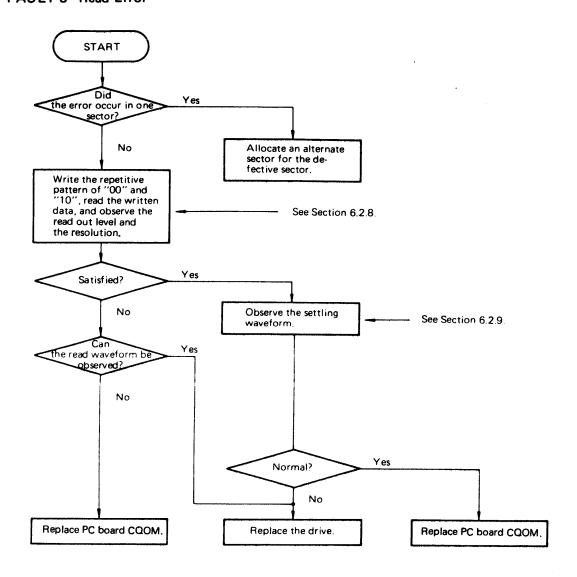

| 6.2.8          | Observation of the Read Waveform             | 6.4        |

| 6.2.9          | Check of the Settling Waveform after Seeking |            |

| 7.             | SPARE PARTS                                  |            |

|                |                                              |            |

| 8.             | IC DETAIL                                    |            |

| 8.1            | OUTLINE                                      |            |

| 8.2            | LOGIC CONVENTION AND SYMBOLOGY               |            |

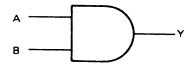

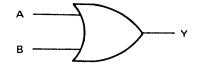

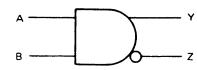

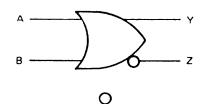

| 8.2.1          | TTL Logic                                    |            |

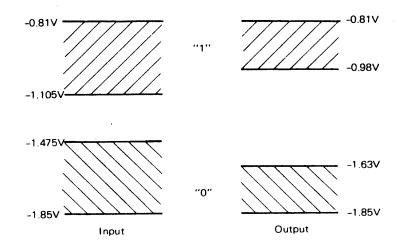

| 8.2.2<br>8.2.3 | ECL Logic                                    | 8-3        |

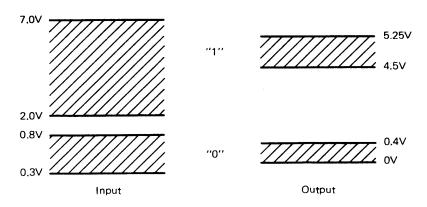

| 8.2.4          | CMOS Logic                                   | 8-3<br>8-4 |

| 8.3            | Logic Symbology SPECIAL IC's                 | 8-5        |

| 8.4            | IC INTERCHANGEABILITY                        | 8-9        |

| 8.4.1          | TTL IC Interchangeability                    | 8-9        |

| 8.4.2          | ECL                                          | 8-1        |

| 8.4.3          | Linear IC                                    | 8-1        |

| 8.4.4          | CMOS                                         | 8-1        |

| 8.4.5          | Special IC's                                 | 8-1        |

| 9.             | PARTS LIST (To Be Supplied)                  | 9-1        |

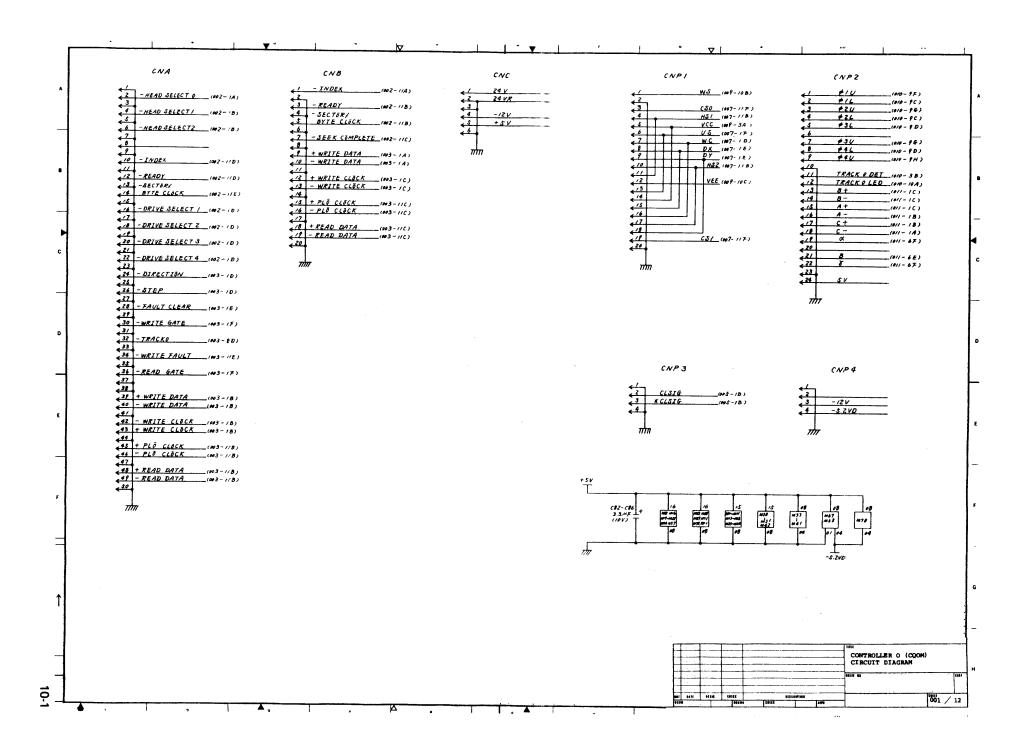

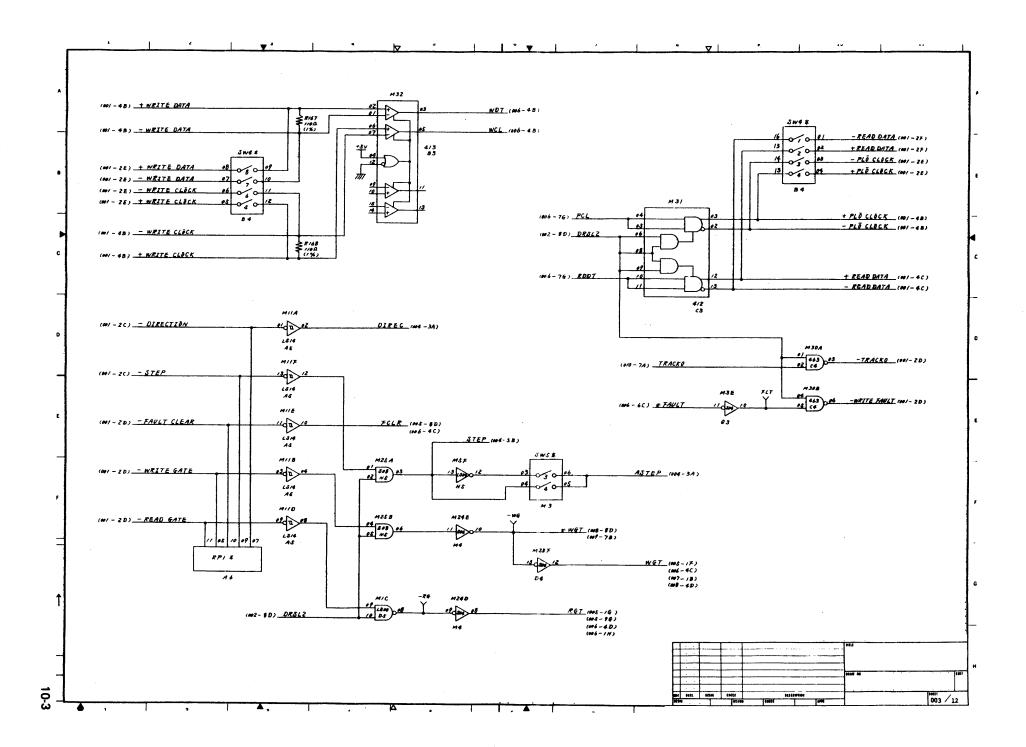

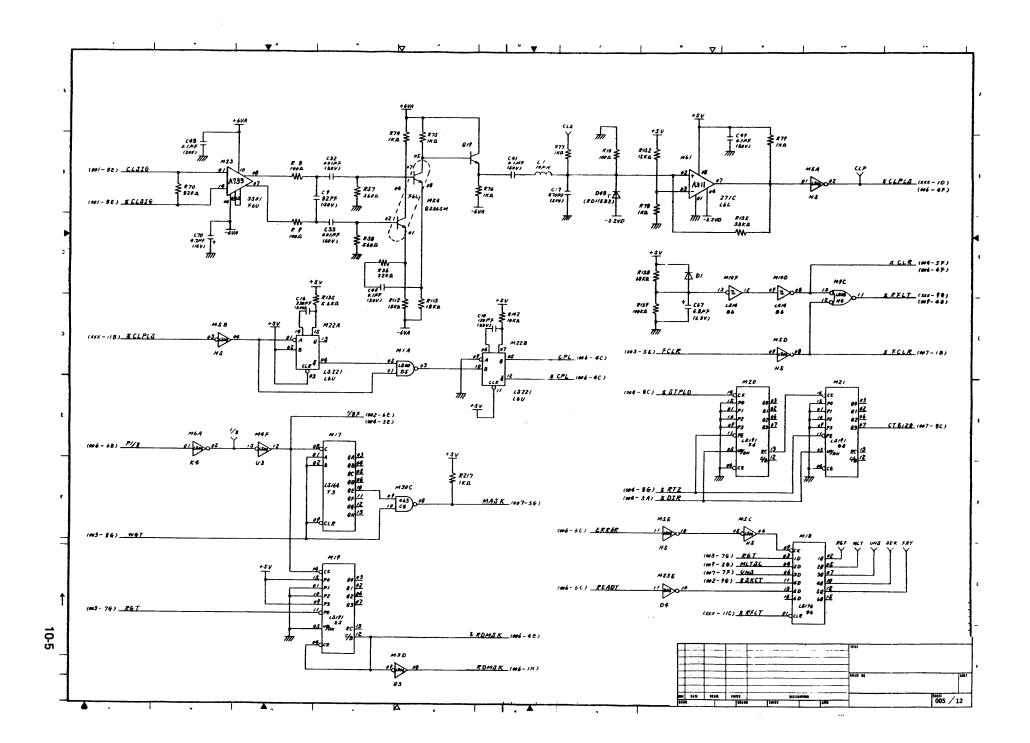

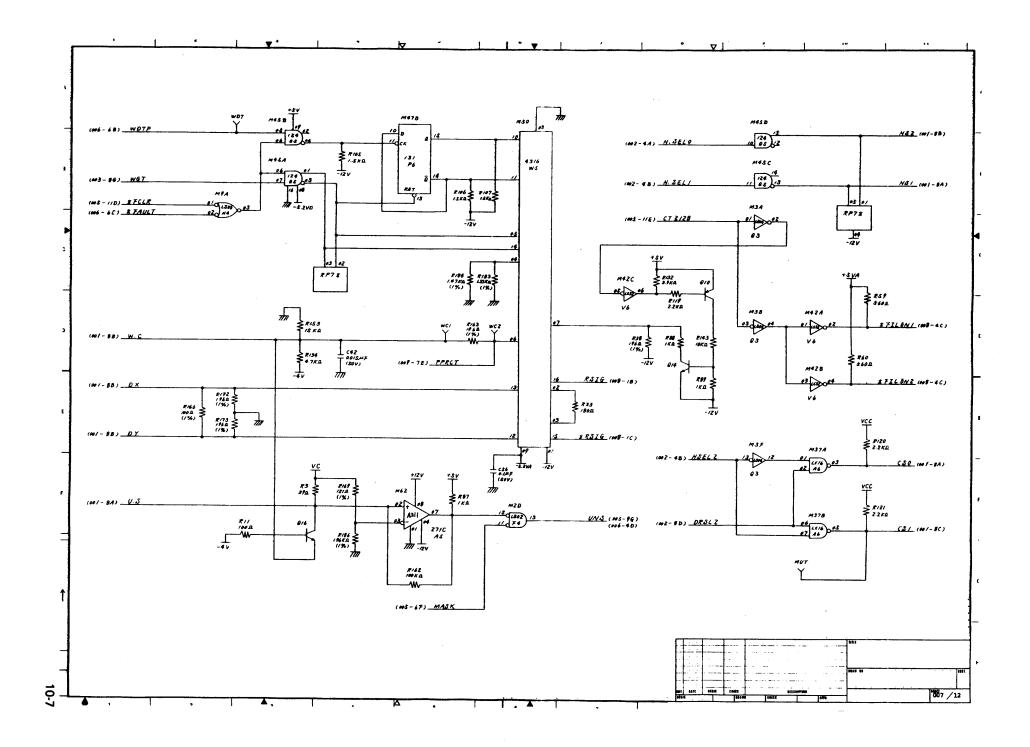

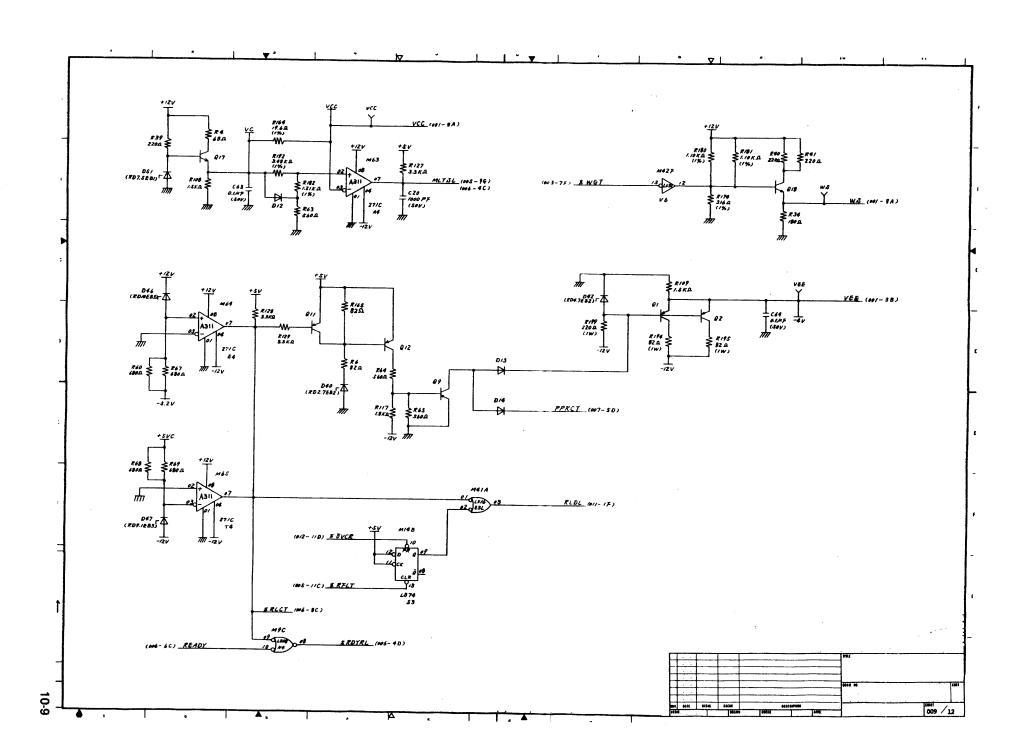

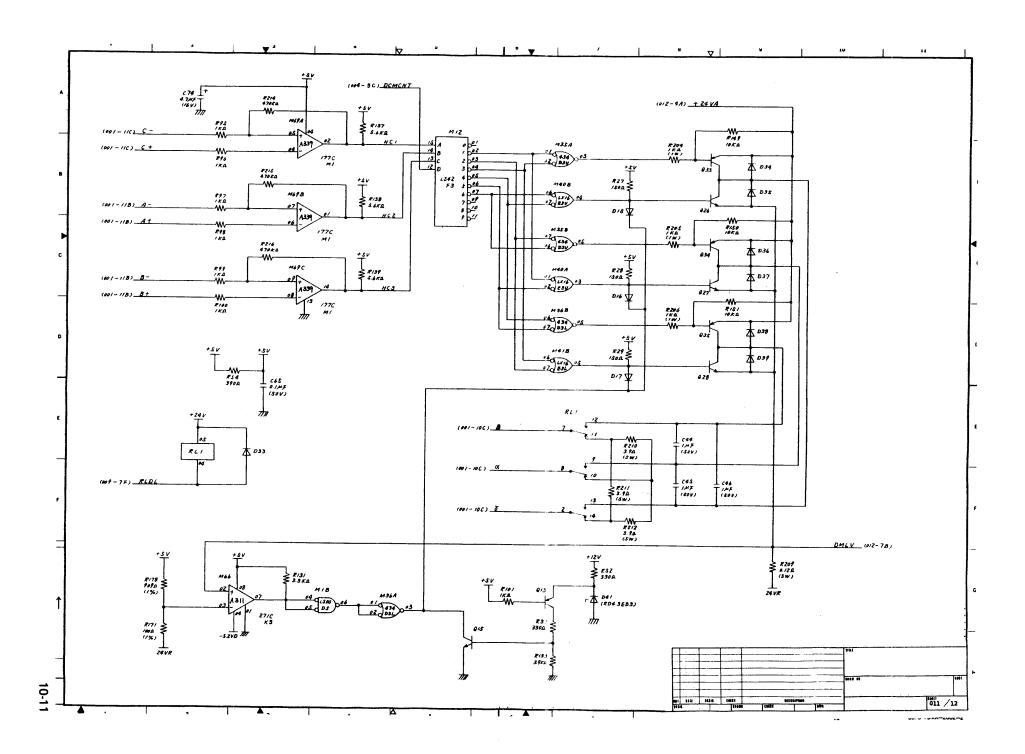

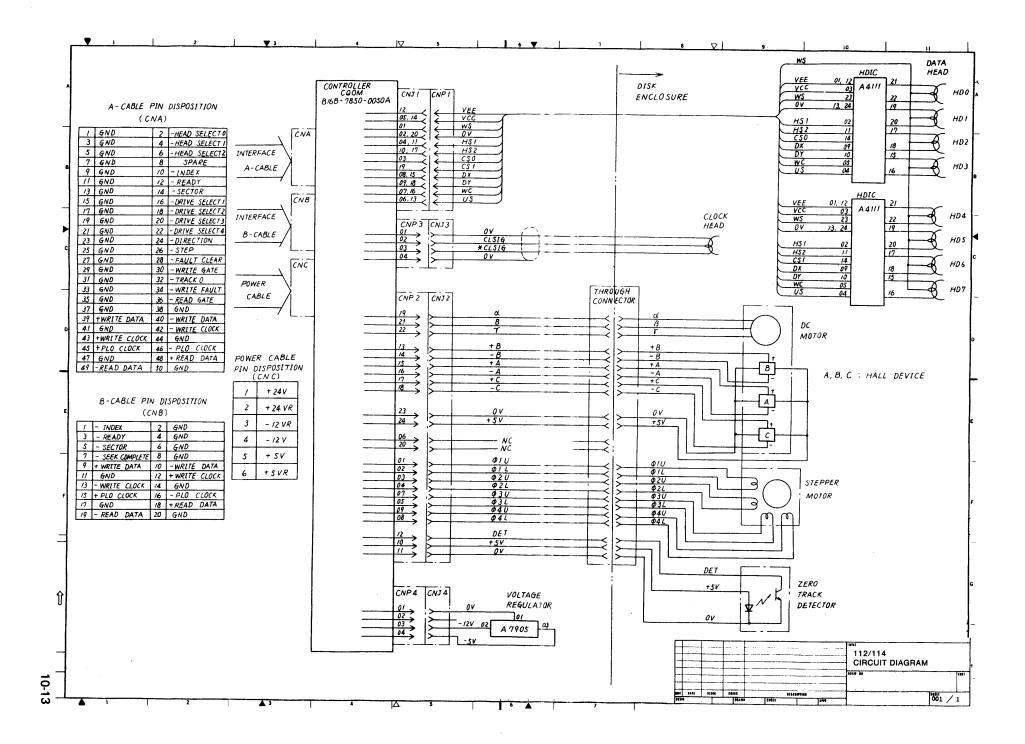

| 9.<br>10.      | SCHEMATICS                                   |            |

| IU.            | SUREMATICS                                   | 10-        |

# Illustrations

| FIGU         | RE                                                             | Pag          |

|--------------|----------------------------------------------------------------|--------------|

| 1.1          | External Appearance                                            | 1 ay         |

| 3.1          | Exterior View and Construction of Carton                       | 2.0          |

| 3.2          | installation in Locker                                         | 2 2          |

| 3.3          | Shows Lock State                                               | 2 4          |

| 3.4          | Securing the Unit                                              | 2.4          |

| 3.5          | Maintenance Access on the Unit                                 | 2 5          |

| 3.6          | Connection of the Unit                                         | 27           |

| 3.7          | Connection of 2 to 4 Units                                     | 2.7          |

| 3.8          | Device Selecting Switch                                        | 2.0          |

| 3.9          | SEEK COMPLETE Switch                                           | 3.0          |

| 3.10         | SECTOR/BYTE CLOCK                                              | 2 10         |

| 3.11         | SECIOR during the Generation of INDEX                          | 2 10         |

| 3.12         | W/R DATA and W/PLO CLOCK                                       | 2 1 1        |

| 3.13         | iviethod of Assigning the Number of Sectors                    | 2.1/         |

| 3.14         | DELAY SKC                                                      | 2 1 /        |

| 3.15         | Drive Selection Control                                        | 2 4 5        |

| 3.16         | Time Margin Measurement Switch                                 | 2 15         |

| 4.1          | Appearance of the Unit                                         | 4.1          |

| 4.2          | Spinale                                                        | 4-2          |

| 4.3          | Carriage Assembly                                              | 12           |

| 4.4          | Air Circulation Inside the DE                                  | 4-4          |

| 4.5          | Read/write mead                                                | 4-5          |

| 4.6          | Structure of Head Slider                                       | 4-5          |

| 4.7          | Clock Signal Waveform/Index Pattern Waveform                   | 4-7          |

| 4.8          | Block Diagram                                                  | 4-19         |

| 4.9          | Start/Stop Circuit Block Diagram                               | 4-20         |

| 4.10         | DC Spindle Motor Driving Circuit Block Diagram                 | 4-22         |

| 4.11         | DC Spindle Motor Driving Circuit Timing Chart                  | 4-23         |

| 4.12<br>4.13 | DC Spindle Motor Control Block Diagram                         | 4-24         |

| 4.13         | DC Spindle Motor Control Timing Chart (1)                      | 4-25         |

| 4.13         | DC Spindle Motor Control Timing Chart (2)                      |              |

| 4.15         | SEEK Control Block Diagram                                     | 4-28         |

| 4.16         | SEEK Control Flow Chart                                        | 4-29         |

| 4.17         | CONTROLLED STEP Mode Timing Chart SLAVE STEP Mode Timing Chart | 4-30         |

| 4.18         | SLAVE STEP Mode Timing Chart                                   | 4-31         |

| 4.19         | RTZ Mode Timing Chart                                          |              |

| 4.20         | SEEK COMPLETE Response Timing Chart                            | 4-33         |

| 4.21         | Stepper Driving Circuit Block Diagram                          | 4-34         |

| 4.22         | Stepper Driving Circuit Timing Chart (Page 1 of 2)             | 4-36         |

| 4.22         | Stepper Driving Circuit Timing Chart (Page 2 of 2)             | 4-37         |

| 4.23         | INDEX and SECTOR Generation Circuit Block Diagram              | 4-38<br>4-40 |

| 4.24         | INDEX and SECTOR Generation Circuit Timing Chart               | 4-40         |

|              | (When a Sector Length is 300 bytes)                            | 4-41         |

| 4.25         | HEAD Select Circuit Block Diagram                              | 4-41         |

| 4.26         | Write Circuit Block Diagram                                    | 4-45         |

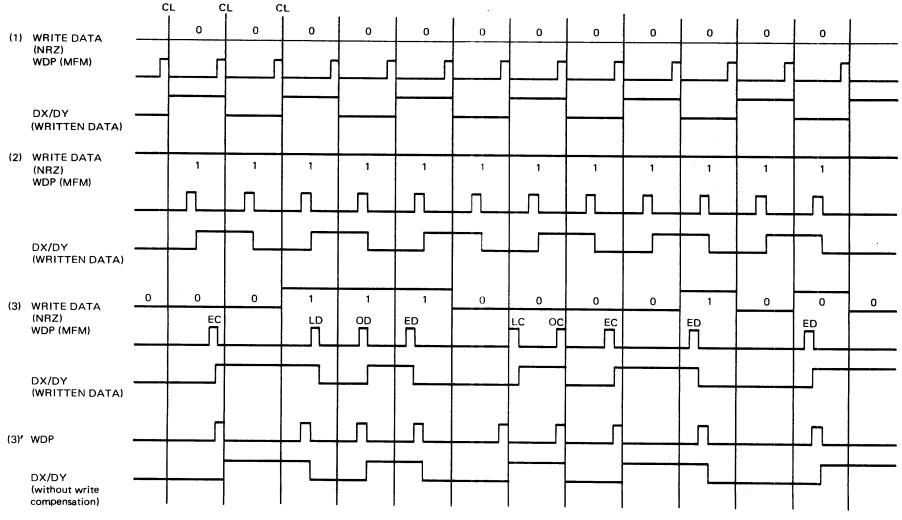

| 4.27         | Correlation between NRZ and MFM with Write Compensation        | 4-40         |

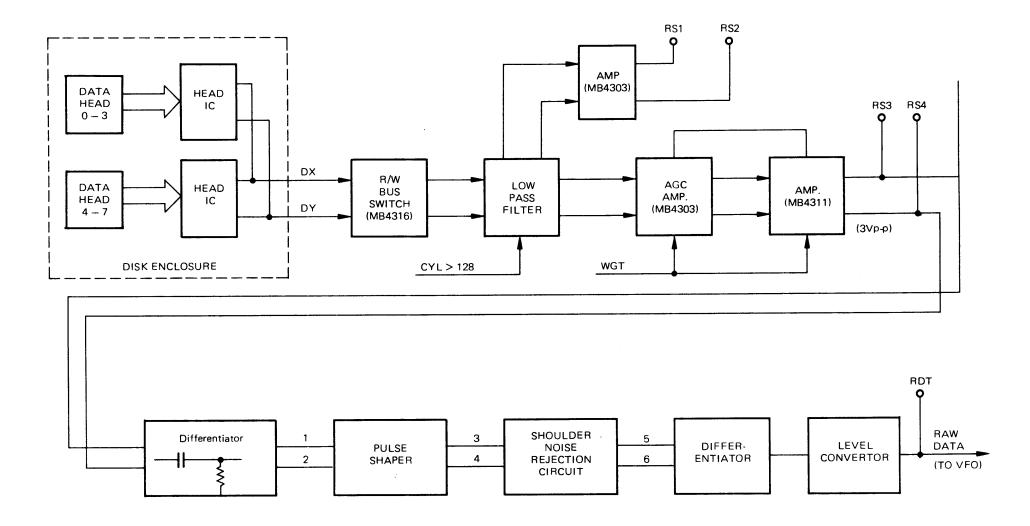

| 4.28         | Read Circuit Block Diagram                                     | 4-47<br>4-48 |

| 4.29         | Read Circuit Waveform                                          | 4-40         |

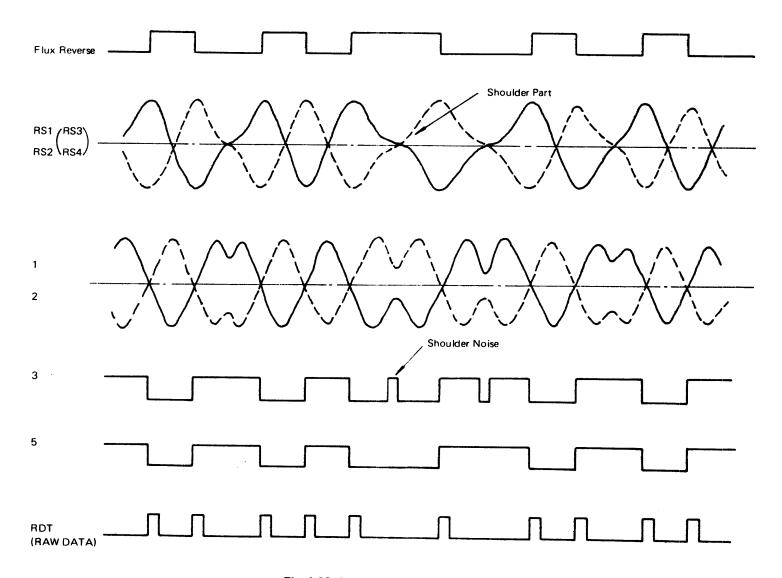

| 4.30         | VFO Circuit Block Diagram                                      | 4-49         |

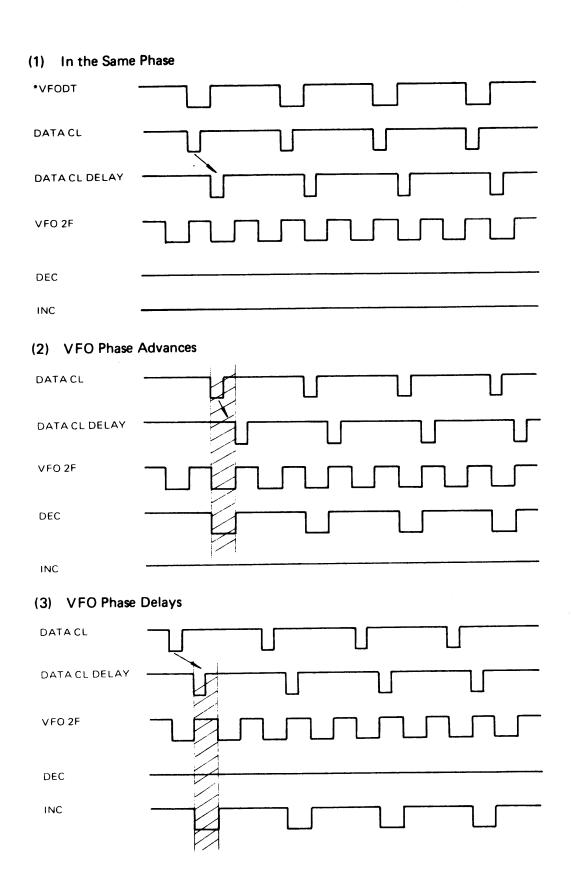

| 4.31         | VFO Circuit Phase Comparator Timing Chart                      | 4-51         |

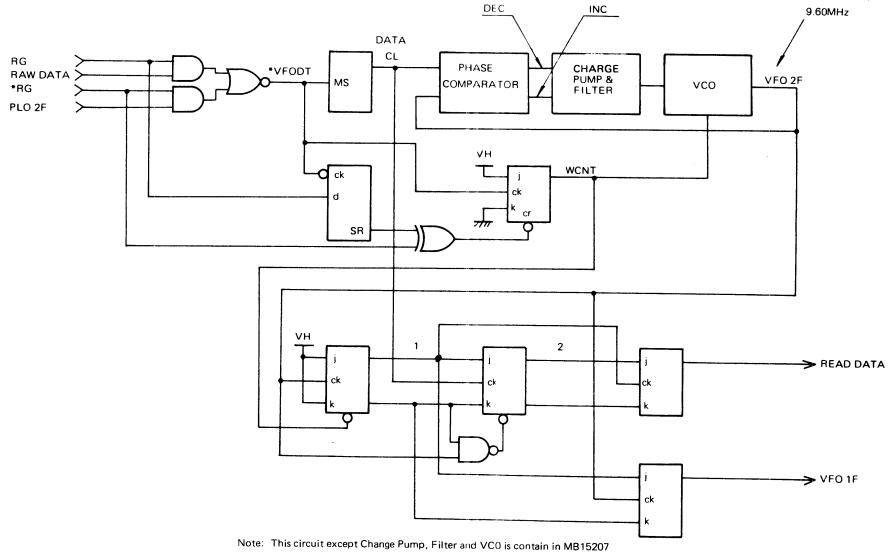

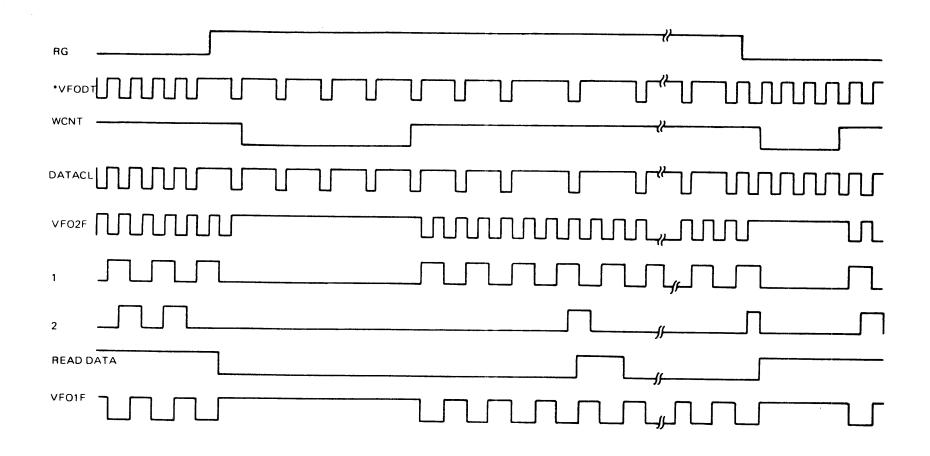

| 4.32         | Data Demodulation Circuit                                      | 4-52         |

| FIGUF      | RE                                       | Page       |

|------------|------------------------------------------|------------|

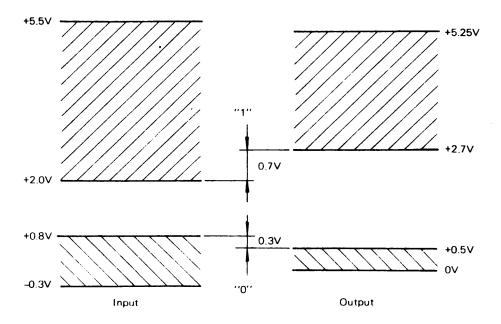

| 8.1        | TTL Medium/High Speed IC Level           | 8-1        |

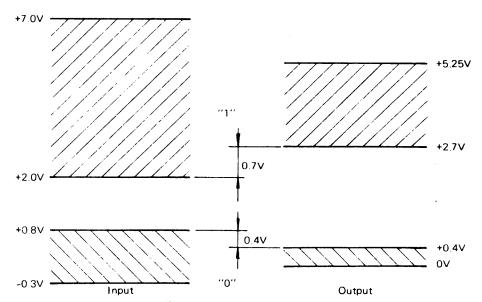

|            | TTL Super High Speed IC Level            | 8-2<br>8-2 |

| 8.3<br>8.4 | Low Power Schottky Level ECL Logic Level | 8-3        |

| 8.5        | CMOS Logic Level                         | 8-3        |

| 8.6        | MB15207/MB60512 Pin Assignment           | 8-7        |

## **Tables**

| TABLI |                                           | Page       |

|-------|-------------------------------------------|------------|

| 1.1   | Performance                               | 1-6        |

| 3.1   | Cable and Connector Specifications        | 3-6        |

| 3.2   | Device Number Selection                   | 3-9        |

| 3.3   | SECTOR/BYTE CLOCK                         | 3-10       |

| 3.4   | SECTOR during the Generation of INDEX     | 3-10       |

| 3.5   | W/R DATA and W/P CLOCK                    | 3-11       |

| 3.6   | Sector Counter Byte Table                 | 3-11       |

| 3.7   | Method of Assigning the Number of Sectors | 3-12       |

| 3.8   | DELAY SKC                                 | 3-14       |

| 3.9   | Drive Selection Control                   | 3-15       |

| 7.1   | Spare Parts List                          | 7-1        |

| 8.1   | MB15207 Pin Numbers and Names             | 8-8        |

| 8.2   | MB60512 Pin Numbers and Names             | <b>0-8</b> |

# Section | General Description

#### 1. GENERAL DESCRIPTION

#### 1.1 GENERAL

#### 1.1.1 General

The 112/114 micro-disk drives are high performance disk drives with unformatted storage capacities of 23.7MB and 47.4MB respectively.

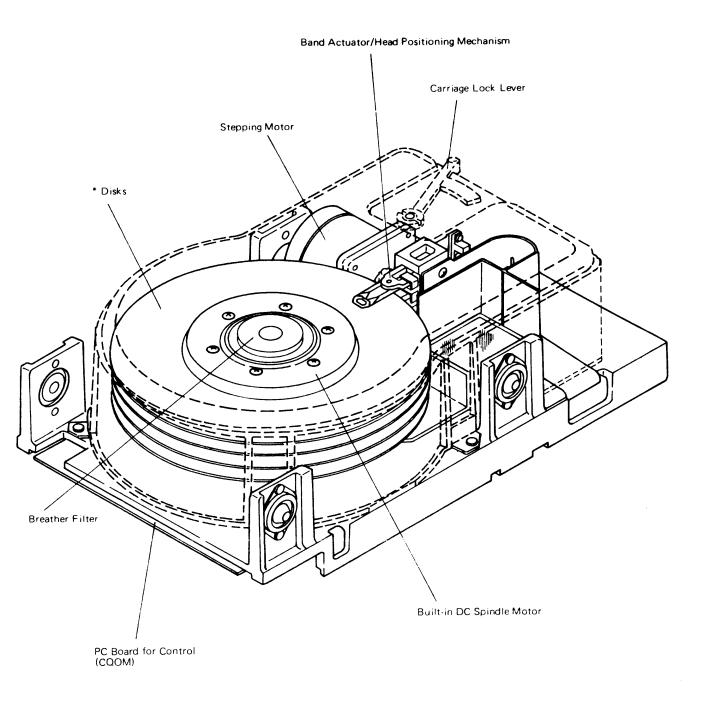

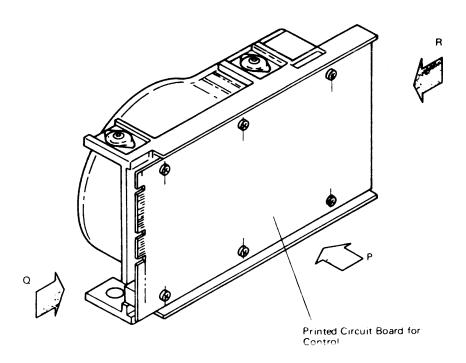

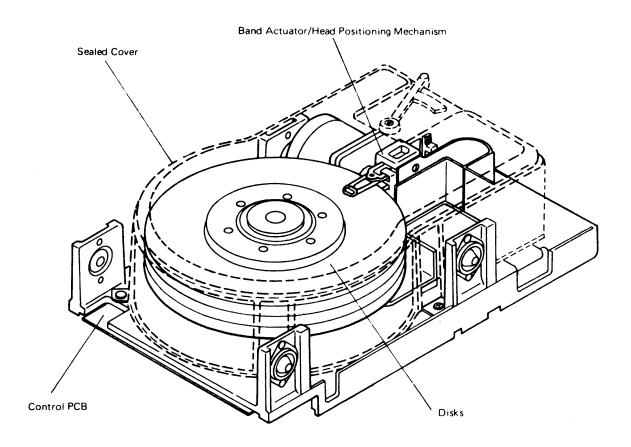

The unit consists of contact start-stop type heads and media, a unique head positioning band actuator, air filter, and a DC motor and other parts to drive the disks. All these are contained within a sealed cover. And outside the cover there is a printed circuit board with the following functions; read-write, driver receiver and sequence logic.

The unit is remarkably compact, highly reliable and inexpensive. It was designed to be the same size as an 8-inch floppy disk drive. The unit can also be connected in daisy chain configuration of up to 4 units. Its data format is of a fixed length and together with its easy-to-handle interface, has simplified system design.

#### 1.1.2 Features

(1) Compact

Since the disks are 200mm in outer diameter and are driven by a DC motor directly connected to the spindle, the device is extremely compact in size. The unit measures 217mm (8.5 in) in width, 111mm (4.4 in) in height and 356mm (14.0 in) in length.

(2) Economical

The positioning mechanism of the drive is a stepping motor which uses a steel band and a viscous damper. This has made the unit less expensive.

(3) High Reliability

The heads, disks, and the positioner are within the disk enclosure and are protected by a plastic cover. In the disk enclosure, there is a breathing filter and a recirculation filter to keep the air clean, thus ensuring reliability.

- (4) Preventive maintenance is unnecessary.

- (5) DC Power

Because a built-in DC motor is used, the unit does not have to be modified to suit line frequencies (50Hz/60Hz) or input power voltages (110, 115, 220, 240V).

(6) Physical Size

The unit is the same size as an 8 inch floppy disk. Therefore, when replacing a floppy disk, the locker need not be changed.

(7) Mounting Plane

The unit can be installed in its locker either vertically or horizontally. This allows easier installation and flexible system design.

(8) Low Power Consumption

Very low power demand (seeking 70W, non seek 60W) permits it to be used in a wide range of environmental temperature (5°C to 45°C) without a cooling fan.

(9) Audible Noise

The unit's low noise output, approx. 60dB (A-scale weighting) even during seeking makes it ideal for office use.

#### (10) Vibration

Vibration is not transmitted to external parts because the unit is fitted to the locker with vibration isolating rubber mounts.

#### 1.2 SPECIFICATIONS

#### 1.2.1 **Environmental Condition of Installation Site**

(1) Temperature

Operating Non-operating

5 to 45°C (41° to 113°F) -40 to 60°C (-40° to 140°F)

Gradient

Less than 15°C/H

(2) Humidity

Operating Non-operating 20% to 80% RH (Moisture must not condense.) 5% to 95% RH  $\,$

(3) Vibration

Operating

Less than 0.2G (3 to 60Hz) (except resonance)

Both ways 2 minutes x 30 cycle (sine wave)

Non-operating (power OFF after installation)

Less than 0.4G (3 to 60Hz)

Both ways 2 minutes x 30 cycle (sine wave)

During storage or transportation

Less than 3G

(4) Shock

Operating Non-operating Less than 2G (maximum 10ms) Less than 3G (maximum 10ms)

During storage or transportation

Less than 5G (maximum 30ms)

(5) Altitude

Operating

Non-operating

Less than 3,000m (10,000 ft) Less than 12,000m (40,000 ft)

#### 1.2.2 Power Source Specifications

#### (1) Consumption Current

| Voltage   | Peak Current                         | Steady Current |

|-----------|--------------------------------------|----------------|

| +5V ±5%   | 6.0A max                             | 3.4A           |

| −12V ±5%  | 0.7A max                             | 0.7A           |

| +24V ±10% | 6.0A max. (Pulse)<br>4.5A (10 sec.*) | 1.6A           |

The voltage value above is the voltage at the power input terminal of the unit. Steady current is the current at AVERAGE SEEK + LATENCY TIME + 1 revolution READ or WRITE.

\* Start-up time

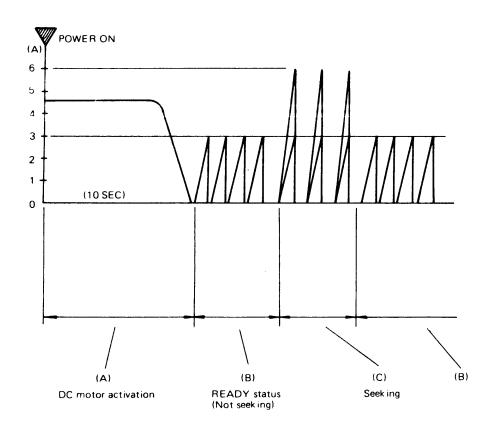

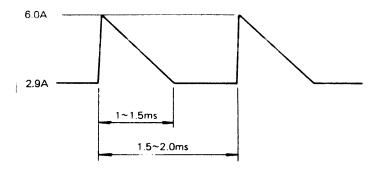

#### (2) Current Wave Form

#### (a) +24V current wave form

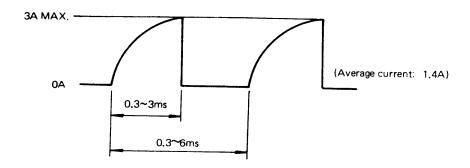

### Magnified wave of (B) part

Note: The current wave shape of the (C) part is the shape formed by the lapping of the above two types of waves asynchronously.

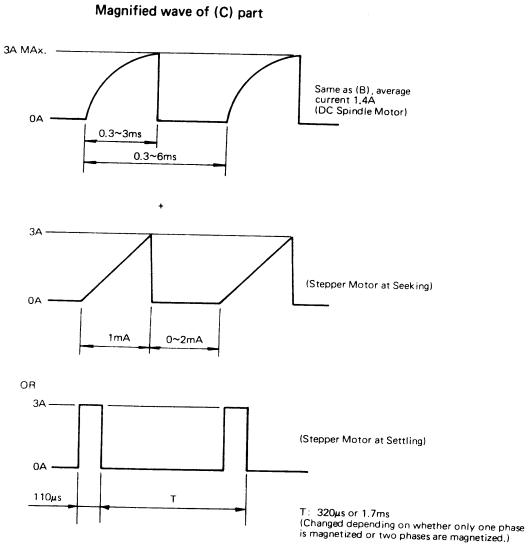

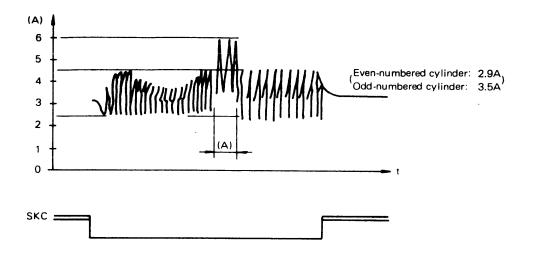

### (b) +5V current wave shape

The +5V current, at the time of seeking, forms the following switching current wave form.

### Magnified wave of (A) part

Note: The 6A peak current of the (A) part is present 3 or 4 times in one seek.

### 1.2.3 Performance

Table 1.1 Performance

|                           | Model  |         | Micro disk drive                                   |          |

|---------------------------|--------|---------|----------------------------------------------------|----------|

| Specification             |        |         | 112                                                | 114      |

| Total storage capacity    |        |         |                                                    |          |

| Unformatted               | [MB]   |         | 23.74                                              | 47.47    |

| Formatted                 | [MB]   |         | 19.97                                              | 39.98    |

| Storage capacity/track    |        |         |                                                    |          |

| Unformat                  | (B)    |         | 24320 <sup>+32</sup>                               |          |

| Format                    | (B)    |         | 20480                                              |          |

| Number of disks           |        |         | 2                                                  | 4        |

| Number of heads (R/W)     |        |         | 4                                                  | 8        |

| Number of heads (Clock)   |        |         | 1                                                  |          |

| Number of cylinders       |        |         | 244                                                |          |

| Number of tracks/cylinder |        |         | 4                                                  | 8        |

| Number of sectors         |        |         | Variable hard                                      |          |

| Recording density         | [BPI]  |         | 12,360                                             |          |

| Track density             | [TPI]  |         | 195                                                |          |

| Transfer rate             | [MB/S] |         | 1.2                                                |          |

| Rotational speed          | [rpm]  |         | 2,964                                              |          |

| Average latency time      | [ms]   |         | 10.1                                               |          |

| Recording method          |        |         | MFM                                                |          |

| Positioning time Mi       | n [ms] |         | 30                                                 |          |

| Av                        | e (ms) |         | 70                                                 |          |

| Ma                        | x [ms] |         | 140                                                |          |

| Input voltage             |        | +24\    | / ±10%, 1.8A (max. 6.0                             | DA)      |

|                           |        | +5V     | ±5%, 3.5A (max. 6.0A)                              | )        |

|                           |        | -12\    | / ±5%, 0.7A (max. 0.7/                             | ۹)       |

| External size             |        |         |                                                    |          |

| Width x height x depth    | [mm]   | 217 × 1 | 11 × 356 (8.5" × 4.4" >                            | < 14.0") |

| Disk size                 | [mm]   |         | ter diameter 200 (7.9")<br>ner diameter 100 (3.9") |          |

| Weight                    | [kg]   |         | 6.3 (13.9 lb.)                                     |          |

<sup>\*</sup> Formatted capacity of 80 sectors/track

#### 1.2.4 Reliability

#### (1) MTBF

MTBF is defined as follows.

MTBF = operating time/the number of equipment failures.

Operating time is the entire time at which the power is ON except during maintenance work. Failure of the unit means trouble that requires either repairs, adjustments, or a replacement. Mishandling by the operator, power failure, control unit problems, cable problems and failure due to unsuitable environment are not included.

The MTBF of the 112/114 is expected to exceed 10,000 hours (engineering specification).

#### (2) MTTR

MTTR is the average time a well-trained service technician should take to diagnose and correct a failure to the sub-assembly level. The 112/114 is designed for an MTTR of 30 minutes or less.

#### (3) Component Life

The 112/114 need not be overhauled for the first five years.

#### (4) Power Loss

Integrity of the data on the disk is guaranteed against all forms of abnormal DC power loss. However, if the power failure occurs during a WRITE operation, the data is not guaranteed.

#### (5) Error Rate

An error detected during initialization, and processed to be replaced by a spare record is not included in the error rate.

- (a) Recoverable Error Rate

- An error which is recoverable with one try of the RETRY command should not exceed once per 10<sup>10</sup> bits read.

- (b) Non Recoverable Error Rate

- Errors that cannot be recovered within 16 retries are included in the MTBF.

- (c) Positioning Error Rate

- The rate of positioning errors recoverable by one retry is one error or less per 10<sup>6</sup> seeks.

- (d) Media Error

- i) No error will be found at H0 and H1 in cylinder 000.

- ii) The following shows the number of defective spots in the 112/114.

112 . . . . Less than 20

114 . . . . Less than 40

### 1.3 EXTERNAL APPEARENCE

\*NOTE: 112 contains two disks. 114 contains four disks.

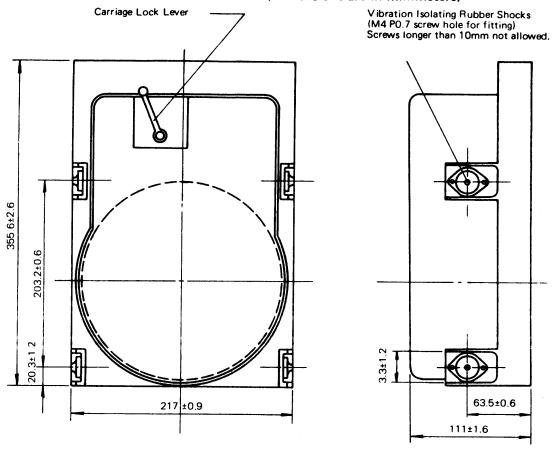

Fig. 1.1 External Appearance

# Section 9 Operation

#### 2. OPERATION

#### 2.1 GENERAL

Power-on/off for the unit is described in this section.

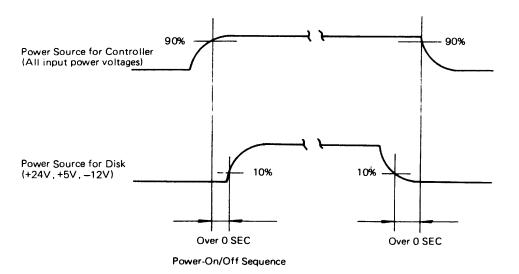

#### 2.2 POWER ON/OFF SEQUENCE

The 112/114 micro disk drive has no power ON/OFF switch of its own. Therefore, power ON/OFF for the micro disk drive is performed by the power ON/OFF function of the system.

If the write gate signal coming from the controller is kept OFF in advance to a power-on or power-off, a sequence of the power source (+24V, +5V, -12V) of the device is unnecessary. That is, the stored data is not destroyed and mechanical and electric errors do not occur. In order to keep the write gate signal OFF during a power-ON/OFF transition, the power source of the controller and the device must adhere to the following sequence.

#### (1) Basic Sequence

(2) By detecting the +5V voltage level in the drives the write gate signal is inhibited and power sequencing is unnecessary if the +5V power source for the drive is supplied from the +5V power source for the controller, and the interface signal from the controller is determined only by the +5V power source for the controller.

# Section 3 Installation and Checkout

#### 3. INSTALLATION AND CHECKOUT

#### 3.1 GENERAL

Unpacking, installation, cable connections, configuration settings, how to install the unit into the system, etc., are described in this section.

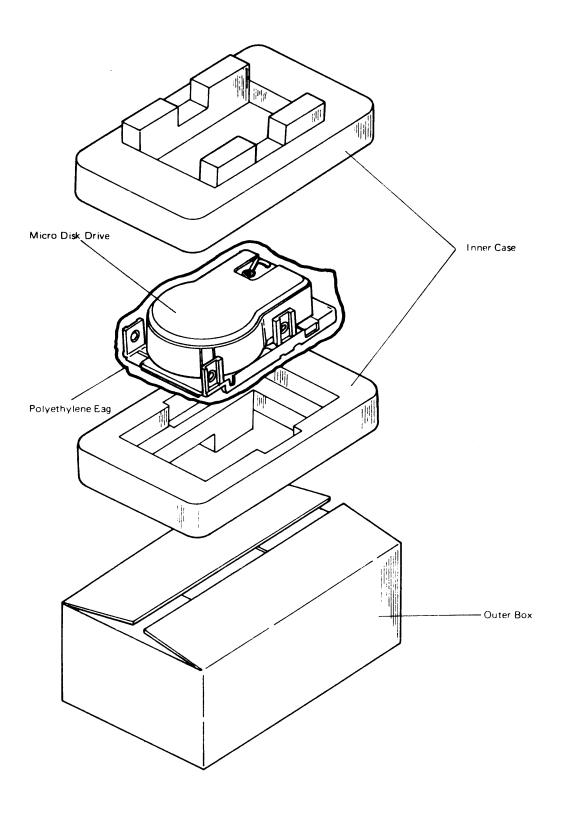

This unit is packed so as to withstand the shocks of long distance transportation. When the difference in the storage (or shipping) environment and the unpacking environment exceeds 20°C (36°F), the carton should be allowed to stand at the unpacking site for approximately 3 hours prior to unpacking in order to avoid condensation.

#### 3.2 UNPACKING

The device is wrapped in a polyethylene bag, and enclosed in a inner case and outer box. An exterior view of the carton is shown in Fig. 3.1.

- (1) Place the unit (Note: Do not turn disk drive upside-down) near the installation area.

- (2) Remove the adhesive tape on the box and open it.

- (3) Remove the upper inner case and pull the unit out by grasping the base of the unit.

- (4) Store packing material for possible future use.

#### 3.3 VISUAL INSPECTION

After unpacking, check the following.

- (1) There should be no crack, rust etc. that mar its appearance and integrity.

- (2) All parts should be firmly fixed and there should be no loose screws, etc.

- (3) The carriage lock (shipping restraint) should be in tact with no abnormalities.

- (4) The duplicate media defect label should be correct.

Fig. 3.1 Exterior View and Construction of Carton

#### 3.4 MOUNTING

#### 3.4.1 Installation in Locker

The accompanying diagram shows how to install the drive according to the dimensions and the structure of the frame. (Dimensions are in millimeters)

Fig. 3.2 Installation in Locker

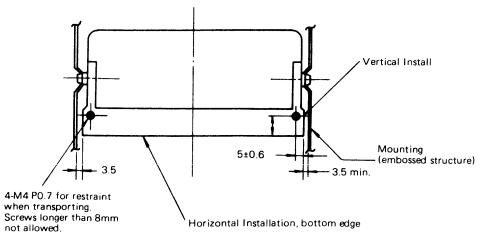

#### 3.4.2 Securing for Transportation

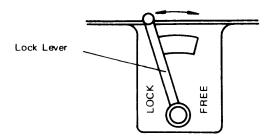

If the unit is installed in the locker during transportation, in order to prevent damage, set the carriage lock lever to LOCK.

CAUTION: Before placing the carriage restraint in the LOCK position, insure that the heads are at Track 0. Do NOT use the carriage restraint to position the heads.

#### (1) Fixing Carriage

Pull up the lock lever, rotate it in the direction of the arrow and fix the carriage (LOCK) or reslease it (FREE).

Fig. 3.3 Shows LOCK State

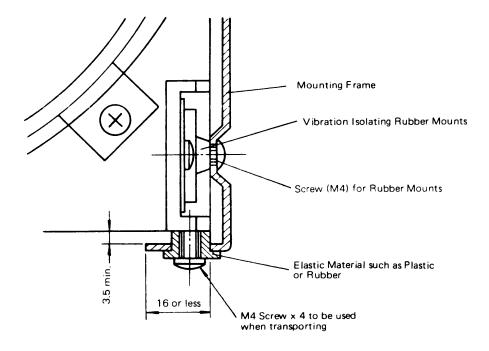

#### (2) Securing the Unit

Secure the unit to the mounting frame using the screw hole that is provided to transport the unit.

Fig. 3.4 Securing the Unit

#### 3.4.3 Service Area

Maintenance, securing for transportation, cable connection, are accessed as shown below. When determining the service area and where to install the locker, make sure that there is enough room for maintenance work.

P side: Maintenance operations on PCB.

Q side: Cable connections.

Installation and removal of the securing screw when transporting.

R side: Accessing the carriage lock lever to secure the carriage.

Installation and removal of the securing screw when transporting.

Bad track label and a name-plate.

Fig. 3.5 Maintenance Access on the Unit

### 3.5 CABLE

### 3.5.1 Cable and Connector Specifications

Table 3.1 shows specifications recommended for cables and connectors.

Table 3.1 Cable and Connector Specification

| Connector     | Name                  | Туре                            | Maker        |

|---------------|-----------------------|---------------------------------|--------------|

| A cable (50P) | Cable side connector  | FCN-767J050-AU/1                | Fujitsu      |

|               |                       | or 88373-1                      | AMP          |

|               |                       | or 3415-0001                    | 3M           |

|               | Device side card edge | -                               | _            |

|               | Cable                 | 455-248-50                      | Spectrastrip |

|               |                       | or 171-50                       | Ansley       |

| 3 cable (20P) | Cable side connector  | FCN-767J020-AU/1                | Fujitsu      |

|               |                       | or 88373-6                      | AMP          |

|               |                       | or 3461-0001                    | 3M           |

|               | Device side card edge | -                               | _            |

|               | Cable                 | 455-248-20                      | Spectrastrip |

|               |                       | or 171-20                       | Ansley       |

| Power cable   | Cable side connector  | 1-480270-0                      | AMP          |

|               | Device side connector | 1-380909-0                      | AMP          |

|               | Contact               | 60619-1                         | AMP          |

|               | Cable                 | AWG14 (+5V, RTN)                |              |

|               |                       | AWG16(+24V, RTN)                | _            |

|               |                       | AWG20 (-5V/-7V to<br>-16V, RTN) |              |

#### 3.5.2 Cable Connections

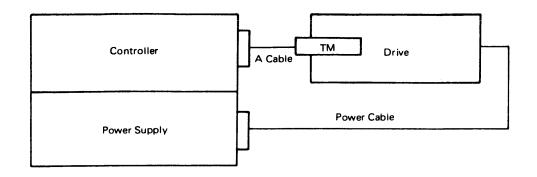

#### (1) Connection of One Unit

Fig. 3.6 is an example of only one unit connected to the controller. The unit is also operable when both Cable A and Cable B are connected at the same time.

Fig. 3.6 Connection of One Unit

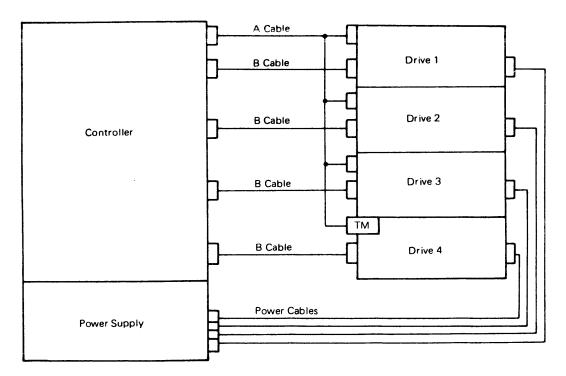

#### (2) Connection of 2 to 4 Units

When 2 to 4 units are connected, cable A (control signal) is daisy chained, and cables B (R/W signal) are connected in radial.

Fig. 3.7 Connection of 2 to 4 Units

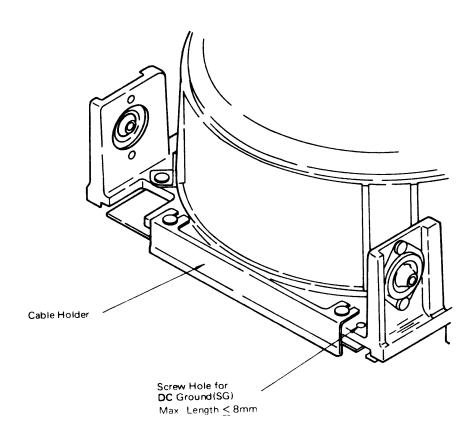

#### (3) Caution in Connecting the Cable

In order to reduce the influence of external electrical noise and the like, the following should be noted.

- (a) The power cable and the interface cable should not be in the same plane.

- (b) If the power is supplied from the system, a voltage drop would occur in the DC cable, so that each voltage must be set while measuring at the input terminal entry of the unit.

- (c) If the unit is installed in a system, and or if it is installed in the 19 inch rack, firmly connect an SG ground to the hole which is provided in the casting so as to reduce the influence of external noise.

A screw hole (M4 P0.7) is provided in the casting for DC ground as shown below. Use an M4 screw less than 8mm in length.

#### 3.6 SWITCH ARRANGEMENT

The functions and assignment procedures of the different switches on the circuit board of the 112/114 are described below.

#### 3.6.1 Drive Select (Device Number Selection)

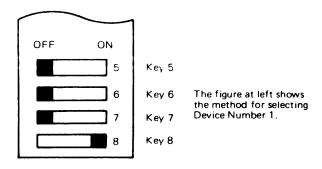

The drive select switch is used to select one logical unit number up to a maximum of 4 devices. Of the 4 switches, you are to turn ON one relevant switch while turning OFF the other 3. The device number selection procedures are shown in Table 3.2 and Fig. 3.8

Table 3.2 Device Number Selection

| Device Number |       | SW3 Switch |       |       |

|---------------|-------|------------|-------|-------|

| Device Number | Key 8 | Key 7      | Key 6 | Key 5 |

| 1             | 0     | ×          | ×     | ×     |

| 2             | ×     | 0          | х     | ×     |

| 3             | ×     | ×          | 0     | х     |

| 4             | ×     | ×          | ×     | 0     |

O: **ON**

X: OFF

#### SW3 (Mounting Location B5)

Fig. 3.8 Device Selecting Switch

#### 3.6.2 Seek Complete

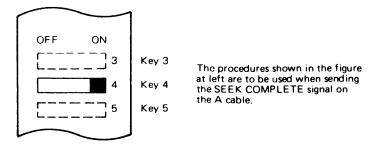

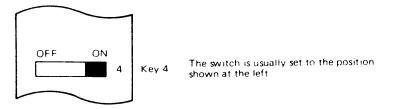

When sending the SEEK COMPLETE onto the A cable of the interface, turn ON Key 4 of SW3.

However, at this point, be sure not to leave DRIVE SELECT Key 4 in the ON status (See Fig. 3.9).

#### SW3 (Mounting Location B5)

Fig. 3.9 SEEK COMPLETE Switch

#### 3.6.3 Sector/Byte Clock

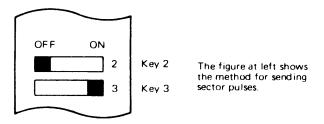

This switch is used to select either SECTOR pulses or BYTE CLOCK onto the interface cable. The switch assignment procedures are shown in Table 3.3 and Fig. 3.10 below.

ON OFF

Table 3.3 SECTOR/BYTE CLOCK

| Signal Name  | SW2   | Switch |

|--------------|-------|--------|

| Signal reame | Key 3 | Key 2  |

| SECTOR       | 0     | ×      |

| BYTE CLOCK   | ×     | 0      |

SW2 (Mounting Location  $\overline{A}$ 2)

Fig. 3.10 SECTOR/BYTE CLOCK

#### 3.6.4 Sector During the Generation of Index

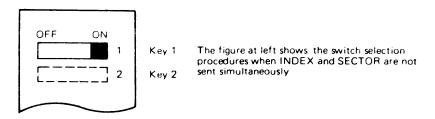

This is used to select whether or not to send the sector mark generated during the same times as Index onto the interface. The switch selection procedures are shown in Table 3.4 and Fig. 3.11.

Table 3.4 SECTOR during the Generation of INDEX

| Salastia - Camana       | SW2   |            |    |

|-------------------------|-------|------------|----|

| Selection Content       | Key 1 | 0:         | 01 |

| Send the SECTOR.        | ×     | <b>X</b> : | 0  |

| Do not send the SECTOR. | 0     |            |    |

SW2 (Mounting Location A2)

Fig. 3.11 SECTOR during the Generation of INDEX

#### 3.6.5 Write/Read Data, Write/PLO Clock

The method for sending WRITE/READ DATA and WRITE/PLO CLOCK signals onto the A cable of the interface is shown in Table 3.5 and Fig. 3.12

Table 3.5 W/R DATA and W/PLO CLOCK

| Signal Name  | Assigned Switch SW4 |

|--------------|---------------------|

| ±WRITE DATA  | Key 7, Key 8 ON     |

| ±READ DATA   | Key 1, Key 2 ON     |

| ±WRITE CLOCK | Key 5, Key 6 ON     |

| ±PLO CLOCK   | Key 3, Key 4 ON     |

SW4 (Mounting Location B4)

Fig. 3.12 W/R DATA and W/PLO CLOCK

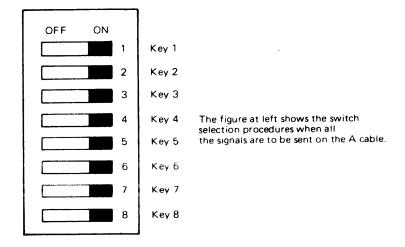

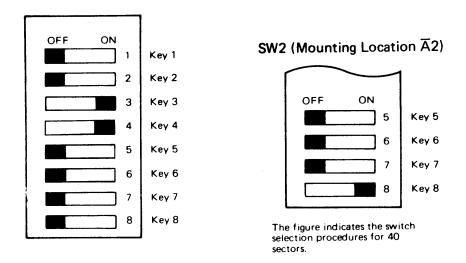

#### 3.6.6 Assigning the Number of Sectors

The number of sectors can be assigned by using a combination of the SW1 and SW2 switch keys. Each key of the respective switch corresponds to binary powers of the byte count (2° to 211 bytes). See Table 3.6.

Table 3.6 Sector Counter Byte Table

| SW1   | No. of Bytes | SW2   | No. of Bytes |

|-------|--------------|-------|--------------|

| Key 8 | 1            | Key 8 | 256          |

| Key 7 | 2            | Key 7 | 512          |

| Key 6 | 4            | Key 6 | 1024         |

| Key 5 | 8            | Key 5 | 2048         |

| Key 4 | 16           |       |              |

| Key 3 | 32           | l     |              |

| Key 2 | 64           | 1     |              |

| Key 1 | 128          |       |              |

The method of assigning the number of sectors is shown in Table 3.7 and Fig. 3.13, where the LAST SECTOR indicates the number of excess bytes. This also indicates that only the last sector becomes longer because of excess bytes.

Table 3.7 Method of Assigning the Number of Sectors

|         |   |   |   |   | SW 1 |   |   |   |   | SW2 |   |   |              |                          |

|---------|---|---|---|---|------|---|---|---|---|-----|---|---|--------------|--------------------------|

| SECTORS | 8 | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 8 | 7   | 6 | 5 | BYTES/SECTOR | LAST SECTOR              |

| 5       | 1 | 1 | 1 | 1 | 1    | 1 | 1 | 1 | 1 | 1   | 1 | 1 | 4095         | +3845 <sup>+32</sup>     |

| 6       | 1 | 0 | 1 | 0 | 1    | 0 | 1 | 1 | 1 | 1   | 1 | 1 | 4053         | +2+32                    |

| 7       | 0 | 1 | 0 | 0 | 1    | 0 | 0 | 1 | 1 | 0   | 1 | 1 | 3474         | +2 <sup>+32</sup>        |

| 8       | 0 | 0 | 0 | 0 | 0    | 1 | 1 | 1 | 1 | 1   | 0 | 1 | 3040         | 0+32                     |

| 9       | 0 | 1 | 1 | 1 | 0    | 0 | 0 | 1 | 0 | 1   | 0 | 1 | 2702         | +2 <sup>+32</sup>        |

| 10      | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 1 | 1 | 0   | 0 | 1 | 2432         | 0+32                     |

| 11      | 0 | 1 | 0 | 0 | 0    | 1 | 0 | 1 | 0 | 0   | 0 | 1 | 2210         | +10 <sup>+32</sup>       |

| 12      | 0 | 1 | 0 | 1 | 0    | 1 | 1 | 1 | 1 | 1   | 1 | 0 | 2026         | +8+32                    |

| 13      | 0 | 1 | 1 | 1 | 0    | 0 | 1 | 0 | 1 | 1   | 1 | 0 | 1870         | +10 <sup>+32</sup>       |

| 14      | 1 | 0 | 0 | 1 | 0    | 0 | 1 | 1 | 0 | 1   | 1 | 0 | 1737         | +2+32                    |

| 15      | 1 | 0 | 1 | 0 | 1    | 0 | 1 | 0 | 0 | 1   | 1 | 0 | 1621         | +5+32                    |

| 16      | 0 | 0 | 0 | 0 | 1    | 1 | 1 | 1 | 1 | 0   | 1 | 0 | 1520         | 0+32                     |

| 17      | 0 | 1 | 1 | 0 | 1    | 0 | 0 | 1 | 1 | 0   | 1 | 0 | 1430         | +10 <sup>+32</sup>       |

| 18      | 1 | 1 | 1 | 0 | 0    | 0 | 1 | 0 | 1 | 0   | 1 | 0 | 1351         | +2+32                    |

| 19      | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 1 | 0   | 1 | 0 | 1280         | 0+32                     |

| 20      | 0 | 0 | 0 | 0 | 0    | 0 | 1 | 1 | 0 | 0   | 1 | 0 | 1216         | 0+32                     |

| 21      | 0 | 1 | 1 | 0 | 0    | 0 | 0 | 1 | 0 | 0   | 1 | 0 | 1158         | +2+32                    |

| 22      | 1 | 0 | 0 | 0 | 1    | 0 | 1 | 0 | 0 | 0   | 1 | 0 | 1105         | +10+32                   |

| 23      | 1 | 0 | 0 | 0 | 0    | 1 | 0 | 0 | 0 | 0   | 1 | 0 | 1057         | +9 <sup>+32</sup>        |

| 24      | 1 | 0 | 1 | 0 | 1    | 1 | 1 | 1 | 1 | 1   | 0 | 0 | 1013         | +8 <sup>+32</sup>        |

| 25      | 0 | 0 | 1 | 1 | 0    | 0 | 1 | 1 | 1 | 1   | 0 | 0 | 972          | +20+32                   |

| 26      | 1 | 1 | 1 | 0 | 0    | 1 | 0 | 1 | 1 | 1   | 0 | 0 | 935          | +10+32                   |

| 27      | 0 | 0 | 1 | 0 | 0    | 0 | 0 | 1 | 1 | 1   | 0 | 0 | 900          | +20+32                   |

| 28      | 0 | 0 | 1 | 0 | 0    | 1 | 1 | 0 | 1 | 1   | 0 | 0 | 868          | +16+32                   |

| 29      | 0 | 1 | 1 | 0 | 0    | 0 | 1 | 0 | 1 | 1   | 0 | 0 | 838          | +18 <sup>+32</sup>       |

| 30      | 0 | 1 | 0 | 1 | 0    | 1 | 0 | 0 | 1 | 1   | 0 | 0 | 810          | +20+32                   |

| 31      | 0 | 0 | 0 | 0 | 1    | 0 | 0 | 0 | 1 | 1   | 0 | 0 | 784          | +16+32                   |

| 32      | 0 | 0 | 0 | 1 | 1    | 1 | 1 | 1 | 0 | 1   | 0 | 0 | 760          | 0+32                     |

| 33      | 0 | 0 | 0 | 0 | 0    | 1 | 1 | 1 | 0 | 1   | 0 | 0 | 736          | +32+32                   |

| 34      | 1 | 1 | 0 | 1 | 0    | 0 | 1 | 1 | 0 | 1   | 0 | 0 | 715          | +10+32                   |

| 35      | 0 | 1 | 1 | 0 | 1    | 1 | 0 | 1 | 0 | 1   | 0 | 0 | 694          | +30 <sup>+32</sup>       |

| 36      | 1 | 1 | 0 | 0 | 0    | 1 | 0 | 1 | 0 | 1   | 0 | 0 | 675          | +20 <sup>+32</sup>       |

| 37      | 1 | 0 | 0 | 0 | 1    | 0 | 0 | 1 | 0 | 1   | 0 | 0 | 657          | +11+32                   |

| 38      | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 1 | 0 | 1   | 0 | 0 | 640          | 0+32                     |

| 39      | 1 | 1 | 1 | 1 | 0    | 1 | 1 | 0 | 0 | 1   | 0 | 0 | 623          | +23+32                   |

| 40      | 0 | 0 | 0 | 0 | 0    | 1 | 1 | 0 | 0 | 1   | 0 | 0 | 608          | 0+32                     |

| 41      | 1 | 0 | 0 | 0 | 1    | 0 | 1 | 0 | 0 | 1   | 0 | 0 | 593          | +7 <sup>+32</sup><br>- 0 |

| 42      | 1 | 1 | 0 | 0 |      | 0 | 1 | 0 | 0 | 1   | 0 | 0 | 579          | +2+32                    |

| 43      | 1 | 0 | 1 | 0 | 1    | 1 | 0 | 0 | 0 | 1   | 0 | 0 | 565          | +25+32                   |

| 44      | 0 | 0 | 0 | 1 | 0    | 1 | 0 | 0 | 0 | 1   | 0 | 0 | 552          | +32+32                   |

| 45      | 0 | 0 | 1 | 1 | 1    | 0 | 0 | 0 | 0 | 1   | 0 | 0 | 540          | +20+32                   |

| 46      | 0 | 0 | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 1   | 0 | 0 | 528          | +32+32                   |

**Table 3.7 Continued**

| ****    | Τ |   |   |   | SW1 |   |   |   | T |   | SW2 | <br>? |       |         |                     |

|---------|---|---|---|---|-----|---|---|---|---|---|-----|-------|-------|---------|---------------------|

| SECTORS | 8 | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 8 | 7 | · 6 | 5     | BYTES | SECTOR  | LAST SECTOR         |

| 47      | 1 | 0 | 1 | 0 | 0   | 0 | 0 | 0 | 0 | 1 | 0   | 0     |       | <br>517 | +21+32              |

| 48      | 0 | 1 | 0 | 1 | 1   | 1 | 1 | 1 | 1 | 0 | 0   | 0     | Į.    | 506     | +32+32              |

| 49      | 0 | 0 | 0 | 0 | 1   | 1 | 1 | 1 | 1 | 0 | 0   | 0     |       | 196     | +16+32              |

| 50      | 0 | 1 | 1 | 0 | 0   | 1 | 1 | 1 | 1 | 0 | 0   | 0     | 4     | 186     | +20+32              |

| 51      | 0 | 0 | 1 | 1 | 1   | 0 | 1 | 1 | 1 | 0 | 0   | 0     |       | 176     | +44+32              |

| 52      | 1 | 1 | 0 | 0 | 1   | 0 | 1 | 1 | 1 | 0 | 0   | 0     | 4     | 167     | +36+32              |

| 53      | 0 | 1 | 0 | 1 | 0   | 0 | 1 | 1 | 1 | 0 | 0   | 0     | 4     | 158     | +46+32              |

| 54      | 0 | 1 | 0 | 0 | 0   | 0 | 1 | 1 | 1 | 0 | 0   | 0     | 4     | 50      | +20+32              |

| 55      | 0 | 1 | 0 | 1 | 1   | 1 | 0 | 1 | 1 | 0 | 0   | 0     | 4     | 42      | +10+32              |

| 56      | 0 | 1 | 0 | 0 | 1   | 1 | 0 | 1 | 1 | 0 | 0   | 0     | 4     | 34      | +16+32              |

| 57      | 0 | 1 | 0 | 1 | 0   | 1 | 0 | 1 | 1 | 0 | 0   | 0     | 4     | 26      | +38+32              |

| 58      | 1 | 1 | 0 | 0 | 0   | 1 | 0 | 1 | 1 | 0 | 0   | 0     | 4     | 19      | +18+32              |

| 59      | 0 | 0 | 1 | 1 | 1   | 0 | 0 | 1 | 1 | 0 | 0   | 0     | 4     | 12      | +12±32              |

| 60      | 1 | 0 | 1 | 0 | 1   | 0 | 0 | 1 | 1 | 0 | 0   | 0     | 4     | 05      | +20 <sup>+32</sup>  |

| 61      | 0 | 1 | 1 | 1 | 0   | 0 | 0 | 1 | 1 | 0 | 0   | 0     | 3     | 98      | +42 <sup>+32</sup>  |

| 62      | 0 | 0 | 0 | 1 | 0   | 0 | 0 | 1 | 1 | 0 | 0   | 0     | 3     | 92      | +16+32              |

| 63      | 0 | 1 | 0 | 0 | 0   | 0 | 0 | 1 | 1 | 0 | 0   | 0     | 3     | 86      | +2+32               |

| 64      | 0 | 0 | 1 | 1 | 1   | 1 | 1 | 0 | 1 | 0 | 0   | 0     | 3     | 80      | o <sub>+</sub> 32   |

| 65      | 0 | 1 | 1 | 0 | 1   | 1 | 1 | 0 | 1 | 0 | 0   | 0     | 3     | 74      | +10+32              |

| 66      | 0 | 0 | 0 | 0 | 1   | 1 | 1 | 0 | 1 | 0 | 0   | 0     | 3     | 68      | +32+32              |

| 67      | o | 1 | 0 | 1 | 0   | 1 | 1 | 0 | 1 | 0 | 0   | 0     | 3     | 62      | +66+32              |

| 68      | 1 | 0 | 1 | 0 | 0   | 1 | 1 | 0 | 1 | 0 | 0   | 0     | 3     | 57      | +44+32              |

| 69      | 0 | 0 | 0 | 0 | 0   | 1 | 1 | 0 | 1 | 0 | 0   | 0     | 3     | 52      | +32+32              |

| 70      | 1 | 1 | 0 | 1 | 1   | 0 | 1 | 0 | 1 | 0 | 0   | 0     | 34    | 47      | +30+32              |

| 71      | 0 | 1 | 1 | 0 | 1   | 0 | 1 | 0 | 1 | 0 | 0   | 0     | 34    | 42      | +38+32              |

| 72      | 1 | 0 | 0 | 0 | 1   | 0 | 1 | 0 | 1 | 0 | 0   | 0     | 3:    | 37      | +56 <sup>+32</sup>  |

| 73      | 1 | 0 | 1 | 1 | 0   | 0 | 1 | 0 | 1 | 0 | 0   | 0     | 3:    | 33      | +11+32              |

| 74      | 0 | 0 | 0 | 1 | 0   | 0 | 1 | 0 | 1 | 0 | 0   | 0     | 3:    | 28      | +48+32              |

| 75      | 0 | 0 | 1 | 0 | 0   | 0 | 1 | 0 | 1 | 0 | 0   | 0     | 3:    | 24      | +20 <sup>+32</sup>  |

| 76      | 0 | 0 | 0 | 0 | 0   | 0 | 1 | 0 | 1 | 0 | 0   | 0     | ł     | 20      | 0 <sup>+32</sup>    |

| 77      | 1 | 1 | 0 | 1 | 1   | 1 | 0 | 0 | 1 | 0 | 0   | 0     | 3.    | 15      | +65 <sup>+32</sup>  |

| 78      | 1 | 1 | 1 | 0 | 1   | 1 | 0 | 0 | 1 | 0 | 0   | 0     | 31    | 11      | +62 <sup>+32</sup>  |

| 79      | 1 | 1 | 0 | 0 | 1   | 1 | 0 | 0 | 1 | 0 | 0   | 0     | 30    |         | +67 <sup>+32</sup>  |

| 80      | 0 | 0 | 0 | 0 | 1   | 1 | 0 | 0 | 1 | 0 | 0   | 0     | 30    | )4      | 0 <sup>+32</sup>    |

| 90      | 0 | 1 | 1 | 1 | 0   | 0 | 0 | 0 | 1 | 0 | 0   | 0     | 27    | 70      | +20 <sup>+32</sup>  |

| 100     | 1 | 1 | 0 | 0 | 1   | 1 | 1 | 1 | 0 | 0 | Ō   | Q     | 24    | 13      | +20 <sup>+32</sup>  |

| 110     | 1 | 0 | 1 | 1 | 1   | 0 | 1 | 1 | 0 | 0 | 0   | 0     | 22    | 21      | +10 <sup>+32</sup>  |

| 120     | 0 | 1 | 0 | 1 | 0   | 0 | 1 | 1 | 0 | 0 | 0   | 0     | 20    |         | +80 <sup>+32</sup>  |

| 130     | 1 | 1 | 0 | 1 | 1   | 1 | 0 | 1 | 0 | 0 | 0   | 0     | 18    |         | +10 <sup>+32</sup>  |

| 140     | 1 | 0 | 1 | 1 | 0   | 1 | 0 | 1 | 0 | 0 | 0   | 0     | 17    |         | +100 <sup>+32</sup> |

| 150     | 0 | 1 | 0 | 0 | 0   | 1 | 0 | 1 | 0 | 0 | 0   | 0     | 16    | 1       | +20 <sup>+32</sup>  |

| 160     | 0 | 0 | 0 | 1 | 1   | 0 | 0 | 1 | 0 | 0 | 0   | 0     | 15    |         | o <sub>+</sub> 32   |

<sup>&</sup>quot;0" indicates the OFF and "1" the ON status.

### SW1 (Mounting Location A3)

Fig. 3.13 Method of Assigning the Number of Sectors

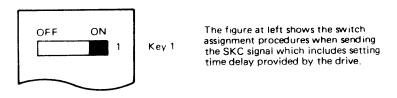

#### 3.6.7 Delay SKC

This is used to select whether or not to include settling time when SEEK COM-PLETE is sent to the interface. The switch assignment procedure are shown in Table 3.8 and Fig. 3.14.

Table 3.8 DELAY SKC

|                        | SW3   |    |     |

|------------------------|-------|----|-----|

| Signal Name            | Key 1 | 1  |     |

| Include settling time  | 0     | 0: | ON  |

| Does not settling time | X     | X: | OFF |

### SW3 (Mounting Location B5)

Fig. 3.14 DELAY SKC

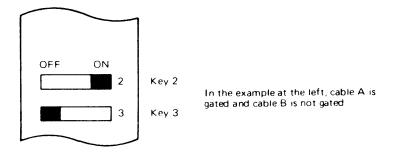

#### 3.6.8 Controlling the Basic Drive Select Signals

Even when the relevant drives are not selected, the four basic signals (such as, INDEX, DRIVE READY, SECTOR/BYTE CLOCK and SEEK COMPLETE) can be sent to the interface cables (both A and B). The method of sending these signals is shown in Table 3.9 and Fig. 3.15.

**Table 3.9 Drive Selection Control**

| Cable A       | SW3   | 0.11- 0       | SW3   |  |

|---------------|-------|---------------|-------|--|

|               | Key 2 | Cable B       | Key 3 |  |

| Gate          | 0     | Gate          | 0     |  |

| Does not gate | ×     | Does not gate | ×     |  |

#### SW3 (Mounting Location B5)

Fig. 3.15 Drive Selection Control

#### 3.6.9 **Time Margin Measurement Switch**

This is a switch for measuring time margins. Set this switch to OFF only when measuring margins.

#### SW2 (Mounting Location A2)

Fig. 3.16 Time Margin Measurement Switch

# 3.6.10 Timing Specification Selection

The drive utilizes SW5 (Mounting Location M3) to provide SA4000 interface compatibility.

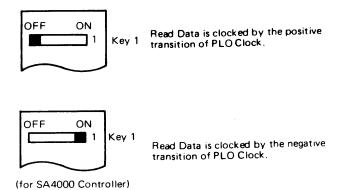

#### (1) PLO Clock and Read Data

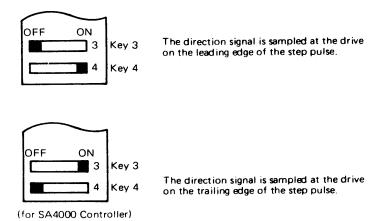

# (2) Direction and Step Pulse

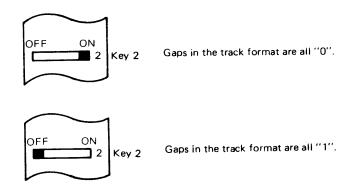

#### (3) Track Format Selection

#### 3.6.12 Media Error

(1) Media Error Display Method

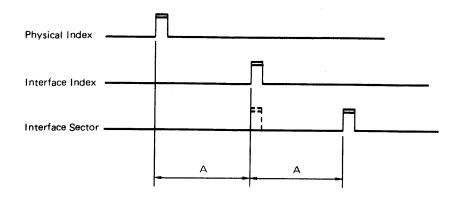

A media defect is displayed by Cylinder Address, Head Address, Position (bytes from Physical Index) and Defect Length (bits). The maximum media defect length is 64 bytes (512 bits). The Physical Index represents the Index Pattern Division recorded on the clock track. The relationships of the Physical Index and Interface Index/Sector are shown below.

- A: This represents the number of bytes of one sector.

- (2) Relation of the Defective Area Display Value and the defective Sector.

- (i) Calculation of the defect Area

Defect Position: B bytes Defect Length: C bits

$C \div 8 = C' \dots$  remainder C''

C÷ 6 - C . . . . remainder C

Defect Area:  $B \sim B + C'$   $(C'' \le 1)$  $B \sim B + C' + 1$   $(2 \le C' \le 7)$

(ii) Calculation of a Defect Sector Number

A Defective Sector Number can be calculated by using the following formula.

Defective sector number =  $\left[\frac{X}{A}\right] - 1$

Note 1: X: Defective position display value

A: Number of bytes of one sector

[ ]: This indicates that all the numbers after the decimal point are to be omitted.

For example, [2.3] = 2

1: Compensates for the difference between Physical and Interface Index.

Note 2: The sector next to the index is assumed to be the 0 sector.

# (3) Examples of Defect Sector Number Calculation

$$X = 800 \sim 802$$

Defect Sector =

$$[\frac{800}{304}] - 1$$

= 2 - 1 = 1

Defect Sector =

$$\left[\frac{800}{304}\right] - 1$$

= 2 - 1 = 1

1 Sector is detective.

$$X = 286 \sim 346$$

$\bigcirc X = 286$

Defect Sector =

$$\left[\frac{286}{304}\right] - 1$$

= 0 - 1 = -1

Defect Sector =

$$[\frac{346}{304}] - 1$$

= 1 - 1 = 0

O Sector and N (last) Sector are defective.

# Section 4 Theory of Operation

#### 4. THEORY OF OPERATION

#### 4.1 GENERAL

This section consists of three parts. The first concerns major assembles of the device. The second takes up the magnetic head and magnetic disk. These are part of the disk enclosure, however, they are explained below because they are closely related to the electric control portion. The last describes electric control such as interface, R/W, etc.

#### 4.2 OPERATION OF MECHANICAL PORTION

#### 4.2.1 Disk Enclosure

In the disk enclosure (DE), disks, spindle, actuator, heads, etc., are protected by a sealed plastic cover. Each of these parts can be seen through the plastic cover. The disk enclosure is sealed at the factory after assembly, and must not be opened in the field.

Fig. 4.1 Appearance of the Unit

# 4.2.2 Spindle

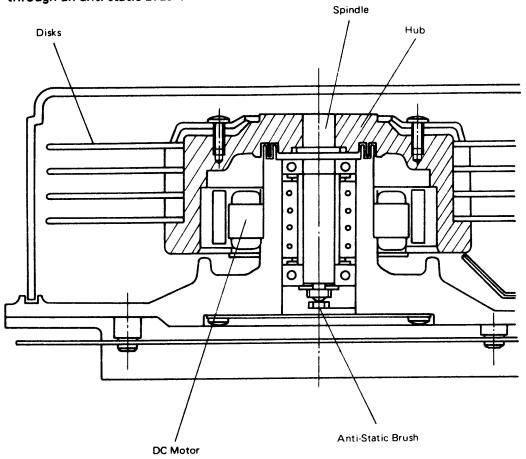

The disk spindle is fixed to the base of the DE from the top side.

The base is sealed to prevent the intrusion of air through the bearings. At the top of the spindle is a hub, to which recording media are fitted. A DC motor is set concentrically with the spindle to drive the disks. The spindle is grounded to the DE through an anti-static brush.

Fig. 4.2 Spindle

# 4.2.3 Carriage Assembly

Carriage assembly consists of a four-phase stepping motor, band actuator, viscous damper, and carriage with linear bearings. The assembly is controlled by a special driving circuit which achieves an average positioning time of 70ms. In addition to high speed, the structure of the assembly gives increased reliability.

Fig. 4.3 Carriage Assembly

If the disks do not rotate, the heads rest on the disk surface. Therefore, during maintenance or when transporting the drive, the carriage must be locked to protect the heads.

#### 4.2.4 Air Circulation in DE

The unit is provided with CSS heads which have a flying height of about 0.45 microns. Therefore, a small dust-particle could cause a head crash. For this reason the DE is perfectly sealed. There are two filters. One for breathing, the other one is for recirculation to keep the air inside the DE clean.

The filter for breathing serves:

- (1) To prevent suction near the spindle when it starts rotating.

- (2) To prevent the intrusion of dust into the DE, when the air pressure inside of the DE decreases due to the difference in temperature between the inside of the DE and the atmosphere.

The recirculation filter is fitted inside of the pipe which forms a closed loop in the DE. When suction occurs by virtue of the rotation of the spindle, the air in the DE circulates through the closed loop. Thus the air circulates continuously whenever the spindle is rotating to keep it clean.

These two filters can eliminate 99.97% of contaminates with a particle size larger than 0.3 micron.

Fig. 4.4 Air Circulation Inside the DE

# 4.3 MAGNETIC HEADS AND RECORDING MEDIA

#### 4.3.1 Magnetic Heads

To accomplish high density recording, CONTACT START/STOP (CSS) flying heads are employed. The heads fly on the surface air flow generated by the rotating disk. The CSS system differs from the conventional ramp load system in that the heads are always over the recording media and rest on the disk surface when the disk is not rotating.

Therefore, the head and disk make contact, and the wear caused by this contact must be minimized. For this reason, the CSS type head is lightly loaded and the surface pressure is reduced by using a tapered flat slider such as that shown in Fig. 4.6. The slider has 3 rails. The air intake end of the slider is tapered to obtain flying force by means of the air flow over the disk surface. Reads and writes are performed by a ferrite core at the rear of the head, the minimum flying height position.

Fig. 4.5 Read/Write Head

Fig. 4.6 Structure of Head Slider

# 4.3.2 Recording Media (Magnetic Disk)

A magnetic disk is made of an aluminum substrate on which magnetic material is coated, measures 200mm (8 inches) in diameter, and 2mm in thickness. It is used to store data. Because of the CSS characteristic of the drive, the media surface is lubricated with a special lubrication in order to prevent wear. Up to four disks are installed for a maximum storage capacity of 23.4M bytes.

The index information is stored in the outer circumference (beyond the data field) on the under side of the lowest disk.

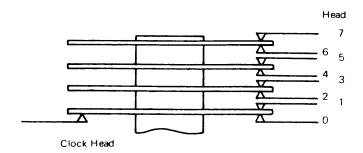

### 4.3.3 Head and Surface Configuration

#### 4.3.4 Clock Track Format

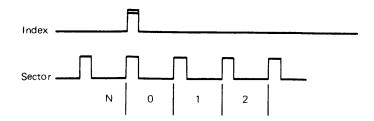

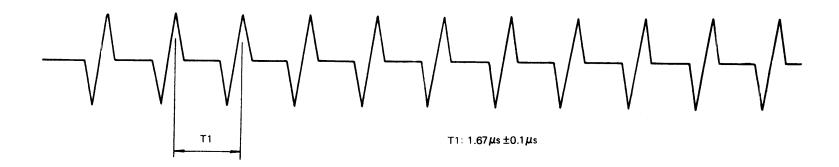

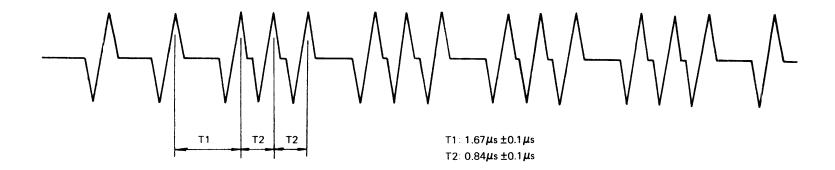

As was described in 4.3.2, the clock track is the outermost track on the bottom surface. It contains  $12,000^{+32}_{-0}$  data intervals for generating clock signals as well as one index pattern.

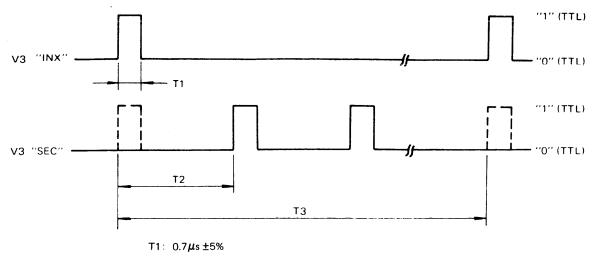

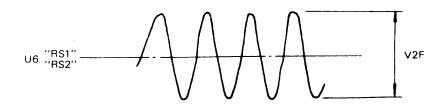

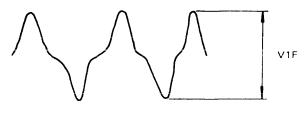

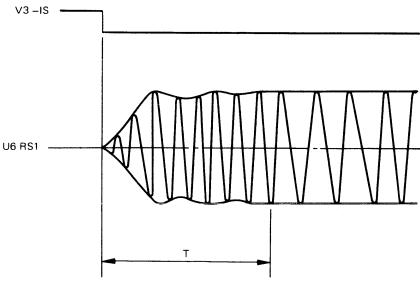

Fig. 4.7 shows the clock signal waveform and index pattern waveform.

# (1) Clock Signal Waveform

# (2) Index Pattern Waveform

Fig. 4.7 Clock Signal Waveform/Index Pattern Waveform

#### 4.4 FORMAT

#### 4.4.1 General

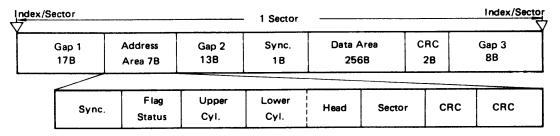

A sector (or record) is used to allocate addresses. Each sector has an address areas (AA) which ensure that the correct sector is located, and a data area (DA) in which data is stored.

The index and sector signals are used to inform the controller of the beginning of a track and sector. The sector format is determined by the control unit. On the other hand, the device must be set to generate the desired fixed length sector format by means of switches.

A fixed length format of 80 sectors is described as an example in this section.

#### 4.4.2 Track Format

Example of a format of 80 sectors.

Note: (1) The format shown here is only an example and the construction of an optimum format compatible to the system is possible.

(2) A different SYNC BYTE pattern between the address area and the data area is permissible. A recommended pattern is "0E" and "09" (Hex.) respectively.

#### 4.4.3 Detail of The Format

(1) GAP 1

The gap allows for displacement of the head, circuit tolerances, and write to read transient after write operation under worst case conditions. The gap must be a minimum of 16 bytes, in which all "O"s are written.

(2) SYNC BYTE

This shows the starting point of the address area.

A recommended pattern is "OE" (Hex.).

(3) FLAG STATUS/LOGICAL UNIT

This shows the status of each sector (record).

Normal record, spare record, or replacement record may be indicated here. However, its meaning is defined by the control unit.

(4) UPPER CYLINDER ADDRESS/LOWER CYLINDER ADDRESS

This indicates the cylinder address on the track.

(5) HEAD ADDRESS

This indicates the head address on the track.

(6) SECTOR ADDRESS

This indicates the sector (record) address on the track.

(7) CRC (CYCLIC REDUNDANCY CHECK)

This is the area which checks whether the data was correctly read.

#### (8) GAP 2

This is an area where a write splice would occur when the data area of the sector was updated. Since the read circuit may be reactivated after the write Splice area, all "0" must be written in this 12 or more Byte area. The read circuit requires an "0"s area to synchronize read circuits.

# (9) SYNC BYTE Indicates the beginning of the data area.

#### (10) DATA AREA

This is the area where data is written and read.

(11) CRC See (7)

#### (12) GAP 3

This is pad time required by the control unit. All "0"s are written in this 6 Byte area.

#### 4.5 INTERFACE

#### 4.5.1 General

Logical and physical conditions for the reception/transmission of signals in the interface of a 112/114 micro disk drive are described in this chapter.

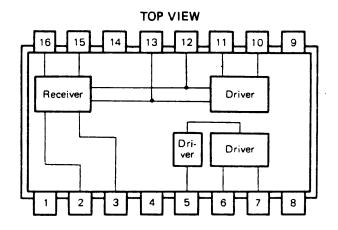

# (1) Connection

There are two connectors for external connection on this unit. These are called "A" and "B" connectors. The cables connected to these are called cable "A" and cable "B". "A" cables may be connected in daisy chain. When this configuration is utilized, the terminator must be removed from all but the last drive. See Fig. 3.7. The "B" cable is connected in a radial fashion. Therefore, the control unit, requires "B" cables and connectors in proportion to the number of drives connected.

#### (2) Timing Specification

The timing specifications for signals are referenced at the connector position of the unit. Consequently, with regard to the signal timing from the unit, time lag of the cable, and time lag due to the number of circuit stages in the control unit must be considered.

# (3) Interface Transmission Level

There are two types of interface drivers and receivers used. For the high frequency signal lines, balanced line differential devices are used. These lines are indicated by "(1 pair)" in the diagrams below. The control and select lines are TTL level and 0 volt is active or true.

# 4.5.2 Type and Name of Signal Line

# (1) A Cable Signal Line

|                       | Controller Side   | Drive Side        |           |

|-----------------------|-------------------|-------------------|-----------|

| (3)                   | HEAD SELECT 0~2   | INDEX             | (1)       |

|                       |                   | READY             | (1)       |

| (4)                   | DRIVE SELECT 1~ 4 |                   |           |

| (1)                   | DIRECTION         | SECTOR/BYTE CLOCK | (1)       |

| (1)                   | STEP              | WRITE FAULT       | (1)       |

| (1)                   | FAULT CLEAR       | TRACK 0           | (1)       |

| (1)                   | WRITE GATE        |                   |           |

|                       |                   | (SEEK COMPLETE)   | (1)*      |

| (1)                   | READ GATE         |                   |           |

| *(1 pair) WRITE DATA  |                   | READ DATA         | (1 pair)* |

| *(1 pair) WRITE CLOCK |                   | PLO CLOCK         | (1 pair)* |

| 12 line + 2 pairs     |                   | 6 line + 2 pairs  |           |

<sup>\*</sup> This signal line is connected by a switch setting on the PCB.

# (2) B Cable Signal Line

|                      | INDEX             | (1)      |

|----------------------|-------------------|----------|

|                      | READY             | (1)      |

|                      | SECTOR/BYTE CLOCK | (1)      |

|                      | SEEK COMPLETE     | (1)      |

| (1 pair) WRITE DATA  | READ DATA         | (1 pair) |

| (1 pair) WRITE CLOCK | PLO CLOCK         | (1 pair) |

| 2 pairs              | 4 line + 2 pairs  |          |

#### 4.5.3 Signal Lines

#### (1) Input Signals

#### (a) HEAD SELECT 0 ~ 2

These binary coded signal lines select one of eight data heads positioned in the disk drive.

#### (b) DRIVE SELECT 1 ~ 4

These signal lines enable the input/output signals of the disk drive having a matching logical unit number. Each line selects one drive. The signal line of DRIVE SELECT 4 can be changed to the SEEK COMPLETE signal by a switch setting on the PCB.

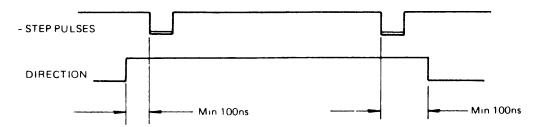

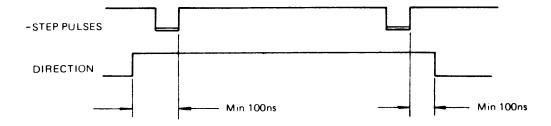

#### (c) DIRECTION

This indicates the seek direction of the data heads when STEP PULSES are sent to the disk drive. When this signal is TRUE, it causes a seek in the inner direction. And if this signal is FALSE, this causes a seek in the outer direction (Toward track 0).

#### (d) STEP

This signal triggers the carriage to move the data heads one track in the direction indicated by the DIRECTION signal. The following three step modes are provided.

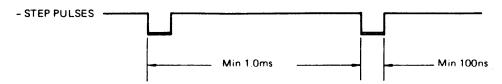

#### i) Controlled Step Mode

If the step pulse rate is 1kHz or less, the drive performs a seek one track in response to one STEP pulse from the controller.

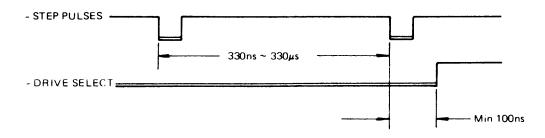

#### ii) Slave Step Mode

If the step pulse rate is more than 3kHz but less than 3MHz the drive does not perform SEEK individually in response to each STEP signal from the controller, but rather starts the seek operation after receiving all STEP pulses from the controller. The drive will then move the heads at high speed to the desired track according to an ideal velocity curve stored in ROM.

When the SEEK operation is finished, the drive responds by sending the SEEK COMPLETE signal.

Note: STEP RATE of 1kHz to 3kHz is prohibited.

#### iii) Return to Zero Mode

When the drive has received more than 255 step pulses in the slave step mode, it performs a SEEK at normal speed to TRACK 0.

#### (e) FAULT CLEAR

This signal line resets the write fault latch. The width of the pulse must be greater than 100ns.

#### (f) WRITE GATE

This signal line gates write current to the selected data head.

#### (q) READ GATE

This signal line gates read data from the selected data head to the data separator. Separated READ DATA and READ CLOCK are then provided to the interface. READ GATE is valid when  $5.0\mu s$  (6-byte) have elapsed after READ GATE is active.

#### (h) WRITE DATA (Balanced Transmission)

This is the write data signal in NRZ format.

The signal is sent out by the controller using balanced line transmission levels.

The WRITE DATA signal is synchronized by the trailing edge of WRITE CLOCK IN THE DRIVE. WRITE DATA may be input to either the A or B cable depending on the switch setting on the PCB.

#### (i) WRITE CLOCK (Balanced Transmission)

This is the WRITE CLOCK signal from the controller synchronized with WRITE DATA. WRITE CLOCK may be input to either the A or B cable dependings on the switch setting on the PCB. This signal is derived from the PLO Clock generated in the drive and sent to the controller.

#### (2) Output Signals

#### (a) Index

This pulse is sent out at the rate of once per revolution of the disks. The width of a pulse is  $0.8\mu s$ . This signal is available to both the A and B cables.

#### (b) Ready

This signal indicates that the drive is selected and the disks are rotating at the correct speed. (The PLO circuit synchronizes with the speed of the disk). This signal is available to both the A and B cables.

#### (c) SECTOR (BYTE CLOCK)

Either SECTOR Pulses or BYTE CLOCK is available through the selection of a switch on the PCB on the drive. This signal is available to both the A and B cables.

#### i) BYTE CLOCK

This is a pulse which occurs  $24,320^{+32}_{-0}$  times on the track. The width of pulse is  $0.42\mu$ s.

#### ii) SECTOR PULSE

The number of SECTOR pulses which occur per revolution of the disks is switch selectable. The pulse is generated by counting the number of bytes within one sector. One sector may contain a maximum of 4,095 bytes. The width of this pulse is  $0.8\mu s$ .

#### (d) TRACK 0

This indicates that the data heads are at Track 0.

#### (e) WRITE FAULT

This indicates that one of the following fault conditions occurred during WRITE. The WRITE FAULT is retained until it is reset by a FAULT CLEAR pulse.

- i) WRITE GATE is sent out when the drive is not READY.

- ii) WRITE GATE and READ GATE are sent at the same time.

- WRITE GATE is sent when two Head ICs are selected at the same time.

- iv) WRITE GATE is sent when SKC (seek complete) is false.

- v) During WRITE, a normal write current does not flow to the data head.

#### (f) READ DATA (Balanced Transmission)

These lines transmit the recovered data in the form of NRZ data synchronized with PLO clock. The READ DATA becomes valid 5.0µs after the leading edge of READ GATE. READ DATA is available to both the A and B cables when enabled by a switch on the PCB.

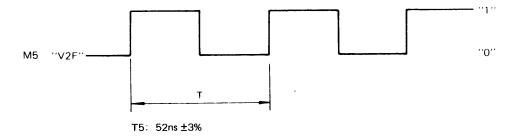

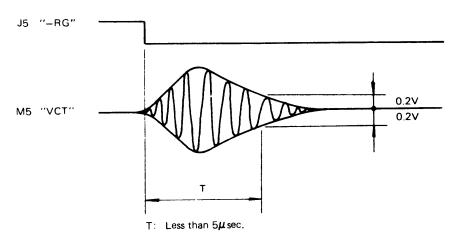

#### (g) PLO CLOCK (Balanced Transmission)

This pulse is sent out every other bit. When READ GATE is false, the PLO CLOCK is synchronized with the pulse read from the clock track. When READ GATE is true, the PLO is synchronized with the READ DATA from the data head. The controller uses the PLO CLOCK during a write operation as WRITE CLOCK. PLO CLOCK is available to both the A and B cables when enabled by a switch on the PCB. This pulse is selectable by a switch key to provide a normal or inverted triggering.

#### (h) SEEK COMPLETE

The SEEK COMPLETE signal indicates that the selected data head in the drive is positioned over the required track. This signal may contain the settling time for the seek operation. A READ/WRITE operation is legal the instant this signal turns TRUE. This signal is available to both the A and B cables, however, in case of CNA it is enabled by a switch key on the PCB.

# 4.5.4 Timing Specifications

# (1) SEEK Timing

#### **CONTROLLED STEP MODE**

# **SLAVE STEP MODE**

# (i) Key 3 - OFF and key 4 - ON on SW5

# (ii) Key 3 - ON and key 4 - OFF on SW5

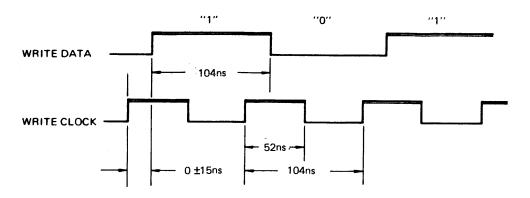

# (2) WRITE/READ DATA Timing WRITE DATA, WRITE CLOCK

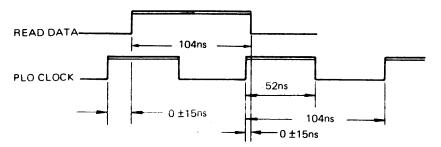

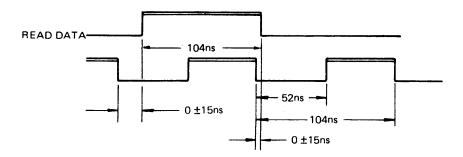

# **READ DATA, PLO CLOCK**

# (i) Key 1 - OFF on SW5

# (ii) Key 1 - ON on SW5

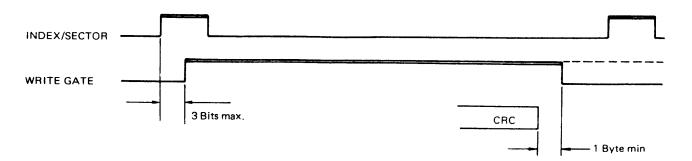

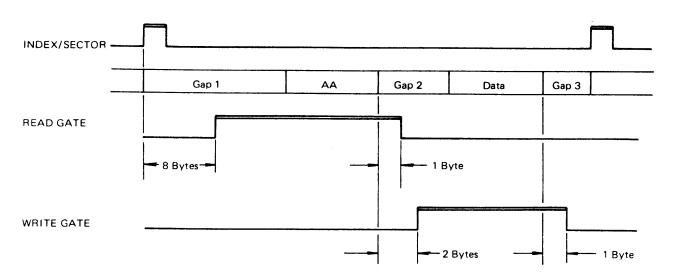

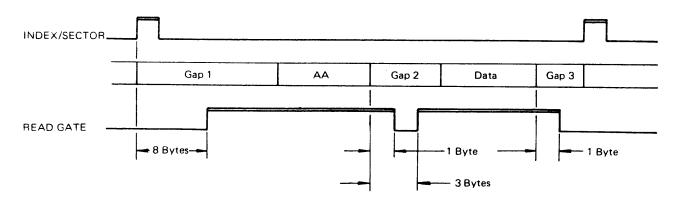

# 4.5.5 Format Timing Specification

# (1) Format Write

# (2) Data Write

#### (3) Data Read

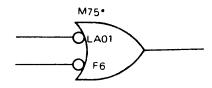

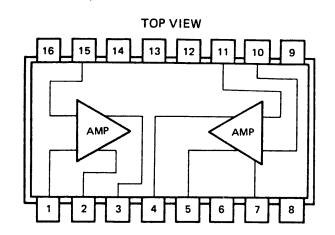

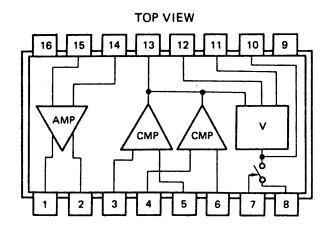

#### 4.5.6 Driver/Receiver

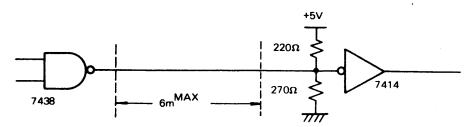

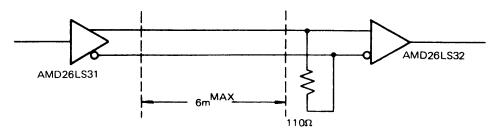

Both types of Driver/Receivers used on the drive are shown in the following diagram. The maximum cable length specification includes all cables from the controller to the last drive when the A cable is daisy chained.

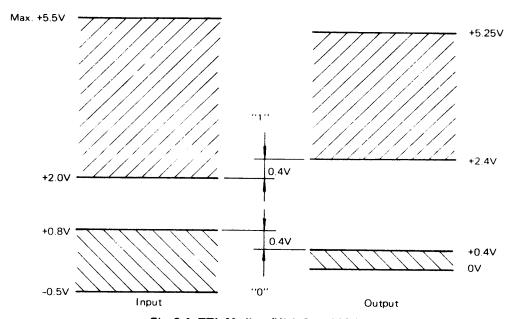

#### Control signal (TTL)

#### R/W signal (Balanced Transmission)

R/W signal (Balanced Transmission)

#### 4.5.7 Pin Assignment in Connectors

#### **CNA**

| 1  | GND         | 2  | -HEAD SELECT 0     |

|----|-------------|----|--------------------|

| 3  | "           | 4  | " 1                |

| 5  | "           | 6  | " 2                |

| 7  | "           | 8  | SPARE              |

| 9  | "           | 10 | -INDEX             |

| 11 | <b>"</b>    | 12 | -READY             |

| 13 | "           | 14 | -SECTOR/BYTE CLOCK |

| 15 | "           | 16 | -DRIVE SELECT 1    |

| 17 | "           | 18 | " <b>2</b>         |

| 19 | "           | 20 | " 3                |

| 21 | "           | 22 | " 4                |

| 23 | "           | 24 | -DIRECTION         |

| 25 | ,,          | 26 | -STEP              |

| 27 | ,,          | 28 | -FAULT CLEAR       |

| 29 | "           | 30 | -WRITE GATE        |

| 31 | "           | 32 | -TRACK 0           |

| 33 | "           | 34 | -WRITE FAULT       |

| 35 | •           | 36 | -READ GATE         |

| 37 | "           | 38 | GND                |

| 39 | +WRITE DATA | 40 | -WRITE DATA        |

#### CNA (continued)

| 41 | GND          | 42 | -WRITE CLOCK |

|----|--------------|----|--------------|

| 43 | +WRITE CLOCK | 44 | GND          |

| 45 | +PLO CLOCK   | 46 | -PLO CLOCK   |

| 47 | GND          | 48 | +READ DATA   |

| 49 | -READ DATA   | 50 | GND          |

Key slot: Between 8P and 10P.

#### **CNB**

| 1  | -INDEX             | 2  | GND          |

|----|--------------------|----|--------------|

| 3  | -READY             | 4  | "            |

| 5  | -SECTOR/BYTE CLOCK | 6  | "            |

| 7  | -SEEK COMPLETE     | 8  | "            |

| 9  | +WRITE DATA        | 10 | -WRITE DATA  |

| 11 | GND                | 12 | +WRITE CLOCK |

| 13 | -WRITE CLOCK       | 14 | GND          |

| 15 | +PLO CLOCK         | 16 | -PLO CLOCK   |

| 17 | GND                | 18 | +READ DATA   |

| 19 | -READ DATA         | 20 | GND          |

Key slot: Between 8P and 10P.

#### CNC

| 1 | +24V     | 2 | +24V RTN |

|---|----------|---|----------|

| 3 | -12V RTN | 4 | -12V     |

| 5 | +5V      | 6 | +5V RTN  |

#### 4.6 ELECTRIC CIRCUIT OPERATION

#### 4.6.1 Block Diagram

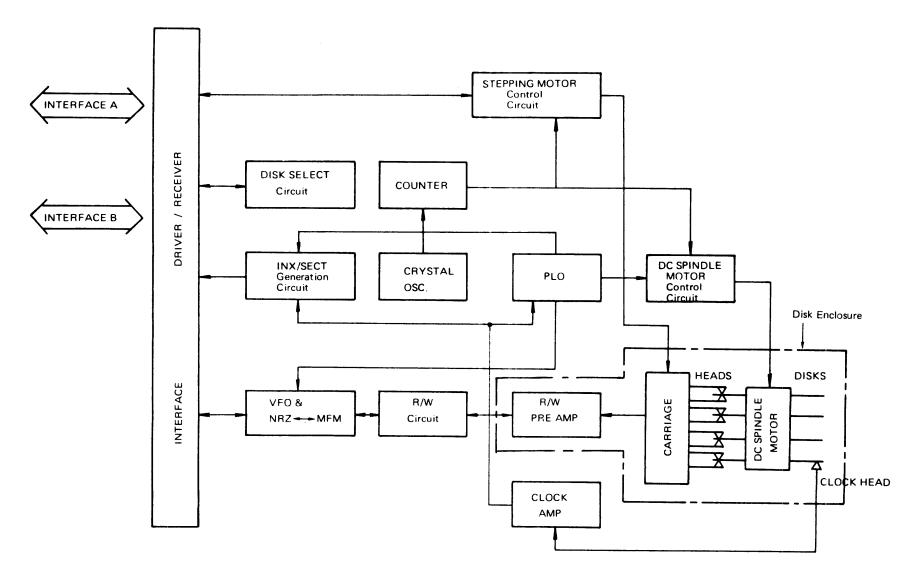

The block diagram for the electric circuit is shown in Fig. 4.8.

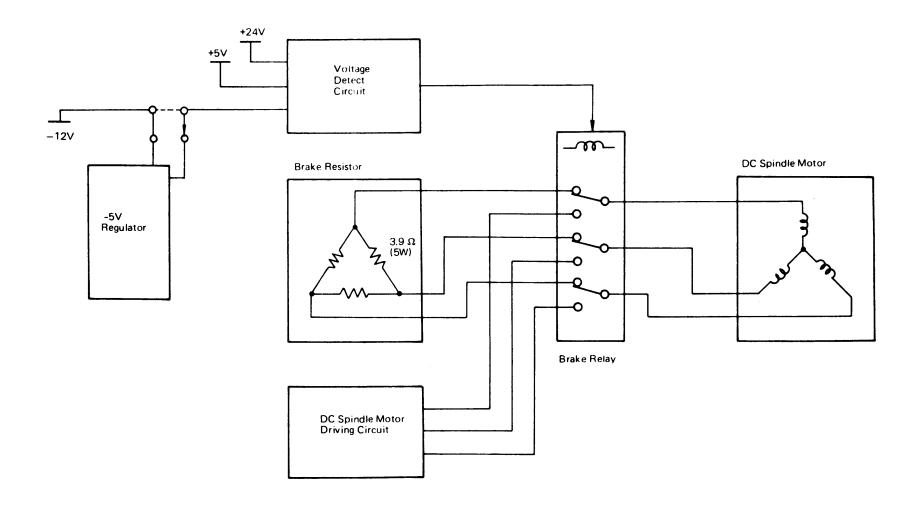

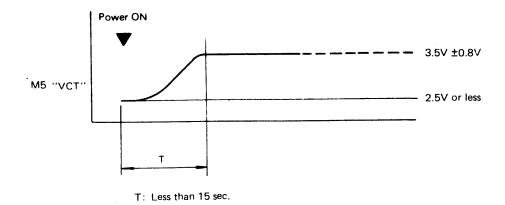

#### 4.6.2 Start/Stop Circuit

When all DC voltages are applied to the unit, the brake relay is opened and the driving circuit of the DC spindle motor is enabled, thus turning the disks. The speed of the spindle motor is monitored by an internal timer. When the disks are rotating at the correct speed, the stepping motor is energized, and the SEEK COMPLETE and the READY signals are sent to the interface. When the power is turned off, the brake relay is closed, and the DC motor is connected to the brake resistor from the driving circuit. This brakes the DC motor and the disk comes to a complete stop in about 25 seconds.

When power is applied to the circuit, a recalibrate to track zero sequence is initiated automatically, and heads are located at cylinder 0 before the Ready Signal goes true.

Fig. 4.8 Block Diagram

Fig. 4.9 Start/Stop Circuit Block Diagram

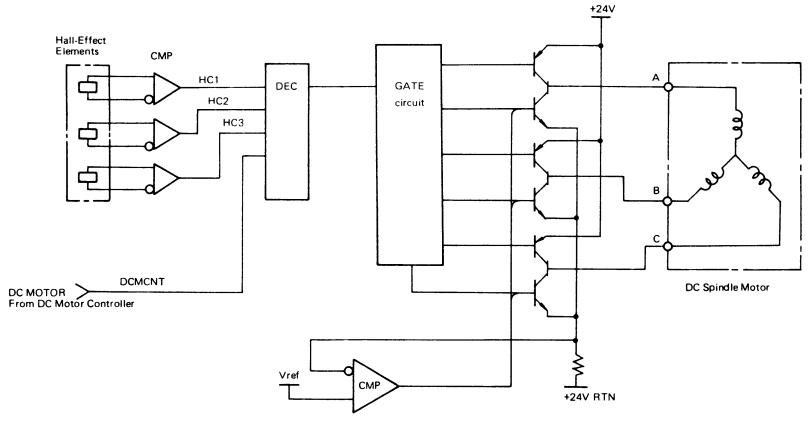

# 4.6.3 DC Spindle Motor Driving Circuit

The integral DC spindle motor consists of 4-poles with a 3-phase outer rotor. The detection of the rotation angle is conducted by three hall-effect elements fitted into the motor.

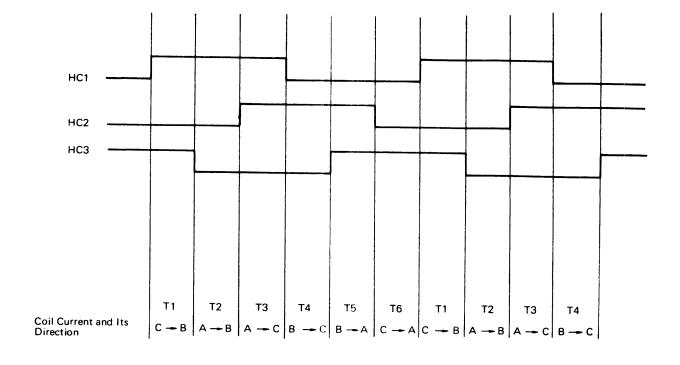

The motor driving circuit controls the coil current of the motor by sensing the three pairs of output signals from the hall-effect elements. The driving circuit also serves to detect the coil current of the motor in order to regulate the current required during start-up, and if the value exceeds specification, the circuit turns off the coil current. Fig. 4.10 shows the block diagram of the DC spindle motor driving circuit. Fig. 4.11 shows the timing chart.

#### 4.6.4 DC Spindle Motor Controller

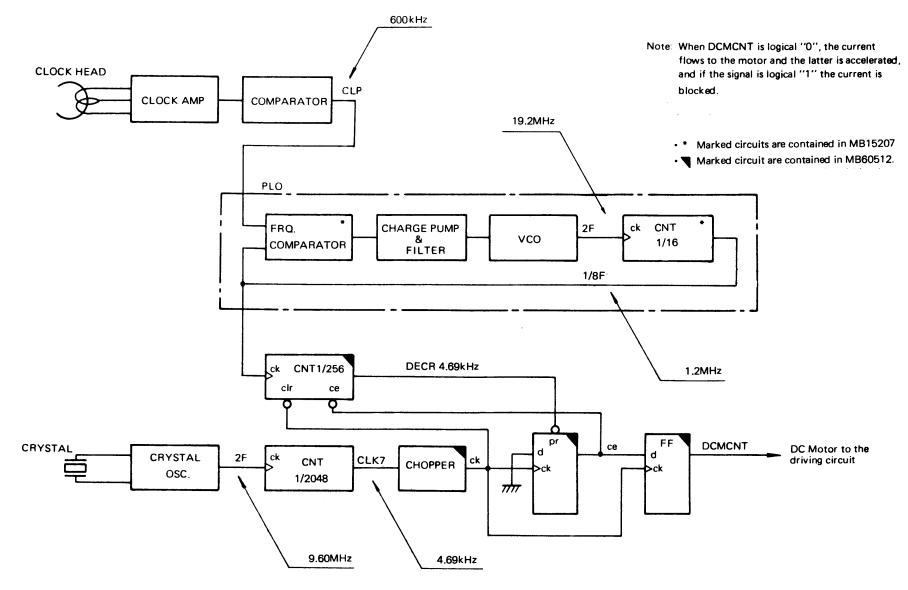

The DC spindle motor controller controls the rotational speed so that it falls within the range 2964 rpm ±2% by comparing the reference frequency of signals generated by the internal oscillator with the frequency of clock signals from the clock head on the lower disk.

Fig. 4.12 shows the block diagram of the DC spindle motor controller, and Fig. 4.13 shows the timing chart.

#### 4.6.5 Unit Select Operation

The unit may be configured as logical unit number 1, 2, 3 or 4 by setting the proper switch keys on the PCB. The select operation enables the interface of the drive with the logical unit designated by the controller. The drive is selected when the logical unit number compares with the drive select 1 to 4 signals from the controller. Refer to Section 3.6.1 for the setting procedure.

Note: DCMCNT is the signal which controls the speed of the DC spindle motor.

When DCMCNT is logical "1", it blocks current to the motor. When DCMCNT is logical "0", it permits the current to flow.

Fig. 4.10 DC Spindle Motor Driving Circuit Block Diagram

Fig. 4.11 DC Spindle Motor Driving Circuit Timing Chart

Fig. 4.12 DC Spindle Motor Control Block Diagram

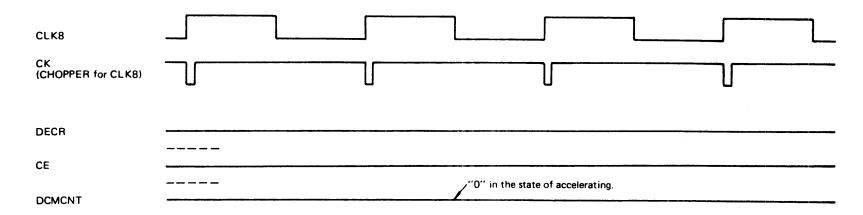

(1) During Acceleration (when motor is rotating slowly) DCMCNT is "0".

(2) During Deceleration (when the motor is rotating fast) DCMCNT is "1".

Fig. 4.13 DC Spindle Motor Control Timing Chart (1)

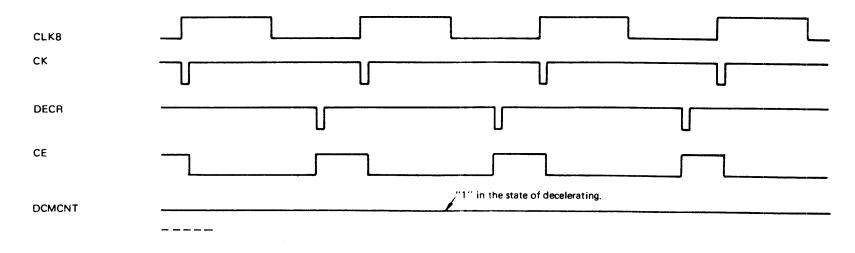

(3) Under Control (the speed of rotation is controlled to the 2964 rpm  $\pm 2\%$ ).

Fig. 4.13 DC Spindle Motor Control Timing Chart (2)

#### 4.6.6 SEEK Control

#### (1) General

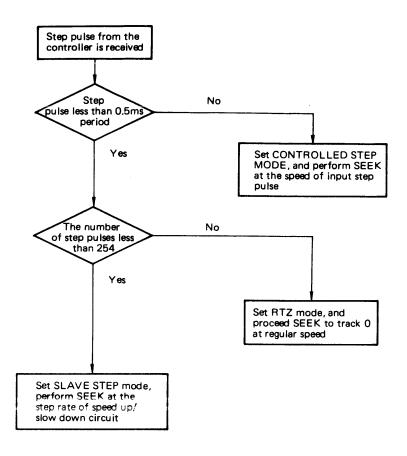

There are two modes of operation for the head positioning stepper motor: controlled step mode and slave step mode. The seek control circuit monitors the frequency of the step pulse transmitted from the controller to the drive, and if the input frequency is less than 1kHz, the controlled step mode is automatically selected. If the input frequency is over 3kHz, the slave step mode is automatically selected. However both the step rates of 1kHz to 3kHz and over 3MHz are prohibited.

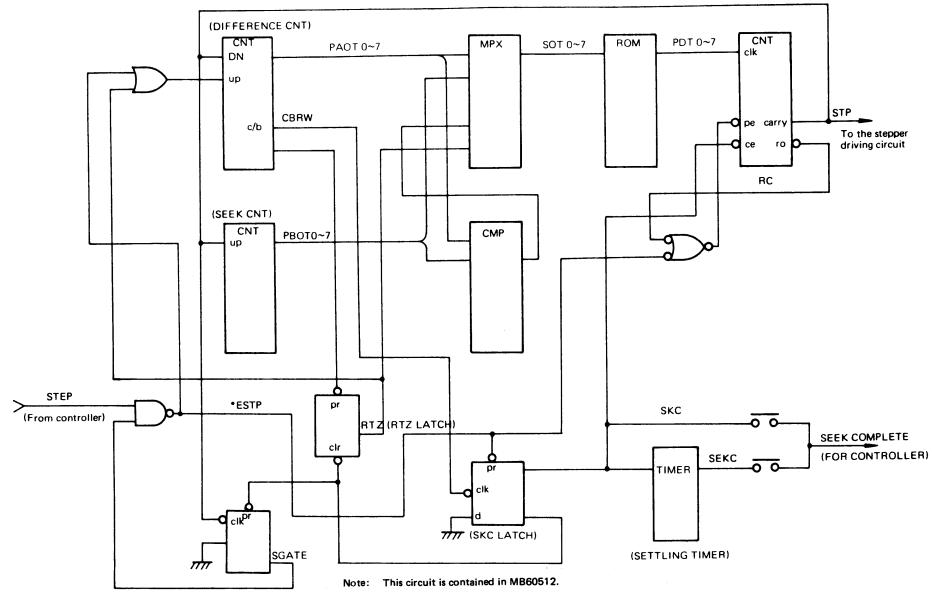

When 255 or more step pulses are received in slave mode, the drive will automatically return the heads to track 0. This operation is called RETURN TO ZERO (RTZ). Fig. 4.14 shows the block diagram of seek control. Fig. 4.15 shows the flowchart.

#### (2) Controlled Step Mode

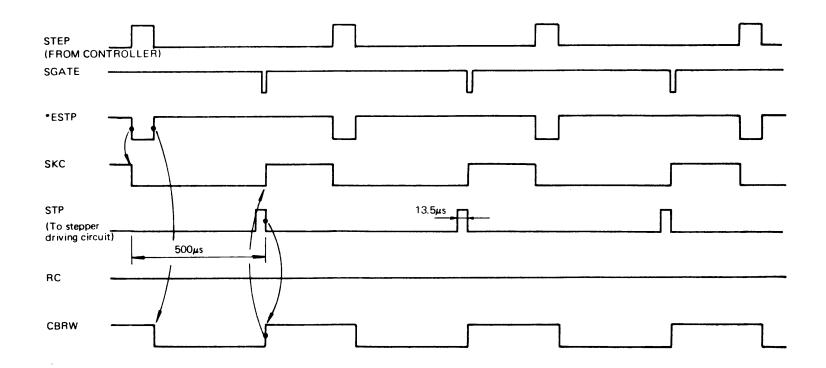

In this mode, the stepper motor performs a SEEK directly controlled and synchronized with the step pulse sent from the controller. The direction of the seek is controlled by the DIRECTION line from the controller. Fig. 4.16 shows the timing chart of controlled step mode.

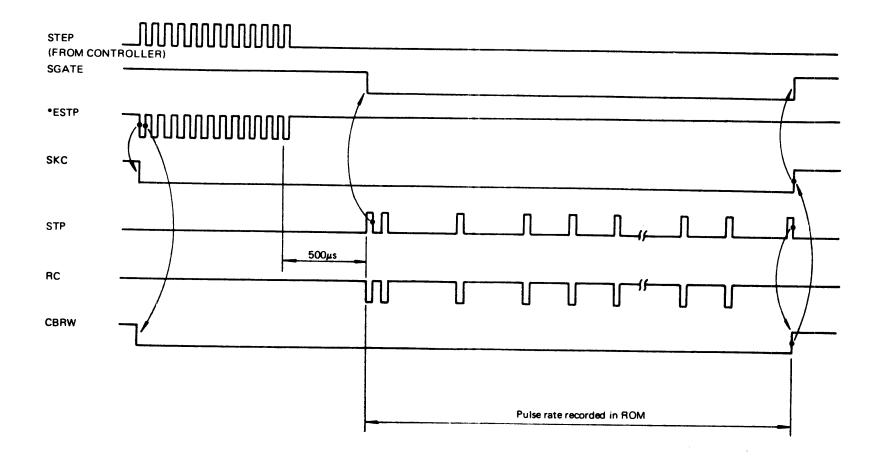

#### (3) Slave Step Mode

In this mode, the seek is performed by step pulses generated by the speed up/slow down circuit within the drive. After receiving and storing all step pulses in the 3kHz to 3MHz range, coming from the controller, the seek is controlled automatically by the drive in order to complete the operation in the least amount of time.

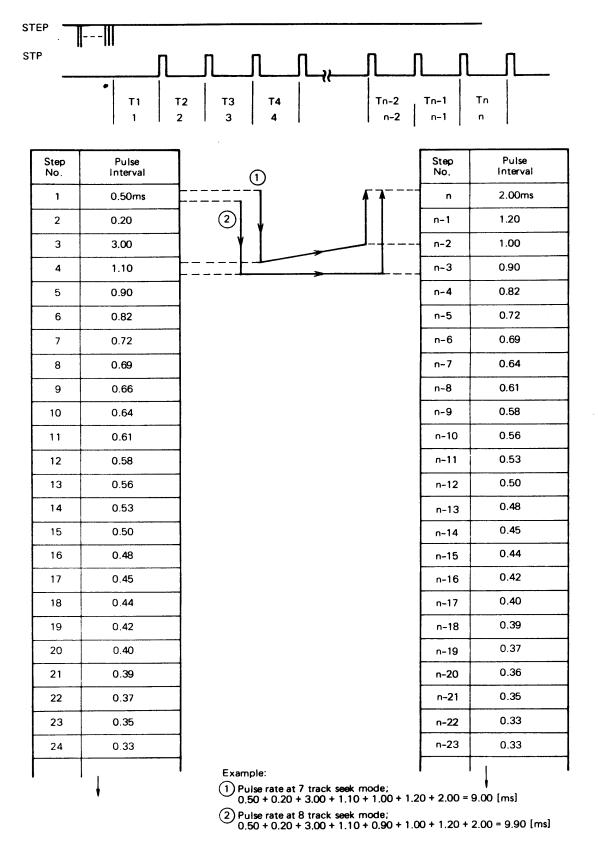

The step rate of the speed up/slow down circuit is stored in ROM which is accessed in the Slave Step mode according to the value of the seek counter and the difference counter. The pulse train is formed depending on the data read out from ROM. Fig. 4.17 shows the timing chart. Fig. 4.18 shows the step rate of speed up/slow down.

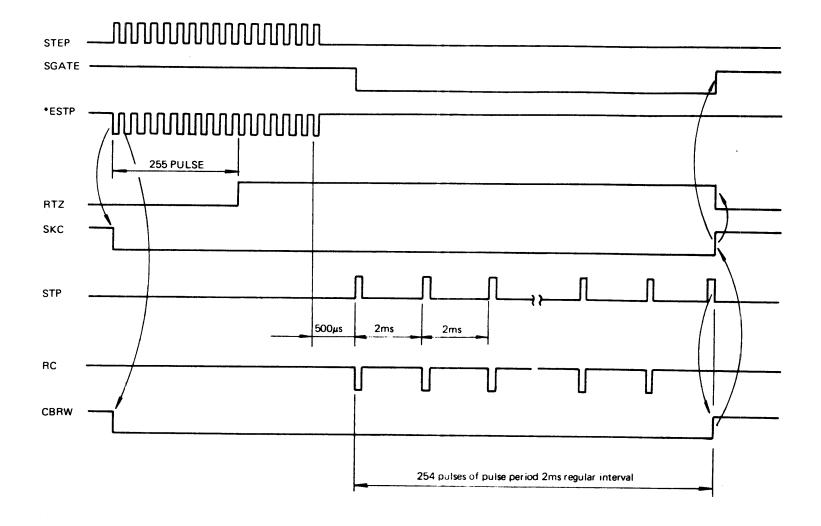

#### (4) RTZ Mode

When more than 255 step pulses in slave step mode are received from the controller, the internal difference counter is kept at 255 and at the same time, RTZ LATCH is set. After all the step pulses from the controller are received, the SEEK is performed in the outer direction until the TRACK 0 indication is received by the speed up/slow down circuit. The step rate of the speed up/slow down circuit, in this case, is determined by the data from ROM accessed by the RTZ LATCH bit. In the RTZ mode, the regular step rate is 500 pps. Fig. 4.19 shows the timing chart.

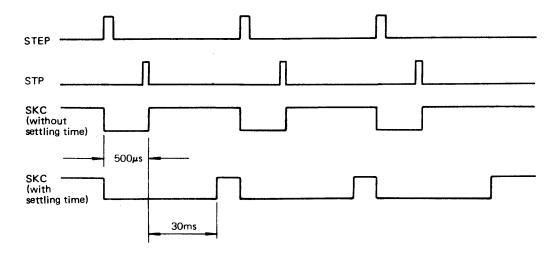

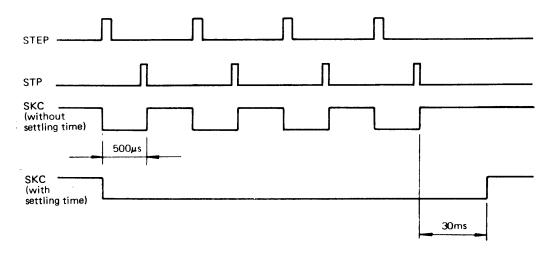

#### (5) SEEK COMPLETE

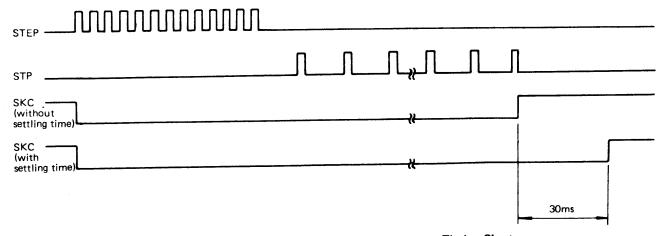

The SEEK COMPLETE signal indicates to the controller that a seek operation has been completed. The unit can be set by a switch on the PCA to use the SKC signal which includes the settling time.

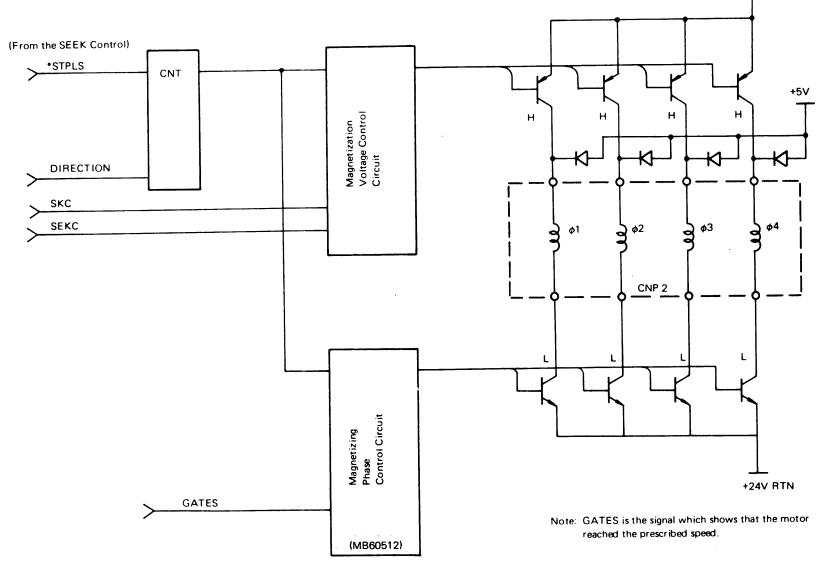

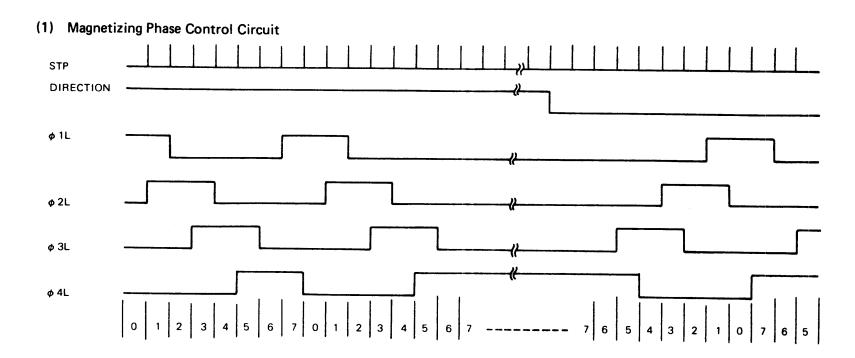

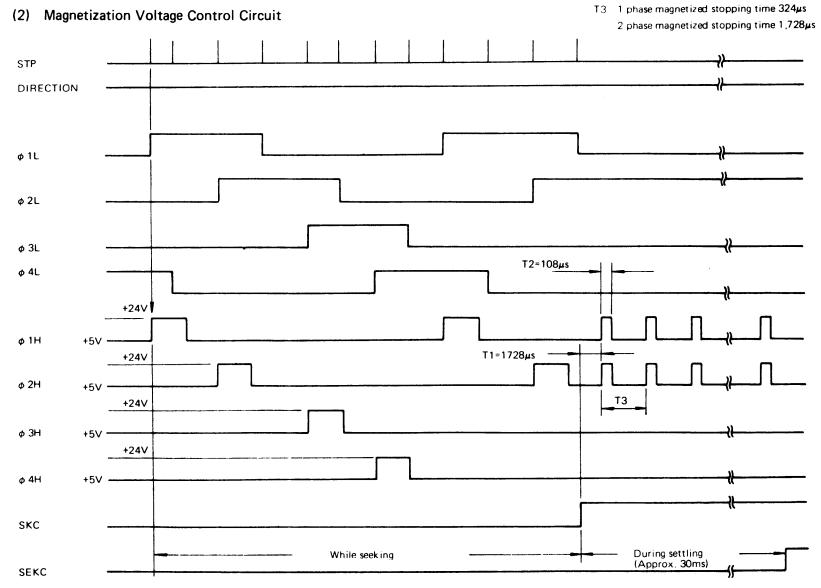

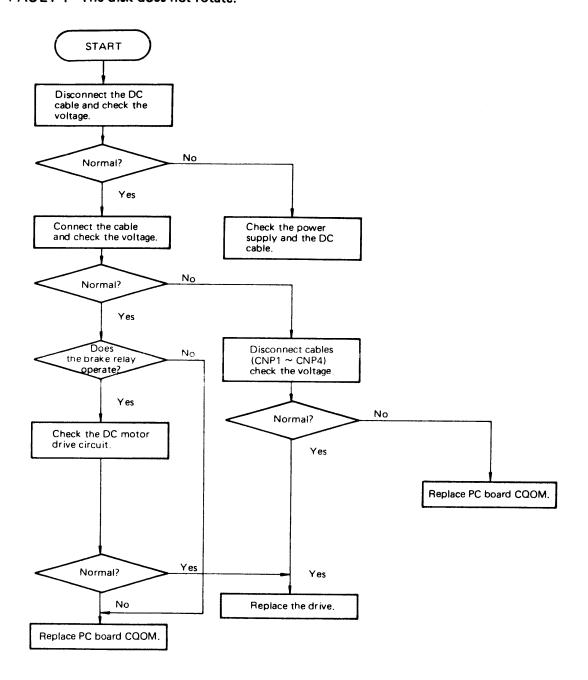

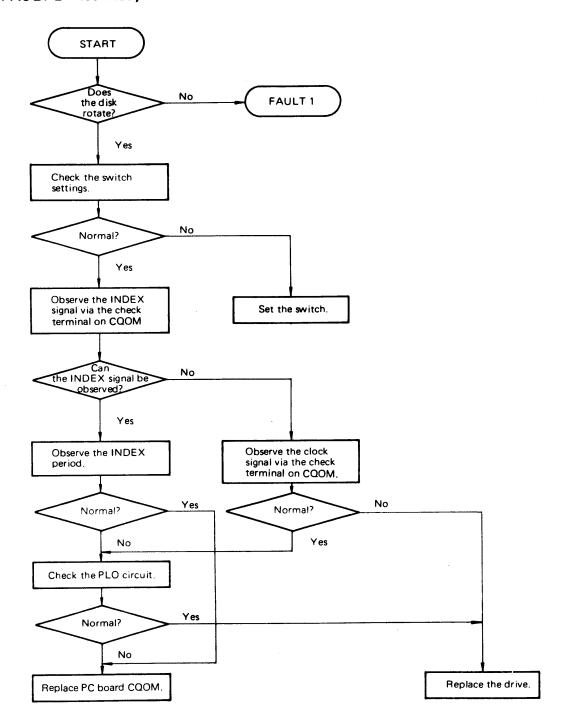

Refer to item 3.6.7 for the setting method of switch. Fig. 4.20 shows the timing chart of the SEEK COMPLETE response.