# MSV05 / MSV05B Tape Controller Manual

830006-102 Rev A

August 18, 1986

MICRO TECHNOLOGY, INCORPORATED

• . ,

This document is intended to provide the user with detailed information sufficient for the understanding, installation and use of the equipment involved.

Every effort has been made to ensure the information contained herein is current and accurate as of the date of publication, however no guarantee is given or implied as to its accuracy.

Micro Technology Inc. reserves the right to make changes, for the purpose of product improvement, at any time.

Printed in the U.S.A.

•

# Contents

| SECTION 1 GENERAL INFORMATION                                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | PAGE<br>1 |

|------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----------|

|                                                                        |   |   |   |   |   |   | • |   |   | • |   | • | • |   | • | -         |

| OVERVIEW                                                               |   | - |   |   |   |   | - | - |   | - |   | - | - | - | - | 1         |

| APPLICABLE HARDWARE                                                    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 1         |

| GLOSSARY OF TERMS                                                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 2         |

| FUNCTIONAL OVERVIEW                                                    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 5         |

| SPECIFICATIONS                                                         | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   | 9         |

| Mechanical                                                             | • |   | • | • | • | • | • | • | • | • | • | • | • | • | • | 9         |

| Electrical                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 9         |

| Environmental                                                          | • | • | • | • | • | • | • | • |   | • | • | • | • | • | • | 10        |

| Performance                                                            | • | • | • | • | • | • | • | • | • | • |   |   | • | • | • | 10        |

| Reliability                                                            | • | • | • | • | • | • | • | • | • | • | • | • |   |   | • | 11        |

| COMPATIBILITY                                                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 11        |

| Hardware                                                               | • |   | • |   | • |   | • |   |   |   |   |   |   | • |   | 11        |

| Software                                                               |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 12        |

| Media                                                                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 13        |

| PRODUCT FEATURES.                                                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 13        |

| Multi-volume Support                                                   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 13        |

| Expanded File Utility Support                                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |           |

| QIC-11 Tape Format Support                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |           |

| PRODUCT LIMITATIONS                                                    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |           |

| SECTION 2 INSTALLATION                                                 |   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 17        |

| GENERAL                                                                |   |   |   |   |   |   |   |   | _ |   |   |   |   |   |   | 17        |

| CONFIGURATION.                                                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 17        |

| Address/Vector Selection                                               |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |           |

| Device Interrupt Priority                                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |           |

| Extended Features                                                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |           |

| Drive Type                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |           |

| Diagnostic Enable                                                      | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |           |

| Automatic Retension Enable                                             | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 23        |

| DRIVE CONFIGURATION                                                    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 24        |

|                                                                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 24        |

| INITIAL INSTALLATION AND CHECKOUT                                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 24        |

| INITIAL INSTALLATION AND CHECKOUT                                      | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 20        |

| SECTION 3 FUNCTIONAL DESCRIPTION                                       | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 27        |

| OVERVIEW.                                                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 27        |

| REGISTER DEFINITION                                                    | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 27        |

| MSV05 Bus Address Register (MSBA)                                      | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 27        |

| MSVOJ DUS AUGLESS REgister (MSDR)<br>MSVO5 Data Buffer Register (MSDR) |   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 28        |

| MSVO5 Status Register (MSSR)                |    | •   |     |   |   |   |   |   |   | 29 |

|---------------------------------------------|----|-----|-----|---|---|---|---|---|---|----|

| MSV05 Extended Data Buffer Register (MSDBX) |    |     |     |   |   |   |   |   |   |    |

| Extended Status Register 0 (MXSTO)          |    |     |     |   |   |   |   | • |   | 32 |

| Extended Status Register 1 (MXST1)          |    |     |     | • |   | • |   |   |   | 34 |

| Extended Status Register 2 (MXST2)          |    |     | ••• | • |   | • |   | • |   | 35 |

| Extended Status Register 3 (MXST3)          | •  | • • | ••  | • | • | • | • | • | • | 35 |

| Extended Status Register 5 (MASIS)          | •  | • • | ••  | • | • | • | • | • | • | 36 |

| REGISTER/PACKET PROTOCOL.                   | •  | • • | ••  | • | • | • | • | • | • | 37 |

| REGISTER/FRONE FROTOCOL                     | •  | • • | ••  | • | • | • | • | • | • | 38 |

| Buffer Ownership and Control                | •  | • • | • • | • | • | • | • | • | • | 20 |

| Message Packet Format                       | •  | • • | •   | • | • | • | • | ٠ | • | 39 |

| Header Word                                 |    |     |     |   |   |   |   |   |   |    |

| Data Length Word                            | •  | • • | •   | • | • | • | • | • | • | 41 |

| Residual Byte/Record/File Count Register    | (R | BPC | CR) | • | • | • | • | • | • | 41 |

| Extended Status Register 0 (MXSTO)          | ٠  | • • | •   | • | • | • | • | • | • | 42 |

| Extended Status Register 1 (MXST1)          | •  | • • | •   | • | • | • | • | • | • | 42 |

| Extended Status Register 2 (MXST2)          | •  | • • | •   | • | • | • | • | • | • | 42 |

| Extended Status Register 3 (MXST3)          |    |     |     |   |   |   |   |   |   |    |

| Extended Status Register 4 (MXST4)          | •  |     | •   | • | • | • | • | • | • | 42 |

| GENERAL STATUS PROCESSING INFORMATION       |    |     | •   |   |   | • | • | • | • | 42 |

| Termination Class/Message Type Relationship |    |     |     |   |   |   |   |   |   |    |

| Additional Information on Status Processing |    |     |     |   |   |   |   |   |   | 43 |

| COMMAND PROTOCOL                            |    |     |     |   |   |   |   |   |   | 45 |

| Command Packet Definitions                  |    |     |     |   |   |   |   |   |   |    |

| Get Status Command                          |    |     |     |   |   |   |   |   |   |    |

| Read Command.                               | •  | ••• | •   | • | • | • | • | • | • | 48 |

|                                             |    |     |     |   |   |   |   |   |   |    |

| Write Characteristics Command               |    |     |     |   |   |   |   |   |   |    |

| Write Command                               | •  | • • | •   | • | • | • | • | • | • | 53 |

| Position Command                            | •  | ••• | •   | ٠ | • | • | • | • | • | 55 |

| Format Command                              | •  | ••• | •   | • | • | • | • | • | • | 56 |

| Control Command                             | •  | ••• | ٠   | ٠ | • | • | • | • | • | 57 |

| Initialize Command                          | •  | ••• | •   | • | ٠ | ٠ | • | • | • | 58 |

| Write Subsystem Memory Command              | •  | • • | •   | • | • | • | • | • | • | 59 |

|                                             |    |     |     |   |   |   |   |   |   |    |

|                                             |    |     |     |   |   |   |   |   |   |    |

| SECTION 4 HARDWARE DESCRIPTION              | •  | • • | •   | • | • | • | • | • | • | 61 |

|                                             |    |     |     |   |   |   |   |   |   |    |

| OVERVIEW                                    | •  |     | •   | • | • | • | • | • | • | 61 |

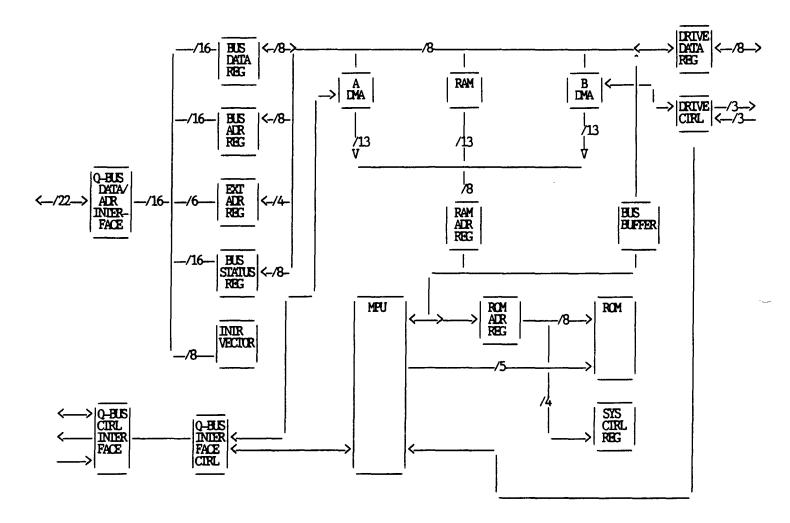

| BLOCK DIAGRAM                               | •  |     | •   |   |   |   |   |   | • | 61 |

| Q-Bus Interface                             |    |     | •   |   | • | • |   | • | • | 61 |

| Q-BUS Data/address Interface                |    |     |     |   |   |   |   |   |   | 61 |

| Bus Data Register                           |    |     |     |   |   |   |   |   |   | 61 |

| Bus Address Register                        |    |     |     |   |   |   |   |   |   | 63 |

| Extended Address Register                   |    |     |     |   |   |   |   |   |   | 63 |

| Interrupt Vector                            |    |     |     |   |   |   |   |   |   | 63 |

| Q-Bus Control Interface.                    |    |     |     |   |   |   |   |   |   | 63 |

| Q-Bus Interface Control                     |    |     |     |   |   |   |   |   |   |    |

|                                             |    |     |     |   |   |   |   |   |   | 63 |

| A-DMA                                       |    |     |     |   |   |   |   |   |   | 63 |

| Microengine                                 |    |     |     |   |   |   |   |   |   | 63 |

| MPU                                         |    |     |     |   |   |   |   |   |   | 64 |

| ROM Address Register                        | •  | ••  | •   | ٠ | • | • | • | • | • | 64 |

| ROM                                         |    |     |     |   |   |   |   |   |   | 64 |

| System Control Register                     |    |     |     |   |   |   |   |   |   | 64 |

| BUS Buffer                                  | •  |     | •   | • | • | • | • | • | • | 64 |

.

| RAM Address Register                 | 64       |

|--------------------------------------|----------|

| RAM                                  |          |

| Drive Interface                      | 64       |

| B-DMA                                | 65       |

| Drive Data Register                  | 65       |

| Drive Control                        | 65       |

| TECHNICAL DESCRIPTION                | 65       |

| Q-Bus Interface                      |          |

| Input/Output Pin Assignments         |          |

| Tape Drive Interface                 | 67       |

| Input/Output Pin Assignments         |          |

| SECTION 5 SOFTWARE CONSIDERATIONS    | 69       |

| CENEDAL                              | 69       |

| GENERAL                              |          |

|                                      |          |

| MTI DIAGNOSTICS                      | 69<br>69 |

|                                      |          |

| Backup Utility Program (BUP)         |          |

| Device Utility Program (DUP)         | 71       |

| Peripheral Interchange Program (PIP) | 71       |

| Source and Binary Compare Utility    |          |

| Making a Bootable RT-11 Tape         | 72       |

| MSBOOT Bootable Program              | 75       |

| Unsupported Utility Function         | 75       |

| OPERATION WITH RSX-11M               | 76       |

| RSX11M PIP.                          | 76       |

| Backup and Restore Utility (BRU)     | 76       |

| Creating a Standalone BRU Tape       | 77       |

| Creating a Bootable BRU Tape         | 78       |

| Restoring a Bootable BRU Tape        | 78       |

| Disk Save and Compress Utility (DSC) | 79       |

| Unsupported Operations               | 79       |

| OPERATION WITH RSTS                  | 79       |

| Save and Restore Utility (SAV/RES)   | 79       |

| Backup Utility                       | 80       |

| RSTS/E PIP                           | 80       |

| OPERATION WITH MICROVMS              |          |

| MicroVMS Backup                      | 82       |

| MicroVMS Copy                        | 83       |

iii

# Appendix

# Tables

| Table | 1-1 | Glossary of Terms                      |  |

|-------|-----|----------------------------------------|--|

| Table | 1-2 | Legal Command Mode Summary             |  |

| Table | 2-1 | Factory Option Summary                 |  |

| Table | 2-2 | Base Address Configuration             |  |

| Table | 2-3 | Vector Address Configuration           |  |

|       |     | Interrupt Priority Level Configuration |  |

| Table | 2-5 | Extended Features Configuration        |  |

| Table | 2-6 | Drive Type/Size Configuration          |  |

| Table | 2-7 | Diagnostic Enable                      |  |

| Table | 2-8 | Automatic Retension Enable             |  |

| Table | 3-1 | Command Code and Mode Field Definition |  |

# **Figures**

| Figure | 1–1 | Command Packets                      | 8  |

|--------|-----|--------------------------------------|----|

|        |     | MSV05 Configuration Jumper Locations |    |

| Figure | 2-2 | Connector Pin Definitions            | 25 |

| Figure | 3–1 | Register Summary                     | 37 |

|        |     | Message Packet                       |    |

|        |     | Memory/Tape Data Byte Positioning    |    |

| Figure | 4-1 | MSV05 Block Diagram                  | 52 |

# Section 1

# **General Information**

## 1. OVERVIEW

The MSV05B is a single dual height module interfacing a wide variety of standard QIC-02 interface 1/4" cartridge tape drives to the Q-22 LSI-11 bus. The MSV05B controller, together with the 1/4" cartridge drive emulates the DEC TSV05 subsystem except for the constraints outlined in this document. The MSV05B contains a set of built in diagnostics which assures the integrity of the controller whenever it is initialized or first powered up.

# 1.1. APPLICABLE HARDWARE

This document describes the functionality and use of the Micro Technology MSV05B cartridge tape controller. The MSV05B controller is compatible with the LSI-11, LSI-11/2, LSI-11/23, LSI-11/73 CPU's and the Micro-Vax processors. All the circuitry is contained on one dual-height board that plugs directly into any standard Q-22 LSI-11 backplane. Alternate address, vector selection, and optional configuration jumpers provide the user added flexibility for various drive and system configuration. The controllers support block mode DMA which can be enabled or disabled at the user's option. The controllers interface to most QIC-02 type drives through a 50 conductor flat ribbon cable.

1

# 1.2. GLOSSARY OF TERMS

Table 1-1 is a list of terms that will be used within this document. Included with each term is its definition.

| Terms                           | Definition                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Packet<br>(I/O Request) | A set of control words issued from the CPU<br>(i.e., operating system, I/O driver or<br>diagnostic program) to the MSVO5B to initiate<br>and control operation.                                                                                                                                                                 |

| Command Buffer                  | An area of contiguous 16-bit words in the<br>host CPU's memory space. The I/O Request<br>Packets are built there and are retrieved by<br>the MSV05B.                                                                                                                                                                            |

| Command Pointer                 | The high (most significant) 16 bits of an<br>18-bit Modulo-4 address which points to a<br>Command Packet located in the CPU's memory<br>space. In extended operation, "Command<br>Pointer" refers to the high 20 bits of a<br>22-bit Modulo-4 address which points to a<br>Command Packet located in the CPU's memory<br>space. |

| Header Word                     | The Header Word is the first word of a<br>Command Packet or a Message Packet.                                                                                                                                                                                                                                                   |

| Message Buffer                  | An area of contiguous words in the CPU's<br>memory space. The Message Packets are stored<br>there by the MSV05B.                                                                                                                                                                                                                |

| Message Packet                  | A group of status words issued from the<br>MSV05B to the CPU to indicate status of the<br>magtape subsystem and/or operation completed.                                                                                                                                                                                         |

| Modulo-4 Address                | An address within the CPU's memory space<br>that is evenly divisible by 4 (i.e., octal<br>O, 4, 10, 14, 20, etc.)                                                                                                                                                                                                               |

| Packet                          | A contiguous sequence of words.                                                                                                                                                                                                                                                                                                 |

| Q-22                            | LSI-11 system bus containing 22-bit memory addressing capability.                                                                                                                                                                                                                                                               |

(cont'd on next page)

Table 1-1 Glossary of Terms

| Terms                                        | Definition                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Streaming<br>Technology                      | Operation of a magtape transport without<br>stopping in the interrecord gap. Requires<br>that, for maximum efficiency, commands of<br>similar type, speed and direction be<br>supplied by the controller within a<br>relatively short "reinstruct" period. The<br>1/4 inch streaming QIC-02 cartridge drives<br>operate in this fashion.                                                  |

| Conventional, or<br>Stop/Start<br>Technology | Operating characteristic of a magtape<br>drive that can rapidly accelerate and<br>decelerate tape motion to allow the tape<br>to come to rest with the read/write head<br>positioned in the interrecord gap.                                                                                                                                                                              |

| Reinstruct Time                              | The period of time following reading or<br>writing the last character of a record<br>allowed by a tape transport for a controller<br>to issue the next command in order to avoid<br>slowing or stopping the tape.                                                                                                                                                                         |

| Access Time                                  | The time between issuance of a tape read,<br>write or space command (by the controller)<br>and the reading or writing of the first<br>character in the target tape record.                                                                                                                                                                                                                |

| Command Delay                                | The elapsed time between the indication from<br>the controller signifying the completion of<br>an operation (e.g., Read or Write) and the<br>issuance of the next command to the<br>controller by the operating software.                                                                                                                                                                 |

| Repositioning                                | A characteristic of a streaming tape drive<br>whereby tape motion is halted and the tape is<br>readied for the next operation by<br>decelerating the tape current direction and<br>bringing it to a stop, then accelerating and<br>decelerating the tape in the opposite<br>direction and bring it to a stop. The tape<br>is not stopped in the gap, as with<br>conventional tape drives. |

(cont'd on next page)

Table 1-1 (cont'd) Glossary of Terms

| Term                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Record Buffering     | Capability of the MSV05B to store an entire<br>tape record, up to 15872 bytes in length,<br>during Read or Write command sequences to<br>allow overlapping of tape repositioning with<br>transfer of data to/from the CPU.                                                                                                                                                                                                                                                                                                                           |

| Packet Protocol      | Method of communication between CPU software<br>and the MSV05B via areas in CPU memory space,<br>following the rules dictated by DEC's TSV05<br>compatibility requirements. A "packet" is a<br>contiguous series of words residing in CPU<br>memory space. The MSV05B accesses a Command<br>Packet (in a Command Buffer area in CPU<br>memory space) to provide status information<br>to the software. This technique allows<br>large amounts of information to be passed<br>while allowing the device to occupy only two<br>hardware I/O addresses. |

| MSDB                 | MSV05B Data Buffer Register a Write-Only<br>hardware register in the I/O address space.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MSBA                 | MSV05B Bus Address Register a Read-Only<br>hardware register in the I/O address space                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MSSR                 | MSV05B Status Register A Read/Write<br>register in the I/O address space                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MXSTn                | Extended Status Register n one of five<br>status registers deposited into the Message<br>Buffer area.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Extended<br>Features | Mode of operation of the MSV05B that extends<br>the functionality of the subsystem beyond<br>that allowed by DEC's TS11/TS04<br>compatibility. Includes 22-bit memory<br>addressing and additional status and<br>functions. Requires use of special soft-<br>ware, which is not supplied and/or may not<br>exist.                                                                                                                                                                                                                                    |

| BOT/EOT              | Beginning of Tape and End of Tape markers  <br>which mark the physical beginning and end of  <br>tape, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 1-1 (cont'd) Glossary of Terms

,

# 1.3. FUNCTIONAL OVERVIEW

The functions listed in Table 1-2 summarize the MSV05B Subsystem Command Set. These commands utilize "command packets" stored in the computer system's memory to operate the transport and transfer data. Some commands have various sub-commands, termed "modes". The interface's device registers are used to initiate command packet processing and retrieve basic status. This section describes register manipulation and provides an overview of packet protocol (the format used to transfer commands and data). A detailed description of the commands is provided in another section of this document.

The MSV05B has four device registers which occupy only two LSI-11 Bus word locations: a Data Buffer (MSDB), a Bus Address Register (MSBA), a Status Register (MSSR), and an Extended Data Buffer (MSDBX). The MSDB is an 18-bit register that is parallel loaded from the LSI-11 Bus. A 16-bit portion of this register is used as a word buffer register; it is written into by the host CPU to initiate an operation. The MSDB can be loaded from the LSI-11 Bus by four different transfers from the CPU. Three transfers are for maintenance purposes (not supported, controller reports special condition with register modification refused bit set) and the fourth is for the normal word transfer (DATO) to initiate an operation. This register is write-only and is not cleared at power on, subsystem initialize, or bus initialize. This register can be loaded without the tape transport connected, since all controller functions reside within the controller.

Commands are not written to the MSV05B's LSI-11 Bus registers. Instead, command pointers, which point to a command packet somewhere in CPU memory space, are written to the MSDB register. The command pointer is used in the MSV05B subsystem to retrieve words in memory called the Command Packet. The words in the Command Packet instruct the system as to the function to be performed. These words contain function parameters such as bus address, byte count, record count, and modifier flags.

The MSBA is an 18-bit register (22-bits when the extended features jumper is enabled) that is parallel loaded from the MSDB whenever the MSDB is written. MSBA bits 1 and 0 are always zero specifying a modulo-4 address. MSBA bits 15-2 are loaded from MSDB bits 15-2. MSBA bits 17 and 16 are respectively loaded from MSDB bits 1 and 0. MSBA bits 17 and 16 are displayed in MSSR bits 9 and 8, respectively. When extended features is enabled the MSBA is extended to 22 bits by first loading the high byte of the MSSR with bits 21-18 of the MSBA. If extended features is disabled these bits are ignored. The MSBA is incremented by two for DMA word transfers or by one for DMA byte transfers.

| Command Names                                                                                                                                                                                                                      | Mode Name/Description                                                                                                                                                                                                                |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Get Status                                                                                                                                                                                                                         | Get Status (update the Extended Status<br>registers in the message buffer in memory)                                                                                                                                                 |  |  |  |

| Read                                                                                                                                                                                                                               | <ul> <li>Read Next (Forward)</li> <li>Read Previous (Space Reverse - Read<br/>Forward - Space Reverse)*</li> <li>Reread Previous (Space Reverse - Read<br/>Forward)*</li> <li>Reread Next (Read Forward - Space Reverse)*</li> </ul> |  |  |  |

| Write<br>Characteristics                                                                                                                                                                                                           | Load Message Buffer Address and Set Device<br>Characteristics                                                                                                                                                                        |  |  |  |

| Write                                                                                                                                                                                                                              | - Write Data<br>- Write Data Retry (Illegal Function Reject)                                                                                                                                                                         |  |  |  |

| Position                                                                                                                                                                                                                           | - Space Records Forward<br>- Space Records Reverse**<br>- Skip Tape Marks Forward<br>- Skip Tape Marks Reverse**<br>- Rewind                                                                                                         |  |  |  |

| Format                                                                                                                                                                                                                             | - Write Tape Mark<br>- Erase<br>- Write Tape Mark Retry (Illegal Function<br>Reject)                                                                                                                                                 |  |  |  |

| Control                                                                                                                                                                                                                            | - Message Buffer Release<br>- Rewind and Unload<br>- NOP (Retension Tape)<br>- Rewind with Immediate Interrupt                                                                                                                       |  |  |  |

| Initialize                                                                                                                                                                                                                         | Controller/Drive Initialize                                                                                                                                                                                                          |  |  |  |

| Write Subsystem  <br>Memory                                                                                                                                                                                                        | Diagnostic Function (Illegal Function<br>Reject)                                                                                                                                                                                     |  |  |  |

| <pre>*These commands are currently rejected but are under<br/>consideration based on software requirements<br/>**These commands are supported with limitations as to the<br/>number of tape marks skipped or records spaced.</pre> |                                                                                                                                                                                                                                      |  |  |  |

Table 1-2 Legal Command Mode Summary

The MSBA register is used for two purposes. As a command pointer to the functional device registers, the MSBA is used as a pointer to the command and message buffers located in the LSI-11 address space. As a data pointer, the MSBA is used as an address pointer to the LSI-11 address space during data transfers between the drive and the host CPU memory.

The MSSR is a 16-bit register that can be updated only from the controller logic. It cannot be modified from the LSI-11 Bus. In this register, major system status can be observed.

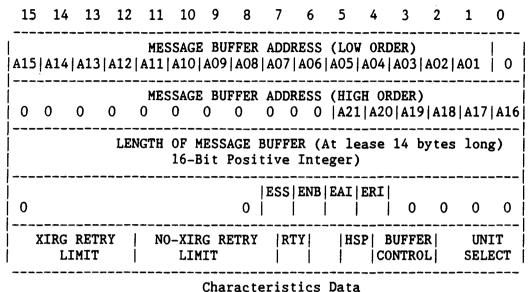

Before the MSV05B can begin a function, a command packet must be assembled in the CPU's system memory. In every case, the packet requires all four words. The packet may be thought of as being three remote device registers, some of which are not used for non-data transfer commands (Figure 1-1):

- 1. Command Register (CMDR)

- 2. Data Pointer (DPR) which is comprised of two word locations:

- a. CMDR+2: Low order address word (A15:00)

- b. CMDR+4: High order address word. In standard mode, only bits 1 and 0 of this word are used, specifying address bits A17 and A16. Loading the high byte of the MSSR first, 22-bit addressing mode can be specified, (if extended features is enabled), in which case bits 5-2 are used to specify address bits A21-A18.

- 3. Positive Byte Count Register (BCR):

- a. CMDR+6: Data operations (DPR required)b. CMDR+2: Non-data operations (no DPR required)

The command pointer must be an address on a modulo-4 boundary (i.e. octal 0, 4, 10, etc.) due to the address limitations of the MSBA register.

The command register is decoded by the controller logic and if valid initiates the appropriate function. Detailed function description are provided in the following sections. The data pointer register (DPR) is loaded into the MSBA to be used as the LSI-11 Bus address for DMA transfers. The Byte Count Register (BCR) is used to indicate the number of bytes (8 bits of data per byte) to be moved to or from the drive during a data transfer. It is also used to specify the number of records in a space record command or the number of files in a skip tape marks command.

Message packets are sent by the controller to the host CPU memory space. Proper operation of the controller requires a message buffer address. This buffer address is specified on a write characteristics

7

initialize. Otherwise, all other commands will be rejected. 1 - Word Type 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 COMMAND 2 - Word Type 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 \_\_\_\_\_ \_\_\_\_\_ COMMAND \_\_\_\_\_\_ BYTE COUNT \_\_\_\_\_ 4 - Word Type 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 \_\_\_\_ COMMAND \_\_\_\_\_ ADDRESS POINTER (Low order) \_\_\_\_\_\_ ADDRESS POINTER (High order) \_\_\_\_\_\_ BYTE COUNT

command and must be the first command issued to the controller after an

Figure 1-1 Command Packets

# 1.4. SPECIFICATIONS

# 1.4.1. Mechanical

| Size:       | Dual-height, standard length module.                                                                                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connectors: | Two connectors used:                                                                                                                                                                 |

|             | <ol> <li>Standard Q-22 LSI-11 bus edge<br/>connector using the A and B<br/>rows</li> </ol>                                                                                           |

|             | <ol> <li>50 pin right angle flat cable<br/>connector located at the handle<br/>end of the module for interface<br/>to industry standard QIC-02<br/>drives.</li> </ol>                |

| Jumpers:    | Jumpers are available to select<br>address, vector, interrupt priority,<br>block mode control, extended<br>features, and various drive characteristics.                              |

| Indicator:  | Single LED used to indicate that the<br>controller passed internal<br>diagnostics initiated during initial<br>power up. Upon successful completion the LED<br>stays on continuously. |

# 1.4.2. Electrical

| Power requirements<br>LSI-11 bus loading: | +5VDC <u>+</u> 5% at 3.0 Amps (max.)<br>1 DC bus load<br>2 AC bus loads                                           |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| LSI-11 bus<br>interface:                  | Adheres to the Q-22 specification but does<br>not generate or check parity. Only uses the A<br>and B rows.        |

|                                           | Receives the following LSI-11 bus signals:                                                                        |

|                                           | BDALOO-BDAL21, BDIN, BDOUT, BSYNC, BRPLY,<br>BWTBT, BBS7, BIRQ4, BIRQ5, BIRQ6, BIAKI<br>BDMGI, BSACK, BINIT, BREF |

|                                           | Drives the following LSI-11 bus signals:                                                                          |

|                                           | BDALOO - BDAL21, BDIN, BDOUT, BSYNC, BRPLY,<br>BWTBT, BBS7, BIRQ4, BIRQ5, BIAKO, BDMR, BDMGO,<br>BSACK            |

Does not interface the following LSI-11 bus signals: BHALT, BDCOK, BPOK, BEVNT Drive interface: Adheres to the ANSI X3T9.6183-20 specifications - QIC-02 device level interface for streaming cartridge tape drives. Transmitter: Signal assertion = 0.0VDC to 0.4VDCMin drive capability = 24 ma (sink) @ 0.50VDC Signal non-assertion = 2.5DC to 5.25VDC Signal type = Tristate Receiver: Signal assertion = 0.0VDC to 0.8VDC Input load (max.) = 0.4ma @ 0.4VDCSignal non-assertion = 2.0VDC to 5.25VDC Hysteresis (min) = 0.2VDCReceives the following signals: CB7, CB6, CB5, CB4, CB3, CB2, CB1, CBO, ACK, RDY, EXC, DIR Transmits the following signals: CB7-CB0, ONL, REQ, RST, XFR Does not interface to the following signals: CBP 1.4.3. Environmental Temperature: 5 to 50 degrees C (41 to 122 degrees F) 10% to 90% (non-condensing) Humidity:

# 1.4.4. Performance

| Transfer rate: | Burst 200 Kbytes/sec<br>Average 86.7 Kbytes/sec                                                   |

|----------------|---------------------------------------------------------------------------------------------------|

| Capacity:      | Limits established by drive<br>characteristics and tape length.<br>Note: It is not advised to use |

300 ft. tapes due to the fact the tape characteristics will not function reliably with streaming cartridge drives. The MSV05B controller measures tape length and will reject the 300 ft. tape with function reject error.

# 1.4.5. Reliability

MTBF

32,300 hrs.

MTTR

.5 hr.

## 1.5. COMPATIBILITY

## 1.5.1. Hardware

The MSV05B controller is compatible with the LSI-11, LSI-11/2, LSI-11/23, LSI-11/73 CPU's and the Micro-Vax processors. All the circuitry is contained on one dual-height board that plugs directly into any standard Q-22 LSI-11 backplane. Alternate address, vector selection, and optional configuration jumpers provide the user added flexibility for various drive and system configuration. The controllers support block mode DMA which can be enabled or disabled at the user's option. The controllers interface to most QIC-02 type drives through a 50 conductor flat ribbon cable.

| Device Address:                 |                              |

|---------------------------------|------------------------------|

| Standard                        | 772520                       |

| 1st Alternate                   | 772524                       |

| 2nd Alternate                   | 772530                       |

| 3rd Alternate                   | 772534                       |

| Device Vector:                  |                              |

| Standard                        | 224                          |

| 1st Alternate                   | floating (jumper selectable) |

| 2nd Alternate                   | floating (jumper selectable) |

| 3rd Alternate                   | floating (jumper selectable) |

| T-towns b Britanitas            |                              |

| Interrupt Priority:<br>Standard | level 5                      |

| Alternate                       | level 4                      |

| Arternate                       | TEVEL 4                      |

|                                 |                              |

| Jumper Options:                 |                              |

| Block Mode Control              | Enables block mode DMA       |

|                                 |                              |

11

| Extended features   | Enables 22-bit addressing                            |

|---------------------|------------------------------------------------------|

| Drive Configuration | Configures the controller for various drive features |

Features:

22-bit Addressing The MSV05B controller generates a 22-bit address compatible with DEC's TSV05 when Extended Features are enabled. When Extended Features are disabled the MSV05B generates an 18 bit address compatible with DEC's TS11.

Record Buffering The MSV05B uses a record buffering technique to optimize operation of streaming tape drives. Records are buffered in an on board 16K byte buffer to avoid the inherent long respositioning delay associated with streaming drives.

> Reading from the tape operates in the opposite fashion. Records are buffered in the on board buffer to allow for both software overhead and target device latency

Micro Diagnostics

Internal diagnostics check various controller components in order to insure proper operation of the MSV05B. These include:

- a. Basic Processor tests

- b. Scratch RAM test

- c. Host DMA controller test

- d. Drive DMA controller test

- e. RAM buffer test

# 1.5.2. Software

The controller is compatible with DEC's TSV05 packet protocol and emulates the TSV05 subsystem within the constraints of the streaming cartridge drive. The product is designed to operate with the basic utilities in DEC's RT11, RSTS, and RSX11M operating systems such as PIP, BRU, DSC, etc. In addition, the new utility BUP (RT11) is supported and provides an excellent high speed backup utility optimized for use with RL02 and TSV05 products. Diagnostic software is supplied to insure that the controller is functioning properly.

# 1.5.3. Media

The DEC TSV05 subsystem is based on industry standard 1/2" 9 track tape recorded at 1600 BPI in various formats. The most common format is ANSI standard and provides a convenient means of interchange in both the DEC community and with other available systems.

The MSV05B interfaces most QIC-02 compatible drives. The predominant manufacturers use the 1/4" cartridge tapes and record in what is termed QIC-24 format.

Since the tapes written on these drives are QIC-24 format compatible it is possible to use drives available from various manufacturers maintaining compatibility.

Cartridge drives implementing the QIC-120 format provide increased data storage capacity while maintaining read compatibility with QIC-24 format tapes. These QIC-120 drives will write one 600 ft. tapes only; other length tapes are rejected by the drive.

# **1.6. PRODUCT FEATURES**

The MSV05B is a cost effective back up device for the DEC compatible marketplace. Emulating the TSV05 subsystem this product interfaces with standard QIC-02 compatible streaming drives. All electronics are contained on a single dual-height controller and interface to drive on a single 50 conductor flat ribbon cable. Either the 5 1/4" full or half height drives provide an excellent package for small system or table top applications. The major features include:

- o dual height board

- o 22-bit addressing

- o block mode DMA support

- o extended features options

- o TSV05 compatibility

- o interface with low cost QIC-02 cartridge streaming drives

# 1.6.1. Multi-Volume Support

In order to properly write data across volume boundaries, it is necessary to identify the end-of-tape (EOT) as with 1/2 inch tape. For 1/2 inch tape, EOT is a warning and a limited amount of information can continue to be written to the tape. Since the physical EOT on the streaming type drives allows only two blocks to be written, a logical EOT (LEOT) was needed.

In order to generate a LEOT status, the cartridge/drive type, number of tracks and tape length are needed. The first two pieces of information are provided with jumpers on the controller. Tape length must be measured. Revision C and later versions of the firmware implement a sizing algorithm described as follows:

When a tape cartridge is inserted, it is rewound to BOT and an attempt is made to read the first block. If a valid header is read with a valid tape length, the tape is rewound and the length is saved. If an error occurs during the first read or the length is 0 (as for tapes written with older firmware), the tape is measured by timing a retension pass, and the length is saved. On the first write to tape, the length is saved. Subsequent use of the cartridge will not require resizing since the length is stored on tape.

The cartridge tape lengths that are currently supported are:

150 feet 450 feet 555 feet 600 feet

Please note that a 300 ft cartridge will cause abnormal tape head wear and is not recommended by the QIC-02 drive manufacturers. An attempt to write on a 300 ft cartridge will result in a Function Reject termination.

Media types other than cartridge are rewound to BOT only, and no sizing is done since the length is determined by jumpers.

Multi-volume copies are supported for the following utilities:

| RT11 | BUP    |

|------|--------|

| RSX  | BRU    |

|      | DSC    |

|      | PIP    |

| RSTS | SAVRES |

|      | PIP    |

When copying to a tape, if the LEOT is encountered, the behavior of the copy is the same as for 1/2 inch tape. The volume will be rewound and unloaded and a message will be displayed on the operator's console to change the tape. The controller will poll the drive for a new cartridge inserted status, size the tape if required (in the off-line mode) and then go on-line, allowing the copy to continue.

# 1.6.2. File Utility Support

An overwrite scheme has been incorporated which allows the controller to closely emulate the full start stop features of the 1/2 inch tape products. The MSV05B supports RSX PIP and RSTS PIP in either ANSI or DOS format. Additional file utility support is under current evaluation.

# 1.6.3. QIC-11 Tape Format Support

When appending to information on the tape, the MSV05B has taken advantage of QIC 24 format which erases a leader past the last written block as a clear delineation of the end of recorded media. The QIC-11 format does not provide this erased area at the end of recorded media and prevented the previous firmware versions of the MSV05B from using this format. Since there is a substantial installed base of QIC-11 format drives, features have been added to eliminate this problem. An erase tape command has been added to provide a means of erasure other than bulk erasing. The TSV05 erase tape command is used with a second word for qualification to prevent accidental erasure. While erasing, the tape length is measured, and when complete, a header containing the length is written to tape so that further sizing is not needed.

To invoke this command with ODT, deposit 100411 (8) in any modulo 4 memory location (eg., 1000 (8), 1004(8) or 1010(8)) and 1234(8) in the next location. Then write the first address to MSV05B base address (772520(8) is standard address). A retension command is also available and can be invoked in a similar manner with a command word of 101012. A qualifying word is not needed for retension.

#### **1.7. PRODUCT LIMITATIONS**

The MSV05B controller emulates the TSV05 subsystem within the constraints of the available 1/4" cartridge streaming tape drives. The major limitation imposed by these drives is their inability to overwrite existing files. This limitation prevents the MSV05B from implementing any function which implies a destructive write. These functions include:

write data retry

erase

write tape mark retry

positioning to previously recorded data and

writing

The controller responds to these functions with an illegal function reject. Both the write data retry and the write tape mark retry are not necessary because of the automatic verification rewrite logic imbedded within the drive. The erase function is typically not used.

Positioning functions such as Space Records Forward, Space Records Reverse, Skip Tape Marks Forward, and Skip Tape Marks Reverse are implemented to the extent that they will allow proper operation of DEC operating systems and utilities. These commands are supported with limitations as to the number of tape marks skipped or records spaced.

Any attempt to position the tape to previously recorded data and to subsequently overwrite is inhibited by most of the available 1/4" cartridge tape drives. Overwriting is prevented because of the unsaturated recording method and the lack of a track erase head. An erase bar is available to write on track 0 while simultaneously erasing the full width of the tape. Under normal use the operating systems software does not implement destructive writes. The MSVO5B incorporates a pseudo-overwrite which allows it to overwrite a limited number of blocks. This number is sufficient to allow proper operation of most DEC software.

There are optional software switches available to allow the user to overwrite either files or records on the tape. These commands/switches must be avoided and if used will result in illegal function or various error conditions presented to the software drivers.

# Section 2 Installation

# 2. GENERAL

The MSV05B controller is shipped with the standard options configured. The primary address and vector are configured to 172520(8) and 224(8), respectively, the device interrupt priority is set to level five, the extended features option is enabled and the automatic retension option is disabled.

# 2.1. CONFIGURATION

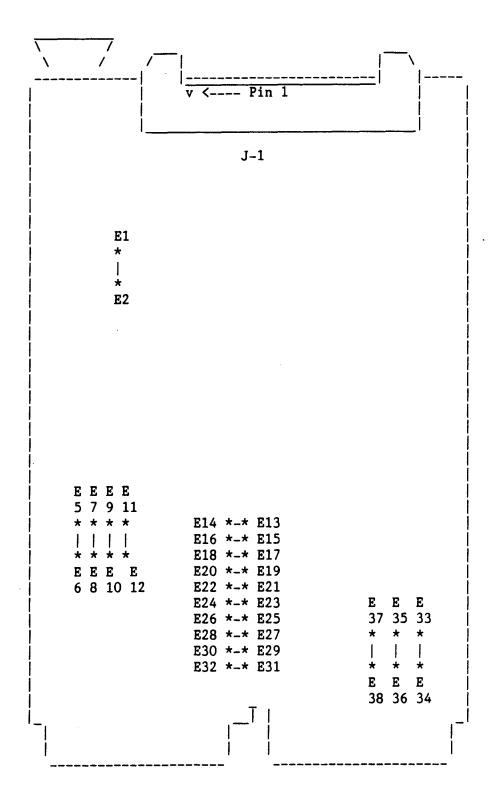

Refer to Table 2-1 for a summary of the factory options. As delivered, the controller will be configured for proper operation with standard 9 track QIC-02 interface tape drives. Refer to Tables 2-2, 2-3 and 2-4 for alternate options regarding the selection of the controller's base address, interrupt vector address and interrupt priority level. The physical location of the jumpers is shown by Figure 2-1.

Several of the options are selectable by using BERG 76264-101 pin jumpers. If these or similar pin jumpers are not available use #30 wire wrap.

Figure 2-1 MSV05B Configuration Jumper Locations

| JUMPER               | USAGE<br>                                                                                                                              | STATUS<br> |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|

| E1 – E2              | Not used                                                                                                                               | NA         |

| E5 – E6<br>E7 – E8   | Retension Option (Disabled)<br>Diagnostic enable (Disabled)                                                                            | OUT<br>OUT |

| E9 - E10<br>E11- E12 | Address Select Bit 0+<br>Address Select Bit 1+  <br>   <br>IN = 0 0 0 = 772520<br>OUT = 1 1 0 = 772524<br>0 1 = 772530<br>1 1 = 772534 | IN<br>IN   |

| E13- E14             | Drive Configuration 2 (See Table 2-6)                                                                                                  | IN         |

| E15- E16             | Extended Features enable                                                                                                               | IN         |

| E17- E18             | Drive Configuration 0 (See Table 2-6)                                                                                                  | OUT        |

| E19- E20             | Drive Configuration 1 (See Table 2-6)                                                                                                  | OUT        |

| E21- E22             | Interrupt Vector Bit 7                                                                                                                 | OUT        |

| E23- E24             | Interrupt Vector Bit 6                                                                                                                 | IN         |

| E25- E26             | Interrupt Vector Bit 5                                                                                                                 | IN         |

| E27- E28             | Interrupt Vector Bit 4                                                                                                                 | OUT        |

| E29- E30             | Interrupt Vector Bit 3                                                                                                                 | IN         |

| E31- E32             | Interrupt Vector Bit 2                                                                                                                 | TUO        |

| E33- E34             | Interrupt Priority Level 5                                                                                                             | IN         |

| E35- E36             | Interrupt Priority Level 4                                                                                                             | OUT        |

| E37- E38             | Block Mode DMA enable                                                                                                                  | OUT        |

Table 2-1 Factory Option Summary

# 2.1.1. Address/Vector Selection

The controller is shipped with the primary device address and vector assignments preset to 172520(8) and 224(8), respectively. Three alternate address assignments are available using jumper options. The alternate address assignments available are 172524(8), 172530(8), and 172534(8). The alternate vector assignments available are jumper selectable within the range of 0-374. Any change in these assignments would necessitate a change in system software.

19

If an alternate address/vector combination is required, refer to Table 2-2 for the proper address jumper configuration and refer to Table 2-3 for the proper vector jumper configuration.

| ODETON                             | JUMP     | ERS           |

|------------------------------------|----------|---------------|

| OPTION                             | E11- E12 | E9- E10       |

| Standard<br>Address *<br>172520    | IN       | <br>  IN<br>  |

| 1st Alternate<br>Address<br>172524 | OUT      | <br> <br>  IN |

| 2nd Alternate<br>Address<br>172530 | IN       | OUT           |

| 3rd Alternate<br>Address<br>172534 | OUT      | <br>0UT       |

Table 2-2 Base Address Configuration

| 1       | Vector  | Address S | Selection Bi | .ts / Jump | ers     |       |       |

|---------|---------|-----------|--------------|------------|---------|-------|-------|

| Bit 7   | Bit 6   | Bit 5     | Bit 4        | Bit 3      | Bit 2   | Bit 1 | Bit O |

| E21-E22 | E23-E24 | E25-E26   | E27–E28      | E29-E30    | E31-E32 | 1     |       |

| <br>]   |         |           | our          |            |         |       | 1     |

Table 2-3 Vector Address Configuration

20

# 2.1.2. Device Interrupt Priority

The MSV05B supports the four-level device interrupt priority scheme compatible with the LSI-11/23. The controller asserts interrupt requests and monitors higher level request lines during interrupt arbitration. The level four request is always asserted by the controller, regardless of its priority, to maintain compatibility with the LSI-11 and LSI-11/2 processors.

The interrupt priority level is configured to level five at the factory. Refer to Table 2-4 for the proper jumpers to insert for the desired priority level.

| OPTION                             | JUMPERS  |          |  |

|------------------------------------|----------|----------|--|

| OFIION                             | E33- E34 | E35- E36 |  |

| Interrupt<br>Priority<br>Level 5 * | IN       | <br>OUT  |  |

| Interrupt<br>Priority<br>Level 4   | OUT      | IN       |  |

#### Table 2-4 Interrupt Priority Level Configuration

## 2.1.3. Extended Features

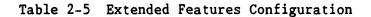

Extended features mode of operation expands the functionality of the subsystem beyond that of the TS11/TS04. This mode includes 22-bit addressing along with additional functions and status. The controller is shipped with Extended Features enabled. This feature is enabled/disabled via jumper E15-E16. See Table 2-5.

| Extended         | JUMPER      |

|------------------|-------------|

| Features         | E 15 - E 16 |

| Enabled *        | IN          |

| Disabled         | OUT         |

| * Factory preset |             |

# 2.1.4. Drive Type

The MSV05B controller interfaces with one QIC-02 drive. The controllers are factory configured for standard QIC-02, QIC-24 9 track drives only. To select the desired Drive Type refer to Table 2-6 for the appropriate jumpers.

| DRIVE TYPE / SIZE            | JUI     |         |          |

|------------------------------|---------|---------|----------|

| DRIVE HIFE / SIZE            | E13-E14 | E19-E20 | E17-E18  |

| Cartridge 9 track *          | IN      | OUT     | OUT      |

| Cartridge 4 track            | IN      | OUT     | IN       |

| Cartridge 15 track (QIC-120) | IN      | IN      | OUT      |

| Cartridge 12 track           | IN      | IN      | IN       |

| Reserved                     | OUT     | OUT     | OUT      |

| Rosscomp 190 MB              | OUT     | OUT     | IN       |

| Reserved                     | OUT     | IN      | OUT      |

| Cassette 20 MB               | out     | IN      | <br>  IN |

| * Factory Preset             |         | <b></b> |          |

Table 2-6 Drive Type / Size Configuration

Cartridge drives implementing the QIC-120 format provide increased data storage capacity while maintaining read compatibility with QIC-24 format tapes. These QIC-120 drives will write on 600 ft. tapes only; other length tapes are rejected by the drive.

# 2.1.5. Diagnostic Enable

The MSV05B controller incorporates a set of internal diagnostics to verify proper controller operation. With the diagnostic enable jumper removed the internal diagnostics only operate once during the power up cycle. Upon successful completion the green LED at the edge of the board is turned on. When the diagnostic enable jumper is installed, the controller continuously operates the self diagnostics turning off the LED at initiation and turning on the LED upon successful completion of each pass of the diagnostics. The effect is to blink the LED once for each successful pass of the diagnostic. If an error occurs the diagnostics will loop on the failing test until successfully completed.

Self tests include:

- a) Proper Micro-processor operation

- b) Condition code testing

- c) Register tests

- d) ALU operation test

- e) RAM verification

- f) Instruction tests

The controller is shipped with this feature disabled. It is only necessary to enable the diagnostics to determine if the controller is not functioning properly. When the self diagnostics are enabled all other controller operations are suspended. To enable this option, refer to Table 2-7.

| DIAGNOSTICS     | JUMPERS |

|-----------------|---------|

|                 | E7 - E8 |

| DISABLED *      | OUT     |

| ENABLED         | IN      |

| *Factory Preset |         |

Table 2-7 Diagnostic Enable

#### 2.1.6. Automatic Retension Enable

When a tape cartridge is inserted into the drive, the default operation of the MSV05B is to rewind to BOT and attempt to read the first block. If valid tape length information is found the drive is rewound and marked online. If an error occurs during this first read or a length of zero is found the tape is sized by timing a retension pass. This information is temporarily held by the controller until the first write to tape, at which time it is saved as part of a header block. Subsequent use of the tape does not require sizing since the length information is stored on tape.

If it is desireable to retension tapes on a regular basis the Automatic Retension option may be enabled. In addition to the default operation, this will cause the MSV05B to do a retension pass each time a tape is inserted into the drive.

|                               | JUMPERS |

|-------------------------------|---------|

| AUTOMATIC TAPE<br>  RETENSION | E5 – E6 |

| DISABLED *                    | OUT     |

| ENABLED                       | IN      |

| <pre> *Factory Preset</pre>   |         |

Table 2-8 Automatic Retension Enable

o

# 2.2. DRIVE CONFIGURATION

The controller provides an industry standard QIC-02 interface compatible with most available drives. However, for proper operation, each drive must be configured with attention to several options. The drive must be strapped to respond to drive select "0", cartridge drives must be operating at 90 ips., QIC-24 format is recommended. If QIC-11 operation is required it will be necessary to bulk erase the tapes prior to the first write operation. This erasure is to insure the proper detection of NDT(no data detected) when appending.

# 2.3. CABLING

A 50-conductor ribbon cable connects the controller to any QIC-02 interface compatible drive. Connect the socket connector to the appropriate header located at the edge of the controller board. Observe the alignment of pin 1 of the socket connector and header as indicated by

the arrows shown in Figure 2-1. The edge connector should be connected to the drive, again observing the location of pin 1.

If the optional cable is purchased from an independent source, the following list of materials (or equivalent) will help in the construction of the required cable.

| QTY    | DESCRIPTION               | MFG | NUMBER    |

|--------|---------------------------|-----|-----------|

| 1 each | 50 pin socket connector   | 3M  | 3425-3000 |

| 1 each | 50 pin edge connector     | 3M  | 3415-0001 |

| A/R    | 50 conductor ribbon cable | 3M  | 3365-50   |

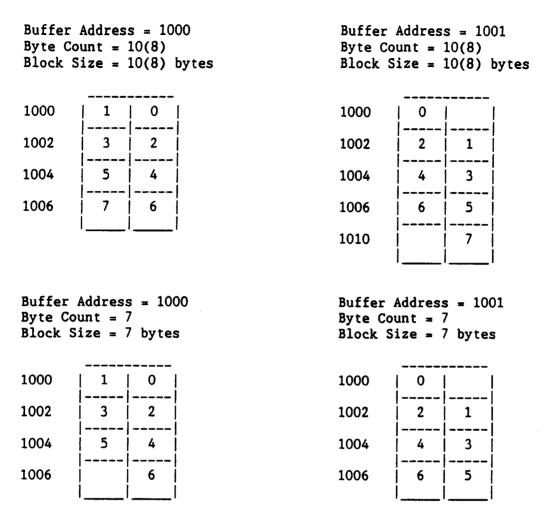

Figure 2-2 illustrates the pin out of connector J-1. The signals named in the figure are described in greater detail in section 4.2.2, Tape Drive Interface.

\_\_\_\_\_

|   |            | 1  | 2  |   |   | NOT | USED |  |  |  |  |  |

|---|------------|----|----|---|---|-----|------|--|--|--|--|--|

|   |            | 3  | 4  |   |   | NOT | USED |  |  |  |  |  |

|   |            | 5  | 6  |   |   | NOT | USED |  |  |  |  |  |

|   |            | 7  | 8  |   |   | NOT | USED |  |  |  |  |  |

|   |            | 9  | 10 | < | > | BBP |      |  |  |  |  |  |

|   |            | 11 | 12 | < | > | BB7 |      |  |  |  |  |  |

|   |            | 13 | 14 | < | > | BB6 |      |  |  |  |  |  |

|   |            | 15 | 16 | < | > | BB5 |      |  |  |  |  |  |

|   |            | 17 | 18 | < | > | BB4 |      |  |  |  |  |  |

|   |            | 19 | 20 | < | > | BB3 |      |  |  |  |  |  |

|   |            | 21 | 22 | < | > | BB2 |      |  |  |  |  |  |

|   |            | 23 | 24 | < | > | BB1 |      |  |  |  |  |  |

|   |            | 25 | 26 | < | > | BBO |      |  |  |  |  |  |

|   |            | 27 | 28 |   | > | ONL |      |  |  |  |  |  |

|   |            | 29 | 30 |   | > | REQ |      |  |  |  |  |  |

|   |            | 31 | 32 |   | > | RST |      |  |  |  |  |  |

|   |            | 33 | 34 |   | > | XFR |      |  |  |  |  |  |

|   |            | 35 | 36 | < |   | ACK |      |  |  |  |  |  |

|   |            | 37 | 38 | < |   | RDY |      |  |  |  |  |  |

|   |            | 39 | 40 | < |   | EXC |      |  |  |  |  |  |

|   |            | 41 | 42 | < |   | DIR |      |  |  |  |  |  |

|   |            | 43 | 44 |   |   | NOT | USED |  |  |  |  |  |

|   |            | 45 | 46 |   |   | NOT | USED |  |  |  |  |  |

|   |            | 47 | 48 |   |   | NOT | USED |  |  |  |  |  |

|   |            | 49 | 50 |   |   | NOT | USED |  |  |  |  |  |

|   |            |    |    |   |   |     |      |  |  |  |  |  |

|   | • <b>-</b> |    | J1 |   |   |     |      |  |  |  |  |  |

|   |            |    |    |   |   |     |      |  |  |  |  |  |

| - | -          |    |    |   |   |     |      |  |  |  |  |  |

|   |            |    |    |   |   |     |      |  |  |  |  |  |

Figure 2-2 Connector Pin Definitions

## 2.4. INITIAL INSTALLATION AND CHECKOUT

Before the following procedures are followed and for purposes of checkout, verify that the controller and drive have been configured correctly as described in Sections 2.1 - 2.3.

- 1. Insert the MSV05B controller into the first available Q-22 slot, ensuring the component side is facing the same direction as the other cards.

- 2. Verify that bus grant continuity has been maintained. Failure to maintain bus grant continuity will cause the system to hang.

- 3. Connect tape drive cable to MSV05B controller card, aligning pin 1(red) on the cable with connector arrow.

- 4. Place the Run/Halt switch on the processor to the Halt position and turn on the processor.

- 5. Verify that the green LED on the MSV05B card edge is illuminated. This indicates the successful completion of the power-up micro-diagnostics by the controller.

If, after initial application of power, the drive does not calibrate or the LED does not illuminate, check the cabling and power supplies. Most QIC-02 drives have separate power connectors for the formatter and tape drive. Verify proper power application.

- 6. If the standard address assignment is selected, open the MSDB register by entering 172520(8) thru console ODT. The processor will display the contents of the MSDB register which at this point is typically 377(8).

- Open the MSSR register (location 172522(8)) using the console ODT as described above. The contents of this location should be 002200(8). For a detailed description of the register protocol and bit definition, refer to Section 3.

- Micro Technology's MSV05B diagnostic (VMSDG) should be used to verify the complete operation of the subsystem. Refer to MTI diagnostic manual, P/N 830002-130, for instructions regarding the operation of the VMSDG diagnostic.

- 9. If the above procedures function as described, the controller is ready for use; otherwise consult the factory or your local representative for assistance.

# Section 3

# **Functional Description**

#### 3. OVERVIEW

This section of the document presents the bit definitions for the MSV05B registers, register (packet) protocol and the command summary. The intent of this section is to provide the programming aspects of the MSV05B controller. In general the MSV05B is identical to DEC's TSV05 which is similar to DEC's TS11/TS04. Where differences exist they are noted in the text.

3.1. REGISTER DEFINITION

# 3.1.1. MSV05B Bus Address Register (MSBA)

The Bus Address Register (MSBA) is a read-only register located at the first I/O register address. In normal operating mode, it displays the low-order 16 bits of the memory address to be used or being used by the controller to access system main memory (e.g., for command buffer fetch, message buffer store, or data transfer).

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

| A15 A |   | 3 A12 | A11 | A10 | A09 | A08 | A07 | A06 | A05 | A04 | A03 | A02 | A01 | A00 | ł |

|-------|---|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

|       | 1 | I     |     |     |     | 1   |     | 1   |     |     |     |     |     | İ   |   |

MSBA Register Format

## Bit Description

- 15-00 A<15:00>--Address bits 15 through 00 These bits normally reflect the low-order 16 bits of the 22-bit address used by the controller to access LSI-11 bus memory. These bits are loaded as follows:

- Writing a word into MSDB, to define the address of the Command Buffer for the next operation. MSDB<15:02> are copied into MSBA<15:02>, and MSBA<01:00> are set to 0.

2. During DMA operation the controller updates the MSBA specifying the DMA address.

# NOTE

#### The MSBA is NOT modified by initialize.

## 3.1.2. MSV05B Data Buffer Register (MSDB)

The MSDB appears as a 16-bit write-only register on the LSI-11 bus. Actually it is a 22-bit register which can be updated by four different types of transfers. Three of these transfers are for maintenance purposes, which is not supported. The fourth is a normal word output transfer (DATO) to specify a command pointer.

The 4-bit extension to MSDB is written at the high byte of the MSSR location. These address bits are ignored if the Extended Features jumper is removed. The extension is cleared after it is used once and so must be reloaded if extended addressing is to be used on subsequent command pointers. (Must be loaded before the MSDB is loaded.) It is also cleared by Initialize.

The controller will respond whenever the MSDB location is written to, but will be loaded only when the SSR bit in the MSSR register is set (if SSR is clear, the RMR bit in the MSSR will be set). Writing into MSDB clears SSR.

# NOTE

Maintenance mode is not supported at this time. Attempts to enter Maintenance Mode will result in an RMR error with SC set.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

|P15|P14|P13|P12|P11|P10|P09|P08|P07|P06|P05|P04|P03|P02|P17|P16 | |M15|M14|M13|M12|M11|M10|M09|M08|M07|M06|M05|M04|M03|M02|M01|M00 |

#### MSDB Register Format

# Bit Definition

15-02 P<15:02> P<17:16> -- Command pointer. When the MSDB 01-00 is written as a word and SSR is asserted, the data are loaded into bits 17-02 of the MSBA. MSBA bits 01-00 are cleared to 0. In addition, the extended address register MSDBX is loaded into MSBA bits 21-18. Note the MSDBX must be loaded before writing the MSDB with the command pointer.

#### 3.1.3. MSV05B Status Register (MSSR)

The MSSR is a 16-bit register whose contents can only be updated by the controller; it cannot be directly modified from the LSI-11 Bus. The register is defined as Read/Write. It can be read to examine status, while writing into it causes a hardware initialize of the controller. A byte transfer (DATOB) to the high byte of the MSSR loads the extended data buffer register (MSDBX).

| SC 0 SCE RMR NXM NBA A17 A16 SSR OFL FC1 FC0 TC2 TC1 TC0 0 | 10 9 8 7 6 5 4 3 2 | 1 0 |

|------------------------------------------------------------|--------------------|-----|

|                                                            |                    |     |

#### MSSR Register Format