# **Microdata**

# MICRO 1600 COMPUTER REFERENCE MANUAL

# MICRO 1600 COMPUTER REFERENCE MANUAL

71-1-1600-001 October 1971

Microdata<sup>®</sup>

Microdata Corporation 644 East Young Street Santa Ana, California 92705

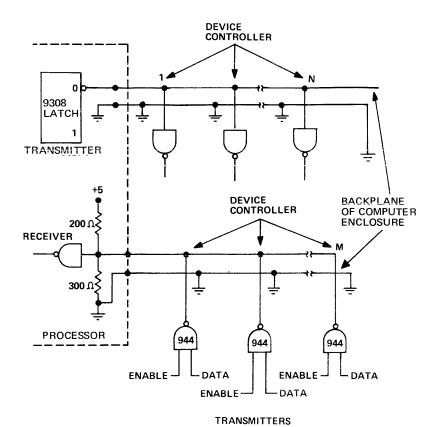

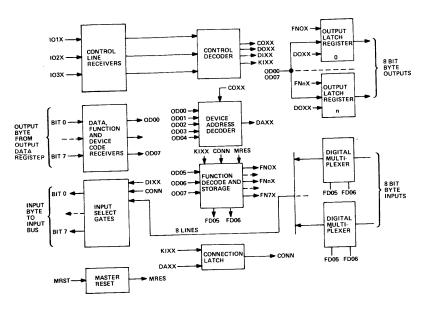

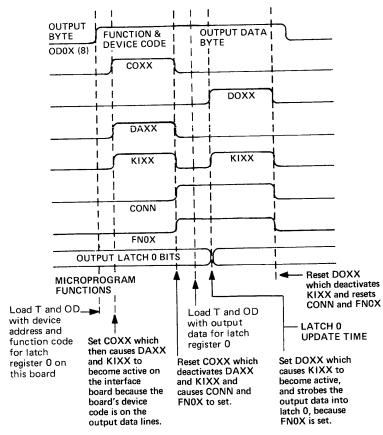

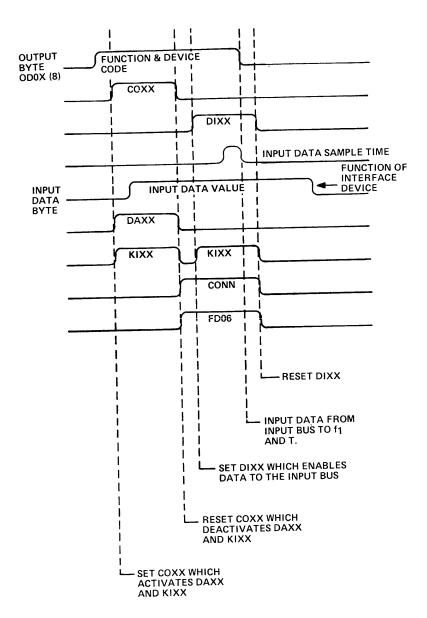

# **TABLE OF CONTENTS**

| CHAPTER 1  | MICRO 1600 DESIGN FEATURES 1                                                                                                                                                                                                 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Introduction                                                                                                                                                                                                                 |

| CHAPTER 2  | SYSTEM DESCRIPTION                                                                                                                                                                                                           |

|            | Registers       3         Data Flow       6         Register 0 Flags and Internal Status       7         Control       8         Memory       9         Power Fail       Auto Restart       10                               |

| CHAPTER 3  | MICROCOMMAND REPERTOIRE                                                                                                                                                                                                      |

|            | Command Formats                                                                                                                                                                                                              |

| CHAPTER 4  | CONTROL PANEL OPERATION 45                                                                                                                                                                                                   |

|            | System Console                                                                                                                                                                                                               |

| CHAPTER 5  | MICRO ASSEMBLER PROGRAM 51                                                                                                                                                                                                   |

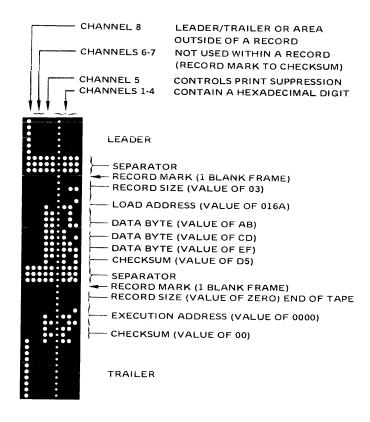

|            | Source Language 51 Statement Format 52 Operand Field Expressions 53 Machine Commands 54 Assembler Instructions 56 Assembly Listing 56 Error Flags 57 Program Tape Format 59 Sample Listing 59 Microcommands (Class Order) 62 |

| CHAPTER 6  | INPUT/OUTPUT                                                                                                                                                                                                                 |

|            | General Description                                                                                                                                                                                                          |

| CHAPTER 7  | PHYSICAL CHARACTERISTICS AND SYSTEM POWER                                                                                                                                                                                    |

|            | Mechanical Configurations                                                                                                                                                                                                    |

| APPENDIX A | MICROCOMMAND REFERENCE TABLE (NUMERICAL ORDER)                                                                                                                                                                               |

# CHAPTER 1

## MICRO 1600 DESIGN FEATURES

## INTRODUCTION

The MICRO 1600 is a microprogrammable digital computer with the capability to satisfy a broad range of application requirements through the use of both expandable high-speed control memory and magnetic core main memory.

The high-speed control memory continuously sequences preprogrammed microcommands which generate control and timing signals to perform all control operations and data manipulations in the computer.

Using application programming at the micro level, the MICRO 1600 can be used directly as a hard-wired controller. When the 1600 emulates the operation of a general purpose computer which executes software instructions stored in core memory, macroinstructions are fetched and interpreted by the microprogram with corresponding operations carried out by execution of microprogrammed routines in the control memory.

Basic macroinstruction sets are available which are significantly more powerful than conventional minicomputers. Individual users can add to or modify the basic macroinstruction set and basic input/output structure by a simple addition or change of firmware in the control memory to increase the flexibility and utility of the machine.

Control memory can be implemented in bipolar read-only memory (BROM), programmable read-only memory (PROM) or alterable read-only memory (AROM) devices. BROM is low cost and is appropriate for volume production of field-proven firmware. PROM permits microprograms to be installed at the factory or in the field with fast turn-around time and low initial set-up costs. It is intended for use in low production volume. AROM permits dynamic microprogramming and/or the debugging of firmware in a real-time environment before implementation into the more permanent BROM and PROM control memories.

There are 30 general-purpose file registers which are implemented with MSI/LSI semiconductor devices. Under program control, these registers are typically assigned functions such as I/O buffer registers, accumulators, index registers, and program counters.

The internal data paths and I/O are byte-oriented with eight-bit word lengths. Under control of microcommands, effective word lengths are variable.

Owing to its inherent flexibility, the MICRO 1600 can be applied as a direct function processor, general-purpose computer, special-purpose computer, emulator or language processor.

The MICRO 1600's control memory can be expanded to 16,384 16-bit words. This will permit implementation of languages such as BASIC, COBOL, FORTRAN, or equivalent complex firmware requirements. Direct language implementation will eliminate intermediate compile operations and results in an interpretive processor or a compile-and-go capability with performance exceeding conventional minicomputers.

Packaging variations permit operations ranging from a stripped-down low-cost minicomputer with three printed circuit boards and a card cage to a "super" computer with multiprocessor capability.

# GENERAL CHARACTERISTICS

Advanced features and operating characteristics include:

- 65,536 bytes of memory in basic enclosure

- 4096 and 8192 byte core memory modules

- 1 microsecond main core memory speed (full cycle)

- Dual processors with common main memory

- Macro processors

Standard macro processors, the 1600/10, 1600/20 and 1600/21 are available. These permit users to apply the machine using conventional software programming while providing advanced system features.

Alterable read-only memory

Alterable read-only memory permits firmware programmers to operate new microprograms in a true on-line environment.

Supporting standard software including special firmware development packages.

AP1600 — Micro language cross-assembler written in FORTRAN MAP1600 — Micro language assembler written for use on the MICRO 1600/20 and 1600/21 computers.

SIM1600 — MICRO 1600 simulator written for use on the MICRO 1600/20 and 1600/21 computers.

ICM1600 — Integrated circuit memory MAP generator permits direct conversion of AP/MAP1600 outputs to control memory bit patterns.

ROM Diagnostics — Pluggable standard CPU diagnostics in read-only memory.

AROS1600 — Alterable read-only memory operating system for control of AROM used for firmware checkout and debug.

- Direct memory access (DMA)

- 30 general purpose eight-bit file registers plus eight-bit status register

- Up to 16,384 words of read-only memory in 256-word modules

- 200-nanosecond microcommand execution time

- Real-time clock (optional)

- Standard automatic shutdown in event of power failure and automatic startup when power returns

- Operating temperature range 0 to 50°C

- Dimensions: 10-1/2 inches high, 19 inches wide, 20 inches deep

- Power: 115/230 VAC, 47-63 Hz, 350 watts

- Optional 16-level stack for recursive firmware

## CHAPTER 2

# SYSTEM DESCRIPTION

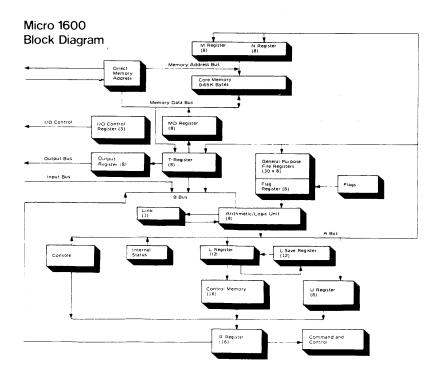

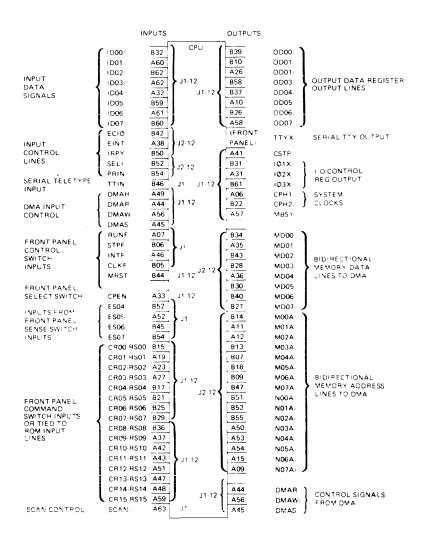

The MICRO 1600 is an eight-bit computer employing microprogram control. The computer incorporates eight-bit registers and data paths, executing with every clock pulse a 16-bit microcommand stored in a high-speed semiconductor control memory. The major elements of the system are shown in Figure 1.

This chapter describes the registers, data flow, memory and control. The microcommands are described in Chapter 3 and the input/output in Chapter 4.

#### REGISTERS

All registers except the file registers have specific functions in the machine. The file registers are used by the programmer for general purpose use. Description of the processor's registers follow.

Figure 1. MICRO 1600 Block Diagram

# T Register

The eight-bit T Register serves as an operand register for most operate commands and a buffer register for data being written into the memory and output on the byte I/O bus. The contents of the T Register are transferred to the MD or OD Registers on memory write or output respectively, thus freeing the T Register for other uses. Memory read operations cause the accessed data to be placed in the T Register 400 nanoseconds after the memory read is initiated.

# M Register

The eight-bit M Register holds the 8 high-order bits of the processor's 16-bit memory address.

## N Register

The eight-bit N Register holds the 8 low-order bits of the processor's 16-bit memory address.

# **U** Register

The eight-bit U Register is used to modify the 8 high-order bits of the control memory output. The contents of the U Register are ORed with the Control Memory output on the R-Bus as it is gated into the R Register for those commands which have zeros in bits 15-12 or zeros in bits 2-0 and a 1 in bit 15. The U Register permits efficient use of control memory by allowing a common routine to be used for different operations, when the operations differ by only a few commands.

# File Registers

Two files of 16 registers each provide storage for internal flags, and user's data. Typical assignments include program counters, accumulators, index registers, temporary buffers, etc. The primary or secondary file is selected by command and the primary file is selected after reset or power-on.

Only registers 1-15 are available to the user. Register 0 is common to both files and contains flags as described later. This register cannot be written into but can be used as a source of data. Readout of register 0 does not alter its contents.

# Link Register

The two-bit LINK Register holds the carryout of the high-order bit position of the adder for Add, Increment, Subtract, Decrement and Compare commands and the shifted off end bit for Shift commands. The ML link bit is selected and/or set when the M or N Registers have been selected as a destination, otherwise the AL link bit is used.

# IC Register

The three-bit IC Register is the I/O Control Register which specifies the I/O bus control signal to be enabled. The output of this register is decoded within I/O device controllers into three output control signals and four input control signals. The register is loaded and cleared by microcommands, therefore the timing of control signals on the bus is up to the microprogram. When the IC Register contains a value of 4-7 one of the

input modes is specified and the Input bus is substituted for the T Register on any commands which select T or the complement of the T.

## L Register

The 12-bit L Register holds the address of the next control word in sequence and provides for direct addressing of 4096 words of control memory. The register is incremented by one as each instruction is executed unless it is loaded by a new value which will effect a jump in the sequence. There are no restrictions in incrementing the L Register. The register can be loaded by a Jump command which alters the 10 low-order bits, a Jump Extended command which alters all 12 bits, a Return command which alters all 12 bits, or by specifying the L Register as the destination which alters the 9 low-order bits.

When the extended control memory option is included in the machine a Bank Select Register allows addressing to 32K. In this case the 3 high-order bits are set by the Bank Select command.

## L Save Register

The 12-bit L Save Register saves the incremented contents of the L Register when a Jump Extended command is executed, unless this has been inhibited by prior execution of an Inhibit L Save command. Execution of a Return command causes the contents of the L Save Register to be transferred back to the L Register. In this manner the L Save Register acts as a linkage register allowing one level of subroutine.

When the L Save stack option is included in the machine the L Save Register is replaced by an L Save Stack of 16 12-bit registers which perform the same function. Selection of the current stack register is under command control.

# R Register

The 16-bit R Register holds the microcommand currently being executed. The input to the R Register is from the R-Bus which is normally the output of the control memory, but may also be the console switches.

# MD Register

This eight-bit register is a buffer which holds data being written into memory. It is not directly accessible to the programmer, but automatically copies the contents of the T Register 350 nanoseconds after the write operation is initiated. This frees the T Register for other uses.

# **OD** Register

This eight-bit register is a buffer which holds data being output on the Byte I/O Bus. It is not directly accessible to the programmer, but automatically copies the contents of the T Register when the IC Register is set to a non-zero value. This frees the T Register for other uses.

#### DATA FLOW

# Arithmetic/Logic Unit

The arithmetic/logic unit (ALU) is the heart of the processor's data flow. All transfers and manipulation of data are done through this unit. The operations that it performs include: add, subtract, AND, OR, exclusive-OR, transfer and shifting. The two inputs to the ALU are the selected file register and the operand placed on the B Bus.

### A and B Buses

The output of the ALU is placed on the A Bus where it can be routed to all the processor's registers. Other inputs to the A Bus are the internal status byte, the four sense switches on the front panel and a selected file register shifted four bits to the right. The information on the A Bus is routed to a register implied by the operation code of the command, or optionally to the selected file register and a designated register.

The B Bus is the second input to the ALU. Sources of data on the B Bus are the literal in the eight low-order bits of the command and the true or complement of the contents of the T Register or the data on the Input Bus. The Input Bus is substituted for the T Register as a selected source when the I/O control IC Register is in an input mode. After a switchable delay after placing the I/O control in an input mode, data from an I/O unit will be available on the Input Bus.

# **Arithmetic and Memory Link Bits**

Two link bits are provided in a register commonly referred to as LINK. These bits store the carry out of the high-order bit position of the ALU on arithmetic and compare commands, and the shifted off end bit in shift commands. The Memory Link (ML) is used when the M or N Registers are selected as the destination register; otherwise the Arithmetic Link (AL) is used. The two link bits permit intermixed memory address and data arithmetic operations.

# T Register

The T Register is a transient working register used to hold operands for the ALU, receive data from memory, write data to memory and output data to external units. The T Register is backed up by the MD and OD Registers which buffer data being written in memory and output respectively. The purpose of these two buffers is to free the T Register for other operations during the relatively lengthly write and output operations. The T Register, and sometimes its complement constitute selectable operands on the B Bus. If the T Register is not selected in those commands which have that option the operand on the B Bus will be zero. If both the true and complement of the contents of the T Register are selected, the operand is all 1's. Data read from memory is set into the T Register two clock intervals after the read is initiated. Commands which select T Register as the source of operand during the first two clocks of the read operation are delayed until the third clock.

# REGISTER 0 FLAGS AND INTERNAL STATUS

# Register 0 Flags

Register 0 which is common to both the primary and secondary files contains a set of flags which reflect the result of a previous operation and external conditions which require frequent testing. The flags in bits 0-2 are the result condition flags and are updated when the C modifier (bit 4) of the operate instructions is a one. A description of the Register 0 flags follows:

- O Overflow Condition: The overflow condition flag stores the overflow condition of an Add, Increment, Subtract, Decrement, or Copy command. Arithmetic overflow occurs when carry out of the high-order bit of the adder differs from the carry into it. The over-flow also stores the shifted off end bit of shift commands.

- 1 Negative Condition: The negative condition flag stores the high-order bit of the result. When overflow occurs this flag will be the complement of the true sign.

- 2 Zero Condition: The zero condition flag stores the zero condition of the result. The zero test can be linked over multiple byte operations under control of the L modifier (bit 7) of operate instructions. When this bit is 1, the zero condition flag may not be set to indicate the zero condition of the current byte, but may only be reset to indicate a non-zero result. For this flag to indicate zero over multiple bytes it must be set by a zero result on the first operation which will have the L modifier zero and not be reset by non-zero conditions on succeeding bytes which will have the L modifier a one.

- 3-1/0 Request: The I/O request flag is turned on by one or more external I/O units requesting an I/O operation.

- 4 Internal Interrupt: The internal interrupt flag is turned on when an internal interrupt condition is present. The internal interrupt is identified in the internal status (Table 1).

Table 1. Internal Status

| Bit | Status Meaning                 |

|-----|--------------------------------|

| 0   | Panel Interrupt                |

| 1   | DMA Termination                |

| 2   | Real Time Clock Interrupt      |

| 3   | Spare                          |

| 4   | Spare                          |

| 5   | Spare                          |

| 6   | Panel Step Switch              |

| 7   | Power fail (Restart Interrupt) |

- 5 I/O Reply: The I/O reply flag is turned on by the external I/O unit currently communicating with the processor. This flag is normally not used in MICRO 1600 I/O units.

- 6 Serial TTY or Stack Overflow: The serial teletype input flag indicates the state of the serial teletype input. A zero indicates that the input is in a MARK state. This flag is used for MICRO 800 compatibility. The stack overflow flag is turned on when the L Save Stack has overflowed.

- 7 External Interrupt: The external interrupt flag is turned on by one or more external I/O units requesting an interrupt. This flag must result in a command which reads the address of the interrupt vector and resets the request.

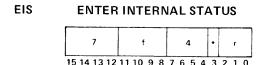

## **Internal Status**

The internal status reflects the state of the internal interrupts. When any of these functions is requesting an interrupt, bit 4 of the register 0 flag is turned on. Most of the internal interrupt status signals are turned off when the status is read. The status can be read by an Enter Internal Status command. The assignment of the internal status bits is as shown in Table 1.

#### CONTROL

The sequential control of the processor is obtained from a microprogram stored in a 16-bit control memory. Each word accessed from the control memory is placed in the R Register where it directly controls selection of operands, ALU function, register enables and the determination of the next control memory location. In effect the contents of control memory control the action of the processor at each clock. Because the Micro 1600 is a microprogrammed type of computer there is a minimal amount of command decoding and each command is executed in a single clock period, unless there is a delay imposed by the memory.

# **Control Memory**

The control memory is a 16-bit high-speed memory implemented with semiconductor read-only memory (ROM) devices, or read-write memory providing an alterable control memory (ACM). The standard MICRO 1600 can be expanded to 4096 words of control memory. Control memory can be added in 256 word pages. An option allows expansion to 32,768 words of control. The control memory can be randomly accessed with an access time, including logic delays of less than 200 nanoseconds.

The execution of commands and the accessing of the control memory are overlapped. While one command is in the R Register being executed the next command in sequence is being accessed and the L Register has been incremented to the address of the command being accessed. When the normal sequence is altered by a jump a delay of 200 nanoseconds takes place to allow reading of the first command at the start of a new sequence.

Two types of ROM devices are used for control memory. The first has the ones and zeros pattern of the microprogram built into the device by a special masking used in the manufacturing process. These devices are used for standard Microdata firmware. The other type is a similar ROM device, but can be programmed after device manufacturing by selectively burning out fuses corresponding to the bits of the desired program. This type of device is commonly called a programmable read-only memory (PROM) and costs considerably more than the masked ROM. Each board of control memory can accommodate up to 2048 words in 256-word increments.

The ACM provides for a dynamically alterable control memory. This type of memory is very useful when debugging firmware. The memory initially is treated as an external unit on the I/O bus when it is loaded and then treated as an extension of the control memory in the processor. ACM modules may contain up to 1024 words. Use of ACM modules in the system require additional cooling and +5-volt power supply current. Each 256 words of ACM requires approximately 2.0 ampere.

# L Save Stack and Extended Addressing Option

The L Save Register can be expanded to 16 15-bit L Save Registers by means of a stack option permitting multilevel subroutines. When this option is included the L Save Register in the processor is disabled. Along with this feature is a 3-bit Bank Select Register permitting the full 32,768 words of control memory to be addressed. The 3-bits of the Bank Select Register are controlled by the Bank Select command which must be followed by a Jump Extended. Associated with the L Save Stack registers is a 4-bit stack pointer which points to the next available stack register. Incrementing and decrementing of this pointer is done by command. It is reset to register zero on power-up and with the panel reset switch. This stack and extended addressing option is included with a 2048-word control memory module. Only one stack may be used in a system.

#### Timing

The processor is controlled by a 10 MHz crystal oscillator which is divided by two to produce a 5 MHz clock. This frequency may be reduced if desired. However, all timing will be delayed including timing delays which may be coded in the program.

#### MEMORY

## Memory Interface

The memory modules receive their address over a set of 16 address lines on the printed circuit backplane. This address is derived from the M and N Registers of the processor or the Direct Memory Access (DMA) option. A set of eight data lines on the backplane provides for transfer of data between the memory and processor or between the memory and DMA. Data read from the memory under control of the processor is transferred to the processor's T Register which is cleared one clock time after the start of the memory read operation. Data to be written into the memory is placed on the data lines by the processor's MD Register which receives its input from the T Register.

## Memory Modules

The standard memory is a 4096 or 8192-byte core memory module built on a single printed circuit board. The memories make use of lithium cores for operation over a wide temperature range. The memories may be operated in either a full or half cycle mode. Full cycle operation provides for a read-restore or clear-write type of operation with the program initiating only one operation. The half cycle operation allows the read and write operations to be programmed separately. This is normally used to effect a read-modify-write type of operation. After performing a half cycle read the addressed location is left in an all ones state.

# Memory Addressing

Addressing is available to a maximum of 65,536 bytes. Normally the high-order address line is disabled and forced to zero limiting addressing to 32,768 bytes. This is done because standard Microdata macro computer configurations use the high-order bit of address words for indexing control, leaving only 15 bits for address. Full 16 bits of address may be used for special applications. Core memory modules of different sizes may be intermixed within a system. However, only one 4196-byte module can be used in conjunction with one or more 8192-byte modules.

# **Memory Timing**

The memory cycle time is 1.0 microseconds with an access time of 400 nanoseconds until data is in the T Register. The half cycle time is 600 nanoseconds with an access time of 400 nanoseconds. Execution of commands which specify that the M or N Register are to receive data is delayed if the memory is busy. These commands are executed on the last clock of the cycle, i.e., the fifth clock on a full cycle operation and the third clock on a half cycle operation. Operate commands which select the contents of the T Register are not executed at the first or second clock following the initiation of a read operation. This allows the accessed data to be placed in the T Register before the command is executed. Two exceptions to this imposed delay occur when either an OR, Exclusive OR, or AND command selects both the T Register and its complement or when a command selects either the T Register or its complement with the input buss enabled. For these operations the command will execute in one machine cycle and the memory data will be loaded into the T Register as previously specified.

#### Direct Memory Access (DMA)

A Direct Memory Access (DMA) channel allows external devices to directly communicate with memory at data transfer rates up to 1 million bytes/second.

# POWER FAIL - AUTO RESTART

Standard with the MICRO 1600 is a feature which provides for detection of loss of AC power and an orderly startup when power is turned on. Both power fail and restart are indicated by a 1 in bit 7 of the internal status, which in turn turns on the Internal Interrupt flag of file register 0.

#### Power Fail

The standard power supplies are equipped with circuitry for detecting low AC line voltage. When low AC line is detected the Internal Status bit 7 is turned on. The microprogram must periodically test for internal interrupts. After the low line is detected the power supply will hold all voltages within operating range for a minimum of one millisecond. After sensing the power fail interrupt the microprogram should save all volatile registers containing valid data in core memory and bring the processor to a halt. When the processor halts a reset is applied to the system to provide for an orderly loss of power.

#### Restart

When power is applied a reset is applied to the system until the power supply voltages stabilize at their operating values. This reset initializes the system, sets the L Register to zero, sets internal status bit 7 and prevents accidental operation of the core memory. The microprogram can distinguish the restart from the power fail by testing internal status bit 7 soon after starting execution when the reset is removed. This test should not be used later when there is a chance that the status bit will reflect power fail.

#### CHAPTER 3

# MICROCOMMAND REPERTOIRE

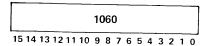

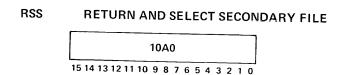

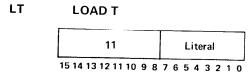

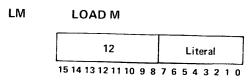

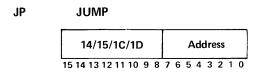

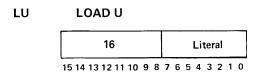

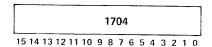

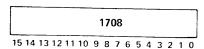

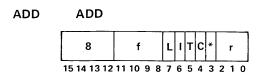

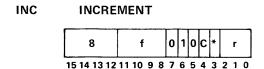

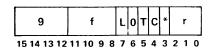

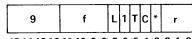

This chapter contains a description of all MICRO 1600 microcommands. With each description is a diagram showing the format of the command and its operation code given in hexadecimal. Above the diagram is the command's mnemonic and the name of the command. Under each diagram is a description of the command, followed by a list of the registers and indicators that can be affected by the command. The timing of each command is 200 nanoseconds except as noted, or if memory timing delays described in Chapter 2 are encountered.

### COMMAND FORMATS

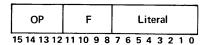

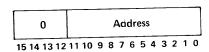

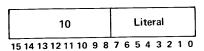

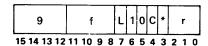

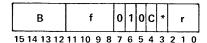

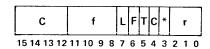

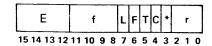

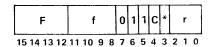

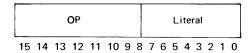

There are five basic command formats. Each command is 16 bits in length and is stored in a single control memory location.

#### Literal Commands

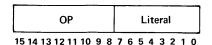

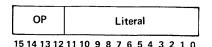

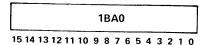

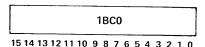

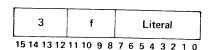

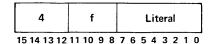

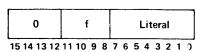

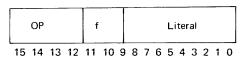

The literal classes of commands have the following formats:

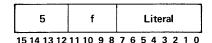

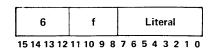

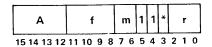

The operation code occupies the four high-order bits. Bits 11-8 contain the file register designator. Bits 7-0 contain an eight-bit literal which is transferred as an operand.

The operation code occupies the eight high-order bits. Bits 7-0 contain an eight-bit literal which is transferred as an operand.

The operation code occupies the four high-order bits. Bits 11-0 contain a 12-bit literal which is transferred as a control memory address. (This format is used for Jump Extended only.)

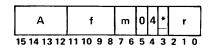

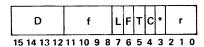

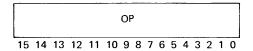

# **Operate Commands**

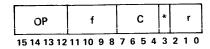

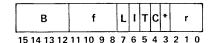

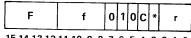

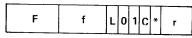

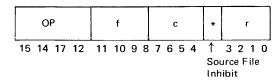

The operate class of commands have the following format:

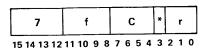

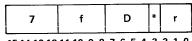

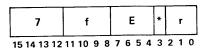

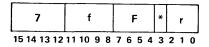

The operation code occupies the four high-order bits. Bits 11-8 contain the file register designator (f). Bits 7-4 contain the control (C) field designator.

C-Field Designators

| C-Field Bit Position | Designator | <u>Definition</u>     |

|----------------------|------------|-----------------------|

| 1000                 | L          | Link control/Add Link |

| 0001                 | С          | Modify Cond. Codes    |

| 0010                 | Т          | Select T              |

| 0100                 | F          | Select T Complement   |

| 0100                 | 1          | Add 1/Increment       |

| 0100                 | D          | Decrement             |

Bit 3 is file inhibit. When bit 3 is set to a one the resultant operation of the command is inhibited from being transferred to the designated file. Symbolically, this is specified to the assembler programs by appending an \* to the command mnemonic. The destination register (r) is specified in the three low-order bits, 2-0. When the designator is L or K the command requires 400 nanoseconds to execute.

r Field Destination Register Designators

| Bit Configuration | Designator | Register Designated               |

|-------------------|------------|-----------------------------------|

| 000               |            | None                              |

| 001               | T          | T Register                        |

| 010               | M          | M Register                        |

| 011               | N          | N Register                        |

| 100               | L          | L Register (adds 200 nanoseconds) |

| 101               | K          | K Register (adds 200 nanoseconds) |

| 110               | U          | U Register                        |

| 111               | S          | U Register ORed into upper        |

|                   |            | 8 bits of commands with           |

|                   |            | OP codes 8 through F.             |

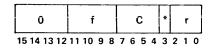

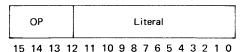

#### Generic Commands

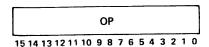

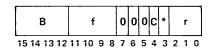

The generic class of commands have the following Formats:

The operation code occupies all 16 bits of the microcommand.

# JE JUMP EXTENDED

The contents of the 12-bit address field are placed in the L Register. If an inhibit L Register Save command has not been executed since the last Jump Extended, the following operation will also take place. The old contents of the L Register are stored in the L Save Register, or when the L Save Stack option is present, the L Register is stored in the 12 low-order bits of the current stack level, and the contents of the control memory bank Select Register is stored in the upper three bits of the current stack level. A Jump Extended command requires 400 nanoseconds to execute.

This command permits jumping anywhere within 4096 words of control memory in the basic machine. When the L Save Stack and extended control memory option is included, this command controls jumping anywhere within the current selected 4096-word bank of control memory. To jump from one bank of control memory to another, a Bank Select command (BSL) is executed followed by a Jump Extended command to the desired location in the selected 4096-word bank of control memory.

The Jump Extended command is assigned an operation code of 0 and is a special form of the Execute command which OR's the contents of the U Register into the eight high-order bits of the command. In order to obtain an operation code of 0 in the R Register, the four high-order bits of the U Register must be set to zero. If desired the four low-order bits of the U Register may be used to set bits 8-11 of the L Register; otherwise they should also be set to zero.

# LZ LOAD ZERO CONTROL

The load zero control command's eight-bit literal field is used to specify combined operations of the load zero group of generic instructions. If the literal field is 00 no operation (NOP) occurs. When multiple bits are specified, the designated control functions will execute.

This single command in a "vertical" sequence of microprogramming, contains "horizontal" microprogramming characteristics with the ability to perform multiple operations in a single 200 nanosecond clock interval.

### Load Zero Literal Field

| Bit Configuration | Code | Mnemonic — Operation                           |

|-------------------|------|------------------------------------------------|

| 0000 0000         | 00   | NOP — No Operation                             |

| 0000 0001         | 01   | ECR — Enable Communication Rate<br>Generators  |

| 0000 0010         | 02   | DCR — Disable Communication Rate<br>Generators |

| 0000 0100         | 04   | ICR - Input Communication Rate Generators      |

| 0000 1000         | 80   | Unassigned                                     |

| 0001 0000         | 10   | Unassigned                                     |

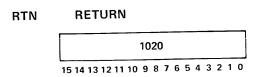

| 0010 0000         | 20   | RTN - Return                                   |

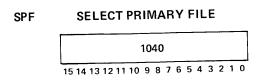

| 0100 0000         | 40   | SPF — Select Primary Files                     |

| 1000 0000         | 80   | SSF - Select Secondary Files                   |

Example: LZ 62 combines the three operations — DCR (disable rates), RTN (return) and SPF (SELECT primary files).

Note: If two commands with opposite functions are executed the existing state is changed to the opposite. Example: LZ 03 defines both enable and disable communication rate generators. When this command is executed the status of the communication rate generator control is complemented. If it was on, it is turned off. If it was off, it is turned on.

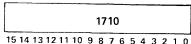

# NOP NO OPERATION 1000 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

This command performs no operation and can be used to insert a delay of 200 nanoseconds.

# ECR ENABLE COMMUNICATION RATE GENERATORS 1001 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The optional communication rate generators are enabled. These four hardware strappable time interval counters may be used for input bit sampling and output bit updating by microprograms performing serial to parallel and parallel to serial conversions.

# DCR DISABLE COMMUNICATION RATE GENERATORS

1002 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The optional communication rate generators are disabled.

# 1004 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

If the communication rate generators are enabled, and one or more rate is requesting service; bit 5 of the internal status byte will be set to a one and file zero, bit 3 will be set to a 1 indicating the presence of an internal interrupt.

This command allows the four communication rate generator flags to be read and reset by following it immediately with an Enter Internal Status (EIS) command. Bits 5-2 of this status byte will contain the current state of the four rate generators, and bits 7, 6, 1, and 0 should be ignored. The state of the internal status byte is not affected by this two command sequence.

The contents of the L Save Register are placed in the L Register or when the L Save Stack option is present, the low-order 12 bits of the current stack level are placed in the L Register and the high-order three bits of the current stack level are placed in the control memory bank select register. Execution requires 600 nanoseconds and the Inhibit L Save mode is cleared, if set, causing further Jump Extended commands to save the current contents of the L Register.

This command causes the primary file of registers to be selected for further file register operations. The primary file is also selected after a power on or by pressing master reset on the front panel.

# RSP RETURN AND SELECT PRIMARY FILE

This command combines the functions of Return (RTN), and Select Primary File (SPF), and executes in 600 nanoseconds.

# SSF SELECT SECONDARY FILE 1080 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

This command causes the secondary file of registers to be selected for further file register operations. This set will remain selected until execution of a Select Primary File command, or the occurrence of a master reset.

This command combines the functions of Return (RTN), and Select Secondary File (SSF), and executes in 600 nanoseconds.

The following commands provide for loading eight-bit literals into registers.

The contents of the eight-bit literal field are placed in the T Register. The condition flags and LINK are not affected.

The contents of the eight-bit literal field are placed in the M Register at a time when the memory is not busy. The condition flags and LINK are not affected.

# LN LOAD N 13 Literal 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The contents of the eight-bit literal field are placed in the N Register and the M Register is cleared at a time when the memory is not busy. The condition flags and LINK are not affected.

The contents of the eight-bit address field are placed in the eight low-order bits of the L Register, bits 8 and 11 of the command are placed in bits 8 and 9 of the L Register respectively. Bits 10 through 12 of the L Register and the optional control memory bank select register remain unchanged. The location of the next command is the address specified by the new contents of the L Register. These jump commands provide for jumping within a four-page block of 1024 words whose starting address is zero modulo 1024. The assembler program selects the proper command code from the address which must be in the 1024-word block containing the command. The command executes in 400 nanoseconds.

The contents of the eight-bit literal field are placed in the U Register. The condition flags and LINK are not affected. Due to look-a-head access method of the control memory, the new contents of the U Register are not available for command modification during the machine cycle immediately following the Load U command.

## LS LOAD SEVEN CONTROL

| 17                    |   |   | L | ite | era | ı |   |   |

|-----------------------|---|---|---|-----|-----|---|---|---|

| 15 14 13 12 11 10 9 8 | 7 | 6 | 5 | 1   | ~   | 2 | 1 | _ |

The individual bits of the literal field control independent functions. Any number of bits in the literal field may be one's. A number of the control functions are given mnemonics and are described later in this section. The function of each bit is as follows:

| Bit<br>Position | Function                     |

|-----------------|------------------------------|

| 0               | (unassigned and unavailable) |

| 1               | (unassigned and unavailable) |

| 2               | Disable External Interrupts  |

| 3               | Enable External Interrupts   |

| 4               | Disable Real Time Clock      |

| 5               | Enable Real Time Clock       |

| 6               | (unassigned and unavailable) |

| 7               | Halt Processor               |

# DEI DISABLE EXTERNAL INTERRUPTS

This command causes the external interrupt system to be disabled. Interrupts are not lost when the interrupt system is disabled, but cannot be recognized by the processor.

# EEI ENABLE EXTERNAL INTERRUPTS

The external interrupt system is enabled allowing the processor to recognize external interrupts.

# DRT DISABLE REAL-TIME CLOCK

The real-time clock and interrupt are disabled.

# ERT ENABLE REAL-TIME CLOCK

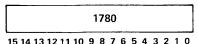

1720 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The real-time clock and interrupt are enabled. The first interrupt will occur after a full interrupt interval.

# HLT HALT

The processor is halted stopping all microcommand execution. However, the Direct Memory Access channel, if activated, will continue its operation until completion.

### LE LOAD EIGHT CONTROL

| 18                    | Literal  |

|-----------------------|----------|

| 15 14 12 12 11 10 0 9 | 76542210 |

This command is not implemented in the standard MICRO 1600. It can be defined for special user applications employing techniques similar to those used in Load Zero Control Group and Load Seven Control Group.

# RLT RETURN AND LOAD T

| 19                    |   |   | L | it | era | al |   |   |

|-----------------------|---|---|---|----|-----|----|---|---|

| 15 14 13 12 11 10 9 8 | 7 | 6 | 5 | 4  | 3   | 2  | 1 | 0 |

This command combines the functions of Return (RTN), and Load T (LT) and executes in 600 nanoseconds.

# MLC MODIFY LOWER COMMAND

This command causes the contents of the Output Data Buffer to be ANDed with 8 low-order bits of the next command accessed from the control memory. If the IC Register is set to 0, the contents of the Output

Data Buffer will be the same as the T Register. If the IC Register is not set to 0, the Output Data Buffer will contain the value that was in the T Register at the time the IC Register was set non-zero.

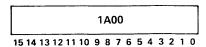

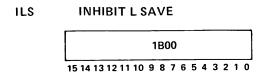

This command inhibits the saving of the L Register in the L Save Register or the Bank Select Register and the L Register in the current level of the L Save stack until execution of a Return command.

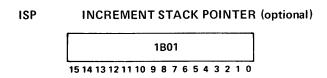

The contents of the four-bit stack pointer register are incremented by one to select the next level in the stack for saving the contents of the L Register during the next Jump Extended. If the modified contents of the register are greater than 15, bit 6 in file 0 will be set; otherwise it will be reset.

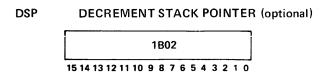

The contents of the four-bit stack pointer register are decremented by one to select the previous level in the stack for a return operation. If the modified contents of the register are less than zero, bit 6 in file 0 will be set; otherwise it will be reset.

# CSP CLEAR STACK POINTER (optional)

1B04 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The contents of the four bit stack pointer register are set to zero.

# BSL BANK SELECT (optional)

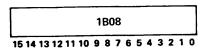

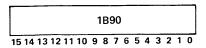

The bank select register is set to zero selecting the first 4096-word bank of control memory. The actual selection of the new bank takes place when the next Jump Extended command is executed. As shown below, variations of this command are used to select up to eight individual banks.

| BSL 0 | 1B08  | Select bank 0 | (0-4095)        |

|-------|-------|---------------|-----------------|

| BSL 1 | 1B 09 | Select bank 1 | (4096-8191)     |

| BSL 2 | 1B 0A | Select bank 2 | (8192-12,287)   |

| BSL 3 | 1B 0B | Select bank 3 | (12,288-16,383) |

| BSL 4 | 1B 0C | Select bank 4 | (16,384-20,479) |

| BSL 5 | 1B 0D | Select bank 5 | (20,480-24,575) |

| BSL 6 | 1B 0E | Select bank 6 | (24,576-28,671) |

| BSL 7 | 1B 0F | Select bank 7 | (28,672-32,767) |

# SSP SELECT STACK POINTER (optional)

This command causes loading and reading of the four-bit Stack Pointer Register. Execution of this command with the IC Register cleared causes the contents of the four low-order bits of the T Register to be placed in the stack pointer. Execution of this command following a stack input command places the contents of the stack pointer on the four low-order bits of the input bus.

#### SSU SELECT STACK UPPER (optional)

This command causes loading and reading of the upper seven bits of the selected L Save Stack register. Execution of this command with the IC Register cleared causes the contents of the T Register to be placed in the upper seven bits of the current L Save Stack level. Execution of the command following a stack input command places the contents of the upper seven bits of the current L Save Stack level on the input bus.

#### SSL SELECT STACK LOWER (optional)

This command causes loading and reading of the lower eight bits of the selected L Save Stack register. Execution of this command with the IC Register cleared causes the contents of the T Register to be placed in the lower eight bits of the current L Save Stack level. Execution of the command following a stack input command places the contents of the lower eight bits of the current L Save Stack Level on the input bus.

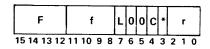

#### LF LOAD FILE REGISTER

| 2           |    | f  | _ |   |   |   | ı | Lit | er | al | _ |   |

|-------------|----|----|---|---|---|---|---|-----|----|----|---|---|

| 15 14 13 12 | 11 | 10 | 0 | o | 7 | _ | _ | _   | 2  | ~  | _ | _ |

The contents of the eight-bit literal field are placed in the file register designated by f. Since file register 0 is not used for general storage, it is not to be loaded by this command. The condition flags and LINK are not affected.

#### ΑF ADD TO FILE REGISTER

The contents of the eight-bit literal field are added to the contents of the file register designated by f. Since file register 0 is not used for general storage, it is not altered by this command. Two's complement subtraction may be performed by placing the two's complement of the operand in the literal field. The condition flags and LINK are not affected.

The following three test commands provide for arithmetic comparison and logical testing of bits. When the compare or test condition is met the next command in sequence is treated as a no operation, and there is a delay of 200 nanoseconds before executing the next command.

### TZ TEST IF ZERO

If, for all the one bits of the literal field, the corresponding bits of the file register designated by f are zero, the next command is not executed. This command performs the logical product of the literal and the contents of the file register and tests for zero result. The condition flags, LINK and designated file register are not affected.

### TN TEST IF NOT ZERO

If, for any one bit in the literal field, the corresponding bit of the file register designated by f is also a one, the next command is not executed. This command performs a logical product of the literal and the contents of file register and tests for not zero. The condition flags, LINK and designated file register are not affected.

### CP COMPARE

If the sum of the contents of the literal field and the file register designated by f is greater than 255, the next command is not executed. The condition flags and designated file register are not affected. The LINK stores the carry out of the adder. This means that if the skip is not taken, the content of LINK will be a 0, or if the skip is taken, the content of LINK will be set to a 1.

All forms of command seven unconditionally update the arithmetic condition codes in file 0, but do not affect the LINK. A destination of seven is undefined for these commands. In other words, the U Register may not be used to modify the command. All permissible variations of the basic command seven are explained. Unlisted c field values, (bits 7-4), are not assigned assembler mnemonics and will not be executed by the simulator.

The following four commands provide special data flow operations.

#

The status of the four console sense switches, with four low-order one bits appended, are placed in the file register designated by f, if \* is zero, and in the register designated by r. The status of a switch is a one, when the switch is set.

The four high-order bits of the file register designated by f are placed in the four low-order bits of that file, if \* is zero, and in four low-order bits of the register designated by r. The four high order bits of the result are set to ones.

The eight internal status bits are placed in the file register designated by f, if \* is zero, and in the register designated by r. The internal interrupt flag in file 0 is reset by this command, along with the console interrupt, real time clock, and power fail/restart status bits. Console step is reset upon release of the console switch and spare bits are controlled according to their individual implementation in hardware.

# ECS ENTER CONSOLE SWITCHES

7070 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The contents of the eight low-order console command switches are ANDed with the eight low-order bits of the next command. The value of a switch is a one, when the switch is set. If the switch is either not set, or, as in the case of a basic panel, not there, its value is a zero. File register 0 and destination register 0 must be selected because data movement is not permitted.

The command could be used to implement eight additional sense switches. This is done by following the Enter Console Switches command with a Load Register or Load File command that has a literal value of all ones.

The next eight command descriptions explain control of the input/output buss for standard Microdata peripheral controllers. If a system is to contain only special controllers, these signals could be assigned any desired function subject to the following rule. Whenever the value in the I/O Control Register (IC), is set to four, five, six, or seven, the input buss is enabled in the CPU. This means that the input buss will be substituted for the T Register by any command that selects the T Register or its complement.

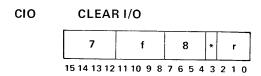

A value of 0 is placed in the I/O Control Register (IC), which removes all control signals from the I/O buss. This places the buss in the no activity mode. All standard Microdata peripheral controllers require the K Register to return to the zero state after each non-zero setting. When the current contents of the IC Register is 0, 1, 2, or 3, the file register designated by f is moved to the register designated by r. When the current contents of the IC Register is 4, 5, 6, or 7, the contents of the input buss are ANDed with the file register designated by f. The result is placed in the file register, if \* is zero, and in the register designated by r.

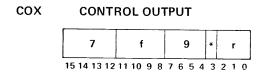

A value of 1 is placed in the IC Register which enables the control output signal until removed by a Clear I/O command. The contents of the file register designated by f are moved to the register designated by r.

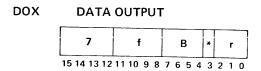

A value of 2 is placed in the IC Register which enables the data output signal until removed by a Clear I/O command. The contents of the file register designated by f are moved to the register designated by r.

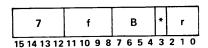

# SOX SPARE OUTPUT

A value of 3 is placed in the IC Register which enables the spare output signal until removed by a Clear I/O command. This command also removes the MARKing current from the serial I/O channel causing a SPACEing condition. The contents of the file register designated by f are moved to the register designated by r.

# CAK CONCURRENT ACKNOWLEDGE

A value of 4 is placed in the IC Register which enables the concurrent acknowledge signal until removed by a Clear I/O command. Upon removal of this signal, the requesting controller will reset the concurrent request flag bit in file 0. The contents of the file register designated by f are moved to the register designated by r.

# IAK INTERRUPT ACKNOWLEDGE

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

A value of 5 is placed in the IC Register which enables the interrupt acknowledge signal until removed by a Clear I/O command. Upon removal of this signal, the requesting controller will reset the external interrupt request flag bit in file 0. The contents of the file register designated by f are moved to the register designated by r.

# DIX DATA INPUT

A value of 6 is placed in the IC Register which enables the data input signal until removed by a Clear I/O command. The contents of the file register designated by f are moved to the register designated by r.

# SIX STACK INPUT

A value of 7 is placed in the IC Register which enables the stack input signal until removed by a Clear I/O command. If the L Save stack is not in the machine, this signal may be used as a spare input.

The following commands operate on a specified file register. In addition some other operation such as input or memory control may take place. Some commands in this section are adaptations of others. For example, the Increment command is a form of the Add command. These adaptations are provided with their own mnemonics because of their frequent use and to simplify programming.

The sum of the contents of the file register designated by f and the selected operand is formed. The sum is placed in the file register if \* is zero and in the register designated by r. The state of the carry out of the high-order bit position of the adder is placed in LINK. The five Modifier bits perform the following control:

- L Link Control: The content of LINK is added to the sum. When

this flag is a one the zero condition flag can be reset but not

set. This allows for propagation of the zero test over multiple

byte operations, the first of which would have this bit off.

- I Increment: One is added to the sum.

- T Select T: The contents of the T Register or the input bus is selected as the B-bus operand. If this bit is off the operand is zero.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

This command is a form of the Add command. The contents of the file register designated by f are incremented and the result is placed in the file register if \* is zero and in the register designated by r. The state of the carry out of the high-order bit position of the adder is placed in LINK. The two modifier bits perform the following control:

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

# SBT SUBTRACT (Two's complement)

The two's complement difference of the contents of the file register designated by f and the selected operand is formed. The difference is placed in the file register if \* is zero and in the register designated by r. The state of the carry out of the high-order bit position of the adder is placed in LINK. The four modifier bits perform the following control:

- L Link Control: The content of LINK is added to the one's complement difference. When this flag is a one the zero condition flag can be reset but not set. This allows for propagation of the zero test over multiple byte operations, the first of which would have this bit off.

- T Select T: The contents of the T Register or the Input Bus is selected as the B Bus operand. If this bit is off the operand is zero.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

# SBO SUBTRACT (One's complement)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The one's complement difference of the contents of the file register designated by f and the selected operand is formed. The difference is placed in the file register if \* is zero and in the register designated by r. The state of the carry out of the high-order bit position of the adder is placed in LINK. The four modifier bits perform the following control:

- L Link Control: The content of LINK is added to the difference. When this flag is one the zero condition flag can be reset but not set. This allows for propagation of the zero test over multiple byte operations, the first of which would have this bit off.

- T Select T: The contents of the T Register or the Input Bus is selected as the B Bus operand. If this bit is off the operand is zero.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the File register.

## DEC DECREMENT

The contents of the file register designated by f is decremented by one and the result is placed in the file register if \* is zero and in the register designated by r. The state of the carry out of the high-order bit position of the adder is placed in LINK. The two modifier bits perform the following control:

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

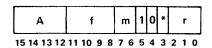

# RMF READ MEMORY, FULL CYCLE

The contents of the file register designated by f in unaltered, incremented or decremented form as determined by m, is placed in the file register if \* is zero and in the register designated by r. The condition flags and LINK are not affected. Subsequently a full cycle memory read is initiated at the location specified by the contents of the M and N Registers. Command execution is delayed if the memory is busy when the command is accessed. The accessed data is placed in the T Register 400 nanoseconds after the command is executed and the addressed memory location is left unaltered.

The contents of the file register are modified as follows:

m

- No flag 00 The contents of the selected file register are transferred unaltered to the specified destination register.

- D 01 Decremented: The contents of the file register minus 1 are routed as specified unless the M register is specified to receive the result. When the M register is selected the contents of the file register, minus 1, plus the content of LINK are routed.

- L 10 Add Link: The content of LINK is added to the contents of the file register and the sum is routed as specified.

- 1 11 Increment: The contents of the file register is incremented by 1 and the result is routed as specified.

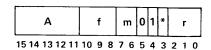

# RMH READ MEMORY, HALF CYCLE

The contents of the file register designated by f in unaltered, incremented or decremented form as determined by m, is placed in the file register if \* is zero and in the register designated by r. The condition flags and LINK are not affected. Subsequently a half cycle memory read is initiated at the location specified by the contents of the M and N Registers. Command execution is delayed if the memory is busy when the command is accessed. The accessed data is placed in the T Register 400 nanoseconds after the command is executed and the memory location is left in an all one's condition.

The contents of the file register are modified as follows:

m

- No flag 00 The contents of the selected file register are transferred unaltered to the specified destination register.

- D 01 Decremented: The contents of the file register minus 1 are routed as specified unless the M Register is specified to receive the result. When the M Register is selected the contents of the file register, minus 1, plus the content of LINK are routed.

- L 10 Add Link: The content of LINK is added to the contents of the file register and the sum is routed as specified.

- 1 11 Increment: The contents of the file register is incremented by one and the result is routed as specified.

# WMF WRITE MEMORY, FULL CYCLE

The contents of the file register designated by f in unaltered, incremented or decremented form as determined by m is placed in the file register if \* is zero and in the register designated by r. The condition flags and LINK are not affected. Subsequently a full cycle memory write operation is initiated at the location specified by the contents of the M and N Registers. Command execution is delayed if the memory is busy when the command is accessed.

The data to be written must be in the T Register at the time the command is executed, or must be entered into the T Register with the next command. The T Register may be used for other uses with the second command after the WMF.

The contents of the file register are modified as follows:

m

- No flag 00 The contents of the selected file register are transferred unaltered to the specified destination register.

- D 01 Decremented: The contents of the file register minus 1 are routed as specified unless the M Register is specified to receive the result. When the M Register is selected the contents of the file register, minus 1, plus the content of LINK are routed.

- L 10 Add Link: The content of LINK is added to the contents of the file register and the sum is routed as specified.

- I 11 Increment: The contents of the file register is incremented by one and the result is routed as specified.

# WMH WRITE MEMORY, HALF CYCLE

The contents of the file register designated by f in unaltered, incremented or decremented form as determined by m is placed in the file register if \* is zero and in the register designated by r. The condition flags and LINK are not affected. Subsequently a half cycle memory write operation is initiated at the location specified by the contents of the M and N Registers. Command execution is delayed if the memory is busy when the command is accessed. The data to be written must be in the T Register when the command is executed. The contents of the addressed memory location must be all one bits for a proper write to take place, because there will be an ANDing of the original contents of the memory location and the contents of the T Register. The T Register may be used for other purposes with the first command after WMH.

The contents of the file register are modified as follows:

m

- No flag 00 The contents of the selected file register are transferred unaltered to the specified destination register.

- D 01 Decremented: The contents of the file register minus 1 are routed as specified unless the M Register is specified to receive the result. When the M Register is selected the contents of the file register, minus 1, plus the content of LINK are routed.

- L 10 Add Link: The content of LINK is added to the contents of the file register and the sum is routed as specified.

- 1 11 Increment: The contents of the file register are incremented by one and the result is routed as specified.

# CPY COPY

The selected operand is placed in the file register designated by f if \* is zero and in the register designated by r. The LINK is not affected. The 5 modifier bits perform the following control:

- L Link Control: The content of LINK is added to the operand. When this bit is a one the zero condition flag can be reset but not set. This allows for propagation of the zero test over multiple byte operations, the first of which would have this bit off.

- I Increment: One is added to the operand.

- T Select T: The contents of the T Register or the input bus is selected as the B Bus operand. If this bit is zero the operand is zero.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

# ZOF ZERO FILE

A value of zero is placed in the file register designated by f if \* is zero and in the register designated by r. The LINK is not affected. The two modifier bits perform the following control:

- C Condition Flag Update: The condition flags are updated according to the zero data.

- \* File Write Inhibit: The zero is not placed in the file register.

#### POF PLUS ONE TO FILE

A value of plus one is placed in the file register designated by f if \* is zero and in the register designated by r. The LINK is not affected. The two modifier bits prefer the following control:

- C Condition Flag Update: The condition flags are cleared.

- \* File Write Inhibit: The plus one is not placed in the file register.

#### LOR LOGICAL OR

The logical inclusive-OR of the contents of the file register designated by f and the selected operand is placed in the file register if \* is zero and the register designated by r. The LINK is not affected. The five modifier bits perform the following control:

- L Link Control: When this bit is a one the zero condition flag can be reset but not set. This allows for propagation of the zero test over multiple byte operations, the first of which would have this bit off.

- F Select T Complement: The one's complement of the contents of the T Register or input bus are selected as the B Bus operand.

If the T Register is also selected the effective operand contains all one's.

- T Select T: The contents of the T Register or the Input Bus is selected as the B Bus operand. If both the T and F bits are off the selected operand is zero.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

# MOV MOVE

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The contents of the file register designated by f are moved to the register designated by r. The LINK is not affected. The three modifier bits perform the following control:

- L Link Control: When this bit is a one the zero condition flag can be reset but not set. This allows for propagation of the zero test over multiply byte operations, the first of which would have this bit off.

- C Condition Flag Update: The condition flags are updated according to the contents of the file register.

- \* File Write Inhibit: The result is not placed in the file register.

# XOR EXCLUSIVE-OR

The exclusive-OR of the contents of the file register designated by f and the selected operand is placed in the file register if \* is zero and in the register designated by r. The LINK is not affected. The five modifier bits perform the following control:

- L Link Control: When this bit is a one the zero condition flag can be reset but not set. This allows for propagation of the zero test over multiple byte operations, the first of which would have this bit off.

- F Select T Complement: The one's complement of the contents of the T Register or Input Bus are selected as the B Bus operand.

If the T Register is also selected the effective operand contains all one's.

- T Select T: The contents of the T Register or the Input Bus is selected as the B Bus operand. If both the T and F bits are off the selected operand is zero.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

#### AND AND

The logical product (AND) of the contents of the file register designated by f and the selected operand is placed in the file register if \* is zero and in the register designated by r. The LINK is not affected. The five modifier bits perform the following control:

- L Link Control: When this bit is a one the zero condition flag can be reset but not set. This allows for propagation of the zero test over multiple byte operations, the first of which would have this bit off.

- F Select T Complement: The one's complement of the contents of the T Register or Input Bus are selected as the B Bus operand.

If the T Register is also selected the effective operand contains all one's.

- T Select T: The contents of the T Register or the Input Bus is selected as the B Bus operand. If both the T and F bits are off the selected operand is zero.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The result is not placed in the file register.

# SFL SHIFT LEFT

The contents of the file register designated by f are shifted one bit position to the left and placed in the file register if \* is zero and the register designated by r. The high-order bit which is shifted out is placed in LINK. A zero or the content of LINK is shifted into the vacated bit position as determined by the L modifier bit. The three modifier bits perform the following controls:

- L Link Control: LINK content is shifted into low-order bit of result. When this bit is a one the zero condition flag can be reset but not set. This allows for propagation of zero test over multiple byte operations, the first of which would have this bit off.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The shifted register contents are not placed in the file register.

#### SLI SHIFT LEFT AND INSERT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The contents of the file register designated by f are shifted 1 bit position to the left and placed in the file register if \* is zero and the register designated by r. The high-order bit which is shifted out is placed in LINK. A one is inserted in the vacated low-order bit position. The two modifier bits perform the following control:

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The shifted register contents are not placed in the file register.

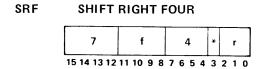

#### SFR SHIFT RIGHT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The contents of the file register designated by f are shifted one bit position to the right and placed in the file register if \* is zero and the register designated by r. A zero or the content of LINK is shifted into the vacated bit position as determined by the L modifier bit. The low-order bit which is shifted out is placed in LINK. The three modifier bits perform the following control:

- L Link Control: LINK content is shifted into low-order bit of result. When this bit is a one the zero condition flag can be reset but not set. This allows for propagation of zero test over multiple byte operations, the first of which would have this bit off.

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- $^{st}$  File Write Inhibit: The shifted register contents are not placed in the file register.

# SRI SHIFT RIGHT AND INSERT

The contents of the file register designated by f are shifted 1 bit position to the right and placed in the file register if \* is zero and the register designated by r. A one is inserted into the vacated high-order bit position. The low-order bit which is shifted out is placed in LINK. The two modifier bits perform the following control:

- C Condition Flag Update: The condition flags are updated according to the result of the current operation.

- \* File Write Inhibit: The shifted register contents are not placed in the file register.

The two Execute commands are special commands which cause the eight high-order bits of the U Register to be ORed with the eight high-order bits of control memory output. The ORing is performed before the command is gated into the R register. The actual command executed is a combination of the bits in the U Register and those read out of control memory. The Execute command is designated by zero in the four high-order bits of the command in control memory. An effective command with zeros in these bits is a Jump Extended. The 12 remaining bits of the Execute command can be coded as needed. The same effect as the Execute command can be obtained by coding destination register 7 on operate commands.

The Execute command is used for command modifications generally to save on the number of commands needed in a program. Three uses of this feature are:

- Indexing of file registers in a loop.

- Selection of alternate file register depending on program variables.

- Performing different functions such as load, add, subtract etc. in a common string of coding.

An example is shown below. The X'81' contents of the U Register merge with the execute command in control memory to form an Add to file register 5.

| U Register        | '81'   |

|-------------------|--------|

| Control Memory    | '0420' |

| Effective Command | '8520' |

# **EOT EXECUTE, OPERATE TYPE**

The eight-bit contents of the U Register are ORed with the eight high-order bits of the command to form an effective command which is then executed. The f, C, \*, and r fields are used as described for the desired effective command. In coding the c-field bits any modifier may be used.

# ELT EXECUTE, LITERAL TYPE

The eight-bit contents of the U Register are ORed with the eight high-order bits of the command to form an effective command which is then executed. The f and Literal fields are used as described for the desired effective command.

# **CHAPTER 4**

# CONTROL PANEL OPERATION

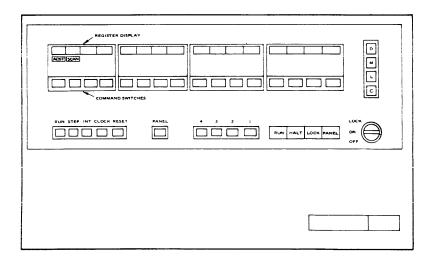

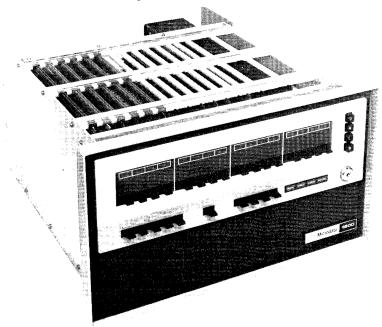

The MICRO 1600 system console control panel (Figure 2) provides for control of the running of the processor, display of register contents and execution of commands. The panel is very useful in debugging microprograms and can also be used for macro level machine control and software debugging. The control panel can be replaced by a minimum basic console control panel which eliminates the display and manual command execution.

All console panels are pluggable and fully interchangeable without modification of the computer.

An optional parallel Teletype controller, physically contained within the control consoles, may be specified.

#### SYSTEM CONSOLE

The system console provides control plus a selectable display of all hardware registers in the machine including the files. It is designed for maintenance operations and for installations where system development and firmware checkout is being performed.

Figure 2. MICRO 1600 System Console

#### **DISPLAYS**

# Data Display

The 16-bit data indicators (16 lamps on console) display the 8-bit A Bus, Memory Address, 16-bit Control Memory Output, or 12-bit Control Memory Address as selected by the Display Selector switches.

#### Run

The RUN indicator is on when the processor is running.

#### Halt

The HALT indicator is on when the power is applied and the processor is not running.

#### Lock

The LOCK indicator is on when the panel is disabled.

#### **Panel**

The PANEL indicator is on when the command switches are enabled and substituting for the control memory.

#### Scan

The SCAN indicator is on when in the SCAN mode. This takes place with the PANEL switch off and command switch 14 is on.

# **Address Stop**

The ADST indicator is on when the processor has stopped because of address breakpoint.

#### **SWITCHES**

# **Display Selector**

The four interlocked switches located in the upper right hand corner select one of the four displays as follows:

- D Data: This 8-bit display is the processor's A Bus. The data on the A bus when the processor is halted and in the panel enable mode depends on the setting of the command switches.

- $M\,-\,$  Memory Address: This 16-bit display is of the memory address lines. This is normally the contents of the M and N registers.

- L Control Memory Address: This 12 or 15-bit display is the contents of the L Register.

- C Control Memory: This 16-bit display is of the output of the control memory. When the processor is halted the R Register contains the same data.

#### **Command Switches**

These 16 locking switches are substituted for the control memory when the PANEL switch is in the down position. When the processor is halted

the switch setting is constantly clocked into the R Register and depressing the CLOCK switch causes the command set in the switches to be executed. The command may also be executed repeatedly by depressing the RUN switch. These switches are used to gate registers onto the A Bus for display and for entering data into registers.

#### Panel Switch

This locking switch selects the source of commands. When in the normal up position the control memory is used and when in the down position the 16 command switches on the panel are substituted for the control memory.

#### Sense Switches