# MICROPROGRAMMING REFERENCE MANUAL

# 3200 **MICROPROGRAMMING** REFERENCE MANUAL

February, 1976

#### PROPRIETARY INFORMATION

The information contained herein is proprietary to and considered a trade secret of Microdata Corporation and shall not be reproduced in whole or part without the written authorization of Microdata Corporation.

Microdata Corporation 17481 Red Hill Avenue, Irvine, California 92714 Post Office Box 19501, Irvine, California 92713 Telephone: 714/540-6730 · TWX: 910-595-1764

# TABLE OF CONTENTS

| Section | <u>Title</u>                                                                                                                                                                                                                                | Topic                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1       | INTRODUCTION THE MICRODATA 3200 COMPUTER HOW TO USE THIS MANUAL                                                                                                                                                                             | 1.1<br>1.2                                    |

| 2       | HARDWARE ORGANIZATION AN OVERVIEW THE MICRO-CONTROL SECTION THE USER-LEVEL INSTRUCTION FETCH SECTION THE DATA INTERFACE SECTION THE ARITHMETIC/LOGIC SECTION THE LOCAL MEMORY AND AUXILIARIES SECTION THE FRONT PANEL SECTION               | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 |

| 3       | INTRODUCTION TO CAP32 MICROINSTRUCTION FORMAT C-REGISTER FIELDS                                                                                                                                                                             | 3.1<br>3.2                                    |

| 4       | FBUS DESTINATIONS AND SOURCES DIRECT FBUS DESTINATIONS LOCAL MEMORY (LM) FBUS DESTINATIONS LOCAL MEMORY (LM) AND SINGLE-BIT GENERATOR ARRAYS AS FBUS SOURCES                                                                                | 4.1<br>4.2<br>4.3                             |

|         | OTHER DIRECT FBUS SOURCES MONOBUS DATA ACCESS MONOBUS WORD AND BYTE TRANSFERS                                                                                                                                                               | 4.3<br>4.4<br>4.5<br>4.6                      |

| 5       | ALU SOURCES AND OPERATIONS ALU SOURCES ALU PAIRED LOGIC OPERATIONS AND ABUS DECREMENTATION ALU ARITHMETIC OPERATIONS ALU ARITHMETIC FLAGS ALU TARGET FLAG REGISTER ELEMENTARY SHIFT OPERATIONS                                              | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6        |

| 6       | CONTROL MEMORY ADDRESSING AND CAP32 ASSEMBLY LISTING CONTROL MEMORY ADDRESSING CAP32 ASSEMBLY LISTING                                                                                                                                       | 6.1<br>6.2                                    |

| 7       | BRANCHING CAPABILITIES  UNCONDITIONAL AND CONDITIONAL BRANCHING CONDITIONAL BRANCHING: GI AND WNZ TESTS CONDITIONAL BRANCHING: ARITHMETIC FLAG AND WORKING REGISTER TESTS SUBROUTINE BRANCHING FULL-BYTE LITERAL SUBROUTINES AND CONTROLLED | 7.1<br>7.2<br>7.3<br>7.4                      |

|         | WORD PAIRING  ABSOLUTE STATEMENT LOCATION AND CONTROL  BRANCHING                                                                                                                                                                            | 7.5<br>7.6                                    |

|         |                                                                                                                                                                                                                                             |                                               |

# TABLE OF CONTENTS (Continued)

| <u>Section</u> | <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Topic                                                   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 8              | VECTORS AND PSEUDO-INSTRUCTIONS AN OVERVIEW DATA VECTORS USER-LEVEL INSTRUCTION FETCH AND DECODE CYCLE FIRST-DIGIT BRANCHING VECTORS AND INTERRUPT VECTORS SECOND-DIGIT BRANCHING VECTORS FURTHER CAP32 PSEUDO-INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                  | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                  |

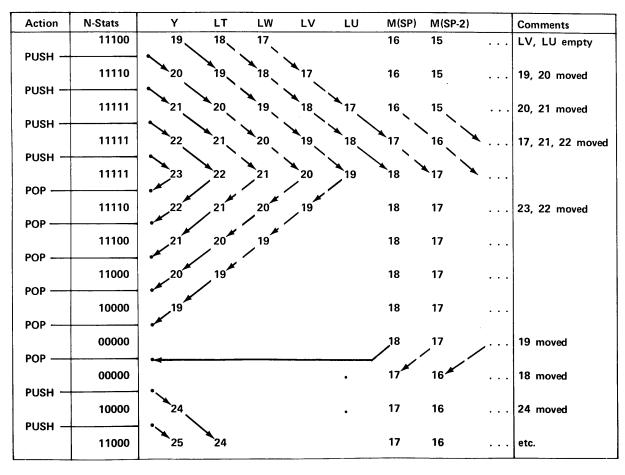

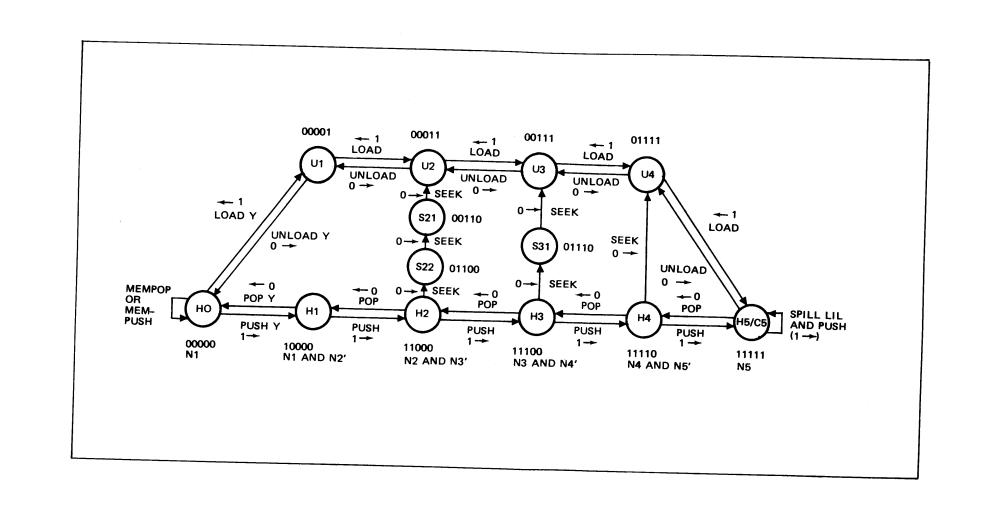

| 9              | STACK PROCESSING STACK PROCESSING IN MAIN MEMORY ONLY STACK ORGANIZATION: THE T-COUNTER AND N-STATS SIMPLE STACK OPERATIONS IN AN ACTIVE STACK HEAD SPECIAL STACK HEAD PROCESSES STATE DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                               | 9.1<br>9.2<br>9.3<br>9.4<br>9.5                         |

| 10             | INPUT/OUTPUT MICROPROGRAMMING INPUT/OUTPUT CONTROLLERS INTERRUPT SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.1<br>10.2                                            |

| 11             | CONTROL PANELS BASIC PANEL MAINTENANCE PANEL MAINTENANCE PANEL CONTROLS AND INDICATORS MAINTENANCE PANEL FIRMWARE DISPLAY SELECTOR SWITCHES AND MONOBUS INTERFACE MAINTENANCE PANEL BREAK CONDITION MAINTENANCE PANEL INTERNAL LOGIC                                                                                                                                                                                                                                                                                                                                                                         | 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6            |

| Appendix       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u>Table</u>                                            |

| A              | REFERENCE TABLES  SYNTAX FOR CAP32 OPF AND REF FIELDS  RELATED TO C-FIELD VALUES  DIRECT FBUS DESTINATION CODE SETS USED IN  CAP32 SUBFIELD REF1  LOCAL MEMORY FBUS DESTINATION CODES USED  IN CAP32 SUBFIELD REF1  LOCAL ARRAY FBUS SOURCE CODES USED IN CAP32  SUBFIELD OPF1  CONTROL AND USE OF THE G-COUNTER  DIRECT FBUS SOURCES OTHER THAN LOCAL ARRAYS  ALU SOURCES USED IN CAP32 SUBFIELD OPF1  ELEMENTARY LEFT SHIFT CODES  ELEMENTARY RIGHT SHIFT CODES  CCNTROL MEMORY ADDRESSING MODE  AVAILABLE CONDITIONAL BRANCH TESTS  I-REGISTER BYTE EFFECTS ON THE CPU  INTERRUPT TYPES IN PRIORITY ORDER | A-1 A-2 A-3 A-4 A-5 A-6 A-7 A-8 A-9 A-10 A-11 A-12 A-13 |

# TABLE OF CONTENTS (Continued)

| Appendix | <u>Title</u>                                     | <u>Table</u> |

|----------|--------------------------------------------------|--------------|

|          | STACK HEAD CONTROL: MANIPULATION OF T-COUNTER    | A 1.4        |

|          | AND N-STATS                                      | A-14         |

|          | DEVICE REGISTER BLOCK STATUS WORD (DRB(0))       | A-15         |

|          | DEVICE REGISTER BLOCK ORDER BYTE (DRB(1)./:0)    | A-16         |

|          | DEVICE REGISTER BLOCK MODE BYTE (DRB(1).15:8)    | A-17         |

|          | BASIC PANEL KEY-SWITCH FUNCTIONS                 | A-18         |

|          | MAINTENANCE PANEL STATUS INDICATORS              | A-19         |

|          | MAINTENANCE PANEL HARDWARE CONTROL SWITCHES (HC) | A - 20       |

|          | MAINTENANCE PANEL HARDWARE DISPLAY SELECTOR      |              |

|          | SWITCHES (HS)                                    | A-21         |

|          | MAINTENANCE PANEL ACCESS THROUGH THE MONOBUS     | A-22         |

|          | STRUCTURE OF THE PANEL STATUS WORD (PSW)         | A - 23       |

INDEX

#### 1 INTRODUCTION

#### 1.1 THE MICRODATA 3200 COMPUTER

The Microdata 3200 is a high-performance, low-priced computer which employs microprogramming techniques to expand user capabilities. This manual describes the logical and physical structure of the 3200, and presents microprogramming procedures for users wishing to develop a computer that is an extension of the standard Microdata 32/S computer.

# The 3200 Computer

The Microdata 3200 is a 16-bit machine with 16K bytes of 350 nanosecond MOS main memory, addressable to the byte level. It is microprogrammed using a bipolar 32-bit Control Memory (expandable to 4K words) that has a 135 nanosecond cycle time.

The 3200 utilizes a common bus, called the MONOBUS, for accessing all main memory modules and I/O device controllers. Memories and controllers of various speeds may be mixed on the asynchronous MONOBUS and uniformly accessed with standard memory reference instructions. Overlapped bus requesting and data transferring permits very high-speed data transfers.

Input/Output (I/O) can be byte or word oriented under program control, or block oriented under either computer control (concurrent I/O) or controller hardware control (Direct Memory Access). Four external interrupt lines establish the relative priorities of groups of I/O device controllers. Relative priority among the controllers on each line is established by their positions along the MONOBUS. Each I/O device controller may be manually assigned to a specific address and interrupt line. A unique interrupt processing procedure and environment may be specified for each I/O device address.

#### 3200 Microprogramming

The standard Microdata 32/S computer is implemented via firmware on the microprogrammable 3200. To develop a computer that is an extension of the standard 32/S, an appropriate set of microprograms (i.e., firmware) must be developed, debugged, and stored in the Control Memory of the 3200. The 3200 then efficiently emulates the computer defined by the special microprogrammed firmware.

Meaningful microprograms may be realized through the use of the CAP32 Microassembly Language. Source routines written in CAP32 are assembled by the CAP32 Microassembler, which is a program written in PL/1 for operation on host machines such as the IBM 360/50, 370/145, or larger machines of that family. A CAP32 Microassembler that will run on the Microdata 32/S is currently being planned; consult a Microdata representative for availability information.

Conventional programming can often be performed with little attention being paid to hardware aspects. This is not true of microprogramming. The 3200

structure makes it mandatory that the programmer have a thorough knowledge of the logical and physical structure of the system. The 3200 is competent over a wide range of problems, but is superlative where the problem matches the optimization features of the machine. Thus, the programmer must know the 3200 hardware from a logic viewpoint, must know the CAP32 language, and must know the effects of one upon the other.

The 3200 machine language microcode that results from the CAP32 microassembly is stored in the 3200 Control Memory, defining a user-level machine language. The "3200-x" machine defined by that microcode will then execute user-programs written in user-language "x".

#### 1 INTRODUCTION

#### 1.2 HOW TO USE THIS MANUAL

This manual is written in modular format with each pair of facing pages presenting a single topic.

The approach taken in this manual differs substantially from the typical reference manual format. Here each pair of facing pages discusses an individual topic. Generally the left-hand page is devoted to text, while the right-hand page presents figures referred to by that text. At the head of each text page are a pair of titles, the first one naming the section and the second one naming the topic. Immediately below these titles is a brief summary of the material covered in the topic.

The advantage of this format will become readily apparent to the reader as he begins to use this manual. First of all, the figures referred to in the text are always conveniently right in front of the reader at the point where the reference is made. Secondly, there is a psychological advantage to the reader in knowing that when he has completed reading a topic and goes to turn the page, he is done with one idea and ready to encounter a new one.

A scan of the Table of Contents provides a quick overview of the objectives of this manual. The topics should normally be studied in the sequence in which they are presented; however, extensive cross-references (and a complete index) permit random access. Cross-references are provided via footnotes which reference the applicable topic(s) by topic number.

A complete set of reference tables are provided in the appendix to this manual. These tables are referenced as needed throughout the topics.

Special symbols are used throughout this manual for purposes of clarity and conciseness; these symbols are defined in Figure A. In presenting general instruction and code formats, certain conventions apply; these conventions are defined in Figure B.

| Symbol | Description                                                                                                                                                                                                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .•     | The period character (.) is used in signal names to specify the applicable bit(s). For example, "FBUS.3" denotes the third bit of the FBUS, while "Z.2" denotes the second bit of the Z-Register.                                                                                                                            |

| :      | The colon (:) is used as a separator for range limits. For example, "0:9" denotes the numeral 0 through 9, while "FBUS.4:0" denotes bits 4 through 0 of the FBUS.                                                                                                                                                            |

| :=     | This sumbol is used to denote replacement. For example, "X := 13" means that the current content of the X-Register is replaced by the value 13, while "Y := Y+1" means that the current content of the Y-Register is incremented by 1. This symbol is primarily used in the Reference Tables in the appendix to this manual. |

Figure A. Special Symbols Used in This Manual

| Convention | Description                                                                                                                                           |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPPER CASE | Characters or words printed in upper case are required and must appear exactly as shown.                                                              |

| lower case | Characters or words printed in lower case are parameters to be supplied by the user.                                                                  |

| []         | Brackets surrounding a word and/or parameter indicate that the word and/or parameter is optional and may be included or omitted at the user's option. |

Figure B. Conventions Used in General Formats

#### 2.1 AN OVERVIEW

The hardware of the 3200 is divided into two main categories: the Central Processing Unit (CPU) and the External Devices. Communication between the CPU and the External Devices is via the high-speed MONOBUS.

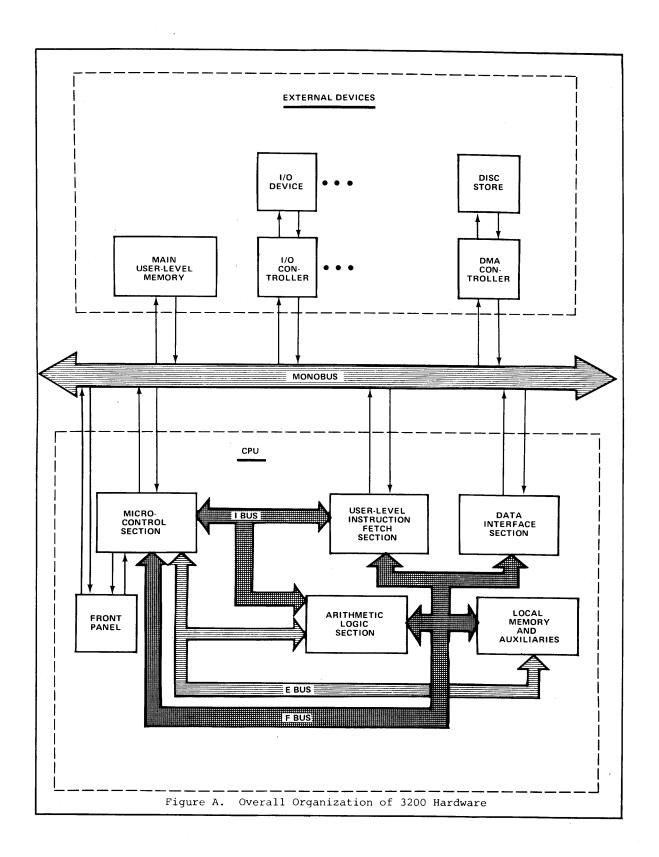

The overall organization of the 3200 hardware is illustrated in Figure A. The CPU is divided into six main sections:

- The Micro-Control Section

- The User-Level Instruction Fetch Section

- The Data Interface Section

- The Arithmetic/Logic Section

- The Local Memory and Auxiliaries Section

- The Front Panel Section

These sections of the CPU are synchronized with a 135-nanosecond clock; they are described in detail in the remaining topics of this section.

The External Devices consist of the Main User-Level Memory and a full complement of peripherals (such as tapes, discs, terminals, and communications controllers). All external devices, including the Main User-Level Memory, work asynchronously from the CPU and communicate over a high-speed bus arrangement, called the MONOBUS.

The MONOBUS contains 16 data lines, 18 address lines, and 19 control lines, providing high-speed data transfers in as little as 500 nanoseconds (depending on the speed of the external device). The MONOBUS is controlled by the CPU and the Direct Memory Access (DMA) unit. Allocation of the MONOBUS to one of the controlling units is by priority polling, each unit holding the MONOBUS just long enough to effect the current transfer. The MONOBUS includes 4 priority interrupt lines to signal the CPU for service.

The Main User-Level Memory uses MOS semiconductor technology, and has a write and read access time of 300 nanoseconds. The memory module contains 16K bytes of storage, and is addressed at the byte level. A two-byte word structure is superimposed, with word addresses being even. Word addresses therefore correspond to the byte address of the more significant (left) byte of the word. Data transfer is via 16-bit words over the MONOBUS.

With the MONOBUS addressing capability of  $18\ \mathrm{bits}$ , there are  $256\mathrm{K}$  addresses available. Some of these are reserved for I/O devices, and for addressing the Control Memory for the transfer of microcode. The rest are available for addressing main memory.

#### 2.2 THE MICRO-CONTROL SECTION

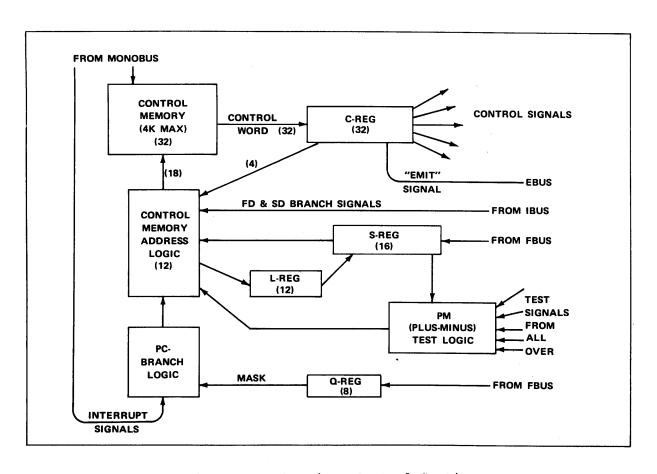

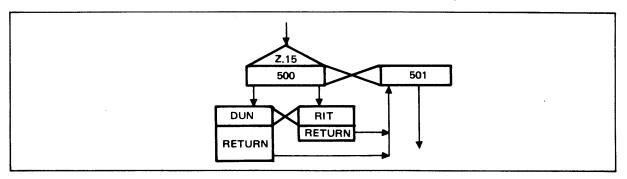

The structure of the Micro-Control section is shown in Figure A. The eight parts of the Micro-Control section have significant roles in microprogramming.

To the programmer, the 32-bit Control (C) Register is probably the most important item in the 3200. The C-Register receives and executes a single 32-bit microcommand from the Control Memory. Control signals diverge from the C-Register and effect gates throughout the CPU and on the MONOBUS, thus controlling all data transfers and transformations. The programmer must know the effect of each C-Register bit and how statements in the CAP32 language effect those bits. 1

The Control Memory (32-bits/word, 4K words max) stores the microroutines which define the behavior of the user-level machine. The Control Memory may be implemented either in Read-Only Memory or in Writable Control Memory (or a blend of both).

Control Memory Addressing Logic provides decoding for the 8 addressing modes of the Control Memory. Since the Control Word is short (32 bits) and is accessed from the Control Memory with each CPU clock, optimum use must be made of Control Memory addressing bits. The CAP32 Microassembler assists in this regard, as most Control Memory addressing is handled automatically by CAP32. The programmer must know the addressing modes sufficiently to understand CAP32's limitation problems, and modify his microroutine structure so that CAP 32 can cope with his demands.<sup>2</sup>

The 12-bit Last Access (L) Register holds the Control Memory address of the microcommand being executed. In several Control Memory addressing modes, the L-Register contents form part of the address of the next control word accessed.  $^3$

The 16-bit Save (S) Register is a multipurpose register which receives and saves the contents of the L-Register, and effects a subroutine return. The S-Register can receive data from the CPU on the FBUS. These data are used for Control Memory addressing.

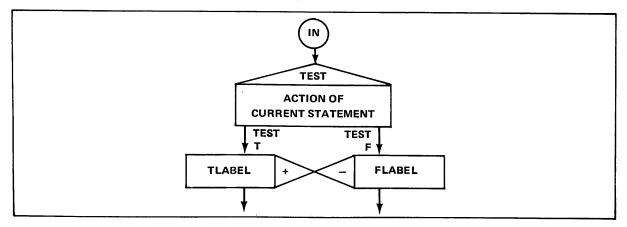

The Plus-Minus Branching Test Logic monitors selected bits throughout the system, and (under microprogram control) modifies the least significant bit of the Control Memory address under designated test conditions.<sup>5</sup>

The Procedure Control Branch Logic responds to machine conditions and external interrupt signals. Normally, the handling of machine faults and interrupts occurs automatically through the efforts of the PC Branch hardware at the time of each first digit branch. However, microroutines must be provided to define desired responses to various conditions arising.

The 8-bit Query (Q) Register contains a mask word controlling the set of interrupts enabling the PC Branching Logic. The Q-Register is set from the FBUS.  $^6$

## References:

<sup>1</sup>Topic 3.2

<sup>2</sup>Topic 6.1

<sup>3</sup>Topic 6.1

<sup>4</sup>Topics 7.4, 7.5, and 8.2

<sup>5</sup>Topics 7.1, 7.2, and 7.3

<sup>6</sup>Topic 8.4

Figure A. The Micro-Control Section

2

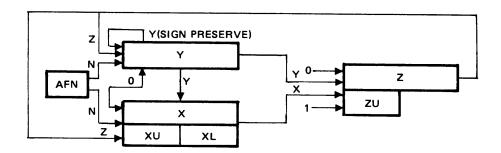

## 2.3 THE USER-LEVEL INSTRUCTION FETCH SECTION

The User-Level Instruction Fetch section of the Microdata 3200 is the mechanism which implements the user-program at the microlevel.

The microroutine is a sequence of microcommands which carry out a single user-level machine instruction. The User-Level Instruction Fetch section retrieves and interprets user-instructions one at a time, transferring microlevel control to the microroutine which will execute the microcommand sequence for instruction fetched.

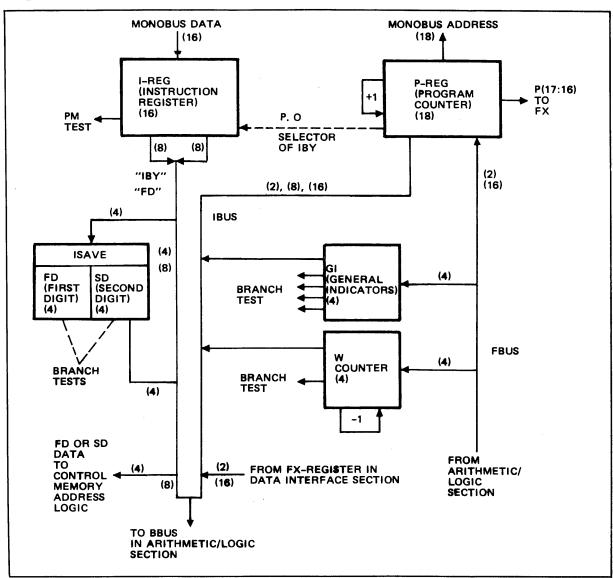

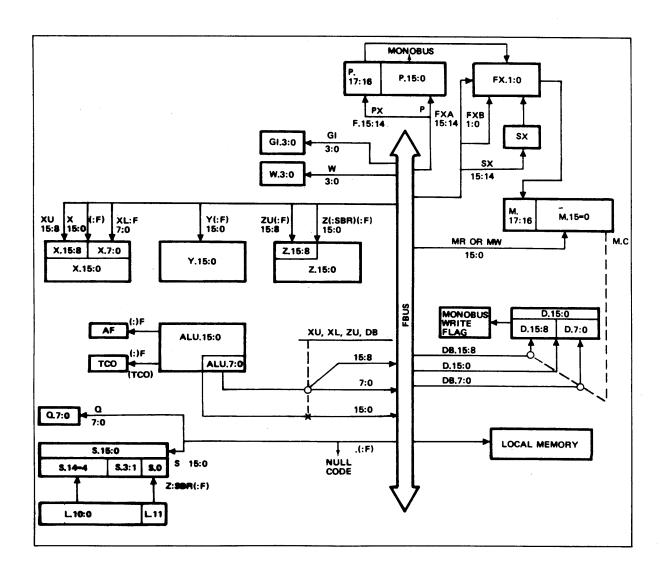

Figure A illustrates the User-Level Instruction Fetch section; this section contains two main registers:

- Instruction (I) Register

- Program (P) Register

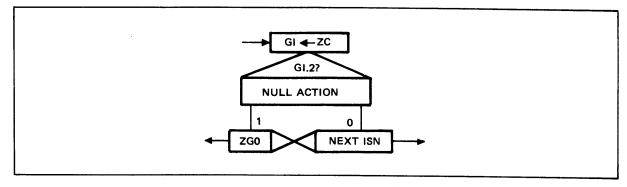

Associated with the I-Register is an I-Save section including the First Digit (FD) and Second Digit (SD). This portion of the 3200 also includes two miscellaneous items: the General Indicators (GI) and the W-Counter.

The 18-bit P-Register is 1 of 2 CPU registers capable of directly addressing the MONOBUS. The other is the M-Register, which is used to fetch data. (The P-Register has the higher priority.) The P-Register fetches instruction words and any other words in the program stream from the Main User-Level Memory into the I-Register. When the P-Register is incremented to an even value corresponding to a word address in Main Memory, the instruction fetch cycle is automatically initiated and the P-Register addresses the MONOBUS. About 300 nanoseconds later (barring MONOBUS congestion) the fetched instruction or program stream word appears in the I-Register.

The 16-bit I-Register word is subsequently handled byte-by-byte in the CPU, with the Least Significant Bit (LSB) of P-Register determining which I-Byte is to be used. An I-Byte may be sent to the Arithmetic/Logic section via the IBUS and BBUS. Alternatively, the First Digit (upper 4 bits of the current I-Byte) may be used to control a 16- or 32-way branch in Control Memory. The P-Register is incremented automatically by a First Digit Branch (FDB). The programmer can optionally increment the P-Register when an I-Byte is sent to the Arithmetic/Logic section. 1

The I-Save Register retains the current I-Byte when the FDB is used, freeing the I-Register to receive the next I-Word prior to the time needed.

SD, the second digit of I-Save, is available for a second 16- or 32-way branch, or for further general decoding in the Arithmetic/Logic section. Selected combinations of bits from both digits of I-Save may be the basis for simple 2-way branches as well.  $^2$

The General Indicators (GI) can be set to any values by a block transfer from the FBUS, then read back into the Arithmetic/Logic section via the IBUS. The GI's can also be used as independent bits to control 2-way branching.<sup>3</sup>

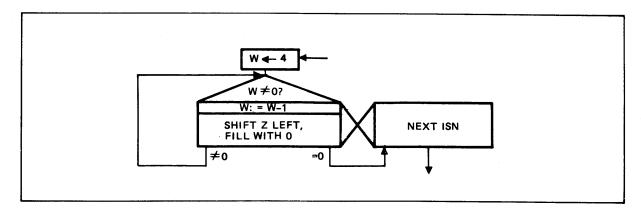

The W-Counter is a 4-bit down-counter that can be initialized from the FBUS, then read back into the Arithmetic/Logic section, or tested against zero and decremented.  $^4$

<sup>&</sup>lt;sup>4</sup>Topic 7.2

Figure A. The User-Level Instruction Fetch Section

<sup>&</sup>lt;sup>1</sup>Topics 8.3 and 8.4

<sup>&</sup>lt;sup>2</sup>Topic 8.5

<sup>&</sup>lt;sup>3</sup>Topic 7.2

#### 2 HARDWARE ORGANIZATION

#### 2.4 THE DATA INTERFACE SECTION

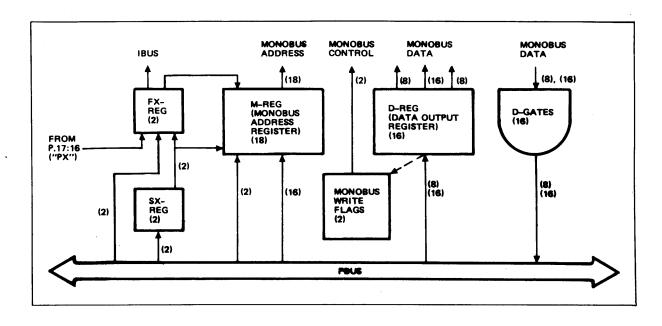

The Data Interface section is the second path of the communication between the MONOBUS and the CPU; this communication path is of lower priority than the User-Level Instruction Fetch interface. Whereas the Instruction Fetch section is used only to direct words from the program stream into the CPU, the Data Interface is bidirectional and is used for moving to and from the CPU.

The Data Interface section is illustrated in Figure A. This logic section consists of 2 main registers (the M-Register and the D-Register), a set of input D-Gates, 2 auxiliary registers, and 2 1-bit MONOBUS Write Flags. The CPU side of the Data Interface is almost entirely the FBUS (the CPU's 16-bit central data bus). There is a connection from the upper 2 bits of the P-Register (P.17:16) into the FX-Register to aid in 18-bit addressing within a 16-bit system. P.17:16 is also referred to as PX.

When loaded with an 18-bit address, the M-Register initiates a request for MONOBUS control. The address may point to a word or byte in the Main User-Level Memory, to a word in the Control Memory, or to a peripheral controller. When the MONOBUS responds, a read or write action occurs that depends on the loading of the D-Register with a word or byte to be transmitted. If the full D-Register (or either byte of the D-Register) is loaded before the conclusion of the current MONOBUS access, one or both of the MONOBUS Write Flags are turned on. The contents of the D-Register are then read into the CPU from the MONOBUS. Without Write Flags on, data are read into the CPU from the MONOBUS through the D-Gates, onto the FBUS.

Though the D-Register, D-Gates, and FBUS are all 16-bits wide, adequate provision is made for handling 8-bit data. Provision is also made to control the release of MONOBUS, so that a fast Read/Write cycle can be executed without losing MONOBUS Control.

Auxiliary registers FX and SX assist in extending the normal 16-bit data orientation of the system to permit 18-bit addressing of the MONOBUS. Connections from the FBUS, PX, SX, and Local Memory addressing logic provide data and control for establishing the upper 2-bits of the MONOBUS address. This is accomplished by explicit microinstructions, or as a natural byproduct of other activity. 1

Reference:

<sup>1</sup>Topic 4.5

Figure A. The Data Interface Section

#### 2 HARDWARE ORGANIZATION

### 2.5 THE ARITHMETIC/LOGIC SECTION

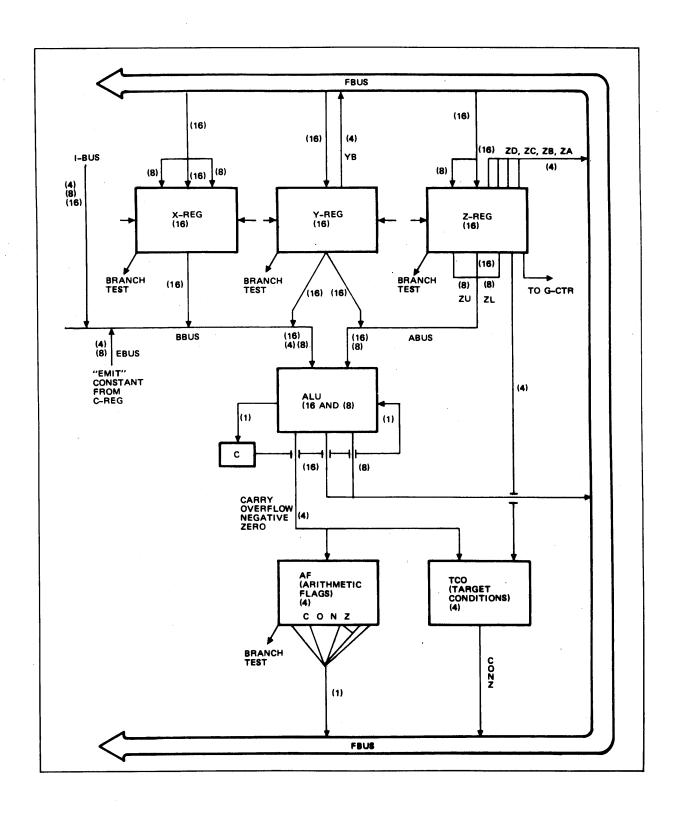

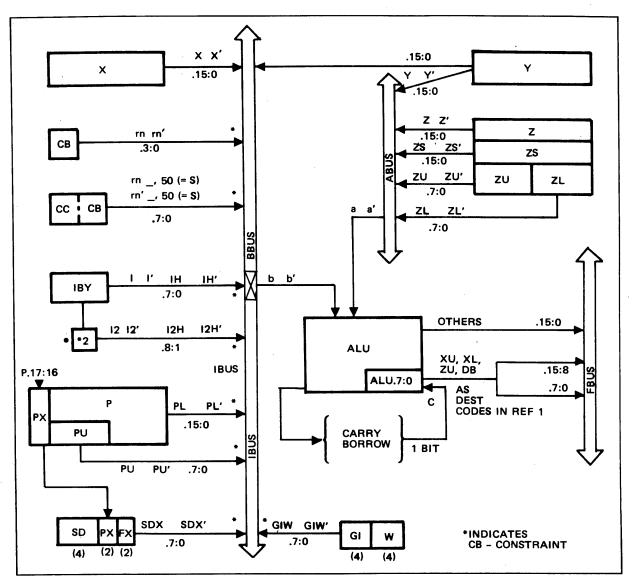

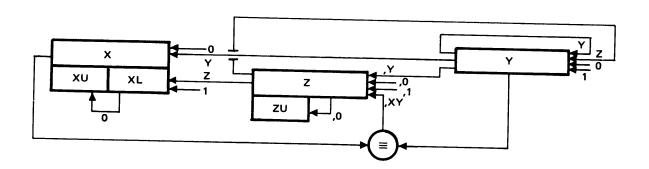

The Arithmetic/Logic section of the 3200 CPU consists of three 16-bit Working Registers (X, Y, and Z), the ALU proper, Arithmetic Flags, and the Target Flags (TFG) Register. All of these entities are interconnected through the ABUS, the BBUS, and the FBUS.

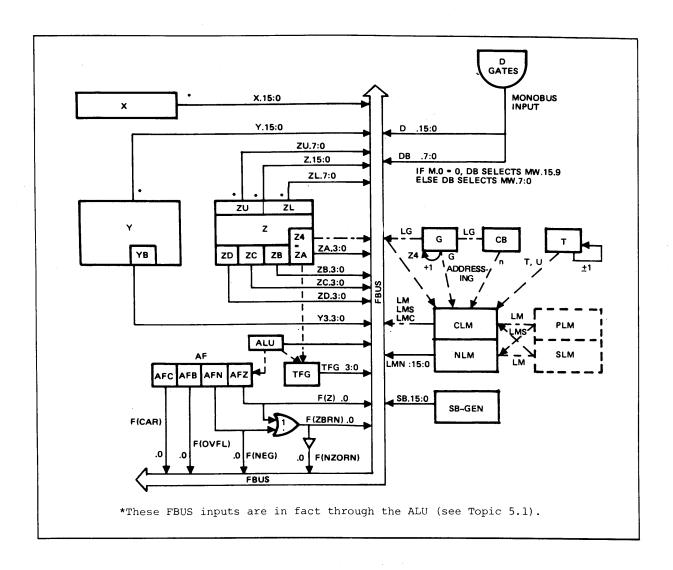

The Arithmetic/Logic section is illustrated in Figure A. The BBUS receives outside inputs via the IBUS (from the User-Level Instruction Fetch section) and from the C-Register (in the Micro-Control section) via the EBUS. Selected bits from the ALU are transmitted to the Branching Test Logic in the Micro-Control section, and to the Local Memory Addressing Logic.

Registers X, Y, and Z provide a variety of single and combinatorial shift capabilities, with bit fill selectable by the programmer. Shifting is carried out as a separate working register operation, not as part of an ALU operation. 1

The ALU provides addition and subtraction (with and without use of an input carry or borrow), data transfer, complementing, AND, OR, and EXCLUSIVE-OR operations. Data widths are 8 or 16-bits and are determined by the output destination. ALU output is always via the FBUS to the selected destination(s).  $^2$

Input to the ALU is via the ABUS and/or BBUS. The ABUS is fed by the Y-or Z-Register. The BBUS is fed by the X- or Y-Register, and the EBUS or IBUS. Restrictions which apply to the combination of sources, data widths, etc., are discussed in the referenced topics.<sup>3</sup>

ALU number representation and arithmetic are in 2's complement form. The Arithmetic Flags, when specifically enabled, are set after each ALU operation and reflect the Carry/Borrow, Overflow, Negative, and Zero conditions of the ALU output. The left-to-right order of the target flags (C, O, N, Z) are worth remembering.

Target Flags (TFG) is a 4-bit register than can be set to the same four condition values as the Arithmetic Flags. Alternately, TFG can be set from the lowest 4 bits of the Z-Register (Z.3:0 = Z4 = ZA).

<sup>&</sup>lt;sup>1</sup>Topic 5.6

<sup>&</sup>lt;sup>2</sup>Topics 4.1 and 4.2

<sup>&</sup>lt;sup>3</sup>Topics 5.1, 5.2, and 5.3

<sup>&</sup>lt;sup>4</sup>Topic 5.5

Figure A. The Arithmetic/Logic Section

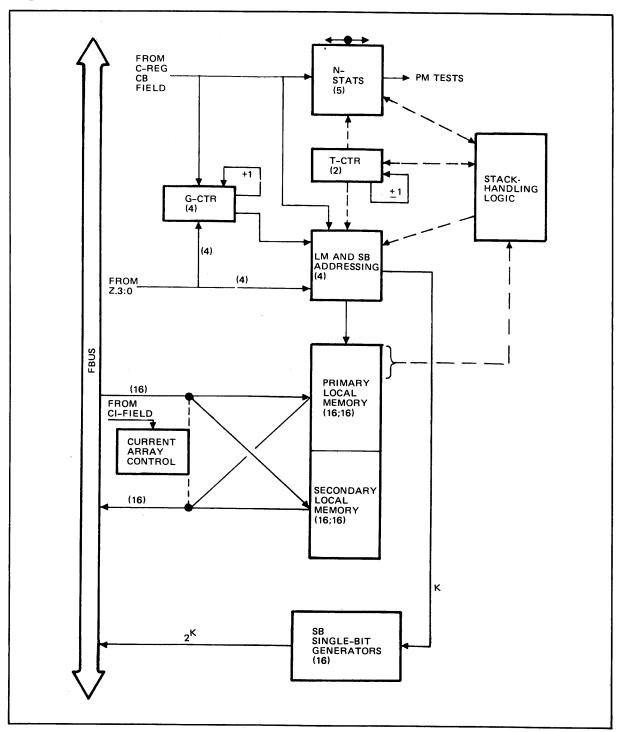

#### 2.6 THE LOCAL MEMORY AND AUXILIARIES SECTION

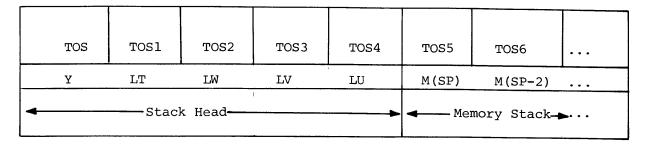

This section of the 3200 CPU contains the Local (Fast) Memory and several auxiliary sub-sections. The Local Memory consists of 32 high-speed, 16-bit registers.

The structure of the Local Memory and Auxiliaries section is shown in Figure A. This logic section contains the following sub-sections:

- Local Memory (LM)

- Single-Bit Generator (SB)

- LM and SB Addressing Logic

- G-Counter

- T-Counter

- N-Stats

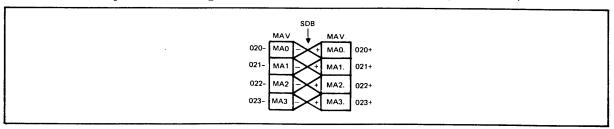

Communication with the Local Memory (LM) and Auxiliaries is via the FBUS, with the C- and Z-Register having some direct inputs. The LM and SB Addressing Logic provides control signals effecting the upper 2 bits of M-Register (for MONOBUS addressing).

The Single-Bit Generator (SB) provides a 16-bit signal on the FBUS equal to any one of the 16 possible powers of 2 which are expressable in 16 bits (the selected power of 2 corresponding to the specified LM and SB address in the range 0:15). Each signal consists of one "1", bit, hence the name.

The LM consists of 32 high-speed, 16-bit registers arranged in 2 banks of 16 registers each, for addressing purposes. These are designated as "Primary" and "Secondary" Local Memory. Ten of the 16 Primary LM Registers have special hardwired functions as well as serving as general-purpose high-speed local storages. LMO:LM3 serve as part of the stack head. LM10:LM15, when addressed, effect the 2 most significant bits of the MONOBUS address (M.17:16). See referenced topics for further details. 1

The LM and SB addressing Logic provides capabilities for addressing any one of the SB Generators, or any one of the 32 Local Memory registers as a source or destination (but not both in the same microcycle). It also provides for a variety of side-effects that can be specified to occur in a Local Memory access microcycle.

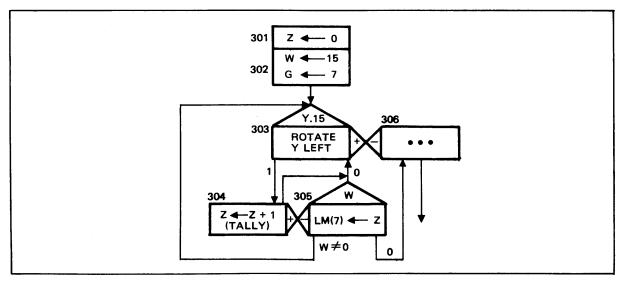

The G-Counter is a 4-bit cyclic up-counter that can be initialized from the lowest 4 bits of the Z-Register or Emit Field. The G-Counter is then used for LM and SB addressing and optionally incremented as a side effect.<sup>2</sup>

The T-Counter is a 2-bit cyclic bidirectional counter used by the 32/S emulation in stack head manipulation. The N-Stats is a 5-bit shift register used to represent the current stack head structure. Detailed stack head processing is discussed in the referenced topics. For now, it is enough to recognize that stack head manipulation provided in the 3200 localizes the Top-of-Stack in the Y-Register, with 0 to 4 additional words in LMO:LM3 forming the rest of the stack head. The remainder of the stack is in the Main Memory. The Stack Handling Logic provides the integration of N-Stats, T-Counter, and LM and SB Addressing, that makes efficient stack handling possible.

#### References:

<sup>1</sup>Topics 4.2 and 4.3

<sup>2</sup>Topic 4.3

<sup>&</sup>lt;sup>3</sup>Topics 9.1 through 9.5

Figure A. The Local Memory and Auxiliaries Section

#### 2 HARDWARE ORGANIZATION

#### 2.7 THE FRONT PANEL SECTION

The Front Panel section of the CPU is unique in that a large fraction of the available front-panel display and control capabilities is subject to microprogram control. It can be tailored to the particular firmware set (and user-level instruction set) that is being implemented.

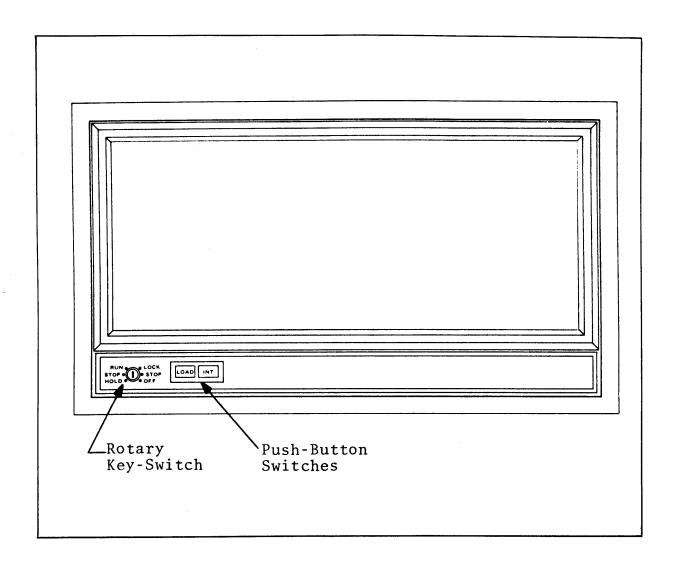

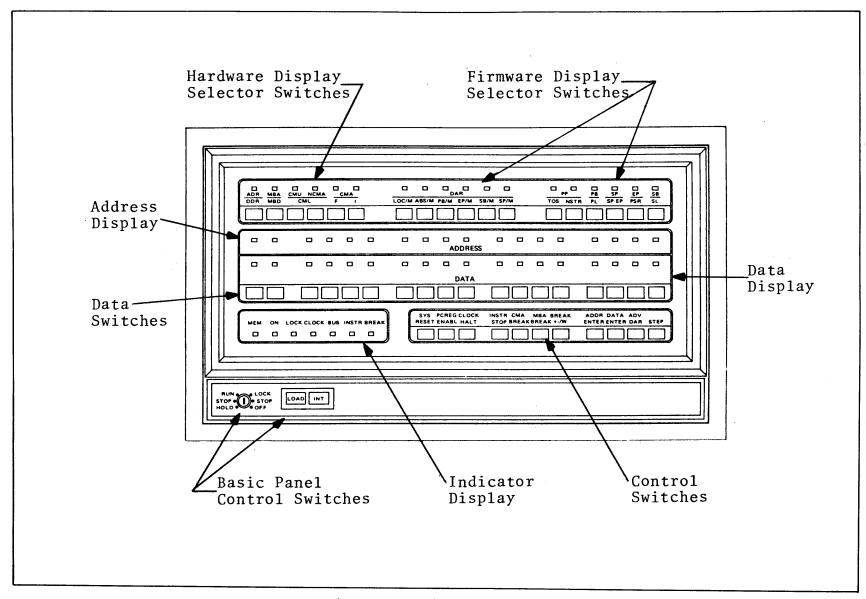

The front panel normally supplied for users interested in extensive micro-programming development is adapted for operation with the 32/S firmware set. Every panel contains switches for the following basic functions: OFF, STOP, LOCK, RUN, HOLD, LOAD, and INT. The full maintenance panels used in micro-programming development also contain 7 Status Indicators, 11 Control Switches, 18 Data Bit Entry Switches, 18 Display Selector Switches, an 18-Light Address Display, and a 16-Light Data Display.

Due to flexible firmware control of the Front Panel logic, the displays and controls are not limited in their effect to the CPU, but may also interact with the remainder of the system via the MONOBUS.

The complete maintenance panel is directly addressable on the MONOBUS, to permit the necessary microprogram to read the Data Switches and Panel Status Word, and to output to the Display Registers.

The basic front panel is illustrated in Figure A. Figure B shows the complete maintenance front panel of the 32/S emulation.

Details regarding the Front Panel are covered in a separate section of this manual. 1

Topics 11.1 through 11.6

Figure A. Basic Panel

| ADR MBA CMU NCMA CMA DAR LOC/M ABS/M PB/M EP/M SB/M SP/M TOS NSTR PL SP EP SS L                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS                                                                                                                                        |

| DATA                                                                                                                                           |

|                                                                                                                                                |

| MEM ON LOCK CLOCK BUS INSTR BREAK  SYS PCREC CLOCK INSTR CMA MBA BREAK ADDR DATA ADV RESET ENABL HALT STOP BREAKBREAK +-W ENTER ENTER DAR STEP |

| AUN LOCK LOAD INT HOLD OFF                                                                                                                     |

Figure B. Maintenance Panel

### 3.1 MICROINSTRUCTION FORMAT

This topic describes the general format of the CAP32 microinstruction.

CAP32 source microprograms contain one statement per line: an executable microinstruction which will assemble into a line of object microcode, or a microassembler pseudoinstruction directing CAP32 to perform an evolution at microassembly time. Each CAP32 instruction contains up to four specific fields, as shown in Figure A.

The Label Field (LAF), which starts in column 1, is conventional in form. It may be empty, contain an asterisk denoting a comment line, or contain a symbol. (Many of the CAP32 pseudoinstructions require a symbol in LAF.) If the line contains an executable instruction, a symbol in LAF will permit the line to assume the destination of a normal jump or branch instruction. Jumps or branches to unlabeled lines in CAP32 are restricted to +n from the microprogram counter (denoted by \*+n or \*-n). Jumps or branches to a line relative to a labeled line (of the form symbol +n) are not supported.

A symbol in CAP32 consists of 1 to 6 alphanumerics, beginning with a letter. Letters include the period symbol (.), and the 26 letters (A through Z). The alphanumerics consist of the letters and the decimal digits (0 through 9). Hence, a symbol in CAP32 may have a period inserted anywhere, and may include digits after the first character. For example: I5D, FD3, .FDX, and .001 are legitimate CAP32 symbols. 4FLUSH, SEGMENT, and \$SAFE are illegal.

In a pseudoinstruction, the Operation Field (OPF) consists of a keyword identifying the particular pseudo operation called for. Otherwise, the instruction is executable and the OPF consists of 1 or 2 subfields (OPF1 and OPF2) separated by a comma (with no space). OPF2 may in turn contain 2 subfields separated by a comma.

OPF1 specifies in part the principal operation to take place during the 135-nanosecond microcycle in which the current microinstruction is executed. Other fields of the statement must also be interpreted to complete the specification of the action. The principal operation specified by OPF1 may be:

- A shift in one or more working registers (X, Y, or Z).

- An arithmetic or logic expression evaluation.

- A data transfer from the D-Gates (hence the MONOBUS), the Local Memory, or one of the other sources feeding the FBUS.

When occurring, OPF2 specifies a concurrent secondary action involving the stack handling facilities or the G-Counter.  $^2$

The Result Field (REF) consists of 1 to 3 subfields (REF1, REF2, and REF3). REF1 completes the specification of the principal operation partially specified by OPF1. The allowed values of REF1 are heavily dependent on OPF1. For shift operations, REF1 specifies the working register(s) to be

shifted. For data transfers and arithmetic or logic operations, REF1 specifies the destinations receiving the FBUS signal from the Arithmetic/Logic section, or the named signal source. Allowable destinations, operations, and sources are discussed in detail in the referenced topics.<sup>3</sup>

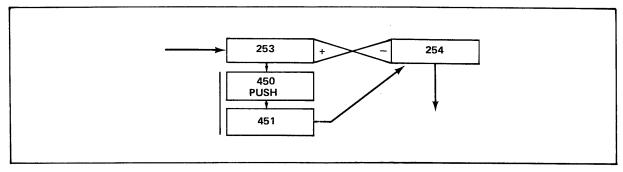

When occurring, REF2 specifies the label of the next microinstruction to be executed. When making a conditional branch, REF2 also specifies the condition to be tested and the alternative destinations. If REF2 does not appear, CAP32 selects the next sequential microinstruction.

When occurring, REF3 specifies desired concurrent side effects. REF3 also permits direct encoding of the C-Register bits, free from CAP32 micro-assembler constraint, but without its aid and protection.

| Field                 | Definition                                              |

|-----------------------|---------------------------------------------------------|

| Label Field (LAF)     | From col 1 to the first blank; empty if col 1 is blank. |

| Operation Field (OPF) | From next non-blank to first subsequent blank           |

| Result Field (REF)    | From next non-blank to first subsequent blank.          |

| Comment Field (COF)   | From next non-blank, if any, to end of line.            |

Figure A. CAP32 Instruction Fields

<sup>&</sup>lt;sup>1</sup>Topics 7.1 through 7.6

<sup>&</sup>lt;sup>2</sup>Topic 4.3 and Topics 9.1 through 9.5

<sup>&</sup>lt;sup>3</sup>Topics 4.1 through 4.6 <sup>4</sup>Topics 4.3, 5.5, and 8.4

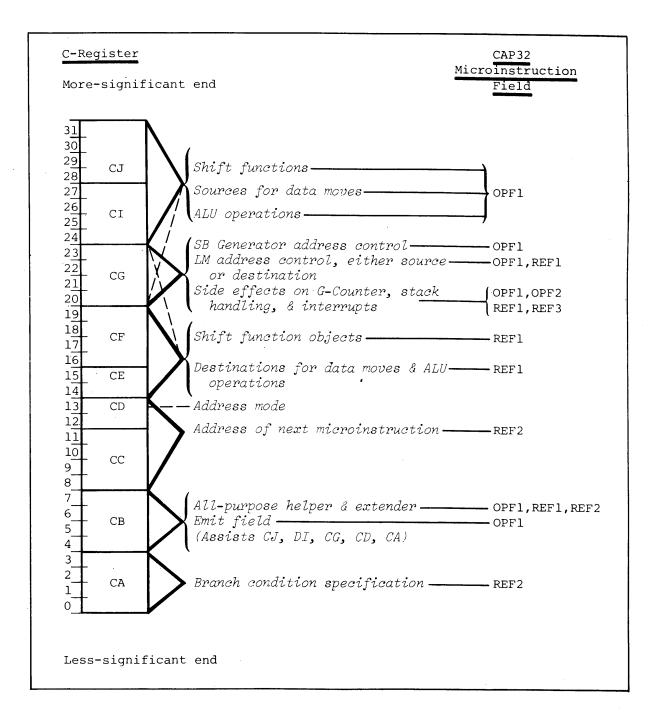

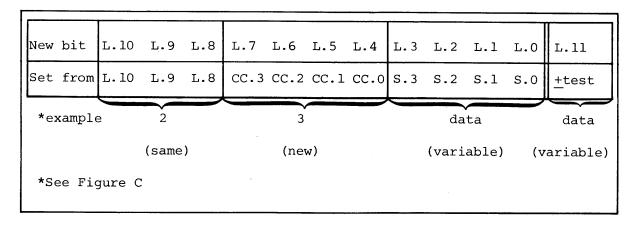

#### 3.2 C-REGISTER FIELDS

This topic describes the relationship of the CAP32 microinstruction fields to the related Control (C) Register fields.

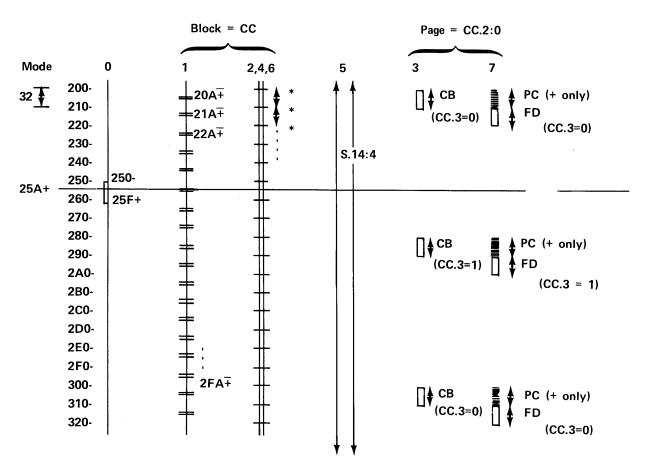

The C-Register fields are shown in Figure A by bit position, field name, field function, and the CAP32 microinstruction field effecting them. The C-Register is 32 bits wide, numbered from 31 at the most significant end to 0 at the least significant end. The C-Register contains bits C.31:0, with nine fields identified (CJ, CI, CG, CF, CE, CD, CC, CB, and CA). All of the fields are four bits wide (on Hex digit boundaries), except CE and CD which share a single HEX digit (CE is one bit wide and CD is three bits wide). Since CD is based on a natural Hex digit boundary at its right end, its range is valued at 0:F. CE is to the right of Hex digit boundary, so when interpreting a Hex display of the microcode, CE will add either 0 or 8 to the Hex digit containing CE and CD. Hence the CE field has a value of either 0 or 8.

When a given field has a specified value, such as field "Cx" having value "v", the condition "Cxv" is said to exist. For example, condition CIA occurs when field CI has Hex value A.

Usage of the CB field, thus probably blocking it for other usage during the current microcommand cycle, is referred to as "CB-Constraint".

Knowledge of the C fields is required to understand constraints that the machine architecture places on source language statements, and the resulting performance. Each CAP32 instruction is assembled into one Control Word. A "loading" of the C-Register occurs at the time the Control Word is executed as a microinstruction. The C-Register appears on the microprogram listing as the object microcode in Hexadecimal notation. 1

Normally, the CAP32 Microassembler determines the value of each C-Register field as the programmer desires (expressed in CAP32), handling many of the details automatically. For example, the choice of Control Memory addressing mode (field CD) is established by CAP32 in most cases, and the address is determined by CAP32 through use of a memory allocation routine. The routine seeks to completely fill up the available memory, while meeting the restrictions inherent in the 3200 branching structure.<sup>2</sup>

If the programmer desires, he may force CAP32 to establish each micro-instruction precisely as desired, using one or more expressions of the form "Cfield=value" in subfield REF3 of the CAP32 instruction. For example, "CB=14,CA=2" would force the CB field to value Hex E, and the CA field to value 2. These forced specifications supersede those values the remainder of the CAP32 statement would have produced. This procedure has inherent hazards.

<sup>&</sup>lt;sup>1</sup>Topic 6.2

<sup>&</sup>lt;sup>2</sup>Topics 7.1 through 7.6

Figure A. Field Structure of the C-Register with Relation to Fields and Subfields of the CAP32 Microinstruction

#### 4.1 DIRECT FBUS DESTINATIONS

FBUS destinations are specified in the REF1 subfield of the CAP32 microinstruction; they are separated into two categories: direct FBUS destinations and Local Memory (LM) FBUS destinations.

Direct FBUS destinations are specified by using one code from Reference Table A-2 (e.g., X, or Y:Z, or ZU:F). Local Memory (LM) FBUS destinations are specified by using one code from Reference Table A-3 (e.g., LM(G,IG)). Two destination codes may appear in the same microinstruction REF1 subfield if one is from each category (e.g., X:LM(8), or DB:LM(T,DT), or LM(G):Y:Z).

The remainder of this topic is devoted to a discussion of the direct FBUS destination codes. The user should refer to Reference Table A-2 (in Appendix A) and to Figure A (in this topic).

The null code (.) is used in REF1 if no destination is required for the FBUS signal (i.e., the microcommand is a conditional branch, without data movement).

REF1 code F is an input selector for the Target Register, and an enabling specification for the Arithmetic Flags (AF). Here the AF's are to be set to reflect the Carry, Overflow, Negative, and Zero status of the ALU output. (As such, F is not a true FBUS destination code but is listed with them.)

REF1 code SBR specifies selected bits of the S-Register to store the L-Register contents. The L-Register holds the Control Memory address of the current microcommand. SBR is distinguished from REF1 code S which directs setting of the full S-Register from the FBUS.

REFl codes X, Y, and Z specify the most common FBUS destinations (Working Registers X, Y, and Z), which in turn may drive the ALU, provide for shifts, or be tested.  $^3$

REF1 codes XU, XL, and ZU specify transfer of half the FBUS to half of a Working Register. Similarly, code DB specifies output of a single byte (half the FBUS) to the MONOBUS Data Register D. Each of these codes directs copying of the ALU output low-order byte (ALU.7:0) into the ALU output high-order byte (ALU.15:8). Thus if the FBUS source is the ALU, a shift of the ALU output lower-byte into both halves of the FBUS results. Note that if the ALU is not the FBUS source, no shift occurs on the FBUS.

REF1 codes D, DB, MR, MW, and P impact the MONOBUS, providing memory and I/O device access. REF1 codes P and PX control the user-level Program Counter. The user is cautioned that code P loads P.15:0 from the FBUS and also initiates MONOBUS action; thus, code PX must be used first if a major jump in memory or I/O address space is planned. This direct control of the user-level Program Counter is only for jumps and unusual situations. Normal advance of the counter to the next sequential instruction is provided automatically.

REFl codes FXA, and FXB, and SX enable the selection of the memory bank for the next data access to the main memory or I/O devices. Final selection of memory location or I/O address is through REFl codes MR or MW. $^6$  REFl codes

W and GI provide for setting of the W Counter and General Indicator (GI) bits. Finally, code Q provides for setting of the Interrupt Masks.

#### References:

<sup>1</sup>Topics 5.4 and 5.5

<sup>2</sup>Topic 2.2

4Topics 4.5 and 4.6

<sup>5</sup>Topic 8.3

<sup>6</sup>Topic 4.5

<sup>7</sup>Topic 8.4

Figure A. Effects of Direct FBUS Destination Codes

$<sup>^{3}</sup>$ Topics 4.3, 5.1, 5.3, and 5.6

#### 4.2 LOCAL MEMORY (LM) FBUS DESTINATIONS

The second category of FBUS destination is Local Memory (LM). LM destinations are specified by using one code from Reference Table A-3.

LM consists of 32 high-speed registers in two arrays, denoted Primary and Secondary. Array selection (Primary and Secondary) is accomplished when LM is used as an FBUS signal source. LM destination codes cannot modify the current array selection mode established by a previous LM source code. Thus an LM destination is always in the "Current" LM array, denoted CLM.

The syntax of an LM destination code used in subfield REFl is either of the following:

LM(index)

LM(index, side-effect)

where "index" has a value in the range 0:15, and where "side-effect" specifies a unique concurrent side-effect, such as setting or incrementing the G-Counter.

The G-Counter is a 4-bit register specifically connnected an an LM index. When the G-Counter is used as an index, incrementation of the register can be a specified side-effect (i.e., using code IF), thus providing a convenient means of "stepping" through either array of 16 LM registers. Incrementation occurs after use of the G-Counter as an index. The G-Counter is initially set as the side-effect load G (LF) when one of the other indexing methods is used.

Index code Z4 allows direct use of data to index into the LM. The data item is first loaded into Z.3:0, then LM destination code LM(Z4) or LM(Z4,LG) is used, where LG loads the G-Counter with the current value Z4.

LM can be indexed directly through a microcode literal value, denoted by rn in Table A-3. In the CAP32 program form a symbol previously defined by a REGNAM pseudoinstruction may be used for rn. In the final machine Control Word, the value of rn is contained in the CB field. Hence, where possible, G or Z4 LM indexing should be used rather than rn indexing, to minimize the use of the all-purpose helper field CB. This also reduces the probability of conflict between the indexing and another control function of the same microcommand. Often, LM(rn,LG) will be used when an LM register is written (a few microcommands later), thus eliminating the CB-Constraint.

The fourth method of LM indexing is via the T-Counter (codes LM(U,IT) or (LM(T,DT)). This method is totally involved with the specific facilities for stack handling.<sup>3</sup>

An important restriction to keep in mind is that LM may be used as a source or as a destination during one microcycle, but not as both. Word transfers

from one LM register to another (with or without modification) requires cycling the word through Working Register X, Y, or Z, and the ALU, which takes two microcommands.

Finally, anticipating subsequent topic coverage, the user should note that certain LM registers have special properties. Registers 0:3 of one array are used in the stack head, addressable by the T-Counter. Registers 10:11 have special influence on MONOBUS addressing, making them particularly appropriate as Program Counters. Registers 12:15 have special influence on MONOBUS addressing, making them particularly appropriate as Data Stack Environment Pointers.

<sup>&</sup>lt;sup>1</sup>Topic 2.6

<sup>&</sup>lt;sup>2</sup>Topic 4.3

<sup>&</sup>lt;sup>3</sup>Topics 9.1 through 9.5

<sup>&</sup>lt;sup>4</sup>Topic 9.2

# 4.3 LOCAL MEMORY (LM) AND SINGLE-BIT GENERATOR ARRAYS AS FBUS SOURCES

FBUS sources are specified in the OPFl subfield of the CAP32 microinstruction. The local array FBUS sources consist of the Local Memory (LM) and the Single-Bit Generator arrays.

A Single-Bit Generator produces a full word of 16 bits; this word contains a single 1-bit, with the rest 0's. If the code SB(index) or SB(index,side-effect) is used in the OPF1 subfield of a CAP32 statement, the value 2\*\*index is placed on the FBUS. That is, bit "FBUS.index" is set to 1 and all other FBUS bits are set to 0. The allowable syntax and sematics for "index" are shown in part 2 of Reference Table A-4. For example, if OPF1=SB(5), then at execution time FBUS=002016=1000002. Similarly, if G=15 and OPF1=SB(G), then at execution time FBUS=800016.

Specification of an LM register as a source is complicated by the existence of the two LM arrays (Primary and Secondary) each containing 16 registers. Two of the OPF1 codes, LM and LMS, establish a definite (permanent) LM mode. The LM code establishes the Primary LM array as the Current Local Memory (CLM). LMS establishes the Secondary array as the CLM. The other two OPF1 codes, LMC and LMN, leave the established CLM as is: LMC prescribes use of the CLM, while LMN prescribes use of the Noncurrent Local Memory (NLM).

The codes used to index within the selected LM array are identical to those described for LM FBUS destinations<sup>1</sup>, except that they are used in subfield OPFl instead of REFl. Also, codes U and T may be used with or without side-effects, as desired. Codes U and T are discussed in conjunction with Stack Handling.<sup>2</sup> Note again that LM may be either a source or destination in any microcommand, but not both, since C-Field CG is used for gating both separately.

Working registers X, Y, and Z may be used as FBUS sources, by using codes X, Y, or Z (respectively) in subfield OPF1. The signals from X, Y, or Z come through the ALU, as discussed in the referenced topics.

Codes LG and IG, used for independent of local array source or destination codes, also effect the G-Counter. (Reference Table A-5 provides details.) The G-Counter can be set by using code Z4,LG or code rn,LG as subfield OPF2 of a CAP32 statement. In this case Z4=Z.3:0 and rn denotes a register name defined by REGNAM, or a decimal number in the range 0:15. The G-Counter can be incremented by using code IG as subfield REF3 of a CAP32 statement, inserting a null REF2 subfield if necessary.

Sample usage of the source codes described above are illustrated in Figure A.

<sup>&</sup>lt;sup>1</sup>Topic 4.2

<sup>&</sup>lt;sup>2</sup>Topics 9.1 through 9.5

<sup>&</sup>lt;sup>3</sup>Topics 5.1 through 5.6

| CAP32 Microinstruction |     | Action                                                                                                                                                                                                                       |  |

|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SB(0)                  | Y   | Loads Register Y with value 1.                                                                                                                                                                                               |  |

| SB(1)                  | Z   | Loads Register Z with value 2.                                                                                                                                                                                               |  |

| LMC(7,LG)              | Z   | Loads Register Z with the value now stored in Register 7 of the currently active LM array, and sets the G-Counter to 7.                                                                                                      |  |

| LMS (14)               | Y:Z | Selects the secondary LM array to be currently active, and loads registers Y and Z with the contents of secondary LM register 14.                                                                                            |  |

| LMN (G, IG)            | D   | With the primary LM array currently active (and keeping it that way), this instruction loads the MONOBUS D-Register with the contents of the secondary LM array indexed by the G-Counter. The G-Counter is then incremented. |  |

Figure A. Sample Usage of LM and Single-Bit Generator Arrays as FBUS Sources.

#### 4.4 OTHER DIRECT FBUS SOURCES

In addition to the local array FBUS sources<sup>1</sup>, seventeen other sources drive the FBUS directly, bypassing the ALU. These sources vary from 16 bits to 1 bit in active width, and provide 0's in unused bit positions. Each is specified by use of the proper code in subfield OPF1.

Reference Table A-6 summarizes these additional direct FBUS sources.

OPF1 codes D or DB cause the current MONOBUS Data Word (MDW), or possibly just one byte of that word, to be placed on the FBUS.  $^2$

OPF1 code TFG loads the 4 low-order bits of the FBUS from the 4-bit Target Flags Register (TFG). TFG is a register which reflects the conditions of same previous ALU operation. Each bit loaded into the F-BUS reflects a specific target flag: 3, carry; 2, overflow; 1, negative; 0, zero.

OPF1 code SWIT allows bits representing 4 hardware test switches in the 4 low-order bit positions of the FBUS. These internal cabinet switches are for programmed maintenance use and are not operator-available.

Four OPF1 codes (ZD, ZC, ZB, and ZA) load FBUS.3:0, the 4 low-order bits of the FBUS, with the 4 Hex digits stored in the Z-Register. ZD indicates the most significant Hex digit; ZA indicates the least. These source codes are convenient for many decoding operations. OPF1 code YB loads FBUS.3:0 with Hex digit B from Y-Register Y.7:4.

Finally, eight OPF1 codes of the form F(f) bring to the low-order bit of the FBUS (FBUS.0) selected 1-bit flags derived logically from the 4 micro-level hardware Arithmetic Flags (AF). Six of the eight codes provide all of the normal comparisons of the ALU result against zero (Zero, Non-Zero, Negative, Non-Negative, Positive, Non-Positive). The final two codes report Carry and Overflow conditions. A CB-Constraint results.

All direct sources listed in Table A-6 drive the FBUS directly (not through the ALU); hence, they do not respond to the Byte-type destination codes so as to copy their bit pattern from the lower byte to the upper byte of the FBUS. Thus, destination codes XU, ZU, or DB will not cause any transfer of these 4-bit or 1-bit source signals into the upper byte of X, Z, or D (respectively).

Source codes D or DB must not be used in the same microcommand as destination codes D or DB. If such use is attempted, the MONOBUS Controller may hang in permanent error.

The entire set of direct FBUS inputs is shown graphically in Figure A.

#### References:

<sup>1</sup>Topic 4.3 <sup>3</sup>Topic 5.5 <sup>5</sup>Topic 4.2 <sup>2</sup>Topic 4.5 <sup>4</sup>Topic 5.4

Figure A. Direct FBUS Inputs and Selected ALU FBUS Inputs

#### 4.5 MONOBUS DATA ACCESS

The three modes of MONOBUS data access are: Read, Read-Rewrite, and Write. All three involve data transfers between the MONOBUS and the FBUS, using the D-Register for data written to the MONOBUS from the FBUS, and using D-Gates to input (read) a MONOBUS Data Word to the FBUS.

MONOBUS access begins by establishing a MONOBUS address in the 18-bit Monobus Address Register (M). The upper 2-bit segment (M.17:16) should be planned first; these bits are set as a side-effect of loading the lower 16 bits of M from the FBUS. M.17:16 is set from the Local 2-bit FX Register unless the lower 16 bits of M come from the Local Memory (LM) Registers, specified by CB indexing in the range 10:15. If the CB type index specification of LM source indexing is 10 or 11, then M.17:16 is set from the upper 2 Program Counter bits (P.17:16), thus setting FX. In the CB type index is 12,13,14, or 15, then M.17:16 is set from the two-bit 5X Register, thus setting FX. With the setting of the upper 2 MONOBUS address bits planned, a microcommand is executed transferring the lower 16 bits from their source to M, via the FBUS. The microcommand has the basic syntax:

address-source MR

or

address-source MW

REF1 code MR is used for Read access; MW is used for either Write access or Read-Rewrite access. MR and MW do not actually establish data flow direction across the MONOBUS/FBUS interface. Rather, they specify conditions under which the MONOBUS will be released after use. Code MR specifies immediate release of the MONOBUS after any access. Code MW specifies the MONOBUS is to be held until after a Write access is completed. Sequence 'source MR, source D' does not work.

The actual data flow direction between FBUS and MONOBUS is set by the pair of MONOBUS Write Flags associated with the two bytes of the D-Register. The data flow direction is MONOBUS to FBUS (i.e., read) unless one or both Write Flags are set. This occurs when destination code D or DB is used in subfield REF1, shown in Reference Table A-2. The Write Flags are cleared at the end of every MONOBUS Write access. Hence, if D or DB is used in REF1, then a Write occurs; otherwise a Read access occurs and D or DB should be used in OPF1 to take the data from the D-Gates and place then on the FBUS.

Summaries of the three different access modes are depicted in Figures A, B, and C.

The user should note that microcommand "data-source D" can precede microcommand "address-source MW" if desired. However, "data-source DB" must follow "address-source MW". The system will suspend operation if D or DB is used in subfield OPF1 without prior use of MR or MW in REF1 since previous access.

1. Use following microcommand:

address-source MF

- Allow other microcommands to intervene here; up to 2-cause no further delay.

- 3. Use one of the following microcommands:

- D data-destination

- DB data-destination

- 4. MONOBUS is released as soon as data is received on the FBUS.

Figure A. Read Access Procedure

1 Use following microcommand:

address-source MW

- Allow other microcommands to intervene here; up to 2 cause no further delay.

- 3. Use one of the following microcommands:

- D data-destination

- DB data-destination

- 4. MONOBUS is not released after Read; provide data revision microcode here but do not waste any microcycles as the MONOBUS is tied up.

- 5. Use one of the following microcommands:

data-source

D

data-source

6. MONOBUS is released after Write.

Figure B. Read-Rewrite Access Procedure

1. Use following microcommand:

address-source MW

- Allow other microcommands to intervene here; up to 2 cause no further delay.

- 3. Use one of the following microcommands:

data-source

data-source DB

4. The MONOBUS is released as soon as the WRITE is complete.

Figure C. Write Access Procedure

## 4.6 MONOBUS WORD AND BYTE TRANSFERS

The lowest order bit of a MONOBUS address (M.0) denotes the byte address within the current MONOBUS word. The high-order byte is indicated by an M.O value of O; a value of l indicates the low-order byte.

The incoming signal on the MONOBUS from the I/O or Memory Controller to the D-Gates includes both bytes. The high-order byte is always from the even address (with address-bit.0=0); the low-order byte is always from the odd address (with address-bit.0=1). Therefore, a MONOBUS access is always full-word oriented, up to the D-Gates connected to the FBUS.

If the FUBS source code DB is used in subfield OPF1, then bit M.O is used to select one byte of the input word at the D-Gates for transmission to the FBUS. The other byte of the input word is lost insofar as that Read cycle is concerned. The MONOBUS is realeased after the selected byte is passed to the FBUS, and that word must be fetched again if the other byte is subsequently needed.

Behavior is slightly different on output. DB as a destination code in REF1 causes a data transfer from the FBUS into one byte of the D-Register as determined by M.O, and sets the corresponding Upper or Lower MONOBUS Write Flag.

#### CAUTION

Because M.O selects the byte, the value of M must be set before D is loaded, or the wrong byte may be selected.

Only the selected byte is transmitted from D to the MONOBUS; the Controller receiving the byte also receives a control signal indicating it is just a single byte.

Since M cannot be set without initiating a MONOBUS access cycle, it is not possible to load the two bytes into D separately and then write them both out together as a MONOBUS word. DB is designed for byte-by-byte output only. Composition of separate bytes into an output word should be carried out in the Working Registers, then transmitted to the D-Register by use of output code D in subfield REF1.

Figure A presents a number of CAP32 examples illustrating the concepts introduced in this and the previous topic.

| CAP32 Sequ                  | ence                         | Action                                                                                                                                                                                                                                                             |

|-----------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LM(7)<br>LMS(5)             | MW<br>D                      | Writes SLM(5) in memory at FX//PLM(7 i.e., writes secondary LM register 5 to the MONOBUS address given by FX and primary LM register 7.                                                                                                                            |

| LM(4)<br>DB                 | MR<br>Y                      | Reads from the MONOBUS address given in $PLM(4)$ and places input data byte in Y.                                                                                                                                                                                  |

| LM(5)<br>D<br>Y+1           | MW<br>Y<br>D                 | Increments the word at MONOBUS addres given in PLM(5). Note that "increment" means Read, Add 1, Rewrite.                                                                                                                                                           |

| X<br>D<br>Y<br>D            | MR<br>Y<br>MR<br>Y           | Reads a full word from the address no specified in FX and X (i.e., FX//X). That word is then used as the 16 lower order bits of a new address, still using FX as the upper two bits of the address. A data word is then read from the new address and placed in Y. |

| LM(8)<br>D<br>ZU<br>Y<br>Z  | MW<br>Y:Z<br>Z<br>ZU<br>D    | Reads the word addressed by FX//PLM(8 and then interchanges the two bytes of that word, rewriting it at the same address.                                                                                                                                          |

| Y<br>D,8,LG<br>ZU<br>ZL     | MR<br>Z<br>LM(G,IG)<br>LM(G) | Reads a word addressed by FX//Y. Places the upper byte of that word in the lower byte of CLM(8) (i.e., CLM(8).7=0). Places the lower byte of the word in the lower byte of CLM(9).                                                                                 |

| Y,4,LG<br>LM(G,IG)<br>LM(G) | MW<br>XU<br>XL:F<br>D        | Composes a data word from upper bytes of CLM(4) and CLM(5), and writes this word at address FX//Y.                                                                                                                                                                 |

Figure A. Sample MONOBUS Word and Byte Transfers

## 5.1 ALU SOURCES

The ALU is a major channel for signal transfer to the FBUS. The ALU transfers, complements, decrements, and provides two-operand logic and arithmetic functions of up to 14 different sources. These include numeric literals, Program Counter (P), Instruction Register (I), and the Working Registers (X, Y, and Z).

Figure A illustrates all ALU sources. The reader should also carefully study Reference Table A-7 in Appendix A.

If an FBUS destination is specified as byte-type (by use of XU, XL, ZU, or DB in REF1), the lower 8 bits of the ALU output are copied into the upper byte of the FBUS (15:8); the upper byte of the ALU output (ALU.15:8) is lost.

When any signal is transmitted through the ALU, the Arithmetic Flags and the Target Flags may be set at the option of the programmer. 1

The syntax for transfers from any source via the ALU to the FBUS is to simply name the source in the OPFl subfield. To transfer the one's complement of the source rather than the source signal itself, place a prime (single quote) after the source name in OPFl. Figure B gives a number of examples.

Any ALU source signal can be transmitted (or complemented and then transmitted) to the FBUS. However, for arithmetic and logical functions (or decrementing) the ALU input bus structure must be considered. Figure A emphasizes bus identification of each source (ABUS or BBUS). Only Working Register Y appears on both the ABUS and the BBUS. All other sources appear on one bus only, not both. An entire family of sources feed into the BBUS through its extension (IBUS). These include the Program Counter (P), its upper byte (PU), two mixed fields (SDX and GIW), and a group of I-type inputs. <sup>2</sup>

# References:

<sup>1</sup>Topics 5.4 and 5.5

<sup>&</sup>lt;sup>2</sup>Topics 8.3, 8.4, and 8.5

Figure A. ALU Sources and Bus Structure

| CAP32 Mi | croinstruction | Action                                                      |  |  |

|----------|----------------|-------------------------------------------------------------|--|--|

| 12'      | <b>Y</b>       | Sets Y equal to $FFF_{16}$ (i.e., one's complement of 12).  |  |  |

| 15'      | LM(5)          | Sets CLM(5) equal to FFF0 <sub>16</sub> .                   |  |  |

| Υ'       | Y:LM(6)        | Complements Y and stores result in both Y and in $CLM(6)$ . |  |  |

Figure B. Complementation Examples

#### 5

## 5.2 ALU PAIRED LOGIC OPERATIONS AND ABUS DECREMENTATION

The ALU provides four two-input (paired) logic operations, taking one input from the ABUS and the other from the BBUS. A special decrementation logic operation is also provided.

# Paired Logic Operations

For these operations, the syntax of subfield OPF1 taken on one of the following four forms:

a!b

a&b

a&b'

a\*b

where "a" and "b" denote ABUS and BBUS source codes respectively); where "!" denotes a bitwise Inclusive-OR logic operation; where "&" denotes a bitwise AND logic operation; where "\*" denotes a bitwise Exclusive-OR logic operation. Note that only in the form a&b' is complementation provided for the operand.

All logical operations are performed on 16 bits; however, a code used for a byte-size destination (XU, XL, ZU, DB) causes loss of the upper 8 bits, with the lower 8 bits of the result being copied into the upper byte (thus the result is present in both bytes of the ALU output).

Reference Table A-7 indicates that literals may be used as masks (i.e., as inputs to AND operations) only on BBUS inputs to the ALU. These are somewhat restricted by the normal limitation of literals to 4 bits. An 8-bit literal requires a subroutine call and return. All literals may be complemented, which aids in forming masks. Working Registers also aid in forming complex masks through their upper byte and Hex digit codes.

If destination code F is used in REF1 (singly or in combination), the Arithmetic Flags (AF) for Zero (AFZ) and Negative (AFN) conditions are set to reflect the result. However, the Carry Flag (AFC) and the Overflow Flag (AFO) settings are always zero after a logic operation. Target Flags may also be influenced.

Sample logic operations are shown in Figure A.

## ABUS Decrementation

Decrementation is normally considered arithmetic (subtracting 1 from the operand); however, the 3200 includes a special decrementation instruction which does not effect the Overflow and Carry Flags, but rather acts as a special logic operation. Special decrementation applies to ABUS sources only; it is specified by the following syntax:

a-ONE destination

where "a" denotes an ABUS source code. The "a" is followed by a minus sign and "ONE" spelled out. If "l" is used in place of "ONE", decrementing will occur, but through normal channels of arithmetic with Carry (Borrow) and Overflow provided, and with CB-Constraint. The use of "ONE" avoids CB-Constraint. Sample ABUS decrementation operations are illustrated in Figure B.

# References:

| CAP32 Mic      | roinstruction(s) | Action                                                                      |  |  |

|----------------|------------------|-----------------------------------------------------------------------------|--|--|

| Y*Y            | LM(G)            | Clears $CLM(G)$ .                                                           |  |  |

| Z!1            | Z                | Z.0 is set to 1, while Z.15:1 remain unchanged.                             |  |  |

| LMC(G)<br>Z&Y' | Z<br>LM(G)       | Clears the bits of CLM(G) that correspond in position to bits Y of value 1. |  |  |

Figure A. Sample Paired Logic Operations

| CAP32 Microinstruction(s) |           | Action                                                                        |  |  |

|---------------------------|-----------|-------------------------------------------------------------------------------|--|--|

| Y-ONE                     | Y         | Sets Y equal to Y-1 mod 10000 <sub>16</sub> .                                 |  |  |

| Y-ONE                     | LM(Z4,LG) | Sets CLM(Z.3:0) equal to Y-1 mod 10000 <sub>16</sub> ; sets G equal to Z.3:0; |  |  |

|                           |           | leaves Y and Z unchanged.                                                     |  |  |

| SB(6)                     | Υ .       | Clears upper 10 bits of X without                                             |  |  |

| Y-ONE                     | Y         | using Z.                                                                      |  |  |

| Y&X                       | X         |                                                                               |  |  |

| Z-ONE                     | Z         | Clears the upper $k$ bits of $X$ , where                                      |  |  |

| Z'                        | ${f z}$   | k is the value stored in Z.3:0. If                                            |  |  |

| SB(Z4)                    | Y         | Z.3:0 = 0, then all of X is cleared                                           |  |  |

| Y-ONE                     | Y         |                                                                               |  |  |

| Y&X                       | X         |                                                                               |  |  |

| Y&X                       | X         | Reads a word from the MONOBUS at lo                                           |  |  |

| LMN(9)                    | MR        | tion $FX//SLM(9)$ , then places a valu                                        |  |  |

| D                         | Y         | one less than the value of that wor                                           |  |  |

| Y-ONE                     | Y:LM(14)  | into Y and $PLM(14)$ ; assumes $PLM = C$                                      |  |  |

Figure B. Sample ABUS Decrementation and Paired Logic Operations

## 5.3 ALU ARITHMETIC OPERATIONS

The ALU provides 4 two's complement arithmetic operations: addition or subtraction with carry or borrow, and addition or subtraction without carry or borrow.

An arithmetic operation is specified by using one of the following syntax forms in the OPF1 subfield:

a+b

a+b+C

a-b

a-b-C

where "a" and "b" denote the ABUS and BBUS source codes, as for the paired logic operations<sup>1</sup>; and where "C" denotes the use of the carry or borrow bit from the next less significant word (i.e., carry for addition and borrow for subtraction). Note that reverse subtraction (i.e., b-a) is not provided.

A carry output bit is provided from either addition operation, and a borrow output bit is provided from either subtraction operation. The borrow bit is the complement of the carry bit normally provided at a simple binary adder's output; the borrow is 1 if a borrow is required.

If destination code F is used in subfield REF1, then all four AF's are set by the results of the arithmetic operation. Similarly, if code TFG is used in subfield REF3, and code F is used in subfield REF1, then the 4 bits of TFG are also set by the arithmetic result.

Arithmetic is either 16-bits or 8-bits wide, depending on the FBUS destination code. REFl codes XU, XL, ZU, and DB are 8-bit arithmetic; all other destination codes are 16-bit arithmetic.

Figure A shows sample arithmetic operations.

<sup>&</sup>lt;sup>1</sup>Topic 5.2

<sup>&</sup>lt;sup>2</sup>Topic 5.4 <sup>3</sup>Topic 5.5

| Y-Y       | LM(G)       | Clears $CLM(G)$ to 0.                 |

|-----------|-------------|---------------------------------------|

| Y+X       | Y           | Adds X to Y.                          |

| Z+Y       | Y           | Adds Z to Y.                          |

| Z         | MW          | Adds X to memory word addressed       |

| D         | Y           | by $FX//Z$ .                          |

| Y+X       | D           |                                       |

| LM(G)     | Y           |                                       |

| Y+1       | LM(G)       | Increments $PLM(G)$ .                 |

| Y-ONE     | Y           |                                       |

| Υ'        | Y           | Changes sign of Y.                    |

| Y,6,LG    | MR          |                                       |

| D         | X           | Adds word from memory at address Y    |

| LM(G)     | Z           | to the two-word integer in            |

| Z+X       | LM(G, IG):F | PLM(7)//PLM(6).                       |

| LM(G)     | Z           |                                       |

| Z+O+C     | LM(G)       |                                       |

| Y         | MR          | Adds 1 to the secondary LM register   |

| D         | ${f z}$     | indexed by the 4 lowest-order bits of |

| LM(Z4,LG) | Z           | the memory word addressed by Y.       |

| Z+1       | LM(G)       | · ·                                   |

| LMC(4,LG) | Y           | Adds $X$ to $CLM(4)$ .                |

| Y+X       | LM(G)       |                                       |

| LMC (4)   | Y           | Adds $CLM(4)$ to $X$ .                |

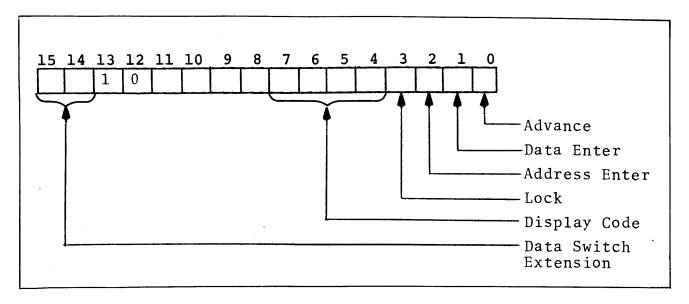

| Y+X       | Х           |                                       |