## PRODUCT DESCRIPTION

Micropolis 1550 Series

5 1/4-Inch Rigid Disk Drive

# MICROPΩLIS

## PRODUCT DESCRIPTION

Micropolis 1550 Series 5 1/4-Inch Rigid Disk Drive

#### PREFACE

This Product Description, intended for use by engineers, designers, and planners, describes the typical characteristics of the Micropolis 1550 Series of 5 1/4-inch Disk Drives. The information contained in this Product Description reflects current Micropolis design and experience, and is subject to change without notice.

> © Copyright 1988, 1989 Micropolis Corporation 21211 Nordhoff Street Chatsworth, CA 91311

> > Phone: (818)709-3300 FAX: (818)709-3302 Telex: 651486

# **TABLE OF CONTENTS**

| Section                  | on 1 - DESCRIPTION                                                                                                                                                                                    |                              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 1.1<br>1.2<br>1.3        | Features of the 1550 Series                                                                                                                                                                           | 1-3<br>1-7<br>1-7            |

| Section                  | on 2 - INTERFACE                                                                                                                                                                                      |                              |

| 2.1<br>2.2<br>2.3        | Interface and Power Connector Pin Assignments Interface Electrical Characteristics Interface Signal Descriptions 2.3.1 Control Input Signals 2.3.2 Control Output Signals 2.3.3 Data Transfer Signals | 2-3<br>2-4<br>2-4<br>2-13    |

| 2.4                      | Read, Write, and Format Parameters                                                                                                                                                                    | 2-21                         |

| Section                  | on 3 - INSTALLATION                                                                                                                                                                                   |                              |

| 3.1<br>3.2<br>3.3        | Physical Interface                                                                                                                                                                                    | 3-1<br>3-2<br>3-2<br>3-3     |

| 3.4<br>3.5               | Daisy-Chaining the 1550 Drive                                                                                                                                                                         | 3-5<br>3-6                   |

| Section                  | on 4 - POWER REQUIREMENTS                                                                                                                                                                             |                              |

| 4.1                      | Power Supply Requirements                                                                                                                                                                             | 4-1                          |

| Section                  | on 5 - DATA ORGANIZATION                                                                                                                                                                              |                              |

| 5.1                      | Track Format                                                                                                                                                                                          | 5-1                          |

| 5.2<br>5.3               | Error Rates Media Defects                                                                                                                                                                             |                              |

| Section                  | on 6 - SERVICEABILITY AND TECHNICAL SUPPORT                                                                                                                                                           |                              |

| 6.1<br>6.2<br>6.3<br>6.4 | Adjustments and Maintenance                                                                                                                                                                           | 6 <b>-</b> 1<br>6 <b>-</b> 1 |

(Intentionally blank)

## SECTION 1. DESCRIPTION

Micropolis 1550-series, high-performance, 5 1/4-inch Winchester Disk Drives provide OEMs with high-speed, high-capacity, random-access storage.

The drives are fully compatible with the Serial mode of the industry standard Enhanced Small Device Interface (ESDI) and are designed to meet the needs of diverse applications environments.

The Series is available in the following configurations (other configurations are available):

| Model                                                                                        | Data Surfaces                         | Capacity                                                                      |

|----------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------|

| Number                                                                                       | per Drive                             | (Unformatted)                                                                 |

| 1558-15<br>1558-14<br>1557-13<br>1557-12<br>1556-11<br>1556-10<br>1555-9<br>1555-8<br>1554-7 | 15<br>14<br>13<br>12<br>11<br>10<br>9 | 382.3<br>356.8<br>331.3<br>305.8<br>280.3<br>254.9<br>229.4<br>203.9<br>178.4 |

#### 1.1 FEATURES OF THE 1550 SERIES

- High-performance positioner delivers 18-millisecond average seek time for fast data access and high system throughput.

- Up to 382.5 Mbytes (unformatted) per drive; up to 2.68 Gbytes per controller.

- MTBF 150,000 hours.

- Hard or soft sectoring permits use with all ESDI controllers.

- Industry-standard 5 1/4-inch form-factor and mounting provisions ensure easy incorporation into current system packages.

- Rugged dual-chassis construction suspends the Head/Disk Assembly (HDA) on shock/vibration isolators to provide exceptional protection during transportation, installation, and operation.

- Balanced rotary positioner provides immunity to shock and vibration, and permits the drive to be mounted in any orientation.

(continued on next page)

# 1.1 FEATURES OF THE 1550 SERIES (continued)

- Positive media protection upon spin down is provided by retracting and locking the positioner in a data-free landing zone. A dynamic brake stops the motor quickly.

- Board-swap design results in an MTTR of less than 15 minutes.

- Microprocessor-based, adaptive electronics eliminates adjustment or periodic maintenance and improves overall reliability.

## 1.2 CHARACTERISTICS

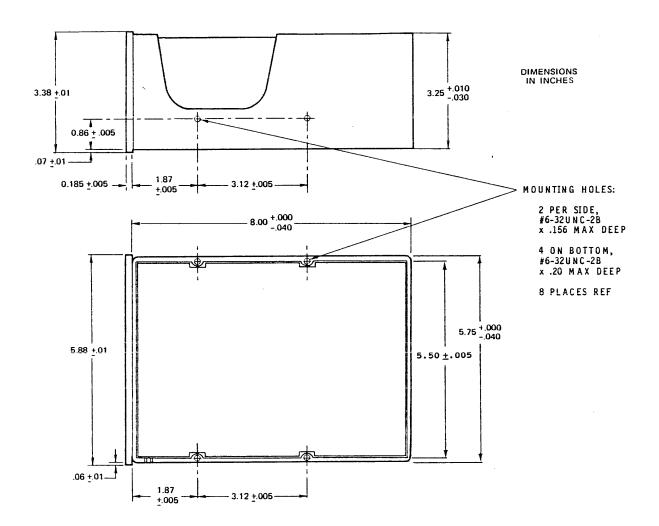

## **General Performance Specifications** Seek Time (including settling time) 4 msec Track-to-Track Average 18 msec 19 msec One-Third Stroke (maximum) 40 msec Maximum Rotational Latency 8.33 msec Average 16.67 msec Nominal Maximum 12 seconds typical Start Time (to Drive Ready) 20 seconds maximum 20 seconds maximum Stop Time 10.00 Mbits/sec Transfer Rate **General Functional Specifications** 1224 Cylinders Interface encoding method NRZ Internal encoding method RLL3600 Spindle speed (rpm) + 0.5 Speed variation (%) **General Physical Specifications** 3.25 in (82.6 mm) Height Drive: 5.75 in (146 mm) Width 8.00 in (203 mm) Depth 3.38 in (85.7 mm) Bezel: Height 5.88 in (149 mm) Width

Drive Weight (1558-15, maximum): 8.3 lbs

Depth

0.185 in (4.7 mm)

(3.8 kg)

# 1.2 CHARACTERISTICS (continued)

| Informatted    |        |        |        | Мо      | del Numbe | ır      |         |         |         |

|----------------|--------|--------|--------|---------|-----------|---------|---------|---------|---------|

|                | 1554-7 | 1555-8 | 1555-9 | 1556-10 |           |         | 1557-13 | 1558-14 | 1558-15 |

| Mbytes/Unit    | 178.4  | 203.9  | 229.4  | 254.9   | 280.3     | 305.8   | 331.3   | 356.8   | 382.3   |

| Data Heads     | 7      | 8      | 9      | 10      | 11        | 12      | 13      | 14      | 15      |

| Cylinders      |        |        |        |         | 1224 -    |         |         |         |         |

| Bytes/Track    |        |        |        |         | 20,832    |         |         |         |         |

| Mbytes/Surface |        |        |        |         | 25.49 -   |         |         |         |         |

| Formatted *    |        |        |        |         |           |         |         |         |         |

| 1024-Byte      | Form   | at:    |        |         |           |         |         |         |         |

|                |        |        |        |         | del Numbe |         |         |         |         |

|                | 1554-7 | 1555-8 | 1555-9 | 1556-10 | 1556-11   | 1557-12 | 1557-13 | 1558-14 | 1558-15 |

| Mbytes/Unit    | 166.6  | 190.4  | 214.2  | 238.1   | 261.9     | 285.7   | 309.5   | 333.3   | 357.1   |

| Sectors/Track  |        |        |        |         | - 19      |         |         |         |         |

| Bytes/Track    |        |        |        |         | 19,456    |         |         |         |         |

| Mbytes/Surface |        |        |        |         | 23.81 -   |         |         |         |         |

| 512-Byte 1     | Format | t:     |        |         |           |         |         |         |         |

| -1             |        | -      |        | Mo      | del Numbe | r       |         |         |         |

|                | 1554-7 | 1555-8 | 1555-9 |         |           | 1557-12 | 1557-13 | 1558-14 | 1558-15 |

| Mbytes/Unit    | 157.9  | 180.4  | 203.0  | 225.6   | 248.1     | 270.7   | 293.2   | 315.8   | 338.4   |

| Sectors/Track  |        |        |        |         | - 36      |         |         |         |         |

| Bytes/Track    |        |        |        |         | 19,456    |         |         |         |         |

| W              |        |        |        |         | 23 81 -   |         |         |         |         |

## 1.2 CHARACTERISTICS (continued)

```

Vibration

Operating (the drive can be operated and subjected to vibra-

tion up to the following levels, and will meet

error specifications shown on page 1-6)

5 - 40 \text{ Hz}

0.006 inches, peak-peak

40-300 Hz

0.5

G peak

Non-Operating (the drive will sustain no damage if subjected

to vibration up to the following levels)

Packaged (in original Micropolis shipping container)

5 - 10 Hz

0.2

inches, peak-peak

G peak

10 - 44 Hz

1

44 - 98 Hz

0.01

inches, peak-peak

98-300 Hz

5

G peak

Unpackaged

5 - 31 Hz

0.02

inches, peak-peak

31 - 69 Hz

1

G peak

69 - 98 Hz

0.004 inches, peak-peak

98-300 Hz

G peak

Shock

Operating

Range 1 (meets error specifications shown on page 1-6)

1/2 Sinusoidal

11 msec, 2 G peak

Range 2 (no component damage or data corruption)

1/2 Sinusoidal

11 msec, 8 G peak

NOTE: Shock levels exceeding Range 1 will result in deterioration of drive performance for

the duration of those shock levels, but the drive will return to normal operating

specifications after the shock period has passed.

Non-Operating (the drive will sustain no damage if subjected

to shock up to the following levels)

Packaged (in original Micropolis shipping container)

Free-fall drop

36 inches

1/2 Sinusoidal

20 msec, 50 G max

Unpackaged

Free-fall drop

0.75 inches

1.5 inches

Topple test

1/2 Sinusoidal

5 msec, 40 G max

11 msec, 20 G max

20 msec, 15 G max

50 msec, 15 G max

100 msec, 20 G max

```

## 1.2 CHARACTERISTICS (continued)

#### **Environmental Limits**

Operating Storage

Ambient 10°C to 50°C -40°C to 65°C Temperature (50°F to 122°F) (-40°F to 149°F)

Temperature 2.0°C/5 Minutes 24.0°C/Hour \* Gradient, max (3.6°F/5 Minutes) (43.2°F/Hour)

\* This gradient should not be exceeded when moving a drive from storage to operation.

Relative 10% to 90% 10% to 90% Humidity non-condensing non-condensing

26.7°C (80°F) 26.7°C (80°F) maximum wet bulb non-condensing non-condensing

Altitude -200 ft to 10,000 ft -1,000 ft to 50,000 ft

## Power Dissipation (typical drive, nominal voltage)

Stand-by 29 Watts; 98.9 Btu/hr Positioning (average) \*\* 35 Watts; 119.4 Btu/hr

\*\* This value is for 1/3-stroke seeks with an 8-millisecond idle period between seeks to simulate a typical system environment.

#### **Acoustic Noise**

Less than 47 dBA (sound pressure)

## Reliability

Errors

Soft Read  $\leq$  10 in  $10^{11}$  bits read Hard Read  $\leq$  10 in  $10^{13}$  bits read Seek  $\leq$  10 in  $10^7$  seeks

Unit MTBF 150,000 Power-On Hours

## Maintainability (HDA not included)

MTTR Less than 15 minutes

## 1.3 MAJOR COMPONENTS

The disk drive consists of a mechanical assembly and an electronics package. For a detailed functional theory of operation, see the 1550 Series Technical Manual, Micropolis No. 104189.

## 1.3.1 Mechanical Assembly

The mechanical assembly consists of a sealed Head/Disk Assembly (HDA) and an outer Frame.

## a. Head/Disk Assembly

The Head/Disk Assembly (HDA) consists of a die-cast structure that contains virtually all the drive's mechanical components. Two die-cast members create a sealed clean area. Components included in the clean area are the read/write heads, the magnetic disks, the head preamplifier, and the rotary positioner. Electrical connection between the mechanics in the clean area and the electronic circuit boards is made with flexible circuits. Air circulates through the clean area by disk rotation-induced flow. The air is filtered by a 0.3-micron absolute filter. The sealed area breathes to the outside via a similar filter.

## - Disk/Spindle Assembly

The magnetic disks are mounted on the spindle assembly, which incorporates a three-phase brushless DC motor, commutated by Hall-effect devices. The casting supports each end of the spindle assembly.

#### - Head Assembly

The drives have one servo head and up to 15 data heads. The head assembly flies over the disk surface on an "air bearing" created by the rotation of the disk. The heads rest on the disk surface (i.e., the landing zone) when the disk is not rotating.

#### - Positioner Assembly

The positioner is a balanced rotary motor mechanism. Each end of the positioner shaft is supported by the casting. The servo head and data heads are attached to the head-arm assemblies mounted to the pivot housing. The motor torque rotates the positioner about its axis of rotation. Rotation is constrained to keep the heads over the safe operating area of the disk by means of limit stops.

Position reference is made to tracks recorded on the disk surface nearest the baseplate. Position information is recorded on these tracks in a "Modified Dibit" format. An area of the disk (not used for data storage) is reserved for landing the heads. When power is removed from the drive, the positioner assembly is automatically retracted to that landing zone, and a latch is activated to prevent the positioner from leaving the landing zone. Thus, no operator intervention is necessary when shipping a drive or when shipping the equipment in which a drive is installed.

## - Recording Media

The recording media is a 130-millimeter (5 1/4-inch) diameter aluminum disk substrate covered with a thin coating of magnetic media. The disk surface permits head-to-disk contact without damage.

#### - Braking

The heads contact the disk surface when the disks are not spinning and during start and stop cycles. To minimize head and disk wear, dynamic braking is used to bring the spindle to a quick stop.

## b. Frame (Outer Chassis)

The HDA is suspended within an outer frame on shock mounts. This method of suspension isolates the HDA from mounting-related distortion or stress, or shock and vibration.

## 1.3.2 Electronic Components

The electronic components for the 1550 Series are mounted on three printed circuit boards:

- a. Device Electronics board.

- b. Auxiliary board (plugs into the Device Electronics board).

- c. Preamplifier (inside the HDA).

The electronic circuitry provides overall control and data functions for the drive. Microprocessor-based logic controls power-up and power-down sequencing and velocity profile generation. Servo circuits ensure positioner speed and accuracy. Interface drivers and receivers provide for transmission and reception of control, data, and status signals across the interface; while read/write circuits provide for data flow onto and off the disks.

## SECTION 2. INTERFACE

## 2.1 INTERFACE AND POWER CONNECTOR PIN ASSIGNMENTS

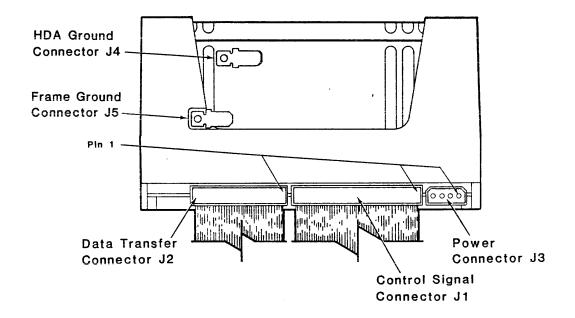

The 1550 Series is pin- and function-compatible with the Serial mode of the Enhanced Small Device Interface (ESDI) for 5 1/4-inch Winchester disk drives. In the Serial mode, interface signals (control, data, and status) are transmitted serially via handshaking request/acknowledge signals. Electrical interface between the drive and the host system is accomplished via five connectors: Control Signal Connector J1 (see Table 2-1) and Data Transfer Connector J2 (see Table 2-2), Power Connector J3 (see Table 2-3), and optional Ground Connectors J4 and J5. See Figure 3-1 for the locations of the five connectors.

TABLE 2-1. CONTROL SIGNAL CONNECTOR J1 PIN ASSIGNMENTS

| J1 Conne<br>Signal | ctor Pin<br>Ground | Signal Name                       | Source     |

|--------------------|--------------------|-----------------------------------|------------|

| 2                  | 1                  | -HEAD SELECT 2 <sup>3</sup>       | Controller |

| 4                  | 3                  | -HEAD SELECT 2 <sup>2</sup>       | Controller |

| 6                  | 5                  | -WRITE GATE                       | Controller |

| 8                  | 7                  | -CONFIGURATION/STATUS DATA        | Drive      |

| 10                 | 9                  | -TRANSFER ACKNOWLEDGE             | Drive      |

| 12                 | _ 11               | -ATTENTION                        | Drive      |

| 14                 | 13                 | -HEAD SELECT 20                   | Controller |

| 16                 | 15                 | { -SECTOR } -ADDRESS MARK FOUND } | Drive      |

| 18                 | 17                 | -HEAD SELECT 2 <sup>1</sup>       | Controller |

| 20                 | 19                 | -INDEX                            | Drive      |

| 22                 | 21                 | -READY                            | Drive      |

| 24                 | 23                 | -TRANSFER REQUEST                 | Controller |

| 26                 | 25                 | -DRIVE SELECT 1                   | Controller |

| 28                 | 27                 | -DRIVE SELECT 2                   | Controller |

| 30                 | 29                 | -DRIVE SELECT 3                   | Controller |

| 32                 | 31                 | -READ GATE                        | Controller |

| 34                 | 33                 | -COMMAND DATA                     | Controller |

Recommended Cable: 3M Scotchflex 3365/34 Mating Connector: AMP 88373-3 (key slot between pins 4 and 6)

TABLE 2-2. DATA TRANSFER CONNECTOR J2 PIN ASSIGNMENTS

| J2 Connec |    | Signal Name                     | Source     |

|-----------|----|---------------------------------|------------|

| 1         | -  | -DRIVE SELECTED                 | Drive      |

| 2         | -  | { -SECTOR } -ADDRESS MARK FOUND | Drive      |

| 3         | -  | -COMMAND COMPLETE               | Drive      |

| 4         | -  | -ADDRESS MARK ENABLE            | Controller |

| 5         | 6  | (Reserved)                      | Drive      |

| 7         | -  | +WRITE CLOCK                    | Controller |

| 8         | -  | -WRITE CLOCK                    | Concrotter |

| 9         | _  | (Reserved)                      | Drive      |

| 10        | 12 | +READ/REFERENCE CLOCK           | Drive      |

| 11        | 12 | -READ/REFERENCE CLOCK           | DIIVE      |

| 13        | 15 | +NRZ WRITE DATA                 | Controller |

| 14        | 16 | -NRZ WRITE DATA                 | Concrotter |

| 17        | 19 | +NRZ READ DATA                  | Drive      |

| 18        | 19 | -NRZ READ DATA                  | DIIVE      |

| 20        | -  | -INDEX                          | Drive      |

Recommended Cable: 3M Scotchflex 3365/20

Mating Connector: AMP 88373-6 (key slot between pins 4 and 6)

Power is supplied to the drive via AMP MATE-N-LOK Connector J3; refer to Section 4 for power requirements. Voltages in Table 2-3 are  $\pm 5\%$ , measured at the drive's power connector.

TABLE 2-3. DC POWER CONNECTOR J3 PIN ASSIGNMENTS

| Pin | Voltage    | Pin | Voltage   |

|-----|------------|-----|-----------|

| 1 2 | +12 V      | 3   | +5 RETURN |

|     | +12 RETURN | 4   | +5 V      |

Suggested wire size: 18 AWG (minimum) for all pins

Mating connector: AMP 1-480424-0 Pins: AMP 350078-4

## 2.2 INTERFACE ELECTRICAL CHARACTERISTICS

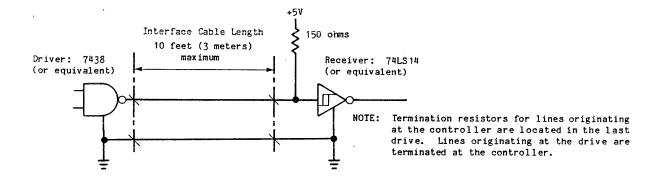

Figure 2-1 summarizes the electrical characteristics of the signals at Control Signal Connector J1. These signals control the drive and transfer drive status to the host controller. The signals are low-true at the interface, high-true into drivers and out of receivers, and have the following logic levels:

True = 0.0 VDC to 0.4 VDC @ I = -48 milliamps (maximum) False = 2.5 VDC to 5.25 VDC @ I = +250 microamps (open collector)

Figure 2-1. Control Signal Driver/Receiver Combination

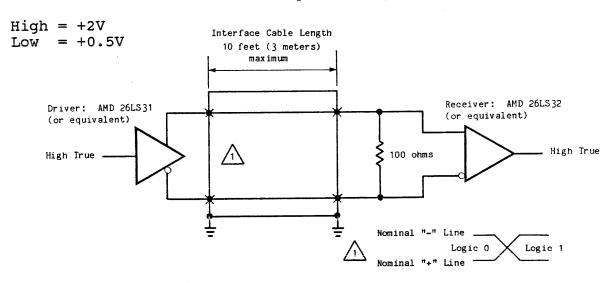

All interface data transfer signals are differential in nature. Figure 2-2 summarizes the electrical characteristics of those differential signals at Data Transfer Connector J2 (one TTL control signal and four TTL status signals are also provided at Connector J2). The signals are high true into drivers and out of receivers and have the following levels (EIA RS-422):

Figure 2-2. Data Line Driver/Receiver Combination

#### 2.3 INTERFACE SIGNAL DESCRIPTIONS

## 2.3.1 Control Input Signals

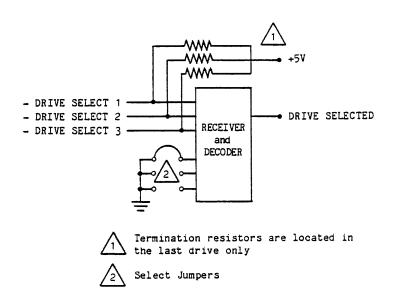

DRIVE SELECT 1 through DRIVE SELECT 3 (J1, Pins 26, 28, and 30)

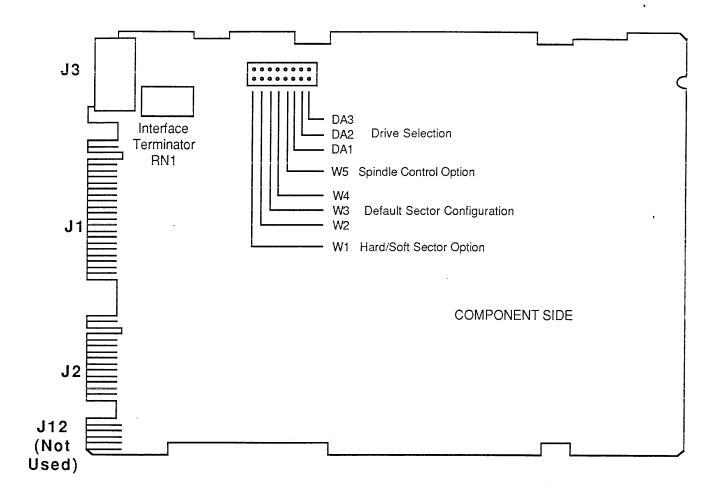

Up to seven drives can be connected to one host controller/formatter. Drive Select 1, Drive Select 2, and Drive Select 3 carry the binary-coded address of the drive to be selected. The address of the drive is set with drive-selection jumpers DA1, DA2, and DA3 as a binary combination. When the address is decoded and the decoded value matches the value specified by the three drive-selection jumpers, that drive is enabled to receive commands and transmit status. Drive Select 1 is the least significant bit.

|                                 | Int                         | terface Signa              | als                        |

|---------------------------------|-----------------------------|----------------------------|----------------------------|

| Drive<br>Address                | DRIVE SELECT 3 (DA3)        | DRIVE<br>SELECT 2<br>(DA2) | DRIVE<br>SELECT 1<br>(DA1) |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 0<br>0<br>.0<br>1<br>1<br>1 | 0<br>1<br>1<br>0<br>0<br>1 | 1<br>0<br>1<br>0<br>1<br>0 |

1 = true, 0 = false Drive Address  $\emptyset$  is used as a "deselect" (i.e., no drive is selected).

Figure 2-3. Drive Select Termination and Matrix

HEAD SELECT 20 through HEAD SELECT 23 (J1, Pins 14, 18, 4, and 2)

These four lines furnish a binary-coded address which, when decoded, selects the corresponding data head. The four lines provide for the selection of up to sixteen data heads (addressed 0 through 15). A 150-ohm resistor pack allows for line termination.

For 1550-series drives, the maximum number of data heads is sixteen. The heads are addressed  $\emptyset$  through 15 (depending on the model) in a binary-coded sequence where Head Select  $2^0$  is the least significant bit. If all four Head Select lines are inactive, Head  $\emptyset$  is selected. An attempt to write to a head with an address greater than any contained in the drive will result in a write fault.

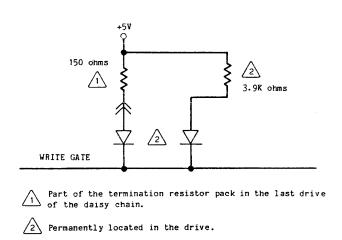

#### WRITE GATE (J1, Pin 6)

When the Write Gate signal is active, (i.e., low) data may be written to the disk. The high-to-low transition of this signal creates a write splice.

This line is protected from terminator power loss by implementation of the circuit as shown in Figure 2-4.

Figure 2-4. Write Gate Termination

#### READ GATE (J1, Pin 32)

When the Read Gate signal is active (i.e., low), data may be read from the disk. A 150-ohm resistor pack allows for line termination.

Read Gate should be activated only during a PLO Sync field and at least the number of bytes defined by the drive prior to the ID or Data Sync bytes.

The length of the PLO Sync field is determined by the response to the Request PLO Sync Field Length command.

Read Gate must be dropped before a splice area and raised again after going through the splice area.

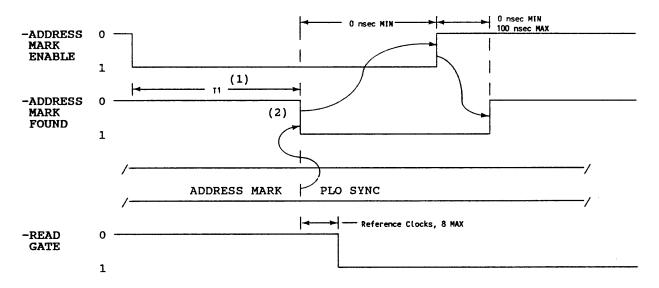

## ADDRESS MARK ENABLE (J2, Pin 4)

The Address Mark Enable signal is a control input in the radial (J2) cable. It is not multiplexed. This signal line is permanently terminated in the drive as shown in Figure 2-1.

## a. For Soft Sector Configuration

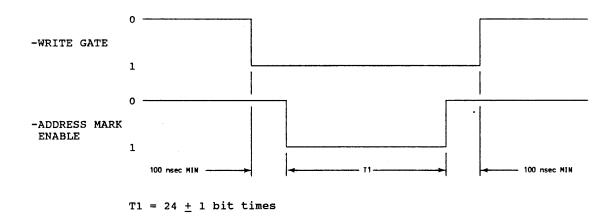

The Address Mark Enable signal, when active with the Write Gate signal, causes an Address Mark to be written. The Address Mark Enable signal must be held active for 24 bit times; see Figure 2-5 for timing.

If both the Write Gate and Read Gate signals are false, the active state of the Address Mark Enable signal causes a search for Address Marks.

Figure 2-5. Write Address Mark Timing

#### b. For Fixed Sector Configuration

Assertion of the Address Mark Enable signal does <u>not</u> cause an Address Mark to be written.

TRANSFER REQUEST (J1, Pin 24)

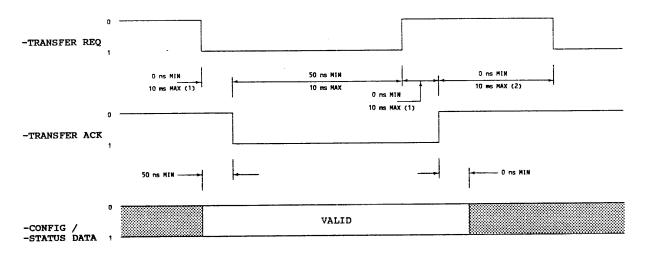

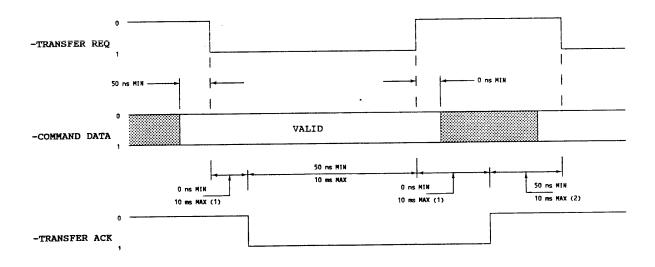

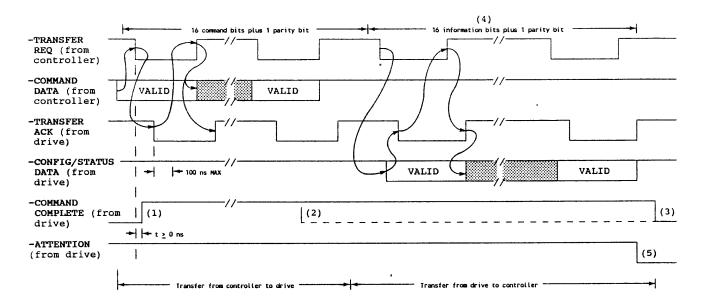

The Transfer Request signal functions as a "handshake" signal that is used in conjunction with the Transfer Acknowledge signal during Command and Configuration/Status transfers; see Figures 2-6 and 2-7 for timing. Typical timing for the complete 17-bit transfer is less than 200 microseconds.

- (1) Typical timing is less than 10 microseconds.

- (2) Except on the last bit.

Figure 2-6. One Bit Transfer Timing - From Drive

- (1) Typical timing is less than 10 microseconds.

- (2) Except on the last bit.

Figure 2-7. One Bit Transfer Timing - To Drive

COMMAND DATA (J1, Pin 34)

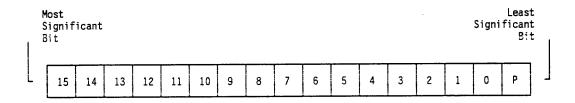

When a command is sent to the drive, 16 bits of serial data, plus parity, are presented on this line. Figure 2-8 shows the two available structures for the command data word.

| ; | Most<br>Signif<br>Bit | icant |       |    |    |       |       |    |   |       |       |       |       |   |   | Signi | Leas<br>fican<br>Bi |     |

|---|-----------------------|-------|-------|----|----|-------|-------|----|---|-------|-------|-------|-------|---|---|-------|---------------------|-----|

| L | 15                    | 14    | 13    | 12 | 11 | 10    | 9     | 8  | 7 | 6     | 5     | 4     | 3     | 2 | 1 | 0     | Р                   | ] - |

|   |                       | CMD F | UNCTI | ON |    | CMD M | ODIFI | ER |   |       |       | ALL . | ZEROS |   |   |       | P*                  |     |

|   |                       | CMD F | UNCTI | ON |    |       |       |    | C | MD PA | RAMET | ER    |       |   |   |       | р*                  |     |

<sup>\*</sup> Bit P: Parity (odd)

Figure 2-8. Command Data Word Structure

Parity utilized in all commands is odd. The parity bit is a "1" when the number of 1 bits in a 16-bit command is even. As a result, the total number of 1 bits in a command, including parity, is always odd.

Command Data is controlled by "handshake" protocol with the Transfer Request and Transfer Acknowledge signals; Figure 2-7 specifies the timing. Upon receipt of the serial data, the drive performs the function specified by the bit configuration. The most significant bit (MSB) is transmitted first. No communications should be attempted unless the Command Complete line is true. See Table 2-4 for the Command definitions associated with the various bit configurations. Note that the Command Data line must be at a logic zero when not in use.

Command Codes (Table 2-4)

0000 - Seek

The Seek command causes the drive to seek to the cylinder indicated by bits 0 - 11. A Seek command restores track and data strobe offsets to zero.

0001 - Recalibrate

Recalibrate returns the heads to Cylinder  $\emptyset$ . This command also restores track and data strobe offsets to zero.

COMMAND DATA (continued)

TABLE 2-4. COMMAND DATA DEFINITION

| COMMA<br>15                               | ND FUN<br>14                         | CTION<br>13                               | BITS<br>12                           | CMD FUNCTION<br>DEFINITION                                                                                                                                         | CMD MODIFIER<br>APPLICABLE<br>(Bits 11 - 8) | CMD PARAMETER<br>APPLICABLE<br>(Bits 11 - 0)           | STATUS/CONFIGURA-<br>TION DATA RETURNED<br>TO CONTROLLER |

|-------------------------------------------|--------------------------------------|-------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|

| 0 0 0                                     | 0<br>0<br>0<br>0                     | 0<br>0<br>1<br>1<br>0                     | 0<br>1<br>0<br>1<br>0                | SEEK RECALIBRATE REQUEST STATUS REQUEST CONFIGURATION SELECT HEAD GROUP (not implemented)                                                                          | NO<br>NO<br>YES<br>YES<br>NO                | YES<br>NO<br>NO<br>NO<br>VES                           | NO<br>NO<br>YES<br>YES<br>NO                             |

| 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>0<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | CONTROL DATA STROBE OFFSET TRACK OFFSET INITIATE DIAGNOSTICS SET BYTES PER SECTOR RESERVED RESERVED RESERVED RESERVED RESERVED SELECT HEAD GROUP (not implemented) | YES YES NO NO NO                            | NO<br>NO<br>NO<br>NO<br>YES<br>-<br>-<br>-<br>-<br>YES | NO<br>NO<br>NO<br>NO<br>-<br>-<br>-<br>-<br>NO           |

| 1                                         | 1                                    | 1                                         | 1                                    | RESERVED                                                                                                                                                           | _                                           | _                                                      | -                                                        |

NOTES: All unused or not applicable lower-order bits must be zero.

Any reserved or unimplemented command or function is treated as an invalid command.

Simultaneous data strobe and track offsets are allowed by multiple commands.

#### 0010 - Request Status

Request Status causes the drive to send 16 bits of status information to the host controller as determined by the command modifier bits. Parity is odd for all responses. Note that only command modifiers 0000 (Request Standard Status) and 0001 (Request Vendor Unique Status) are used; command modifiers 0010 through 1111 are not implemented.

## Request Standard Status (command modifier 0000)

When command modifier bits 11 - 8 of the Request Status command are 0000, the drive responds with 16 bits of standard status information; refer to Table 2-11, Status Response Bits.

- Bits 15 12 of this status are defined as status bits, which do not cause the Attention signal to be asserted.

- Bits 11 0 of this status are fault or status change bits that cause the Attention signal to be asserted each time one is set.

COMMAND DATA (continued)

Request Vendor Unique Status (command modifier 0001)

Vendor Unique Status consists of one word of status and is only valid if bit 2 of the Standard Status is a one. This status is only intended to be utilized by trained field maintenance personnel and is not intended to be interpreted by disk controllers or operating systems.

If this bit is detected, the controller should attempt to reset Standard Status and reattempt the original function a minimum of three times prior to defining the drive as inoperative. After the last attempt, the Vendor Unique Status word should be read by the controller and sent back to the system for a print out of these codes which may then be utilized by the field maintenance personnel.

## 0011 - Request Configuration

The Request Configuration command causes the drive to send 16 bits of configuration data to the host controller. The parity utilized in all configuration responses is odd. The specific drive configuration is specified by bits 11 - 8 of the command; see Table 2-5.

TABLE 2-5. REQUEST CONFIGURATION MODIFIER BITS

| COMMA | AND MODI<br>10 | IFIER 1 | BITS<br>8 | FUNCTION                                          |

|-------|----------------|---------|-----------|---------------------------------------------------|

| 0     | 0              | 0       | 0         | GENERAL CONFIGURATION OF THE DRIVE AND FORMAT     |

| 0     | 0              | 0       | 1         | NUMBER OF CYLINDERS, fixed                        |

| 0     | 0              | 1       | 0         | NUMBER OF CYLINDERS, removable                    |

| 0     | 0              | 1       | 1         | NUMBER OF HEADS                                   |

| 0     | 1              | 0       | 0         | MINIMUM UNFORMATTED BYTES PER TRACK               |

| 0     | 1              | 0       | 1         | UNFORMATTED BYTES PER SECTOR (hard sector only)   |

| 0     | 1              | 1       | 0         | SECTORS PER TRACK (hard sector only)              |

| 0     | 1              | 1       | 1         | MINIMUM BYTES IN THE ISG FIELD                    |

| 1     | 0              | 0       | 0         | MINIMUM BYTES PER PLO SYNC FIELD                  |

| 1     | 0              | 0       | 1         | NUMBER OF WORDS OF VENDOR-UNIQUE STATUS AVAILABLE |

| 1     | 0              | 1       | 0         | RESERVED                                          |

| 1     | 0              | 1       | 1         | RESERVED                                          |

| 1     | 1              | 0       | 0         | RESERVED                                          |

| 1     | 1              | 0       | 1         | RESERVED                                          |

| 1     | 1              | 1       | 0         | RESERVED                                          |

| 1     | 1              | 1       | 1         | VENDOR IDENTIFICATION (not implemented)           |

#### 0100 - Select Head Group

Not implemented in the 1550 Series at this time. Execution will result in an Unimplemented Command fault.

COMMAND DATA (continued)

#### 0101 - Control

The Control command causes operations specified by command modifier bits 11 - 8 to be performed as shown in Table 2-6.

TABLE 2-6. CONTROL COMMAND MODIFIER BITS

| COMM/<br>11 | AND MODI<br>10 | FIER<br>9 | BITS<br>8 | FUNCTION                                                    |

|-------------|----------------|-----------|-----------|-------------------------------------------------------------|

| 0           | 0              | 0         | 0         | RESET INTERFACE ATTENTION AND STANDARD STATUS (bits 0 - 11) |

| 0           | 0              | 0         | 1         | RESERVED                                                    |

| 0           | 0              | 1         | 0         | STOP SPINDLE MOTOR *                                        |

| 0           | 0              | 1         | 1         | START SPINDLE MOTOR                                         |

| 0           | 1              | 0         | 0         | RESERVED                                                    |

| 1 0         | 1              | 0         | 1         | RESERVED                                                    |

| . 0         | 1              | 1         | 0         | ! RESERVED                                                  |

| 0           | 1              | 1         | 1         | RESERVED                                                    |

| 1           | X              | X         | X         | RESERVED                                                    |

<sup>\*</sup> Available on request

#### 0110 - Data Strobe Offset

The Data Strobe Offset command causes the drive to offset the data strobe in the direction specified by bits 11 - 8; see Table 2-7.

The 1550 Series implements only <u>one</u> value of Data Strobe Offset. The drives respond to all offset commands as legal functions by offsetting the one value in the specified direction.

Seek or Recalibrate commands restore offsets to zero. Simultaneous Track and Data Strobe offsets are allowed by using multiple commands.

TABLE 2-7. DATA STROBE COMMAND MODIFIER BITS

| COMM/<br>11 | AND MODI<br>10 | FIER 1 | BITS<br>8 | FUNCTION            |

|-------------|----------------|--------|-----------|---------------------|

| 0           | 0              | 0      | 0         | RESTORE OFFSET TO 0 |

| 0           | 0              | 0      | 1         | RESTORE OFFSET TO 0 |

| 1 0         | 0              | 1      | 0         | EARLY OFFSET        |

| 1 0         | 0              | 1      | 1         | LATE OFFSET         |

| 0           | 1              | 0      | 0         | EARLY OFFSET        |

| 1 0         | 1              | 0      | 1         | LATE OFFSET         |

| 0           | 1              | 1      | 0         | EARLY OFFSET        |

| 0           | 1              | 1      | 1         | LATE OFFSET         |

| 1           | X              | X      | X         | RESERVED            |

COMMAND DATA (continued)

## 0111 - Track Offset

The Track Offset command causes the drive to perform a track offset in the direction and amount specified by bits 11 - 8 as shown in Table 2-8.

Seek and Recalibrate commands restore the offsets to zero. Simultaneous Track and Data Strobe offsets are allowed by the use of multiple commands.

TABLE 2-8. TRACK OFFSET COMMAND MODIFIER BITS

| COMM/<br>11 | AND MODI<br>10 | FIER E | BITS<br>8 | FUNCTION            |

|-------------|----------------|--------|-----------|---------------------|

| 0           | 0              | 0      | 0         | RESTORE OFFSET TO 0 |

| 0           | 0              | 0      | 1         | RESTORE OFFSET TO 0 |

| 0           | 0              | 1      | 0         | POSITIVE OFFSET     |

| 0           | 0              | 1      | 1         | NEGATIVE OFFSET     |

| 0           | 1              | 0      | 0         | POSITIVE OFFSET     |

| 0           | 1              | 0      | 1 '       | NEGATIVE OFFSET     |

| 0           | 1              | 1      | 0         | POSITIVE OFFSET     |

| 0           | 1              | 1      | 1         | NEGATIVE OFFSET     |

| 1           | X              | X      | Х         | RESERVED            |

#### 1000 - Initiate Diagnostics

The Initiate Diagnostics command causes the drive to perform internal diagnostics. The Command Complete signal indicates the completion of the diagnostics. The Attention signal, along with the Command Complete signal, indicates that a fault was encountered and that status should be requested to determine a proper course of action. Extended fault information is made available in one word of Vendor Unique Status; see COMMAND DATA (Request Status, 0010).

## 1001 - Set Unformatted Bytes Per Sector

Note that this command is valid only if the drive is configured to be in the drive hard sector mode.

The Set Unformatted Bytes Per Sector command causes the drive to set the number of bytes per sector indicated by bits 11 - 0. Sector size may be selected in one-byte increments, with a minimum of 82 bytes/sector. If this command is not implemented by the host controller, default sector sizes may be jumper selected by default sector option jumpers; see Section 3.3.3.

COMMAND DATA (continued)

1110 - Set Configuration

Not implemented in the 1550 Series at this time. Execution will result in an Unimplemented Command fault.

## 2.3.2 Control Output Signals

The output signals transfer drive status to the host controller. All J1 output signals are enabled/gated by their respective Drive Select line decode; J2 output signals are ungated. Figure 2-1 shows the driver/receiver combination used in 1550-series drives for control output signals.

DRIVE SELECTED (J2, Pin 1)

Drive Selected is the status line that informs the host system of the selection status of the drive. This signal goes active when the drive is programmed as drive n (where n=1, 2, 3, 4, 5, 6, or 7) and the Drive Select lines at J1 are activated by the host system to produce a binary code equal to n.

READY (J1, Pin 22)

When true, together with the Command Complete signal, the Ready signal indicates that the drive is conditioned to read, write, or seek. When this line is false, seeking or writing is inhibited.

CONFIGURATION/STATUS DATA (J1, Pin 8)

The drive presents serial configuration or status data on this line upon request from the host controller. The serial data is made available at the interface using Transfer Request and Transfer Acknowledge signals for the "handshake" protocol; see Figure 2-6. The parity used is odd. Once initiated, 16 bits plus parity are transmitted, MSB first. Refer to Figure 2-9 for the data word structure.

Figure 2-9. Configuration/Status Data Word Structure

CONFIGURATION/STATUS DATA (continued)

Figure 2-10 shows a typical serial operation.

- NOTES: (1) Applicable for all Request Status and Configuration commands.

- (2) COMMAND COMPLETE is negated for all commands to the drive. COMMAND COMPLETE shall be negated following the assertion of TRANSFER REQ and the maximum time by which COMMAND COMPLETE shall be negated is 100 nanoseconds after TRANSFER ACK is asserted.

- (3) COMMAND COMPLETE is asserted to signify completion of execution of a command. Applicable for all commands.

- (4) COMMAND COMPLETE is asserted to signify completion of the requested Configuration/Status transfer.

- (5) If an error was encountered during the current command, ATTENTION shall be activated at least 100 nanoseconds before COMMAND COMPLETE is activated.

#### Figure 2-10. Typical Serial Operation(s)

#### Configuration Response Bits

In response to the Request Configuration (0011) command, 16 bits of configuration information are returned to the host controller.

- If command modifier bits 11 8 are 0000, the general configuration status information shown in Table 2-9 is returned.

- If command modifier bits 11 8 are not 0000, specific configuration data shown in Table 2-10 is returned for the Request Configuration command with those modifiers.

CONFIGURATION/STATUS DATA (continued)

TABLE 2-9. GENERAL CONFIGURATION RESPONSE BITS

| BIT<br>POSITION                           | FUNCTION                                                                                                                                                                                                                                                                                                    | VALUE                                                                 |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 15<br>14<br>13<br>12<br>11                | TAPE DRIVE FORMAT SPEED TOLERANCE GAP REQUIRED TRACK OFFSET OPTION AVAILABLE DATA STROBE OFFSET OPTION AVAILABLE ROTATIONAL SPEED TOLERANCE > 0.5% TRANSFER RATE > 10 MHz                                                                                                                                   | 0<br>0<br>1<br>1<br>0                                                 |

| 9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1 | TRANSFER RATE > 5 MHz ≤ 10 MHz  TRANSFER RATE < 5 MHz  REMOVABLE CARTRIDGE DRIVE  FIXED DRIVE  SPINDLE MOTOR CONTROL OPTION IMPLEMENTED  HEAD SWITCH TIME > 15 usec  RLL ENCODED (not MFM)  CONTROLLER SOFT SECTORED (ADR Mark)  DRIVE HARD SECTORED (Sector Pulses)  CONTROLLER HARD SECTORED (Byte Clock) | 1<br>0<br>0<br>1<br>X Selectable<br>0<br>1<br>X } Selectable<br>X o , |

TABLE 2-10. SPECIFIC CONFIGURATION RESPONSE BITS

| COMM. | AND MODI<br>10 | FIER<br>9   | BITS<br>8   | FUNCTION                                                                                                                                                                                   |

|-------|----------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0   | 0<br>0<br>0    | 0<br>1<br>1 | 1<br>0<br>1 | NUMBER OF CYLINDERS, Fixed NUMBER OF CYLINDERS, Removable media (zero) NUMBER OF HEADS Bits 15-8: Removable drive heads Bits 7-0: Fixed heads                                              |

| 0 0   | 1<br>1<br>1    | 0<br>0<br>1 | 0<br>1<br>0 | MINIMUM UNFORMATTED BYTES PER TRACK MINIMUM UNFORMATTED BYTES PER SECTOR (hard sector only) NUMBER OF SECTORS PER TRACK (hard sector only) Bits 15-8: Reserved Bits 7-0: Sectors per track |

| 0     | 1              | 1           | 1           | MINIMUM BYTES IN ISG FIELD<br>Bits 15-8: ISG Bytes after Index/Sector Pulse<br>Bits 7-0: Bytes per ISG                                                                                     |

| 1     | 0              | 0           | 0           | MINIMUM BYTES PER PLO SYNC FIELD Bits 15-8: Reserved Bits 7-0: Bytes per PLO Sync Field required when READ GATE is asserted                                                                |

| 1     | 0              | . 0         | 1           | NUMBER OF WORDS OF VENDOR-UNIQUE STATUS AVAILABLE Bits 15-4: Reserved Bits 3-0: Number of vendor-unique status words                                                                       |

| 1     | 0              | 1           | 0           | ר                                                                                                                                                                                          |

|       |                |             |             |                                                                                                                                                                                            |

|       | •              |             |             | Reserved                                                                                                                                                                                   |

| 1;    |                | •           | 0           | ]                                                                                                                                                                                          |

| 1 1   | 1              | 1           | -           | VENDOD IDENTIFICATION (not implemented)                                                                                                                                                    |

|       | 1              | 1           | 11          | VENDOR IDENTIFICATION (not implemented)                                                                                                                                                    |

CONFIGURATION/STATUS DATA (continued)

2) Status Response Bits

In response to the Request Status (0010) command, 16 bits of status information are sent to the host controller; see Table 2-11.

- a. Bits 15 12 are defined as state bits which do not cause the Attention signal to be asserted.

- b. Bits 11 0 are fault or status-change bits which cause the Attention signal to be asserted.

TABLE 2-11. STATUS RESPONSE BITS

| BIT<br>POSITION | FUNCTION                                   |

|-----------------|--------------------------------------------|

| 15              | RESERVED                                   |

| 14              | REMOVABLE MEDIA NOT PRESENT                |

| 13              | WRITE PROTECTED, Removable Media           |

| 12              | WRITE PROTECTED, Fixed Media               |

|                 |                                            |

| 11              | RESERVED                                   |

| 10              | RESERVED                                   |

| 9               | SPINDLE MOTOR STOPPED (1)                  |

| 8               | POWER-ON RESET CONDITIONS EXIST (2)        |

| 7               | COMMAND DATA PARITY FAULT                  |

| 6               | INTERFACE FAULT                            |

| 5               | INVALID OR UNIMPLEMENTED COMMAND FAULT (3) |

| 4               | SEEK FAULT                                 |

| 3               | WRITE GATE WITH TRACK OFFSET FAULT         |

| 2               | VENDOR UNIQUE STATUS AVAILABLE             |

| 1 1             | WRITE FAULT (4)                            |

| 0               | REMOVABLE MEDIA CHANGED                    |

- (1) Spindle Motor stopped due to previous command to stop, or drive is in Power-On Reset condition.

- (2) Reconfiguration or Start Spindle Motor command may be required.

- (3) This status is issued when a command is received which is invalid or has not been implemented.

- (4) Conditions that can cause a Write Fault are:

- a. Write current in a head without WRITE GATE active, or no write current with WRITE GATE active and the drive selected.

- $\hbox{b. Multiple heads selected, no head selected, or improperly selected with WRITE GATE active.}\\$

- c. WRITE GATE active to a write-protected drive.

- d. Simultaneous activation of READ GATE and WRITE GATE.

- e. DC voltages grossly out of tolerance.

## TRANSFER ACKNOWLEDGE (J1, Pin 10)

The Transfer Acknowledge signal functions as a "handshake" signal with the Transfer Request signal during Command and Configuration/Status transfers; refer to Figures 2-6 and 2-7.

## ATTENTION (J1, Pin 12)

The Attention signal is asserted when the drive wants the host controller to request Standard Status. Generally, this is a result of a fault condition or a change of status. Writing is inhibited when Attention is asserted. The Attention signal is deactivated by Reset Interface Attention; see Section 2.3.1, COMMAND DATA (Control, 0101).

## INDEX (J1, Pin 20; and J2, Pin 20)

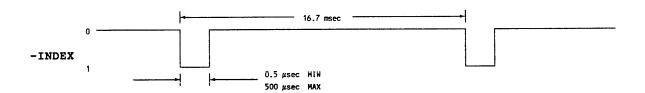

An Index pulse is generated once per disk revolution (nominally every 16.7 milliseconds) to indicate the beginning of a track. This signal is normally high and makes the transition to logical true to indicate Index; see Figure 2-11. Only the transition from high to low (the leading edge) is valid. This signal is available on J1 (gated) and on J2 (ungated).

Figure 2-11. Index Pulse Timing

## SECTOR or ADDRESS MARK FOUND (J1, Pin 16; and J2, Pin 2)

Sector and Address Mark Found are <u>mutually exclusive</u> and thus share the same line. The signal used is determined by the option configuration and is user-selectable by means of jumper W1; refer to Section 3.3.3. These signals are available on J1 (gated) and J2 (ungated).

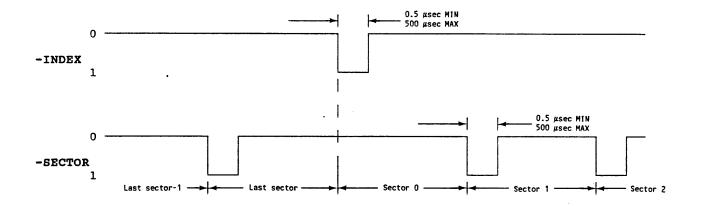

## 1) <u>Sector</u> (Drive Hard Sector)

This optional interface signal indicates the start of a sector. No short sectors are generated. The leading edge of the sector pulses is the only edge that is accurately controlled.

The Index pulse indicates sector zero; see Figure 2-12.

Figure 2-12. Sector Pulse Timing

## 2) Address Mark Found (Controller Soft Sector)

This optional signal indicates the detection of the end of an Address Mark; see Figure 2-13 for timing.

- (1) T1 = 24 bit times minimum.

- (2) Leading edge indicates the location of the end of an address mark.

Figure 2-13. Read Address Mark Timing

COMMAND COMPLETE (J2, Pin 3)

The Command Complete status line permits the host controller to monitor the drive's activity, without selecting the drive.

Command Complete goes false for the following reasons:

- A recalibration sequence is initiated (by drive logic) at power-on if the data heads are not positioned over Track Ø.

- Upon receipt of the first Command Data bit.

The Command Complete signal remains false during the entire command sequence.

## 2.3.3 Data Transfer Signals

All data-transfer lines between the drive and the host system are differential and may not be multiplexed. Four pairs of balanced signals are used to transfer data: NRZ Write Data, NRZ Read Data, Write Clock, and Read/Reference Clock. Figure 2-2 shows the driver/receiver combination used for data-transfer signals.

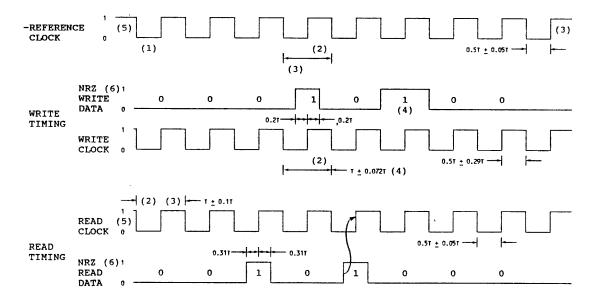

NRZ WRITE DATA (J2, Pins 13 and 14)

The NRZ Write Data pair of signals defines the data to be written on the disk. The data is clocked by Write Clock; see Figure 2-14 for timing.

NRZ READ DATA (J2, Pins 17 and 18)

Read Data is transmitted to the host system via the NRZ Read Data signal pair. The data is clocked by the Read/Reference Clock signal; see Figure 2-14 for timing. These lines are held at a zero level until PLO sync has been obtained and the data is valid.

WRITE CLOCK (J2, Pins 7 and 8)

The Write Clock signal pair is provided by the host controller, at the bit data rate. This clock frequency is dictated by the Read/Reference Clock during the write operation; see Figure 2-14 for timing. Write Clock need not be supplied to the drive continuously, but it should be supplied prior to a write operation and should last for the entire operation.

## 2.3.3 Data Transfer Signals (continued)

READ/REFERENCE CLOCK (J2, Pins 10 and 11)

The timing diagram in Figure 2-14 illustrates the sequence of events (with associated timing restrictions) for proper read/write operation of the 1550-series drives.

The Read/Reference Clock signal from the drive determines the data-transfer rate. The transition from Read Clock to Reference Clock is performed without "glitches," but up to two clock cycles may be missing.

Read/Reference Clock is synchronized to spindle rotation.

- NOTES: (1) All times are in nanoseconds measured at I/O connector of the drive. T is the period of the clock signals and is the inverse of the Reference or Read Clock frequency.

- (2) Similar period symmetry shall be  $\pm 4$  nanoseconds between any two adjacent cycles during reading or writing.

- (3) Except during a head change or PLO synchronization, the clock variances for spindle speed and circuit tolerances shall not vary more than -5.5% to +5.0%. Phase relationship between Reference Clock and NRZ Write Data or Write Clock is not defined.

- (4) Write Clock must be the same frequency as drive-supplied Reference Clock (i.e., Write Clock is the controller-received and retransmitted drive Reference Clock.

- (5) Reference Clock is valid when Read Gate is inactive. Read Clock is valid when Read Gate is active and PLO synchronization has been established.

- (6) See Figure 2-2 for definition of  $\emptyset$  and 1 on these differential signal lines.

Figure 2-14. NRZ Read/Write Data Timings

## 2.4 READ, WRITE, AND FORMAT PARAMETERS

## 2.4.1 Summary of Critical Read-Function Timing Parameters

Controller variations of the read timing are allowed if the following drive-dependent parameters are met:

#### Read Initialization Time

A read operation may not be initiated until 15 microseconds following a head change.

## • Read-Gate Timing

The Read Gate signal may not be enabled or true during a write-splice area. The Read Gate signal must be deactivated 1 bit time minimum before a write-splice area and may be enabled 1 bit time minimum after a write-splice area.

## Read Propagation Delay

Data read at the interface is delayed by up to 9 bit times from the data recorded on the disk.

## Read Clock Timing

Read Clock and Read Data are valid within the number of PLO Sync field bytes specified by the drive configuration after Read Enable and a PLO Sync field is encountered. The Interface Read/Reference Clock line may contain no transitions for up to 2 Reference Clock periods for the transitions between reference and read clocks. The transition period will also be 1/2 a Reference Clock period minimum with no shortened pulse widths.

## 2.4.2 General Summary of Critical Write-Function Parameters

Controller timing variations in the record-update function are allowed if the following drive-dependent write (and interrelated read) timing parameters are met:

#### • Read-to-Write Recovery Time

Assuming head selection is stabilized, the time lapse from deactivating READ GATE to activating WRITE GATE shall be 5 Reference Clock periods minimum.

## Write Clock-to-Write Gate Timing

The Write Clock signal must precede the Write Gate signal by a minimum of 2 1/2 Reference Clock periods.

## 2.4.2 General Summary of Critical Write-Function Parameters (continued)

Write-Driver Plus Data-Encoder Turn-On from Write Gate

The write-driver plus data-encoder turn-on time (write-splice width) is between 3 and 7 Reference Clock periods.

• Write-Driver Turn-Off from Write Gate

To account for data-encoding delays, the Write Gate signal must be held on for at least 2 byte times after the last bit of the information to be recorded.

• Write-to-Read Recovery Time

The time lapse before Read Gate or Address Mark Enable signals can be activated after deactivating the Write Gate signal is 10 microseconds.

• Head-Switching Time

The Write Gate signal must be deactivated at least 1 microsecond before a head change. Write Gate may not be activated until 15 microseconds after a head change or after the Command Complete signal is true.

Reference Clocks Valid Time

The Read/Reference Clock lines will contain valid Reference Clocks within 2 Reference Clock periods after deactivation of the Read Gate signal. Pulse widths will not be shortened during the transition time, but clock transitions may not occur for up to 2 Reference Clock periods.

Read Clocks Valid Time

The Read/Reference Clock line will contain valid Read clocks within 2 Clock periods after establishing PLO synchronization. Pulse widths will not be shortened during the Reference Clock to Read Clock transition time, but missing clocks may occur for up to 2 clock periods.

Write Propagation Delay

Write data received at the I/O connector will be delayed by the Write Data encoder by up to 8 bit times maximum prior to being recorded on the disk.

## SECTION 3. INSTALLATION

## 3.1 PHYSICAL INTERFACE

The electrical interface between the 1550-series drive and the host system is accomplished with five connectors: J1, J2, J3, J4, and J5. The connectors and their recommended mating connectors are described below.

#### 3.2 POWER AND INTERFACE CABLES AND CONNECTORS

Figure 3-1 shows the locations of the power and interface connectors. Pin assignments for connectors J1, J2, and J3 are listed in Section 2.1.

Figure 3-1. Power and Interface Connections

The signal interface connection is made via connectors J1 and J2 on the Device Electronics board. The control cable interconnects the controller and J1; the data cable interconnects the controller and J2.

#### Control Signal Connector J1

J1 is a 34-pin board-edge connector. The signals on this connector control the drive and transfer drive status to the host controller.

Recommended Cable: 3M Scotchflex 3365/34

Mating Connector: AMP 88373-3 (key slot between pins 4 and 6)

### • Data Transfer Connector J2

J2 is a 20-pin board-edge connector. The signals on this connector contain read or write data.

Recommended Cable: 3M Scotchflex 3365/20

Mating Connector: AMP 88373-6 (key slot between pins 4 and 6)

### DC Power Connector J3

J3 is a 4-pin, keyed AMP MATE-N-LOCK connector. This connector supplies DC power (+5V and +12V) to the drive.

Mating Connector: AMP 1-480424-0

Pins: AMP 350078-4

Suggested Wire Size: 18 AWG

### Ground Connectors J4 and J5

3/16-inch spade lugs J4 and J5 are provided for grounding; J4 is on the HDA, and J5 is on the frame. Characteristics of the system determine proper ground connection; refer to Figure 3-1 for the exact location of the connectors.

Mating Connector: AMP 60972-2 or equivalent

### 3.3 DRIVE OPTION SELECTION

## 3.3.1 Drive Addressing and Interface Termination

Figure 3-2 shows the locations of the three Drive Address jumpers (DA1, DA2, and DA3) for Drive Address selection (Drive Addresses 1 through 7) and Interface Terminator Pack RN1 on the Device Electronics board. The drive is configured for Drive Address 1 at the factory. Drive Address 0 is used as a "deselect" (i.e., no drive is selected).

TABLE 3-1. DRIVE SELECT MATRIX

| Drive                             | Select Jumpers                      |                                           |                                           |  |

|-----------------------------------|-------------------------------------|-------------------------------------------|-------------------------------------------|--|

| Address                           | DA3 DA2 DA1                         |                                           |                                           |  |

| 1 *<br>2<br>3<br>4<br>5<br>6<br>7 | out<br>out<br>out<br>in<br>in<br>in | out<br>in<br>in<br>out<br>out<br>in<br>in | in<br>out<br>in<br>out<br>in<br>out<br>in |  |

<sup>\*</sup> The factory default configuration.

The three Drive Select interface lines are decoded to select the correspondingly addressed drive to the host controller/formatter. In multiple-drive systems, each drive must have its own unique address.

Terminator Pack RN1 provides proper termination for the interface lines. When daisy-chaining multiple 1550 drives, the terminator is installed only in the last drive on the daisy chain.

Figure 3-2. Option Jumpers and Interface Terminator

# 3.3.2 Spindle Control Option

Jumper W5 selects the spindle control option.

- When W5 is installed, the drive must wait for a Start Spindle Motor command to start the spindle motor.

- When W5 is not installed (the factory default configuration), the drive automatically starts the spindle motor at power-on.

# 3.3.3 Sectoring Options

Figure 3-2 shows the locations of the four jumpers (W1, W2, W3, and W4) associated with sector configuration options.

Jumper W1 selects hard- or soft-sectored mode.

- When W1 is installed, the drive is configured to operate in the soft sector mode. Address mark generation and detection are enabled, and the Sector/Address Mark Found interface signal is used to report address mark found. Sector size is selected by the host controller.

- When W1 is not installed (the factory default configuration), the drive is configured to operate in the <u>hard sector</u> mode. The Sector/Address Mark Found signal is used to transmit sector pulses to the host controller. Sector pulses are derived from the servo disk. The number of sector pulses generated equals:

INT [

$$\frac{20,832}{n}$$

]

where 20,832 = byte clock derived from servo disk

INT = integer part of

n = the number of bytes/sector (82 minimum)

The number of bytes/sector may be specified using the Set Bytes Per Sector command or by selecting a default sector configuration with option jumpers W2, W3, and W4. Sector configurations may be selected as shown in Table 3-2. Note that the factory default sector configuration is 36 sectors (W2 installed, W3 and W4 not installed).

TABLE 3-2. DEFAULT HARD SECTOR CONFIGURATION WITH JUMPER OPTIONS

| anomona. | BYTES/                | JUMPERS |     |     |     |

|----------|-----------------------|---------|-----|-----|-----|

| SECTORS  | Formatted Unformatted |         | W4  | W3  | W2  |

| 35       | 512                   | 595     | out | out | out |

| 36 *     | 512                   | 578     | out | out | in  |

| 19       | 1024                  | 1096    | out | in  | out |

| 9        | 2048                  | 2314    | out | in  | in  |

| 5        | 4096                  | 4166    | in  | out | out |

| 32       | 512                   | 651     | in  | out | in  |

| 64       | 256                   | 325     | in  | in  | out |

| 1        | 20832                 | 20832   | in  | in  | in  |

<sup>\*</sup> The factory default configuration.

Other hard sector configurations are available; contact Micropolis Product Support (818/709-3300) for details.

## 3.4 DAISY-CHAINING THE 1550 DRIVE

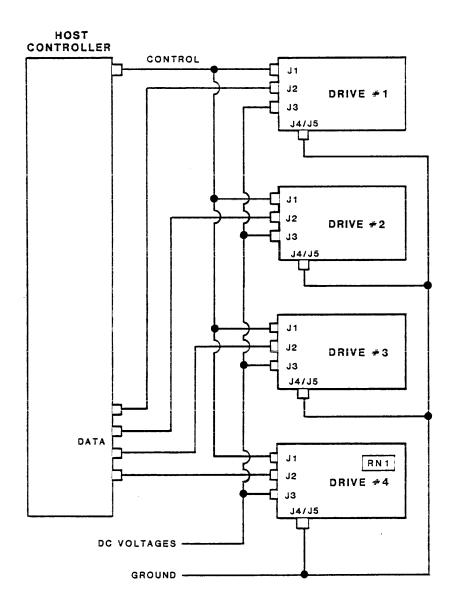

Up to seven 1550-series drives may be connected to a single host controller/formatter. Control signals at J1 are transmitted via standard, daisy-chain interconnection. Data signals at J2 are transmitted via radially connected data-transfer lines.

Figure 3-3 shows the connections for a system configuration using four drives.

NOTE:

- 1) Interface Terminator RN1 is installed only in the last physical drive in the control chain.

- Connectors J4 and J5 are provided for grounding; system characteristics determine the proper ground connection.

Figure 3-3. 1550 Daisy-Chain Configuration

## 3.5 DIMENSIONS AND MOUNTING

The 1550 Series uses industry-standard mounting techniques for 5 1/4-inch Winchester disk drives (the same as for 5 1/4-inch flexible disk drives). Figure 3-4 shows mounting hole locations.

Recommended orientation is vertical on either side, or horizontal with the Device Electronics board down; other mounting orientations may be used provided the ambient air temperature around the drive is kept at or below 50°C (122°F).

Inasmuch as the drive frame acts as a heat sink to dissipate heat from the unit, the enclosure and mounting structure should be designed to allow natural convection of heat around the HDA and frame. If the enclosure is small or natural convection is limited, a fan may be required.

# **CAUTION**

Screws must be selected so that they do not penetrate the bottom mounting holes more than .20 inches and the side mounting holes more than .156 inches. Maximum torque applied to the screws must not exceed 10 in-lbs.

Figure 3-4. Dimensions and Mounting

(Intentionally blank)

# **SECTION 4. POWER REQUIREMENTS**

## 4.1 POWER SUPPLY REQUIREMENTS

DC voltage and current requirements for the 1550 Series are shown below. Voltages may be applied in any sequence during power-up. Voltage verification must be performed at the drive connector. The rise time of the +5V must be less than one second for proper operation of the power-on reset circuits. Figure 4-1 shows the current profile for the +12V.

| Voltage                                              | Star<br>Avg.  | t-up<br>Peak   | Avg.  | lle<br>Peak    | Seeki<br>Avg. |                | Ripple (5)<br>(maximum) |

|------------------------------------------------------|---------------|----------------|-------|----------------|---------------|----------------|-------------------------|

| +5V <u>+</u> 5%<br>maximum: (2)                      | 1.5A          | 1.5A           | 1.5A  | 1.5A           | 1.5A          | 1.5A           | 2%                      |

| +12V <u>+</u> 5% (3)<br>typical: (4)<br>maximum: (2) | 4.25A<br>4.35 | 4.25A<br>4.35A | 1.80A | 1.90A<br>2.10A | 2.25A         | 3.10A<br>3.30A | 2%                      |

TABLE 4-1. DC POWER REQUIREMENTS

- (1) These values are for 1/3-stroke seeks with an 8-millisecond idle period between seeks to simulate a typical system environment.

- (2) Maximum values to be considered for power supply design and system integration.

- (3) +5%, -10% tolerance during start-up.

- (4) Typically measured values.

- (5) Peak-to-peak, includes noise.

DC POWER PIN ASSIGNMENTS (Connector J3)

Voltage \*

Pin | Voltage \*

|          | 1 2      | +12 VDC<br>+12 RETURN | 3<br>4           | +5 RETURN<br>+5 VDC                        |        |

|----------|----------|-----------------------|------------------|--------------------------------------------|--------|

| 5 T Amps |          |                       |                  |                                            |        |

| 4.2      | 25A ((   |                       | _                |                                            |        |

| 3        |          |                       |                  | 3. 1A                                      |        |

| 2        |          | 1.9A                  | t <sub>r</sub> = | 2.0A<br>1<br>600 usec 1<br>(typ) 1         |        |

| 0   0    | art-Up — | Drive Rea             |                  | sec (typ) 26 msec (typ)  — Full Stroke See |        |

| (12      | sec typ) | (Idling)              | ,                | Tall broke bee                             | . (0), |

Figure 4-1. 12V Peak Current Profile (typical, 1558-15)

(Intentionally blank)

# SECTION 5. DATA ORGANIZATION

## 5.1 TRACK FORMAT

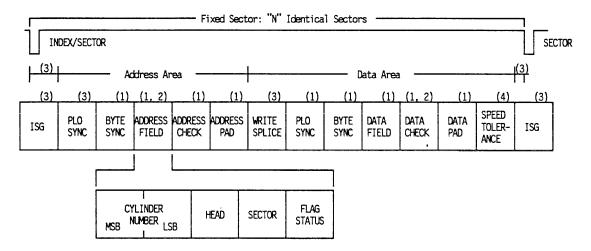

## 5.1.1 Fixed Sector Format

The record format on the disk is under control of the host controller. The Index and Sector pulses are available for use by the controller to indicate the beginning of a track and allow the controller to define the beginning of each sector.

A suggested format for fixed data records is shown in Figure 5-1.

- (1) These areas are examples only and may be structured to suit individual customer requirements.

- (2) The number of check bytes is user defined.

- (3) The PLO SYNC field and ISG are reported in response to Request Configuration commands:

- ISG is 16 bytes minimum (12 bytes after Index, 4 bytes before Index).

- PLO SYNC is 11 bytes minimum.

- (4) Not required for the 1550 Series.

Figure 5-1. Fixed Sector Format

The format presented in Figure 5-1 consists of three functional areas:

- Intersector Gap

- Address Area

- Data Area

The Data Area is used to record the system's data files. The Address Area is used to locate and verify the track and sector location on the disk where the Data Areas are to be recorded.

# 5.1.1 Fixed Sector Format (continued)

### Intersector Gap

The Intersector (ISG) Gap provides a separation between each sector. The minimum number of bytes in the Intersector Gap field is 16 (4 bytes before Index and 12 bytes after Index). The Intersector Gap size is chosen to provide for:

- Write-to-read recovery time (minimum, drive-required time between Write Gate deassertion and Read Gate assertion).

- Drive-required head-switching time.

- Host controller decision-making time between sectors.

- Other drive-required ISG times.

- Variations in detecting Index.

### Address Area

The Address Area provides a positive indication of the track and sector locations. The Address Area is normally read by the host controller, and the address bytes verified prior to a Data Area read or write. The Address Area is normally only written by the controller during a format function, and thereafter only read to provide a positive indication of the sector location and establish the boundaries of the Data Area. The Address Area consists of the following bytes:

# a. PLO Sync Field (11 bytes minimum)

PLO Sync Field bytes are required by the drive to allow the drive's read-data, phase-locked oscillator to become phase-and frequency-synchronized with the data bits recorded on the media. The host controller should send zeros during this time. The number of bytes required may be determined by the Request Configuration command; see Section 2.3.1, Command Code 0011. The minimum number of bytes in the field is 11.

## b. Byte Sync Pattern (1 byte minimum)

This byte establishes byte synchronization (the ability to partition the ensuing serial bit stream into meaningful information groupings, such as bytes) and indicates to the host controller the beginning of the address field information. It is recommended that the Byte Sync Pattern contain the hexadecimal pattern FE.

# 5.1.1 Fixed Sector Format (continued)

### c. Address Field

The Address Field bytes are user-defined and interpreted by the host controller. A suggested format consists of five bytes, which allows two bytes for the cylinder address, one byte for the head address, one byte for the sector address, and one byte for flag status.

# d. ADR Check Bytes (Address Field Check Codes)

An appropriate error-detection mechanism is generated by the host controller and applied to the address for file integrity purposes. These codes are written on the media during formatting. The controller maintains data integrity by recalculating and verifying the check codes when the address field is read. ADR Check Bytes are user defined.

# e. ADR Pad (2 bytes minimum) - (Address Field Pad)

The Address Field Pad bytes must be written by the host controller and are required by the drive to ensure proper recording and recovery of the last bits of the address-field check codes. These pad bytes should be zeros.

#### Data Area

The Data Area is used to record data fields. The contents of the data fields within the Data Area are specified by the host system. The remaining parts of the Data Area are specified and interpreted by the host controller to recover the data fields and ensure their integrity. The Data Area consists of:

# a. Write Splice (1 byte minimum)

The Write Splice is required by the drive to allow time for the write drivers to turn on and reach recording amplitude sufficient to ensure data recovery. Allowance should be made for this byte in the format, and the controller should send zeros during this time.

# b. PLO Sync Bytes (11 bytes minimum)

PLO Sync bytes are required when reading data to allow for the drive's phase-locked oscillator (PLO) to become phaseand frequency-synchronized with the data bits recorded on the media.

# 5.1.1 Fixed Sector Format (continued)

The host controller should send zeros during these byte times. The number of bytes required may be determined by the Request Configuration command; refer to Section 2.3.1, Command Code 0011. The minimum number of bytes in the field is 11.

## c. Byte Sync Pattern (1 byte minimum)

The Byte Sync Pattern establishes byte synchronization and indicates the beginning of the data field to the host controller.

It is recommended that the Byte Sync Pattern contain the hexadecimal pattern FE.

### d. Data Field

The Data Field contains the host system's data files.

# e. Data Check Bytes (Data Field Check Codes)

The Data Check bytes are generated by the host controller and are written on the media at the end of the Data Field. Data integrity is maintained by the controller recalculating and verifying the Data Field Check Codes or applying error correction algorithms, if applicable, when the Data Field is read.

The Data Check Field is user defined.

# f. Data Pad (2 bytes minimum) - (Data Field Pad)

The Data Pad bytes must be issued by the host controller. The pad is required by the drive to ensure proper recording and recovery of the last bits of the Data Field Check Codes.

The controller should send zeros during these byte times.

## g. Format Speed Tolerance Gap

The Format Speed Tolerance Gap is not required. This is due to the fact that the Read/Reference clock is synchronized to the rotation of the disk by the servo phase-locked loop. The number of clocks between sector or index pulses is fixed and independent of spindle speed variation.

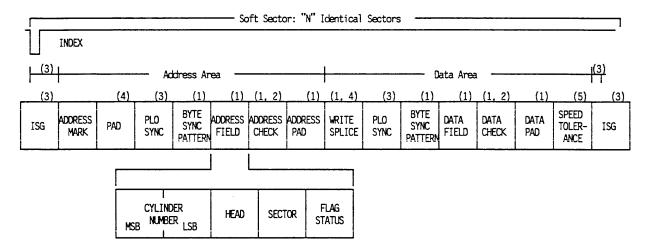

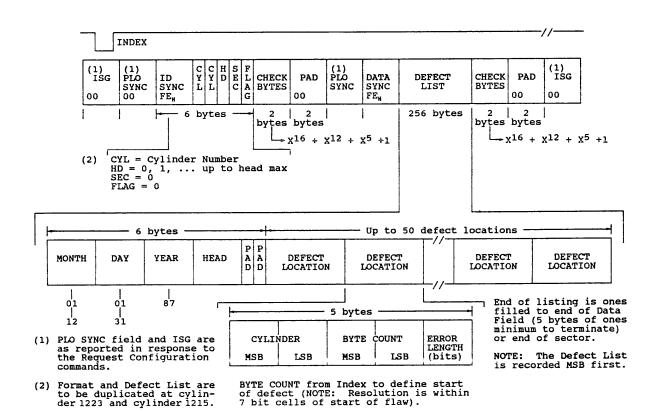

## 5.1.2 Soft Sector Format

The format shown in Figure 5-2 is similar to the format commonly used for hard sector drives and indicates minimum requirements.