mips

### M/120 RISComputer Technical Reference

Order Number 3112DOC

September 1988

Your comments on our products and publications are welcome. A postage-paid form is provided for this purpose on the last page of this manual.

#### © 1988 MIPS Computer Systems, Inc. All Rights Reserved.

RISCompiler and RISC/os are Trademarks of MIPS Computer Systems, Inc. UNIX is a Trademark of AT&T Bell Laboratories. Ethernet is a Trademark of XEROX.

Ada is a registered trademark of the U. S. Government (Ada Joint Program Office.) VADS and Verdix are registered trademarks of the Verdix Corporation.

APSO and GVAS is a trademark of the Verdix Corporation

MIPS Computer Systems, Inc. 930 Arques Ave. Sunnyvale, CA 94086.

Customer Service Telephone Numbers:

California:

(800)

992-MIPS

All other states:

(800)

443-MIPS

International:

(415)

330-7966

This book provides information on the MIPS M/120 RISComputer System, a 32-bit, multiuser, UNIX system. The M/120 uses the R2000 processor and is based on the MIPS RISC (Reduced Instruction Set Computer) architecture.

### **Audience**

This book should be read by anyone who needs to unpack, setup, operate, write programs for, or interface devices to the M/120 RISComputer.

## **Topics Covered**

This book contains the following chapters:

- Chapter 1, System Overview. Gives an overview of capabilities and features of the system.

- Chapter 2, Installation. Describes the installation instructions for the M/120 RISComputer System.

- Chapter 3, Programming Model. Provides a system programmer's view of the M/120 System. Defines the system memory map, the interrupt system, and the purpose of the system's configuration and status registers. Also summarizes the addresses and functions of programmable registers provided by the devices in the M/120's I/O subsystem.

- Chapter 4, Writing Device Drivers. Describes the specific information needed by programmers writing and installing device drivers for the M/120 under the RISC/os™ (UMIPS) operating system.

- Chapter 5, PROM Monitor. Describes the PROM Monitor

which provides the tools for examining and changing memory,

downloading programs over serial lines (RS-232C), and booting

programs from disk, tape, or Ethernet. The PROM Monitor also

provides tools for altering power-up configuration options in

non-volatile RAM.

- Appendix A, AT Bus Compatibility Considerations. Describes the system's implementation of the AT bus interface and includes details of the configuration options available.

- Appendix B, Tape Drive Operation and Maintenance. Describes the operating procedures for the standard cartridge tape drive and the maintenance considerations for the drive.

- Appendix C, Installing Disk Drives in the Expansion Cabinet. Describes how to install disk drives in the optional expansion cabinet that can be added to the M/120 system.

- Appendix D, Power On Diagnostics. Describes the built—in diagnostic program that is executed when the system is powered up.

- Appendix E, Sample Driver Listing. Contains a listing for a sample device driver program.

- Appendix F, Standalone Programs. Describes the *format* and *sash* standalone programs.

- Index. Contains index entries for this publication.

### For More Information

The following publications contain additional information that you may need as you use the M/120 RISComputer:

- MIPS RISC Architecture, Prentice-Hall ISBN0-13-584749-4

- MIPS Language Programmer's Guide 02–00035

- MIPS Assembly Language Programmer's Guide 02-00036

- RISC/os (UMIPS) System Administrator's Guide 02–00136

## **Contents**

| Chapter 1<br>System Overview |                                               |            |

|------------------------------|-----------------------------------------------|------------|

| System Overview              | T 1                                           | 1–1        |

|                              | Introduction                                  | 1-1<br>1-1 |

|                              | System Description  Motherhound               | 1-3        |

|                              | Motherboard                                   | 1-3        |

|                              | Central Processing Unit                       | 1-5        |

|                              | System Memory                                 | 1-6        |

|                              | AT Bus Slots                                  | 1–6        |

|                              | Packaging                                     | 1-6        |

|                              | Peripherals  Cantalla Switches and Indicators | 1-0        |

|                              | Controls, Switches, and Indicators            | 1-7        |

|                              | Expansion Cabinet Specifications              | 1-9        |

|                              | Specifications                                | 1-9        |

| Chapter 2                    |                                               |            |

| Installation                 |                                               |            |

|                              | Site Selection                                | 2–1        |

|                              | Space Requirements                            | 2–1        |

|                              | Power Requirements                            | 2–3        |

|                              | Environmental Requirements                    | 2–4        |

| •                            | Select the Voltage                            | 2–5        |

|                              | Install Additional or Optional PC Cards       | 2–7        |

|                              | Removing the Side Panel                       | 2–7        |

|                              | Install Additional Memory Cards               | 2–8        |

|                              | Install Optional AT Cards                     | 2–9        |

|                              | Reinstall the Side Panel                      | 2–10       |

|                              | Install Serial I/O Devices                    | 2–11       |

|                              | General Considerations                        | 2–11       |

|                              | Terminal Connector Pinouts                    | • 2–12     |

|                              | Connecting the Console                        | 2–13       |

Connecting Other Serial I/O Devices

Cable the System to an Ethernet Network

Power Up the M/120 System

2–13

2-15

2-16

# 3 Programming Model

| Signal and Bit Naming Conventions             | 3–2  |

|-----------------------------------------------|------|

| Data Formats and Addressing                   | 3–2  |

| System Memory Map                             | 3–3  |

| Interrupt System                              | 3–6  |

| Interrupt Level-0                             | 3–7  |

| Interrupt Status Register (ISR)               | 3–7  |

| Interrupt Mask Register                       | 3–8  |

| Memory Fault Handling                         | 3–8  |

| Fault ID Register (FID)                       | 3–9  |

| Fault Address Register (FAR)                  | 3–11 |

| System Configuration Register                 | 3–12 |

| Direct Memory Access (DMA)                    | 3–14 |

| DMA Controller Operating Modes                | 3–15 |

| DMA Controller Interface Registers            | 3–15 |

| DMA Software Control                          | 3–16 |

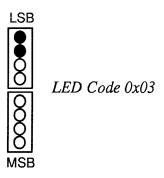

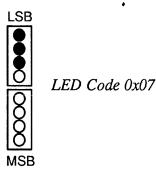

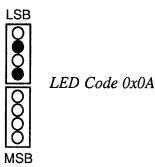

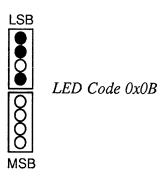

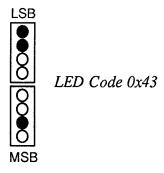

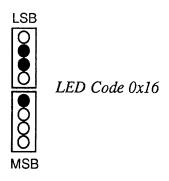

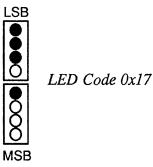

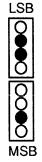

| LED Register                                  | 3–17 |

| The ID PROM                                   | 3–17 |

| I/O Subsystems                                | 3–18 |

| Counter/Timer                                 | 3–18 |

| Counter/Timer Interrupt Acknowledge Registers | 3–19 |

| Counter/Timer Register Summary                | 3–19 |

| Real-Time Clock & NVRAM                       | 3–20 |

| Serial Ports                                  | 3–21 |

| SCSI Interface                                | 3–23 |

| SCSI Controller Registers                     | 3-24 |

| SCSI Operation Details                        | 3–25 |

| Ethernet Interface                            | 3–25 |

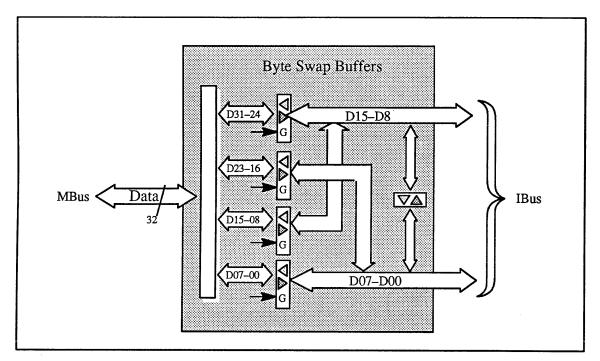

| AT Bus Interface                              | 3–26 |

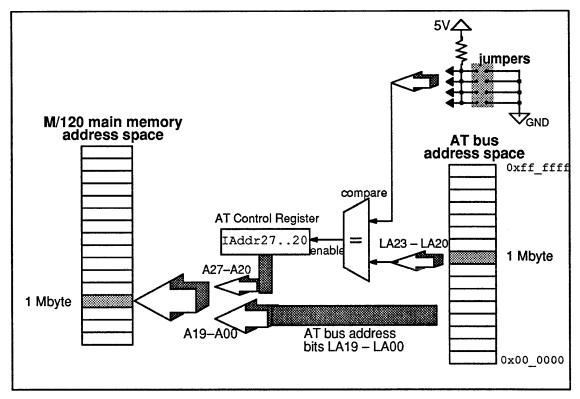

| AT Bus Memory Access and Control              | 3–26 |

| AT Bus Memory Mapping                         | 3–26 |

| AT Bus Byte Swapping                          | 3–27 |

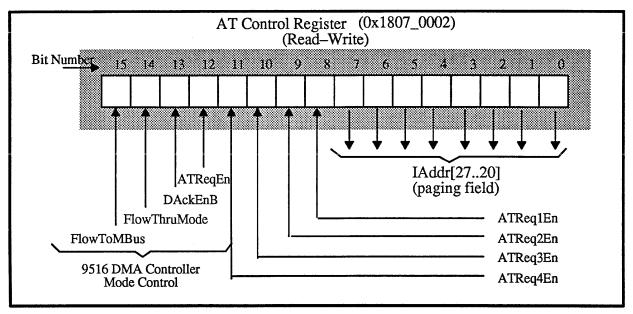

| AT Bus Control Registers                      | 3–28 |

| AT Control Register                           | 3–28 |

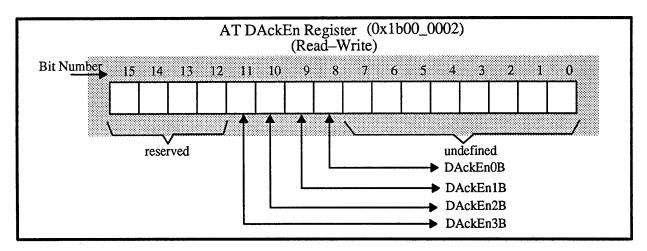

| AT DAckEn Register                            | 3-30 |

# Chapter 4 Writing Device Drivers

| Introduction                                         | 4–1        |

|------------------------------------------------------|------------|

| File Structure of the Kernel Subset The io Directory | 4–1<br>4–2 |

| The master.d Directory                               | 4–2        |

| The bootarea Directory                               | 4–3        |

| AT&T and MIPS Reconfiguration Differences            | 4–3        |

| AT&T's Reconfiguration Process                       | 4–3        |

| MIPS' Reconfiguration Process                        | 4–3        |

| Adding New Drivers                                   | 4-4        |

| Set Your Environment Variable                        | 4-4        |

| Compile Your Driver                                  | 4–5        |

| Create a Master File                                 | 4–5        |

| Copy and Rename the Kernel and Sygen Files           | 4–6        |

| Modify the New Kernel File                           | 4–6        |

| Modify the New Sysgen File                           | 4–6        |

| Build the Kernel                                     | 4–7        |

| M/120 Machine Considerations                         | 4–7        |

| The AT Bus                                           | 4–7        |

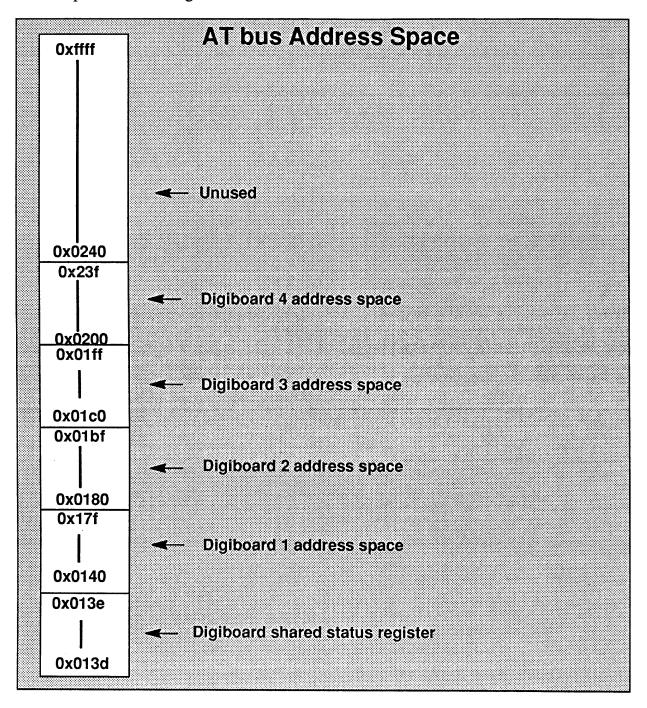

| AT Bus Address Space                                 | 4–8        |

| Kernel Support Routines                              | 4_9        |

| Delay(n) Macro                                       | 4_9        |

| Address Translation                                  | 4-9        |

| Interrupt Priority Level Assignment                  | 4–10       |

| Changing Interrupt Levels                            | 4–11       |

| Kernel/PROM Interface                                | 4–11       |

| Memory Management                                    | 4-12       |

| Volatile Memory and Optimizing Compilers             | 4-12       |

| Write Buffer Considerations                          | 4–13       |

| SCSI Devices                                         | 4–14       |

| Debugging Drivers                                    | 4-15       |

| Halting the System                                   | 4–15       |

| System Error Messages                                | 4-15       |

# Chapter 5 PROM Monitor

| Introduction                     | 5–1  |

|----------------------------------|------|

| Description                      | 5–1  |

| Memory Usage                     | 5–1  |

| File Name Syntax                 | 5–2  |

| Environment Variables            | 5–3  |

| Input Editing                    | 5–4  |

| Time of Day and Non-Volatile RAM | 5–5  |

| Using Breaks to Change Baud Rate | 5–5  |

| Extending the PROM Monitor       | 5–5  |

| Command Set                      | 5–6  |

| auto                             | 5–7  |

| boot                             | 5–8  |

| cat                              | 5–9  |

| disable                          | 5–10 |

| dump                             | 5–11 |

| enable                           | 5–13 |

| fill                             | 5–14 |

| g                                | 5–15 |

| go                               | 5–16 |

| help                             | 5–17 |

| init                             | 5–18 |

| init_tod                         | 5–19 |

| load                             | 5–20 |

| p                                | 5–22 |

| printenv                         | 5–22 |

| pr_tod                           | 5–23 |

| setenv                           | 5–24 |

| sload                            | 5–25 |

| spin                             | 5–26 |

| unsetenv                         | 5–27 |

| warm                             | 5–28 |

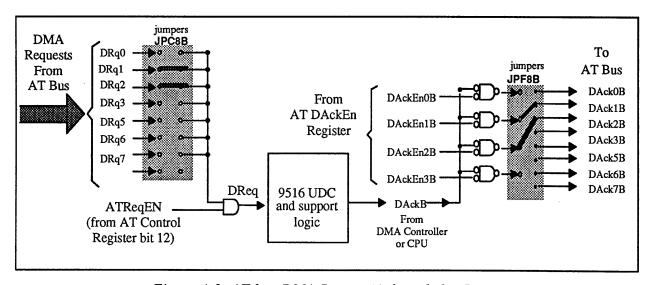

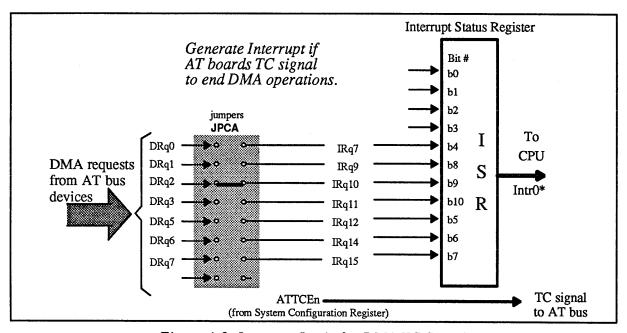

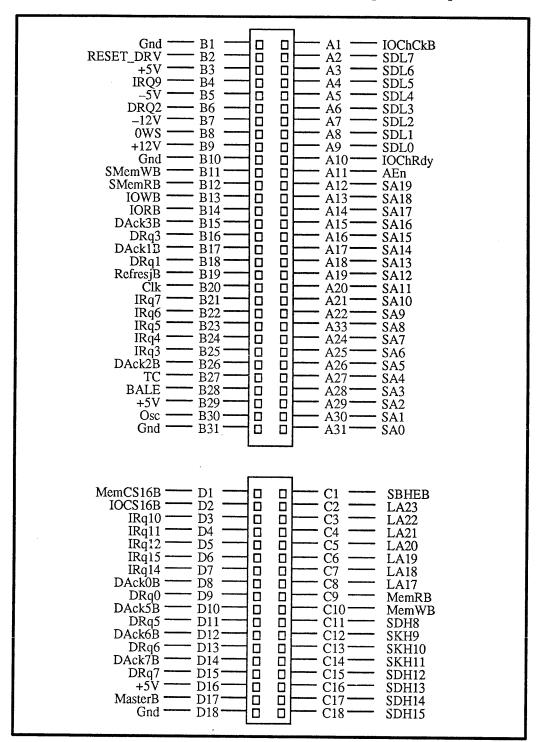

#### Appendix A AT Bus Compatibility Considerations A-1Memory Mapping Options A-3AT Bus Memory Refresh A-3 **Device Drivers** A-3Connectors A-3**Bus Timing DMA** Operations A-3DMA Request and Acknowledge Options A-4DMA Terminal Count (TC) Signal A-5AT Bus Interrupts A-6 A-7 Alternate Controllers A-7 Bus Access Control for Alternate Controllers A-8 AT Bus Option and Jumper Summary AT Bus Pin and Signal Assignments A - 11Appendix B Tape Drive Operation and Maintenance B-1Operation B-2Maintenance Appendix C Installing Disk Drives in the Expansion Cabinet Appendix D Power On Diagnostics D-1Introduction D-5 Pon\_Leds D-5Pon\_Duart D-6 Pon\_Banner D-6 Pon\_Cache1 D-7 Pon\_Cache2 D-8 Pon Cache3 D-8 Pon\_Cache4 D-9 Pon\_IdProm D-9 Pon\_WB Pon\_Memory D-10 Pon\_Scr D-10 D-11 Pon\_VM D-12 Pon Allexc Pon\_Parity D-13

Pon\_NVram

Pon\_Timers

D-14

D-15

|              | Pon_Duarts                     | D-16 |

|--------------|--------------------------------|------|

|              | Pon_Imr                        | D-17 |

|              | Pon_Fp1 and Fp2                | D-17 |

|              | Pon_UdcSlave                   | D-18 |

|              | Pon_Chain1                     | D-19 |

|              | Pon_Chain2                     | D-20 |

|              | Pon_ScsiSlave                  | D-20 |

|              | Pon_ScsiMaster                 | D-21 |

|              | Pon_EnetProm                   | D-22 |

|              | Pon_LanceSlave                 | D-22 |

|              | Pon_LanceMaster                | D-23 |

|              | Pon_Atreg                      | D-24 |

| Appendix E   |                                |      |

| Sample Driv  | per Listing                    |      |

|              | The C8.c Driver Program        | E-1  |

|              | The Header file ss.h           | E-22 |

|              | The SS.c Library               | E-24 |

| Appendix F   |                                |      |

| Standalone 1 | Programs                       |      |

|              | Introduction                   | F-1  |

|              | Format                         | F-3  |

|              | Format Desription              | F-3  |

|              | Additional Format Information  | F-8  |

|              | Standalone Shell (sash)        | F-10 |

|              | Extending the Standalone Shell | F-10 |

|              | Sash Commands                  | F-10 |

|              | cp (copy)                      | F-12 |

# Chapter 1 System Overview

### Introduction

This chapter describes the M/120 RISComputer System, which is a 32-bit, multi-user, UNIX system. The M/120 uses the R2000 processor and is based on the MIPS RISC (Reduced Instruction Set Computer) architecture. The M/120 is a high-performance UNIX system, which is suitable for use as a departmental minicomputer or as a compute server in a networked environment.

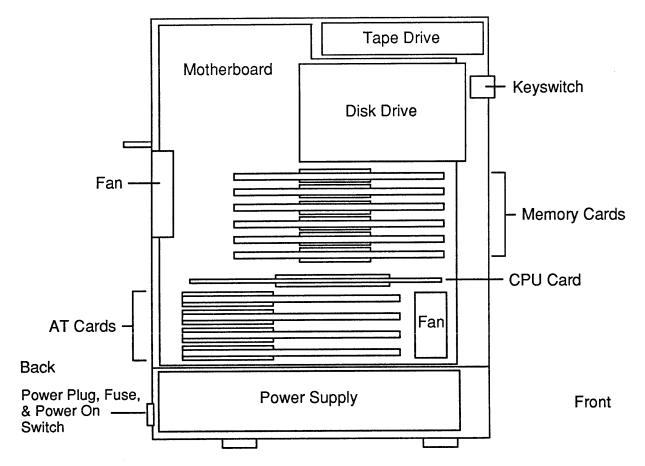

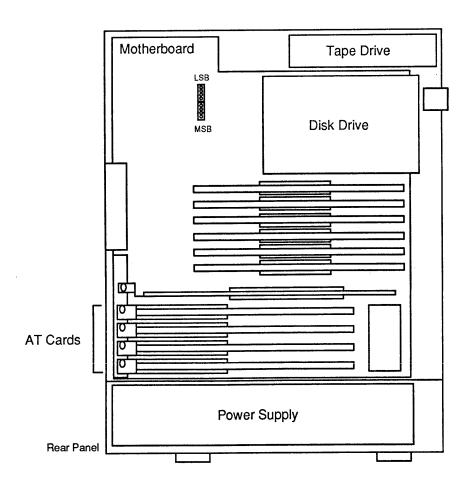

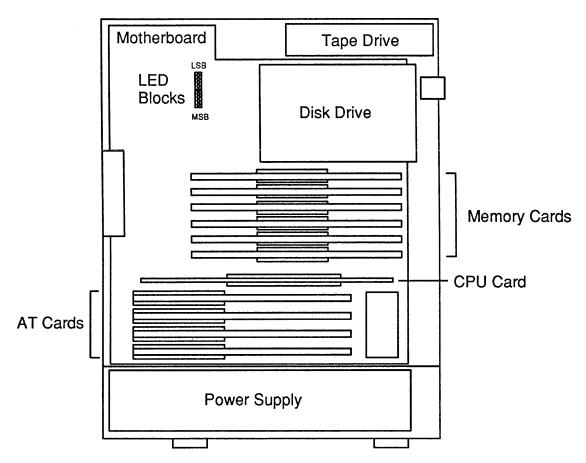

The M/120 is packaged in an upright enclosure that includes a power supply. A Motherboard supports card slots for the CPU and multiple memory cards that transfer data over a proprietary bus. In addition, there are four IBM PC/AT-compatible card slots for I/O expansion and additional connectivity. The system includes four RS-232C serial I/O ports, an Ethernet controller and port, and a Small Computer Systems Interface (SCSI) controller and port. The main enclosure houses a 5 1/4 inch Winchester disk drive and a cartridge tape drive. Up to five additional disk drives can be added to the system using the side-by-side Expansion Cabinet. Figure 1.1 on the following page shows the physical location of the system components.

The software for the M/120 includes a tailored UNIX V, Release 3 called RISC/os (also known as UMIPS). Included with RISC/os are the assembler, the C and Pascal optimizing compilers, symbolic debugger, linkage editor, and various profiling and development tools. The system tools include such items as an archiver, a build tool, a symbol table, and a disassembler.

RISC/os also includes Sun Microsystem's Network File System (NFS), which is a powerful network file interchange medium for the wide range of systems that support NFS. With NFS, you can integrate the M/120 System into heterogeneous computing environments.

### **System Description**

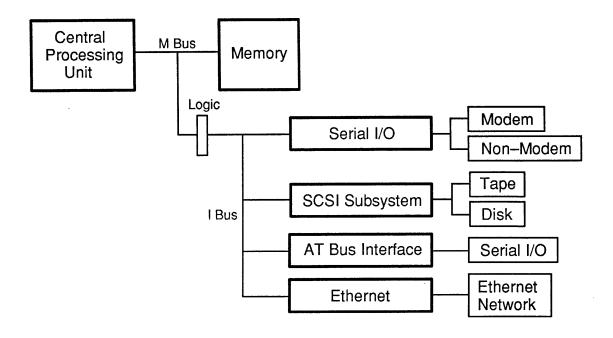

The minimum system configuration includes the subassemblies given in the following list. These subassemblies are shown in Figure 1.2 on the following page.

- Motherboard

- Central Processing Unit

- System Memory

- AT Bus Slots

- Packaging

- Peripherals

- Controls, Switches, and Indicators

Figure 1.1. M/120 System Components (Left Side View)

Figure 1.2. M/120 System Block Diagram

### Motherboard

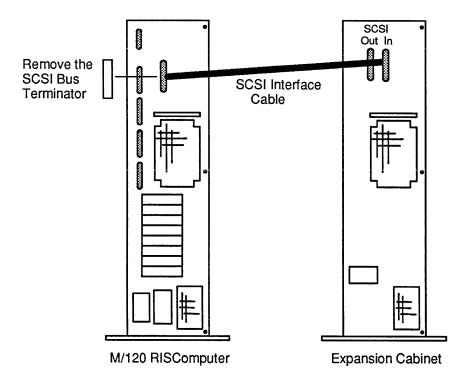

The Motherboard contains a Small Computer Systems Interface (SCSI) as defined by the ANSI X3T9.2 committee. This interface supports up to seven target devices in asynchronous, synchronous, or mixed modes with DMA data transfers. The SCSI logic is brought out to an external connector that allows the integration of up to five additional SCSI devices in an Expansion Cabinet.

The Motherboard incorporates logic for the Lance Ethernet controller that supports the IEEE 802.3 Ethernet standard. The Lance Ethernet hardware implementation consists of the Am7990 Local Area Network controller and the Am7992A Serial Interface Adapter. The Ethernet controller functions in a memory—mapped I/O mode for efficient networking operation. This configuration supports full Ethernet only. It does not support Cheapernet.

The main memory controller on the Motherboard supports up to six, 8-megabyte memory array boards, which plug into the Motherboard memory slots.

The PC/AT bus interface on the Motherboard supports both slave and master type AT cards. The M/120 has four full size AT card slots that can be used for adding peripherals to the system. The Motherboard also contains EPROMs for boot code and power—up diagnostics, and system clocks.

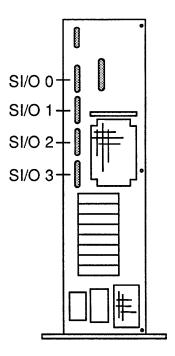

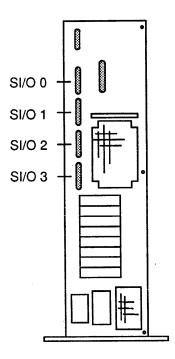

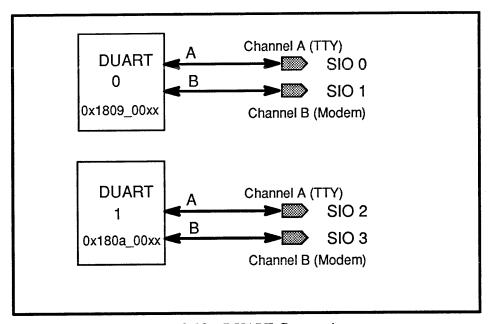

The Motherboard contains two DUARTS that support four RS-232C ports. The serial I/O ports (ports 0-3) are located on the rear panel of the computer. Refer to Figure 1.3 on the following page. Ports 1 and 3 support full modem control for connecting modems and printers. These ports may be used as a download facility. Ports 0 (zero) and 2 are configured for terminal equipment and are suitable for a console. All four ports are Data Terminal Equipment (DTE) configured. Connection to terminal equipment requires a null modem connector.

### **Central Processing Unit**

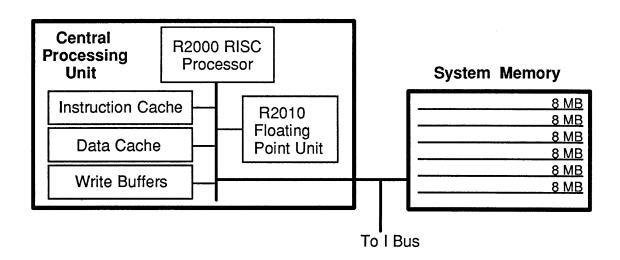

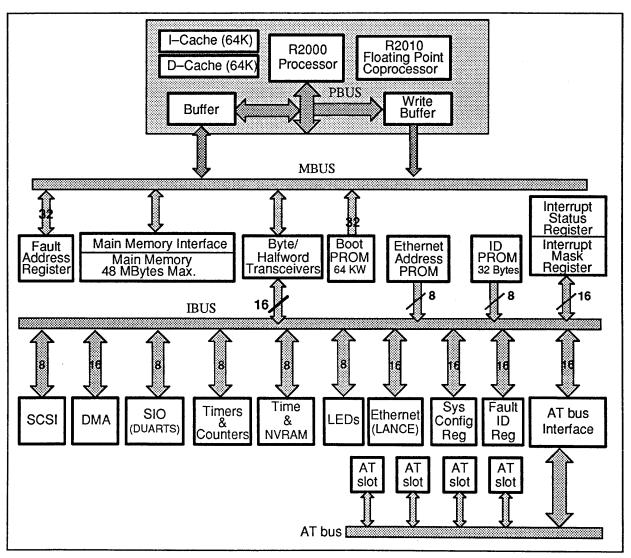

The Central Processing Unit (CPU) is located on a separate printed circuit board module, which plugs into the Motherboard. There are two different CPU modules available: the one used in the M/120–3 has a 12.5 MHz CPU clock speed, and the version used in the M/120–5 has 16.7 MHz CPU clock speed. The CPU module is the core processor in the M/120 System. It includes the R2000 RISC Processor, the R2010 Floating Point coprocessor, a 64K byte Instruction Cache, a 64K byte Data Cache, and the R2020 Write Buffers. Figure 1.4 on the following page is a block diagram of the CPU module.

Figure 1.3. Location of Serial Ports (M/120 Rear View)

Figure 1.4. Central Processing Unit

The R2000 processor is a full-custom, 32-bit CMOS microprocessor based on the Reduced Instruction Set Computer (RISC) technology. The R2000 processor design uses only simple load/store operations for memory access and utilizes large caches for speed and efficiency. The custom CMOS processor combines two tightly coupled units on a single chip. The CPU executes instructions directly without microcode, and the memory management unit provides virtual memory and exception handling mechanisms needed for the efficient support of multiuser operating systems.

The R2010 Floating Point Unit (FPU) is an M/120 option. The CPU Module can be ordered without the Floating Point Unit, but unless specified, the Floating Point Unit is included. The R2010 FPU operates in conjunction with the R2000 processor and extends the R2000's instruction set to perform arithmetic operations on values in floating—point representations. The FPU executes instructions in parallel with the CPU, and most floating point instructions can execute or load/store during the same single cycle instruction executions as the CPU. The R2010 FPU contains sixteen 64—bit registers that each can hold data for single or double precision calculations. The R2010 FPU, with associated system software, fully conforms to the requirements of ANSI/IEEE Standard 754—1985, "IEEE Standard for Binary Floating—Point Arithmetic."

The M/120 CPU Instruction Cache and Data Cache each provide 64K bytes of high-speed memory that allow the processor to operate at maximum speed.

The CPU module incorporates four write buffer devices that enable the M/120 CPU to perform write operations at full speed, avoiding memory write time delays. The write buffers provide 4—deep buffering of 32—bit address and data words. Byte and half—word gathering of data is incorporated to reduce write accesses to main memory for full words where possible.

### **System Memory**

The main memory controller is contained on the Motherboard and integrates a synchronous high-speed main memory bus with the CPU Module. Peak memory bandwidth is 11 megabytes per second for reads and 16 megabytes per second for writes. This controller logic supports up to six R2450 Memory Cards, which each contain 8 megabytes of memory. Refer to Figure 1.4. The Memory Cards plug into the Motherboard as daughter boards for main memory expansion. The system can be configured to contain from 8 megabytes (minimum configuration) to 48 megabytes (maximum configuration) of system memory. Both the controller and the R2450 cards support byte parity.

Each R2450 Memory Card contains 8 megabytes of memory implemented with 1 Mbit DRAMs, plus the additional DRAMs required for parity memory. The first four R2450 card slots are bus-compatible, identical, and reserved for R2450 Memory Cards only. The last two slots can be used for either R2450 Memory Cards or for special function cards. A special bus master can be plugged into either of these two slots, but not both. The M-bus arbitor supports only one additional master.

The physical address space that is occupied by any given Memory Card is card—slot address-able on 8 megabyte boundaries. Each Memory Card slot is associated with a unique 8 megabyte address space. Therefore, the additional Memory Cards do not require jumper blocks for specifying the base memory address.

### **AT Bus Slots**

The M/120 features system expandability through the IBM PC/AT Bus Interface. This four slot bus is designed to support virtually any card that works in a PC/AT or compatible machine.

The AT Bus Interface supports both slaves and masters. A PC/AT slave can be accessed directly by the M/120 CPU as a memory mapped I/O device. A slave can transmit data to or receive data from the main memory via a single DMA channel. A PC/AT master can directly write to or read from a one megabyte address space of the M/120 main memory through mapping hardware. For additional information on the AT Bus compatibility considerations, see Appendix A.

The M/120 can access the full 16 megabyte AT address space as mapped into the M/120 main memory. Control registers set the mode of operation on the AT bus.

A large number of vendors offer AT bus controllers. These are normally supplied with MS–DOS, OS/2, or Xenix device driver software. When implementing a selected AT controller in the M/120, the device driver will usually have to be modified or completely rewritten to run on the M/120's R2000 processor with RISC/os, which is the MIPS port of the UNIX operating system. Refer to Chapter 4, Writing Device Drivers, for additional information.

### **Packaging**

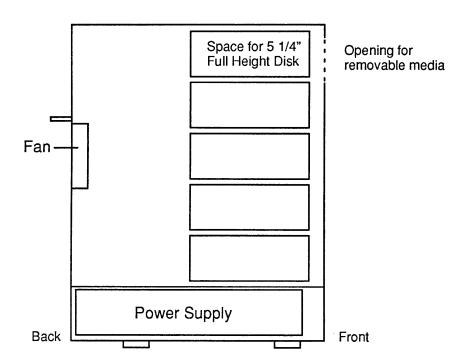

The 400 watt power supply for the M/120 is mounted at the bottom of the system enclosure. It is switch selectable for worldwide AC power type compatibility. Air flow is from front to rear, with internal baffles to provide even cooling.

AT card cutouts are provided so that normal I/O connections can be made to them from the lower rear part of the system cabinet. Connectors for the four integral console and serial I/O ports, Ethernet, and the SCSI bus are also located on the rear panel.

One 5 1/4 inch SCSI disk is mounted in the main system cabinet. A 120 megabyte cartridge tape is also mounted in the cabinet at the top for operator convenience. The left side exterior panel is removable for access to all interior parts.

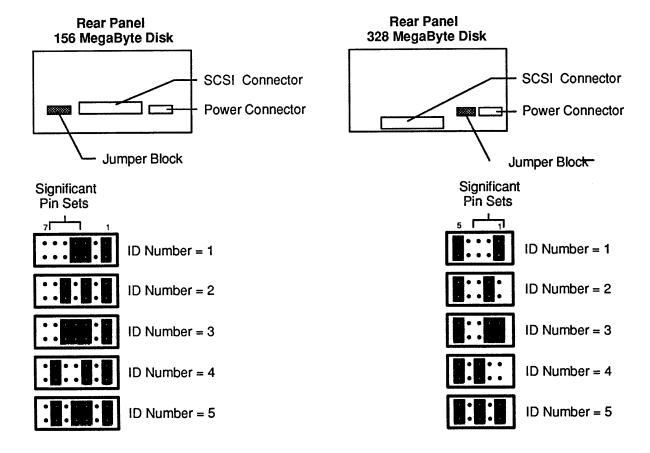

### **Peripherals**

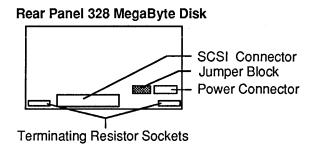

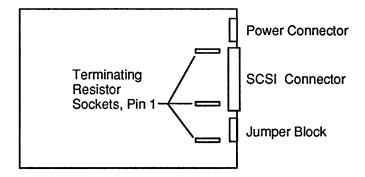

There are two different Disk Drive capacities available for the M/120: a 328 megabyte Disk Drive and a 156 megabyte Disk Drive. The base configuration consists of a 328 megabyte formatted 5 1/4 inch, embedded SCSI Disk Drive. The 328 megabyte Disk Drive has an average access time of 16.5 ms and supports synchronous transfer rates to 4 megabytes per second. The 328 megabyte Disk Drive also incorporates a read look—ahead algorithm that maximizes sequential UNIX file system read performance. The drive consumes 27 watts of power (steady state) and its actuator and spindle motor design provide quiet operation.

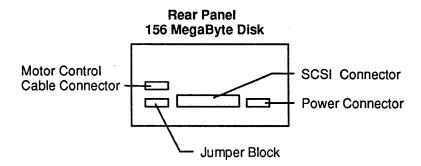

For applications requiring a smaller capacity, the M/120 is also available with a 5 1/4 inch Disk Drive that provides 156 megabytes of formatted storage. This Disk Drive has an average access time of 16.5 ms and has an asynchronous SCSI bus transfer rate of 1.25 megabytes per second. The 156 megabyte Disk Drive consumes 27 watts of power.

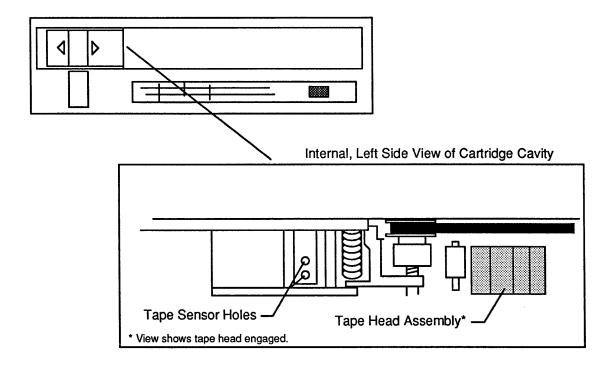

A Quarter Inch Cartridge (QIC) Tape Drive for software distribution and backup purposes is also included in the base M/120 configuration. The standard Tape Drive for the M/120 is the high capacity 120 megabyte configuration (QIC–120). A 60 megabyte configuration supporting the QIC–24 format (QIC–11 read only) is also available. Both Tape Drives have an embedded SCSI interface that operates at 1.25 megabytes per second asynchronous. The Tape Drives are 5 1/4 inch half—height units that support 90 kilobytes per second sustained while streaming. Power consumption for both Tape Drives is 25 watts while in operation. For information on the Tape Drive operation and for preventative maintenance instructions, see **Appendix B**.

### Controls, Switches, and Indicators

The M/120 controls, switches, and indicators are listed below.

- Keyswitch

- Power On Switch

- Power On LED

- Disk Drive LED

- Tape Drive LED

- Head Loading Lever

The **Keyswitch** has three positions: lock, unlock, and reset. The key is removable in both the lock and the unlock positions. The three keyswitch positions are defined as follows.

Lock When the key is in the bottom or lock position, the system cannot be booted if the power is on and the system is at the PROM Monitor. This position also prevents the system from being shutdown and places restraints on operating system Run state transitions. Refer to the Telinit man page, telinit (1m), for additional information.

Unlock When the key is in the middle or unlock position, the system can be booted when the power is on and the system is at the PROM Monitor prompt. The system can also be shut down when the key is in the unlock position and root or the superuser is the initiator of the shutdown.

Reset The top position is a momentary switch and causes a system reset. The Power On Diagnostics are not run when this reset is used.

The **Power On Switch** is located on the rear panel of the computer adjacent to the power cord connection. When the Power On Switch is set to the ON position while the Keyswitch is in th Unlock position, then the Power On diagnostics are performed. (If the bootmode variable is

not set to d, then the Power On diagnostics are not performed. See Chapter 5, PROM Monitor for a discussion of the boodmode variable.)

There are three LEDs on the front panel of the computer: the Power On LED, the Disk Drive LED, and the Tape Drive LED. The Power On LED indicates that the power is on. The Disk Drive LED flickers when the Disk Drive is active. The Tape Drive LED comes on when a cartridge is inserted and the tape is not at the load point or end of tape. The Tape Drive LED stays on until the tape is rewound to the Load Point by a REWIND command. Normally, the cartridge should only be removed when the LED is off.

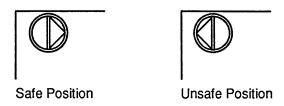

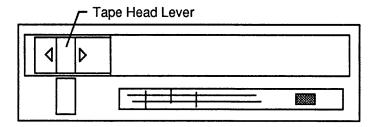

The Head Loading Lever locks the tape cartridge in place and loads the tape heads. This lever also moves the heads away from the tape and ejects the cartridge tape.

### **Expansion Cabinet**

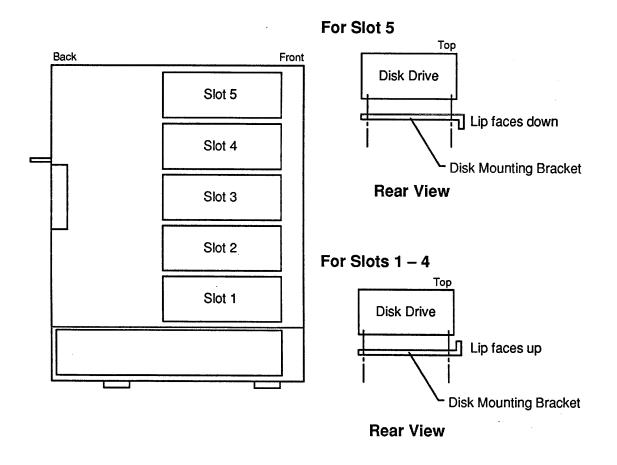

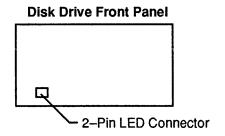

Additional SCSI devices can be supported in an Expansion Cabinet that has the same physical dimensions and general appearance as the M/120 base system cabinet. The Expansion Cabinet is connected using the SCSI port and cabling. Up to five full height 5 1/4 inch disks or equivalent size SCSI devices may be configured in an Expansion Cabinet. Refer to Figure 1.5. A section of removable front trim on the Expansion Cabinet is provided so that a removable media device may be installed and accessed. The Expansion Cabinet contains a 400 watt power supply that supports a full complement of installed disks.

Figure 1.5. Side View of Expansion Cabinet

# **Specifications**

|                       |                                    | Outstand Tonic Batter          | E 05" L - 11 L            |                   |

|-----------------------|------------------------------------|--------------------------------|---------------------------|-------------------|

| General               | LUDO DAGO                          | Cartridge Tape Drive           | 5.25" half h              | •                 |

| CPU Type              | MIPS R2000                         | Controller                     | SCSI, integ               | •                 |

| Word length           | 32 bits                            | 1/4" tape capacity             | 120MB (QI                 |                   |

| FPU type              | MIPS R2010                         | optional                       | 60MB (QIC                 | ·                 |

| Minimum Memory        | 8 Megabytes                        | Operating speed                | 90 ips, stre              | •                 |

| Maximum Memory        | 48 Megabytes                       | Power consumed                 | 25 watts in               |                   |

| Memory Configuration  | 8 MB/slot, 6 slots                 | Tape drive MTBF                |                           | @25% duty         |

| Virtual Address Space | 4GB, 2GB/process                   | Configuration                  | 1 in base c               | abinet            |

| SCSI Bus              | ANSI X3.131-1986                   | Dimensions, Weights, and Power |                           |                   |

| Max transfer rate     | 4.0MB/second sync                  |                                | Base                      | Expansion         |

| Target devices        | Up to 7, sync or async             |                                | System                    | Cabinet           |

| -                     |                                    | Height                         | 58.5cm<br>(23.0")         | 58.5cm<br>(23.0") |

| Ethernet Port         | IEEE 802.3, standard               | Width                          | 18.8 cm                   | 18.8cm            |

| Media type            | Coaxial cable                      |                                | (7.0")                    | (7.0")            |

| Data rate             | 10 Mbits per second                | Depth                          | 45.7cm                    | 45.7cm            |

| Access control        | CSMA/CD protocol                   |                                | (18.0")                   | (18.0")           |

| Serial I/O            | RS-232C, DB-25S                    | Weight                         | 25Kg<br>(55 lbs)          | 20 lbs<br>(empty) |

| In base system        | 4 ports<br>(2 w/ modem control)    | Shipping weight                | 30kg<br>(65 lbs)          | 46kg<br>(100 lbs) |

| Using AT Bus          | 8 lines per slot                   | Power supply                   | 400 watts                 | 400 watts         |

| AT Bus slots          | 4                                  | AC circuit rating              | 1000                      | 1000              |

| Max baud rate         | 19,200                             | ŭ                              | volt amps                 | volt amps         |

|                       |                                    | Heat in BTUs/hour              | 2040                      | 340               |

| Disk Drive Type       | 5.25" full height                  |                                | 800 watts                 | empty             |

| Controller            | SCSI, integral                     | <b>.</b>                       |                           |                   |

| Recording type        | Winchester                         | Regulatory                     |                           | _                 |

| Capacities            | 328MB formatted<br>156MB formatted | RFI emissions                  | FCC Class<br>VDE Class    | •                 |

| Average seek time     | 16.5 ms                            | Safety                         | UL, CSA, T                | TUV,              |

| Average latency       | 8.3 ms                             |                                | VDE, IEC                  |                   |

| Average access time   | 24.8 ms                            | Environmental                  |                           |                   |

| Data command          | 0.75 ms for 328MB                  |                                | 10° C to 40               | ۸٥ 🔿              |

| overhead              | 2.0 ms for 156MB                   | Ambient temp, op               |                           |                   |

| Power consumed        | 27 watts (92BTU/hr)                | Relative humidity              | 10% to 80%                |                   |

| Disk drive MTBF       | 40,000 hours                       | ACualtaga                      | to 3000m (                | •                 |

| Configurations        | 1 in base cabinet                  | AC voltage                     | 90 to 130 v<br>180 to 264 |                   |

|                       | up to 5 in Expan Cab               | AC frequency                   | 47 to 63 Hz               |                   |

| Weight                | 3.7 kg (8 lbs) each                | AC pwr cord length             | 2m (6 ft)                 | -                 |

|                       |                                    | No per cold leligiti           | دانا (۱۵ ۱۱)              |                   |

# Chapter 2 Installation

This chapter contains the installation instructions for the M/120 RISComputer System. This chapter is divided into the following sections:

- Select the Site

- Select the Voltage

- Install Additional or Optional PC Cards

- Install Serial I/O Devices

- Cable the System to an Ethernet Network

- Power Up the M/120 System.

### Select the Site

When selecting a site for the M/120 computer, the important considerations are the space requirements, the power requirements, and the environmental requirements.

### **Space Requirements**

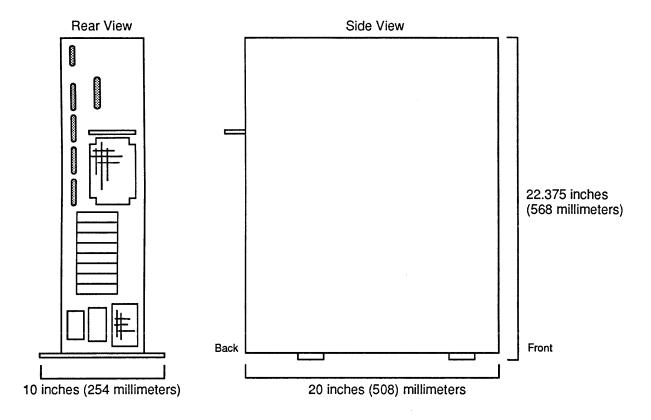

This section describes the physical dimensions of the M/120 and the minimum floor area required. The outside dimensions for the M/120 are shown in Figure 2.1 on the following page.

Since the M/120 does not have any swinging doors, the additional floor space required for an installed system is minimal compared to the actual physical dimensions. A small amount of space is required in back of the computer to allow for cable clearance. Table 2.1 on the following page summarizes the floor requirements needed for an installed M/120 System. The M/120 has a removable side panel that allows access to the inside of the computer system. Due to the compact design and portability features (53 lbs), space requirements for service and maintenance are not provided.

Figure 2.1. M/120 Physical Dimensions

Table 2.1. Minimum Required Area

| Dimension | Inches | Millimeters |

|-----------|--------|-------------|

| Height    | 22.375 | 568         |

| Width     | 10     | 254         |

| Depth     | 24     | 609         |

### **Power Requirements**

This section describes the voltage requirements, grounding, noise suppression, and types of power connectors.

The M/120 has a switchable power supply that requires 115 VAC or 230 VAC. The voltage is preset at the factory based upon the purchase order. If you need to change the preset factory setting, instructions are provided later in this chapter. Table 2.2 on the following page lists the voltage requirements.

**Table 2.2. Voltage Requirements**

| VAC (Volts AC) | HZ (hertz) | A (amps) | Range                   |

|----------------|------------|----------|-------------------------|

| 115            | 50/60      | 6        | 90 - 132 VAC, 50/60 Hz  |

| 230            | 50/60      | 3        | 180 – 264 VAC, 50/60 Hz |

The AC power connector mounted on the rear panel of the computer system is a standard 3-conductor connector. The M/120 includes a 3-conductor power cord, which is terminated with a 3-conductor plug. For 230V (220-240) operation, the power cable should be terminated with the proper outlet connector for your local power source.

A green ground wire is connected to the metal frame of the system cabinet. This safety ground protects personnel against short circuits and other malfunctions. In order for this protective ground to work, the power cord must be plugged into an outlet that has a ground connection. The outlet ground connection must be connected to the distribution panel where the system's circuit breaker is installed.

The grounding wires for the outlets that are to be used by the M/120 and its peripheral equipment must be connected to the same ground wire (separate from neutral) at the distribution panel. A grounding wire should be installed from the distribution panel to earth ground. The earth ground could be the structural steel of the building, a ground rod, or a building entrance earth ground connection. All grounding wires should be insulated, and conduit must not be used as a ground path.

If specific protection against lightning is needed, consult Article 280 of the National Electrical Code. Article 280 describes the installation of lightning arrestors on power and communication lines.

Electromagnetic interference (noise), which can cause computer malfunctions, can be placed onto power distribution circuits by office equipment, janitorial equipment, electric motors, etc. To eliminate or to reduce the noise to an acceptable level, the computer and its peripherals must be provided with separate circuit breakers from those used by other electrical equipment.

### **Environmental Requirements**

An environment that meets the specifications given in Table 2.3 must be provided or created in order for the system to operate properly.

**Table 2.3. Environmental Specifications**

| Conditions            | Temperature                          | Humidity                 |

|-----------------------|--------------------------------------|--------------------------|

| Maximum Operating     | 50–104 degrees F (10–40 degrees C)   | 20% – 80% non–condensing |

| Recommended Operating | 59–82 degrees F (15–28 degrees C)    | 50%                      |

| Maximum Storage       | –40 to 149 deg. F (–40 to 65 deg. C) | 95% non–condensing       |

If the system is moved from one environment to another, then it is recommended that the equipment is not powered on until the system has had time to acclimatize to the new environment. Wait one hour for every 10 degree C increment of change that occurred before powering up the system.

Excessively high humidity levels can cause improper operation of disk drives and of paper-handling peripherals (printers). Excessively low humidity levels can increase problems with static electricity.

The discharge of static electricity from personnel can damage equipment, cause errors in system operation, and damage the contents of software media. To prevent damage from static electricity, use ground mats connected to earth ground around the computer. These mats dissipate accumulated static charge.

The M/120 is equipped with cooling fans to circulate environmental air throughout the cabinet. The total system heat dissipation is 800 watts (approximately .8 BTU per second).

If the system is to operate continuously, you must determine if the air conditioning is turned on or off during weekends and off—work hours. If the operation of the air conditioning is varied, then measurements should be taken during the down or off periods to verify that the temperature range of the system is not exceeded. If the operating temperature is exceeded, then additional air conditioning must be provided, or, as a last resort, the system must be shut down.

## Select the Voltage

The voltage is preset at the factory according to the purchase order. If the voltage selection needs to be changed, then use the following procedure. Changing the voltage selection is a two-step process. The two fuses must be changed and the voltage select switch must be toggled. Proceed as follows.

- 1. Turn the M/120 System power off.

- 2. Remove the power cord from the rear panel of the computer. Access to the fuses cannot be obtained without removing the power cord.

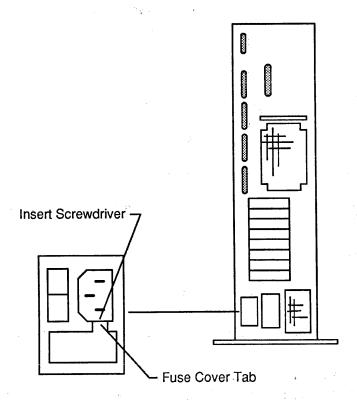

- 3. Snap the fuse cover out of the machine using a flat-head screwdriver. Refer to Figure 2.2.

- 4. Pull the fuse holder and cover out of the computer.

- 5. Slide the fuse holder out of the fuse cover, and remove the two fuses.

Figure 2.2. Removing the Fuse Holder

- 6. Position each fuse on the fuse holder, and press each fuse into place. For 115 VAC, install two 6 amp fuses (Little Fuse 312–006, 3AG). For 230 VAC, install two 3 amp fuses (Little Fuse 312–003, 3AG).

- 7. Slide the fuse holder back into the fuse cover.

- 8. Slide the fuse assembly back into the machine until it snaps into place.

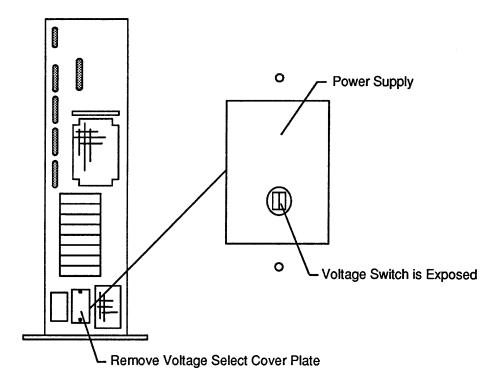

- 9. Remove the two screws from the metal plate containing the CAUTION note to gain access to the voltage select switch. This cover plate is located next to the power socket on the lower edge of the rear panel. Refer to Figure 2.3.

- 10. Use Figure 2.3 below to locate the voltage select switch on the end of the power supply.

Figure 2.3. Location of Voltage Select Cover Plate and Voltage Switch

- 11. Toggle or slide the voltage switch to the other voltage selection using a flat-head screw-driver. The voltage switch is labeled with 115V and 230V. When selecting a voltage, toggle the switch so that the voltage you want to select is displayed on the switch.

- 12. Reinstall the voltage select cover plate by reinstalling the two screws.

Do not install the power cord at this time.

### **Install Additional or Optional PC Cards**

This section provides instructions for removing the side panel of the computer and gaining access to the inside of the computer. This section also includes information on installing additional memory cards in the computer and information on installing optional AT Cards.

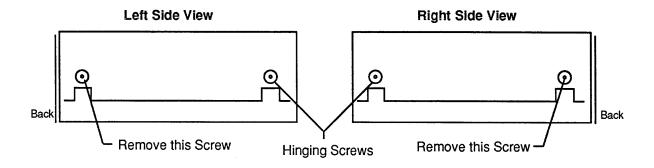

### Removing the Side Panel

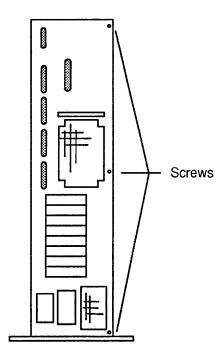

- 1. Turn the power switch off, and disconnect the power cord from the computer.

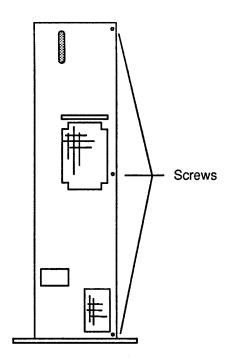

- 2. Remove the three screws along the right edge of the rear panel. Refer to Figure 2.4.

Figure 2.4. Side Panel Screws

3. Slide the side panel towards the back of the machine about one inch. Then, lift the side cover from the machine. The latching tabs located on the top and bottom, front edges of the side panel must clear the other half of the latching assemblies before the side panel can be lifted from the computer.

### **Install Additional Memory Cards**

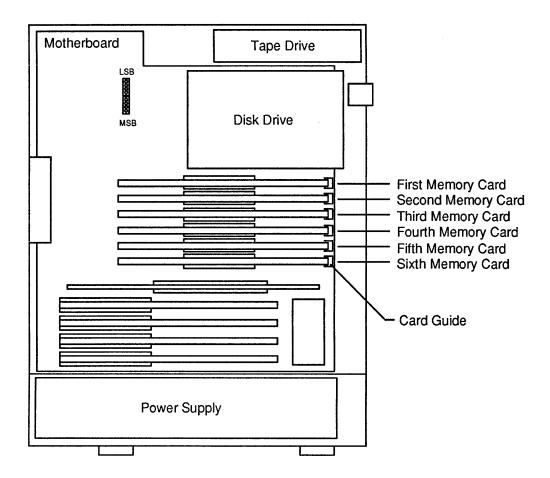

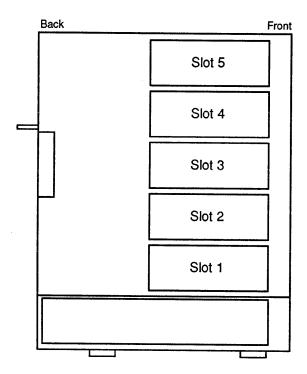

Up to six R2450 Memory Cards can be installed in the M/120 RISComputer System. The basic system includes one Memory Card, which is installed in the top slot. Additional Memory Cards must be sequentially added from the top slot down. If you only install two Memory Cards, then the cards would be installed in the top two slots. Figure 2.5 shows the order that Memory Cards must be added to the system.

To install a Memory Card in the computer, position the card with the component side up, and insert the card in the card guide on the front side of the cabinet. Slide the card into the connector on the Motherboard until firmly seated.

Figure 2.5. Location of Memory Card Slots

### **Install Optional AT Cards**

Up to four AT Cards can be installed in the M/120 to extend the capabilities of the system. Not all AT Cards are compatible, and therefore cannot be plugged into the AT slots. For detailed specifications on the AT Bus Compatibility Considerations, see Appendix A. A UNIX driver must be written for each AT Card that is installed in the M/120. Information on writing a UNIX device driver can be found in Chapter 4, Writing Device Drivers. Use the following procedure to install an AT Card.

- 1. Remove the Expansion Slot cover for the slot in which you want to install an AT Card by removing the screw. The four AT card slots are shown in Figure 2.6.

- 2. Position the AT card with the mounting bracket on the left side (towards the back of the computer), and carefully slide the card into the connector on the Motherboard.

- 3. Reinstall the screw removed in step one to secure the AT Card and mounting bracket.

Figure 2.6. Location of AT Card Slots

### Reinstall the Side Panel

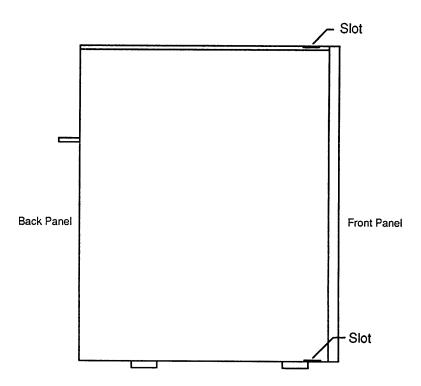

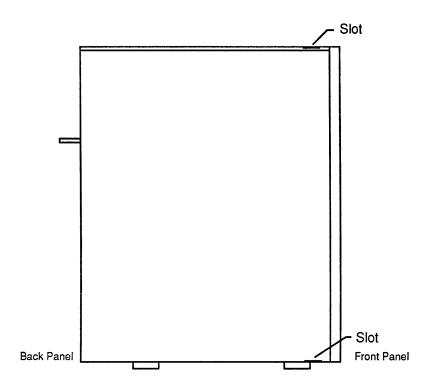

- 1. Align the latching tabs on the side panel with the slot at the top and the slot at the bottom of the computer chassis. See Figure 2.7.

- 2. Press the latching tabs into the two slots, and slide the side panel towards the front of the machine.

- 3. Reinstall the three screws on the rear panel that secure the side panel.

Figure 2.7. Location of Latching Tab Slots

### **Connect Serial I/O Devices**

This section provides the technical information needed in order to connect external equipment to the serial (RS-232C) I/O ports.

There are four serial ports located on the rear panel of the computer, which are shown in Figure 2.8. Serial I/O ports 1 and 3 support modem control for connecting modems and printers. Ports 0 (zero) and 2 are configured for terminal equipment. All ports are DTE (Data Terminal Equipment) configured. Connecting terminal equipment requires a null modem connector.

Figure 2.8. Location of Serial Ports

#### **General Considerations**

The standard for RS-232C cables recommends that cables should not be longer that 50 feet. Longer cables may be used, but a longer cable may create line noise, which would affect the data and cause errors. If a cable longer than 50 feet is required, then an appropriate extender device should be used.

FCC regulations on EMI (Electromagnetic Interference) require the use of shielded cable. For best results, connect the I/O panel via a metallic connector hood and jackscrews. For terminal equipment, do not connect the shield to any other pins on the RS-232C connector.

If a cable must be disconnected from a peripheral device, then disconnect the cable from the rear panel of the computer. Improper termination of cables can reduce the system speed and throughput.

### **Terminal Connector Pinouts**

All four ports can be connected to terminals. However, ports 0 (zero) and 2 are specifically intended for this function.

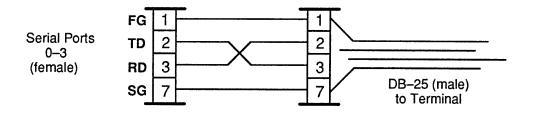

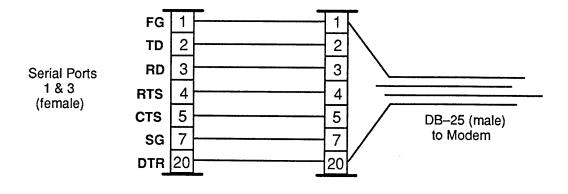

The number of wires or pins used in building a cable depends on the application of the port being used. If the port is intended for a standard terminal, then use the connections shown in Figure 2.9. If the port is to be used for a modem adapter, then use the connections shown in Figure 2.10.

#### NOTE

The connections shown in Figures 2.9 and 2.10 are general connections. Your configuration and equipment may require different adapter connections. Refer to your peripheral manual for specific requirements.

Figure 2.9. Connections for a Terminal Adapter

Figure 2.10. Connections for a Modem Adapter

### **Connecting the Console**

The cable for connecting the terminal you have designated as the system console may have been provided with the peripheral equipment. If not, then a cable may be available from the distributor from whom you purchased the peripheral equipment. Use the following procedure to connect the system console.

- 1. Connect the RS-232C cable to the connector labeled SI/O 0 (zero) on the rear panel of the M/120 computer. Tighten the connector screws to secure the cable connector.

- 2. Connect the other end of the console cable to the terminal you have designated as the system console.

- 3. Connect the system console power cord to a power source.

- 4. Turn on the system console, and set the console terminal parameters as specified below using the SETUP mode as described in the documentation for your terminal.

- Baud rate = 9600 baud (unless the system default baud rate has been changed)

- Bits per character = 8

- Protocol = XON/XOFF

- Parity = Disabled

- Mode = Character (not block) and full duplex

- Stop bits = 1

### Connecting Other Serial I/O Devices

Cables for connecting serial I/O devices may have been provided with the peripheral equipment. If not, then cables may be available from the distributor from whom you purchased the peripheral equipment. Standard RS-232 cables can also be obtained from almost any supplier of computer supplies.

Before cabling the system, verify that the system is alive and that all cards were installed correctly by powering up the computer system. Proceed as follows to power up the computer system and to cable the system.

- 1. Set the power switch on the rear panel of the computer in the off position, and then connect the computer power cord to a power source.

- 2. Turn the keyswitch to the Unlock position, and set the system power switch to the ON position. The Power On diagnostic and system information messages will be displayed on the system console. The PROM Monitor prompt (>>) is displayed on the system console after the Power On diagnostic and system information messages are displayed. (If the Boot-

mode variable described in Chapter 5, PROM Monitor is set to d, the system performs a different start up sequence. Refer to Chapter 5 for details.)

- 3. Power down the console and computer system, and unplug all power cords.

- 4. Connect the serial I/O device cables to the rear panel of the computer. Tighten the two screws on each cable connector.

- 5. Connect the other end of each cable to the correct peripheral, and tighten the connector screws. Refer to each peripheral device manual for additional installation instructions.

## **Cable the System to an Ethernet Network**

Use the following information and your Ethernet equipment manuals to install your Ethernet network.

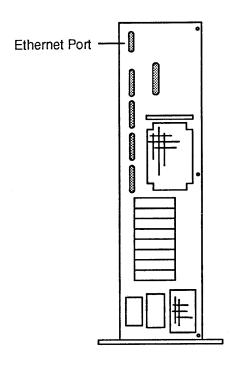

The Ethernet port is located on the top, left side of the rear panel as shown in Figure 2.11. The pinouts for the Ethernet port are given in Table 2.4.

Figure 2.11. Location of Ethernet Port

Table 2.4. Rear Panel Connector to Transceiver Cable Pin Signals

| Pin_ | Signal Name           |

|------|-----------------------|

| 1    | Shield                |

| 2    | Collision Presence +  |

| 3    | Transmit +            |

| 4    | Ground                |

| 5    | Receive +             |

| 6    | Power Return (Ground) |

| 7    | Reserved              |

| 8    | Reserved              |

| 9    | Collision Presence -  |

| 10   | Transmit –            |

| 11   | Reserved              |

| 12   | Receive -             |

| 13   | Power (+ 12v fused)   |

| 14   | Reserved              |

| 15   | Reserved              |

# Power Up the M/120 System

#### Note

If you have an Expansion Cabinet that needs Disk Drives or other peripheral devices installed, then turn to **Appendix C** and complete the instructions given before continuing.

- 1. Connect any disconnected interface cables to the associated peripheral equipment.

- 2. Connect any power cords for attached peripherals including the console to a power source.

- 3. Verify that the power switch on the rear panel is in the OFF position, and connect the power cord for the computer to a power source. It is recommended that a single power line be dedicated to the computer.

The AC power connector is a standard, 3-prong AC power receptacle. Use an AC power cable that is rated at 10 Amperes at 250 volts AC. MIPS supplies power cables for most North American users. For users who need power cables for other types of outlets, contact your local dealer or distributor.

- 4. Turn on the system console, and wait for the cursor to appear.

- 5. Turn the keyswitch to the Unlock position.

- 6. Press the Power On switch located on rear panel of the M/120 RISComputer. The Power On diagnostics will be performed. For additional information on the Power On diagnostics, refer to **Appendix D**. The Power On diagnostic messages and the system information messages are displayed on the system console. The PROM Monitor prompt shown below is displayed on the system console after these messages:

>>

(If the Bootmode variable described in Chapter 5, PROM Monitor is set to d, the system performs a different start up sequence. Refer to Chapter 5 for details.)

7. Enter "auto" at the PROM Monitor prompt as shown below if you want to boot the Operating System. If you want to use the PROM Monitor, then refer to **Chapter 5, PROM Monitor** for a description of each PROM Monitor command.

#### >>auto <Enter>

Turn to the System Administration Guide for additional information and instructions on booting the Operating System.

# Chapter 3 Programming Model

This chapter provides a programmer's view of the M/120 System. It defines the system memory map supported by the M/120, describes the interrupt system supported by the system, and specifies the purpose of the system's configuration and status registers. The chapter also summarizes the addresses and functions of programmable registers provided by the devices used to implement the M/120's I/O subsystem. Figure 3.1 shows the organization of the M/120 and the major programmable elements within the system.

Figure 3.1 M/120 System Block Diagram

# **Signal and Bit Naming Conventions**

Throughout this manual, the names of bits in control and status registers or signal names follow the following rules:

- Register bits whose names end with the letter B or with an asterisk (\*) are true or asserted when they are set to "0". All other bits are true or asserted when they are set to "1". For example, the bit named TimeOut is true (indicating a timeout condition) when it is set to "1", and the bit named DAckEnB is true (indicating that the DAck signal is enabled) when it is set to "0".

- Signals whose names end with the letter B or with an asterisk (\*) are true or asserted when they are at a logic "0" or low voltage level. All other signals are true or asserted when they are at a logic "1" or high voltage level. For example, the signal named Intr4\* is true (indicating an interrupt condition) when it is at a logic "0" level.

# **Data Formats and Addressing**

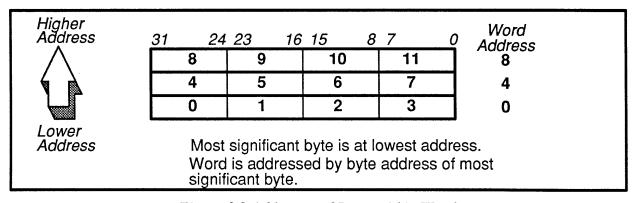

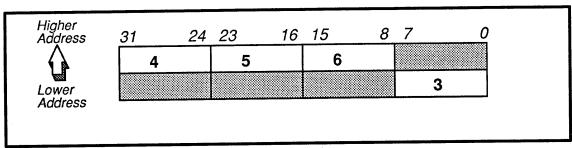

The M/120 uses an R2000 processor as its central processing unit. The R2000 defines a 32-bit word, a 16-bit half-word, and an 8-bit byte. The system is configured as a **big-endian** system: byte 0 is always the most significant (leftmost) byte, thereby providing compatibility with MC 68000® and IBM 370® conventions.

Figure 3.2 shows the ordering of bytes within words and the ordering of words within multiple—word structures for the M/120.

Figure 3.2 Addresses of Bytes within Words

The R2000 uses byte addressing, with alignment constraints, for half—word and word accesses. half—word accesses must be aligned on an even byte boundary, and word accesses must be aligned on a byte boundary divisible by four.

As shown in Figure 3.2, the address of a multiple-byte data item is the address of the most-significant byte.

Special instructions are provided for addressing words that are not aligned on 4—byte (word) boundaries. These instructions are Load Word Left/Right (LWL, LWR) and Store Word Left/Right (SWL, SWR). These instructions are used in pairs to provide addressing of mis—aligned words with one additional instruction cycle over that required for aligned words. Figure 3.3 shows the bytes accessed when addressing a mis—aligned word with a byte address of 3 for each of the two conventions.

Figure 3.3 Mis-aligned Word: Byte Addresses

# **System Memory Map**

Figure 3.4 shows the physical memory map that is defined by the M/120, and Figure 3.5 provides more detail on the address assignments within the address space assigned to local I/O. The four GBytes of address space is allocated into blocks devoted to main memory, AT bus memory and I/O devices, local I/O devices (timers, time-of-day clock, serial port DUART, and so on), PROMS, and AT bus interrupt cycle vectors. Additional details on address assignments within each of these blocks is provided later in this chapter.

The M/120 memory map provides for up to 128 Mbytes of contiguous main memory in the physical address space from 0x0000\_0000 through 0x07ff\_ffff. However, the maximum specified "real" main memory that can be installed in the six available slots is 48 Mbytes and occupies a contiguous physical address space from 0x0000\_0000 through 0x02ff\_ffff. The main memory address space is partitioned into six equal sized 8 MByte address spaces. The physical address space occupied by a memory board is slot specific on 8 MByte boundaries; each unique memory card slot is responsible for a unique 8 MByte address space. This approach eliminates the need for any "address bank" select jumpers or similar mechanisms.

The first four memory board slots (0–3) are bus-compatible, identical, and reserved for R2450 Memory Boards ONLY. The last two slots (4–5) can be used for either R2450 Memory Boards or for special function cards than may require the capability of operating as bus masters. Note that only one of these two slots can contain a card acting as bus master.

Parity errors generated by an R2450 Memory Board can be "bypassed" by software (via the *System Configuration Register*) to facilitate debug and diagnostics.

| Address Range              | Assigned to                                | Number of bytes          |

|----------------------------|--------------------------------------------|--------------------------|

| 0x1fff ffff<br>0x1f00 0000 | Boot PROM                                  | 16 Megabytes             |

| 0xleff ffff<br>0xle00 0000 | ID PROM                                    | 16 Megabytes             |

| 0x1dff ffff<br>0x1d00 0000 | Ethernet PROM                              | 16 Megabytes             |

| 0x1cff ffff<br>0x1800 0000 | Local I/O (see Figure 3.5)                 | 96 Megabytes             |

| 0x17ff ffff<br>0x1000 0000 | PC AT I/O & PC/AT Memory (see Figure 3.21) | 128 Megabytes            |

| 0x0fff ffff<br>0x0800 0000 | unused                                     | 128 Megabytes            |

| 0x07ff ffff<br>0x0300 0000 | reserved                                   | 80 Megabytes             |

| 0x02ff ffff<br>0x0280 0000 | R2450<br>Main Memory                       | 8 Megabytes<br>(slot #6) |

| 0x027f ffff<br>0x0200 0000 | R2450<br>Main Memory                       | 8 Megabytes<br>(slot #5) |

| 0x01ff ffff<br>0x0180 0000 | R2450<br>Main Memory                       | 8 Megabytes<br>(slot #4) |

| 0x017f ffff<br>0x0100 0000 | R2450<br>Main Memory                       | 8 Megabytes (slot #3)    |

| 0x00ff ffff<br>0x0080 0000 | R2450<br>Main Memory                       | 8 Megabytes<br>(slot #2) |

| 0x007f ffff<br>0x0000 0000 | R2450<br>Main Memory                       | 8 Megabytes<br>(slot #1) |

Figure 3.4 M/120 System Physical Memory Map

| Address Range              | Assigned to                           |  |

|----------------------------|---------------------------------------|--|

| 0x1b00 0002                | AT DAck Enable Register               |  |

| 0x180f 0006<br>0x180f 0002 | 7990 Lance Controller (Ethernet)      |  |

| 0x180e 000a<br>0x180e 0002 | 9516 DMA Controller (UDC)             |  |

| 0x180d 00f3<br>0x180d 0003 | MB87030CR SCSI Controller             |  |

| 0x180c 00ff<br>0x180c 0003 | 8254 Interval Timers                  |  |

| 0x180b 1fff<br>0x180b 0003 | MK48T02 Calendar Clock & 2Kbyte NVRAM |  |

| 0x180a 003f<br>0x180a 0003 | 2681 DUART1                           |  |

| 0x1809 003f<br>0x1809 0003 | 2681 DUART0                           |  |

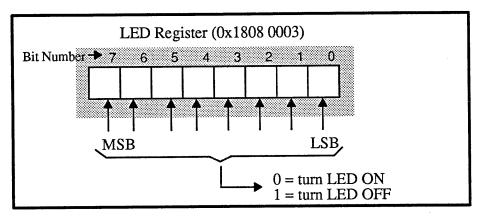

| 0x1808 0003                | LED Register                          |  |

| 0x1807 0002                | AT Control Register                   |  |

| 0x1806 0003                | Timer1 Acknowledge                    |  |

| 0x1805 0003                | Timer0 Acknowledge                    |  |

| 0x1804 0002                | Fault ID Register                     |  |

| 0x1803 0000                | Fault Address Register                |  |

| 0x1802 0002                | Interrupt Mask Register (IMR)         |  |

| 0x1801 0002                | Interrupt Status Register (ISR)       |  |

| 0x1800 0002                | System Configuration Register         |  |

Figure 3.5 M/120 Local I/O Map

Each of the devices and registers in the local I/O address space are described in detail later in this chapter.

# **Interrupt System**

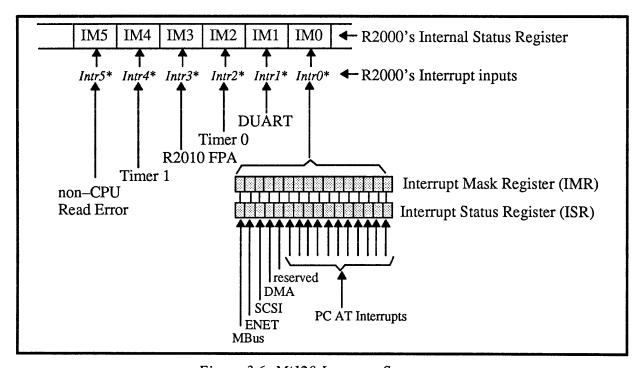

The R2000 CPU supports six level-triggered interrupt inputs (Intr0\* through Intr5\*). Figure 3.6 illustrates the assignment of these interrupts in the M/120 system.

Each of the R2000 interrupts can be individually enabled/disabled by setting/clearing an appropriate bit in the processor's internal Status Register. *All* interrupt inputs to the processor can also be disabled via a single bit in this register. (Refer to the *MIPS RISC Architecture* book for a complete description of the processor's Status Register.) Additionally, the Level-0 interrupts (Intr0\*) from the AT-bus and other I/O system controllers can be individually enabled/disabled via the *Interrupt Mask Register*.

Figure 3.6 M/120 Interrupt Structure

Each of the interrupt sources, their initiation, and termination is described later in this chapter when the corresponding device is discussed. The following is a summary of the interrupt sources.

- Level 0 interrupt (Intr0\*) is connected to the 11 PC/AT interrupt sources as well as local interrupts from devices such as the SCSI, DMA or Ethernet controllers. The *Interrupt Mask Register* is used to enable/disable the generation of the Level 0 interrupt from these sources.

- Level 1 interrupt (Intr1\*) is derived from a signal which logically ORs the interrupt output from DUARTO (console and remote serial ports) and DUART1. Level 1 interrupts are acknowledged (and terminated) by reading or writing the DUARTs' Interrupt Status/Mask Register.

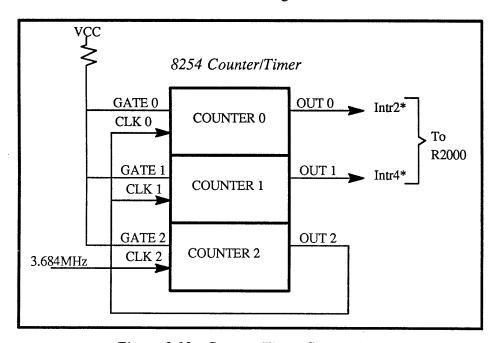

- Level 2 and Level 4 interrupts (Intr2\* and Intr4\*) are assigned to the 8254 programmable timers, Timer0 and Timer1 respectively. Two physical addresses in the Local I/O space are designated as timer/counter acknowledge registers. Reading these registers clears the corresponding timer interrupt.

- Level 3 interrupt (Intr3\*) is used by the R2010 FPA coprocessor interface.

- Level 5 interrupt (Intr5\*) is used to signal bus errors (except those occurring during CPU reads) reported by the M/120 main memory bus or the PC/AT bus. Software can read the Fault ID Register to determine the cause of the interrupt. This interrupt level is reset when the interrupt handler reads the contents of the Fault Address Register, which contains the 32-bit address of the physical location which caused the error. Reading the Fault Address Register clears the Fault ID Register as well. Refer to the section Memory Fault Handling later in this chapter for additional details.

## Interrupt Level-0

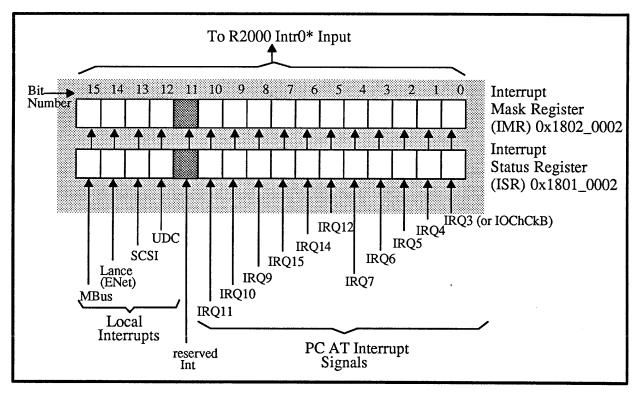

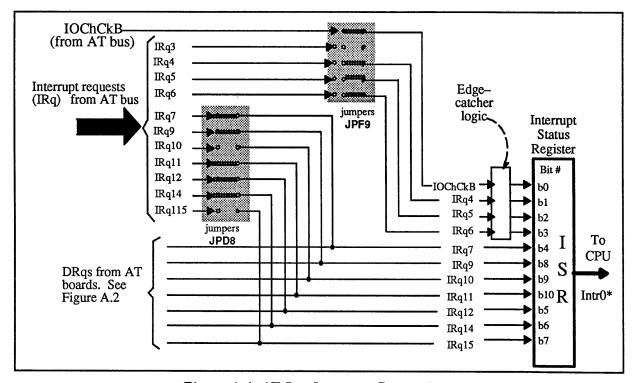

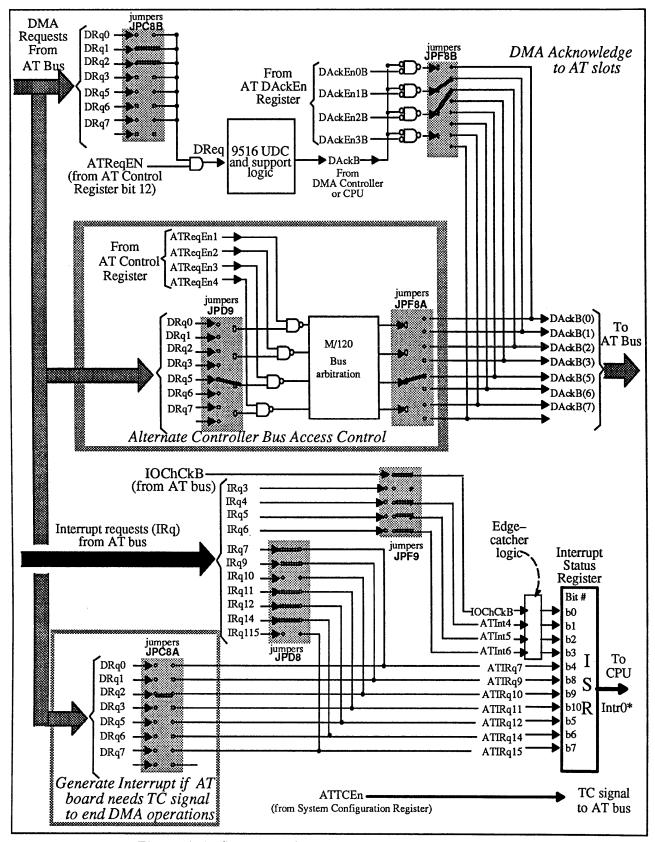

There are 16 possible sources that can cause the system to assert the level 0 interrupt input (Intr0\*) to the R2000 microprocessor. These interrupt sources are grouped together and routed through a single 16-bit register referred to as the *Interrupt Status Register* (ISR), and are selectively maskable through a separate 16-bit *Interrupt Mask Register* (IMR). Any interrupt reporting to the ISR register may cause a level 0 interrupt assertion if its corresponding "enable" bit at the IMR is enabled. Figure 3.7 shows the bit assignments for the ISR and IMR.

To acknowledge and cause the remission of a level 0 interrupt asserted by a device, the interrupt handler routine must access the interrupting device's control or status registers to ascertain and service the cause of the interrupt, This causes the interrupting device to "de—assert" the interrupt at its input to the ISR within two clock cycles.

## Interrupt Status Register (ISR)

The *Interrupt Status Register* (ISR) located at half—word physical address 0x1801\_0002 can be read to determine the source of the Intr0\* interrupt level. The presence of a logic "1" value in an ISR bit position indicates that there is an interrupt pending for that source. All bits within the ISR default to undefined state at power—up or manual system reset. However, no interrupt is generated at Intr0\* because the *Interrupt Mask Register* (IMR) defaults to all interrupts disabled at reset.

Figure 3.7. M/120 Interrupt Status and Interrupt Mask Registers

#### Interrupt Mask Register

The 16-bit *Interrupt Mask Register* (IMR) is a read/write addressable register located at 0x1802\_0002. All local interrupt sources can be masked by writing the appropriate mask bit(s) to the IMR. Refer to Figure 3.6 for IMR bit assignments. All bit positions within the IMR default to logic "0" (interrupts disabled) at power-up or manual system reset. Writing a logic "1" to an IMR bit enables the associated interrupt.

Bits 10 through 0 of the register are assigned to the AT bus interrupt requests. Note that the hardware imposes no prioritization of the AT bus interrupts.

Software can enable/disable multiple bits of the IMR register simultaneously. If an interrupt enable bit is previously set (enabled) and an interrupt occurs before or at the same time that interrupt enable bit is reset in the IMR, the interrupt will be allowed.

# **Memory Fault Handling**

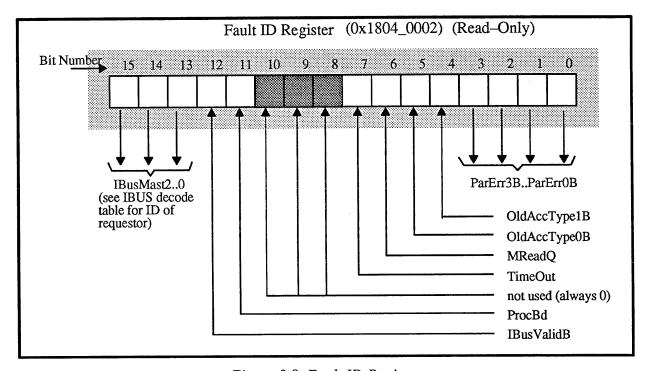

The M/120 System provides two registers to facilitate handling of faults that occur during memory transactions. The R2000 processor's level 5 interrupt (Intr5\*) is asserted as a result of a Bus Error or Time Out. An interrupt handler can determine the cause of the fault by examining the contents of the Fault ID Register (FID) and can determine the source of the fault by reading the Fault Address Register (FAR).

#### Fault ID Register (FID)

The Fault ID Register (FID) is a 16-bit register that helps system software recover from a memory fault by logging the exact nature or cause of the fault. (The device address responsible for the fault is captured in the Fault Address Register). This information is preserved in the FID register until the FAR is read. Typically, the interrupt exception handler would read the contents of the FID register to determine the cause of the interrupt, and then read the contents of the FAR to ascertain the address where the fault occurred.

Figure 3.8 illustrates the bit assignments within the FID register and the paragraphs that follow describe the function of each bit.

Figure 3.8. Fault ID Register

**ParErr3B..ParErr0B** (bit3..bit0): These bits indicate which of the four bytes comprising a 32-bit word contain a parity error: if the parity error is in the low-order byte (bits 0-7) then bit3 would be set to "0", and so on. This field is undefined and should be ignored if the *TimeOut* bit is set.

OldAccType1B OldAccType0B (bit5..bit4): This field is the ones—complement of the AccType field which existed on the M—Bus at the time of the fault. The AccType field normally indicates a "data—type" or size of transfer (byte, half—word, tri—byte, word) as shown in the following table.

| OldAccTypeB<br>1 0 | Data Size                            |

|--------------------|--------------------------------------|

| 1 1<br>1 0         | Byte (8 bits)<br>Half–word (16 bits) |

| 0 1 0 0            | Three bytes (24 bits) Word (32 bits) |

MReadQ (bit6): This bit indicates whether the fault occurred during a read operation or write operation: the bit is set to "1" if a read operation was in process and set to "0" if a write operation was being performed. A read indication could mean, for example, the R2412 CPU reading from the I-Bus or the Am9516 UDC reading from M-Bus memory.

**TimeOut** (bit7): This bit indicates that the source of the fault monopolized the M-Bus for an excessive amount of time (approximately16 microseconds) and was disengaged from the M-Bus in order to allow a refresh cycle to execute. This could happen if, for example, an I-Bus device were to read from a non-existent memory location or if the processor were to attempt a write to any PROM.

Reserved (bit10..bit8): These bits are not used and will always return "0" when read.

**ProcBd** (bit11): This bit indicates that the processor board (either the CPU or the write buffer) was responsible for the fault. This bit, in conjunction with MReadQ, indicates whether the fault was due to the write-buffer address (MReadQ = "0") or the CPU read (MReadQ = "1").

**IBusMast2..IBusMast0** (bit13..bit12): These three bits encode one of eight possible I–Bus masters as follows:

|          | FaultID Reg Bits |          |                             |  |

|----------|------------------|----------|-----------------------------|--|

| 15<br>M2 | 14<br>M1         | 13<br>M0 | Unit Requesting IBus Access |  |

| 0        | 0                | 0        | PC AT Level 4               |  |

| 0        | 0                | 1        | PC AT Level 3               |  |

| 0        | 1                | 0        | PC AT Level 2               |  |

| 0        | 1                | 1        | PC AT Level 1               |  |

| 1        | 0                | 0        | 9516 DMA for Chaining       |  |

| 1        | 0                | 1        | 9516 DMA for PC AT          |  |

| 1        | 1                | 0        | 9515 DMA for SCSI           |  |

| 1        | 1                | 1        | Lance                       |  |

**IBusValidB** (bit15): This bit, when set to "0" indicates that the encoded field *IBusMast*(2:0) is valid. If the *IBusValidB* bit is set to "1" the data in the *IBusMast*(2:0) field should be ignored.

### Fault Address Register (FAR)

The Fault Address Register (FAR) is a 32-bit, read-only word-addressable register at memory mapped I/O address 0x1803\_0000. The FAR is always synchronously latching the physical addresses used by the system's memory controller logic in anticipation of a memory fault (parity error or bus timeout).

When the system's memory controller logic detects a memory fault, it asserts the level-5 interrupt (Intr5\*) and disables the FAR from latching additional memory addresses. The captured fault address is held until software reads the *Interrupt Status Register* (ISR). Reading the ISR causes the Intr5\* signal to be de-asserted and also allows the FAR to resume latching physical addresses.

# **System Configuration Register**

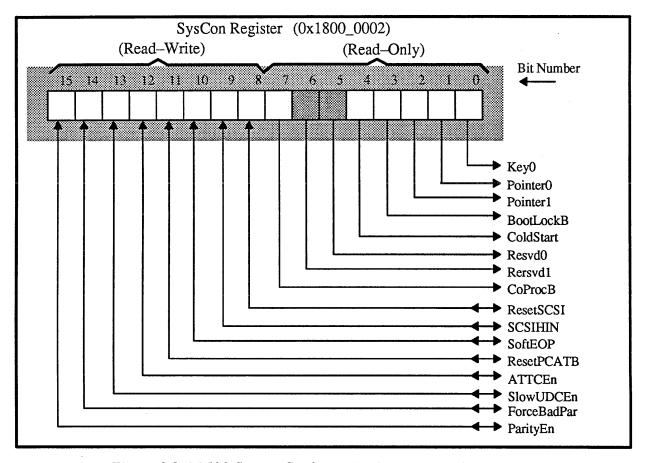

The 16-bit System Configuration Register located at address 0x1800\_0002 provides information about the configuration of various system elements and lets software control the operation of some system devices and activities. The low-order eight bits of this register are read-only and should not be written into. Figure 3.9 shows how the bits in the register are interpreted. The paragraphs that follow describe each of the bits in detail.

Figure 3.9 M/120 System Configuration Register Bit Assignments

**Key0** (Bit 0): Indicates the type of CPU board currently in use on the R2400. In current versions of the system, this bit is set to "1".

**Pointer[1:0]** (Bits 2:1): These bits are intended for diagnostic purposes and indicate the current position of the SCSI byte transfer counter in the system's SCSI/DMA logic. Diagnostic software can determine a residual byte–count which exists between the SCSI Protocol Controller and the main memory as shown in the following table.

| Pointer<br>1 0 | Residual byte count |

|----------------|---------------------|

| 0 0            | none                |

| 0 1            | 3 bytes remaining   |

| 1 0            | 2 bytes remaining   |

| 1 1            | 1 byte remaining    |

**BootLockB** (Bit 3): This bit is set to "0" if the front-panel keyswitch is in the *Lock* position and indicates to system software that the operating system should not be booted after reset. This is a security feature based on the position of the front-panel keyswitch. This bit is set to "1" if the keyswitch is in the *Unlock* position and tells system software that it should allow a manual or auto-boot sequence to continue from power-up all the way to multi-user UMIPS.

ColdStart (Bit 4): This bit is set to "1" if a "power-up" system reset has just been executed and it indicates to system software that main memory initialization is required. This bit is set to "0", if the reset was executed via the front-panel keyswitch and indicates to system software that the contents of main memory may contain relevant information which the operating systems software may wish to examine.

Rsvd1,Rsvd0 (Bita 6:5): These two bits are reserved.

CoProcB (Bit 7): When set to "0", indicates the presence of the R2010 FPA coprocessor.

**ResetSCSI** (Bit 8): Set by software to initialize the SCSI/UDC DMA state machine. Software must first set this bit to "1" and then to set the bit back to "0" to initiate and then terminate the reset operation.

SCSIHIN (Bit 9): Set by software to indicate the direction of a SCSI DMA data transfer to the SCSI/UDC DMA state machine and the SCSI Protocol Controller. When set to "1" it indicates that data is to be transferred from a SCSI device (tape or disk) into main memory, when set to "0" the direction of data transfer is from main memory out to a SCSI device.

**SoftEOP** (Bit 10): Set by software to send an EOP (end-of-process) signal to the 9516 UDC. Refer to the *Direct Memory Access (DMA)* section later in this chapter for details.

**ResetPCATB** (Bit 11): Generates the signals to reset the AT bus. Software must first set this bit to "0" and then set the bit back to "1" to assert and then release the bus reset signal.

ATTCEn (Bit 12): Enables the transfer complete (TC) signal required by some devices to terminate a DMA cycle on the AT bus. Refer to the *Direct Memory Access (DMA)* section later in this chapter for details.

**SlowUDCEn** (Bit 13): Used by software to signal when "slow-readable" UDC registers (Am9516 DMA device) will be accessed by the CPU (programmed I/O mode). Refer to the *Direct Memory Access (DMA)* section later in this chapter for details.

ForceBadPar (Bit 14): Used by software to cause "bad—parity" to be forced into the main memory parity checker logic. This bit is primarily intended for diagnostic software use.

ParityEn (Bit 15): Used by software to enable or disable the occurrence of a level-5 interrupt resulting from a parity error. Software can set the bit to a logic "1" value to enable a parity error to cause a level-5 interrupt. This bit is primarily intended for diagnostic software use.

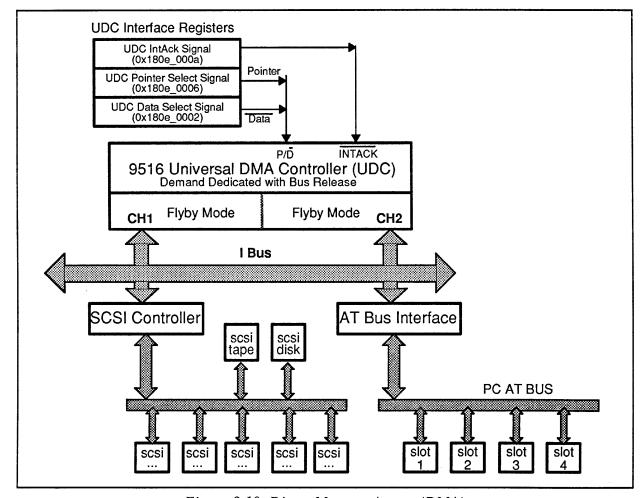

# **Direct Memory Access (DMA)**

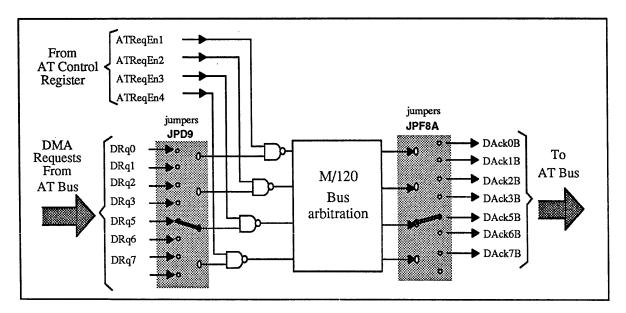

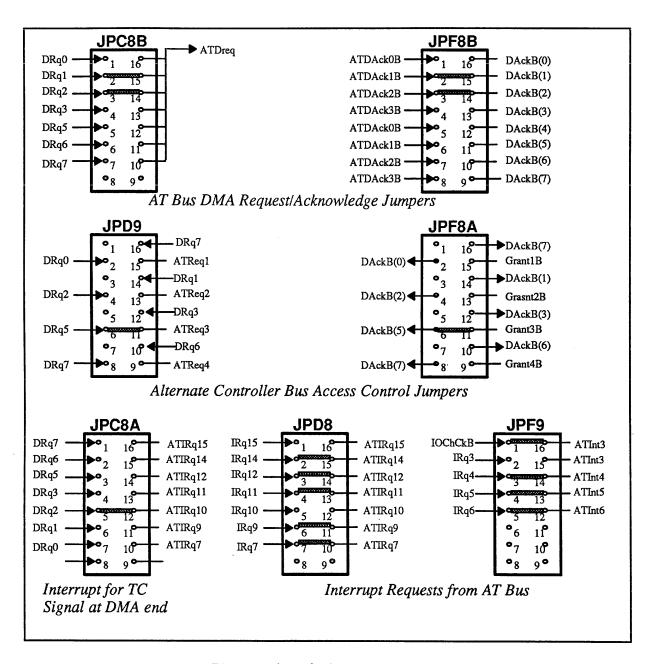

The M/120 uses an Am9516 Universal DMA Controller (UDC) to support direct memory access operations in the system. One channel (CH#2) of the UDC is dedicated to supporting transactions to and from the AT bus and the other channel (CH#1) is dedicated to supporting the SCSI interface. Figure 3.10 illustrates the role of the controller in the system and shows the registers associated with the UDC interface. The paragraphs that follow briefly describe how the UDC is utilized in the M/120 system. Refer to the Am9516 Universal DMA Controller Technical Manual for a complete description of the device and its capabilities.

Figure 3.10 Direct Memory Access (DMA)

# **DMA Controller Operating Modes**

Although the 9516 supports several different transfer types and transaction types, the M/120 hardware and RISC/os software place constraints on the controller modes that can be used in the system. The general constraints are: