#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

### Cambridge, Massachusetts

#### PROJECT MAC

ARTIFICIAL INTELLIGENCE PROJECT

MEMORANDUM MAC-M-262 September, 1965

## A THEORY OF COMPUTER INSTRUCTIONS

#### WARD DOUGLAS MAURER

## Introduction

This paper has arisen from an attempt to determine the nature of computer instructions from the viewpoint of general function and set theory. Mathematical machines, however the term is understood, are not adequate models for the computers of today; this is true whether we are talking about Turing machines. sequential machines, push-down automata, generalized sequential machines, or any of the other numerous machine models that have been formulated in the last fifteen years. Most of these models are either not general enough, as the sequential or Turing machines with their single input and output devices; or capable of accurately reproducing only one important programming feature; or in a sense too general (see the discussion of sequential machines in Chapter 10 below). On the other hand, modern computers, whether they are binary, decimal, or mixed, whether they have one or two instructions per word, or one instruction covering several words, have several important common features. All of their instructions have input, output, and affected regions (in the sense of Dafinitions B and K below). The study of the input and output regions and the structure of affected regions of all the instructions on a given computer can provide a key to its logical efficiency.

Various directions of further study may suggest themselves. This computers introduced here seem to cover at least two situations which have nothing to do with "hardware": the construction of an algorithm (such as a flow chart) and

#### EREATA

- P. 15, line 14: " Bx"

- P. 19, line 10: "if x @ OR(I1) but ... "

- P. 19, line 22: "if x & OR(I2),"

- P. 20, line 3: "S<sub>1</sub> IR(J) = S<sub>2</sub> IR(J)"

- P. 20, line 18: "x € OR(I1)"

- P. 20, line 19: "x & OR(I2)"

- P. 27, bottom: "by construction of 5 "

- P. 29, line 10: "S1(z) = S2(z) for z ( IR(I),"

- P. 33, third line from bottom was omitted; it should read:

"as the intersection of all subsets N of M which possess the predicate AP2(N', 1);"

- P. 34, line 9: "M', I1), so that"

- P. 34, tenth line was omitted; it should read:

- "I1), I2) = I2(I1(S2)) M AR2(AR2(M', I1), I2). Therefore AR2(AR2(M', "

- P. 34, seventh line from bottom: "AR, (M', I) = AR (M', I) U ..."

- P..34, second line from bottom: "This shows that (M' OR(I))"

- P. 34, bottom: "(M (OR(I) AR(M', I))) (M Z) possesses ..."

- P. 35, Line 2-4; replace with:

- "AR(M', I)  $\cup$  (M' OR(I) Z). To show the converse relation, we note that AR(M', I)  $\subseteq$  AR<sub>2</sub>(M', I) follows directly from the definitions; also if we choose S<sub>1</sub> M-M' "

- P. 35, line 5: "= S2 M-M' "

- P. 46, line 1: "input, output, and affected!

the construction of a program in a computer language such as ALGOL. Also, we may be able to prove far-reaching theorems by imposing restrictions on the computers herein defined.

#### A Simple Model

Most modern computers are either binary or decimal; but some are a combination of the two, and theoretically there is no reason why a computer could not be constructed to the base 3, 7, 16, etc. To say that a computer is constructed to the base n means that each "element" of the computer (i. e., each bit position or decimal digit in a computer word) is capable of "assuming" the values 0 through n-1. For the sake of convenience, we shall now make a restriction (which is removed in Chapter 4) that the base n is constant over the whole computer.

All computers have a <u>memory</u>, which is a finite collection of "elements" of the above type. We may now drop the quotes and speak of the memory of a computer as a finite set M, whose elements are permitted to assume values from 0 through n-1. A particular <u>state</u> (sometimes known as an "instantaneous description") of the computer is then a specification of such a value to each element of M; i.e., a function from M into the set of all integers from 0 to n-1. This suggests that our treatment of the "number base" n of a computer, above, is inadequate, and that we ought instead to consider a set B, called the <u>base space</u>, whose cardinality is the <u>base</u> of the computer. A state of the computer is then an arbitrary map from M into B.

Some computers have accumulators, index registers, "Q-registers", and/or other special-purpose registers. It is important to note that we are regarding all such registers as subsets of M. Each register has its own "elements" (bit positions or decimal digits), which are regarded here on the same basis as the corresponding "elements" of a standard core memory cell; i.e., as elements of the set M.

Almost all computers have input-output devices. It is possible, of course, for computers to compute without using input-output devices, and one might expect that such devices are not necessary from this point of view. In fact, input-output devices and the instructions governing them are included in the present model, by extending the memory to be infinite; this is discussed in Chapter 10. We shall therefore postpone discussion of input and output, and assume that our computer has no such devices.

Passage from one state to the next is carried out by means of <u>instructions</u>.

An instruction, then, is a method of passing from one state to another state; i.e., a map I: \$\frac{1}{2} \rightarrow \text{where } f\$ is the set of all states under consideration. Let us assume for the moment that \$\frac{1}{2}\$ is in fact the set of all maps from M into B. Let us, in turn, denote the set of all instructions in a given computer by \$\frac{1}{2}\$. We then have the following definition.

DEFINITION A. Let M and B be finite sets, let  $\mathcal{J}$  be the set of all mappings S: M  $\rightarrow$  B, and let  $\mathcal{J}$  be a set of maps I:  $\mathcal{J} \rightarrow \mathcal{J}$ . Then the 4-tuple (M, B,  $\mathcal{J}$ ,  $\mathcal{J}$ ) is a <u>finite complete computer</u>. The set M is the <u>memory</u> of the computer; the set B is the <u>base space</u>; the members S  $\in \mathcal{J}$  are the <u>states</u>; and the members I  $\in \mathcal{J}$  are the <u>instructions</u>.

## Input and Output Regions of an Instruction

Each instruction I: d -> d has associated with it two subsets of M, in a manner dictated by intuitive considerations.

As an example, let us consider a computer whose memory contains a "core cell" Y and an "accumulator" AC, i.e., Y C M and ACC M, and there is an instruction (possibly called "clear and add Y," "load Y," or "zero and add Y") which moves the data in Y to AC. When we speak of "the data in Y" we are implying that the computer is in a given state S: M B, and the restriction of this map to Y (denoted by S Y), which is a map from Y into B, is a code representation of a number, one or more characters, or the like. What we seek is a rigorous formulation of the phrase "moves the data." Stated another way: The instruction I = (CLA Y), or "clear and add Y," is a map from A into A, where A is the set of all maps S: M B. Yet there are clearly associated with the instruction I, two subsets of M; one is Y, and the other is AC. What is the precise relation between I and these two subsets?

Before we answer this question, we would like to make two wishes:

- (a) We would like to call Y the "input region" and AC the "output region" of I. Each instruction, then, may "take" date only from its input region, and may "place" data only in its output region.

- (b) We would like the definition of "input and output region" to give meaningful results when applied to any instruction -- at least, any common instruction on a real computer. In order to make this precise, let us mention certain commonly used instructions, with their (putative) input and output regions:

I. A store instruction (STO Y), which stores data from AC in the cell Y. Input region, AC; output region, Y.

II. An add instruction (ADD Y), which adds the data in Y to the current contents of the AC, and leaves the result in the AC. Input region, YU AC; output region, Y. (note: The same holds if "add" is replaced by any other binary operation, such as: subtract, multiply, divide; logical and, or, exclusive or.)

III. A shift instruction (RQL 6) which rotates register MQ left by six places. Input region, MQ; output region MQ.

Without giving any more examples at the moment, we proceed to our definitions.

DEFINITION B. Let  $(M, B, \mathcal{J}, \mathcal{J})$  be a computer, and let  $I \in \mathcal{J}$ . Then the <u>input region</u>  $IR(I) \subseteq M$  and the <u>output region</u>  $OR(I) \subseteq M$  are defined as follows:

$$OR(I) = \left\{ x \in M: \exists \ S \in \mathcal{L} \ \exists \ S(x) \neq I(S)(x) \right\}$$

$$IR(I) = \left\{ x \in M: \exists \ S_1, S_2 \in \mathcal{L}, \ y \in OR(I) \ \exists \ S_1(z) = S_2(z), \ z \neq x, \right.$$

$$and \ I(S_1)(y) \neq I(S_2)(y) \right\}$$

Roughly speaking, OR(I) is the set of all elements of M which "can be affected" by I; if x # OR(I), then x is "unaffected," i.e., the state of x before the instruction, S(x), equals the state of x after the instruction, I(S)(x), for any state  $S \in \mathcal{J}$ . The input region IR(I) is the set of all elements of M which can affect OR(I); an element x is in IR(I) if there exists a state  $S_1$  such that, by changing it on x alone (and obtaining  $S_2$ ) one gets different results on some element of OR(I) after the instruction I. Note that the definition of IR(I) depends on OR(I); this seems to be unavoidable.

The following property of input and output regions is fundamental. PROPOSITION I. Let  $S_1$  and  $S_2$  be any two states and let I be any instruction. If  $S_1 \mid IR(I) = S_2 \mid IR(I)$ , then  $I(S_1) \mid OR(I) = I(S_2) \mid OR(I)$ .

Proof: Let IP(I) (the <u>input property</u>) be the following predicate of subsets of M: M' possesses IP(I)  $\Leftrightarrow$   $(S_1 \mid M' = S_2 \mid M' \implies 1(S_1) \mid OR(I) = I(S_2) \mid OR(I)$  for all  $S_1$ ,  $S_2 \in \mathcal{L}$ ). We must prove that IR(I) possesses IP(I). We first prove that the predicate IP(I) is preserved under the taking of intersections. Let  $M_1'$  and M'' be two subsets of M, each of which possesses IP(I). Let  $S_3$  and  $S_4$  be any two states such that  $S_3 \mid M' \cap M'' = S_4 \mid M' \cap M''$ . Let  $S_5$  be defined by  $S_5(x) = S_3(x)$ ,  $x \in M'$ ;  $S_5(x) = S_4(x)$ ,  $x \notin M'$ . We have  $S_5 \mid M' = S_3 \mid M'$  and, as can easily be verified,  $S_5 \mid M'' = S_4 \mid M''$ . Since M' and M'' each possess IP(I), we have  $I(S_5) \mid OR(I) = I(S_3) \mid OR(I)$  and also  $I(S_5) \mid OR(I) = I(S_4) \mid OR(I)$ . Therefore  $I(S_3) \mid OR(I)$ .

Now take the intersection of <u>all</u> subsets of M which possess IP(I), Since M is finite, there will be only a finite number of these, and the intersection will therefore possess IP(I). We show that this intersection (call it M<sub>1</sub>) is equal to IR(I). Note that the definition of IR(I) can be rewritten:  $IR(I) = \{x \in M: M - \{x\}\} \text{ does not possess } IP(I)\}$ . Thus we need only prove: for each  $x \in M$ ,  $M - \{x\}$  possesses IP(I) if and only if  $x \notin M_1$ . But if  $M - \{x\}$  possesses IP(I), then  $M_1 \subseteq M - \{x\}$  by definition. so  $x \notin M_1$ ; conversely, if  $x \notin M_1$ , then there exists some set  $M_2$  possessing IP(I) to which x does not belong, and if  $M_2$  possesses IP(I), then since  $M - \{x\} \supseteq M_2$ ,  $M - \{x\}$  certainly possesses IP(I). This completes the proof.

Thus, if two states agree on the input region of an instruction, the results on applying I agree on the output region. This would seem to follow immediately from the definitions; yet the length of the above proof is not artificial. The result, in fact, does not hold if M is infinite (unless other changes are made).

#### A Few Generalizations

At this point we may ask: How general can we make the sets M, B,

, and I without losing its most important properties? The only important property of computers we have at the moment is Proposition I;

however, it turns out that the same conditions which ensure Proposition

I also are sufficient for our other purposes. In Chapter 6 we shall

discuss what happens when these conditions are relaxed.

As we have seen, there is no reason to suppose that B has either 2 or 10 elements. Of course, if B is empty, then so is , while if B has exactly one element, there can be only one state S (and hence only one instruction I). Since these two cases are uninteresting, we may postulate that there exist at least two elements in B. In fact, this postulate will become essential later on.

Even for real computers, we may consider other cardinalities for B than 2 and 10. We may, for example, regard a character machine as a computer with the separate 6-bit (or 7-bit, or 8-bit) characters as elements of M, and give B a cardinality of 64 (128, 256). For a binary computer with 36-bit words, we can consider the words as elements of M (provided there are no 15-bit index registers) and consider B as having a cardinality of 2<sup>36</sup>. This raises the further question: Can we sllow B to be infinite? Certainly. In fact, in the previous example, we could let the words of a computer be the elements of a set M, and make the (idealized)

assumption that a word may contain eny integer (or any real number). Thus we get a computer in which the base space is the integers or the reals. None of the theory discussed here precludes the case in which the base space is infinite. The only condition imposed on B is the one above: that its cardinality be at least 2.

Is it possible to consider  $\mathcal{L}$  as only a <u>subset</u> of the set of all maps S: M->B? If it were possible, consistently with  $\mathcal{L}$  (i.e.,  $S \in \mathcal{L}$  implies  $I(S) \in \mathcal{L}$ , for all  $I \in \mathcal{L}$ ) then the choice of  $\mathcal{L}$  might have an effect on the input and output regions of an instruction. It turns out that it is necessary to impose one condition:

(P1) If

$$S_1$$

,  $S_2 \in \mathcal{A}$ , and M' is any subset of M, then the state  $S_3$ , with  $S_3(x) = S_1(x)$ ,  $x \in M'$ ,  $S_3(x) = S_2(x)$ ,  $x \notin M'$ ,

# is a member of & .

Thus for a decimal machine, it is possible to consider families of such as the following: S & of if and only if S can only take the values 3 or 7 on a subset M<sub>1</sub> of M; only the values 0 or 1 on another subset M<sub>2</sub>; and may take any value elsewhere. If M is finite, however, no other conditions need be imposed on of .

However, if we allow M to be infinite, a new situation comes up.

In this case, in fact, it is unwise to admit even the entire class of maps S from M into B. This raises the question as to whether we should ever let M be infinite; shouldn't we stick to <u>finite</u> computers, in which M (and therefore 2) is finite, just as is usually done in sequential

mechine theory? Of course, of can only be finite if B is finite; but there is another consideration.

Let us consider the following example of an (infinite) computer. The memory M consists of the integers. The base space, B, is the union of three finite sets, K,  $\Sigma$ , and  $\Delta$ . A map S: M  $\longrightarrow$  B is said to be in  $\mathcal{A}$  if and only if:

Note that this family  $\mathcal{L}$  satisfies the condition given above. There is exactly one instruction  $I \in \mathcal{L}$ . For  $x \neq 0$  or 1, I(S)(x) is defined to be S(x-1). Let us be given two arbitrary maps,  $\mathcal{L}: \mathbb{K} \times \Sigma \to \mathbb{K}$ , and  $\lambda : \mathbb{K} \times \Sigma \to \Delta$ . Then we define

$$\Sigma(S)(0) = S(S(0), S(-1)),$$

$$I(S)(1) = \lambda(S(0), S(-1)).$$

It should be evident that we have given a realization of a sequentiel machine [1] as a computer. The states of the sequential mechine

are the values S(0). The inputs enter at -1, and the outputs appear at 1.

The entire input and output "tapes" are part of the memory, although the

instruction makes no use of this memory (except for -1) other than to

move it forward by one square. Without going into the merits of this

particular realization, we see that infinite computers are, in fact,

interesting. However, for infinite computers, it becomes necessary to

impose another condition on & :

(P2) If

$$S_1$$

,  $S_2 \in \mathcal{A}$ , then  $\{x \in M: S_1(x) \neq S_2(x)\}$  is finite.

No special conditions at all are needed on the set  $\mathscr{L}$ . We may therefore make our general definition of a computer as follows:

DEFINITION C. Let M be arbitrary, let B have at least two elements, let  $\mathscr{L}$  be a set of maps S: M  $\Rightarrow$  B satisfying conditions (P1) and (P2) given above, and let  $\mathscr{L}$  be a set of maps I:  $\mathscr{L} \rightarrow \mathscr{L}$ . Then the 4-tuple (M, B,  $\mathscr{L}$ ,  $\mathscr{L}$ ) is a computer. As before, M is the memory, B is the base space, the members of  $\mathscr{L}$  are called states, and the members of are called instructions.

The reason for introducing the conditions (P1) and (P2) has to do with Proposition I. We should like to know, not only that the conditions insure that Proposition I can be properly extended, but that they are likewise necessary for this purpose.

PROPOSITION II. Let  $(M, B, \mathcal{L}, \mathcal{L})$  be a computer and let  $I \in \mathcal{L}$ .

If  $S_1$  and  $S_2$  are any two states of  $\mathcal{L}$ , then  $S_1 \mid IR(I) = S_2 \mid IR(I)$  implies  $I(S_1) \mid OR(I) = I(S_2) \mid OR(I)$ . Conversely, let M and B be arbitrary sets, and let  $\mathcal{L}$  be a set of maps  $S: M \to B$  which fails to satisfy (P2). Then there exists a map  $I: \mathcal{L} \to \mathcal{L}$  and two states  $S_1$ ,  $S_2 \in \mathcal{L}$  such that  $S_1 \mid IR(I) = S_2 \mid IR(I)$ , but  $I(S_1) \mid OR(I) \neq I(S_2) \mid OR(I)$ .

Proof: Let IP(I) be as in Proposition I. The proof that the predicate IP(I) is preserved under intersections is exactly as in Proposition I, although we note that the construction of the state  $S_5$

from  $S_3$  and  $S_1$  is now possible because S satisfies condition (P1). Now take the intersection of all subsets of M which possess IP(I). This intersection will be equal to IR(I), just as in Proposition I, and it remains only to prove that M<sub>1</sub>, the intersection, possesses IP(I). Let  $S_1$  and  $S_2$  be any two states such that  $S_1 \mid M_1 = S_2 \mid M_1$ . Let  $M_2 = \{x \in M: S_1(x) \neq S_2(x)\}$ . Since S satisfies condition (P2),  $M_2$  is finite, and  $M_1 \cap M_2 = \emptyset$ . Let  $M_1 \cap M_2 = \emptyset$  be the elements of  $M_2$ . Since  $M_1 \cap M_2 = \emptyset$  possesses IP(I) (just as in Proposition I), and, by applying condition (P1) repeatedly, we see that  $M_1 \cap M_2 = \emptyset$  but  $M_1 \cap M_2 = \emptyset$  and  $M_2 \cap M_3 = \emptyset$ . But  $M_1 \cap M_2 = \emptyset$  and  $M_2 \cap M_3 = \emptyset$  but  $M_3 \cap M_3 = \emptyset$  and  $M_4 \cap M_3 = \emptyset$ . Therefore,  $M_4 \cap M_2 = \emptyset$  and  $M_4 \cap M_3 = \emptyset$  but  $M_4 \cap M_4 = \emptyset$  and  $M_4 \cap M_4 = \emptyset$ . Therefore,  $M_4 \cap M_4 = \emptyset$  so that  $M_4 \cap M_4 = \emptyset$  and  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap M_4 = \emptyset$ . Therefore,  $M_4 \cap M_4 = \emptyset$  so that  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap M_4 = \emptyset$  and  $M_4 \cap M_4 = \emptyset$ . Therefore,  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap M_4 = \emptyset$  so that  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap M_4 = \emptyset$ . Therefore,  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap M_4 = \emptyset$  and  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap M_4 = \emptyset$ . Therefore,  $M_4 \cap M_4 = \emptyset$  for  $M_4 \cap$

Now let  $S_1$  and  $S_2$  be any two states of S such that  $M_1 = \{x \in M: S_1(x) = S_2(x)\}$  is infinite. Let  $y \in M_1$ , and define a map  $I: \mathcal{L} \rightarrow \mathcal{L}$  as follows: I(S)(z) = S(z),  $z \neq y$ ;  $I(S)(y) = S_2(y)$  if  $\{x \in M: S(x) \neq S_1(x)\}$  is finite;  $I(S)(x) = S_1(y)$ , otherwise. Clearly y is the only element of M that can be in OR(I), and since  $S_1(y) \neq I(S_1)(y)$ , we have  $OR(I) = \{y\}$ . We claim that  $IR(I) = \emptyset$ . To see this, suppose  $x \in IR(I)$ , and consider states  $S_1'$  and  $S_2'$  as in the definition of IR(I), with  $S_1'(z) = S_2'(z)$  for  $z \neq x$ . Since  $\{x \in M: S_1'(x) \neq S_1(x)\}$  and  $\{x \in M: S_2'(x) \neq S_1(x)\}$  are either both finite or both infinite, we must have  $I(S_1')(y) = I(S_2')(y)$ , or  $I(S_1') \setminus OR(I) = I(S_2') \setminus OR(I)$ , a contradiction. Therefore  $S_1 \setminus IR(I) = S_2 \setminus IR(I)$  is true vacuously, but  $I(S_1) \setminus OR(I) \neq I(S_2) \setminus OR(I)$ . This completes the proof.

#### 4. The Product Model

We might also consider how to take account of computers which are part binary and part decimal; i.e., in which there are two base spaces  $B_1$  and  $B_2$ , and the elements S(x) are in  $B_1$  for  $x \in M'$  (where  $M' \subset M$  is the "binary part" of the memory) and in  $B_2$  for  $x \notin M'$ . One way to do this is to consider a single base space  $B_1 \cup B_2$ , and to put a corresponding restriction on  $A_1 : S \in A_1$  if and only if  $S(x) \in B_1$ ,  $x \in M'$ , and  $S(x) \in B_2$ ,  $x \notin M'$ . This family  $A_1$  satisfies (P1).

Another way is to re-examine the structure of the set  $\mathscr{L}$ . The set of all maps S:  $M \to B$  can be thought of as the cartesian product of copies of B, over M as the index set. The set of states  $\mathscr{L}$  given in the preceding paragraph can be thought of as the cartesian product of two cartesian products: one of copies of  $B_1$  over index set M'; the other, of copies of  $B_2$  over index set M-M'. Might we consider a cartesian product of arbitrary sets  $B_X$ , for  $X \in M$ , where M is some index set? This would correspond to a set of maps S:  $M \to B$ , where B is the union of the (distinct)  $B_X$ , and  $S \in \mathscr{L}$  if and only if  $S(X) \in B_X$  for each  $X \in \mathbb{R}$ . This, however, raises the question as to whether such a family  $\mathscr{L}$  always satisfies (P1). For finite computers, the following proposition answers this question in a very strong manner.

PROPOSITION III. Let (M, B,  $\mathcal{L}, \mathcal{L}$ ) be a finite computer (i.e., the memory M is finite). For each  $x \in M$ , let  $B_x = \{b \in B: S(x) = b \}$  for some  $S \in \mathcal{L}$ . Then  $\mathcal{L}$  is in fact the set of all maps  $S: M \longrightarrow B$  such that  $S(x) \in B_x$  for all  $x \in M$ .

PROOF: Lot S:  $M \to B$  be any map such that  $S(x) \in B_x$  for all  $x \in M$ . We wish to prove that  $S \in \mathcal{L}$ . Since  $S(x) \in B_x$ , there exists, for each  $x \in M$ , a map  $S_x \in \mathcal{L}$  such that  $S_x(x) = S(x)$ . The proof is completed by applying condition (P1) repeatedly to the states  $S_x$ . Since the condition need only be applied a finite number of times (one for each element of M), the state S will be in  $\mathcal{L}$ ; clearly no other states can be in  $\mathcal{L}$ .

Thus, if M is finite, the cartesian product of arbitrary sets  $B_{K}$ , over M as index set, corresponds to the set of states  $\mathcal{L}$  of a computer, which satisfies (P1). Furthermore, in this case, we gain no generality by considering a subset of  $\mathcal{L}$ . For, if the subset  $\mathcal{L}$  satisfies (P1), then it defines its own subsets  $B_{K}$  in the first place. Thus we are led to an alternate definition of a finite computer.

DEFINITION D. Let M be finite, and for each  $x \in M$ , let  $B_{x}$  be a non-empty set. Let  $\mathcal{L} = \prod_{x \in M} B_{x}$ . If  $\mathcal{L}$  is a set of maps  $I: \mathcal{L} \to \mathcal{L}$ , then  $(M, \mathcal{L}, \mathcal{L})$  is a <u>finite computer</u>. The index set M is the <u>memory</u>; the elements of  $\mathcal{L}$  are the <u>states</u>; and the elements of  $\mathcal{L}$  are the <u>instructions</u>.

If M is infinite, the statement of Proposition III does not hold. Even if  $\mathscr A$  satisfies condition (P2), and  $B_{\mathbf x} = B$  for all  $\mathbf x \in M$ , the most we can say is that, given any state  $S \in \mathscr A$ . A consists of all states S' such that  $\{x \in M: S(\mathbf x) \neq S'(\mathbf x)\}$  is finite. This is exactly the situation which is known in algebra as a restricted product. For example, if we are given an infinite number of groups  $G_{\mathbf x}$ , then the restricted product of the  $G_{\mathbf x}$  is the set of all elements of the cartesian product which have only a finite number of non-identity elements. The result is a subgroup of the

"complete product," i.e., the cartesian product with multiplication,

performed by multiplying co-ordinates. We give a general definition of

restricted products before passing to the generalization of Proposition NYL.

DEFINITION B. Let M be an arbitrary index set, and for each  $z \in M$  let  $B_x$  be a non-empty set and  $b_x$  an element of  $B_x$ . The restricted product of the  $B_x$ , relative to the  $b_x$ , is the set of all elements  $z \in \prod_{x \in M} B_x$  such that, if  $z_x$  is the co-ordinate of z in  $x \in M$ , then  $\{x \in M: z_x \neq b_x\}$  is finite.

PROPOSITION IV. Let  $(M, B, \mathscr{L}, \mathscr{L})$  be a computer, let  $S_0 \in \mathscr{L}$ , and for each  $x \in M$ , let  $B_x = \{b \in B: S(x) = b \text{ for some } S \in \mathscr{L}\}$ . Then  $\mathscr{L}$  is in fact the set of all maps  $S: M \to B$  such that  $S(x) \in B_x$  for all  $x \in M$ , and such that  $\{x \in M: S_0(x) \neq S(x)\}$  is finite.

Proof: Let S:  $M \to B$  be any map such that  $S(x) \in B_x$  for all  $x \in M$  and let  $\{x \in M: S_0(x) \neq S(x)\}$  be a finite set  $M' \subseteq M$ . Since  $S(x) \in B_x$ . There exists, for each  $x \in M'$ , a map  $S_x \in \mathcal{L}$  such that  $S_x(x) = S(x)$ . The proof is completed by applying condition (P1) repeatedly to  $S_0$  and the (finite) collection of states  $S_x$ . Since the condition need only be applied a finite mamber of times, the state S will be in  $\mathcal{L}$ . Clearly, under the conditions (P1) and (P2), no other maps S:  $M \to B$  can be in  $\mathcal{L}$ .

Thus any restricted product of sets B corresponds to the set of states of a computer, satisfying (P1) and (P2). Furthermore, we again gain no generality by considering a subset of d. Thus we may give our alternative definition of a computer in full generality.

DEFINITION P. Let M be an arbitrary non-empty set, and for each  $x \in M$ , let B be a non-empty set and b a member of B Let L be the restricted

product of the D<sub>x</sub>, relative to the b<sub>x</sub>. If I is a set of sup (X = 0.5) the thru (H, A , M) to a community. The index set M is the memory; the elements of A are the states; and the elements of A are the introductions

(Perimition C and Definition P) are not really different; the set of states  $\mathcal{J}$  is being viewed in a different guise in each case. For Definition F, cortain numiliary concepts need to be redefined. If M' is a subset of M, we denote the natural projection of  $\mathbf{x} \in \mathbf{M}$  B<sub>x</sub> onto  $\mathbf{x} \in \mathbf{M}$ , B<sub>x</sub> by Pr(M, M'), and if  $\mathbf{S} \in \mathcal{J}$ , we denote the element  $\Pr(\mathbf{M}, \mathbf{M}')(\mathbf{S})$  by  $\mathbf{S} \mid \mathbf{M}'$ . The element  $\mathbf{S} \mid \{\mathbf{x}\}$ , where  $\mathbf{x} \in \mathbf{M}$ , is a member of B<sub>x</sub> which may be denoted by  $\mathbf{S}(\mathbf{x})$ . With these new definitions of  $\mathbf{S}(\mathbf{x})$  and  $\mathbf{S} \mid \mathbf{M}'$ , such concepts as input and output region may again be defined, and correspond exactly to these notions under the model of Definition C.

It may happen, under the product model, that some of the sets  $B_X$  have cardinality 1 (for example, by selecting a subset  $\mathcal{L}$ , all of whose members are such that S(x) = b for some  $x \in M$ ,  $b \in B$ ). The internal structure of such a computer is the same as that of the computer obtained by eliminating all such sets  $B_X$ . In particular, an element  $x \in M$  for which  $B_X$  has cardinality 1 can never be contained in IR(X) or OR(X), for any instruction X.

## i. Composition and Decumposition

In this chapter, we shall use computers under Definition C. One of the first things we notice about computer instructions, as they are installed here, is that if two instructions are performed one after the sharp, as they are in a real computer, the result is their computer. Specifically, if  $I_1: \int - \int d d d I_2: \int - \int d d d I_3: \int - \int d d d I_4: \int - \int d d d I_5: \int - \int d d d$

PROPOSITION V. Let  $(M, B, J, \mathcal{Q})$  be a computer,  $I_1, I_2 \in \mathcal{Q}$ , and let  $J: J \rightarrow J$  be defined by  $J(S) = I_2(I_1(S))$ . Then  $IR(J) \subseteq IR(I_1) \cup IR(I_2)$  and  $OR(I_1) - OR(I_2) \subseteq OR(I) \subseteq OR(I_1) \cup OR(J_2)$ . If  $IR(I_2) \cap OR(I_1) = g$ , then  $IR(I_2) \subseteq IR(J) \subseteq IR(I_1) \cup IR(I_2)$  and  $OR(J) = OR(I_1) \cup OR(I_2)$ .

Proof: To carry through calculations like this, it is helpful to have the following lemmatic facts.

- (a) The input property IP(I) is preserved under the taking of captizets, as well as intersections; if M' possesses IP(I), and M' ⊋ M', then M' possesses IP(I). The input region IR(I) is the intersection of all subsets of M which possesses IP(I). Therefore, a subset possesses IP(I) if and only if it contains IR(I)

- (b) If M' possesses IP(I), then  $S_1 \mid M' = I \mid M'$  implies  $I(S_1) \mid M' = I(S_2) \mid M^1$ . For let  $S_1 \mid M' = S_2 \mid M'$  and let  $y \in I'$ . If  $y \in OR(I)$ , then  $I(S_1)(y) = I(S_2)(y)$  by Propositions I and II. If  $y \notin OR(I)$ , then

$\mathbb{E}(S_1)(y) = S_1(y) = S_2(y) = \mathbb{E}(S_2)(y)$ , by definition of OR(I) and by hypothesis. The lemma is thereby proved.

(c) If  $IR(I_2) \cap OR(I_1) = \emptyset$ , then for each  $S \in \mathcal{L}$  we have  $I_2(S) \mid OR(I_2) = J(S) \mid OR(I_2)$ . To see this, let  $x \in IR(I_2)$ ; we have  $S(x) = I_1(S)(x)$ , since  $x \notin OR(I_1)$ , and this shows that  $S \mid IR(I_2) = I_1(S) \mid IR(I_2)$ . By Propositions I and II,  $I_2(S) \mid OR(I_2) = I_2(I_1(S)) \mid OR(I_2) = J(S) \mid OR(I_2)$ .

We proceed to the calculations. Let  $x \notin OR(I_1)$ ,  $x \notin OR(I_2)$ . Then  $S(x) = I_1(S)(x)$  and  $S(x) = I_2(S)(x)$  for all states  $S \in \mathcal{A}$ , so  $S(x) = I_1(S)(x) = I_2(I_1(S))(x) = J(S)(x)$ . Therefore  $x \notin OR(J)$ , which shows that  $OR(J) \subseteq OR(I_1) \cup OR(I_2)$ . Also, if  $x \in OR(I)$  but  $x \notin OR(I_2)$ , so that there exists a state  $S \in \mathcal{A}$  with  $S(x) \neq I_1(S)(x)$  but  $I_1(S)(x) = I_2(I_1(S))(x) = J(S)(x)$ , then  $S(x) \neq J(S)(x)$ , so that  $x \in OR(J)$ ; this shows that  $OR(I_1) = OR(I_2) \subseteq OR(J)$ .

Now let  $x \notin IR(I_1)$ ,  $x \notin IR(I_2)$ . Let  $S_1$  and  $S_2$  be any two states of  $\mathscr{L}$  such that  $S_1(z) = S_2(z)$ ,  $z \neq x$ ; i.e., if  $H_1 = H - \{x\}$ , then  $S_1 \mid H_1 = S_2 \mid H_1$ . Since  $H_1$  possesses  $IP(I_1)$ , we have  $I_1(S_1) \mid H_1 = I_1(S_2) \mid H_1$ , and also  $I_1(S_1) \mid OR(I_1) = I_1(S_2) \mid OR(I_1)$ . Since  $H_1 \cup OR(I_1)$  possesses  $IP(I_2)$ , we have  $I_2(I_1(S_1)) \mid H_1 \cup OR(I_1) = I_2(I_1(S_2)) \mid H_1 \cup OR(I_1)$ , and also  $I_2(I_1(S_1)) \mid OR(I_2) = I_2(I_1(S_2)) \mid OR(I_2)$ ; that is,  $I(S_1) \mid H_1 \cup OR(I_1) \cup OR(I_2)$  =  $I(S_2) \mid H_1 \cup OR(I_1) \cup OR(I_2)$ , and since  $IR(I_1) \cup IR(I_2)$ . We have  $IR(I_1) \cup IR(I_2) = IR(I_1) \cup IR(I_2)$ .

If  $IR(I_2) \cap OR(I_1) = \emptyset$ , then let  $x \in OR(I_1) \cup OR(I_2)$ . If  $x \in OR(I_2)$ , then  $x \in OR(J)$  by the above. If  $x \in OR(I_2)$ , then let S be a state such that  $S(x) \neq I_2$  (S)(x). By (c) above, we have  $I_2(S)(x) = J(S)(x)$ , so that  $S(x) \neq J(S)(x)$  and  $x \in OR(J)$ . Thus  $OR(I_1) \cup OR(I_2) = OR(J)$ , since the inequalities hold in both directions.

To show that  $\operatorname{IR}(\mathbb{I}_2) \subseteq \operatorname{IR}(J)$ , under the same hypothesis, we say show, by (a) above, that  $\operatorname{IR}(J)$  possesses  $\operatorname{IP}(\mathbb{I}_2)$ . Let  $S_1$ ,  $S_2 \in \mathcal{J}$  be such that  $S_1 : \operatorname{IR}(J) = S_2 : \operatorname{IR}(J)$ ; then  $J(S_1) \mid \operatorname{OR}(J) = J(S_2) \mid \operatorname{OR}(J)$ . Since  $\operatorname{OR}(\mathbb{I}_2) \subseteq \operatorname{OR}(I_2)$ , we have  $J(S_1) \mid \operatorname{OR}(\mathbb{I}_2) = J(S_2) \mid \operatorname{OR}(\mathbb{I}_2)$ . Applying (c) above, we see that  $\mathbb{I}_2(S_1) \mid \operatorname{OR}(\mathbb{I}_2) = \mathbb{I}_2(S_2) \mid \operatorname{OR}(\mathbb{I}_2)$ . Thus  $\operatorname{IR}(J)$  possesses  $\operatorname{IP}(\mathbb{I}_2)$ , completing the proof of Proposition 7.

The condition  $IR(I_2) \cap OR(I_1) = \emptyset$ , under which stronger statements can be made about input and output regions, is usually less interesting than its opposite. For example, if we perform a "clear and add X" followed by a "store in Y", we are using two instructions in which the input region of the second overlaps (in fact, coincides with) the output region of the first.

Under even stronger conditions, such as when  $IR(I_2) \cap OR(I_1) = \emptyset$  and  $OR(I_1) \cap OR(I_2) = \emptyset$ , we can show that  $IR(J) = IR(I_1) \cup IR(I_2)$ . In fact, a more general statement holds, with a weaker conclusion: If  $OR(I_1) \cap OR(I_2) = \emptyset$ , and  $OR(I_1) \cup OR(I_2) = OR(J)$ , then  $IR(I_1) \subseteq IR(J)$ . To show this, we have only to show, as before, that IR(J) possesses  $IP(I_1)$ . Let  $S_1$ ,  $S_2 \in \mathcal{L}$  be such that  $S_1 \mid IR(J) = S_2 \setminus IR(J)$ , and let  $x \notin OR(I_1)$ ; we must show that  $I_1(S_1Xx) = I_1(S_2)(x)$ . Since  $x \in OR(I_2)$ , we have  $I_1(S_1)(x) = I_2(I_1(S_1))(x) = J(S_1)(x)$ , and also  $I_1(S_2)(x) = J(S_2)(x)$ . Since  $x \in OR(J)$ , we have  $J(S_1)(x) = J(S_2)(x)$ . Therefore  $I(S_1)(x) = I(S_2)(x)$ . The statement made above, that  $IR(I_2) \cap OR(I_1) = \emptyset$  and  $OR(I_1) \cap OR(I_2) = \emptyset$  implies  $IR(J) = IR(I_1) \cup IR(I_2)$ , now follows from all of the precoding.

If  $J': \mathcal{L} \to \mathcal{L}$  is defined by  $J'(S) = I_1(I_2(S))$ , then J = J' (i.e.,  $I_1$  and  $I_2$  will commute) if  $OR(I_1) \cap (IR(I_2) \cup OR(I_2)) = \emptyset$  and  $OR(I_2) \cap (IR(I_1) \cup OR(I_1)) = \emptyset$ .

Under what conditions can we decompose an instruction I:  $A \to A$  into the product of simpler maps from A into A (regardless of whether these are instructions on A)? It should be apparent by now that the "simplest" instructions, in our sense, are those which have small input and output regions. It turns out that, if  $IR(I) \cap OR(I) = \emptyset$ , the instruction I can be written as the product of instructions having output region  $\{x\}$ , for  $x \in OR(I)$ . Even when  $IR(I) \cap OR(I) = \emptyset$ , we can "split off" the elements of OR(I) = IR(I). Thus we reduce to the case  $IR(I) \supseteq OR(I)$ .

PROPOSITION VI. Let  $x \in OR(I) - IR(I)$ . Then I may be written as  $I(S) = I_2(I_1(S))$ , where  $IR(I_1) \subseteq IR(I)$ ,  $IR(I_2) \subseteq IR(I)$ ,  $OR(I_1) = \{x\}$ , and  $OR(I_2) = OR(I) - \{x\}$ .

Proof: Define  $I_1(S)(x) = I(S)(x)$ ,  $I_1(S)(z) = S(z)$ ,  $z \neq x$ ; and define  $I_2(S)(x) = S(x)$ ,  $I_2(S)(z) = I(S)(z)$ ,  $z \neq x$ . Then  $I_2(I_1(S))(x) = I_1(S)(x) = I(S)(x)$ , and, for  $z \neq x$ ,  $I_2(I_1(S))(z) = I(I_1(S))(z)$ . By lemma (b) in Proposition V, since  $M = \{x\} \supseteq IR(I)$  and  $I_1(S) \mid M = \{x\} = S \mid M = \{x\} \}$ , we have  $I(I_1(S)) \mid K = \{x\} = I(S) \mid K = \{x\} \}$ . Thus  $I(S) = I_2(I_1(S))$ . It is clear from the definitions that  $OR(I_1) \subseteq \{x\}$  and  $OR(I_2) \subseteq OR(I) = \{x\} \}$ . By Proposition V,  $OR(I) \subseteq OR(I_1) \cup OR(I_2)$ ; intersecting both sides of this statement first with  $\{x\} \}$  and then with  $M = \{x\} \}$ , we obtain  $\{x\} \subseteq OR(I_1)$  and  $OR(I) = \{x\} \subseteq OR(I_2)$ , so that  $OR(I_1) = \{x\} \}$  and  $OR(I_2) = OR(I) - \{x\} \}$ . If  $S_1, S_2 \in \mathcal{A}$  are such that  $S_1 \mid IR(I) = S_2 \mid IR(I)$ , then  $I(S_1) \mid OR(I) = I(S_2) \mid OR(I)$ , so that  $I_1(S_1)(x) = I_1(S_2)(x)$ , and  $I_2(S_1) \mid OR(I) - \{x\} = I_2(S_2) \mid OR(I) - \{x\} \}$ . Hence IR(I) satisfies both input properties  $IP(I_1)$  and  $IP(I_2)$ , and  $IR(I_1) \subseteq IR(I)$ ,  $IR(I_2) \subseteq IR(I)$ .

### Products and Restructuring

In this chapter, we shall use computers as in Definition F. We would like to answer the questions: Can we have a product of two computers? On we have a subcomputer of a computer? It turnes out that there is another question, related to these two, but of greater interest than either of them.

Since the set of states  $\mathcal{S}$  of a computer is a product over an index set M, it would seem that two computers can be combined by taking a product over both index sets. If  $\mathcal{S}_1$  and  $\mathcal{S}_2$  are the sets of states of the two computers, and  $\mathcal{S}$  is the set of states of the product, then  $\mathcal{S}=\mathcal{S}_1\times\mathcal{S}_2$ ; and if  $\mathbf{I}_1\colon\mathcal{S}_1\to\mathcal{S}_1$  and  $\mathbf{I}_2\colon\mathcal{S}_2\to\mathcal{S}_2$ , then we may define, in a natural way,  $\mathbf{I}_1\times\mathbf{I}_2\colon\mathcal{S}_1\times\mathcal{S}_2\to\mathcal{S}_1\times\mathcal{S}_2$ .

DEFINITION G. Let  $(M_1, \mathcal{A}_1, \mathcal{A}_1)$  and  $(M_2, \mathcal{A}_2, \mathcal{A}_2)$  be two computers in the sense of Definition F; that is, for each element of  $M_1$  and of  $M_2$  we have defined a set  $B_x$  and an element  $b_x$ , and  $\mathcal{A}_1$  ( $\mathcal{A}_2$ ) is the restricted product, over  $M_1$  (over  $M_2$ ), of the  $B_x$  relative to the  $b_x$ . Let  $\mathcal{A}$  be the restricted product of the  $B_x$  relative to the  $b_x$  over  $M_1$  ()  $M_2$ . Then  $\mathcal{A} = \mathcal{A}_1 \times \mathcal{A}_2$ . If  $I_1 \in \mathcal{A}_1$  and  $I_2 \in \mathcal{A}_2$ , we define the map  $I_1 \times I_2$ :  $\mathcal{A} \to \mathcal{A}$  by  $(I_1 \times I_2)(S_1, S_2) = (I_1(S_1), I_2(S_2))$ , and we denote the set of all such  $I_1 \times I_2$ , for  $I_1 \in \mathcal{A}_1$ ,  $I_2 \in \mathcal{A}_2$ , by  $\mathcal{A}_1 \times \mathcal{A}_2$ . Then the computer  $(M_1 \cup M_2, \mathcal{A}_1, \mathcal{A}_1)$  is the product of the two computers  $(M_1, \mathcal{A}_1, \mathcal{A}_1)$  and  $(M_2, \mathcal{A}_2, \mathcal{A}_2)$ .

respectively, of the input and output regions of I are the unions, respectively, of the input and output regions of I<sub>1</sub> and I<sub>2</sub>. Computers which are porducts, in this form, almost never occur in the real world. This is so even though our definition, despite its length, is the most natural definition we can make of a product computer. Several situations with real computers—for example, the addition of extra memory to an already existing computer—almost correspond to the taking of a product. It may be argued that the addition of extra memory always involves some complexity of a purely technical nature. But there is another perfectly good reason, and this is that product instructions are in a sense incomplete. Data can never be moved, under a product instruction, from the memory M<sub>1</sub> to the memory M<sub>2</sub>, or vice versa, despite the fact that the input and output regions of the product may intersect both M<sub>1</sub> and M<sub>2</sub>. We say that M<sub>1</sub> cannot "affect" M<sub>2</sub>. This is one of the bases for our introduction of affected regions in the next chapter.

If M is the product of M<sub>1</sub> and M<sub>2</sub>, then M<sub>1</sub> and M<sub>2</sub> are certainly "subcomputers" of M. As a matter of fact, this kind of subcomputer is the only kind that makes sense, unless we change our definition of product (for example, to cover enlargement of the sets B<sub>x</sub>).

DEFINITION H. Let  $(M, \mathcal{L}, \mathcal{L})$  be a computer in the sense of Definition F, and let M' be a subset of M. Let  $\mathcal{L}'$  be the restricted product, over the index set M', of the B relative to the b (defined by M and  $\mathcal{L}$ ). Suppose that for each instruction I  $\in \mathcal{L}$  there exists a map I':  $\mathcal{L}' \to \mathcal{L}'$ , such that I'(S | M') = (I(S)) | M' for each S  $\in \mathcal{L}$ . Let  $\mathcal{L}'$  be the collection of all such  $\mathcal{L}$ . Then  $(M', \mathcal{L}', \mathcal{L}')$  is a <u>subcomputer</u> of  $(M, \mathcal{L}, \mathcal{L})$ .

In particular, if  $(M, \mathcal{L}, \mathcal{L})$  is the product of  $(M_1, \mathcal{L}_1, \mathcal{L}_1)$  and  $(M_2, \mathcal{L}_2, \mathcal{L}_2)$ , then  $(M_1, \mathcal{L}_1, \mathcal{L}_1)$  and  $(M_2, \mathcal{L}_2, \mathcal{L}_2)$  are, in this sense, subscarputors of  $(M, \mathcal{L}, \mathcal{L})$ . The question may be raised as to whether there is a condition on the input and output regions of the instructions of which would be necessary and sufficient for subcomputers of a certain form to exist. There is a condition, but it is on the affected regions, which are defined in Chapter 7.

Let  $(M_0 \mathcal{L}_{\mathcal{A}} \mathcal{L})$  be a computer and let  $\mathcal{L}$  be a decomposition of M, that is, a class of disjoint non-empty subsets of M whose union is M. For each  $D \in \mathcal{D}$ , let  $B_D$  be the restricted product of the  $B_X$ , relative to the  $b_X$ , over D as an index set, and let  $b_D$  be the element of this restricted product whose co-ordinate on the component  $B_X$  is  $b_X$ . Let  $\mathcal{L}'$  be the restricted product of the  $B_D$  relative to the  $b_D$ , over D as an index set. Then there is a canonical one-to-one correspondence between  $\mathcal{L}$  and  $\mathcal{L}'$ ; to the element of  $\mathcal{L}$  whose co-ordinate at  $X \in M$  is  $B_X$  corresponds the classest of  $\mathcal{L}'$  whose co-ordinate at  $X \in M$  is  $B_X$  corresponds the classest of  $\mathcal{L}'$  whose co-ordinate at  $X \in M$  is a number of  $B_D$  whose co-ordinate at  $X \in M$  is a possible to speak of  $\mathcal{L}$  as a set of maps  $X : \mathcal{L}' \to \mathcal{L}'$ .

DESTRICTION J. Let  $(M, \mathcal{L}, \mathcal{Q})$  be a computer, and let  $\mathcal{Q}$  be an arbitrary decomposition of M as above. Then  $\mathcal{Q}$  is called a <u>memory structure</u> for  $(M, \mathcal{L}, \mathcal{L})$ . The process of passing from  $(M, \mathcal{L}, \mathcal{Q})$  to  $(\mathcal{Q}, \mathcal{L}', \mathcal{L})$ , as above, is called <u>restructuring</u>  $(M, \mathcal{L}, \mathcal{L})$ .

If  $I \in \mathcal{J}$ , then I has imput and output regions as an instruction of  $(M, \mathcal{J}, \mathcal{J})$  and as an instruction of  $(\mathcal{D}, \mathcal{J}', \mathcal{J})$ . The regions in  $\mathcal{D}$  are found by including any member of  $\mathcal{D}$  which contains a member of the corresponding regions in M.

the first place, the restructured computer has the same states as the original computer, and therefore restructuring is not a physical process (such as a change in hardware) so much as a logical reorientation of the way we view the computer. And it is a process in which computer programmers engage quite often. If a block of data in a binary computer is alphanumeric, for example, we think of the block as broken up into six-bit characters, which is equivalent to taking a memory structure in which the six-bit groups are sets occurring in the decomposition  $\mathcal{O}$ . Over these sets the  $\mathcal{B}_{\mathcal{D}}$  have order 64. Again, we can take a memory structure in which computer words are members of the decomposition. Over a computer word  $\mathcal{D}$ , the set  $\mathcal{B}_{\mathcal{D}}$  will have cardinality  $2^{36}$  (or  $2^{b}$ , where there are  $\mathcal{D}$  bits in a word). If the word is floating point, and we ignore the fact that decimals are given to only a finite accuracy, we can think of  $\mathcal{B}_{\mathcal{D}}$  as being the set of real numbers, thus bringing in an "idealized" computer.

The concept of restructuring also answers a question we may have had about the property (P1). Given a 4-tuple (M, B, L, J), as in Definition C, in which Loos not satisfy (P1), but "almost" does so, and at the same time does satisfy (P2). How many of the properties of the set of states of a computer does L'almost" preserve? Putting this question on a rigorous basis, let us look at all subsets M' of M, melative to which (P1) is always satisfied. By the following theorem, this set always consists of the

members of a decomposition O and their unions. The concept of restructuring makes seems even without (1), and so we may restructure our 'almost-computer" by the decomposition O -- and the result will be a computer.

PROPOSITION VII. Let M and B be arbitrary sets, let  $\mathcal{L}$  be a set of maps S: M  $\rightarrow$  B which satisfies (P2) (as in Definition C), and let  $\mathcal{L}$  be a set of maps I:  $\mathcal{L} \rightarrow \mathcal{L}$ . Let  $\mathcal{P}$  be a class of subsets of M, as follows: P  $\in \mathcal{P}$  if and only if, given  $S_1$ ,  $S_2 \in \mathcal{L}$ , there exists  $S_3 \in \mathcal{L}$ , with  $S_3(\pi) = S_1(\pi)$  for  $\pi \in \mathcal{P}$  and  $S_3(\pi) = S_2(\pi)$  for  $\pi \notin \mathcal{P}$ . Then  $\mathcal{P}$  consists of the members of a decomposition  $\mathcal{O}$  of M, and their unions. If (M,  $\mathcal{L}$ ,  $\mathcal{L}$ ) is restructured under  $\mathcal{O}$ , then ( $\mathcal{O}, \mathcal{L}', \mathcal{L}$ ), as in Definition J, is a computer.

Proof: To show that P consists of the members of Q and their unions, it suffices to show that P is closed under the formation of complements and arbitrary intersections. For let  $x \in M$ , and let  $D_x$  be the intersection of all members of P containing x; there exist such members, in fact, M itself is one of them.  $D_x \in P$  and  $x \in D_x$ . If  $D_y$  and  $D_z$  are not identical, say  $D_y = D_z \neq \emptyset$ , there exists  $x \in D_y$ ,  $x \notin D_z$ ; then  $D_y \cap (M - D_z)$  is in P, contains y, and is contained in  $D_y$ , and is therefore equal to  $D_y$ , so that  $D_y \cap D_z = \emptyset$ . Hence the  $D_x$  are either disjoint or identical. By De Morgan's laws, P is closed under the formation of arbitrary unions, so that every union of sets  $D_x$  is in P; if  $P \in P$  and  $x \in P$ , then  $D_x \subseteq P$ , so that P is a union of sets  $D_x$ , and their unions.

That P is closed under the formation of complements is obvious. If  $s_1$ ,  $s_2 \in \mathcal{A}$ , and contains  $s_3$ :  $s_3 \mid P = s_1 \mid P$ ,  $s_3 \mid M-P = s_2 \mid M-P$ , and  $s_4$ :  $s_4 \mid Q = s_1 \mid Q$ ,  $s_6 \mid M-Q = s_2 \mid M-Q$ , then  $\mathcal{A}$  contains  $s_5$ :  $s_5 \mid Q = s_3 \mid Q$ ,  $s_5 \mid M-Q = s_2 \mid M-Q$ , from which it follows that  $s_5 \mid P \cap Q = s_1 \mid P \cap Q$ ,  $s_5 \mid M-Q \cap Q = s_2 \mid M-Q \cap Q = s_3 \mid M-Q \cap Q = s_4 \mid P \cap Q$ . Hence P is closed under finite intersections.

To prove the last statement of Proposition VII, it is first necessary to redefine restructuring in terms of Definition C of a computer. If  $(M, B, \mathcal{A}, \mathcal{A})$  is a computer under Definition C (with the possible exception of property (Pl.)), and  $\mathcal{A}$  is a decomposition of M, then we may define the restructured computer  $(\mathcal{A}, B^i, \mathcal{A}^i, \mathcal{A})$  as follows (again possibly without (Pl)). The set of all distinct  $S \mid M^i$ , for  $M^i \subseteq M$ , will be denoted by  $\mathcal{A} \mid M$ . Then  $B^i$  is the union of all  $\mathcal{A} \mid D_X$ , where  $D_X \in \mathcal{A}$  and  $X \in D_X$ , and  $\mathcal{A}^i$  is the set of all maps  $S \colon \mathcal{A} \to B^i$  such that  $S(D_X) \in \mathcal{A} \mid D_X$  for all  $D_X \in \mathcal{A}$ . Now, if  $\mathcal{A}$  satisfies (P2), but not necessarily (P1), and if  $\mathcal{A}$  and  $\mathcal{A}$  are constructed as above, then the restructured computer  $(\mathcal{A}, B^i, \mathcal{A}^i, \mathcal{A})$  will be such that  $\mathcal{A}^i$  satisfies (P1) relative to  $\mathcal{A}$ . For let  $S_1^i$ ,  $S_2^i \in \mathcal{A}^i$  and  $\mathcal{A}^i \subseteq \mathcal{A}^i$  be are to verify that  $S_3^i \in \mathcal{A}^i$ , where  $S_3^i(D)$ , for  $D \in \mathcal{A}^i$ , and  $S_3^i(D) \subseteq S_2^i(D)$ , for  $D \notin \mathcal{A}^i$ . If  $S_1$ ,  $S_2 \in \mathcal{A}^i$  correspond to  $S_1^i$ ,  $S_2^i \in \mathcal{A}^i$ , and  $S_3^i(D) \subseteq S_2^i(D)$ , for  $S_1^i \subseteq \mathcal{A}^i$  is the union of all  $S_1^i \subseteq \mathcal{A}^i$ , then, by construction of  $\mathcal{A}^i \cap \mathcal{A}^i \subseteq \mathcal{A}^i$  and

and there exists a state  $S_3 \in \mathcal{A}$  with  $S_3(x) = S_1(x)$ ,  $x \in \mathbb{N}^s$ , and  $S_3(x) = S_2(x)$ ,  $x \neq \mathbb{M}^s$ . This state  $S_3$  corresponds to  $S_3' \in \mathcal{A}'$ , completing the proof of Proposition VII.

### 7. Affected Regions

Affected and affecting regions as we define them here, are a substructure on the input and output regions of an instruction. According to our definitions, the input region OR(I) is the set of all elements of memory which can be affected by I; the input region IR(I) is the set of all such elements which can affect OR(I). Given a subset of IR(I), what elements can affect it? We give precise definitions of these concepts.

DEFINITION K. Let (M. B. & ....) be a computer and let I be an instruction on I. Then

AR(M\*, I) =

$$\{x \in OR(I): \exists s_1, s_2 \in \mathcal{L} : s_1(z) \text{ for } z \in TR(1), \\ z \notin M^c, \text{ and } I(s_1)(x) \neq I(s_2)(x)\}$$

for each set M' C IR(I), and

$RA(M^0, I) = \{x \in IR(I): AR(\{x\}, I) \cap M^0 \neq \emptyset \}$ for each set  $M^0 \subseteq OR(I)$ . We call  $AR(M^0, I)$  an <u>affected region</u>, or the <u>region affected by  $M^0$  under I</u>, and we call  $RA(M^0, I)$  an <u>affecting region</u> or the <u>region affecting  $M^0$  under I</u>, or the <u>region which affects  $M^0$  under I</u>.

Every non-null subset of IR(I) affects some non-null subset of OR(I), otherwise there would exist  $L \subseteq IR(I)$  such that  $S_1 \setminus IR(I) - L = S_2 \setminus IR(I) - L$  implies  $I(S_1) \setminus OR(I) = I(S_2) \setminus OR(I)$ , and the set IR(I) - L would possess IP(I), contrary to the statement that IR(I) is the intersection of all subsets of M possessing IP(I). Also,  $AR(\emptyset, I) = \emptyset$  and  $RA(\emptyset, I) = \emptyset$ ; the second statement is trivial, and the first is just a restatement of Propositions X and II. It follows directly from the definition that, if  $M^1 \subseteq M^1$ , then  $AR(M^1, I) \subseteq AR(M^1, I)$ , and thus  $AR(A \cap B, I) \subseteq AR(A, I) \cap$

AR(B, I) and AR(AUB, I)  $\supseteq$  AR(A, I)  $\cup$  AR(B, I). In fact, AR(AUB, I) ... AR(A, I)  $\cup$  AR(B, I); to show the inequality in the opposite direction, let  $S_1$ ,  $S_2 \in \mathcal{S}$  be such that  $S_1 \mid \text{IR}(I) - (A \cup B) = S_2 \mid \text{IR}(I) - (A \cup B)$ . Let  $S_3 \in \mathcal{S}$  be defined by  $S_3 \mid A = S_1 \mid A$ ,  $S_3 \mid M - A = S_2 \mid M - A$ . Then  $S_3 \mid \text{IR}(I) - A = S_2 \mid \text{IR}(I) - A$ , and, since IR(I) - (A \cup B)  $\cup$  (A - E) = IR(I) - B,  $S_3 \mid \text{IR}(I) - B = S_1 \mid \text{IR}(I) - B$ . Thus  $I(S_1) \mid \text{OR}(I) - \text{AR}(B, I) = I(S_3) \mid \text{OR}(I) - \text{AR}(B, I)$  and  $I(S_2) \mid \text{OR}(I) - \text{AR}(A, I) = I(S_3) \mid \text{OR}(I) - \text{AR}(A, I)$ , and therefore  $I(S_1) \mid \text{OR}(I) - (\text{AR}(A, I) \cup \text{AR}(B, I))$ . This shows that a member of AR(A \cup B, I) cannot lie outside AR(A, I) \cup AR(B, I), i.e., AR(A \cup B, I) \subseteq AR(A, I) \cup AR(B, I).

It therefore follows that all the affected regions of an instruction I are determined by the affected regions of single elements  $x \in IR(I)$ . These regions can be single elements of OR(I), or they can be the entire output region. In the instruction (ADD Y) on a computer with an accumulator, the input region is YUAC, and the output region is AC; the affected region of each bit position of Y (or of AC) is the  $\infty$  rresponding bit position of AC, together with all the bit positions to its left (provided there is no provision for overflow). If there is end-around carry, the affected region of every bit position of Y or AC is the entire AC.

On the other hand, some elements of OR(I) may not be affected at all; i.e., we may have  $AR(IR(I), I) \neq OR(I)$ . This may happen, in particular, for an instruction in which  $IR(I) = \emptyset$ , that is, a. constant instruction (such as "store zero"). In such an instruction  $S \mid OR(I)$  is a constant, i.e., independent of S. Every instruction may be written as an instruction for

which AR(IR(I), I) = OR(I), followed by a constant instruction.

We may now formalize the statement we made in the last chapter about the product of two computers.

PROPOSITION VIII. Let  $(M_1, \mathcal{J}_1, \mathcal{J}_1)$  and  $(M_2, \mathcal{J}_2, \mathcal{J}_2)$  be computers, and let  $(M, \mathcal{J}, \mathcal{J})$  be their product. Let  $I = I_1 \times I_2$  be an instruction of  $\mathcal{J}$ , where  $I_1 \in \mathcal{J}_1$  and  $I_2 \in \mathcal{J}_2$ . Then  $IR(I) = IR(I_1) \cup IR(I_2)$  and  $OR(I) = OR(I_1) \cup OR(I_2)$ . Furthermore,  $AR(IR(I_1), I) = OR(I_1)$  and  $AR(IR(I_2), I) = OR(I_2)$ . Thus, under a product instruction, no member of either memory can affect the other.

The proof is by direct computation.

As an illustration, suppose we take M<sub>1</sub> to be the core memory and the registers of a real computer,  $\checkmark_1$  to be the set of all maps from M<sub>1</sub> to  $\{0, 1\}$ , and  $\checkmark$  to be the set of all instructions in this computer that can be defined without reference to a location counter (arithmetic, logical, shift, floating point instructions, etc.) Let us take M<sub>2</sub> to consist of one element, called a <u>location counter</u>;  $\checkmark_2$  consists of all maps from M<sub>2</sub> to  $\{0, 1, ..., c-1\}$ , where c is the size of core, and  $\checkmark$  consists of one instruction I which increases the counter by 1: I(S)(M<sub>2</sub>) = S(M<sub>2</sub>)+1. If we take the product of these two computers, we get nothing essentially better than what we had to start with: each instruction increases the value of the location counter by 1, and that is all. We obtain an improvement when we let M<sub>1</sub> affect M<sub>2</sub>: letting the location counter affect the contents of core (by decoding the instruction stored at the given location). We obtain an even further improvement when we let M<sub>1</sub> affect M<sub>1</sub>. An instruction

which is such that the contents of core affect the location counter is known as a conditional jump (or transfer, or branch).

We obtain another proposition on subcomputers.

PROPOSITION IX. Let  $(M, \mathcal{S}_n \mathcal{I})$  be a computer, and let M' be a sub-set of M. Let  $\mathcal{S}'$  be the restricted product of the  $B_{\chi}$  relative to the  $b_{\chi}$  for  $\chi \in M'$  as in Definition H. Then there exists a subcomputer  $(M', \mathcal{S}', \mathcal{I}')$  of  $(M, \mathcal{I}, \mathcal{I})$  if and only if, for each  $\chi \in \mathcal{I}$  and each  $\chi \in IR(\chi)$ ,  $\Lambda R(\chi \chi)$ .

Thus M' is the memory of a subcomputer if and only if M' is never affected by M-M' (although M' can affect M-M').

Proof: Suppose the condition holds. Let  $I \in \mathcal{L}$  and define I':  $\mathcal{L}' \to \mathcal{L}'$  as follows. Let  $S \mid M' \in \mathcal{L}'$ , let  $S_1 \in \mathcal{L}$  be such that  $S_1 \mid M' = S \mid M'$  (e.g.  $S_1 = S$ ) and defined  $I'(S \mid M') = (I(S_1)) \mid M'$ . If  $S_2 \in \mathcal{L}$  is another state with  $S_2 \mid M' = S \mid M'$ , then, since no element of M' is in AR( $\{x\}$ , I) for  $x \notin M'$ , we have  $(I(S_1)) \mid M' = (I(S_2)) \mid M'$ ; thus the instruction I, as above, is well defined. If  $\mathcal{L}$  is the class of all such I', then  $(M', \mathcal{L}', \mathcal{L}')$  is a subcomputer of  $(M, \mathcal{L}, \mathcal{L})$ . Conversely, if  $y \in M' \cap AR(\{x\}, I)$ , where  $x \notin M'$ , and  $S_1, S_2 \in \mathcal{L}$  are such that  $S_1 \mid M - \{x\} = S_2 \mid M - \{x\}$  (so that in particular  $S_1 \mid M' = S_2 \mid M'$ ) and  $I(S_1)(y) \neq I(S_2)(y)$ , then no instruction I' can be defined on M' such that  $I'(S \mid M') = (I(S)) \mid M'$  for each  $S \in \mathcal{L}$ .

## 8. A Test for the Validity of an Algorithm

Let us consider two instructions,  $I_1$  and  $I_2$ . If  $A \subseteq IR(I_1)$ , we may calculate  $AR(A, I_1) = A^*$ , and then  $AR(A^*, I_2) = A^*$ . What relation does  $A^*$  have to  $AR(A, I_1I_2)$ ? The trouble is that these regions may not all be defined; for instance,  $A^*$  may not be contained in  $IR(I_2)$ . For this end other reasons, we will need a definition of affected region which does not depend on IR(I) and OR(I). Fortunately, this definition has a simple relation to the preceding one.

DEFINITION L. Let (M, B,  $\mathcal{A}$ ,  $\mathcal{A}$ ) be a computer and let I be an instruction of  $\mathcal{A}$ . Then

$$AR_2(M^1, 1) = \{ x \in M : \exists S_1, S_2 \in \mathcal{A}, S_1(x) = S_2(x) \text{ for } x \notin M^1 \text{ and } 1(S_1)(x) \neq 1(S_2)(x) \}$$

for each subset M° \( \simeq \text{M.} \) We call AR2(M°, I) the second affected region of M° under I.

Now let  $I_1$  and  $I_2$  be two instructions and let I be their product:  $I(S) = I_2(I_1(S))$ . We verify the relation

$$AR_2(M', I) \subseteq AR_2(AR_2(M', I_1), I_2)$$

for each subset  $M' \subseteq M$ . It is easier to do this if we first characterize  $AR_2(M', I)$  in a different way. We recall that IR(I) is the intersection of all subsets N of M which possess the predicate IP(I): if  $S_1 \mid N = S_2 \mid N$ , then  $I(S_1) \mid OR(I) = I(S_2) \mid OR(I)$ . Similarly, we may characterize  $AR_2(M', I)$ : if  $S_1 \mid M-M' = S_2 \mid M-M'$ , then  $I(S_1) \mid M-N = I(S_2) \mid M-N$ . For x is not in this intersection, if and only if there exists such a set N to which x

does not belong, i.e.,  $S_1 \mid M-M' = S_2 \mid M-M' \mid mplies I(S_1)(x) = I(S_2)(x)$  (since  $x \in M-M$ ); that is, if and only if  $x \notin AR_2(M', I)$ .

It remains to show that  $AR_2(M', I)$  itself possesses  $AP_2(M', I)$ ; this is left as an exercise along the lines of Propositions I and II, using properties (PI) and (P2) of S. It follows from this that a set  $N\subseteq M$  possesses  $AP_2(M', I)$  if and only if it contains  $AR_2(M', I)$ , since  $AP_2(M', I)$  is clearly preserved under the taking of supersets. Now the verification of our equation is straightforward. If  $S_1 \mid M-M' = S_2 \mid M-M'$ , then  $I_1(S_1) \mid M-AR_2(M', I_1) = I_1(S_2) \mid M-AR_2(M', I)$ , so that  $I_2(I_1(S_1)) \mid M-AR_2(AR_2(M', I_1), I_2)$ .  $I_1(M', I_2)$  possesses  $IP_2(M', I)$ , and thus  $IR_2(M', I) \subseteq IR_2(AR_2(M', I_1), I_2)$ .

We now give the relation between AR(M', I) and  $AR_2(M', I)$  when  $M' \subseteq IR(I)$ . In order to do this we must first introduce the unit component of a computer.

DEFINITION M. Let  $(M, \mathcal{L}, \mathcal{L})$  be a computer as in Definition F, and let  $Z \subseteq M$  be the set of all elements  $x \in M$  such that  $B_{\chi}$  has exactly one element. Then Z is the <u>unit component</u> of  $(M, \mathcal{L}, \mathcal{L})$ .

(In the same way, we could speak of the binary component, the decimal component, etc. )

PROPOSITION X.  $AR_2(M^4, I) = AR(M, I) \cup (M^4 - OR(I)-Z)$ , where Z is the unit component of  $(M, \mathcal{A}, \mathcal{A})$ .

Proof: Let  $S_1$ ,  $S_2 \in \mathcal{L}$  be such that  $S_1 \mid M-M' = S_2 \mid M-M'$ . Then  $I(S_1) \mid M-M'-OR(I) = S_1 \mid M-M'-OR(I) = S_2 \mid M-M'-OR(I) = I(S_2) \mid M-M'-OR(I)$ ; also  $I(S_1) \mid OR(I)-AR(M', I) = I(S_2) \mid OR(I)-AR(M', I)$  since  $S_1 \mid IR(I)-M' = S_2 \mid IR(I)-M'$ ; finally,  $I(S_1) \mid Z = I(S_2) \mid Z$ . This shows that  $(A \cup OR(I)) \cap I(I)-AR(M', I) \cap I(I)$  or  $I(I)-AR(M', I) \cap I(I)$  possesses I(I). And since I(I).

OR(I), this is equal to AR(M', I)  $\cup$  (M' - OR(I) - Z). Thus  $AR_2(M', I) \subseteq AR(M', I) \cup (M' - OR(I) - Z)$ . Conversely, let  $x \in AR_2(M', I)$ ; then for every two states  $S_1$ ,  $S_2 \in \mathcal{L}$  with  $S_1 \mid M-M' = S_2 \mid M-M'$ , we have  $I(S_1)(x) = I(S_2)(x)$ . This means that  $x \in AR(M', X)$ ; also if we choose  $S_1 \mid M-M' = S_2 \mid M-M'$ ,  $S_1(x) \neq S_2(x)$ , as is possible for  $x \in M'-Z$ , and if in addition  $x \notin OR(I)$ , we have  $I(S_1)(x) = S_1(x)$ ,  $I(S_2)(x) = S_2(x)$ , so that  $I(S_1)(x) = I(S_2)(x)$ , and  $x \in AR_2(M', I)$ . Therefore  $AR(M', I) \cup (M' - OR(I)-Z) \subseteq AR_2(M', I)$ . This completes the proof.

As a corollary, we may determine that second affected regions have the same connective properties as ordinary affected regions. For instance, if  $M' \subseteq M''$ , then  $AR_2(M', I) \subseteq AR_2(M'', I)$ ; also  $AR_2(M' \cup M'', I) = AR_2(M'', I) \cup AR_2(M'', I)$ .

These facts may be applied to computer algorithms, i.e., programs.

Let us consider a program which has no jumps or conditional jumps, so that it can be thought of as just a sequence of instructions. Such a program might be one to determine the value of x according to the quadratic formula. The coefficients A, B, and C, the solutions ROOT1 and ROOT2, the accumulator AC, and the temporary register TEMP are all subsets of the memory M of the computer. Now the composition of all the instructions in the sequence is itself a map I: I which may or may not be an instruction on the computer), and as such has its own input, output, and affected regions. If the instruction I determines the two values ROOT1 and ROOT2 from the coefficients A, B, and C, then ROOT1 and ROOT2 should be affected by A, B, and C, and by nothing else. By the use of the formula for second affected regions, and Proposition X, we may derive a mechanical test for this condition. It will never absolutely guarantee that I

errors of the type which cause the resulting (incorrect) algorithm to have the wrong affected regions. In an incorrect algorithm, for example, NOCTI might not be affected by A at all. This will happen, in particular, when one of the partial results has been overstition--or, in programmers' slang, "clobbered"--at some stage of the algorithm.

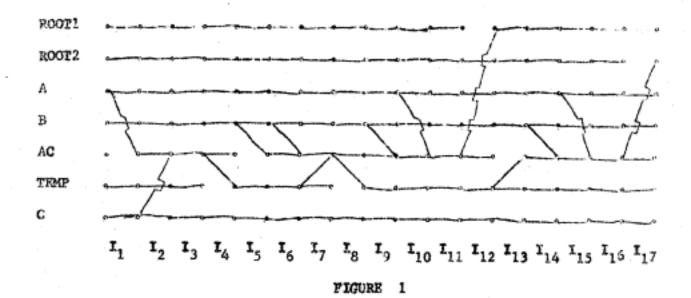

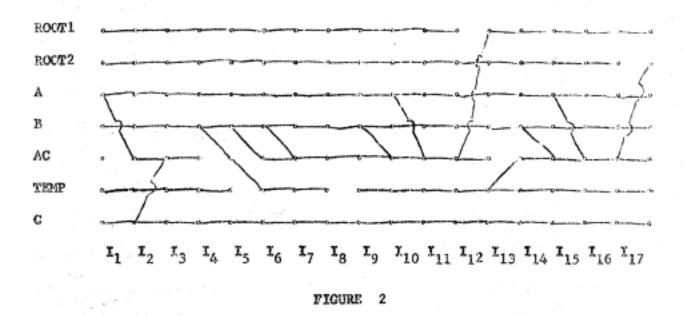

A diagram of this test, for the special case of the quadratic formula, is given in Figure 1. (The procedure could also, of course, be programmed.) The various relevant subsets of M are listed at the left; the steps in the elgorithm are listed at the top. Each subset at each stage is represented by a dot. Each dot is connected by lines to all the dots at the next stage representing the second affected region of the subset given by that dot, and, to only those dots. A dot in the left-hand row can affect a dot in the right-hand row, only if there is a connected forward path from one to the other. Note that in Figure 1 there is, in fact, a connected forward path from each of A, B, C to each of ROOT1, ROOT2. Figure 2 shows what happens when two of the instructions (in this case I4 and I5) are interchanged. In this case there is no commetted path from C to ROOT1 or ROOT2, and we know immediately that the resulting algorithm must be incorrect. The algorithm proceeds as follows:

| 11: | Bring the value of A to AC. (Speaking in formal terms, I1(S) AC = S A.) | IR(I <sub>1</sub> ) | OR(I <sub>1</sub> ) |

|-----|-------------------------------------------------------------------------|---------------------|---------------------|

| 12: | Multiply the value of C by the contents of AC.                          | CUAC                | AC                  |

| 131 | Multiply the value of AC by 4.                                          | AC                  | AC                  |

| 142 | Store AC in the temporary cell TEMP.                                    | AC                  | TEMP                |

| 151 | Bring the value of B to AC.                                             | В                   | VC                  |

|                    |                                                                            | $IR(I_{\hat{\chi}})$ | or(ti) |

|--------------------|----------------------------------------------------------------------------|----------------------|--------|

| 1.53               | Multiply the value of B by the contents of AC.                             | BUAC                 | E.C.   |

| 17:                | Subtract the value in THMP from the contents of AC.                        | TEMP<br>U AC         | AG     |

| 13:                | Take the square roots of the value in AC and transmit them to AC and TEMP. |                      |        |

| $\mathfrak{r}_9$ : | Subtract the value of B from the contents of AC.                           | BUAC                 | AC     |

| 1.10               | Divide the value in AC by the value in A.                                  | AUAC                 | ΛC     |

| 1,11:              | Divide the value in AC by 2.                                               | ΛC                   | AC     |

| 112:               | Store the value of AC as ROCT1                                             | AC                   | ROOT1  |

| 1,3:               | Bring the value of the cell TEMP to the AC.                                | TEMP                 | AC     |

| 1,48               | Subtract the value of B from the contents of AC.                           | TEMP<br>U AC         | AC     |

| 1,5:               | Divide the value in AC by the value in A.                                  | AU AC                | AC     |

| 1 <sub>16</sub> :  | Divide the value in AC by 2.                                               | VC                   | AC     |

| 1,7:               | Store the value of AC as ROOT2                                             | AC                   | EOOT2  |

We may also verify that  $AR(M^1, I)$  is the intersection of all subsets  $Q \subseteq OR(I)$  which possess the property  $AP(M^1, I)$ : if  $S_1 \mid IR(I)-M^1 = S_2 \mid IR(I)-M^1$ , then  $I(S_1) \mid OR(I)-Q = I(S_2) \mid OR(I)-Q$ . The intersection of two sets possessing  $AP(M^1, I)$  possesses  $AP(M^1, I)$  by virtue of property (P1), and the intersection of an arbitrary number of sets possessing  $AP(M^1, I)$  possesses  $AP(M^1, I)$  by virtue of property (P2). Thus a set possesses  $AP(M^1, I)$  if and only if it contains  $AR(M^1, I)$ . The entire subject of input, output, and affected regions can, in fact, be introduced by means of properties such as these, rather than directly as in Definitions B and K.

#### Transmission

The instructions defined below move data from one part of a computer memory to snother in an unchanged fashion.

DEFINITION N. Let (M, B,  $I_*J_*$ ) be a computer, and let G: M  $\rightarrow$  M be any map. The map I:  $I \rightarrow J_*$ , defined by I(S)(x) = S(G(x)), is the transmission instruction induced by G.

The following types of instructions are transmission instructions, induced by various maps G: move; load; store; block transfer; circular shift; sign extending shift; swap or exchange. A move instruction involving two single elements x1, x2 € M, which moves the data in x1 to x2, is induced by a map G such that  $G(x_2) = x_1$ , G(z) = z for  $z \neq x_2$ . A move instruction involving all the bits of two 6-bit words, x, ..., x, and y1, ..., yd, which moves the data in the x, to the y, is induced by a map G such that  $G(Y_i) = x_i$ ,  $1 \le i \le d$ , and G(z) = z for  $z \ne y_i$ . The same is true of a block transfer. "Load" and "store" are synonyms for "move," with a register involved as the output region for a "load," or as the input region for a "store." In all these cases IR(I) ( OR(I) = # (except possibly for the block transfer). A circular shift of a d-bit register x0, ...,  $x_{d-1}$ , by k bits to the left,  $k \le d$ , is induced by a map G such that  $G(x_i)$ = n, where j = i+k (mod d). A sign extending shift of this register by k bits to the right is induced by a map C such that G(x1) = x1, where j = max(0, 1-k). An exchange of two elements x and x is induced by a map G which permutes x, and x,; the same idea may be extended to the case of two registers. In these last three cases IR(I) = OR(I).

If the transmission instruction I is induced by the map G, then  $IR(I) = \left\{G(x) \in M: \ G(x) \neq x\right\}; \ OR(I) = \left\{x \in M: \ G(x) \neq x\right\}; \ \text{and}$   $AR_2(M^2, I) = G^{-1}(M^2). \ \text{This is a further example of the fact that second affected regions are often easier to calculate than ordinary affected regions.}$

## Yuput-Ourput Devices and Machine Theory

Although the set M in a computer is referred to as the "memory," it is well to remember that, strictly speaking, H is just an abstract net, which may not be a computer memory. In fact, we will construct, in the next chapter, computers with "memories" that have nothing to do with hardware. This point is further underscoved by the fact that, when we are discussing input and output devices, the most effective model seems to involve including the entire (infinite) input and/or output sequence as part of the set M. The computer, of course, cannot make use of such an infinite "memory", other than to move it forward by one or more positions.

A linear input device can be constructed from a subset  $M' \subseteq M$  which corresponds to the positive integers. An input instruction is an instruction I, with I(S)(x) = S(x+k), for  $x \in M'$ ,  $k \ge 0$ . Ordinarily, the set  $\{1, \ldots, k\} \in M'$  will affect other subsets of M, but no other subset of M' will affect M-M'. A linear output device can also be constructed from M' as above; an output instruction is an instruction I with I(S)(x) = S(x-k), for  $x \in M' = \{1, \ldots, k\}$ , in which M-M' may affect  $\{1, \ldots, k\}$ , but M' does not affect M-M'. If the subset M' has both input and output instructions, it may be called an infinite push-down store. A linear input-output device can be constructed from a subset M'  $\subseteq M$  which corresponds to the integers. On such a device, we might have the following types of instructions:

Forward read -- I(8)(x) = S(x-k); {0, ..., k-1} affects M-M',

Forward write -- I(S)(x) = S(x-k), except for  $0 \le x \le k-1$ ; M-M' affects  $\ne 0$ , ..., k-1 $\end{Bmatrix}$ ; M' does not affect M-M'. Forward position -- I(S)(x) = S(x-k); M' does not affect M-M'. Backward read -- I(S)(x) = S(x+k);  $\ne (1, ..., k-1)$  affects M-M'. Backward write -- X(S)(x) = S(x+k), except for  $0 \le x \le k-1$ ;

M-M° affects  $\{0, ..., k-1\}$ ; M° does not affect M-M°, Backward position -- I(S)(x) = S(x-k); M° does not affect M-M°.

It may be left as an exercise to construct a computer which performs the functions of a "machine" or "automaton" as variously defined, e.g.: sequential machine; generalized sequential machine; Turing machine; Rabin-Scott two-tape automaton; push-down automaton; Fleck automaton.

The theory of sequential machines is, by now, quite extensive; at the same time, it is common knowledge that the theory of sequential machines is of little help to the computer programmer. The reason is not, as some people would believe, that the theory is not general enough; the reason is that the theory is too general. In a sequential machine the states form an arbitrary set. But in a computer with 32,768 thirty-six-bit words, there are 2<sup>1,179,648</sup> states of the core memory alone. It is perfectly true that a computer can be thought of, in certain contexts, as a sequential machine. There are functions that determine what outputs are to be produced, and what new states entered, on the application of an input. The enumeration of such functions would be, not only completely impractical, but pointless, because what actually happens in a computer, depends on what instruction is being interpreted at the moment, and what its input, and output, and affected regions are.

## 11. Programs Written in Languages

Doew the theory of computers, as developed here, apply to other objects than real computers? Are there objects which are computers, in the sense here defined, which have instructions with easily manageable input and output regions, but which do not involve "hardware"? There is at least one object of this nature which seems to be important—a program written in an algorithmic language such as ALGOL.

Let us consider such a program, and let V denote the set of all distinct variables in the program. (We are ignoring, for the moment, the fact that distinct variables may have the same name -- if, for example, they are local to two different sub-blocks. Such variables are considered here to be distinct. We are also assuming that no block in the program calls itself, and in general that there is no need for recursive procedures of any kind -- a restriction which will be removed later.) If the program contains arrays, V contains one element for each member of the array, according to its dimension; if the dimension is not specified, it is assumed, for the moment, to be infinite. Let R, Z, and C denote the reals, integers, and complex numbers, respectively, and let P denote the set of all statements of the program. We now construct a computer (M, 4 .  $\mathcal{L}$ ), as in Definition F, as follows: M = V U {L}, where L is a single object called the location; for each x & V, B = R, Z or C, according as x is declared to be real, integer, or camplex respectively, while B . . P. Each statement of the program is now an instruction. For example:

- (a) An <u>arithmetic statement</u>, such as A = X+Y-Z, is an instruction with output region  $\{A, L^2\}$ , defined by  $I(S)(A) = S(X) + S^2Y S(Z)$ , while I(S)(L) is the statement immediately following this one.

- (b) A conditional statement, such as IF (X4Y-Z=0), is an instruction with output region { L} . The condition is evaluated on the state S; in this case, it is determined whether S(X) + S(Y) S(Z) is actually equal to 0. If it is not, I(S)(L) is the next statement; if it is, I(S)(L) is the statement following the next statement.

- (c) A go to statement is an instruction with output region { The value of I(S)(L) is the (labelled) statement referred to.

If some of the blocks in the program do call themselves, or each other, so that certain of the variables need to be kept at several recursive levels, then each of these variables is replaced, in the set M, by an infinite push-down store as defined in the preceding section. (Or, for the sake of simplicity, every variable of the program, whether it needs to not, may be represented in M by such a store.) If other types of variables are allowed, such a matrices, then  $B_{x}$  may be altered to be a set of metrices or other objects. If switch variables are allowed, then  $B_{x} = P$  for a switch variable. For each subroutine in the program with n parameters, we introduce into M a set of n elements  $p_{1}$ : ...,  $p_{n}$ , with  $p_{i} = M$ . When the subroutine is called, the elements  $p_{i}$  are filled with their corresponding values; i.e., the statement CALL XYZ(P1, P2, ..., PN) is an instruction with  $I(S)(p_{1}) = P_{1}$ , etc. When the parameter P1 is referred to in the subprogram, its value is S(S(P1)).

In this situation, there is one "universal" instruction, namely the instruction which executes whichever statement is contained in L. If S(L) is to be thought of as an instruction, this universal instruction is given by I(S)(x) = S(L)(S)(x). This situation also holds in a real digital computer; the universal instruction is the instruction obtained by depressing the "step" key.

It is clear that the entire mechanism of input, output, and affected regions is just as applicable to these computers as to real computers.

#### 1.2. Enistence of Instructions

Can the input, output, affected regions of an instruction be taken arbitrarily? For computers with finite memory, the answer is yes, subject to the restrictions we have already mentioned. No input or output region can contain an element x & M such that B has exactly one element. The input region of an instruction can be void, but the output region cannot, unless the instruction is the identity. The affected regions of subsets of IR(I) are determined by the affected regions of one-element subsets of IR(I). Other than this, however, there are no restrictions for finite memory and no restrictions on input and output regions for infinite memory. Affected regions in a computer with infinite memory must satisfy certain other conditions. We shall give necessary and sufficient conditions, in the case of countable memory, for a set of affected regions to correspond to the affected regions of an actual instruction.

PROPOSITION XI. Let (M, B, S, J) be a computer and let P and Q be subsets of M. Then there exists a map  $T: J \rightarrow J$  with IR(I) = P and OR(I) = Q if and only if:

- (1) P ∩ Z = Ø and Q ∩ Z = Ø, where Z is the unit component.

- (2) Q # Ø, unless P = Ø.

Proof: If  $z \in Z$ , then we can never have  $S(z) \neq I(S)(z)$ , so  $z \notin OR(I)$  for any possible instruction I. Also, if  $S_1(y) = S_2(y)$  for  $y \neq z$ , then, since  $S_1(z) = S_2(z)$ , we have  $S_1 = S_2$ , so we can never have  $I(S_1)(y) \neq I(S_2)(y)$ ; hence  $z \notin IR(I)$ . If  $Q = \emptyset$ , we have S(x) = I(S)(x) for all  $x \in M$ , so that I(S) = S and I is the identity (and  $IR(I) = \emptyset$ ).

Now, let P and Q be chosen according to the conditions (1) and (2).