# MASSACHUSETTS INSTITUTE OF TECHNOLOGY ARTIFICIAL INTELLIGENCE LABORATORY

Memo No. 380

Sept. 1976

Forward Reasoning and Dependency-Directed Backtracking

In a System for Computer-Aided Circuit Analysis

by Richard M. Stallman and Gerald Jay Sussman

#### Abstract:

We present a rule-based system for computer-aided circuit analysis. The set of rules, called EL, is written in a rule language called ARS. Rules are implemented by ARS as pattern-directed invocation demons monitoring an associative data base. Deductions are performed in an antecedent manner, giving EL's analysis a catch-as-catch-can flavor suggestive of the behavior of expert circuit analyzers. We call this style of circuit analysis propagation of constraints. The system threads deduced facts with justifications which mention the antecedent facts and the rule used. These justifications may be examined by the user to gain insight into the operation of the set of rules as they apply to a problem. The same justifications are used by the system to determine the currently active data-base context for reasoning in hypothetical situations. They are also used by the system in the analysis failures to reduce the search space. This leads to effective control of combinatorial search which we call dependency-directed backtracking.

Work reported herein was conducted at the Artificial Intelligence Laboratory, a Massachusetts Institute of Technology research program supported in part by the Advanced Research Projects Agency of the Department of Defense and monitored by the Office of Naval Research under contract number N00014-75-C-0643.

Many people contributed to this work: Allen Brown, Drew McDermott, Johan de Kleer, Kurt Vanlehn, Louis Braida, Richard Fikes, and Earl Sacerdoti gave us some excellent ideas. Guy Steele, Charles Rich and Ben Kuipers gave us some important editorial help. John Allen, David Marr, Pat Winston and Paul Penfield also provided good advice.

## Contents:

| Introduction                              | - | - 2 |

|-------------------------------------------|---|-----|

| Analysis by Propagation of Constraints    |   | 5   |

| Facts and Laws                            |   | 11  |

| The Method of Assumed States              |   | 14  |

| Making Choices                            |   | 16  |

| Dependencies and Contexts                 |   | 18  |

| Contradictions                            |   | 22  |

| Compound Devices and Identified Terminals |   | 24  |

| The Queue-based Control Structure         |   | 27  |

| The Data Base of Facts and Demons         |   | 30  |

| Conclusions                               |   | 33  |

| Appendix: An Annotated Example            |   | 36  |

| Votes                                     |   | 62  |

| Bibliography                              |   | 65  |

|                                           |   | 00  |

#### Introduction

A major problem confronting builders of automatic problem-solving systems is that of the combinatorial explosion of search-spaces. One way to attack this problem is to build systems that effectively use the results of failures to reduce the search space — that learn from their exploration of blind alleys. Blind alleys Another way is to represent the problems and their solutions in such a way that combinatorial searches are self limiting. Limiters

A second major problem is the difficulty of debugging programs containing large amounts of knowledge. The complexity of the interactions between the "chunks" of knowledge makes it difficult to ascertain what is to blame when a bug manifests itself. Complexity One approach to this problem is to build systems which remember and explain their reasoning. Explainers Such programs are more convincing when right, and easier to debug when wrong.

We have designed and implemented LISP a problem-solving language called ARSARS in which problem-solving rules are represented as demons with multiple patterns of invocation Pottern-directed invocation monitoring an associative data base. Data bases It performs all deductions in an antecedent manner, threading the deduced facts with justifications which mention the antecedent facts used and the rule of inference applied. These justifications may be examined by the user to gain insight into the operation of the system of rules as they apply to a problem. The same justifications are employed by the system to determine the currently active data-base context for reasoning in hypothetical situations. Context Justifications are also used in the analysis of blind alleys to extract information which will limit future search.

We have used ARS to implement a set of rules for electronic circuit analysis. This set of rules, a version of EL, EL encodes familiar approximations to physical laws such as Kirchoff's laws and Ohm's law as well as models for more complex devices such as transistors. Facts, which may be given or deduced, represent data such as the circuit topology, device parameters, and voltages and currents. The antecedent reasoning of ARS gives analysis by EL a "catch-as-catch-can" flavor suggestive of the behavior of a circuit expert. The justifications prepared by ARS allow an EL user to examine the basis of its conclusions. This is useful in understanding the operation of the circuit as well as in debugging the EL rules. For example, a device parameter not mentioned in the derivation of a voltage value has no part in determining that value. If a user changes some part of the circuit specification (a device parameter or an imposed voltage or current), only those facts depending on the changed fact need be "forgotten" and re-deduced, so small changes in the circuit may need only a small amount of new analysis. Finally, the search-limiting combinatorial methods supplied by ARS lead to efficient analysis of circuits with piecewise-linear models.

The application of a rule in ARS implements a <u>one-step deduction</u>. A few examples of one-step deductions, resulting from the application of some EL rules in the domain of resistive network analysis, are:

- If the voltage on one terminal of a voltage source is given, one can assign the voltage on the other terminal.

- If the voltage on both terminals of a resistor are given, and the resistance is known, then the current through it can be assigned.

- 3: If the current through a resistor, and the voltage on one of its terminals, is known, along

with the resistance of the resistor, then the voltage on the other terminal can be assigned.

4: If all but one of the currents into a node are given, the remaining current can be assigned.

The style of analysis performed by EL, which we call the method of propagation of constraints, propagation requires the introduction and manipulation of some symbolic quantities. Though the system has routines for symbolic algebra, Symbolic manipulation they can handle only linear relationships. Nonlinear devices such as transistors are represented by piecewise-linear models that. cannot be used symbolically; they can be applied only after one has guessed Advice a particular operating region for each nonlinear device in the circuit. Trial and error can find the right regions but this method of assumed states is potentially combinatorially explosive. ARS supplies dependency-directed backtracking, a scheme which limits the search as follows: The system notes a contradiction when it attempts to solve an impossible algebraic relationship, or when discovers that a transistor's operating point is not within the possible range for its assumed region. The antecedents of the contradictory facts are scanned to find which nonlinear device state guesses (more generally, the backtrackable choicepoints) are relevant; ARS never tries that combination of guesses again. A short list of relevant choicepoints eliminates from consideration a large number of combinations of answers to all the other (irrelevant) choices. This is how the justifications (or dependency records) are used to extract and retain more information from each contradiction than a chronological backtracking system. Backtracking A chronological backtracking system would often have to try many more combinations, each time wasting much labor rediscovering the original contradiction.

#### How it works:

In EL all circuit-specific knowledge is represented as assertions in a relational data base. General knowledge about circuits is represented by laws, which are demons subject to pattern-directed invocation. Some laws represent knowledge as equalities. For example, there is one demon for Ohm's law for resistors, one demon that knows that the current going into one terminal of a resistor must come out of the other, one demon that knows that the currents on the wires coming into a node must sum to zero, etc. Other laws, called Monitors handle knowledge in the form of inequalities: For example, I-MONITOR-DIODE knows that a diode can have a forward current if and only if it is ON, and can never have a backward current.

When an assertion (for example, (= (VOLTAGE (C O1)) 3.4), which says that the voltage on QI's collector has the value 3.4 volts) is added to the data base, several demons will in general match it and be triggered. (In this example, they will include DC-KVL, which makes sure that all other elements' terminals connected to QI's collector are also known to have that voltage, and VCE-MONITOR-BJT, which checks that QI is correctly biased for its assumed operating region.). The names of the triggered laws are put on a queue, together with arguments such as the place in the circuit that the law is to operate. Eventually they will be taken off the queue and processed, perhaps making new deductions and starting the cycle over again.

When a law is finally processed, it can do two useful things: make a new assertion (or several), or detect a contradiction. A new assertion is entered in the data base and has its antecedents recorded; they are the asserting demon itself, and all the assertions which invoked it or were used by it. This complete memory of how every datum was deduced becomes useful when a

contradiction is to be handled. A contradiction indicates that some previously made arbitrary choice (e.g. an assumption of the linear operating region of some nonlinear component) was incorrect. ARS scans backward along the chains of deduction from the scene of the contradiction, to find those choices which contributed to the contradiction, and records them all in a NOGOOD assertion to make sure that the same combination is never tried again. (NOGOOD ((MODE Q1) CUTOFF) ((MODE D5) ON)) is a NOGOOD assertion that says that it cannot be simultaneously true that transistor QI is cut off and diode D5 is conducting. Such a NOGOOD might be deduced if QI and D5 were connected in series. Next, one of the conspiring choices is arbitrarily called the "culprit" ("scape-goat" might be a better term) and re-chosen differently. This is not mere undirected trial and error search as occurs when chronological backtracking with a sequential control structure is used, since it is guaranteed not to waste time trying alternative answers to an irrelevant question. The NOGOOD assertion is a further innovation that saves even more computation by reducing the size of the search space, since it contains not all the choices in effect, but only those that were specifically used in deducing the contradiction. Frequently some of the circuit's transistors will not be mentioned at all. Then, the NOGOOD applies regardless of the states assumed for those irrelevant transistors. If there are ten transistors in the circuit not mentioned in the NOGOOD, then since every transistor has three states (in the EL model) the single NOGOOD has ruled out 310-59049 different states of the whole circuit.

# Analysis by Propagation of Constraints

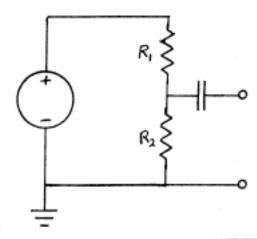

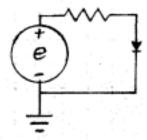

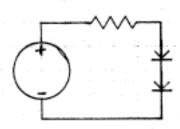

Consider a simple voltage divider:

Suppose that the voltage at the midpoint is known to be 3 volts, relative to the indicated ground. Since there is known to be no DC current through the capacitor, it is possible to determine the strength of the voltage source. Forward reasoning is doing it this way: First, use Ohm's law to compute the current through  $R_2$  from its resistance and the difference of the voltages on its terminals. Next, the current through  $R_1$  can be seen, via KCL, to be the same as that through  $R_2$ . Finally, that current, together with  $R_1$ 's resistance and the voltage at the midpoint, can be fed to Ohm's law to produce the voltage at the top. This is an example of what we call "forward reasoning" or (as applied to circuits) "propagation of constraints".

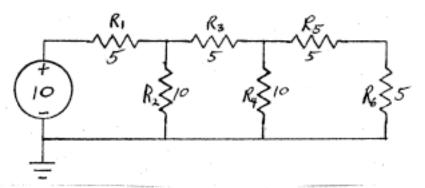

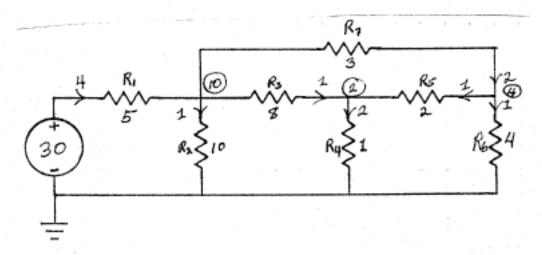

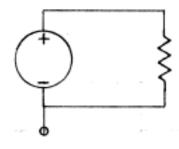

However, not all circuit problems can be solved so simply. Consider a ladder network:

Such a network might be solved with three node equations or by series-parallel reduction. More in the spirit of forward reasoning is "Guillemin's Trick":

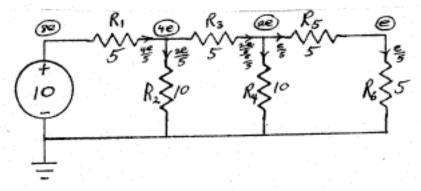

We assume a node voltage, e, at the end of the ladder. This implies a current, e/5, going down  $R_6$  by Ohm's Law. KCL then tells us that this current must come out of  $R_5$ . But we know the voltage on the right of  $R_5$  and the current through it, so we deduce that the voltage on its left is 2e. We use this voltage to deduce the current through  $R_4$  and then KCL to give us the current through  $R_3$ . We continue this process until we get all node voltages defined in terms of e:

But now we know 8e = 10, therefore, e = 5/4 volt. We have solved the network with I equation in I unknown.

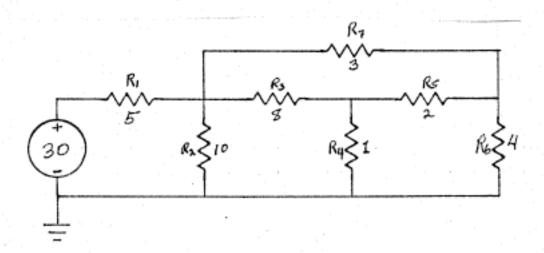

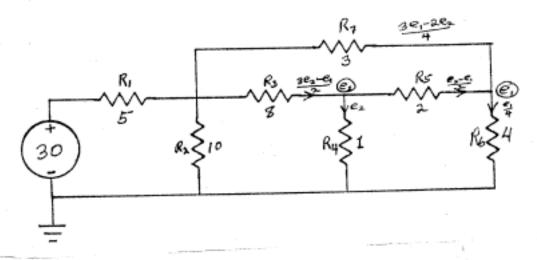

Alas, Guillemin's trick fails in the following circuit:

At first glance, this is a 3 node equation network with no possible series-parallel reductions. We want to generalize Guillemin's trick to solve this network (with fewer than 3 equations).

We first assume a node potential,  $e_1$ , at the top of  $R_6$ . Thus, we deduce that the current through  $R_6$  is  $e_1/4$ . At this point we can make no further one-step deductions. Rather than give up, let's poke it again. We assume a node potential,  $e_2$ , at the top of  $R_4$ . We can now conclude that the current through  $R_4$  is  $e_2/1$  and the current through  $R_5$  (measured to the right) is  $(e_2-e_1)/2$ . We can now use KCL to deduce that the current through  $R_7$  (to the right) is  $(3e_1-2e_2)/4$  and that the current through  $R_3$  is  $(3e_2-e_1)/2$ :

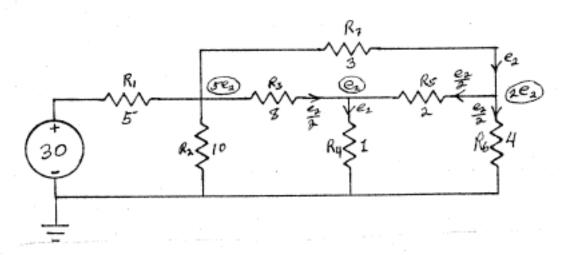

At this point we can deduce that the voltage on the leftmost terminal of  $R_7$  is  $e_1 \cdot (3/4)(3e_1 - 2e_2)$  or  $(13e_1 - 6e_2)/4$ . We can also deduce that the voltage on the leftmost terminal of  $R_3$  is  $e_2 \cdot 8((3e_2 - e_1)/2) = 13e_2 \cdot 4e_1$ . Since these terminals are connected together we have two expressions for the same node voltage. Setting them equal and simplifying, we get  $e_1 \cdot 2e_2$ . The result of this simplification is:

Continuing, we deduce that the current through  $R_2$  must be  $5e_2/10=e_2/2$ . By KCL, the current through  $R_1$  must be  $2e_2$ . Ohm's law now gives as the voltage at the left of  $R_1$  as  $15e_2$ . But this voltage is set by the voltage source, so  $15e_2=30$ . We conclude that  $e_2=2$ :

We have solved the network with only two unknowns. As we approach a full graph network, this method degrades smoothly to be the node method, but usually it uses far fewer unknowns.

What have we been doing?

A fundamental concept here is that of a <u>one-step deduction</u>. In the case of a resistive network with voltage and current sources there are only a few kinds of one-step deductions possible:

- I: If the voltage on one terminal of a voltage source is given, one can assign the voltage on the other terminal.

- If the voltage on both terminals of a resistor are given, then the current through it can be assigned.

- If the current through a resistor is given, and the voltage on one terminal is given, then the voltage on the other terminal can be assigned.

- 4: If all but one of the currents into a node are given, the remaining current can be assigned.

Another basic concept here is that of a coincidence. A coincidence occurs when a one-step deduction is made which assigns a value to a network variable which already has a value. We have seen several coincidences. In the ladder network example a one-step deduction of type 3 assigns the node voltage 8e to a node which is already at 10 volts. In the second example, the node at the top of R<sub>2</sub> was assigned two different node voltages by two one-step deductions of type 3, and the voltage 15e<sub>2</sub> even though it already was known to be 30 volts. In each of these cases the coincidence resulted in the formulation of an equation between the competing assignments. At the time of a coincidence, the resulting equation should be solved, if possible, for one of its unknowns in terms of the others. The circuit is then redrawn with that unknown eliminated.

Thus, the basic propagation analysis algorithm is rather simple:

Algorithm: Propagation of Constraints

Choose a datum node and assign it a potential of 0.

loop: IF there is a one-step deduction available

Choose a deduction and make it.

ADVICE:

[1] IF the last action was the assignment of a node potential, look for a type 1, 2, or 3 deduction involving that node.

[2] IF the last action assigned a current, look for a type 3 or 4 deduction involving that branch.

IF the deduction caused a coincidence THEN

IF the equation implied by the coincidence is a tautology

Ignore the coincidence (and be reassured by the fact that it checks!).

contradiction

ERROR: You did something wrong.

otherwise

Solve for one unknown in terms of the others (or for a number, if there are no others!). Eliminate that unknown throughout the circuit.

Go to loop.

IF there is a node without a node potiential

Choose such a node and assign it a new node potential variable.

Go to loop.

RETURN

All of the unknowns introduced by the algorithm are sure to have had their values determined by the time the algorithm returns.

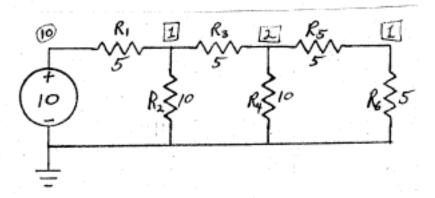

Now, what about choosing where to place unknowns? We want to get as much action as we can out of each one. One measure of the simultaneity of the situation is given by a count of the number of unknown nodes connected to a given one. Braids For example, consider our ladder again. All nodes except the ground and the top of the voltage source are unknown. In the following circuit each unknown node has been annotated with the number of unknowns it is connected to.

We can see that the middle node has two unknown neighbors while the others have only one. If we place a node potential on the middle node, we can only deduce one current while if we place it at either one of the I neighbor nodes we will get the whole answer. The rule is to place the node potential at a node of minimum unknown neighbors. This also has bearing on where to place the datum. In general, we want a node which is maximally connected to unknowns, so as to constrain them quickly.

#### Facts and Laws

Analysis by propagation of constraints is a form of antecedent reasoning in which a given, closed set of questions (in this case, the voltages and currents at all points in the network) is to be answered. ARS provides a general framework for the implementation of antecedent reasoning systems; we developed it to support the particular set of rules for electrical analysis which we call EL. Like any programming language, ARS is best explained by showing how it can be used to implement an example. We will now display sample parts of EL, and how they implement parts of the analysis method already described.

To EL a circuit is made up of <u>devices</u> and <u>nodes</u>. A device is any of the components one would normally think of as present in the circuit, such as resistors, capacitors, transistors, and voltage sources. Each device has two or more terminals by which it is connected to the rest of the circuit. But two device terminals are never connected *directly*. Instead, they are both connected to a common node (that is the sole purpose of nodes).

ARS requires that all knowlege to be manipulated be represented as assertions, and their manipulators to be expressed as demons. EL therefore deals with facts that name the devices and nodes in the circuit, and state which terminals connect to which nodes. A node or device is named by an IS-A assertion, such as (IS-A R1 RESISTOR) or (IS-A NS4 NODE). The IS-A assertions serve several purposes. They control the matches of restricted variables and they enable EL to find all the nodes in the circuit, which is necessary for deciding where to put a symbolic unknown when one is needed.

Most devices have parameters; for example, a resistor has a resistance and a transistor has a polarity. These parameter's values are recorded, if known, by facts like (= (RESISTANCE R1) 1000.0), which says that R<sub>1</sub>'s resistance is 1000 Ohms. They do not have to be specified, and EL can be "back-driven" to deduce them if enough voltages and currents are known. An example of this use of EL to aid the choice of device parameters is given in the appendix.

The connections of the circuit are described by assertions like (CONNECT N54 (#1 R1)), each naming a single node and a single device terminal. These assertions need never be entered by an EL user, however, because we supply a special input format for conveniently defining devices and wiring them up into circuits (see Appendix).

Each type of device has conventional names for its terminals. For example, a resistor's terminals are known as #1 and #2; a transistor's are called E, B and C. The conventional terminal names have to be used because they are the ones that the laws for the device know about. It would be easy to wire a resistor up by its #3 and #4 terminals, but the EL law embodying Ohm's Law would not know about them.

The knowledge EL accumulates during the analysis of a circuit involves mostly the values of the voltage at or the current through particular device terminals. They are represented by assertions such as (= (VOLTAGE (#1 R1)) 10.0). The values of symbolic unknowns, when learned, are stored in the form (VALUE X15 15.4).

Perhaps the simplest circuit rules are those, such as Ohm's law, which can be represented by algebraic equations. In ARS such a law can be written very simply:

```

(LAW DC-OHM ASAP ((R RESISTOR) V1 V2 I RES)

()

((= (VOLTAGE (#1 !?R)) !>V1) (= (VOLTAGE (#2 !?R)) !>V2)

(= (CURRENT (#1 !?R)) !>I) (= (RESISTANCE !?R) !>RES))

(EQUATION '(&- V1 V2) '(&* RES I) R))

```

This is the EL law that implements Ohm's law. Like all EL laws, it has an arbitrary name, a set of slots or antecedent patterns to control its invocation, and a body which in this case consists of an algebraic equation. The name, chosen by us for mnemonic significance, is DC-OHM. ASAP indicates its invocation priority, which is normal, as it is for all laws that are simply equations between circuit parameters. DC-OHM declares the local variables V1, V2, I and RES to hold the two terminal voltages, the current, and the resistance value of the resistor. In addition, the type-restricted local variable R is used for the resistor about which the deduction will be made. The long list beginning with (= (VOLTAGE ... contains the demon's trigger slots. Their purpose is dual: to provide patterns to direct the invocation or triggering of the demon, and to gather the information needed in applying Ohm's law once the demon is invoked.

The ARS antecedent reasoning mechanism will signal DC-OHM whenever a fact is asserted that matches any of DC-OHM's trigger slots. DC-OHM itself then automatically checks all of its trigger slots to see which ones are instantiated and which ones are not. That information is passed to the function EQUATION, whose job is to deduce whatever it can from the equation it is given. If one of the terms in the equation (1, V1, V2, and RES, in this case) is unknown, EQUATION can deduce it from the others. If all the terms are known, EQUATION checks that they actually satisfy the equation, and if any of them is an algebraic expression involving symbolic variables, EQUATION can solve for one of them. Whenever EQUATION asserts a conclusion, it automatically records the instantiations of the trigger slots as the antecedents of the conclusion.

Notice the () before the list of trigger slots in DC-OHM. That is the list of mandatory slots, of which in this case there are none. Mandatory slots are just like trigger slots except that the law is not processed unless all of them are instantiated. DC-OHM's slots are not mandatory, since if any single one is missing DC-OHM can accomplish something by deducing a value for it. Mandatory slots are useful when a law is contingent on some fact. For example, different laws apply to conducting transistors and cut-off transistors. EL represents the knowlege that a transistor is cut off with an assertion such as

(DETERMINED (MODE Q1) CUTOFF)

When a transistor is cut off, no current flows into any of its terminals. One law, DC-BJT-CUTOFF-IC, enforces the absence of collector current:

```

(LAW DC-BJT-CUTOFF-IC ASAP ((Q BJT) IC)

((DETERMINED (MODE !?Q) CUTOFF))

((= (CURRENT (C !?Q)) !>IC))

(EQUATION 'IC 8.8 Q))

```

This law has a mandatory slot requiring that the transistor in question be cut off. If that is known, the law will be applied and will deduce that the collector current is zero. If that is not known, the law will never be applied. Note that the slot that detects a known value of the collector current is not a mandatory slot, and its only function is to make sure that such a known value will be noticed by the law and checked for consistency.

#### The Method of Assumed States

The propagation method can be extended to any devices with laws that are invertible: if one terminal voltage or current is in fact fixed when others are given, then an algebraic expression for it in terms of those others may be needed in the course of propagation. Moreover, the expression must be "tractable", in the sense that the (human or mechanical) algebraic manipulation system may need to substitute in it, simplify it, or even solve it for unknowns appearing in it, in order to carry out the solution. For example, handling a diode is too complicated, since it would create the need to solve exponential equations. But even an "ideal diode" - a piecewise-linear approximation to a real diode - is too complicated to be handled symbolically as fluently as is necessary. It would introduce conditionals and "max" and "min" functions into the expressions, and they are not invertible.

But if the algebraic manipulation technology can't handle the device's laws as a whole, stronger methods of reasoning can break them down. Electrical engineering has a method known as the "method of assumed states", which is applicable to piecewise-linear devices such as ideal diodes. It involves making an assumption about which linear region the device is operating in (for a diode, whether it is "on" or "off"). This makes the conditionals simplify away, leaving tractable algebraic expressions to which propagation of constraints applies. Afterwards, it is necessary to check that the assumed states are consistent with the voltages and currents that have been determined.

For an example of such reasoning, consider the diode and resistor in series: Assuming

the diode to be nonconducting, we would deduce that there is zero current flowing, and that the voltage at the midpoint equals e. Since e is positive, that contradicts the conditions necessary for the diode to be off, as we assumed. On the other hand, if we assume that the diode is conducting, we deduce that the voltage at the midpoint is zero, and can then determine the amount of current. The current is flowing downward through the resistor and diode, which is consistent with the assumption that the diode is conducting.

When this method is mechanized, it is necessary to cycle through all of the possible states (linear regions) of the device, testing each one for consistency with the voltages and currents that follow from it. When there are several complicated devices, it is necessary to consider all combinations of all different states for each device. This causes an exponential explosion of the number of states of the system that must be investigated.

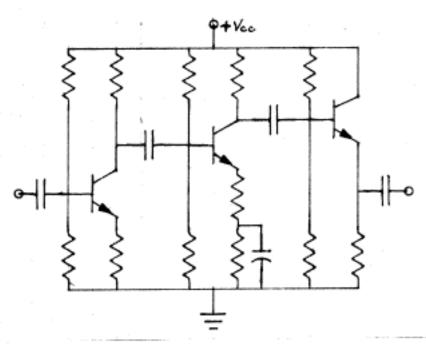

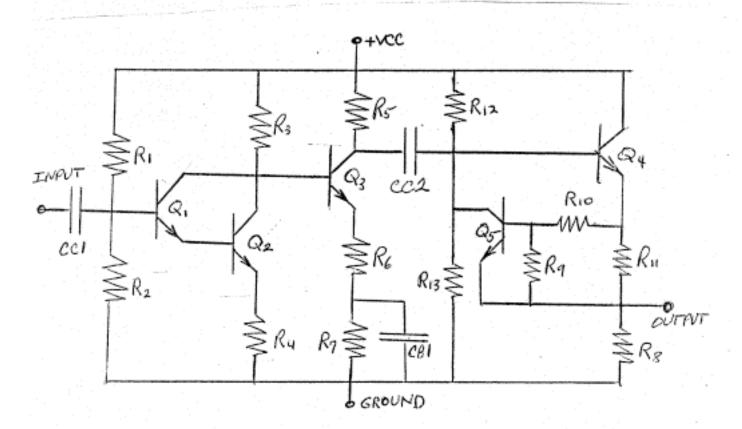

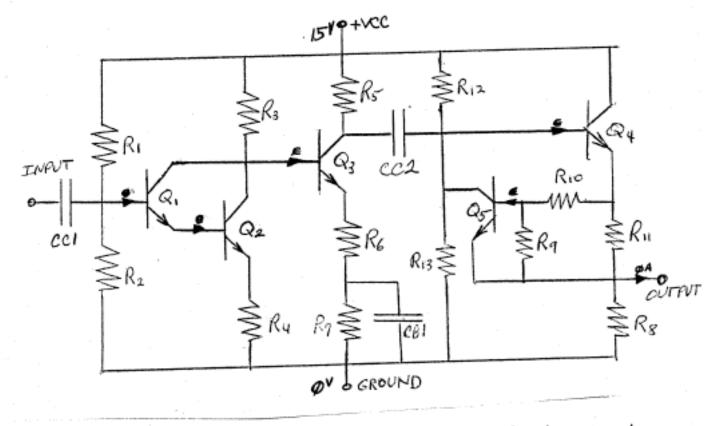

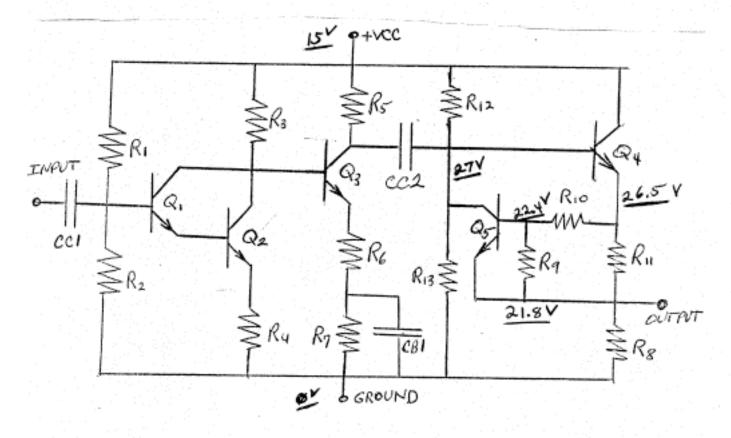

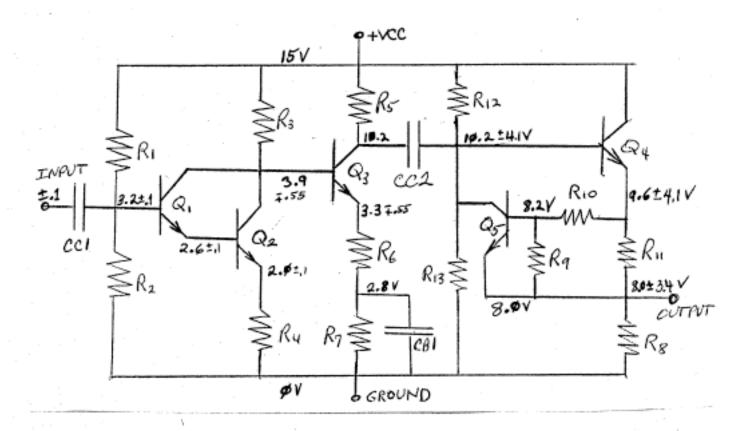

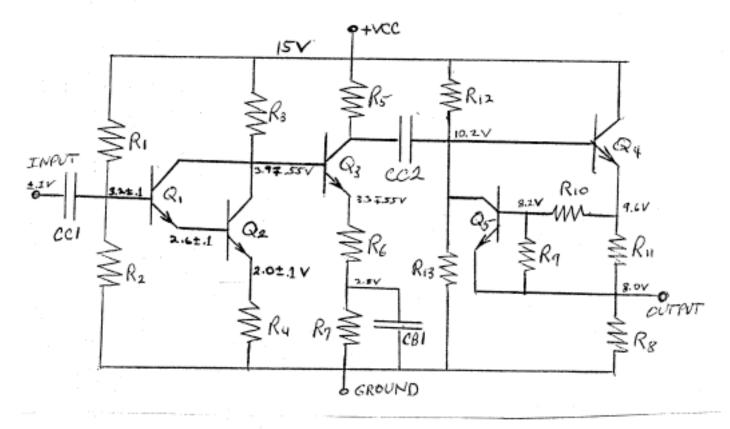

has three transistors. If the transistor model admits three states, active, cutoff and saturated, then there are, at first glance, 36363 or 27 different triples of states that must be considered, of which only one (all three transistors active) is self-consistent. But actually, the states of the transistors are completely independent; the stages are coupled only for AC signals and have no effect on each other's bias conditions. Knowing this, we can find the correct state for each transistor separately, giving only 3+3+3 or 9 assumptions to be tested. Such situations are very frequent, and their detection is an effective way of reducing the work entailed by the combinatorial search for the correct states.

# Making Choices

Using the method of assumed states requires the ability to make choices, and to handle contradictions by making new choices. These abilities are built into ARS, but the conditions for the detection of a contradiction are a matter of expert electrical knowlege, contained in EL laws. An equation law detects a contradiction if it sees that the equation is not satisfied by the known values of the quantities in it.

However, the method of assumed states carries another sort of knowlege, of the boundaries of the different operating regions of piecewise-linear devices. EL has special laws known as monitor laws which check that a device is in fact in an environment consistent with the state assumed for it. The conditions tested by monitor laws are often inequalities, which are not as conducive to symbolic manipulation as equations. ARS's symbolic algebra routines are helpless with them, so monitor laws can't do their job unless numerical values are known for all the parameters entering into the inequality.

When the operating region of a nonlinear device is known, that knowledge is represented by a <u>DETERMINED</u> assertion, such as (DETERMINED (MODE Q1) CUTOFF). The general form is <u>DETERMINED</u>, followed by the "question", followed by the "answer". Such knowledge might have been deduced (such as when we first learn that a transistor's emitter current is zero, and then deduce that it must be cut off), or it might be the result of an arbitrary choice. In the latter case, the choice *itself* is represented by a similar <u>CHOICE</u> assertion: (CHOICE (MODE Q1) CUTOFF), from which we pretend that the <u>DETERMINED</u> assertion was "deduced". The reason for having the two different assertions is that all the transistor laws that depend on the transistor's state can look for the <u>DETERMINED</u>, and thus work no matter how the known state was arrived at, while the backtracking mechanism can look for the CHOICE, and avoid trying to choose other answers for a question whose answer is not in doubt.

In fact, for the sake of efficiency, we have lumped together the state conditions not by state but by the circuit variable they test. Here is the monitor that checks transistors' collector currents for consistency with whatever state is assumed.

```

(MONITOR-LAW IC-MONITOR-BJT HIPRI-ASAP ((Q BJT) (IC NUMBER) (BE-DROP NUMBER))

((= (CURRENT (C !?Q)) !>IC) (= (BE-DROP !?Q) !>BE-DROP))

()

(COND ((APPROX IC 8.8)

(OBSERVE "(DETERMINED (MODE ,Q) CUTOFF) ANTECEDENTS))

((< (&* IC BE-DROP) 8.8) (CONTRADICTION DEMON ANTECEDENTS Q))

(T (ASSERT-NOGOOD "(MODE ,Q) 'CUTOFF ANTECEDENTS NIL))))

```

It is called a MONITOR-LAW instead of just a LAW so that it will insist on having numerical values for the local variables declared to need them, IC (the collector current) and BE-DROP (whose sign indicates the polarity of the transistor). A zero collector current is consistent with only one state, CUTOFF. The function OBSERVE reports a contradiction to ARS if the transistor is in any other state. In addition, as a timesaving measure, if the transistor's state has not at the moment been chosen, OBSERVE chooses CUTOFF since it is the only consistent choice. If IC and BE-DROP have

opposite signs, the collector current is flowing backwards through the transistor, which is impossible in any state; in that case, a contradiction is reported to ARS for processing. Otherwise, there is a physically possible, nonzero collector current, which is consistent with any state except CUTOFF. The function ASSERT-NOGOOD reports that to ARS, causing a contradiction if an assumption of CUTOFF is currently in force. If not, a NOGOOD assertion is created (see Contradictions, below) so that future search through the space of state-combinations will be limited.

## Dependencies and Contexts

The method of assumed states requires that ARS be able to reason from hypothetical assumptions. In addition, intelligent processing of contradictions involves distinguishing the guilty assumptions from the innocent ones. ARS's dependency records play a central role in both activities.

ARS keeps complete records of every deduction that it makes. The premises of the deduction can be found from the conclusion, and the conclusion from the premises. These records are used by ARS for several purposes: explaining the derivation of a fact to the user, finding the choices relevant to a contradiction, and delineating those facts which are currently believed to be true. A fact is believed (in) if it has well-founded support from atomic assumptions which are currently believed. An assumption, such as an arbitrary choice of a device operating region, may become disbelieved, perhaps because of a contradiction involving it. A fact which does not have well-founded support from believed assumptions is said to be out. If a choice (and its consequences) which has been outed returns to favor, we use the dependency information to save the effort of reinventing implications from scratch. This process is called unouting. At any time, those facts actually believed are said to be in, while those under a cloud are out. Dependency information remains forever, even as the facts involved rise or fall in favor.

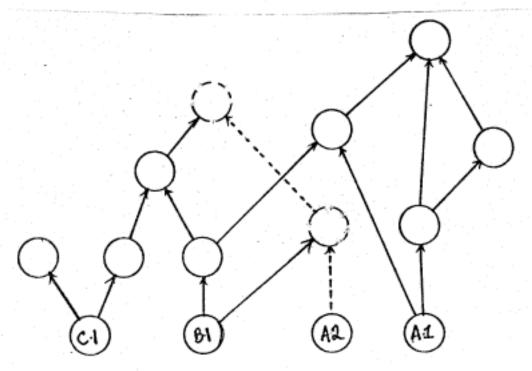

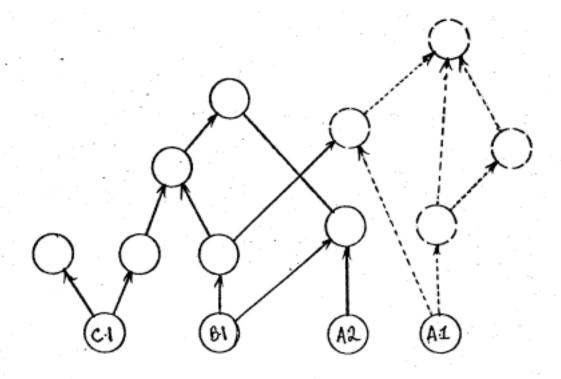

Here is a picture of the contents of an ARS fact data base, containing several atomic facts (device-state choices, or circuit construction specifications) and sundry consequences of them, showing a particular context selected. Al, Bl and Cl are atomic data that are currently in. Suppose Al and A2 are device-state assumptions, and in fact are alternative assumptions about the same device, so when Al is in, A2 must be out.

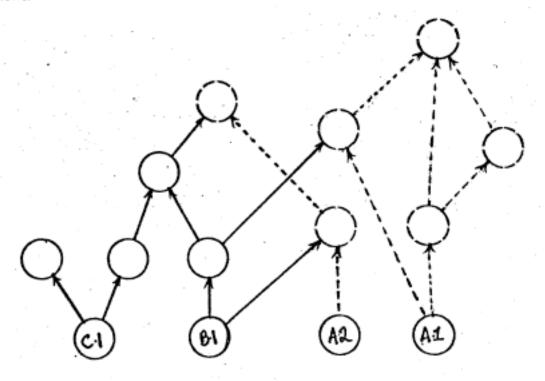

If Al were to be retracted, the fact garbage collector would be invoked, leaving the data base as follows:

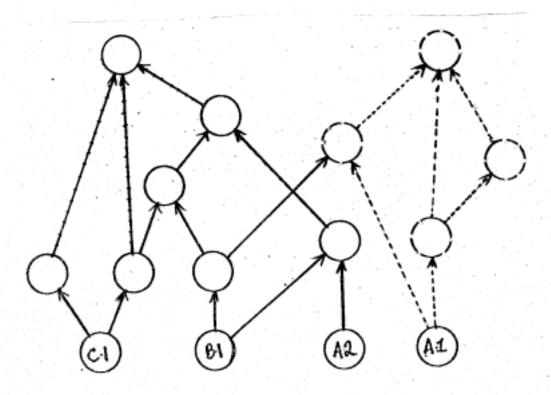

Believing A2 instead of Al would cause unouting of several consequences:

In addition, deduction would have the chance to add more facts:

It may happen that a fact can be deduced in more than one way. If one is certain of one's premises, extra proofs of a known fact can be discarded. When the premises can be arbitrary choices that might be taken back, extra proofs are important, because they might remain valid when the premises of the original proof are not. Although a program might be guaranteed to find the second proof again if the first were invalidated, that would waste time. Therefore, ARS keeps separate records of each way that it finds to deduce a fact. When two facts imply each other (with appropriate other premises) it may happen that ARS records a deduction of the first from the second and also a deduction of the second from the first. At first we were shocked by this, but it is inescapable, because with one set of choices in effect it may be necessary to deduce the first via the second, while with other choices the second may be accessible only via the first. However, such loops in the dependency chains creates a problem for processes such as contradiction processing which must trace out the reasons for a fact. It is soluble, however, because if any fact that is in has (as we would hope!) a valid reason for being believed, it must be the apex of a non-looping subgraph reaching down to atomic assumptions such as the wiring of the circuit and device-state choices. For every one of the facts that is currently in, ARS singles out one of the ways it was deduced as its support, and those marked deductions are chosen to form a subgraph that contains no loops. Backward tracing of the dependency records then follows only the supports, and therefore always terminates. The selection of the supports is a by-product of the process used to determine which facts are still to be believed when an atomic assumption is taken back, which operates by scanning forward from the atomic assumptions currently believed and marking all their consequences as a garbage collector would. The facts that are marked become in, and the garbage facts are out.

Because facts and dependency information are never totally forgotten even when they are disbelieved, a short cut is possible when a once believed but later invalidated fact is validated once more. In a process known as unouting all the old consequences of the vindicated fact are reexamined, and if their other antecedents are all currently believed they too are marked in. If not for unouting, those consequences would be rededuced eventually anyway by the laws that originally deduced them, but unouting is much faster.

Taken together, the two processes of outing and unouting can be viewed as context-switching between contexts each associated with some subset of the set of possible assumptions. Since there are so many contexts to visit, the facts are not marked with the names of the contexts they are in; instead, context switching must identify and mark the facts that are in the context being entered. These contexts form a tangled hierarchy instead of the usual tree. Entering a subcontext is believing an additional assumption, which is done by unouting together with normal deduction. Moving to a higher context is disbelieving some assumption; this is done, by means of the fact garbage-collector, when contradictions happen. Note that, as in Conniver, a "subcontext" generally contains more assertions, and a "supercontext" contains fewer.

In fact, one could imagine the entire set of contexts as existing initially, but with no knowledge in any of them save the initial assumptions; then reasoning happens, adding more knowledge which is automatically placed in the context(s) determined by the premises of each deduction. Contexts in which contradictions are believed are the ones ruled out as acceptable solutions to the problem. The others are fertile ground for extension of knowledge. This point of view raises one above the petty details of when one should backtrack (try working a different context), and also raises the possibility of switching contexts simply because they appear unfruitful, and not necessarily contradictory (but this has not been implemented). Also, since backtracking is just a change of the point of attack, it loses no information.

A fact does not itself belong to any context, although it may be known in a particular context, or in several contexts for independent reasons. The dependency records also do not belong specifically to the context that was in effect when the deduction was made. Because of that, they are always ready to pull the consequences into a new context if the antecedents are deduced in it. Although a fact deduced is certainly in the currently selected context, it may also automatically, by virtue of its dependency links, be in some supercontext of it (and also many sibling contexts), if its proof did not make essential use of all of the atomic facts that define the currently selected context. In other words, a fact when deduced is not simply "installed" in the currently selected context, the way it would be in Conniver; it goes automatically into the highest supercontexts that its derivation will work in, and is merely "inherited" by the selected context.

This context mechanism might be applied to the understanding of processes that develop over time by associating a unique atomic datum with each significant local event occurring in the process. There would then be, for each stage of the process, a context in which the state of the system at that stage was known. However, the understanding of the process would not be tied to any global "time coordinate", and would not require any spurious time-ordering between events that were not causally related. Any "spacelike hypersurface" slicing through the process would have a corresponding context; time would be a decentralized object that could be advanced locally in one region of the process while being "left at the same instant" in other regions.

## Contradictions

When EL uses the method of assumed states to analyze circuits containing nonlinear devices, incorrect assumptions are detected by means of a contradiction, which is the specific event in which the chosen assumptions are seen be inconsistent. A contradiction is detected by a particular law - most often by monitor laws that exist for just that purpose. Contradictions are remembered both by contradiction assertions which are placed in the dependency-structure at the point of contradiction, and by NOGOOO assertions which record essentially the same information in a form easily used by the routines which choose alternate state-assumptions. A contradiction assertion does not explicitly contain any information; its significance lies entirely in its list of antecedents. A NOGOOD assertion explicitly lists the state assumptions that conspired to produce the contradiction. A typical contradiction might depend on dozens of atomic facts, including some device-state choices such as (CHOICE (MODE Q3) BETA-INFINITE) and (CHOICE (MODE D2) OFF), as well as many circuit construction details such as (RESISTANCE R1 1000.0) and (CONNECT\_N54 (B Q1)). The contradiction assertion would have all of them as antecedents (indirectly); the NOGOOD assertion might be (NOGOOD ((MODE Q3) BETA-INFINITE) ((MODE D2) OFF)), and its antecedents would include the RESISTANCE and CONNECT assertions but not the CHOICEs.

When we view sets of assumptions as determining contexts, a contradiction is a fact deduced in a specific context, which shows that context (and all of its subcontexts) to be of no further interest. But if the fact of the existence of the contradiction is to be available for use (such as in controlling a search), that fact must reside in a different context. NOGOOD assertions fill that role. The simplest way to remember the contradiction's existence would be to assert a fact containing a list of all of the atomic assumptions of the contradicted context, found by walking back through the dependency tree from the contradictory facts (or, just as good, from the contradiction assertion). In the example we are using, the RESISTANCE, the CONNECT, and both CHOICEs would be listed in the NOGOOD, which would have no antecedents. Since such a NOGOOD would be true regardless of the truth of any of the premises it listed, it would exist in the highest context of all, which is the one that depends upon no atomic facts. However, (not (A and B)) can also be stated as (A implies (not B)). Any subset of the basis of the contradiction can be deemphasized by being made antecedents of the NOGOOD rather than part of its list. In our original example, the RESISTANCE and CONNECT assertions were de-emphasized. De-emphasis makes the information totally unavailable in some contexts (those that do not include the de-emphasized antecedents), but by the same token reduces the number of NOGOODs that are in at any moment, and also reduces the size of each NOGOOD's list. That is valuable, since whenever ARS needs to choose a state for a device it must examine all NOGOODs that are in, to eliminate choices already known to be incorrect; each NOGOOD must be processed to see whether it lists the choice under consideration, and whether the other atomic facts it lists are currently also in. De-emphasizing some of the atomic facts causes the normal context mechanism to help with this filtering of the NOGOOD assertions.

Of course, de-emphasis can have drawbacks. The most extreme possible de-emphasis would leave only one assertion in the NOGOOD's list, while all the others became antecedents of the NOGOOD. This would make the NOGOOD almost useless for pointing out contexts which were not worth visiting. Imagine that Al, Bl and Cl are atomic facts that lead to a contradiction, and that

Al is listed as no good, with BI and CI as conditions. If later AI and BI were in, and CI were under consideration for belief, that N0G00D assertion would be out, and there would be no understanding that CI led to a context already tried and discarded. The N0G00D would not be performing its intended function. This would not be a disaster, since bringing CI in would bring back the original contradiction assertion also by unouting, but much time might be wasted. This "thrashing" is most painful with such excessive de-emphasis, but any de-emphasis has the ability to cause thrashing if its implicit assumptions about the relative stability of the atomic facts prove to be wrong.

A practical system must find a compromise between thrashing, and examining too many too-big NOGOOOs whenever a choice is made. We do not know of any domain-independent solution to the problem. What is clear is that it is good to de-emphasize facts that are unlikely to change. In the domain of electronic analysis, we emphasize device-state choices, and de-emphasize circuit wiring and intrinsic device parameters such as the resistance values of resistors, since during the analysis of a specific circuit the latter usually do not change. In circuit design there might be occasions when some circuit voltages that represent the design criteria would be least likely to change, device-state assumptions would be guessed at next (along with approximate circuit wiring), and placement and values of resistors and capacitors would be chosen last. Then, NOGOOO assertions might emphasize the detailed wiring decisions and de-emphasize the large-scale ones. A second level of NOGOOO assertions might speak of overall circuit plans, de-emphasizing only the design criteria. Thus, the level of a contradicted context in the tangled hierarchy would guide the choice of a context for the NOGOOO.

## Compound Devices, and Identified Terminals

Engineers often think of a subcircuit as a "black box". A truly black box — one whose insides are hidden, such as an op-amp — is intellectually (and computationally) just an element. More interesting is a "grey box" which may be ambivalently thought of as a black box or as a configuration of components. Grey boxes are often used to summarize some aspect of the behavior of a configuration as a whole. It is economical to store the most important features of the behavior of common configurations as grey-box laws so that they do not have to be computed from scratch each time the configuration is used. Sometimes, in fact, there are laws about the behavior of a configuration which are crucial to analysis of circuits containing it, but which are very difficult to derive from the behaviors of its components.

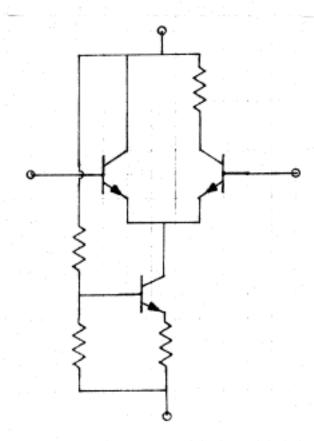

For example, some common configurations of transistors cannot be understood in terms of EL's simple-minded model of transistors. Such an application is the <a href="mailto:emitter-coupled-pair">emitter-coupled-pair</a> (ECP):

The problem here is that one must use the exponential diode model of the transistors to derive the fact that (in a correctly biased ECP) the incremental difference in collector currents is proportional to the difference in incremental base voltages (and furthermore, that constant of proportionality is almost independent of the transistor characteristics). Derivation We could try to solve this problem by attempting to include the exponential diode model of the transistor and the algebraic expertise required to use it. Notice, however, that this important, but difficult to derive fact about the currents in an ECP is in itself a simple linear law for the ECP. Grey-box laws allow us "package" this fact about the configuration so that it can be used in analysis, without increasing the

complexity of our basic transistor model. In this way we can use the much simpler (but less accurate) models in most cases and have a way to impose the constraints on the configurations that depend on the more accurate models.

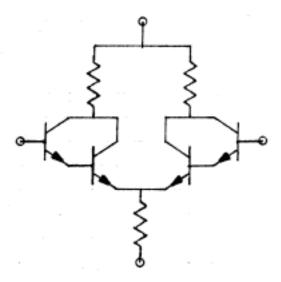

Another problem is that there is not just one ECP circuit. For example, here is another variety of ECP:

If we had to specify a distinct set of grey-box laws to cover each instance of ECP we would be fighting a losing battle. We must express the laws to capture the essence of ECP and not any particular circuit.

The notion of a grey box is implemented by the EL <u>macro-device</u> feature. An EL user may specify that a particular subcircuit is to be viewed as a grey box. EL has the ability to <u>identify</u> a portion of a circuit with a macro-device on a terminal-by-terminal basis. The subcircuit and the macro-device are regarded as alternate descriptions of what is connected to their common environment. The terminals of the macro-device are each identified with a terminal of one of the devices in the subcircuit. The device is allowed to have unidentified connections, and so is the subcircuit - in fact, to speak of the subcircuit is slightly misleading, since it suggests that there must be a boundary surface that divides the circuit into "inside" and "outside", and no such is required. When two terminals are identified, EL assumes that they must have the same voltage and the same current. This is not the same as connecting terminals at a node!

The macro-device is then just a method of attaching extra laws which supply additional constraints among the voltages and currents on the identified terminals and thus help determine the circuit unknowns. Since whatever is learned about a terminal of the macro-device is automatically propagated to the identified terminal of the subcircuit, the two sets of laws can stimulate each other. If they disagree on their conclusions, a contradiction occurs.

When a macro-device, such as ECP, models some aspect of a configuration of devices with nonlinear properties, the special laws of the macro-device may be contingent on the operating regions of its components. It is also often true that the whole configuration has fewer consistent states than one would calculate from the those of the parts taken independently. Furthermore, as

in the case of the ECP, there may not be any assignment of regions (using the simple transistor model) to the components which is consistent with the known behavior of the configuration.

This set of problems is resolved by allowing a macro-device to have a set of operating regions of its own, on which its own laws are contingent. Furthermore, the macro-device must be able to control the assignment of operating regions to its components. Thus, for example, an ECP may be either "active" or "pinned" (Pinned means that one transistor is either saturated or cutoff whereas active means that both transistors still have room to maneuver.). If the ECP is pinned, the normal laws of transistors apply, except that we know that both transistors cannot both be active. If the ECP is active, then both transistors in it are assigned the special region "ecp-active", suspending the normal laws for transistors and providing a set of laws for this special situation. In the ECP case, the active state is further broken down into two subcases — it is either "balanced" or "unbalanced". The ECP is assumed to be balanced, but then if the rest of the circuit unbalances it, the balancing constraint is dropped. These rules are embedded as special laws for the ECP.

Although EL can identify a specified part of a circuit with a device of a specified type, it does not have the ability to associate a macro-device type with a generic equivalent circuit. Such an ability would make possible the two operations of recognition of the occurrence of such macro devices as emitter-coupled-pairs or complementary pairs, without "hints" from the user, and expansion of a macro-device into an identified equivalent circuit. The latter operation might facilitate the use of an EL-like subprogram by a circuit-design program (either entirely automatic, or merely assisting a human). In addition, it might be applied to devices such as transistors, which are not "really" macro-devices, but which an equivalent circuit might at times allow EL to model more accurately.

However, such operations are more complicated than they seem. An equivalent circuit recognizer that would accept only a specific exact pattern of circuitry would be of very little use. This is because the "circuit" of such an application as the ECP is so unconstrained; there can be many different arrangement of components in between the two transistors, that will have slight but useful effects on the behavior of the circuit without making it useless to view the configuration as an ECP. Thus, the recognizer must be able to be flexible in its criteria. The expansion operation is even more problematical, for while the recognizer can accept many circuit configurations, the expander must choose one appropriately, or give the user the ability to specify changes in almost all the details of its expansion. But making the user specify too many details would deprive the expansion operation of its usefulness.

# The Queue-based Control Structure

The gross-scale control structure used in ARS is event-triggered, as in a production system or a Markov algorithm, rather than sequential as in a classical programming language. Sequential control structure is confined to the inside of a law or demon; demons cannot transfer control to other demons, but only return to the scheduler, which has queues of demons to run and arguments to feed them. Demons can affect the future actions of the program only by adding to the queues, but even that is not done directly. Instead, demons assert, and the process of assertion enqueues demons whose trigger-patterns match the newly asserted fact. This produces a degree of isolation for each individual demon, automatically making most device-law demons very modular. It also obviates a great deal of decision-making that would otherwise have to go into the sequential algorithms for handling many local circuit configurations. Circuit analysis must deal with many different types of building blocks, strung together in any order. Without the queue, the overall structure of the deduction process would be that of a loop containing a single many-way dispatch that decided what type of deduction was appropriate to perform next.

There are actually several queues for demon-invocations, with different priorities. Each demon specifies which queue it should go on. There are three queues used for DC analysis. Most demons, including equation-laws, are intended primarily for deducing new facts. They go on the middle priority or normal queue. Monitor demons, which exist mainly for finding contradictions, go on the high priority queue. That is because if there is no contradiction then all the demons will be executed eventually anyway, so their order makes no difference; if there is a contradiction, then the faster it is found, the less time it wastes. The low priority queue is used for choosing device-state assumptions, because it is best to explore all the consequences of one assumption before making more assumptions, in case there is a contradiction. Moreover, the possible states for a device can sometimes be narrowed down by knowledge about the device's environment. Given the opportunity to try deduction or to assume a device's state, it is better to make the deduction first, since they must both be done eventually, and the deduction has a chance of reducing the amount of work involved in finding the correct device-state if the deduction is done first.

There are three more queues for AC analysis, with lower priority than the DC queues. That is because the EL laws make it is very unlikely for a contradiction to involve any of the AC analysis; if the DC analysis finds none, there probably is none. Again, it pays to avoid doing any AC analysis for states that are going to be ruled out anyway.

Unfortunately, the queues of ARS are a very sensitive data structure. If any demon that in fact ought to be run is missing from the queue, nothing will ever detect that fact, or put it back on the queue, since that could be done only by the assertion of the fact that can trigger the demon, and said fact is already asserted. Such problems are not hard to avoid when only straightforward propagation is involved. The real difficulties come with contradictions. They are of two kinds: those accompanying the forgetting or outing of facts, and those that pertain to the very demons which detect the contradictions.

When a demon in ARS detects a contradiction, it drops what it was doing and makes a contradiction-assertion instead, causing the contradiction to be processed immediately. In some cases, that is guaranteed to cause the outing of at least one of the facts on which the demon's operation depended. Such cases are non-problematical, if (as is usually the case) the demon will be

incapable of doing any useful work until a similar fact is later asserted, and such an assertion will enqueue the demon in the normal manner. However, not all demons have that useful property. A case in point is that of the monitor demon IE-MONITOR-BJT, which examines the emitter currents of all transistors. If the emitter current is zero, and the transistor is currently assumed to be active, the monitor detects a contradiction. If there is no assumption in force at the moment about the transistor's state, the demon asserts that the transistor is cut off. Thus, if the demon is run because the emitter current has just been asserted to be zero, and a contradiction is detected, the demon really ought to be run again so it can make "cut off" the new state. To make that happen, the demon explicitly requeues itself.

Most laws are simply equations relating circuit parameters (Ohm's law is an example). The normal case in which such a law can do useful work is when all but one of the parameters it connects are known. In that case the unknown one is determined from the others. If more than two are not known, the demon is helpless. Because of that, no special action is necessary if one of the known parameter values is outed. But it can also happen that all of the parameters are known, but at least one of them is an algebraic expression containing a symbolic unknown. The equation of the law can then be used to solve for the value of the unknown. This is fine and dandy until one of the circuit parameters' values is outed because of backtracking. After that, though there is not enough information any more to solve for the symbolic unknown, it is still possible to compute the missing parameter from the others. For this, the demon must be run again. That is brought about using the mechanism of forget-functions. Any assertion can have a forget-function, which will be called whenever the assertion is forgotten or merely outed. In this example, a special assertion called the CHECKED assertion is placed in the dependency-chain between the assertion of the value of the symbolic unknown and the facts used as the demon's antecedents. Its only use is to hold on to a forget-function that will requeue the equation-demon if the CHECKED assertion ever vanishes (because one of the circuit parameters in the equation was forgotten). In fact, the CHECKED assertion is necessary even if there is no symbolic unknown in the circuit parameters' values, since it is still the case that if one parameter is forgotten it can be rededuced from the others. Note that in this case the equation of the demon has given no new information about the circuit, showing that the equation was algebraically dependent on the other equations describing the circuit. Such an event happens at least once per circuit, since at each node KCL, Kirchoff's current law, states that the sum of the incoming currents is zero, and that set of equations is not independent: KCL on any one node follows from KCL on all the other nodes.

Some monitor demons have the ability to predetermine the state of a device, eliminating the need for searching. For example, if I-MONITOR-DIODE sees a nonzero current in a diode, it can assert that the diode is in the ON state. When a device-state choice is *outed*, all the monitors that might be able to predetermine the state choice should be given a chance to do so. This is also implemented by a forget-function.

Monitor demons often check the signs of currents, or otherwise test inequalities. While equations are quite happy with algebraic expressions, inequalities are stymied by them (unless one uses a more sophisticated algebraic manipulation package than ours). For example, if a transistor's emitter current is assigned a value which involves a symbolic unknown, IE-MONITOR-BJT will be run, but will be unable to perform its function. Presumably that unknown's value will eventually be learned, and it is essential that IE-MONITOR-BJT be run again then, or else a contradiction

might go unnoticed and a false analysis be accepted. That is brought about by means of the <u>HANGING</u> assertion, which records the name of a demon (and its arguments) and the name of a symbolic unknown whose value the demon is waiting for. IE-MONITOR-BJT itself makes a HANGING assertion when it sees such an obstacle. Whenever the value of a symbolic unknown is determined, a check is made for HANGING assertions listing it, and the demons they mention are requeued.

The above examples are not the only cases in which demons need to be requeued; some are quite obscure. The examples described should suffice to show why the queue is a constant source of bugs. Because of that, we have given thought to possible mechanisms that might have the same modularizing ability as the queue, without its fragility. One which was actually implemented at one time was to keep the queue information in the data base of facts. The dispatcher which now removes entries from the queue and processes them, in that implementation used to scan the data base for possible places to run demons and run one. The only new information that had to be stored was the list of demon-invocations already performed — in the form of a HAS-RUN assertion for each successful demon-invocation — so that the dequeuer could avoid running demons redundantly. This eliminated all danger of accidentally losing an entry from the queue, since the whole queue was effectively recomputed each time it was used. It also made CHECKED assertions unnecessary, since the outing of a HAS-RUN assertion would automatically subject the demon to being rerun. Unfortunately, in our implementation, this mechanism proved to be unacceptably slow. Output loss of the subject to the demon to being rerun.

## The Data Base of Facts and Demons

ARS stores all problem-specific knowledge in the form of facts or assertions in an indexed data base. An example of a fact is (= (VOLTAGE (E Q1)) 1.3), which EL takes to mean that Ql's emitter voltage is 1.3 volts. (ALTERNATIVES (MODE DIODE) (ON OFF)) says that the device-state of a diode, known in EL as its MODE, has two possible values, called ON and OFF. The first sample fact is typical of many of the facts EL generates as it runs. The second is actually part of EL, and represents knowledge appropriate to choosing diodes' states.

Besides its statement (which is what "(\* (YOLTAGE (E Q1)) 1.3)" is), a fact also has a unique factname, which is a LISP atom. The factname's LISP property list is used to record the fact's auxiliary information, such as its dependency records, whether it is currently believed, its forget-function (see below) -- everything other than just "what the fact says". In addition, the fact is referred to whenever possible by its factname (in dependency records, for example). It is tempting, when using a relational data base, to break all knowledge into small pieces and make each piece a separate assertion. That can lead to great inefficiency, as we discovered when using early versions of ARS. Since then, we have rewritten ARS to use the indexed data base mainly as a way of placing property lists on arbitrary LISP lists as if they were atoms. One might suggest that a simple hash table might serve, but that is in fact how the data base is implemented anyway. Equality

EL records the names of the devices in a circuit with <u>IS-A</u> assertions, such as (IS-A R1 RESISTOR) or (IS-A N54 NODE). An EL demon driven by those assertions controls an ARS mechanism for typed variables in the trigger slots of laws. Whenever an IS-A is asserted, a LISP property is placed on the device's name that identifies it as a certain type of device. The pattern matching mechanism that triggers demons then insists that a typed pattern variable (such as R, in the demon DC-OHM) match only the name of a device of the appropriate type.

Demons in ARS are programs subject to pattern-directed invocation. Each EL demon generally implements a single item of knowledge about electronics (though a few embody more general problem-solving knowledge). Here, for example, is the demon that embodies the fact that all of the current into one of a resistor's terminals comes out the other one. This law is needed because the fact data base is not constructed so as to retrieve (CURRENT (#1 R1)) and (CURRENT (#2 R1)) from the same place automatically.

```

(LAM DC-2T-R ASAP ((R RESISTOR) 11 12)

()

((= (CURRENT (#1 !?R)) !>11) (= (CURRENT (#2 !?R)) !>12))

(EQUATION '(&+ 11 12) 0.0 R))

```

Its name, chosen by us for mnemonic significance, is DC-2T-R. ASAP indicates its invocation priority. DC-2T-R uses the local variables I1 and I2 to hold the two terminal currents. The long list beginning with (= (CURRENT ... contains the demon's trigger slots. Their purpose is dual: to provide patterns to direct the invocation or triggering of the demon, and to gather the information needed in applying the law once the demon is invoked.

When the function LAW, a LISP macro, is called to create the demon DC-2T-R, it stores information about the trigger slots in the demon data base, which has the form of a stylized decision tree which, applied to a fact, quickly finds those demons which have at least one trigger slot that matches the fact. Each of those demons has one of the facts it needs to be able to do useful work; it might or might not have all it needs. ARS enqueues them all for invocation, and the demons themselves must decide whether they can do anything. For that, they use the trigger slots again, applying them all as patterns to the fact data base. Thus, if (\* (CURRENT (#1 R1)) 10.8) is asserted, DC-2T-R will be triggered, and the value matched by the part variable R will be remembered as an argument (the declaration of R as (R RESISTOR) will prevent triggering unless what R matches is actually the name of a resistor).

When the demon is invoked it will apply all of its trigger patterns to the data base, using its argument as the value of R during the match — that is how we make sure that we find voltages, current and resistance for a single resistor instead of for four different resistors! Variables appearing in the pattern with the "!>" operator have no effect on the triggering of the demon, but at the matching stage they are assigned whatever value they happen to match, if the pattern matches anything at all. Thus, if in addition to the triggering assertion about the voltage at (#1 R1), the two facts (= (VOLTAGE (#2 R2)) 0.0) and (= (RESISTANCE R1) 1000.0) were in the data base, DC-OHM's matching phase would set V1 to 10.8, V2 to 0.0, and RES to 1000.0. I would remain NIL if there were no assertion about the value of (CURRENT (#1 R1)).

In addition to setting local variables, the matching process places a list of the factnames of the facts matched in the variable ANTECEDENTS, along with the demon's <u>demonname</u>. If the demon asserts any new fact, it will normally supply that list as the antecedents of the fact. This is how the dependency records obtain the information of what other facts were used in deducing the new one.

After the matching phase, the <u>body</u> of the demon is executed. In this case the body is just a call to the function EQUATION, which does all the work of extracting any possible new information from the specified equation and the parameter values obtained by the match phase. It also knows how to report a contradiction if the parameters have values that can't fit the equation, and that there is nothing to be done if too few of the parameters are known yet.

### How it works:

ARS has three different storage representations for the three main types of entities it knows: facts, demons, and dependencies. Dependencies are stored as simple LISP lists. Each fact's factname has a CONSEQUENCES property which is a list of the factnames of all the facts deduced from it, and an ANTECEDENT-LISTS property which is a list of lists, one list for each way the fact has been deduced, containing the factnames of the facts used in the deduction.

A demon is more complicated. In addition to the LISP function which implements its body it must enter its trigger slots in a data base that allows that slots that match a given fact to be found easily. ARS compiles the trigger slots into a decision-tree Discrimination nets which it builds incrementally. The tree specifies locations in the fact being matched against (such as, "the CAR of the CAR of the CDR"), and then various things to compare it against, each leading to some demons or to further decisions.

The fact data base is the most complex of the three. It is a bare-bones version of the

Conniver data base. It indexes each fact by each of the atoms in it, together with its position. Thus, the fact (= (VOLTAGE (B Q1)) 10.0) would be indexed under "= in the CAR", "VOLTAGE in the CAADR", "B in the CAADADR", "QI in the CADADADR", and "10.0 in the CADDR". This method of indexing makes it easy to look for all the facts that match a pattern which has some positions unspecified. In ARS's notation, !>F00 is a pattern which matches anything, and sets FOO to what was matched. (= (VOLTAGE (B !>Q)) !>V) ought to match any assertion about the voltage on the base of something. ARS can find all the facts that it matches by looking in the fact data base index under "= in the CAR", "VOLTAGE in the CAADAR", and "B in the CAADADR", and intersecting those lists of facts.

Actually, the index-pairs of atom and location are hashed into a fixed length table, so a bucket may contain things that are irrelevant to the index-pair being fetched. For that reason, an actual matching test must be made on each fact that the indexer returns.

Originally, all three types of data were kept in the fact data base. Facts were kept as lists (<statement> FACT <factname>), demons as lists (<slot> DEMON <demonname>), and dependencies as lists (<factl> DEPENDS <fact2>). This had the advantage of being easy to do, but was very inefficient. This was obviously so for dependencies, whose representation we changed shortly after ARS began to look at them during normal operation. It was not nearly so obvious that this was a bad way to store the trigger slots of demons. That was discovered only by timing measurements. The problem was due to the fact that the search operation for demon slots is different from the search operation for facts. Facts are searched for with a pattern like (= (VOLTAGE (B !>Q)) !>V), and wherever it has an atom, all the facts it matches must have the same atom. On the other hand, when a fact such as (= (VOLTAGE (B Q1)) 10.0) is asserted, the slots that should trigger might differ from the fact itself in any position. For example, (= (!>QTY !>TERMINAL) 10.0) should be triggered if it exists, as should (= !>ANYTHING !>VALUE), (!>RELATION (YOLTAGE (B !>Q)) !>NUMBER), (+ (!>QTY (!>ECB !>Q)) !>VALUE), or even just !>FACT if any demon has it as a slot! The fact data base is poorly suited to that retrieval operation. The implementation of a separate demon data base resulted in a factor of two improvement in the speed of the entire system.

A lesson to be drawn from the experience with the ARS data base is that it is usually worthwhile to factor the retrieval problem. We had a data base whose entries could be divided easily into three classes, such that any retrieval would certainly be looking for entries in only one of the three. Now we have three data base systems, one for each class.

We think this corrected mistake is worth mentioning because it isn't a new one -Conniver made the same mistake! IF-ADDED methods were stored in the fact data base and looked up just as ARS demons formerly were. People have often assumed that the slowness of Conniver was due to the basic interpreter, but in fact measurements showed that Conniver spent most of its time searching the data base. Our results with ARS suggest that Conniver also might run considerably faster with ARS's newer demon data base.

### Conclusions

Our research strategy has been the application of artificial intelligence techniques to the construction of an expert problem solver in a non-trivial domain. We feel that this strategy has been very fruitful. We have developed two methods. One is a method of electrical network analysis we call analysis by propagation of constraints. The other is the technique of efficient combinatorial search by dependency-directed backtracking. Analysis by propagation of constraints would not have been developed in the absence of such artificial intelligence techniques as symbolic manipulation of algebraic expressions and antecedent reasoning. Dependency-directed backtracking is a new artificial intelligence technique whose development was stimulated by the needs of this exceptionally deep, yet well-structured domain.

Electrical circuits is an especially good domain in which to develop artificial intelligence techniques. Reasoning about circuits is deep enough to benefit by the application of powerful techniques, yet the problems are drastically simplified by the fact that the interactions between parts of a circuit are well-defined and constrained to occur by explicit connections. Another advantage is that it is clear whether or not an answer tendered is in fact correct.

An even more important reason for studying reasoning about electrical circuits is that such reasoning is typical of the reasoning done by all engineers, including computer programmers. We wish to understand the nature of reasoning about deliberately constructed systems. An understanding of the epistemology of engineering will enable us to make programs which can significantly aid the design and debugging of engineered systems, including computer programs. We expect that such an understanding will entail the development of techniques concerned with many aspects of reasoning, including constraints, causality, and teleology.

## Generality and Extensibility

ARS is a language in which it is easy to embed problem solving rules for domains in which the solution to a problem may be obtained by the symbolic relaxation of local constraints. It provides special features for explanation of its conclusions to its users and it uses this ability to provide for reasoning hypothetically and for efficient combinatorial searches. We are convinced that the ARS paradigm is applicable to a wide variety of domains. Jon Doyle <Doyle 1976> has looked into the possibility of a set of ARS rules to prove theorems of plane geometry (no constructions) along the lines previously investigated by Nevins <Nevins 1974>. Matt Mason <Mason 1976> has constructed a set of rules for the analysis of the flow of materials and money in a hog farm.

EL, the set of rules of electrical circuit analysis, is a very pleasant system to work with. The explanations it provides to a user can be useful for helping understand the behavior of a circuit — how particular device parameters affect the behavior of interesting circuit parameters. If a particular answer is surprising it is possible to find out why EL thinks that that answer is true. The user can have more confidence in these answers because he can check the reasoning. The complex programs of the future will most certainly have to use similar techniques so as to be responsible for their answers.

EL is very extensible because of the modularity imposed on it by the conventions of ARS. It is easy to add new device types to EL because the rules for the new elements can be

constructed in isolation and usually do not interact with the laws for the existing devices. This is even true in the case of macro-devices because the macro-device gets control of the selection of states for its parts. Gerald Roylance <Roylance 1975> created rules for enough macro-device types to allow the analysis of the 741 operational amplifier. In fact, it would be easy to add enough rules to create whole new analysis modes. To add sinusoidal steady state analysis, for example, would require only a set of laws which characterized parts in terms of impedances and a small extension to the algebraic manipulation package to allow the manipulation of complex quantities.

## Problems and Plans for the Future:

There are many modes of reasoning about circuits which we have not captured in EL. Some of these, such as sinusoidal steady state analysis are really very simple extensions which we have just not yet gotten around to doing. Others, however are much harder and may represent more fundamental problems with the ARS paradigm for embedding of knowledge.

For example, it is not obvious how to represent the knowledge required to do timedomain analysis in ARS. In steady state, dc, or incremental analysis, it is possible to summarize the entire behavior of a network unknown as a simple, algebraically manipulable expression. Time domain analysis requires explicit time functions, some of which might be algebraically horrendous, to be manipulated. Gerald Roylance <Roylance 1976> is beginning to investigate what kinds of qualitative reasoning is required to bypass this algebraic roadblock.

Simple equation demons are an essentially declarative representation for equality constraints, even though demons are procedures. Inequalities are represented as monitors and cannot be manipulated easily. This leads to the following problem: