# MASSACHUSETTS INSTITUTE OF TECHNOLOGY ARTIFICIAL INTELLIGENCE LABORATORY

A.I.MEMO 739

JUNE, 1984

## DIAGNOSTIC REASONING BASED ON STRUCTURE AND BEHAVIOR

Randall Davis

The Artificial Intelligence Laboratory

Massachusetts Institute of Technology

Cambridge, MA 02139

#### Abstract

We describe a system that reasons from first principles, i.e., using knowledge of structure and behavior. The system has been implemented and tested on several examples in the domain of troubleshooting digital electronic circuits. We give an example of the system in operation, illustrating that this approach provides several advantages, including a significant degree of device independence, the ability to constrain the hypotheses it considers at the outset, yet deal with a progressively wider range of problems, and the ability to deal with situations that are novel in the sense that their outward manifestations may not have been encountered previously.

As background we review our basic approach to describing structure and behavior, then explore some of the technologies used previously in troubleshooting. Difficulties encountered there lead us to a number of new contributions, four of which make up the central focus of this paper.

We describe a technique we call constraint suspension that provides a powerful tool for troubleshooting.

We point out the importance of making explicit the assumptions underlying reasoning and describe a technique that helps enumerate assumptions methodically.

The result is an overall strategy for troubleshooting based on the progressive relaxation of underlying assumptions. The system can focus its efforts initially, yet will methodically expand its focus to include a broad range of faults.

Finally, abstracting from our examples, we find that the concept of *adjacency* proves to be useful in understanding why some faults are especially difficult and why multiple different representations are useful.

This report describes research done at the Artificial Intelligence Laboratory of the Massachusetts Institute of Technology. Support for the laboratory's Artificial Intelligence research on electronic troubleshooting is provided in part by the Digital Equipment Corporation and in part by the Defense Advanced Research Projects Agency.

(c) Massachusetts Institute of Technology 1984

## CONTENTS

| 1. INTRODUCTION                                                   | <u>ح</u> |

|-------------------------------------------------------------------|----------|

| 2. CENTRAL CONCERNS                                               | 5        |

| 3 DESCRIBING STRUCTURE                                            | 1        |

| 4. DESCRIBING BEHAVIOR                                            | 1        |

| 4.1 Simulation Rules and Inference Rules 1                        | 1        |

| 4.2 Implementation                                                | 1        |

| 5. TROUBLESHOOTING                                                | 3        |

| 5.1 The Traditional Approach                                      | 3        |

| 6. DISCREPANCY DETECTION AND CANDIDATE GENERATION                 | 5        |

| 6.1 Constraint Suspension                                         | 6        |

| 6.2 Advantages of Discrepancy Detection and Constraint Suspension | 19       |

| 6.3 Subtleties in Candidate Generation                            | 20       |

| 7. MECHANISM AND KNOWLEDGE                                        | 22       |

| 8. ORGANIZING THE PATHWAYS OF INTERACTION                         | 23       |

| 9 FXAMPLE: A BRIDGE FAULT                                         | 25       |

| 9.1 The Example                                                   | 26       |

| 9.2 The Example: Summary and Comments                             | 31       |

| 10. CATEGORIES OF FAILURE                                         | 33       |

| 10.1 Origins                                                      | 33       |

| 10.2 Ordering                                                     | 34       |

| 11. THE ADJACENCY PRINCIPLE                                       | 36       |

| 12 FVALUATION AND FUTURE WORK                                     | 39       |

| 12.1 Advantages of Reasoning From Structure and Behavior          | 39       |

| 12.2 Describing Structure and Behavior                            | 40       |

| 12.3 Limitations in Candidate Generation                          | 43       |

| 12.4 Comments on the Example                                      | 43       |

| 12.5 The Example: Implementation                                  | 44       |

| 12.6 Scaling: Device Complexity and Time                          | 44       |

| 12.7 Limits of Modeling: Analog Devices and Incomplete Models     | 45       |

| 12.8 But That's Not How It's Really Done                          | 46       |

| 13. RELATED WORK                                                  | 47       |

| 13.1 Hardware Diagnosis                                           | 47       |

| 13.2 Fault Models and Categories of Failure                       | 48       |

| 13.3 Other Al Work                                                | 48       |

| 14 SUMMARY                                                        | . 51     |

## 1. INTRODUCTION

The overall goal of this research is to develop a theory of reasoning that exploits knowledge of structure and behavior. We proceed by building programs that use such knowledge to reason from first principles in solving problems. The initial focus is troubleshooting digital electronic hardware, where we have implemented a system based on a number of new ideas and tools.

Troubleshooting digital electronics is a good domain for several reasons. First, troubleshooting seems to be one good test of part of what it means to "understand" a device. We view the task as a process of reasoning from behavior to structure, or more precisely, from misbehavior to structural defect: given symptoms of misbehavior, we are to determine the structural abberation responsible for the symptoms. Second, the task is interesting and difficult because the devices are complex and because there is no established theory of diagnosis for them. Third, the domain is appropriate because the required knowledge is readily available from schematics and manuals. Finally, the application itself is relevant and tractable.

Work with a similar intent has been done in other domains, including medicine [23], computer-aided instruction [6], and electronic troubleshooting [7,18], with the "devices" ranging from the gastro-intestinal tract, to transistors and digital logic components.

This work is novel in a number of respects, some of which have been reported in an earlier publication [8]. As noted there:

We have developed languages that distinguish carefully between structure and behavior, and that provide multiple descriptions of structure, organizing it both functionally and physically.

We have argued that the concept of paths of causal interaction is a primary component of the knowledge needed to do reasoning from structure and behavior.

We have developed an approach to troubleshooting based on the use of a layered set of categories of failure and demonstrated its use in diagnosing a bridge fault.

This paper substantially expands and develops this line of work, reporting several new contributions:

We describe a new technique called *constraint suspension*, capable of determining which components can be responsible for an observed set of symptoms.

We show that the categories of failure, previously derived informally, can be given a systematic foundation. We show that the categories can be generated by examining the assumptions underlying our representation.

This in turn gives us a new way to view our approach to troubleshooting: the methodical enumeration and relaxation of assumptions about the device.

Finally, we describe the concept of *adjacency* and argue that it helps in understanding both what it means to have a good representation, and why multiple representations can be useful.

Section 2 is introductory, supplying a brief review of the overall concerns, expanding on the ideas listed above as a preview of what is central to this work.

<sup>1.</sup> For the sake of continuity and ease of presentation, parts of [8] are reprinted here, including the bridge fault example and some of the background material (machinery for describing structure and function, and the introduction to troubleshooting). This material is reprinted with permission from [8], Copyright Academic Press Inc. (London) Ltd.

If we are to reason from first principles, we require: (i) a language for describing structure, (ii) a language for describing behavior, and (iii) a set of principles for troubleshooting that uses the two descriptions to guide its investigation. The central part of the paper describes each of those components, paying particular attention to the nature of the reasoning that underlies troubleshooting.

Sections 3 and 4 explore our approach to describing structure and behavior, while Sections 5 through 9 deal with troubleshooting. In Section 5 we consider the machinery traditionally used to reason about circuits and show that it fails to solve the problem we face. We then show how a technique called discrepancy detection offers a number of useful advances, but claim that it must be used with care. We suggest that the potential difficulties center around implicit assumptions typically made when using the technique. We find a solution to the problems encountered by making those assumptions explicit, organizing them appropriately, and providing for a way to surrender them one by one, methodically expanding the scope of failure the program considers. Section 9 provides an example of these ideas in operation, showing how they guide the diagnosis of a bridge fault.

In Sections 10 and 11 we draw back from the specific example presented and attempt to generalize our methods. We argue that the concept of paths of interaction offers a useful framework for asking questions about a domain. We claim that the notion of "adjacency" both explains some of the difficulty in reasoning about bridges and provides guidance in selecting and using multiple representations.

Section 12 reviews the machinery we have presented, pointing out its limitations and suggesting directions for future work. Finally, Section 13 compares our work to a number of previous approaches to similar problems.

## 2. CENTRAL CONCERNS

Some of the examples in later sections of this paper require a substantial amount of detail, yet the principles they illustrate are often relatively uncomplicated. In order to be sure that the important points are not lost in the detail, we describe the fundamental principles here briefly, enlarging on them in the remainder of the paper.

† Candidate generation can be achieved by using a new technique we call constraint suspension.

Given the symptoms of a malfunction, we wish to generate candidate components, i.e., determine which components could plausibly be responsible for the malfunction. We model the intended behavior of a device as a network of interconnected constraints, where each constraint models the behavior of one of the components. If the device is malfunctioning, then the outputs predicted by the entire constraint network will not match the actual outputs. Normally, contradictions in constraint networks are handled by retracting one or more of the input values. Constraint suspension takes the dual view and asks instead, *Is there some constraint (component behavior) whose retraction will leave the network in a consistent state?* Each such constraint that we find corresponds to a component whose misbehavior can account for all the observed symptoms. In many cases the technique will also supply the details of the component misbehavior (i.e., show how it is misbehaving). We describe the technique in detail in Section 6.1.

† Paths of causal interaction play a central role in troubleshooting.

An important part of the basic knowledge needed for troubleshooting is understanding the mechanisms and pathways by which one component can affect another. Electronic components typically interact because they are wired together, but they can also interact due to heat, capacitive coupling, etc. We argue that viewing the problem in terms of paths of interaction is more useful and revealing than the fault models (e.g., stuck-ats) traditionally used.

† In doing troubleshooting we are faced with an unavoidable problem of complexity vs. completeness.

To be good at troubleshooting, we need to handle many different kinds of paths of interaction. But this presents a serious problem. If we include all possible paths, candidate generation becomes indiscriminate: every component could somehow be responsible for the observed symptoms. Yet omitting any one path would make it impossible to diagnose an entire class of faults.

† One technique for dealing with this dilemma is enumerating and layering the categories of failure.

As experienced troubleshooters know, some things are more likely to go wrong than others. But what are the "some things"? And what does "more likely" mean? We make both of these notions more precise.

We show how to generate the "things that can go wrong" by making explicit the assumptions underlying our representation; the result is a list of "categories of failure". The categories are organized by using the most likely first and adding additional, less likely categories only in the face of contradictions.

Associated with each category of failure is a collection of paths of interaction. Hence the ordered listing of categories produces an ordering on the paths of interaction to be considered. This allows us to constrain the paths we consider initially, making it possible to constrain candidate generation. But no path is permanently excluded, hence no class of faults is overlooked.

† The result is a strategy for troubleshooting based on the methodical

enumeration and relaxation of underlying assumptions.

This technique allows us to deal with a progressively wider range of different faults without being overwhelmed by too many candidates at any one step.

† The categories of failure can be generated systematically by examining the assumptions underlying our representation.

As we demonstrate in Section 10, the categories can be derived by listing the assumptions implicit in the representation and considering the consequences of violating each in turn. Because the representation employs little more than the traditional notion of black boxes, the categories of failure deal with information transmission, and the results of this exercise have relevance broader than digital electronics. We suggest that the results are applicable to software and speculate about wider applications.

† The concept of <u>adjacency</u> proves to be useful in both troubleshooting and the selection of representations.

We noted above that the possible pathways for device interaction are an important part of the knowledge required for troubleshooting. We take the view that devices interact because they are in some sense adjacent: electrically adjacent (wired together), physically adjacent (hence "thermally connected"), electromagnetically adjacent (not shielded), etc. Each of these definitions can be used as the basis for a different representation of the device, different in its definition of adjacency. The multiplicity of possible definitions helps to explain why some faults are especially difficult to diagnose: they result from interactions between components that are adjacent in a sense (representation) that is unusual or subtle.

This concept appears to generalize in several ways. We view faults as modifications to the original design, and claim that changes that appear small and local in one representation may not appear small and local in another. We also suggest that adjacency can help determine what makes for a "good" representation: one in which the change can be seen as compact. It may also explain some of the utility of using multiple representations: they offer multiple different definitions of adjacency.

† Adjacency is a useful principle to the extent that the <u>single initial</u> <u>cause</u> <u>heuristic</u> holds true.

A common sense heuristic suggests that malfunction of a previously working device generally results from a single cause rather than a number of simultaneous, independent events. When there is indeed a single cause, there will be some representation in which a compact change accounts for the difference between the good and faulty device.

† The concept of a <u>single point of failure</u> is not well defined without specification of the underlying representation.

A failure in a single physical component, for example, may manifest as multiple points of failure in the behavior of the overall device. Consider a single chip with four AND gates in it. If the chip is damaged (via over-voltage, heat, mechanical stress, etc.), we will have a single point of failure in the physical representation, but may find four different points of failure (the four AND gates) in the functional view of the device. We claim as a result that "single point of failure" is by itself an under-determined concept. and that to make precise sense of the term we need to indicate the underlying representation to which "point" refers. We claim further that the use of multiple representations can add diagnostic power by offering different ways of resolving apparently independent failures into a single cause.

#### 3. DESCRIBING STRUCTURE

If we wish to reason about structure and behavior, we clearly need a way of representing both. We consider each of these in turn.

By structure we mean information about the interconnection of modules. Roughly speaking, it is the information that would remain after removing all the textual annotation from a schematic.

Two different ways of organizing this information are particularly relevant to troubleshooting: functional and physical. The functional view gives us the machine organized according to how the modules interact; the physical view tells us how it is packaged. We thus prefer to replace the somewhat vague term "structure" by the slightly more precise terms *functional organization* and *physical organization*. As we will see, every device is described from both perspectives, producing two distinct, interconnected descriptions.

Our aim is to provide a means of encoding in one place all of the information about a circuit that is typically distributed across several different documents. To this end our approach provides a way of representing much of the information traditionally found in a schematic, as well as the hierarchical description often encoded in block diagrams.

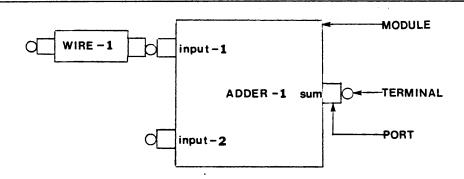

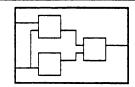

The most basic level of our structure description is built on three concepts: *modules*, *ports*, and *terminals* (Fig. 1). A module can be thought of as a standard black box; ports are the place where information flows into or out of a module. Every port has at least two terminals, one terminal on the outside of the port and one or more inside. Terminals are primitive elements; they are the places we can "probe" to examine the information flowing into or out of a device through a port, but they are otherwise devoid of interesting substructure.

Figure 1 - The basic terms used in structure description.

Two modules are attached to one another by superimposing their terminals. In Fig. 1, for example, wire-1 is a (wire) module that has been attached to the input-1 port of adder-1 (an adder module) in this fashion.

The language is hierarchical in the usual sense: modules at any level may have substructure. In practice, our descriptions terminate at the gate level in the functional hierarchy and the chip level in the physical hierarchy, since for our purposes these are black boxes — only their behavior (or misbehavior) matters. Fig. 2 shows the next level of structure of the adder and illustrates why ports may have multiple terminals on their inside: ports provide the important function of shifting level of abstraction. It may be useful to think of the information flowing along wire-1 as an integer between 0 and 15, yet we need to be able to map those four bits into the four single-bit lines insider the adder. Ports are the place where such information is kept. They have machinery (described below) that allows them to map information arriving at their outer terminal onto their inner terminals.

Since our ultimate intent is to deal with hardware on the scale of a mainframe computer, we

need terms in the vocabulary capable of describing levels of organization more substantial than the terms used at the circuit level. We can, for example, refer to *horizontal*, *vertical*, and *bitslice* organizations, describing a memory, for instance, as "two rows of five 1K ram's". We use these specifications in two ways: as a description of the organization of the device and a specification for the pattern of interconnections among the components.

Our eventual aim is to provide an integrated set of descriptions that span the levels of hardware organization ranging from interconnection of individual modules, through higher level of organization of modules, and eventually on up through the register transfer and PMS [4] levels. Some of this requires inventing vocabulary like that above, in other places we may able to make use of existing terminology and concepts.

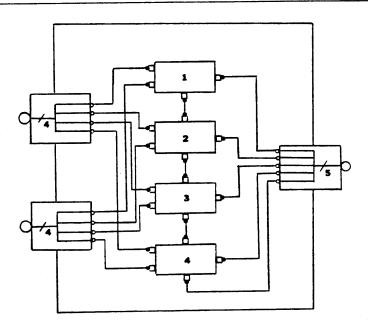

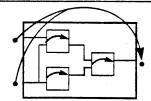

Figure 2 - Next level of structure of the adder, showing that it is implemented as a ripple-carry.

The structural description of a module is expressed as a set of commands for building it. The adder of Fig. 2, for example, is described by the instructions shown in Fig. 3. With NB itsWide bound to 4, the first expression indicates that we should repeat the following sequence of operations 4 times:

create an adder slice

run a wire from the first input of the adder to the first input of the slice

run a wire from the second input of the adder to the second input of the slice

run a wire from the output of the slice to the output of the adder

The next expression builds the carry chain and the last wires up the high order bit.

These commands are executed by the system, resulting in the creation of data structures that model all the components and connections shown. These data structures are isomorphic to the diagram shown above. That is, the data structures are connected in the LISP sense in the same ways that the objects are connected in Fig. 2. As in real devices, information flow occurs as a result of these interconnections: slice-l can place information on its end of the data structure modeling the carry-out wire, for example, because the two are superimposed. This information will then be propagated to the other end of the wire and pass into the data structure modeling slice-2 because those two are superimposed. The utility of this approach is explored below in Section 12.

Figure 3 - Parts are described by a pathname through the part hierarchy, e.g., (input-1 adder).

The definition in Fig. 3 is thus a specification of a prototypical ripple-carry adder; invoking it with a specific value for the width parameter produces one particular instance. We have found it useful to maintain this prototype/instance distinction for several reasons. It allows the standard economy of representation, since information common to all instances can be stored once with the prototype. It also makes possible the parameterization illustrated above, allowing us to describe the overall structure of the device, capturing the generalization inherent in the standard pattern of interconnections. Finally, it allows us to build up a library of module definitions available for later use. There is considerable utility in assembling such a library, utility beyond the ease of describing more complicated devices. By requiring that we define modules outside of the context of their use in any particular circuit, we encourage an important form of "mental hygiene" described further in Section 12.2.

Since our eventual aim is troubleshooting of devices as complex as a computer, the complete description of the device could become quite large. To deal with this we have made use of "lazy instantiation": when an instance of a module is created, only the "shell" is actually built at that time. For the adder above, for example, the outer "box" and ports are built, but the substructure --- the slices --- are not built until they are actually needed. Only when we need to "look inside" the box, i.e., drop down a level of structural detail, is additional structure actually built.

As a result, the system maintains a compact description of the device, expanding only where necessary. This can save a considerable amount of space. Even for the simple adder example above, there is a lot to describe: each slice is built from two half adders and an OR gate, each half-adder is built from an XOR and an AND gate. The initial instantiation is simply an adder with two inputs and an output, rather than four levels of detail and 20 gates. For more complex devices the savings can of course be greater.

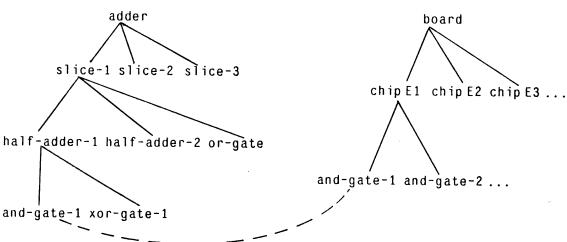

The examples above illustrate how we describe functional organization: an adder composed of slices, which are in turn composed of half-adders, etc. Exactly the same module, port and terminal machinery is used to describe physical organization, but now the hierarchy of modules is cabinets, boards, and chips.

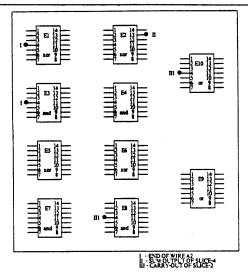

Since, as noted earlier, every component has both a functional and physical description, we have two interconnected description hierarchies. We represent this in our system by having the two hierarchies linked at their terminal nodes (Fig. 4).

<sup>2.</sup> We do not, by the way, have any special mechanism for dealing with wires. They are simply another module, albeit one with a particularly simple behavior: information presented to either port will be propagated to the other.

Figure 4 -- Interconnection of functional and physical descriptions

We determine the physical location of any non-terminal entry in the functional organization by aggregating the physical locations of all of its leaves. These descriptions are available at various levels of abstraction. The physical location of slice-1, for example, is the list of all the locations of its gates (e.g., E1, E4, E7, etc.); alternatively we can also say simply that it is on board-1, if all of those chips are in fact on the same board.

By having available cross-links between the two descriptions, it becomes possible to answer a range of useful questions. For example, we can ask, Where physically do I find the (part that functions as the) address translation register, or, What function(s) does this quad-and-gate chip perform?

Our description language has been built on a foundation provided by a subset of DPL [3]. While DPL as originally implemented was specific to VLSI design, it proved relatively easy to "peel off" the top level of language (which dealt with chip layout) and rebuild on that base the new layers of language described above.

Since pictures are a fast, easy and natural way to describe structure, we have developed a simple circuit drawing system that permits interactive entry of pictures like those in Figs. 1 and 2. Circuits are entered with a combination of mouse movements and key strokes; the resulting structures are then "parsed" into the language shown in Fig. 3.

## 4. DESCRIBING BEHAVIOR

By behavior we mean the black box description of a component: how is the information leaving the component related to the information that entered it? A variety of techniques have been used in the past to describe behavior, including simple rules for mapping inputs to outputs, petri nets, and unrestricted chunks of code. Simple rules are useful where device behavior is uncomplicated, petri nets are useful where the focus is on modeling parallel events, and unrestricted code is often the last resort when more structured forms of expression prove too limited or awkward. Various combinations of these three have also been explored.

## 4.1 Simulation Rules and Inference Rules

Our initial implementation is based on a constraint-like approach ([30], [32]). Conceptually a constraint is simply a relationship. The behavior of the adder of Fig. 1, for example, can be expressed by saying that the logic levels of the terminals on ports *input-1*, *input-2* and *sum* are related in the obvious fashion.

In practice, this is accomplished by writing a set of expressions covering all the different individual relations (the three for the adder are shown below) and setting them up as demons that watch the appropriate terminals. A complete description of a module, then, is composed of its structural description as outlined earlier and a behavior description in the form of rules that interrelate the logic levels at its terminals.

```

to get sum from (input-1 input-2) do (+ input-1 input-2)

to get input-1 from (sum input-2) do (- sum input-2)

to get input-2 from (sum input-1) do (- sum input-1)

```

A set of rules like these is in keeping with the original conception of constraints, which emphasized the non-directional, relationship character of the information. When we attempt to use it to model behavior of physical devices, however, we have to be careful. This approach is well suited to modeling behavior in analog circuits, where devices are largely non-directional. But we can hardly say that the last two rules above are a good description of the *behavior* of an adder chip --- the device doesn't do subtraction; putting logic levels at its output and one input does not cause a logic level to appear on its other input.

The last two rules really model the *inferences we make about the device*. Hence our implementation distinguishes between *simulation rules* that represent flow of electricity (digital behavior, the first rule above) and *inference rules* representing flow of inference (conclusions we can make about the device, the next two rules).

We find this distinction useful in part for reasons of "mental hygiene" (the two kinds of rules deal with different kinds of knowledge) and in part because it contributes to the robustness of the simulation in the face of unanticipated events. Consider for example a circuit that included an adder, and imagine that a fault in that circuit resulted in some other component trying to drive the output of the adder. If we treated all rules the same, our simulation would suggest that the device did the subtraction described above, yet this simply doesn't happen.

## 4.2 Implementation

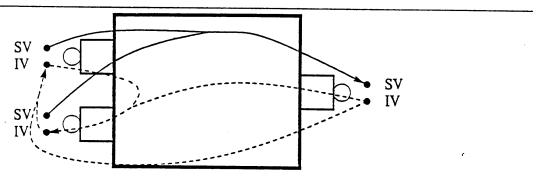

Our implementation accomplishes this distinction by using two parallel but separate networks, one containing the simulation rules modeling causality, the other containing the inference rules. We keep them distinct by giving each terminal two slots, one holding the value computed by the simulation rules, the other holding the value computed by the inference rules (Fig. 5). Each

network then works independently, using the standard demon-like style of propagating values through its collection of slots.

Figure 5 - Adder with one simulation rule (solid) and two inference rules (dashed). (SV - simulation value; IV - inference value)

In addition to firing rules to propagate information around the network, this rule-running machinery also keeps track of dependencies. allowing us to determine how the value in a slot got there. This is done by having each slot keep track of (i) every rule that uses this slot as an input, (ii) every rule that can place a value in this slot (i.e. uses it as an output) and (iii) which rule did, in fact, provide the current value (since, in general, more than one rule can set the value of a slot).<sup>3</sup>

This dependency network offers several advantages. As we explore below, it is one of the foundations of the discrepancy detection approach to troubleshooting. As the work in [6] demonstrated, such a network also makes it easy to explore hypothetical situations. We can place a value in some terminal and observe the consequences, i.e., see what values propagate from it. When done with the exploration, removing the value at the terminal causes the dependency network to remove everything that depends on it as well. This mechanism makes it easy to discover the answer to some questions by simulation: we can get the device to a particular state, then explore multiple alternative futures from that point.

While all of the examples given thusfar deal with combinatorial devices, we can also represent and model simple devices with memory. This requires three simple augmentations of the approach described above. First, we use a global clock and timestamp all values. Second, we extend the behavior rule vocabulary so that it can refer to *previous* values. For example, one simulation rule for a D flip-flop would be

To get output from (input previous-output clock)

do (if clock is high then input else previous-input)

Finally, our propagation machinery is extended to keep a history of values at each terminal (details are in [10]). This model of time is still very simple, but has allowed us to represent and reason about basic flipflops, memories, etc.

<sup>3.</sup> The user can also set a value; this is most commonly done at the primary inputs.

#### 5. TROUBLESHOOTING

Having provided a way of describing functional organization, physical organization and behavior, we come now to the important third step of providing a troubleshooting mechanism that works from those descriptions. We develop the topic in three stages. In the first stage we consider test generation --- the traditional approach to troubleshooting --- and explain how it falls short of our requirements.

We consider next the style of debugging known as discrepancy detection and demonstrate why it is a fundamental advance. Further exploration, however, demonstrates that this approach has to be used with care in dealing with some commonly known classes of faults. We suggest that the difficulties arise from a number of implicit assumptions typically made when troubleshooting.

In discussing how to deal with the difficulties uncovered, we argue for the primacy of *models* of causal interaction, rather than traditional fault models. We point out the importance of making these models explicit and separate from the troubleshooting mechanism. The result is a strategy for troubleshooting based on the systematic enumeration and relaxation of underlying assumptions. This approach allows us to deal with a progressively wider range of different faults, without being overwhelmed by too many candidates at any one step.

We demonstrate the power of this approach on a bridge fault, a traditionally difficult problem, showing how our system locates the fault in a focused process that generates only a few plausible candidates.

## 5.1 The Traditional Approach

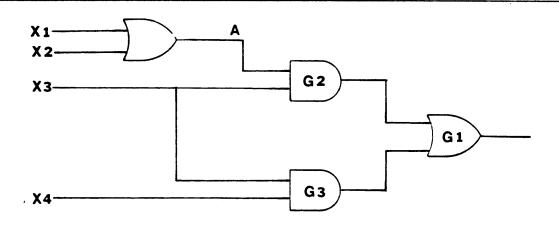

The traditional approach to troubleshooting digital circuitry (e.g., [5]) relies primarily on the process of path sensitization in a range of forms, of which the D-Algorithm [26] is one of the most powerful. A simple example of path sensitization will illustrate the essential character of the process. Consider the circuit shown in Fig. 6 and imagine that we want to determine whether the wire labeled A is stuck at 1. We try to put a zero on it by setting both x1 and x2 to 0. Then, to observe the actual value on the wire we set x3 to 1, thereby propagating the value unchanged through G2, and set x4 to 0, making the output of x4 and x4 to propagate unchanged through G1.

Figure 6 - Simple example of path sensitization.

Troubleshooting with this approach is then accomplished by running a complete set of such tests, checking for all stuck-ats on all wires.

For our purposes this approach has a number of significant drawbacks. Perhaps most important, it is a theory of *test generation*, not a theory of *diagnosis*. Given a specified fault, it is capable of determining a set of input values that will detect the fault (i.e., a set of values for which the output of the faulted circuit differs from the output of a good circuit). The theory tells us how to move from faults to sets of inputs; it provides little help in determining what fault to consider, or which component to suspect. Such questions are a central issue in our work because of complexity: the size of the devices we want to work with in the long run precludes the use of diagnosis trees — complete decision trees for all possible faults.

A second drawback of the existing approach is its lack of sharp distinction between between diagnosis in the field and verification at the end of the manufacturing line. As a result of economic and historical forces, diagnostics written to verify the correct operation of a newly manufactured device have been pressed into service in the field. Yet the tasks are sharply different. We are not requesting verification that a machine is free of faults. The problem facing us is "Given the observed misbehavior, determine the cause." We know that the device has worked in the past, we know that some part of it has failed, and we know the symptoms of that failure. Given the complexity of the device, it is important to be able to use all of this information as a focus for further exploration. Only if this fails might it make sense to fall back on a set of diagnostics that, by design, start with no information and test exhaustively.

A final drawback of the existing theory is its unavoidable use of a set of explicitly enumerated fault models.<sup>4</sup> Since the theory is based on boolean logic, it is strongly oriented toward faults whose behavior can be modeled as some form of permanent binary value, typically the result of stuck-ats and opens. One consequence of this is the paucity of results concerning bridging faults.<sup>5</sup>

In solving the diagnosis problem, though, we have a significant luxury: we can treat as an error any behavior that differs from the expected correct behavior. The misbehavior need not be modelable in terms of any fixed set of faults, it need only be different from what should have resulted.

In summary, the technology often used for troubleshooting is oriented toward test generation and the task of verification. We, on the other hand, are concerned with troubleshooting, a process that makes use of test generation (for an example, see [27]), but which requires as necessary precursors the processes of candidate generation (determining which components may be failing) and "symptom generation" (how they may be failing). The next section explores an approach that supports both of these.

<sup>4.</sup> Fault models are necessary in verification if we want to avoid the exponential effort of exhaustive testing. If we treat a device as a black box (e.g., saying only that it is an adder), we are forced to verify all of its behavior, a task that is potentially exponential in the number of inputs and amount of state. The most common way of avoiding this is by combining knowledge of the substructure of the device (e.g., that it is a carry-chain adder) with a specific set of faults to consider (e.g., stuck-ats on all wires), to produce tests for all such faults on all specified parts of the substructure. This task is at worst a product of the number of faults and wires.

<sup>5.</sup> While the theory underlying verification may be limited in the range of faults it can describe, in practice it turns out to handle a large part of the problem: experience indicates that a large percentage of all faults turn out to be detected (but not diagnosed) by checking just for stuck-ats. Hence we can determine that something is wrong (satisfying the verification task); determining the identity and location of the error (diagnosis), however, is a different problem.

## 6. DISCREPANCY DETECTION AND CANDIDATE GENERATION

One response to these problems has been the use of "discrepancy detection" (e.g., [11,6]). The two basic insights of the technique are (i) the substitution of violated expectations for specific fault models and (ii) the use of dependency records to trace back to the possible sources of a fault. Instead of postulating a possible fault and exploring its consequences, the technique looks for mismatches between the values it expected from correct operation and those actually obtained. This allows detection of a wide range of faults because misbehavior is now simply defined as anything that isn't correct, rather than only those things produced by a struck-at on a line.

The inspiration behind using dependency networks is that any component on the path from an input to an incorrect output could conceivably have been responsible for the faulty behavior. As we have seen, the simulator builds a dependency network by recording the propagation of values as it simulates the circuit. Using those records (or, equivalently, the original schematic) as a guide to which components to examine appears to be an effective way to focus attention appropriately. As we will see, it is in fact an interesting trap.

We work through a simple example to show the basic approach of discrepancy detection, then add to it the idea of constraint suspension. We comment on the strengths of the resulting procedure for candidate generation, then use the same example to illustrate difficulties that can arise.

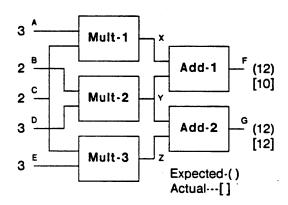

Consider the circuit in Fig. 7.6 If we set the inputs as shown, the system will use the behavior descriptions to simulate the circuit, constructing dependency records as it does so, and indicating that we should expect 12 at F.

Figure 7 - Troubleshooting example using discrepancy detection.

If, upon measuring, we find the value at F to be 10, we have a conflict between observed results and our model of correct behavior. We trace back through the dependency network to enumerate the possible sources of the problem [11]. The dependency record at F indicates that the value expected there was determined using the behavior rule for the adder and the values emerging from the first and second multiplier. One of those three must be the source of the conflict, so we have three possibilities to pursue: either the adder behavior rule is inappropriate (i.e., the first adder is broken),

<sup>6.</sup> As is common in the field, we make the usual assumptions that there is only a single source of error and the error is not transient. Both of these assumptions are important in the reasoning that follows; we comment further on them below.

or one of the two inputs did not have the expected values (and the problem lies further back). Consideration of the first possibility immediately generates hypothesis #1: adder-1 is broken.

To pursue the second possibility, we assume that the second input to adder-1 is good. In that case the first input must have been a 4 (reasoning from the result at F, valid behavior of the adder, and one of the inputs), but we expected a 6. Hence we now have a discrepancy at the input to adder-1; we have succeeded in pushing the discrepancy one step further back along the dependency chain. The expected value there was based on the behavior rule for the multiplier and the expected value of its inputs. Since the inputs to the multiplier are primitive (supplied by the user), the only alternative along this line of reasoning is that the multiplier is broken. Hence hypothesis #2 is that adder-1 is good and multiplier-1 is faulty.

Pursuing the third possibility: if the first input to adder-1 is good, then the second input must have been a 4 (suggesting that the second multiplier might be bad). But if that were a 4, then the expected value at G would be 10 (reasoning forward through the second adder). We can check this and discover in this case that the output at G is 12. Hence the value on the output of the second multiplier can't be 4, it must be 6, so the second multiplier can't be causing the current problem.

This style of reasoning can be described as the *interaction of simulation and inference*: simulation generates expectations about correct outputs based on inputs and knowing how devices work (simulation rules); inference generates conclusions about actual behavior based on observed outputs and device inference rules. The comparison of these two, in particular differences between them, provides a foundation for troubleshooting.<sup>7</sup>

## 6.1 Constraint Suspension

In the discussion above, we glossed over the question of determining when a candidate is valid (as ADDER-1 was) and when it is inconsistent with all the available evidence (as MULT-2 was). One of the novel contributions of this work is the development of the constraint suspension technique as a way of providing an answer to this question.

To see how it works, consider once again the first step of the problem. When we examine the dependency record at F, we find that the value there resulted from the behavior rule for ADDER-1 and the values coming from MULT-1 and MULT-2. As above, the first possibility is that ADDER-1 is broken.

But this is a *local inference* (i.e., it is based only on the dependency record at F) and we have to be sure it's *globally consistent* with all the symptom data. More precisely, we want to ask whether there is *some* assignment of values to the ports of the adder that is consistent with all of the inputs and observed outputs. Is there any way in which ADDER-1 alone could be broken and produce the symptoms noted?

We can do this conveniently by using the "constraint-like" character of our representation and the notion of *constraint suspension*. While the simulation and inference rules are usually kept distinct, for the moment we use the whole collection of them together, in effect a network of constraints that can indicate whether we have a consistent set of assignments to the inputs and outputs. If, for example, we were to try to assign to the network the inputs and *observed* outputs of Fig. 7, it would report a contradiction: there is no way for all the rules to be active (i.e., all the components working as expected) and for those inputs to have produced the observed outputs.

Normally contradictions in constraint networks are handled by retracting one of the values inserted into the network. But here we are sure of the values (the inputs we sent in to the circuit and the outputs we measured); what we are unsure of is the constraints (component behaviors). We

<sup>7.</sup> The guided probe technique, in common use in industry, is based on a set of ideas that is closely related, though not identical. We discuss the differences in Section 13.

therefore take a dual view, and rather than looking for a value we can retract, we look for a *constraint* whose retraction will leave the network in a consistent state. This is the basic idea behind constraint suspension.

To check the global consistency of ADDER-1, for example, we *suspend* (disable) all the rules in ADDER-1, assign the input values to input ports A through E, and assign the *observed* values to output ports F and G. We then allow the whole collection of rules to run to quiescence, determining for us whether there is *some* set of values on the ports of ADDER-1 consistent with the inputs and observed outputs.

If the network does reach a consistent state, we know that the candidate can account for the symptoms. In addition, we can examine the resulting state to see what values the candidate must have at its ports. In the case of ADDER-1, for example, the network indicates that the inputs must be 6 and 6, and the output 10. Thus in the process of determining the global consistency of a candidate, constraint suspension also produces symptom information about the misbehavior.

If the network reports an intractable contradiction, there is no assignment of values to the component that is consistent with all the symptoms, and hence no way for that component to account for the observed malfunction. For example, when we disable the rules of MULT-2 and insert the inputs and observed outputs, an inescapable contradiction results. This demonstrates that MULT-2 cannot account for all the observed values.

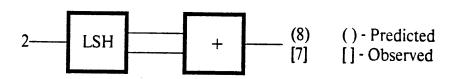

Fig. 8 provides a complete description of the candidate generation process in a code-like notation (the procedure has been made easier to follow by ignoring the simulation/inference distinction for the moment and assuming we have a traditional constraint network). Candidate generation occurs in three basic steps: simulate the circuit and collect discrepancies, determine potential candidates using the dependency records; and finally, for each potential candidate determine global consistency and symptom values by using constraint suspension.

## CANDIDATE GENERATION PROCEDURE

## STEP 1: COLLECT DISCREPANCIES

- 1.1 Insert device inputs into the constraint network inputs : eg. insert 3, 2, 2, 3, and 3 at primary inputs A through E

- ; simulation predicts values at F and G

- 1.2 Compare predicted outputs with observed and collect discrepancies ; e.g., prediction and observation differ at F.

## STEP 2: DETERMINE POTENTIAL CANDIDATES VIA DEPENDENCY RECORDS

- 2.1 For each discrepancy found in Step 1:

- follow the dependency chain back from the predicted value to find all components that contributed to that prediction

- ; these are all the components "upstream" of the discrepancy

- ; e.g., if we follow the dependency chain back from the 12

- ; at F, we find ADDER-1, MULT-1, and MULT-2

- 2.2 Take the intersection of all the sets found by Step 2.1

- ; this yields the components common to all discrepancies (and

- ; hence potentially able to account for all discrepancies)

- ; (in the example above there is only one discrepancy)

## STEP 3: DETERMINE CANDIDATE CONSISTENCY VIA CONSTRAINT SUSPENSION

- 3.1 For each component found in Step 2.2:

- 3.1.1 Turn off (suspend) the constraint modeling its behavior

- 3.1.2 Insert observed values at outputs of constraint network : (inputs were inserted earlier at Step 1.1)

- 3.1.3 If the network reaches a consistent state

- -- the component is a globally consistent candidate

- -- its symptoms can be found at its ports

- -- add the candidate and its symptoms to the candidate list ; e.g., ADDER-1 and its values of 6, 6, and 10

otherwise

the candidate is not globally consistent, ignore it ; e.g., MULT-2

- 3.1.4 Retract the values at constraint network outputs

- 3.1.5 Turn on the constraint turned off in Step 3.1.1

- ; (these last two just get ready for the next iteration of 3.1)

Figure 8 - Candidate generation via constraint suspension (assuming single point of failure)

As we explore further below, there are a number of important assumptions underlying this reasoning. But constraint suspension provides a mechanism that is both very useful and characteristic of a basic theme underlying this work: the careful management of assumptions. The traditional approach to diagnosis proceeds by assuming that it knows how the component might be failing: it is displaying one of the known misbehaviors found in the set of fault models. We, on the other hand, proceed by simply suspending all assumptions about how a component might be behaving. We then allow the symptoms to tell us what the component might be doing. By suspending the constraint in the adder, for example, we are in effect withdrawing all preconceptions about how that component is behaving. We then let the symptoms and the rest of the network tell us whether there is any behavior at all that is consistent with all our observations.

## 6.2 Advantages of Discrepancy Detection and Constraint Suspension

The combination of discrepancy detection and constraint suspension provides a very useful mechanism with a number of advantages:

- † It is fundamentally a *diagnostic* technique, since it allows systematic isolation of the possibly faulty devices, and does so without having to precompute fault dictionaries, diagnosis trees, or the like.

- † It reasons from the structure and behavior of the device: the candidate generation process works from the schematic itself to determine which components might be to blame.

- † Since it defines failure behaviorally, i.e., as anything that doesn't match the expected behavior, it can deal with a wide range of faults, including any systematic misbehavior. This is more widely applicable than a fixed set of models like stuck-ats.

- † As we saw above, the technique yields symptom information about the malfunction: if ADDER-1 is indeed the culprit, then we know a little about how it is misbehaving. As will become clear, this information turns out to be useful in several ways.

- † The approach allows natural use of hierarchical descriptions, a marked advantage for dealing with complex structures.

In the example above, for instance, we determined the relevant candidates at the current, fairly high level of description, never having to deal with lower level descriptions (e.g., gate-level devices). We could now continue the process "inside" either candidate, using the next level of description in exactly the same fashion, to determine what subcomponents might be responsible.

† Continuing the process at the next level might indicate that no subcomponent could be responsible, ruling out that candidate.

We might, for example, find that, given how the adder is implemented, there may no subcomponent of it that can logically account for the "6 plus 6 equals 10" symptom that the adder would have to be displaying. Thus the same candidate generation machinery will either provide a set of candidate subcomponents at the next level, or indicate that none can account for the inferred misbehavior, exonerating this candidate.

† This approach keeps knowledge about logical plausibility distinct from knowledge about physical plausibility. This helps simplify construction of the system.

Constraint suspension answers the question of logical plausibility of a candidate: it determines whether there is *any* set of values the component might display that could account for all the symptoms. The technique (by design) knows nothing about whether that set of values is in fact physically plausible.

Our candidate generation machinery would, for example, consider a forked wire to be a plausible candidate if it inferred that the values at its three ports were 1 at the "input" (the point where some device is driving the wire), and 0 and 1 at the two "outputs" (where the wire in turn drives two other devices). Viewed at the black box level, the wire is a three port device that could well display the symptoms noted. To know that this is implausible requires understanding the physics of a specific technology: a wire will display different values at its ends as a result of breaks, but a broken wire in TTL will manifest as a high. Hence the pattern of values given can be ruled out by using knowledge of the particular technology.

The candidate generator thus provides a list of logically plausible components;

further pruning of this list can then be done by invoking a distinct body of technology specific knowledge. Keeping the two distinct simplifies the construction of both.

† The technique extends in straightforward fashion across multiple tests.

Each test of the overall device provides one set of symptoms specifying the misbehavior of a candidate component. The test in Fig. 7, for instance, gives us one I/O pair for ADDER-1 and one for MULT-1; subsequent tests can provide additional I/O pairs. Two kinds of knowledge then relate results across tests.

The non-intermittency assumption indicates that if a component is misbehaving, that misbehavior is at least consistent and reproducible. Hence if a candidate has identical inputs in a later test, it must have an identical output. If, for example, a later test were to indicate that ADDER-1 was a candidate with inputs 6 and 6, and an output of 13, those two test results (and the non-intermittency assumption) exonerate ADDER-1.

The second source of knowledge comes from additional information concerning faults physically plausible within a specific technology. Consider a situation in which Test 1 indicates that a particular wire is a candidate because it is getting a 0 but propagating a 1, while Test 2 indicates the wire is a candidate because it is getting a 1 but propagating a 0. Considered simply as a two port device, this is logically consistent and the candidate generator will report it as such. But knowledge about TTL circuits tells us that there is no physically plausible fault which will cause a wire to start behaving as an inverter, hence the wire can be exonerated.

† This approach makes the <N>-point-of-failure assumption both explicit and easily modified.

In Fig. 8 above the single point of failure assumption appears in two places: at Step 2.2 where we intersected the sets, and at Step 3.1 where we disable the rules for exactly one component when checking candidate consistency. To deal with any specific N > 1, the simplest change is to take the *union* at Step 2.2 and take pairs, triples, etc., at Step 3.1.

While this does not in any sense solve the problem of multiple points of failure, it does demonstrate two important points. First, it shows that, unlike many approaches, our constraint suspension technique is not limited to dealing with a single point of failure. Second, it does provide some aid in grappling with multiple failures, since we can methodically try possible single failures, then pairs, triples, etc.<sup>8</sup>

Unfortunately, as we demonstrate, the power of all of this mechanism is only part of the story.

#### 6.3 Subtleties in Candidate Generation

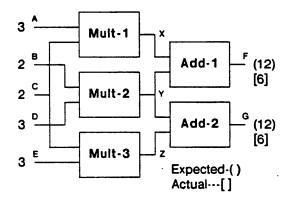

Consider the slightly revised example shown in Fig. 9. Reasoning as before, we would discover in this case that there is only one hypothesis consistent with the values measured at F and G: the second multiplier is malfunctioning, outputting a 0.

<sup>8.</sup> While checking pairs, etc. using constraint suspension (Step 3.1.3) is computationally simple, generation of appropriate pairs, triples, etc., (Step 3.1) is still an exponential process. This has not yet proved to be untenable, since both the number of faults considered and the number of components at any given level of description are relatively small. We are nevertheless exploring ways of improving the process. For example, some simple bookkeeping tricks can be used to rule out some of the pairs, triples, etc., very quickly.

Figure 9 - Troublesome troubleshooting example.

Yet there is another quite reasonable hypothesis: the third multiplier might be bad (or the first).

But how could this produce errors at both F and G? The key lies in being wary of our models. The thought that digital devices have input and output ports is a convenient abstraction, not an electrical reality. If, as sometimes happens (due to a bent pin, bad socket, etc.), a chip fails to get power, its inputs are no longer guaranteed to act unidirectionally as inputs. If the third multiplier were a chip that failed to get power, it might not only send out a 0 along wire z, but it might also pull down wire C to 0. Hence the symptoms result from a single point of failure (MULT-3), but the error propagates along an "input" line common to two devices.

The most immediate problem lies in our implicit acceptance of unidirectional ports and the reflection of that acceptance in the basic dependency tracing machinery. We implicitly assumed that wires get information only from output ports --- when checking the inputs to MULT-1, we assumed that the inputs are "primitive". We looked only at terminals A and C, never at the other end of the wire at MULT-3.

Bridges are a second common fault that illustrates another place where we need to be careful: the reasoning style used above can *never* hypothesize a bridging fault, again because of implicit assumptions and their subtle reflection in the reasoning. Bridges can be viewed as wires that don't show up in the design. But we traditionally make an implicit closed world assumption: the structure description is assumed to be complete and anything not shown there "doesn't exist". Clearly this is not always true. Bridges are only one manifestation: wiring errors during assembly are another possibility.

Let's review for a moment. The traditional test generation technology suffered from a number of problems: among others, it is a technology for test generation, not diagnosis, and it uses a limited fault model. The use of discrepancy detection and constraint suspension improves on this substantially by providing a diagnostic ability, by defining a fault as anything that produces behavior different from that expected, and by working directly from descriptions of structure and behavior. This seems to be perfectly general, but, as we illustrated, it has to be used with care.

Put simply, the virtue of the technique is that it reasons from the schematic; the serious flaw in the technique is that it reasons from the schematic and the schematic might be wrong.

We believe it is instructive to examine the basic source and nature of this problem.

#### 7. MECHANISM AND KNOWLEDGE

In the example above we encountered some interesting situations because we failed to make explicit a number of important assumptions underlying the reasoning. In the power failure example, we were assuming implicitly that there was only one possible direction of causality at an input port, and thus never examined the other end of wire C. Similarly, tracing back through the circuit from input X of ADDER-1, we looked only at MULT-1, because that was the only apparent connection at that point. We never looked at, say MULT-3, because there was no wire leading there, hence no reason to believe one might affect the other.

Note carefully the character of these assumptions: they concern the existence of causal pathways, the applicability of a particular model of interaction. In the power failure example we assumed implicitly that there was no way for MULT-3 to affect MULT-1 through wire C, yet such a path is possible. As we noted above in discussing the possibility of a bridge fault, there seemed to be no path in the schematic that would allow MULT-3 to affect ADDER-1, yet a pathway is in fact possible.

The problem is not in the existence of such assumptions --- they are in fact crucial to the reasoning process. The problem lies instead in the careful and explicit management of them. To see the necessity of having assumptions about causal pathways, consider the nature of the candidate generation task. Given a problem noticed at some point in the device, candidate generation attempts to determine which modules could have caused the problem. To answer the question we must know by what mechanisms and pathways modules can interact. Without *some* notion of how modules can affect one another, we can make no choice, we have no basis for selecting any one module over another.

In this domain the obvious answer is "wires": modules interact because they're explicitly wired together. But that's not the only possibility. As we saw, bridges are one exception; they are "wires" that aren't supposed to be there. But we also might consider thermal interactions, capacitive coupling, transmission line effects, etc.

Generating candidates, then, should not be thought of in terms of tracing wires (or dependency records). Rather, we claim, it should be thought of in terms of tracing paths of causality. Wires are only the most obvious pathway. In fact, given the wide variety of faults we want to deal with, we need to consider many different pathways of interaction.

And that leaves us on the horns of a classic dilemma. If we include every interaction path, candidate generation becomes *indiscriminate* — there will be some (possibly convoluted) pathway by which every module could conceivably be to blame. Yet if we omit any pathway, there will be whole classes of faults we will *never* be able to diagnose.

What can we do? We believe that two steps are important. First, we have to recognize that our inference mechanisms --- in this case dependency detection and constraint suspension --- are not the source of problem-solving power. The power is instead in the knowledge that we supply those techniques, i.e., the pathways of interaction.

And therein lies the second step: there is an important task in enumerating and organizing the pathways of interaction to be considered. How can we do this? We believe that human performance supplies a useful clue.

## 8. ORGANIZING THE PATHWAYS OF INTERACTION

We appear to be faced with an unavoidable dilemma, caught between the desire to be complete and the need to constrain the possibilities we consider. But people face exactly the same dilemma and seem to handle it. What do they do?

The answer seems be an instantiation of Occam's razor: an experienced engineer knows that some things are more likely to go wrong than others. He will, as a result, attempt to generate solutions that employ simpler and more likely hypotheses first, falling back on more elaborate possibilities only in face of an intractable contradiction (i.e., given the current set of assumptions, there is no way to account for the observed misbehavior). There are three important points here.

The engineer has a notion of "the kinds of things that can go wrong".

There is an ordering criterion that indicates which category of hypotheses to entertain first.

The categories are ordered but none is permanently excluded.

To capture this same sort of behavior in our program we need to (i) make precise the notion of "what can go wrong", and (ii) determine what constitutes a "simple" explanation. We consider both of these briefly here, as background for the example that follows, then address the issue in detail in Section 10.

To address the first of these, we need some methodical way to define and generate the possible kinds of failures. This is accomplished by enumerating the assumptions built into our "module and information path" representation and then characterizing the variety of failure that results from violating each assumption. We refer to the resulting list as the *categories of failure*.

One such category is illustrated by the problem presented in Fig. 9. The implicit assumption there was that information flows in only one direction at an input (or output) port. If this assumption is violated, we get a category of failure we term an "unexpected direction" failure. The other categories generated in this way are described in Section 10.

Given such a notion of "what can go wrong", we now need an appropriate metric for ordering the list. This is currently accomplished by relying on the experience of expert troubleshooters, who tell us which categories of failure are encountered more frequently than others. Stuck-ats are more likely than assembly errors, for example. While the ordering criterion may eventually need be more elaborate, its precise content is less an issue here than its character: it is a summary of empirical experience that helps us to order the kinds of hypotheses we consider. For our current domain, this approach produces the following list:

localized failure of function (e.g., stuck-at on a wire, failure of a RAM cell) bridges unexpected direction (e.g., the power failure problem) multiple point of failure assembly error design error

We start by attempting to generate candidates in the localized failure category, assuming that the structure is as shown in the schematic, that there was only a single point of error, that information flowed only in the predicted directions, etc. Only if this leads to a contradiction are we willing to surrender an assumption (e.g., that the schematic was correct) and entertain the notion that a bridge might be at fault. If this too leads us down a blind alley then we would surrender additional assumptions and consider ever more elaborate hypotheses, eventually entertaining the possibility of multiple errors, an assembly error (every individual component works but they have been wired up incorrectly) and even design errors (the implementation is correct but cannot produce the desired behavior).

This mimics what we believe a good engineer will do: make all the assumptions necessary to simplify a problem and make it tractable, but be prepared to discover that some of those simplifications were incorrect. In that case, surrender some of those assumptions and be willing to consider additional kinds of failure.

In terms of the dilemma noted above, the categories of failure serve as a set of

filters. They restrict the paths of interaction we are willing to consider, thereby preventing candidate generation from becoming indiscriminate. In using the localized failure of function category, for example, we are assuming for the moment that the structure is as shown in the schematic, hence there are no additional paths of interaction (and thus no bridges). But these are filters that we have carefully ordered and consciously put in place. If we cannot account for the observed symptoms with the current set of filters in place, we remove one, leaving us with a set that is less restrictive, allowing us to consider additional interaction paths and hence more elaborate hypotheses.

There are of course no guarantees that this will lead us to the correct category of failure without any false steps. It is possible that all the evidence at a given point is consistent with, say, a localized failure of function in a single component, yet replacing that component may make it clear that the fault is elsewhere. As always with Occam's razor, our only assurance is that we are generating a hypothesis that is by some measure the simplest and most likely, and that's the best we can do. We may subsequently discover that the problem is in fact more complex. By making the ordering criteria explicit and accessible, we have at least provided a place for embedding knowledge that can make the choice of hypothesis category as informed as possible at each step.

#### 9. EXAMPLE: A BRIDGE FAULT

As we have noted, traditional automated reasoning about circuits works from a predefined list of fault models and uses the mathematical style of analysis exemplified by boolean algebra or the D algorithm. As a result, it is strongly oriented toward faults that can be modeled as a permanent binary value. One problem with this is its inability to provide useful results concerning bridge faults.

In this section we show how our system works when faced with a bridge fault, illustrating a number of the ideas described above. While the example has been simplified for presentation, there is still unfortunately a fair amount of detail necessary. A summary of the basic steps will help make clear how the problem is solved.

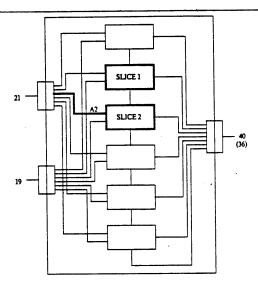

The device is a 6-bit carry-chain adder (Fig. 10). The problem begins when we notice that the attempt to add 21 and 19 produces an incorrect result.

The candidate generation process outlined above generates a set S1 of three candidates, any of whose malfunction can explain this result.

A new set of inputs (1 and 19) is chosen in an attempt to discriminate among the three possibilities. The adder's output is incorrect for this set of inputs also. The candidate generator indicates that there are two candidates capable of explaining this new result.

Neither of these two candidates are found in S1. Thus we reach a contradiction: no one component is capable of explaining the data from both sets of inputs.

Put slightly differently, we have a contradiction under the current set of assumptions and interaction models. We therefore have to surrender one of our assumptions and use a different interaction model.

The next model --- bridge faults --- surrenders the assumption that the structure is as shown in the schematic and considers one class of modifications to the structure: the addition of one wire between physically adjacent pins.

The combination of functional information (the expected pattern of values produced by the fault) and physical adjacency provides a strong constraint on the set of connections which might be plausible bridges.

The first application of this idea produces two hypotheses that are functionally plausible, but both are ruled out on physical grounds.

Dropping down a level of detail in our description reveals additional bridge candidates, two of which prove to be both physically and functionally plausible. One of these proves to be the actual error.

A key point is the utility of ordering the paths of interaction to be considered. Starting with a very restricted category of failure, we discover that it leads us to a contradiction. We surrender an assumption, consider an additional category and hence an additional pathway of interaction: bridge faults. We show how knowledge of both structural and functional organization allows us to generate a select few bridge fault hypotheses, eventually discovering the underlying fault.

9.1 The Example

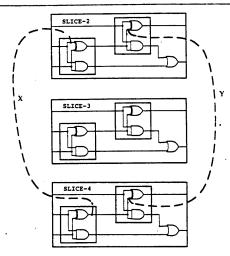

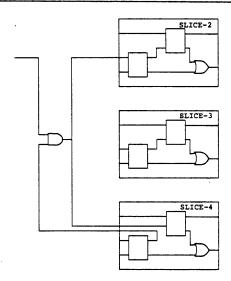

Consider the six bit adder shown in Fig. 10 and imagine that the attempt to add 21 and 19 produces 36 rather than the expected value of 40. Invoking the candidate generation process described above, we would find that there are three devices (SLICE-1, A2 and SLICE-2), any one of whose malfunction can explain the misbehavior.<sup>9</sup>

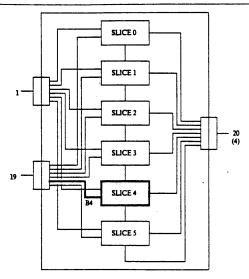

Figure 10 - Six bit adder constructed from single bit slices. Heavy lines indicate components implicated as possibly faulty.

A good strategy when faced with several candidates is to devise a test that can cut the space of possibilities in half. In this case changing the first input (21) to 1 will be informative: if the output of SLICE-2 does not change (to a 0) when we add 1 and 19, then the error must be in either A2 or SLICE-2.10

As it turns out, the result of adding 1 and 19 is 4 rather than 20. Since the output of SLICE-2 has not changed, it appears that the error must be in either A2 or SLICE-2.

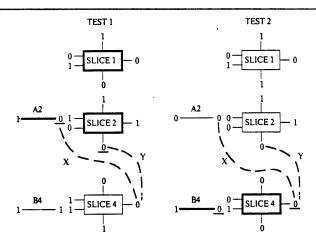

But if we invoke the candidate generator, we discover an oddity: the only way to account for the behavior in which adding 1 and 19 produces a 4 is if one of the two candidates highlighted in Fig. 11 (B4 and SLICE-4) is at fault.

<sup>9.</sup> The example has been simplified slightly for presentation.

<sup>10.</sup> This and subsequent test generation is currently done by hand. Work on automating test generation is in progress [27].

The reasoning behind this test relies on the single fault assumption: if the malfunctioning component really were SLICE-1, both A2 and SLICE-2 would be fault-free. Hence the output of SLICE-2 would have to change when we changed one of its inputs. (Notice, however, if the output actually does change, we don't have any clear indication about the error location: SLICE-2, for example, might still be faulty.)

Figure 11 - Components indicated as possibly faulty by the second test.

Therein lies our contradiction. The only candidates that account for the behavior of the first test are those in Fig. 10, the only candidates that account for the second test are those in Fig. 11. There is no overlap, so there is no single candidate that accounts for all the observed behavior.

Our current category --- the localized failure of function --- has thus led us to a contradiction. We therefore surrender it and consider the next, less restrictive category, one that allows us to consider an additional kind of interaction path --- bridging faults. The problem now is to see if there is some way to unify the test results, some way to generate a single bridge fault candidate that accounts for all the observations.

Much of the difficulty in dealing with bridging faults arises because they violate the rather basic assumption that the structure of the device is in fact as shown in the schematic. But admitting that the structure may not be as pictured says only that we know what the structure isn't. Saying that we may have a bridge fault narrows it to a particular class of modifications to consider, but the real problem here remains one of making a few plausible conjectures about modifications to the structure. Between which two points can we insert a wire and produce the behavior observed?

To understand how we answer that question, consider what we have and what we need. We have test results, i.e., observations of *behavior*, and we want conjectures about modification to *structure*. The link from behavior to structure is provided by knowledge of electronics: in TTL, a bridge fault acts like an and-gate, with ground dominating.<sup>12</sup>

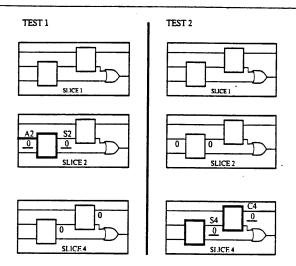

From this fact we can derive a simple pattern of behavior indicative of bridges. Consider the simple example of Fig. 12 and assume that we ran two tests. Test 1 produced one candidate, module A, which should have produced a 1 but yielded a 0 (the zero is underlined to show that it is an incorrect output). Module B was working correctly and produced a 0 as expected. In Test 2 this situation is exactly reversed, A was performing as expected and B failed.

The pattern displayed in these two tests makes it plausible that there is a bridge

<sup>11.</sup> Note that dropping down another level of detail in the functional description cannot help resolve the contradiction, because our functional description is a tree rather than a graph: in our work to date, at least, no component is used in more than one way. (If the functional description were in fact a graph, we could easily continue down it to see if the two candidate sets did indeed have a subcomponent in common).

<sup>12.</sup> This is an oversimplification, but accurate enough to be useful. In any case, the point here is how the information is used; a more complex model could be substituted and carried through the rest of the problem. Note also that for notational convenience, we assume in the rest of the description that ground is equivalent to a 0.

linking the outputs of A and B: in the first test the output of A was dragged low by B, in the second test the output of B was dragged low by A.

Figure 12 - Pattern of values indicative of a bridge. Heavy lines indicate candidates.