Technical Report 1284

# A Parallel Crossbar Routing Chip for a Shared Memory Multiprocessor

Henry Minsky

MIT Artificial Intelligence Laboratory

### A Parallel Crossbar Routing Chip for a Shared Memory Multiprocessor

by

#### Henry Minsky

B.S., Massachusetts Institute of Technology (1984)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

January 1991

© Massachusetts Institute of Technology 1991

#### Abstract

This thesis describes the design and implementation of an integrated circuit and associated packaging to be used as the building block for the data routing network of a large scale shared memory multiprocessor system.

A general purpose multiprocessor depends on high-bandwidth, low-latency communications between computing elements. This thesis describes the design and construction of RN1, a novel self-routing, enhanced crossbar switch as a CMOS VLSI chip. This chip provides the basic building block for a scalable pipelined routing network with byte-wide data channels. A series of RN1 chips can be cascaded with no additional internal network components to form a multistage fault-tolerant routing switch. The chip is designed to operate at clock frequencies up to 100Mhz using Hewlett-Packard's HP34  $1.2\mu$  process. This aggressive performance goal demands that special attention be paid to optimization of the logic architecture and circuit design.

Thesis Supervisor: Thomas Knight, Jr.

Title: Asst. Professor, Dept. Electrical Engineering and Computer Science

This empty page was substituted for a blank page in the original document.

# Contents

| 1 | Intr | oductio  | on                                       | 11 |

|---|------|----------|------------------------------------------|----|

|   | 1.1  | Buildin  | g a Multi-model Parallel Processor       | 11 |

|   | 1.2  | The Ne   | ed for a Switching Network               | 12 |

|   | 1.3  | Interpre | ocessor Switching Network Design Goals   | 13 |

| 2 | A R  | Review ( | Of Interprocessor Communication Networks | 16 |

|   | 2.1  | The Cr   | ossbar Switch                            | 18 |

|   | 2.2  | A Rout   | ing Switch Made From A Single Crossbar   | 18 |

|   |      | 2.2.1    | Multistage Routing Networks              | 21 |

|   |      | 2.2.2    | Direct vs. Indirect Networks             | 21 |

|   |      | 2.2.3    | Non-Blocking Circuit Switched Networks   | 22 |

|   |      | 2.2.4    | Clos Networks                            | 22 |

|   |      | 2.2.5    | Beneš Networks                           | 24 |

|   |      | 2.2.6    | Packet and Circuit Switched Networks     | 26 |

|   |      | 2.2.7    | Self Routing Networks                    | 27 |

|   | 2.3  | The Tra  | ansit Network                            | 28 |

|   |      | 2.3.1    | The RN1 Chip                             | 30 |

| 3 | The  | RN1 F    | Parallel Crossbar Chip                   | 32 |

|   | 3.1  | Backgro  | ound                                     | 32 |

|   |      | 3.1.1    | The Need For Dilation                    | 34 |

|   |      | 3.1.2    | Connection Protocol                      | 34 |

|   | 3.2  | System   | Design Issues                            | 34 |

|   | 3.3 | Chip '  | To Chip Communication Technology        | 35 |

|---|-----|---------|-----------------------------------------|----|

|   | 3.4 | Packa   | ging                                    | 36 |

| 4 | Rot | uting ( | Chip Communication Protocol             | 39 |

|   | 4.1 | Chip '  | To Chip And End To End Network Protocol | 39 |

|   |     | 4.1.1   | Byte Encoding of Command Words          | 40 |

|   | 4.2 | Gran    | nmar to Describe RN1 Protocol           | 41 |

|   |     | 4.2.1   | Opening A Connection                    | 43 |

|   |     | 4.2.2   | Blocked Connection                      | 43 |

|   |     | 4.2.3   | Checksum                                | 44 |

|   |     | 4.2.4   | Turning A Connection                    | 44 |

|   |     | 4.2.5   | Dropping A Connection                   | 44 |

|   |     | 4.2.6   | Turning A Blocked Connection            | 44 |

|   |     | 4.2.7   | Backward Connection                     | 45 |

|   | 4.3 | Messa   | ge Examples                             | 45 |

|   |     | 4.3.1   | Standard Message                        | 45 |

|   |     | 4.3.2   | Blocked Message                         | 45 |

|   |     | 4.3.3   | Turning A Backward Connection           | 47 |

| 5 | Arc | hitectı | ral Description of the Chip             | 50 |

|   | 5.1 | Overv   | view Of The Internal Chip Architecture  | 50 |

|   | 5.2 | Forwa   | rd Ports                                | 52 |

|   |     | 5.2.1   | Forward Port State Machine              | 53 |

|   |     | 5.2.2   | Early Allocate Datapath                 | 53 |

|   |     | 5.2.3   | Checksum                                | 55 |

|   | 5.3 | Back l  | Port Datapath                           | 56 |

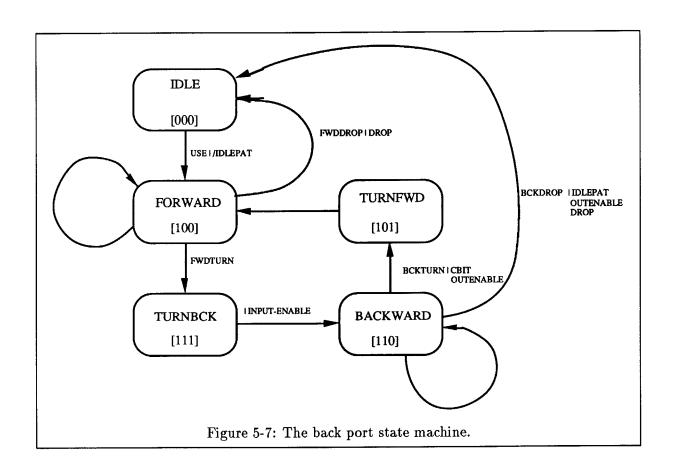

|   |     | 5.3.1   | Back Port State Machine                 | 58 |

|   | 5.4 | Crossp  | point Array                             | 61 |

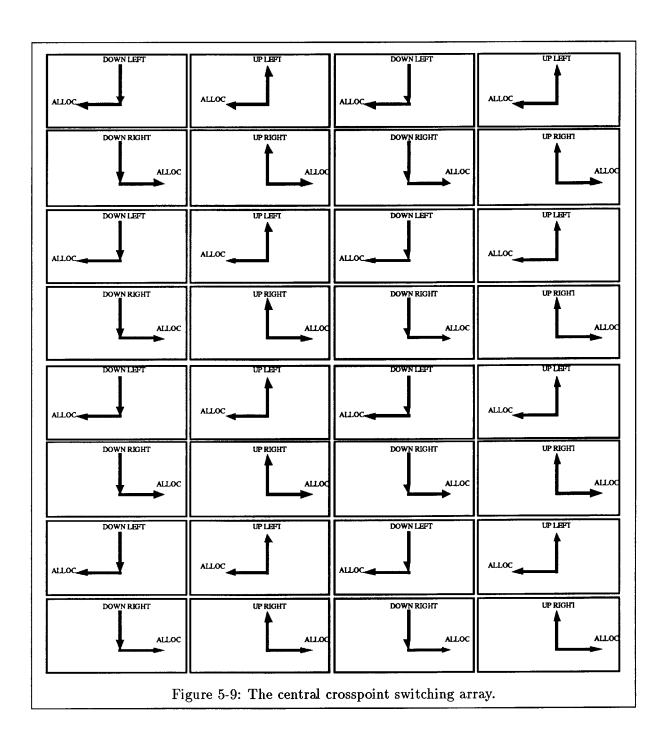

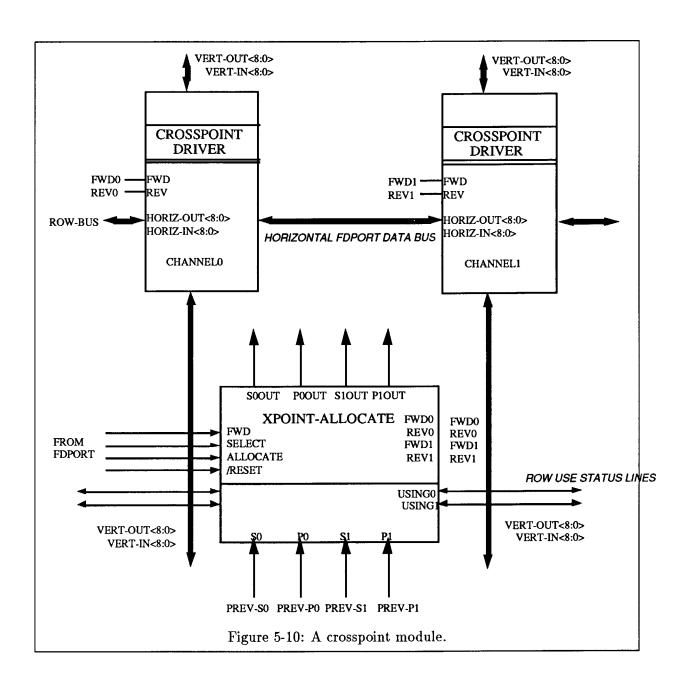

|   |     | 5.4.1   | Crosspoints                             | 61 |

|   |     | 5.4.2   | P And S Control Signals                 | 65 |

|   |     | 5.4.3   | Independent 4x4 Routing Mode            | 67 |

|   |      | 5.4.4 Allocate Logic In A Crosspoint                       | 69        |

|---|------|------------------------------------------------------------|-----------|

|   |      | 5.4.5 Dual vs. Independent Allocation                      | 70        |

|   |      | 5.4.6 Precharged Bus Lines Enhanced With Positive Feedback | 71        |

|   |      | 5.4.7 USE Line Logic                                       | 73        |

|   | 5.5  | Clock Generator                                            | 74        |

|   | 5.6  | Pad Drivers                                                | 76        |

|   | 5.7  | Clock Timing And Data Transfer                             | 76        |

| 6 | Hig  | Performance Circuits: Design And Testing                   | 79        |

|   |      | 6.0.1 Manchester Style Grant Propagate                     | <b>30</b> |

|   |      | 6.0.2 USE Lines                                            | 31        |

|   |      | 6.0.3 Setup on Phi1                                        | 31        |

|   |      | 6.0.4 RESET Logic                                          | 32        |

|   |      | 6.0.5 Clock Distribution                                   | 32        |

|   | 6.1  | Architectural Verification and Testing                     | 32        |

|   | 6.2  | Architectural Level Simulator                              | 32        |

|   |      | 5.2.1 Logic Design and Simulation                          | 33        |

|   | 6.3  | Testing                                                    | 34        |

| 7 | Chi  | Performance, Bugs, and Future Improvements                 | 88        |

|   | 7.1  | Functional Tests                                           | 38        |

|   | 7.2  | Performance                                                | 39        |

|   | 7.3  | Conclusions                                                | )3        |

|   |      | 7.3.1 Simulation: Models vs. Reality                       | )3        |

|   |      | 7.3.2 Test Vectors                                         | )3        |

|   | 7.4  | Future Improvements                                        | )4        |

|   | 7.5  | Possible Architectural Extensions                          | )5        |

| A | Che  | ksum Generator 9                                           | 9         |

| В | Stat | Machine Code 10                                            | 2         |

|   | R 1  | Parward Part State Machine                                 |           |

|            |     |              |      |    |            |             |     |   |      |    |       |    |     |     |   |     |     |     |   |                  |    | Ž.          |     |             | tion to<br>Marie | Á.   |     |   | ; |

|------------|-----|--------------|------|----|------------|-------------|-----|---|------|----|-------|----|-----|-----|---|-----|-----|-----|---|------------------|----|-------------|-----|-------------|------------------|------|-----|---|---|

|            |     |              |      |    |            |             |     |   |      |    |       |    |     |     |   |     |     |     |   |                  |    |             | 1 4 |             |                  |      |     | 4 |   |

|            |     | 10 (         |      |    | a. e       | هنت         | Q   |   | . 14 |    | iee   |    |     |     |   |     |     |     |   |                  |    |             |     |             |                  |      |     |   |   |

|            |     | <b>33</b> 34 | •    |    | <b>.</b> . | <b>44</b> 1 | 91  |   |      |    |       | •  | . • | • • | * | • • | •   | • • | • | • •              |    | <b>6</b> 11 | •   | •           | •                | • •  | • • |   |   |

|            |     |              |      |    |            |             |     |   |      |    | fi.   |    |     |     |   |     |     |     |   |                  |    | T           |     |             |                  |      |     |   |   |

| •          | 3   | RI           | VI   | R  | wi         | <b>l</b> ot | 1   | 0 | 9(   | )  |       |    |     |     |   | - 1 |     |     |   | ri A<br>Militari |    |             |     | <b>9</b> -3 |                  |      |     |   |   |

| \$.<br>\$. |     |              |      |    |            |             | - 7 |   |      |    |       | ė. |     |     |   |     |     |     |   |                  |    | 100         |     |             |                  |      |     | ķ |   |

| 1          |     |              |      |    | . A        |             |     |   |      | ų, |       |    |     |     |   |     |     | 1   |   | 4                |    | 3           |     |             |                  |      |     |   |   |

| 1          | •   | To           | et ' | Vo | cto        | 78          |     |   |      |    |       |    |     |     |   |     |     |     |   |                  | 25 | 1           |     |             |                  |      |     |   |   |

|            |     |              |      |    | 413/       |             |     |   |      |    | ٠     |    |     |     |   |     | Hy. |     |   |                  |    |             |     |             |                  |      | 4.7 |   |   |

| 1          | 2.5 |              |      |    |            |             |     |   |      |    | 1. 3. |    |     |     |   |     |     |     |   | 2 5              |    | 1           |     |             |                  | 8.80 | 15  |   |   |

# List of Figures

| 2-1 | A Transit Machine                                                     | 17 |

|-----|-----------------------------------------------------------------------|----|

| 2-2 | A simple crossbar                                                     | 19 |

| 2-3 | A dilated crossbar                                                    | 20 |

| 2-4 | A simple delta network                                                | 23 |

| 2-5 | A Clos non-blocking network                                           | 24 |

| 2-6 | A Beneš network                                                       | 25 |

| 2-7 | A 16 port Transit Network composed of $4 \times 2$ parallel crossbars | 29 |

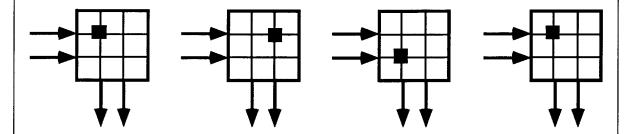

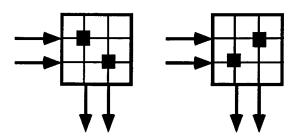

| 3-1 | Routing Modes of RN1                                                  | 33 |

| 3-2 | The RN1 Chip                                                          | 37 |

| 3-3 | Three Dimensional Wiring                                              | 38 |

| 4-1 | RN1 Message Sequence                                                  | 42 |

| 4-2 | Sample Message: Opening A Connection                                  | 46 |

| 4-3 | Sample Message: Blocked Connection                                    | 48 |

| 4-4 | Sample Message: Turning A Backward Connection                         | 49 |

| 5-1 | RN1 Internal Block Diagram                                            | 51 |

| 5-2 | Forward Port Block Diagram                                            | 52 |

| 5-3 | Forward Port State Transition Diagram                                 | 54 |

| 5-4 | Simple Allocate Early                                                 | 55 |

| 5-5 | Simple Allocate Early                                                 | 56 |

| 5-6 | BackPort                                                              | 57 |

| 5_7 | Back Port State Machine                                               | 59 |

| 5-8  | Back Port Turn Detector                        | 60 |

|------|------------------------------------------------|----|

| 5-9  | Crosspoint Array                               | 62 |

| 5-10 | Crosspoint Module                              | 63 |

| 5-11 | Crosspoint Column                              | 64 |

| 5-12 | Line Control Module                            | 66 |

| 5-13 | Grant Chain Logic                              | 68 |

| 5-14 | Allocate Cycle                                 | 68 |

| 5-15 | Allocate Logic                                 | 70 |

| 5-16 | Select Logic                                   | 71 |

| 5-17 | Carry Unit Logic                               | 72 |

| 5-18 | Use Line Logic                                 | 74 |

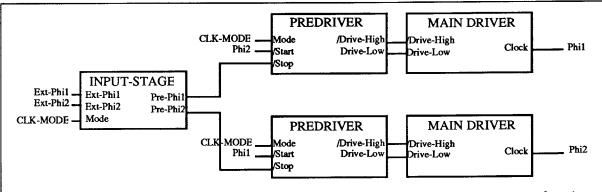

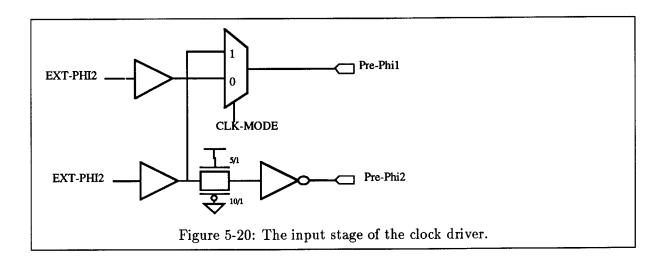

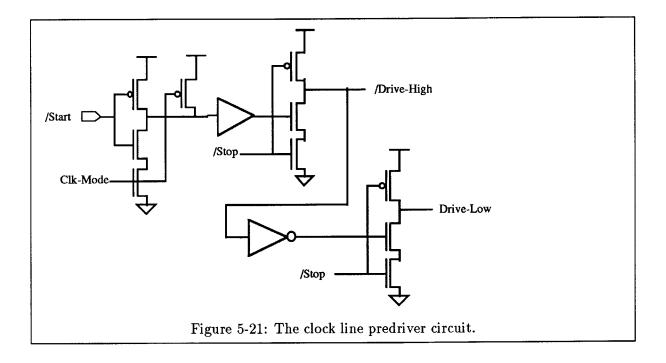

| 5-19 | Clock Generator                                | 74 |

| 5-20 | Clock Generator                                | 75 |

| 5-21 | Clock Generator                                | 75 |

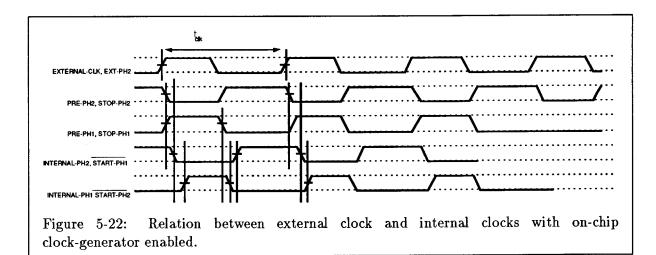

| 5-22 | External Clock Timing                          | 77 |

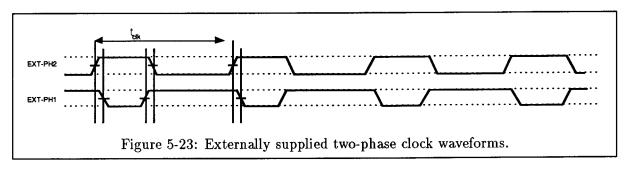

| 5-23 | Two Phase Clock Waveforms                      | 77 |

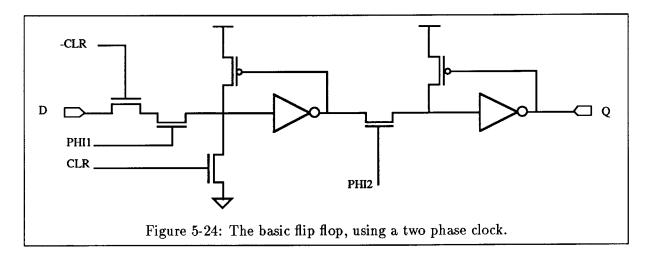

| 5-24 | Basic Two Phase Flip Flop                      | 78 |

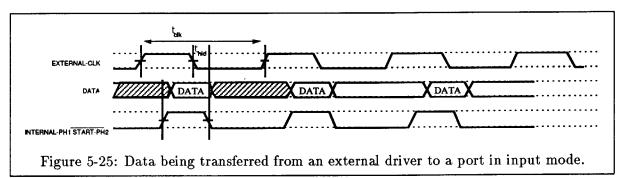

| 5-25 | Data Transfer Timing Diagram                   | 78 |

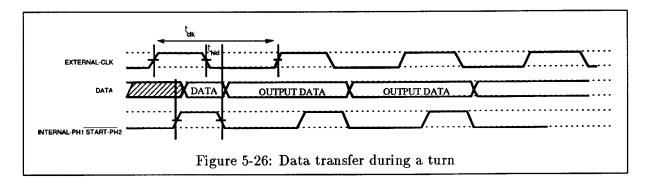

| 5-26 | Data Transfer Timing Diagram                   | 78 |

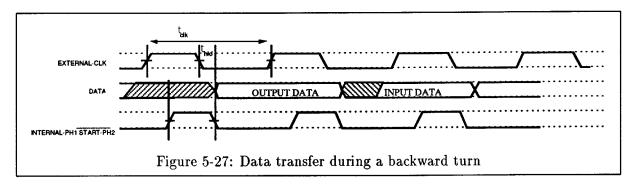

| 5-27 | Data Transfer Timing Diagram                   | 78 |

| 0.1  |                                                |    |

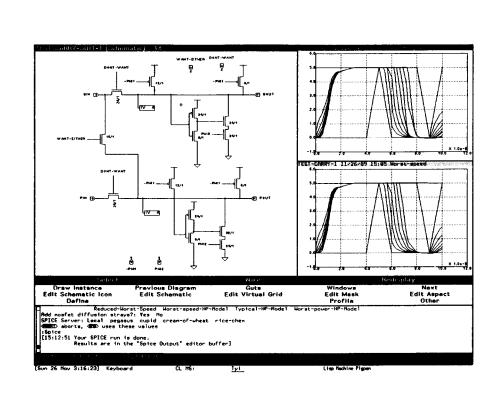

| 6-1  | Crosspoint Low Capacitance Bus Driver          |    |

| 6-2  | Spice Simulation of the dynamic Allocate Logic |    |

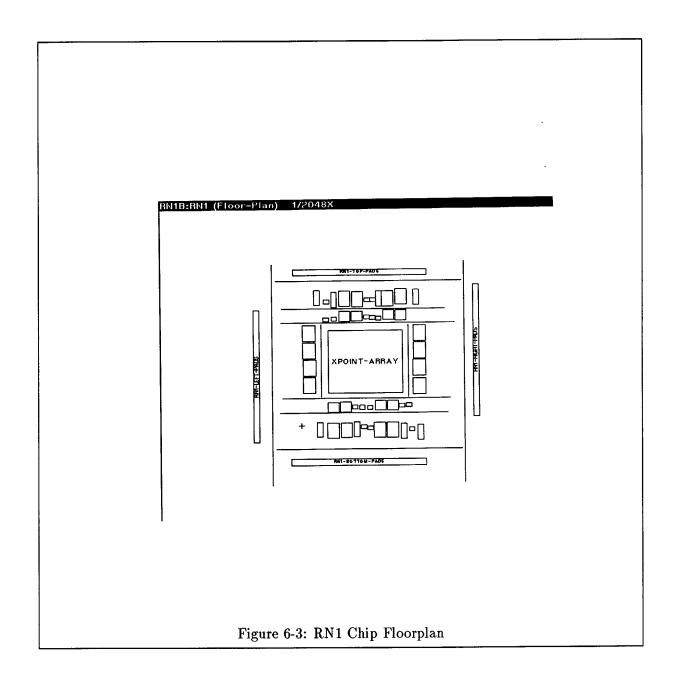

| 6-3  | Chip Floorplan                                 | 86 |

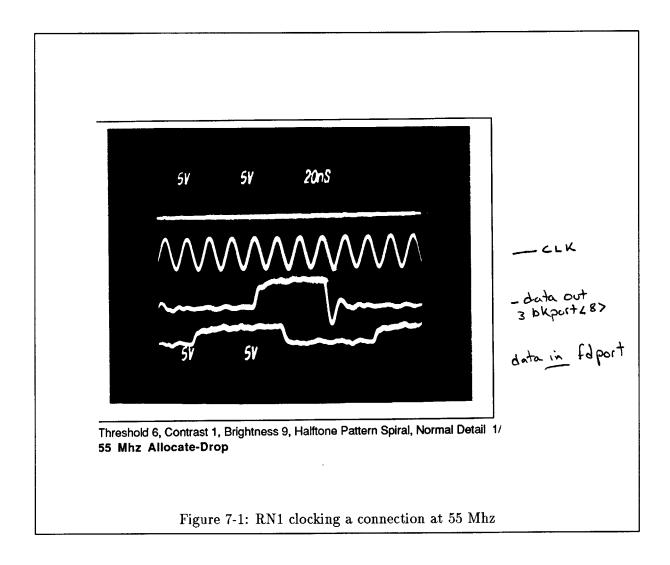

| 7-1  | Scope Trace: RN1 Allocate Timing               | 90 |

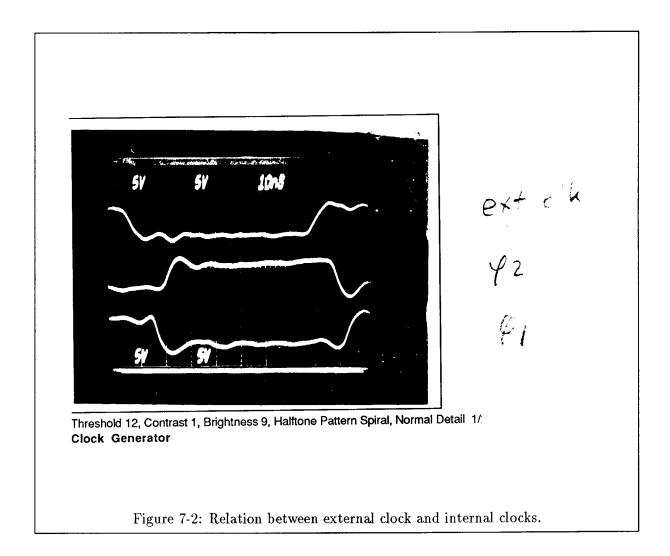

| 7-2  | Scope Trace: Clock Generator                   | 91 |

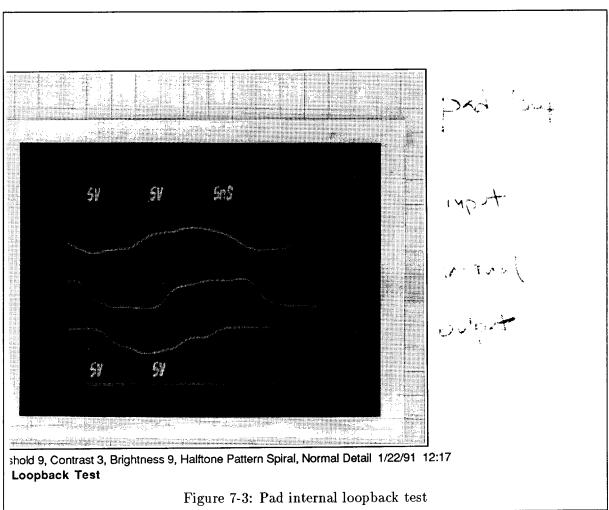

| 7-3  | Scope Trace: Pad Internal Loopback             | 92 |

|      |                                                |    |

# List of Tables

| 2.1 | Categories Of Networks and Representative Architectures | 21 |

|-----|---------------------------------------------------------|----|

| 4.1 | Transit Network Basic Primitive Transactions            | 39 |

| 4.2 | Byte Encoding of Command Words Understood By RN1        | 40 |

| 4.3 | Routing Byte Format                                     | 43 |

| 5.1 | Back Ports Logical Routing Direction                    | 65 |

| 5.2 | P0, S0, P1, S1 Encodings For 8x4 mode (SELECT = 1)      | 65 |

| 5.3 | P0, S0, P1, S1 Encodings For 4x4 mode (SELECT = 0)      | 67 |

| 5.4 | Classes of crosspoint grant priorities                  | 69 |

#### Acknowledgements

I would first of all like to thank Tom Knight, my thesis advisor, without whose support and encouragement I would not have been able to get this far. His vision of engineering in general, and large computer systems in particular, created the framework in which this work was done. The deceptive simplicity of the router protocol is a trademark of Prof. Knight's economical design style. I would next like to thank André DeHon, who has been instrumental in the evolution of this design. André collaborated in the crucial early phase of the design, and contributed many important design ideas and improvements. His encouragement was especially valuable during the long hours of optimization, redesign, and verification which this design entailed. Numerous discussions and arguments have greatly contributed to my understanding of computer design. I also thank him for encouraging me to get this thesis done, finally. Fred Drenckhahn contributed his talent and design wizardry (and good cheer) to actually produce all of the crucial packaging and connector technology.

I want to thank the AI Laboratory for existing in its present form, which means thanking many of the cool laboratory directors and professors; Winston, Tomas Lozano Perez, Eric Grimson, Rod Brooks, Marc Raibert, and of course my father Marvin Minsky, for creating the lab and me. The AI Lab is still a place where you can follow your imagination to wherever it leads you. The many 7th floor denizens, including Ian Horswill, Paul Viola, Alan Bawden, Sandy Wells all helped out at various times with good conversations or crucial insights. Most of all, thanks to my wife Milan, who was always there when I needed her.

This research was done at and supported by the Massachusetts Institute of Technology Artificial Intelligence Laboratory. Support for the Artificial Intelligence Laboratory is provided in part by the Advanced Research Projects Agency under the Office of Naval Research contracts ONR N00014-88-K-0825 and N00014-85-K-0124.

# Chapter 1

# Introduction

This thesis describes the design of RN1, a VLSI chip and associated packaging used to construct a multistage interprocessor communication switch called the Transit network. The Transit network is used to provide a data communication substrate on which to build a shared-memory multiprocessor.

This chapter discusses the general goals of the Transit project, and the need for an interprocessor switching network. Chapter 2 provides an overview of the range of switching network design choices. Chapter 3 introduces the RN1 crossbar chip. Chapter 4 discusses the RN1 chip's communication protocols in depth. Chapter 5 details the internal architecture of the chip. Chapter 6 goes into more detail about high-performance VLSI circuit approaches. Finally, Chapter 7 provides an analysis of chip performance, bugs, and future improvements.

#### 1.1 Building a Multi-model Parallel Processor

The goal of the Transit project is to build a family of moderate to large scale general purpose multiprocessor systems. These systems will initially have from 64 to 256 MIMD processors, currently commercial RISC microcontrollers, communicating with each other in a configuration which will appear to the processors as a global shared memory space. In such a machine, interprocessor communication can be viewed as a special case of memory access (or vice-versa).

The architecture of the Transit machine is designed to support multiple models of parallel computation. At its core is a high-bandwidth low-latency interprocessor communication net-

work. This network will allow efficient implementations of a coherent shared-memory model of computation, a message passing model, a dataflow model, systolic arrays, and even an efficient SIMD model. Each of these computational models depends on a different mixture of bandwidth and latency communication between processing elements.

Existing parallel architectures tend to force the users into a specific programming model. The Transit machine is designed to present the programmer with a fast, simple hardware platform with the primitive operations on which to build a parallel computation application. The trend toward RISC processor architectures is instructive. RISC architectures moved many of the monolithic uniprocessor computational primitives (function call, complex addressing-mode memory references, exception handling) from hardware to software, allowing the compiler writers and programmers to utilize the hardware in a more efficient fashion. The higher performance of the RISC systems over CISC is due in part to the decreased cycle time gained by simpler control paths. But gains in software performance of RISC systems are also due to the flexibility gained by freeing the programmer or compiler writer from being locked into a specific high-level hardware-enforced method of serial computation. Similarly, the Transit architecture is designed to allow writers of parallel processing software to program a machine which supports a set of fast, high-bandwidth data communication primitives, without being committed to a single higher-level computational model.

#### 1.2 The Need for a Switching Network

For any system with reasonably heavy memory access patterns and processors numbering more than about eight, the data bandwidth of a single bus, no matter how wide, becomes insufficient to provide the access needed by all processors. If there are n processors which all wish to use the bus, the bus can, on average, provide each one with access only 1/n of the time. For computations with frequent memory access and large communication bandwidth, more data channels are needed to connect the processors.

A ring topology with n hops can, in the best case, increase the available bus bandwidth by a factor of n over a simple bus, but the latency is also increased by n. Also, the increased bandwidth is not worth as much as it seems because messages which circulate for more than one hop on the ring tie up bus resources as they travel.

A higher performance and more general approach to processor interconnection method is the switching network. This is a core fabric for communication. A switching network can be thought of as a box, with a set of input and output ports, which provides the service of passing data from any input to any output. Chapter 2 provides an overview of switching network concepts.

#### 1.3 Interprocessor Switching Network Design Goals

To provide the interprocessor communication network, we have chosen to implement a circuitswitched, multistage, indirect network called Transit. These terms are defined in Chapter 2. The Transit network is based on the bidelta network topology, with special network and crossbar switch design features to enhance performance and fault-tolerance. The goals for the Transit network are

- Low-latency communication

- High-bandwidth communication

- Fault-tolerant communication

By low-latency communication, we mean interprocessor message times which are comparable to today's main-memory access times. While some parallel computation paradigms, such as dataflow, claim to be able to mask message latency with parallelism, we would like the option of very high speed message delivery. The initial Transit network is designed for a constant three pipeline stage delay, with very high probability of successful message delivery on the first transmission attempt [DeHon 90b].

The network should support data transfers which match the input-output requirements of the processors. The goal for the Transit network is to support 100Mbytes/sec data transfers on each network port. Each processor node will have four network ports assigned to it on which it can transmit one 100Mbyte/sec data stream and receive two such streams simultaneously.

The third design goal is fault-tolerance. We want our network to be able to provide full connectivity for all processing nodes in the event of multiple failures of routing chips, wires, or connectors. Fault tolerance in the Transit network is achieved through a combination of design

#### strategies [DeHon 90a].

#### • Hardware Level

As detailed in the following chapters, the basic routing switch component, the RN1 chip, can operate as a dilated crossbar [Kruskal 86] which provides redundancy in routing connections. The switch can choose one of two alternate paths to route a connection, based on an internal pseudorandom number generator. This provides the basis for path dilation in the network, a technique to improve the routing performance and fault tolerance of the system.

#### • Network Topology Level

A Transit network is a member of a class of logically equivalent wiring topologies which provide inherent redundancy in the choice of paths through the network from a source to a destination. Research into randomized routing of the redundant paths [Leighton 89] through these networks has shown that remarkably consistent performance is achievable, in spite of the presence of faulty chips or wiring. The RN1 chip is designed to support the Transit network topology.

#### • Layered Protocol Level

The Transit network provides what is called *unreliable* message delivery. The pejorative connotation of this term is somewhat deceptive. In the network literature [Tanenbaum 81], any protocol which gives the sender responsibility for message delivery is termed unreliable. The network makes a best-try attempt to deliver data to its destination. The network provides information to the sender on the status of a connection, but if a connection is blocked, it is up to the sender to retry transmission or choose another destination. This is the same approach used in the packet switched Internet Protocol [Comer 88]. Of course, a reliable packet or stream layer can be built on top of this protocol just as a reliable protocol such as TCP/IP is built on an unreliable medium such as ethernet. The robustness of the ARPA internet protocols attests to the fact that an unreliable network level protocol does not imply unreliable end-to-end data communications.

While some routing networks claim to provide reliable message delivery in hardware, the lower overhead of the simple unreliable protocol supported by our network hardware helps

us achieve very high speed connection setup and data transmission. Also, the experience of the ARPA interact has shown that the depending on granusteed manage delivery by the underlying network hardware has proved to be an expensive and error-prope approach.

## Chapter 2

# A Review Of Interprocessor Communication Networks

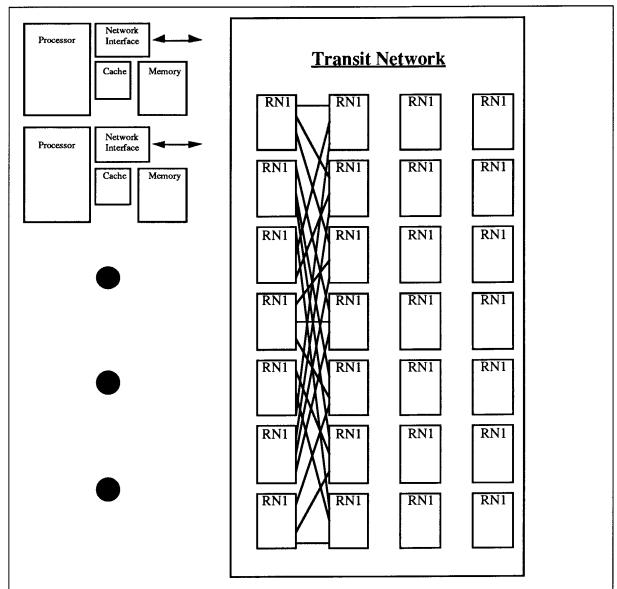

The family of multiprocessor computers we are building [DeHon 90b] all have the common need for processor nodes to communicate through a low-latency high-bandwidth network. The basic configuration as shown in Figure 2-1 consists of a number of processor nodes with local cache and memories and interfaces to the routing switch.

The routing switch should ideally be able to make a connection from any input terminal to any output terminal. Since each processor node can handle only a small number of input connections at a time, it is pointless to give the network the capability of routing all inputs to a single output. The inverse capability, broadcasting data from a single processor to all others, might be useful in some cases; however, interprocessor broadcast communication has some serious pitfalls. Consider the case where a sender node broadcasts a message to every other node in the machine and then wishes to get positive ackowledgement from all receiving nodes. An extreme traffic jam of incoming messages will flood the source node and all paths in the network leading to it. This is one example of a synchronization problem [Tanenbaum 87], a very serious issue in multiprocessor designs. In general, problems will arise when several processors are competing asynchronously for a single resource.

Figure 2-1: A small Transit machine; processors with memory/network interfaces to a routing switch implemented by a Transit routing network.

#### 2.1 The Crossbar Switch

We define an  $n \times m$  crossbar switch to be a component with n input ports and m output ports, which can establish a connection between any input port and any output port. The term crossbar comes from the old electromechanical telephone switching equipment, which had crossed rows and columns of metal bars for the input and output ports, which could be connected by electromagnetic mechanical contacts. Figure 2-2 shows an example of a  $2 \times 2$  crossbar switch.

A crossbar switch can be characterized by its radix, which defines the number of choices of output directions the part has. Note that the radix of a crossbar is not always equal to the number of output ports. An additional parameter, the dilation, characterizes how many physical channels there are in each logical direction. For an  $n \times m$  crossbar,  $dilation \times radix = m$ . The dilation can be thought of as a measure of the redundancy of the logical channels. Figure 2-3 shows a  $4 \times 2$  crossbar switch with dilation 2, with the output ports grouped together into logically equivalent pairs. This switch can be thought of as switching data between two logical directions. A dilation greater than one indicates that a logical channel can support several simultaneous data transmissions on that channel.

In general, in a self-routing network (Section 2.2.7) with switch nodes of dilation greater than one, the decision of which equivalent physical output channel to use is made by the individual routing elements, with perhaps some feedback from the network as to which paths are more likely to succeed. When a dilated crossbar is faced with the choice of several available channels for an output, it is free to choose which available physical channel in the logically equivalent set will be taken.

#### 2.2 A Routing Switch Made From A Single Crossbar

A routing switch of arbitrary size, which can establish connections from any input to any output, can be implemented using a single large crossbar switch. A true crossbar switch has the unfortunate property that the number of active elements (crosspoints) scales as the square of the number of inputs to the switch. The usage of resources in large crossbars is also very wasteful; for a  $1000 \times 1000$  crossbar, there will be 1,000,000 crosspoint elements. Only at

Basic Crossbar (no connections)

Single connections through switch

Two connections through switch

Figure 2-2: A simple  $2 \times 2$  crossbar switch.

Basic dilated crossbar

Logically equivalent connection pair

Figure 2-3: A  $2 \times 2$  crossbar switch with dilation 2.

most 1/1000 of the crosspoints in the switch can be active at once, and the remaining 999,000 crosspoint elements will be idle.

#### 2.2.1 Multistage Routing Networks

While the crossbar provides the simplest model of a routing switch, more hardware efficient routing networks can be built by dividing the routing hardware into a distributed or multi-layer structure. The tradeoff is that now several stages of switching are required to route data from the inputs to the outputs of the network. The wide range of possible multistage routing networks can be divided into several broad classes. Table 2.2.1 shows some of the major categories of routing topologies, and the machines which use such networks. Note that in the best cases, the latencies of these networks is logarithmic in the number of network ports, versus constant time for a full crossbar implementation.

| Network Type          | Example Topology | Complexity   | Latency         | Processor          |

|-----------------------|------------------|--------------|-----------------|--------------------|

| Full Crossbar         | Full Crossbar    | $N^2$        | O(1)            | Cray Y-MP          |

| Grid/Mesh             | Grid             | N            | $O(\sqrt{N})$   | J-Machine          |

| Logarithmic, Direct   | Hypercube        | $N \log_2 N$ | $O(\log_2 N)$   | Connection Machine |

| Logarithmic, Indirect | Omega            | $N \log_r N$ | $\log_r N$      | NYU Ultra          |

| Logarithmic, Indirect | Beneš            | $4N\log_r N$ | $2\log_r N - 1$ | GF11               |

Table 2.1: Categories Of Networks and Representative Architectures

The networks which I will concentrate on in the following sections are the multistage shuffle-exchange networks [Gottlieb 89]. A large group of network topologies are included in this category including banyan, Beneš, delta, omega, butterfly, and many others. The basic routing algorithms of these networks is the same, with a progression of messages advancing strictly forward through the routing network, and depth of the network proportional to the logarithm of the number of destination nodes. The differences between these networks have to do with geometric layout, blocking performance, component count and network depth.

#### 2.2.2 Direct vs. Indirect Networks

The terms direct network and indirect network are used to describe the relative topological placement of processors and routing elements in the network. The direct networks intersperse processing elements with routing elements. The mesh or qrid topology places routing switches

and processors at vertices in a two or three dimensional grid. Latency in a grid or mesh of n processors is proportional to  $\sqrt{n}$  or  $\sqrt[3]{n}$ . Data are routed by passing them from point to point in the grid. The binary hypercube places processors and routers on the vertices of a higher dimensional cube. Latency in an n node hypercube is proportional to  $\log_r[n]$ , where r is the degree of the vertices. One example of a commercial hypercube machine is the Thinking Machines Corporation Connection Machine.

An indirect network separates the routing network from the processors. In an indirect network, the latency for connections through the network tends to be more uniform, since there is usually a constant number of stages between inputs and outputs of the network.

#### 2.2.3 Non-Blocking Circuit Switched Networks

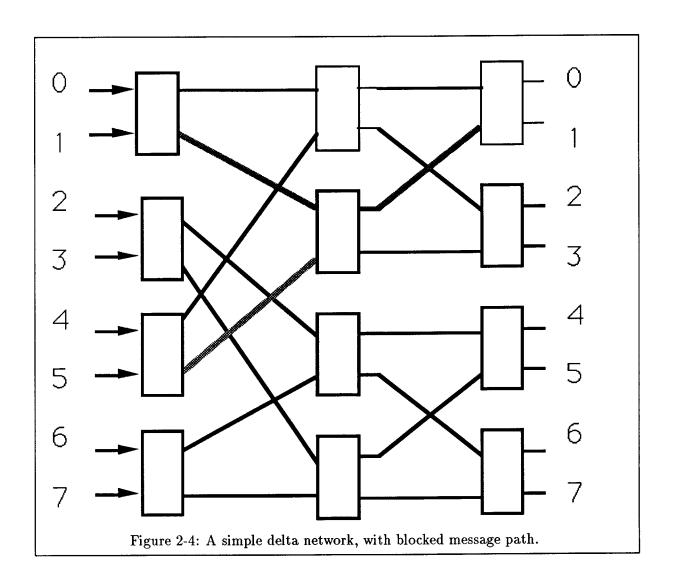

The simplest multistage shuffle-exchange network topologies, such as the *onega* network, have the property that there is one and only one path from a given input port to a given output port. This creates the unfortunate situation that there are many possible states of the switches such that a circuit path from a particular input to an output is blocked by another circuit path. Thus, it is not possible to always open a connection reliably from any port to another. Figure 2-4 shows an example of a blocked path in an 8 port network. There exists an open connection from input port 1 to output port 1, but there is then no way for input port 5 to connect to output port 0, because both path need to use the single upward physical channel of the crossbar switch in the middle stage of the network.

#### 2.2.4 Clos Networks

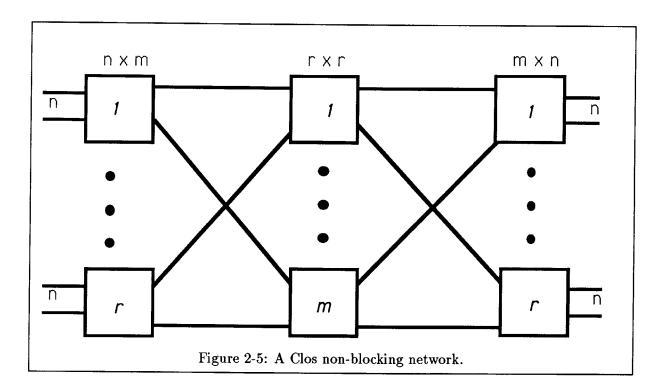

It is possible to design a multistage circuit switched network in which all permutations of sender to receiver connections can be made simultaneously, with no blocked paths. One such multistage network is the Clos network. A non-blocking Clos network, shown in Figure 2-5 is a  $n \times m$  input three stage indirect network whose first stage is made from  $r \times m$  crossbars, and whose middle stage is built from  $m \times r \times r$  crossbars. It can be shown [Benes 65] that when  $m \ge 2n-1$  and when using a simple routing heuristic, that all possible permutations of input to output connections can be made. For large networks, the size of the needed crossbars in Clos network clearly makes it impractical. It also requires a "omniscient" controller to configure the

switches for a route based on global knowledge of the state of the entire switch.

#### 2.2.5 Beneš Networks

Beneš actually defines two kinds of non-blocking behavior. Non-blocking in the wide sense refers to a network for which any possible set of routing switch configurations for a set of connections through the network is possible. Non-blocking in the strict sense refers to a network along with a set of rules that if followed carefully result in routing of all messages such that no blocking occurs. Beneš points out that practical networks which are non-blocking in the strict sense have not been found. The Clos network is an example of a network which is non-blocking in the wide sense.

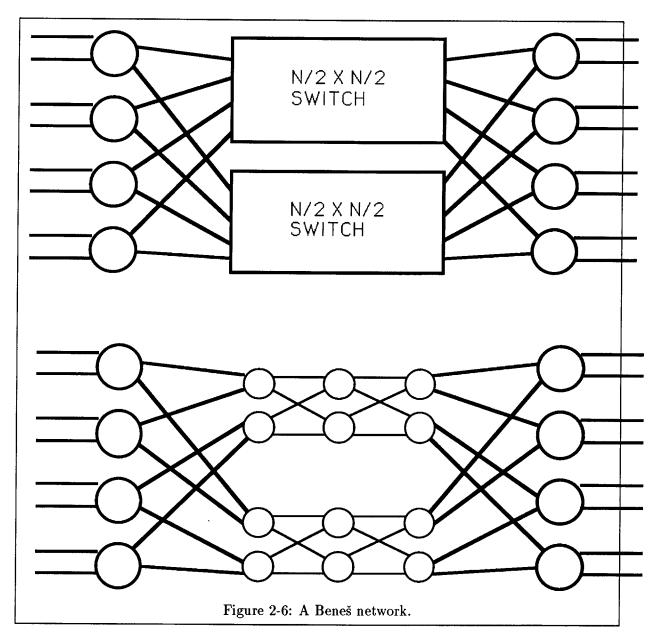

A practical non-blocking network can be created with a recursive formulation of a network built from the Clos network [Hui 90]. For a Beneš network with  $N=2^n$  ports, the construction shown in Figure 2-6 results in a non-blocking network which has  $2\log_2 N - 1$  stages and  $4N\log_2 N$  crossbars.

## N inputs, 2x2 switches

#### 2.2.6 Packet and Circuit Switched Networks

There seems to be no way to build an efficient non-blocking multistage network with less than  $2\log N$  latency. And even if there was, it does not help in the case where multiple messages really want to go to exactly the same destination, i.e., the routing problem is not a simple permutation. There are two alternative approaches to working around the blocking problem in multistage networks. One approach is packet switching, where hardware is added to the network which can buffer blocked messages until the resources needed to route them become available. Another approach is to stick with circuit switching and move the responsibility for retrying blocked connections from the network to the sender.

In packet switching, the sender composes a complete packet of data, along with a destination address, and hands it to the network. The network is usually designed to guarantee that the packet will be delivered eventually to its destination and not lost or corrupted. Accomplishing this goal can be much more complex than it first appears; consider the case where a router switch fails in the middle of forwarding a section of a message. The network must have hardware to deduce that data has been lost in transit, and reproduce the lost data somehow.

In a circuit switched network, on the other hand, the sender requests a connection to a destination node, and the network opens a "virtual circuit" through the routing switches. The sender can then send data through this circuit for as long as it wants after which the circuit is closed down. If a path is blocked, the sender is notified and asked to try again later.

An analogy can be made between a packet switched network and the post-office, and between a circuit switched network and the telephone network. With a packet-switched network, the sender puts a message in an envelope, writes the address on the outside, and gives it to the post-office. The post-office eventually delivers it. In a circuit switched network, sending a message is like making a telephone call. The sender picks up the phone, dials the number, and then waits for a connection. If the line is busy, the sender hangs up and tries again later. If a connection is granted, the sender can transmit data to the destination. The connection is held open as long as the sender is transmitting data.

There is even a kind of hybrid of packet-switching and circuit switching. [Dally 87] describes wormhole routing which combines a kind of wormlike packet switched message delivery. A message is divided into *flits*, where each flit is the smallest unit of data that can be sent across

a network edge in one cycle. A message snakes its way through the network, holding open a circuit the length of its flits, and possibly being buffered or diverted in the network. The wormhole router has the property of guaranteed delivery by a network with no component or wiring faults.

#### 2.2.7 Self Routing Networks

One very desirable feature to have in a multiprocessor communication network is the ability for messages or connections to be routed through the switches based only on local knowledge available at each switch. The telephone companies, in contrast, have switches which are controlled by a global switching program, which uses routing algorithms based on the state of the entire network. This is acceptable when the setup time for a connection or message is short compared to the duration taken by the transmission of data in the connection. For a telephone call, the setup time may take milliseconds, and the call may last for minutes. In a multiprocessor system, however, the normal mode of operation will be huge numbers of short message transactions which represent memory references. It is impractical to build a controller to globally service all of these simultaneous routing requests. It is necessary to have the individual switches in the network route the messages based on the local state of the switch, and perhaps its neighbors. Work has been done by Leighton [Leighton 89] on the distributed propagation of network supervisory information by the switch elements in a multibutterfly, and Chong [Chong 90] on local routing algorithms based on propagation of network state using analog circuit principles.

In a simple undilated multistage shuffle-exchange network the routing algorithm is simple; there is only one logical path from any input to a specific output. Each routing switch chip simply looks at a portion of the address field of the message and switches the connection to the indicated output port. If that output port is busy, the message is blocked. In a packet network, a blocked message must be either rerouted or buffered locally at the switch.

#### 2.3 The Transit Network

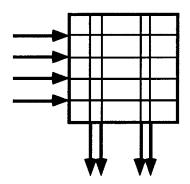

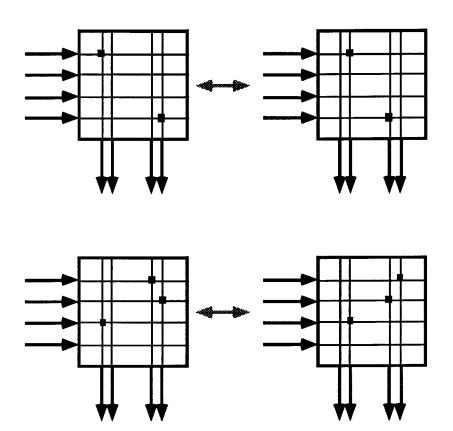

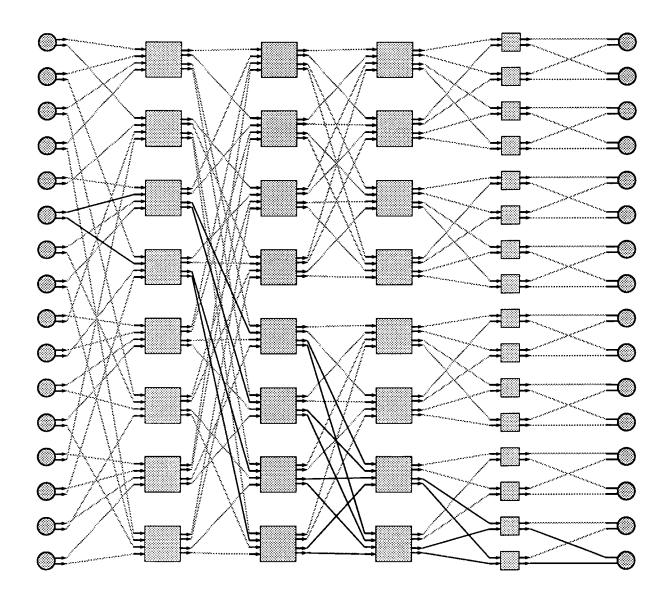

The Transit routing network is a multistage indirect shuffle-exchange network. A Transit network is built from dilated crossbar switches except at the final routing stage. Figure 2-7 shows a 16 port Transit network, made from  $4 \times 2$  dilation 2 crossbars. The bold lines show all the possible paths from port 6 to port 16.

The choice of a high dimensional indirect network vs. a direct network was made partly because of system packaging issues. We wish to get the lowest latency message delivery possible, and are willing to use as much wire (in the form of multilayer printed circuit boards) as we can, within practical engineering limits, to achieve this goal. The simplicity of routing in the delta network makes it that much easier to achieve high performance in our routing switch components. The simple delta network [Patel 81] has serious problems, from both a fault-tolerance and traffic congestion perspective; since there is only one unique path from any input to any output, a single switch node failure or blocked path will prevent connection between that input-output pair. This problem is addressed by the dilated network topology.

[Kruskal 86] defines a d-dilation of a banyan network to be the network obtained by replacing each interstage channel in the original network by d channels. A message entering a switch may exit using any of the d channels going to the desired successor switch at the next stage. The Transit network topology is similar in theory to the class of d-dilated banyan networks since the dilated crossbar switches are used. But the wiring pattern of the d-dilated banyan networks simply replaces each network edge with a dilated edge. The Transit network splits the dilated channels to make sure that they run to different physical routing switches in order to improve fault tolerance.

It should be pointed out that the actual choice of next-stage switch node destinations for dilated channels has a large impact on the tolerance of the network to internal switch failures. [DeHon 90a] describes an analysis of how network reliability in the presence of component failures is influenced by the wiring destinations of dilated network paths. This work is based in part on the ideas put forth by Leighton [Leighton 89] on fault tolerant routing in the multibutterfly network.

<sup>&</sup>lt;sup>1</sup>[DeHon 90a] explains why, from fault-tolerance considerations, the final stage of the Transit network should be composed from simple dilation-1 crossbar switches.

Figure 2-7: A 16 port Transit Network composed of  $4 \times 2$  parallel crossbars.

#### 2.3.1 The RN1 Chip

The RN1 chip, described in detail in the next chapter, is an  $8 \times 4$  dilation 2 crossbar switch component with byte wide data channels. It can also be configured as a two independent  $4 \times 4$  dilation 1 crossbars in the same physical package.

The Transit network to be used for the MBTA project is composed solely of RN1 chips. The network is organized as n stages of radix r routing chips, where the number of stages equals the logarithm, base r, of the desired number of processor nodes. The primary interface to the network takes place at the input ports of the first stage of routing chips. Connections are dynamically constructed through the network to reach the output ports of the final stage of routing chips. These output ports connect to their associated processor nodes. Each processor node has access to two input ports and two output ports. To keep network loading below fifty percent, we can restrict a processor node to using only one of its two network input access ports at a time. The processor node can still attend to two simultaneously incoming requests on its network output ports.

The Transit network depends on the dilation property of the routing components to provide good routing performance and fault tolerance. The basic mechanism depends on a pseudorandom number generator built into each RN1 chip. When a new connection is being routed, if an RN1 chip has two uncomitted output channels in the desired logical direction, one is chosen at random. This serves to expand the number of alternative paths through the network at each stage. This path expansion helps reduce hot spots in the network due to deterministic communication paths. The randomized routing also makes it likely that an attempted route through the network which fails due to a faulty wire or chip in the path will be routed through a different path when the sender tries to reinitiate the connection.

[Gottlieb 89] makes a distinction between message-switched and circuit-switched behavior of the network. They define message-switched traffic as using one-way only communication channels, where a reply from a receiving processor node to a transmitting node must be routed as a separate connection. Circuit-switched connections are able to send data bidirectionally.

The Transit network has the capability to support either message-switched or circuitswitched traffic, i.e., a transmitting node with an open routed connection can turn the connection around and receive data from the far end without requiring the receiver to open a new return connection. Our initial goal is a 64 processes node marking, so with a Branch network built from radix 4 RN1 companents, we will have notwork lattices of log, 64 = 3 through the network, and pipeline delay of 5 for turning around a sommetion.

## Chapter 3

# The RN1 Parallel Crossbar Chip

#### 3.1 Background

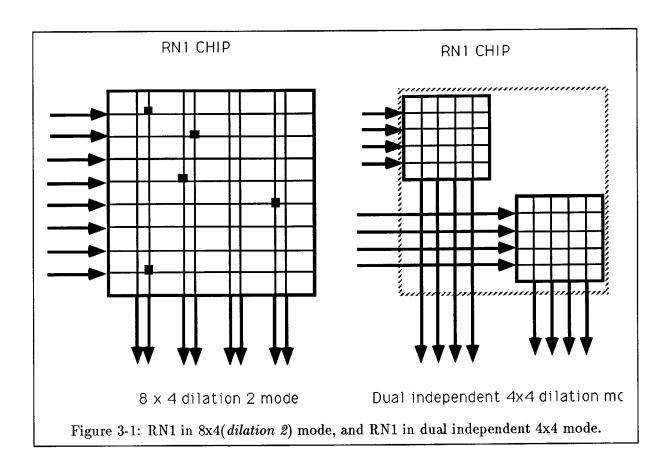

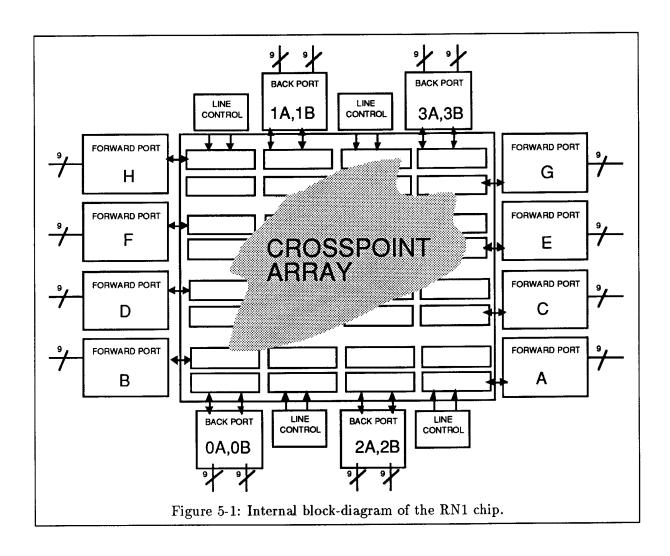

In Chapter 2, we defined an  $n \times m$  crossbar switch to be a component with n input ports and m output ports, which can establish a connection between any input port and any output port. The RN1 chip is a self-routing crossbar switch with byte wide channels. It has two operating modes; it can be an  $8 \times 4$  crossbar with dilation 2, or a pair of independent  $4 \times 4$  crossbars each with dilation 1. Figure 3-1 shows a diagram of the functional equivalent of the two modes of operation.

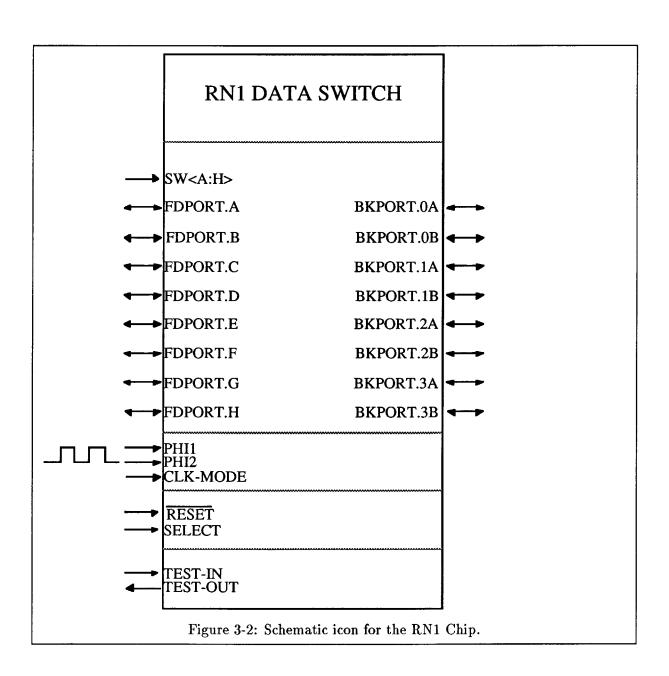

Figure 3-2 shows a block diagram of the RN1 part. The RN1 chip has eight forward ports, FDPORT<A:H>, and eight back ports BKPORT<O:3[A,B]>. We called them forward and back rather than input and output ports, because data can actually be transmitted bidirectionally through a connection. Connections can only be initiated through a forward port, however. Data transmitted from a forward port to a back port is said to be travelling in the forward direction. Data transmitted from a back port to a forward port is said to be travelling in the backward direction. Detailed description of the operation of the chip is given in following chapters.

In the 8x4 mode, RN1 can open a connection from any forward port to any available back port. In the dual independent 4x4 mode, the RN1 acts as two separate 4x4 routers, where the forward ports A,C,E,G can connect only to back ports 0A,1A,2A,3A, and the forward ports B,D,F,H can connect only to back ports 0B,1B,2B,3B.

#### 3.1.1 The Need For Dilation

An essential feature of the RN1 chip is its dilated outputs; the ability for it to route a connection to one of two logically equivalent output ports. This mode of operation allows the construction of a routing network with multiple paths from any source to any destination, such as the Transit network. In fact, the number of alternate paths expands exponentially up to the middle of the routing network [DeHon 90a]. This is in contrast to the simple crossbar switch of dilation 1 as used in a basic omega or butterfly network.

For a network of given size, as measured by the number of ports, number of routing chips, and number of wires, a single Transit network has better routing performance under load than a network built with the same number of parts as two independent omega networks. Dilation is also of great importance for fault tolerance in the network. The Transit network can have a remarkable number of chips removed before any processor loses full connectivity with the rest if the network [Egozy 90e].

#### 3.1.2 Connection Protocol

RN1 supports a circuit switched connection protocol. This means that once a connection has been opened, an arbitrary amount of data can be streamed through it, and it will be delivered to the destination in order with a fixed latency. There is no fixed packet size, at least not at this level. Higher level protocols can of course impose additional constraints on the data format. A connection through the Transit network consists of a path through a set of RN1 chips with sequential interstage open connections. The RN1 chip, and thus the Transit network, is self-routing because a connection is created through the network with each RN1 switch in the path making a routing decision based on purely local information. This is in contrast to an architecture which requires routing control inputs distinct from the data ports, as is common in telecommunications crossbar switches [Gigabit 1988] [Barber 88].

#### 3.2 System Design Issues

The RN1 chip was designed to be a part of a complete computer system. The integrated circuit itself is only a part of the final system, and many aspects of its design were driven by

considerations of how it fit in to the system as a whole. The Transit project goal is to build a practical working system within the bounds of today's technology. Ideally the whole computer system would be fabricated on a single monlithic substrate. The practical size of a chip today is about 1.5 cm square, and contains only a few million transistors. The systems we want to build are larger, and thus require many chips to be packaged and interconnected, powered, and cooled. The system must be partitioned into modules, and the decisions of how to best partition the system are driven by technology constraints and our imaginations.

One of the overall goals of the Transit project is the design of a physically compact and reliable packaging and interconnect system in which hundreds of processor nodes can communicate with one another quickly. A Transit network supporting 256 processors is composed of 256 routing switch chips, and the inevitable support circuits for clocking and interfacing to the nodes. The design decisions for RN1 were made based on a mix of contributing factors, some of which are detailed in the following sections.

## 3.3 Chip To Chip Communication Technology

The on-chip worst-case delay for the RN1 is estimated to be between 8 and 12 nsec. The delay going from on-chip to off-chip through a 5 Volt I/O pad is 4-5 nsec. The transit time between chips is limited by the speed of light in wire, in the best case. In reality, reflections of pulses because of impedance mismatch between drivers can increase the settling time. The 5 volt standard CMOS output levels also takes a non-neglible time to swing.

Prof. Knight has described a design for low voltage self-terminated pad driver and reciever [Knight 89b]. This presents a good alternative for future RN1 designs, combining the economy and low power consumption of CMOS with the benefits of ECL-like speed. The proposed 1 Volt pad voltage swing would significantly reduce power consumption of the chip. The design for the 1 Volt self-terminating pad drivers and receivers has been updated by Prof. Knight and Alex Ishii. New pad test circuits are currently under evaluation in our lab.

Another option is to use ECL gate-array technology for the next version of the RN1 chip. The current packaging scheme makes provision for liquid cooling, so the power dissipation is not a serious problem. Motorola has ECL gate-array with series-terminated pad drivers available in several impedance values.

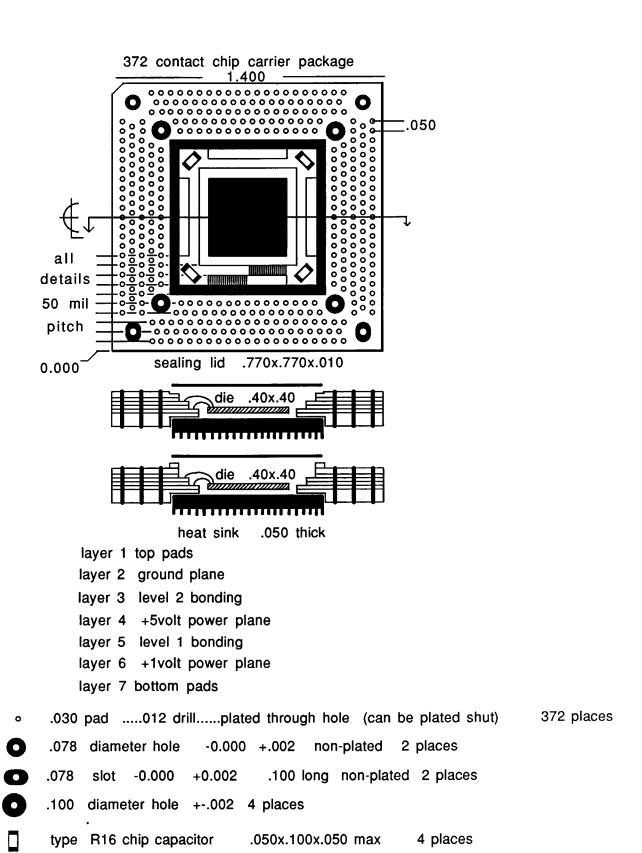

## 3.4 Packaging

The first technological constraint on system partitioning comes with the number of pads that can be placed on a silicon chip using today's commercial technology. The constraint comes both from the requirement that pads be located at the periphery of chips, a limited perimeter area, and the cost of high pin-count packages. The practical limit is between 300 and 500 pins, with packaging costs rising much faster than linear as additional pins are added. This sets constraints on the choice of radix and dilation of our routing switch. If we commit to byte wide ports, this leaves us a practical limit of sixteen ports on a chip. The reader might wonder at that number, since adding up the port pins plus control signals gives a total of only around 160 pins. For even modest performance on a chip of this size, a sizable number of power and ground pads are needed. RN1 uses 80 power and ground pin from the package to the circuit board, and more even more power bond wires from the package to the die.

The interconnection network is a crucial bottleneck in the system design, because of the very large number of wires that must be routed; With a 256 processor system with one network routing stage per board, up to 8,000 wires have to be routed between the routing stages. Since the required number of chips will not all fit on a single circuit board, this means that these thousands of wires must run between circuit boards. In a conventional computer system design, the routing cards would be fitted to a backplane with edge connectors. If we wish to put a four stage network onto four cards, we will need edge connectors with 4,000 pins. Current technology bus connectors allow more like three or four hundred pins on a EuroDIN style connector. Instead, we have decided to dispense with the backplane entirely.

We have taken a unique approach to the board-to-board connection problem, by using our chip packages as both chip-to-board and board-to-board connectors. This is done by our use of custom designed IC packages and connectors[Transit 90]. Our IC packages have 372 contact points which are used to create a board-to-board connector, with the routing chip in between (see Figure 3-3). This allows our machine to be packaged in a dense stack, effectively using all three dimensions for wiring, as opposed to only using two in conventional packaging.

# **Stack Cross-Section** Aluminum plate manifold horizontal board horizontal clock driver spacer RN1 Component (1v, 5v, gnd) window frame horizontal board button board horizontal board cover heatsink debug connector horizontal board Aluminum plate manifold

(Diagram courtesy of Fred Drenckhahn)

Figure 3-3: The *stack* construction technology developed for Transit. The entire machine is a multilayer sandwich of alternating boards and chips. Board to board connections are by way of the chip packages sandwiched between button connectors. Fluid cooling can be run vertically through the stack.

38

# Chapter 4

# Routing Chip Communication Protocol

The Transit network is designed to provide an efficient hardware substrate on which to implement a small but flexible set of primitive network transactions. The essential primitives we wish to implement, as defined in [DeHon 90c], are shown in Table 4.1.

In order to let the Transit network support these primitives efficiently in hardware, the RN1 chip architecture supports a simple protocol which will be described in the following sections.

# 4.1 Chip To Chip And End To End Network Protocol

When a network is built from RN1 chips, the protocol used by the network interface controllers to talk to the network endpoints is the same protocol as is used internally by the network chips to talk to one another. Thus, it is possible to detail a single command protocol which serves to explain both the external user's end-to-end view of the network, and the internal chip-to-chip

| Operation | Description                                        |

|-----------|----------------------------------------------------|

| read      | Read memory data from a remote destination node    |

| write     | Write memory data to a remote destination node     |

| noop      | Open a null connection, used for network testing   |

| reset     | Issue a hardware reset to a destination node       |

| rop       | Network operation emulation primitive <sup>1</sup> |

Table 4.1: Transit Network Basic Primitive Transactions

| COMMAND | ENCODING   | MEANING                              |

|---------|------------|--------------------------------------|

| IDLE    | #000000000 | This port connection is idle.        |

| ROUTE   | #1aabbccdd | Open a connection to address         |

|         |            | #aabbccdd.                           |

| DATA    | #1xxxxxxxx | Send this data through an active     |

|         |            | connection.                          |

| TURN    | #011111111 | Turn control of channel over to      |

|         |            | receiver, and return status          |

|         |            | and checksum bytes.                  |

| DROP    | #000000000 | Drop this active connection.         |

| HOLD    | #100000000 | Temporary pattern to hold connection |

|         |            | open during backward turn.           |

Table 4.2: Byte Encoding of Command Words Understood By RN1

communication protocol.

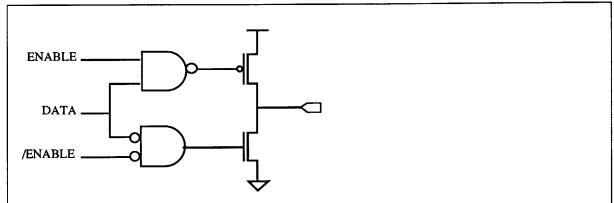

The RN1 chip is operated by sending sequences of commands and data into its forward ports. Each forward and back port presents a bidirectional nine-bit wide datapath, consisting of eight data bits and one control bit. The ninth bit (MSB) is the control bit. This bit is always high when transmitting data and low when signalling occurs or no data is being transmitted. Data is latched into the port synchronously with the clock, on the the falling edge of the external clock.

## 4.1.1 Byte Encoding of Command Words

A complete data transaction using one or more cascaded chips in a network, consists of a sequence of command and data words. Table 4.2 summarizes the valid commands which the RN1 supports.

The meaning of the command words is summarized below.

• IDLE When a forward port is in its IDLE state, its pins are configured as inputs, and all data presented to it with control bit low is ignored. When a back port is in IDLE state, its pins are configured as outputs, with an idle byte pattern as its output.

After a global chip reset all of the forward ports are set to be inputs and are said to be internally in an IDLE state. The back ports are set to be outputs with an IDLE pattern (all zeros are driven). All connections in the internal switching matrix are cleared.

- ROUTE When talking to an idle forward port, raising the control bit indicates a request to open a connection. The top two bits of the data word indicate which of the four logical output directions to attempt a connection with. If the connection is successful, the routing word is forwarded through the connection during the same cycle. In a multistage network, the 8-bit routing word (and all other data) are rotated left two bits by the interstage wiring, presenting the next two bits for routing in the top of the data byte at the next stage.

- DROP The DROP command causes the current connection to be cleared. The DROP command is forwarded through the connection before the connection is dropped. Thus, cascaded chips in the network cause the connection to be ripped down all the way through the network.

- TURN The TURN command causes a reversal of the direction of data transmission on the currently open connection. In the forward direction, STATUS and CHECKSUM bytes are returned from chips in the dead time that would normally fill the pipelined path through the network. In the backward direction, HOLD bytes are transmitted for the dead cycle.

The most common type of network transaction we envision is a 'round-trip' connection. A connection is requested to the desired target address. The bytes of a short message are sent through immediately following the routing byte. The connection is then turned, at which point verification is returned, in the form of status and checksum bytes, that a connection was successfully initiated. Reply data, if any, is then transmitted by the node at the far end of the connection.

## 4.2 Grammar to Describe RN1 Protocol

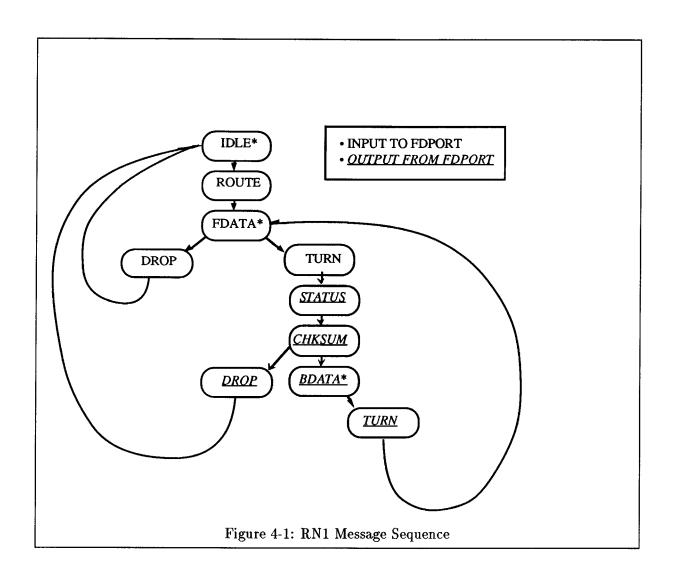

A valid message sequence can be described by Figure 4-1, where [BYTE]\* means a series of zero or more of that type of byte.

## 4.2.1 Opening A Connection

In the IDLE state, the forward ports are watching for a low to high transition of the control bit to indicate the start of a connection request. The host processor should apply idle bytes, consisting of all zero data word and zero control bit, until it is ready to attempt to open a connection. The first non-idle byte received by a forward port is a routing byte.

Table 4.3: Routing Byte Format

A routing byte consists of 8 bits specifying the destination for the message and a 1 in the control bit. The RN1 chip examines the high two data bits (A1,A0) to determine which of the four pairs of output ports will receive the message. Assuming a free output port in that direction is available, the routing byte is passed on through RN1 unchanged during the following clock cycle. Subsequent non-idle (control bit 1) bytes received by the RN1 are forwarded as data bytes. Each data byte is clocked onto the chip on the falling edge of the clock and appears at the outputs, if a connection has been successfully opened, at some point during the remaining period of the clock cycle. The data is thus available on the next clock cycle to the next stage router in the network. The number of data bytes transmitted is determined by higher level protocols, and is not restricted by the RN1 implementation.

In order to cascade more than four levels of RN1 chips, a Forward Port can be configured to take an extra cycle when opening a connection <sup>2</sup>. This extra cycle is used to *swallow* the first ROUTE (nonzero control bit) byte; when swallow is enabled, the first active ROUTE byte is simply discarded. The next byte to be sent is treated as the real routing byte, and is passed along to the back port (when a successful connection was made) in the normal fashion.

## 4.2.2 Blocked Connection

It is possible that at the time a forward port is trying to route a connection, all back ports in the desired direction are already in use. This creates a blocked path. In a multistage network, the partial path up to this chip will be held open, and subsequent data bytes will be discarded,

<sup>&</sup>lt;sup>2</sup>To activate the swallow state for port n, the SWn pin should be tied to VDD

until the connection is turned or dropped. The originator of the message will not be able to tell if the path was blocked unless the connection is turned around.

#### 4.2.3 Checksum

A router checksum is computed on the forward data through each switch. The 14 bit value of this router checksum is returned as part of the status byte (see Appendix A) but is otherwise ignored. It is the responsibility of the sender to compare the router checksum with the router checksum of the transmitted data. The router checksum provides a diagnostic to localize faults in the network. Higher level protocols will need a message checksum in the forward direction to assure the destination processor that the received message is intact.

## 4.2.4 Turning A Connection

At the completion of the forward data transmission a TURN byte consisting of a data word of all ones (\$FF) and a zero control bit is transmitted. The receipt of this byte by the RN1 on the input port signals the reversal of the associated data connection. The turn byte code is pipelined out the back port (if a connection presently exists) just like a normal data word. Simultaneously, connection status information and 6 bits of checksum (with control bit 1) are driven back onto the input pins. During the next cycle, another 8 checksum bits (with control bit 1) are driven back to the input pins.

A connection can actually be turned any number of times. The decision whether to drop or turn is always made by the node which is sourcing data into the channel.

## 4.2.5 Dropping A Connection

Alternately, the connection can be closed down by transmitting a DROP rather than a TURN byte. The DROP byte is pipelined out the back port, just like a normal data word, and the forward and back ports return to the IDLE state on the next cycle.

## 4.2.6 Turning A Blocked Connection

If the forward port is in a blocked state, then a TURN command has no continuing connection to turn around. In this case, the normal STATUS/CHECKSUM is performed, with the STATUS byte containing an indication that the connection was blocked at this stage. After STATUS and CHECKSUM are returned, the forward port returns a DROP command in order to shut down the initial partial path through the network, and returns to the IDLE state. [See the Sample Message Transmissions, Section 4.3 for an example of turning a blocked path]

### 4.2.7 Backward Connection

In the unblocked case, a forward connection which has been turned is now sending data in the 'backward' direction. The connection maintains backward propagation until a DROP or TURN byte is received at the back port. If a DROP is received it is pipelined out the forward port, and the forward and back ports return to the IDLE state on the next cycle.

If a TURN is received from the back port, then on the next cycle, the turn byte is driven out the forward port, while simultaneously, a HOLD pattern (control bit 1, data zeros) is driven out the back port. This holds the connection open during the next cycle, while the turn byte propagates to the previous chip in the network. For an example of this turning of a backward connection, see the third example transmission in the next section.

## 4.3 Message Examples

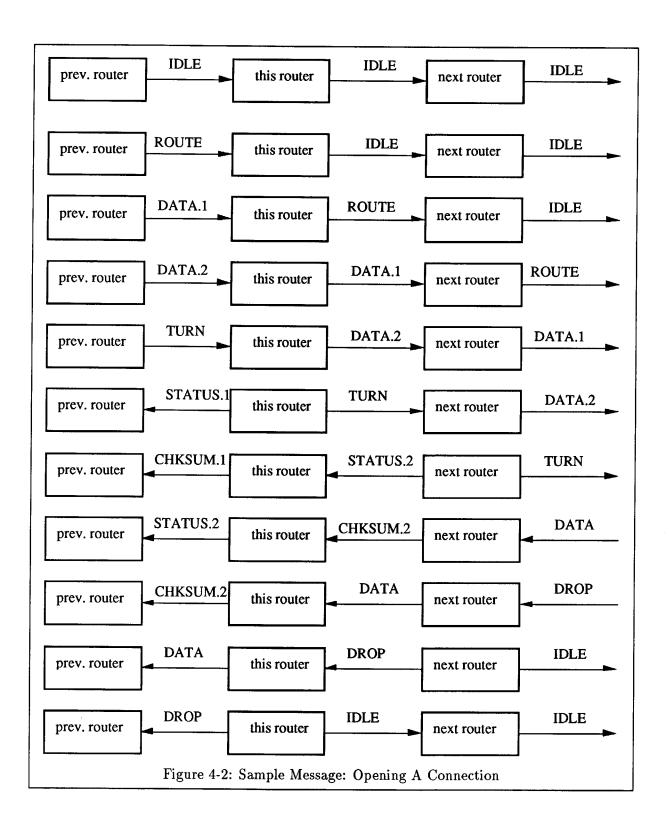

The diagrams on the following pages show examples of sample message transmission sessions. The data at the forward and back ports, and their direction of transmission, is shown by the arrows into and out of the center router chip.

## 4.3.1 Standard Message

Figure 4-2 is a standard message, with two bytes of data sent forward, the connection turned, one byte of data sent back, and the connection dropped from the far end.

## 4.3.2 Blocked Message

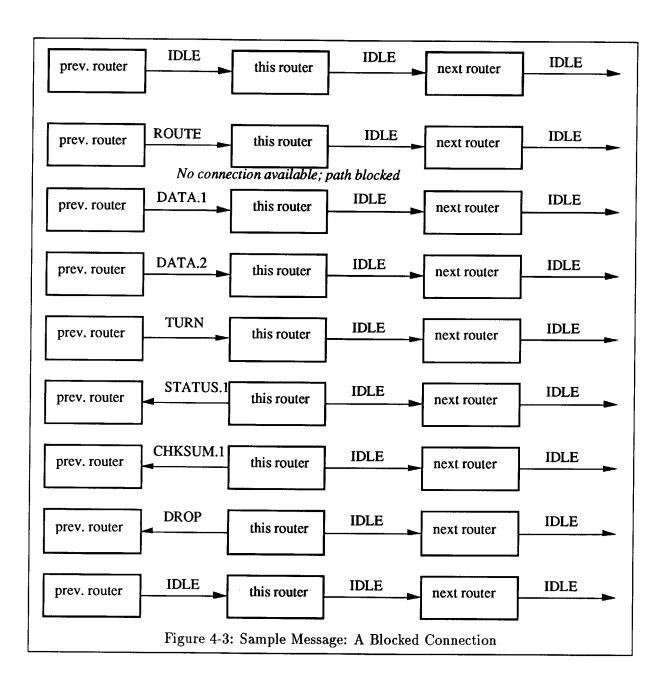

Figure 4-3 is an example of a connection which is blocked when it is opened. All Data bytes are lost, and the status returned indicates that no output connection was grabbed.

Note that the TURN command given to the blocked router returns STATUS and CHECK-

SUM, just like an unblocked connection. The blocked forward port then issues a DROP command in the backward direction, which will collapse the connection back to the source.

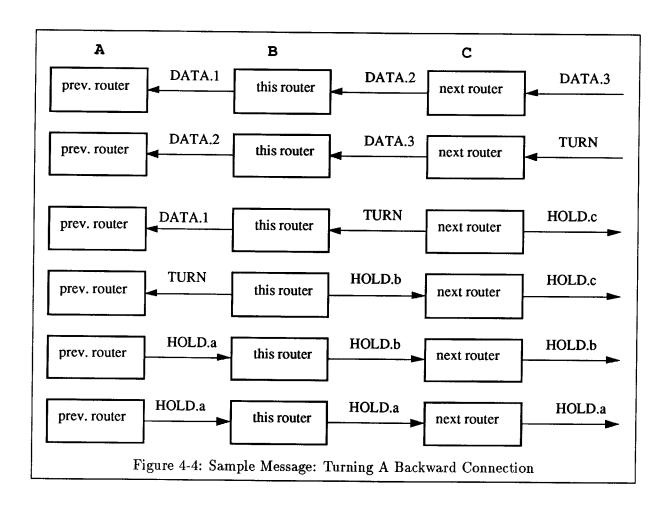

## 4.3.3 Turning A Backward Connection

Figure 4-4 shows an example of a connection which has already been turned (a backward connection) being turned from the back, to become a forward connection again.

The HOLD bytes are distinguished by the suffix .a, .b, .c to show which chip is generating them. They correspond to the STATUS and CHECKSUM bytes in the forward connection turn sequence.

The following diagrams show on each line sequential snapshots in time of the state of a chain of three router chips in a network. The type of data word being transmitted and the direction of data flow is show on the arrows connecting the chips.

# Chapter 5

# Architectural Description of the Chip

# 5.1 Overview Of The Internal Chip Architecture

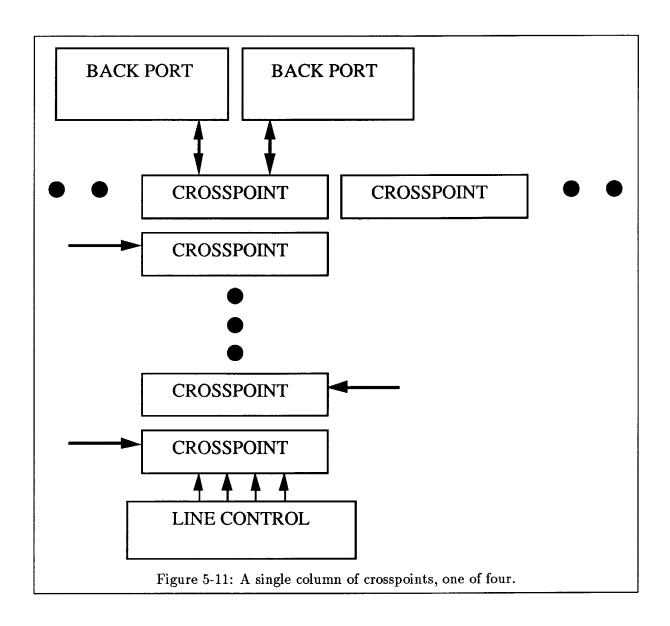

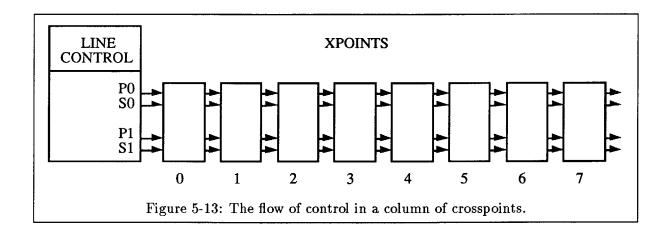

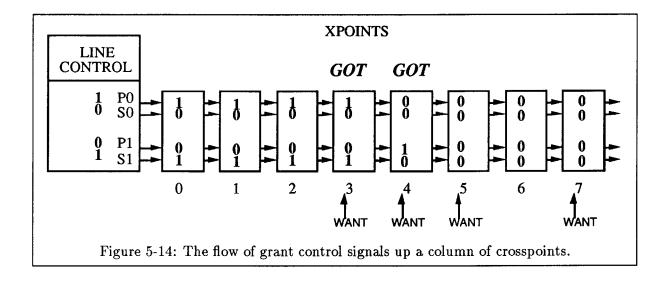

Internally, the RN1 chip consists of a central switching fabric, surrounded on four sides by forward-port and back-port state machines. The forward-port busses run horizontally, and the back-port busses run vertically. The central switching fabric is a tiled array of crosspoint modules. A crosspoint module is located at each intersection of a horizontal bus (forward port) and a vertical bus (back port). Because of the intrinsic redundancy built into the routing architecture, each crosspoint is actually a dual structure, serving a pair of back ports. The crosspoint array is shown in Figure 5-1 as an eight row by four column array of these modules, to better indicate the the close relation between the pairs of back ports. Each column represents one of the four logical routing directions, and the two back port busses in each column provide access for up to two connections in that logical direction.

The following sections detail the construction and operation of the forward ports, back ports, crosspoint array, and line control modules. Clocking and pad logic is also discussed.

## 5.2 Forward Ports

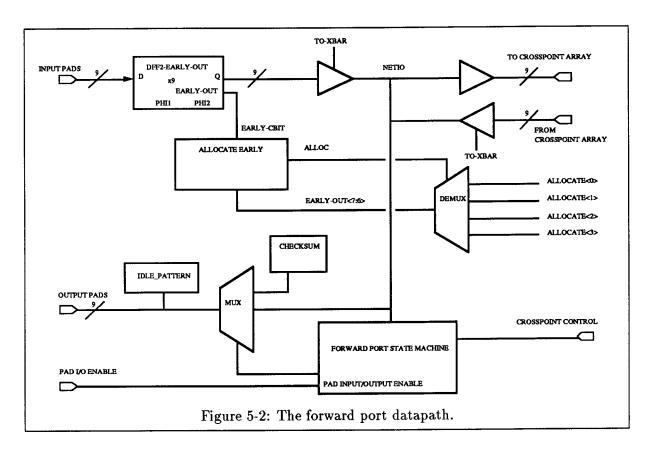

The eight forward ports have the primary responsibility for decoding and opening new connection requests, and returning connection status when a connection is turned. The basic datapath of a forward port is shown in Figure 5-2

The forward port attempts to open a connection using one of its four allocate<3:0> control lines into the crosspoints, as selected by decoding the top two bits of a routing byte. Each allocate line is wired directly to one of the four crosspoints on the internal horizontal data bus. Each crosspoint is capable of making a connection to one of two back port busses in the four logical directions. Crosspoint operation and line-control circuits are explained later in this chapter.

When a forward port is in the IDLE state, its nine I/O pads are enabled as inputs, and the data coming in to the forward port input flip-flops is latched on the falling clock edge <sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>An explanation of the clocking of RN1 is given in Section 5.7

In the IDLE state, the crosspoint drivers are enabled so that data from the flip-flops is driven through the forward port's horizontal bus into the crosspoint array on phi2 rising. The data will not get any further unless a routing byte is recognized, in which case an allocate line is asserted, and the corresponding crosspoint is then armed to try to allocate a connection to a vertical back port bus.

Note: The main data path bus in the forward port, netio, is somewhat vestigial. Our original design had a single common bus going into the crosspoint array, and we continued this thinking to have a single internal bus in the forward port. The single bus datapaths in the crosspoint were changed to two separate busses, one for input and one for output. The forward-port state machine needs to examine data no matter which direction the port is in, backward or forward. Separating out the bus into a forward and backward bus would eliminate the time required to enable the tristate drivers from the input latches or the crosspoint buffers. This is a candidate for redesign in future versions of this chip.

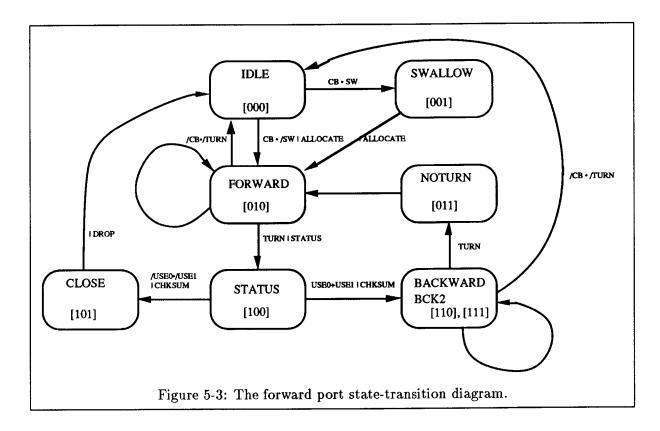

### 5.2.1 Forward Port State Machine

The forward-port state machine has a mix of combinational and clocked logic. The clocked logic determines the next state, while the combinational logic can compute control outputs based on changing inputs during the course of a single clock cycle. Figure 5-3 shows a state-transition diagram for the forward port.

#### 5.2.2 Early Allocate Datapath

According to our timing analyzer, the allocate cycle, in which a new connection is opened, was one of the critical timing paths on the chip. In order to make maximum use of the full clock cycle available, and to assure that certain combinational signals had settled before triggering dynamic logic in the crosspoint array path, we decided we needed to "get a peek early" at the new input data coming from the pads.

At the start of a clock cycle, as the input data arrives from the pads arrives during phi1, it is fed directly into a special "early" datapath. Normally pad data runs into a flip-flop and is simply latched internally during phi1, and not visible at the output until phi2. The early-out ports of the input flip-flops allow the allocate-early logic to see the data as it arrives during

phi1. The danger with looking at the data early is that the it is not yet stabilized by being latched, so it will have glitches during phi1. The alloc signal is generated by decoding the presence of a control bit, and the top two bits of the routing byte. As long as the setup time for phi1 is long enough for the incoming data to settle, the alloc lines will be stable when phi2 comes on.

The allocate-early module functions as a small independent state machine. Its job is to recognize a route command during phi1 (before the data has actually been latched into the input flip-flops), decode the routing destination, and enable one of four allocate control lines into the crosspoint array. Since the flip-flops in the allocate-early state-machine are processing data during phi1, it was neccessary to swap the clock inputs to its state flip flops, putting it a half cycle out of phase with most of the rest of the chip logic.

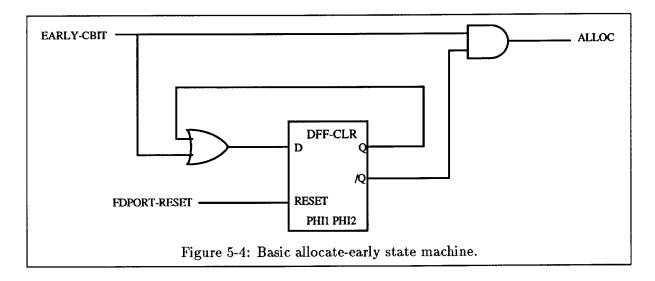

Figure 5-4 shows the basic circuit used for the allocate-early state machine. It consists of a flip flop and an AND and OR gate. In the IDLE state, a high control bit indicates a route command. This means an allocate operation must be initiated during the same clock cycle. The control bit, labeled as early-cb, comes directly from the pads. When the state flip-flop

is reset, the output enables the AND gate to pass an incoming control-bit. On the next cycle, the flip-flop will latch the high control bit value, and thus disables the AND gate from passing another alloc command. The OR gate passes the '1' around to be fed back into the flip-flop input, until the flip-flop is reset externally by the forward port state machine.

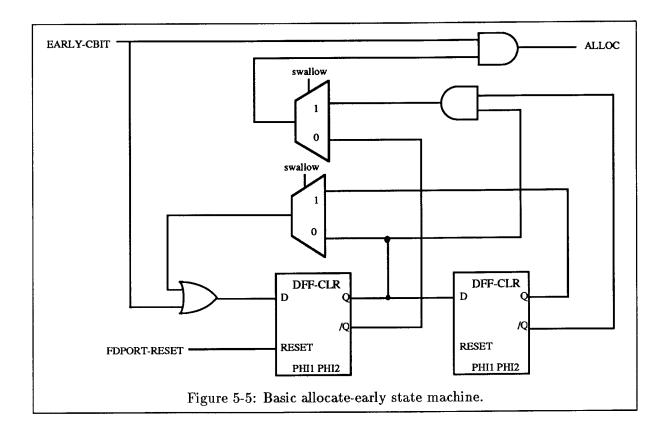

The presence of an extra state in the allocate cycle when the *swallow* state is enabled creates the need for a little more complexity in the allocate-early hardware. Figure 5-5 shows how an extra flip-flop was added to the circuit to enable a one cycle delay in the allocate sequence. The first flip-flop enables the second, and the second flip-flop actually asserts the alloc signal. A pair of muxes select between the one and two cycle allocate sequences, depending on the state of the swallow control signal.

In order to set up for the next routing byte, the allocate-early state machine must be reset when the connection is dropped, or a blocked connection is turned. Tragically, our test vectors did not cover this last rather simple case in the RN1 chip, and thus the allocate-early flip-flop is not reset under the previously mentioned circumstance. See the state diagram in Figure 5-3 for the guilty state-transition.

#### 5.2.3 Checksum

The checksum unit computes a 17 bit internal checksum, and reads out the bottom 14 bits in the status and checksum bytes during a turn. The checksum unit has seventeen flip-flops linked in a shift-register, with XOR feedback taps at bits 16 and 4. The bottom eight bits also have

the sequential data words XOR'ed in each cycle with the feedback taps.

Appendix A details the checksum algorithm as a lisp function. The checksum function was designed to emulate a maximal length sequence pseudorandom number generator. Note that the clock is always running on the checksum circuit, so that during a turn, between the first (status) and second (chksum) byte of the checksum, the shift-register is clocked once. When designing hardware to verify the returned checksum, the reader may test his design against the values shown in the test-vectors in Appendix D. Note that the next revision of the chip, RN1b, will use the CRC-CCITT polynomial checksum algorithm.

# 5.3 Back Port Datapath

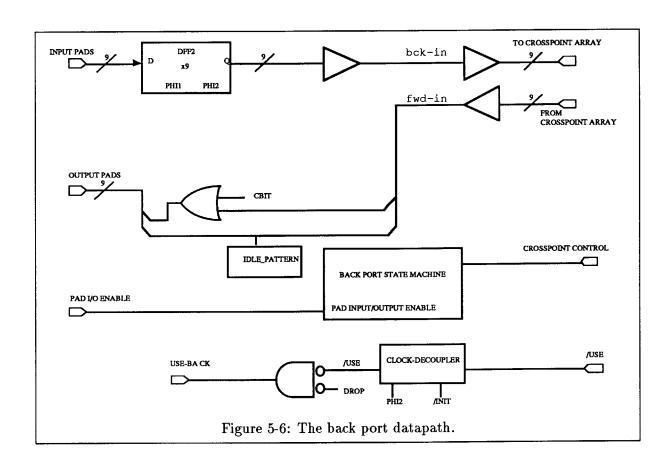

The back port is quite similar to the forward port. It has access to its pads, and data busses running into the crosspoint array. Figure 5-6 shows a block diagram of the datapath.

There are a few circuits in the back port that require explanation. The use line is a status line which comes up out of the crosspoint array. It indicates that this output column was

grabbed by one of the eight forward ports, and that active data will be appearing during this cycle. Since the use signal is a dynamic precharged line, it is important that the back port only examine the value during the evaluate cycle (phi2). During the precharge (phi1) the value will of course be logic high. The clock-decoupler circuit is a latch which allows data to flow through during phi2, and holds the value during phi2 low.

The use signal is sent back down to the line control unit at the base of the output column. This allows the line control to decide whether to make the output column available for routing by other forward ports during the next cycle.

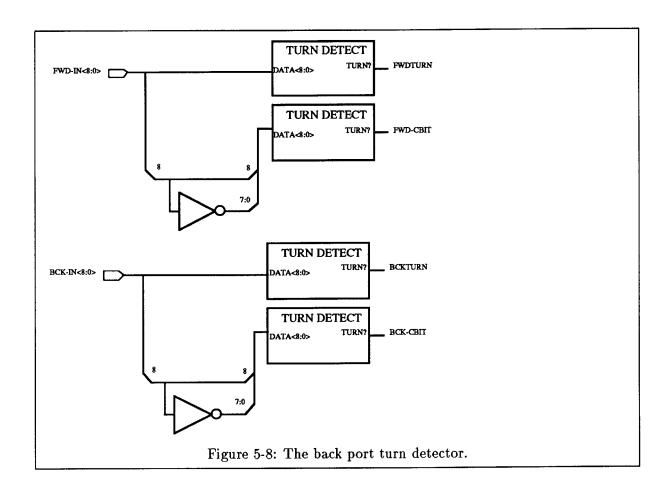

Unlike the forward port, there are two fully independent nine-bit busses in the back port for data coming off the back-port pads, bck-in<8:0>, and data coming from the crosspoint, fwd-in<8:0>. As noted earlier, this is probably the right model for the forward port as well. Perhaps someone will take this to heart in the next design of the switch chip.

#### 5.3.1 Back Port State Machine

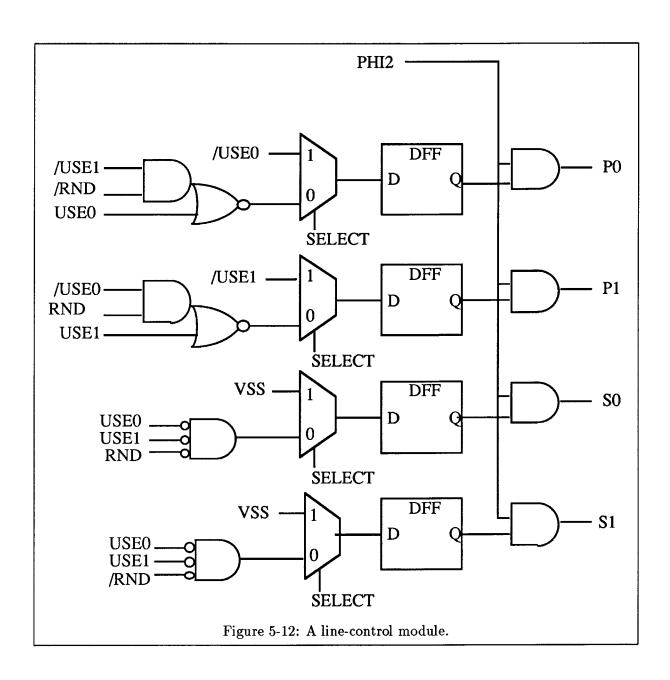

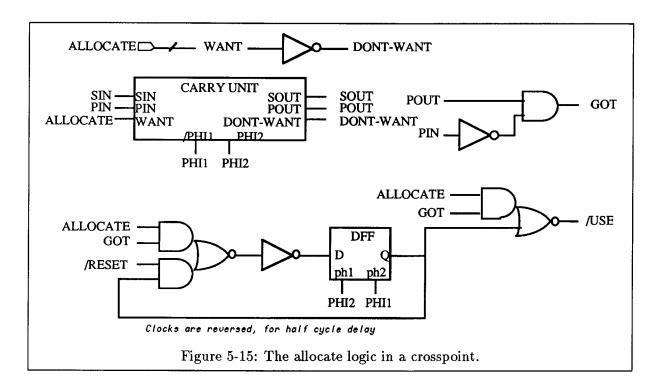

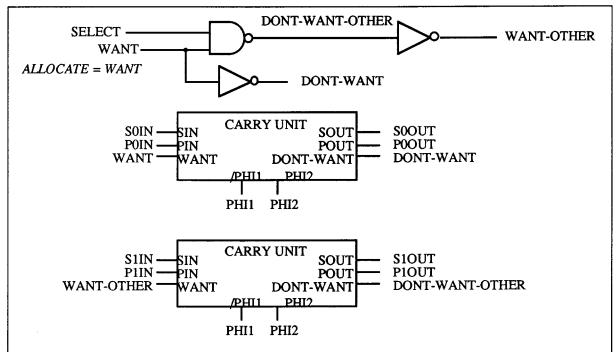

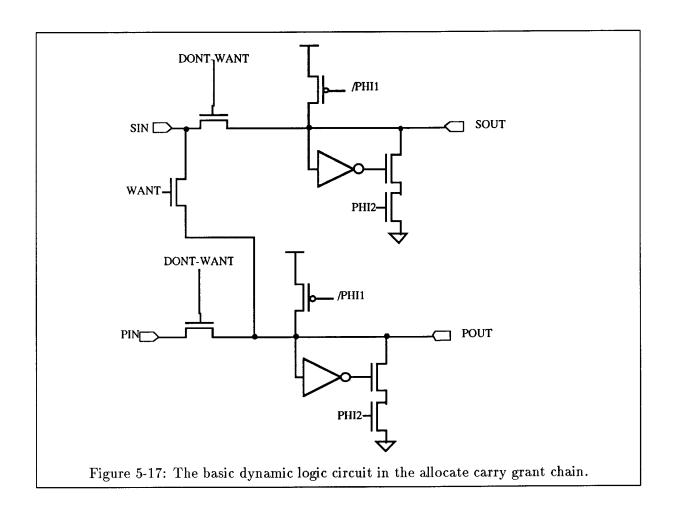

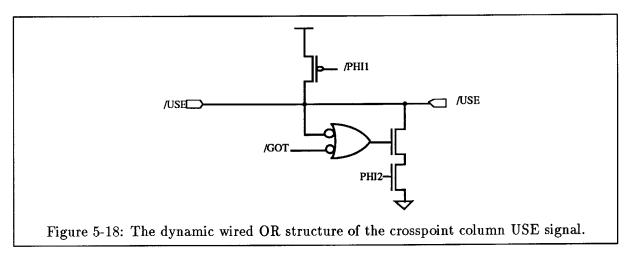

The back port state machine, out-fsm-std, is slightly simpler than the forward port state machine. It mainly has the task of watching for use, turn, or drop signals on the fwd-in or bck-in busses. The state transition diagram is shown in Figure 5-7.