# Asymptotically Zero Energy Computing Using

#### Split-Level Charge Recovery Logic

by

#### Saed G. Younis

S.B. Electrical Engineering, Massachusetts Institute of Technology (1986) M.S. Electrical Engineering and Computer Science, Massachusetts Institute of Technology (1989)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1994

© Massachusetts Institute of Technology 1994

Thesis Supervisor: Thomas F. Knight, Jr.

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY ARTIFICIAL INTELLIGENCE LABORATORY

A.I. Technical Report No. 1500

June, 1994

#### Asymptotically Zero Energy Computing Using Split-Level Charge Recovery Logic

Saed G. Younis younis@ai.mit.edu

Abstract: The dynamic power requirement of CMOS circuits is rapidly becoming a major concern in the design of personal information systems and large computers. In this work we present a number of new CMOS logic families, Charge Recovery Logic (CRL) as well as the much improved Split-Level Charge Recovery Logic (SCRL), within which the transfer of charge between the nodes occurs quasistatically. Operating quasistatically, these logic families have an energy dissipation that drops linearly with operating frequency, *i.e.*, their power consumption drops quadratically with operating frequency as opposed to the linear drop of conventional CMOS. The circuit techniques in these new families rely on constructing an explicitly reversible pipelined logic gate, where the information necessary to recover the energy used to compute a value is provided by computing its logical inverse. Information necessary to uncompute the inverse is available from the subsequent inverse logic stage. We demonstrate the low energy operation of SCRL by presenting the results from the testing of the first fully quasistatic  $8 \times 8$  multiplier chip (SCRL-1) employing SCRL circuit techniques.

Acknowledgements: This report describes research done at the Artificial Intelligence Laboratory of the Massachusetts Institute of Technology. Support for the Laboratory's Artificial Intelligence Research is provided in part by the Advanced Research Projects Agency under Office of Naval Research contract N00014-91-J-1698 and DABT63-92-C-0039.

#### Acknowledgments

In consulting with Tom Knight throughout this work, many a times I was the recipient of the following advice

"... of course you can do it that way, but if I was doing it I would..." and many a times I went my own way. On reflection, I wish that for the most part, I had not. When it comes to technical intuition of the kind that usually turns out to be true, Tom Knight seems to have an enviable supply. I'm thankful for having worked with him technically and grateful for having known him personally.

I wish to thank Gregory Papodopoulos and Kim Molvig for their commitment and support of this work.

I would also like to thank members of toms-knights group including Sir Philip Alvelda, Sir Mike Bolotski, Sir Andre Dehon and Sir Tom Simon for their instrumental help during the design of SCRL-1.

Special thanks to Andy Boughton and Jack Costanza for their generosity, and friendship during the testing of SCRL-1 chip and throughout my hacking days at MIT.

This research is supported in part by the Defense Advanced Research Projects Agency under contract N00014-91-J-1698 and DABT63-92-C-0039

### Contents

| Ι | Int  | roduction and Background                               | 1  |

|---|------|--------------------------------------------------------|----|

| 1 | Intr | roduction                                              | 2  |

|   | 1.1  | New Ideas, Old Physics                                 | 2  |

|   | 1.2  | Quasistatic Switching                                  | 2  |

|   | 1.3  | What is Reversible Logic                               | 4  |

|   | 1.4  | Temporal Reversibility                                 | 4  |

|   | 1.5  | Diode Based Proposals                                  | 5  |

|   | 1.6  | Charge Sharing versus Quasistatic Operation            | 6  |

|   | 1.7  | Logic Families and Universality                        | 6  |

|   | 1.8  | Contributions of this Work                             | 6  |

| 2 | Qua  | asistatic Switching in CMOS                            | 8  |

|   | 2.1  | Introduction                                           | 8  |

|   | 2.2  | Energy Dissipation in CMOS                             | 8  |

|   |      | 2.2.1 Dissipation Due to Leakage                       | 8  |

|   |      | 2.2.2 Dissipation due to $V_{dd}$ to $V_{ss}$ Shorting | 9  |

|   |      | 2.2.3 Dynamic Dissipation                              | 9  |

|   | 2.3  |                                                        | 10 |

|   |      |                                                        | 11 |

|   |      | 2.3.2 Multiple Capacitive Loads                        | 11 |

|   |      |                                                        | 13 |

|   | 2.4  |                                                        | 14 |

|   | 2.5  |                                                        | 15 |

|   |      |                                                        | 15 |

|   |      | 2.5.2 Generator Dissipation for Sinusoidal Ramps       | 19 |

|   |      |                                                        | 21 |

|   |      |                                                        | 21 |

|   | 2.6  |                                                        | 21 |

|   |      |                                                        | 22 |

|   |      |                                                        | 23 |

|   | 2.7  | <u> </u>                                               | 23 |

|   |      |                                                        | 24 |

|   |      |                                                        | 24 |

|   |      | <del>-</del>                                           |    |

|    |      | 2.7.3 Micromechanical Switch                           | 26        |

|----|------|--------------------------------------------------------|-----------|

|    | 2.8  | Zero Energy Computing and Reversibility                | 28        |

|    | 2.9  | Summary                                                | 28        |

|    |      |                                                        |           |

| II | De   | evelopment of Charge Recovery Logic                    | 29        |

| 3  | Ear  | ly Implementations of Charge Recovery Logic            | 30        |

|    | 3.1  | Introduction                                           | 30        |

|    | 3.2  | Fully-Symmetric CRL Implementation                     | 30        |

|    |      | 3.2.1 Fully-Symmetric CRL Gate                         | 30        |

|    |      | 3.2.2 Reversible Pipeline of Fully-Symmetric CRL       | 33        |

|    | 3.3  | N-Channel CRL                                          | 36        |

|    |      | 3.3.1 N-Channel CRL Gate                               | 36        |

|    |      | 3.3.2 N-Channel CRL Reversible Pipeline                | 40        |

|    | 3.4  | Dynamic Considerations and Nonlinearities              | 40        |

|    | 3.5  | Spice Simulation                                       | 41        |

|    | 3.6  | Circuit Example                                        | 41        |

| 4  | Spli | t-Level Charge Recovery Logic                          | 44        |

|    | 4.1  | Introduction                                           | 44        |

|    | 4.2  | Split-Level CRL Gate                                   | 44        |

|    | 4.3  | Reversible Pipeline Connection and Timing              | 45        |

|    | 4.4  | SCRL Clocking Variants                                 | 47        |

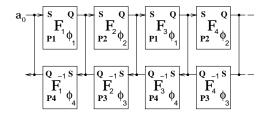

|    |      | 4.4.1 Two-Phase SCRL                                   | 47        |

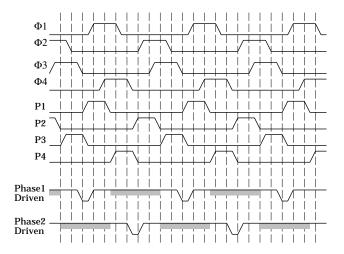

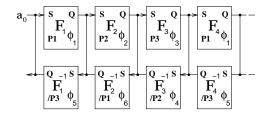

|    |      | 4.4.2 Three-Phase SCRL                                 | 48        |

|    | 4.5  | Non-Inverting Stage                                    | 49        |

|    | 4.6  | External Inductors                                     | 51        |

|    | 4.7  | Spice Simulation                                       | 51        |

|    | 4.8  | Lowering Irreversibility Cost                          | 52        |

|    |      | 4.8.1 Irreversibility Is Not Free                      | 52        |

|    |      | 4.8.2 Statistically Controlled Irreversibility         | 53        |

|    |      | 4.8.3 Where to Break Reversibility                     | 53        |

|    |      |                                                        |           |

| II | I I  | mplementation and Testing of SCRL-1 Demonstration Chip | <b>54</b> |

| 5  | Den  | nonstration Chip Details                               | 55        |

|    | 5.1  | Introduction                                           | 55        |

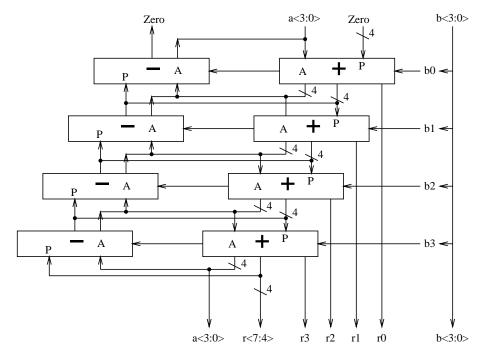

|    | 5.2  | High Level Multiplier Design                           | 55        |

|    | 5.3  | Multiplier Details                                     | 57        |

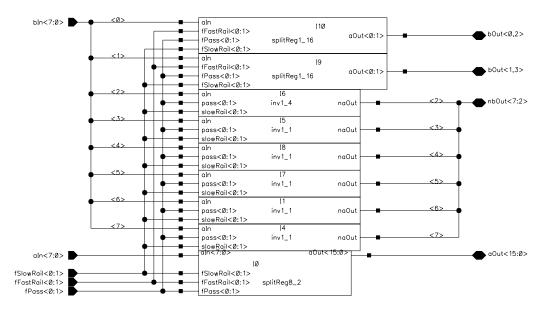

|    |      | 5.3.1 Reversible Level 1                               | 58        |

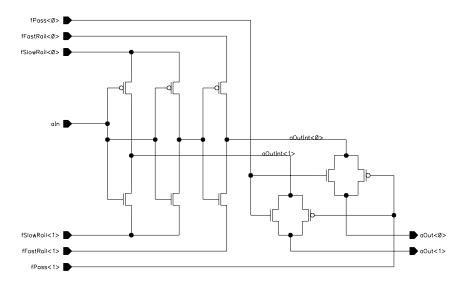

|    |      | 5.3.2 Reversible Level 2                               | 60        |

|    |      | 5.3.3 Reversible Level 3                               | 63        |

|              |                          | 5.3.5 Reversible Level 9      | 54<br>54<br>54 |

|--------------|--------------------------|-------------------------------|----------------|

|              |                          | 5.3.7 Reversible Level 11     | 66             |

|              |                          |                               | 57<br>57       |

|              |                          |                               | 8              |

|              | 5.4                      | Input Pads                    | 9              |

|              |                          | 1                             | 0              |

|              |                          | <u> </u>                      | '0<br>'0       |

|              | 5.5                      |                               | 0              |

|              | 5.6                      |                               | 1              |

|              | 5.7                      | Design Entry and Verification | '3             |

| 6            | Tes                      | t and Measurement Results 7   | 4              |

|              | 6.1                      |                               | 4              |

|              | 6.2                      | 9                             | 4              |

|              | 6.3                      |                               | '4<br>'5       |

|              | 6.4                      |                               | 6              |

|              |                          |                               | 6              |

|              |                          | 0 1                           | 9              |

|              | 6.5                      |                               | 30             |

|              | 6.6                      |                               | 31<br>32       |

|              |                          |                               | 33             |

|              |                          |                               | 34             |

|              |                          | 1                             | 34             |

|              |                          | 1 0                           | 86             |

|              | 6.7                      | Summary                       | 88             |

| IV           | $^{\prime}$ $\mathbf{F}$ | uture Research Areas 8        | 9              |

| 7            |                          |                               | 0              |

|              | $7.1 \\ 7.2$             |                               | 00<br>00       |

|              | 7.3                      |                               | )1             |

|              | 7.4                      |                               | 1              |

|              | 7.5                      | SCRL Circuit Improvements     | 1              |

| $\mathbf{A}$ |                          |                               | 3              |

|              | A.1                      | CRL and Large Systems at LNT  | 3              |

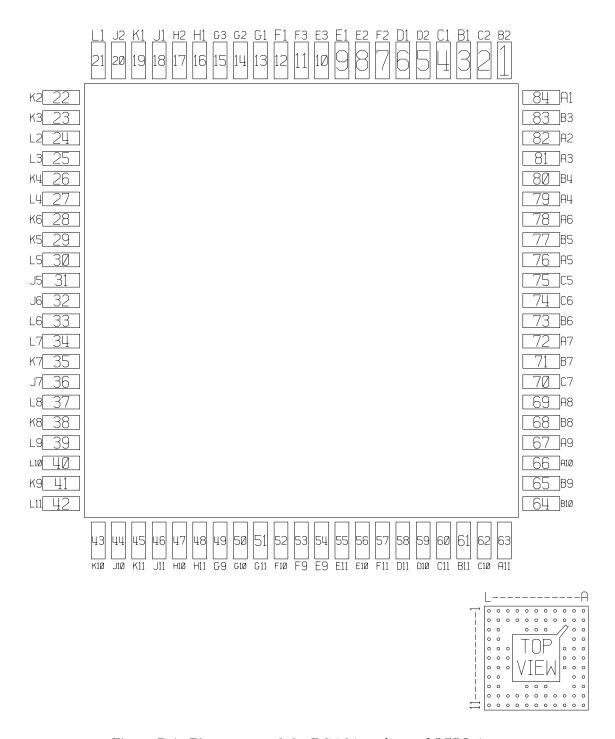

B SCRL-1 Pinout 99

## List of Figures

| 2.1  | Energy analysis model of CMOS circuits                                                          | 9  |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.2  | Normalized power dissipation plot for a voltage step, solid line, and for a                     |    |

|      | current step, dashed line.                                                                      | 12 |

| 2.3  | Model of CMOS circuit with separate driving current sources                                     | 12 |

| 2.4  | Model of CMOS circuit with common driving current source                                        | 12 |

| 2.5  | Voltage waveform at the terminals of a constant current source driving a                        |    |

|      | capacitive load $C$                                                                             | 13 |

| 2.6  | The two places of system dissipation                                                            | 15 |

| 2.7  | Conventional and non-dissipative circuit analysis models                                        | 16 |

| 2.8  | Plot of $V_c(t,\omega_d)$ showing the effect of fast rise and fall times on energy loss.        | 17 |

| 2.9  | (a) Linear plot of $F_{saving}$ factor vs. $\omega_d$ . (b) Log-Log plot of $F_{saving}$ factor |    |

|      | vs. $\omega_d$ . In both plots $\omega_d$ is normalized to $\omega_{d max}$                     | 19 |

| 2.10 | Typical stepwise ramp generator circuit driving a capacitive load $C_L$                         | 22 |

| 2.11 | Model of a CMOS computing circuit driven by a stepwise source                                   | 22 |

| 2.12 | Schematic diagram of a simple Electroquasistatic Micromechanical switch                         | 27 |

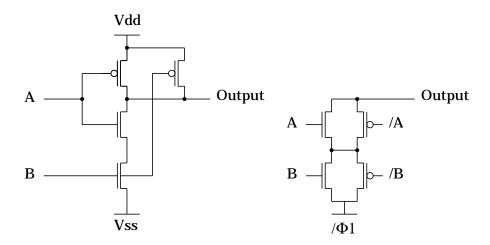

| 3.1  | Conventional NAND gate and an early attempt at a CRL NAND gate                                  | 30 |

| 3.2  | Modified gate with dual-rail added                                                              | 31 |

| 3.3  | The universal CRL NAND gate                                                                     | 32 |

| 3.4  | Completed CRL NAND gate with pipelining support                                                 | 33 |

| 3.5  | First CRL implementation with output cross-coupled clamps                                       | 34 |

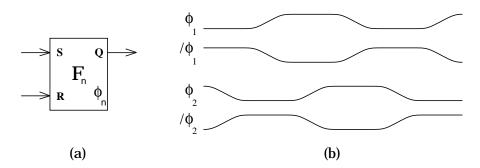

| 3.6  | (a) CRL abstraction box. (b) Timing of the four clock rails                                     | 34 |

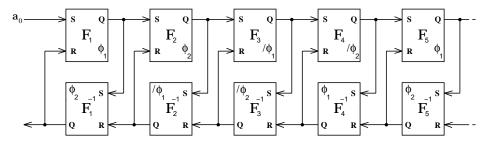

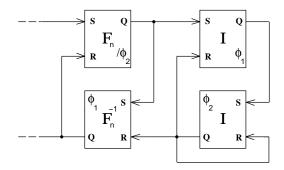

| 3.7  | Non-dissipative multi-stage pipeline connection                                                 | 35 |

| 3.8  | Last pipeline stage connection for dissipation reduction                                        | 36 |

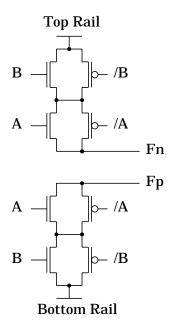

| 3.9  | Schematic diagram of a 2-Input AND/NAND N-Channel CRL gate                                      | 37 |

| 3.10 | Timing of the fast rails in N-Channel CRL                                                       | 38 |

| 3.11 | Schematic diagram of an N-Channel CRL gate that rests at $V_{ss}$                               | 38 |

| 3.12 | Schematic diagram of an N-Channel CRL gate that rests at $V_{dd}$                               | 39 |

| 3.13 | N-Channel CRL gate with latch-up protection devices                                             | 39 |

| 3.14 | Schematic diagram illustrating the connection topology of a 1-cycle through-                    |    |

|      | put 3-bit CRL adder using fast carry-save implementation                                        | 42 |

| 4.1  | Split-Level CRL inverter.                                                                       | 44 |

| 4.2  | SCRL abstraction box                                                                            | 45 |

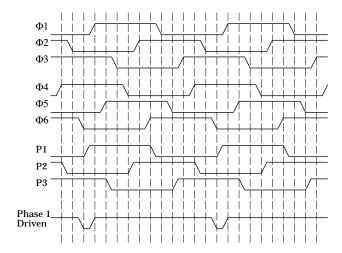

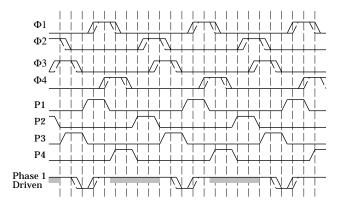

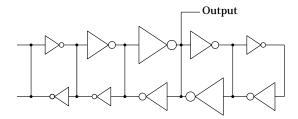

| 4.3  | Non-dissipative multi-stage pipeline connection                                    | 46  |

|------|------------------------------------------------------------------------------------|-----|

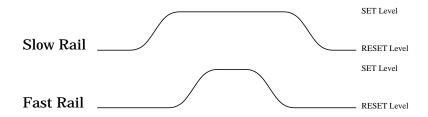

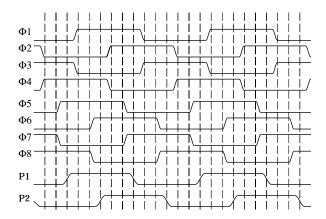

| 4.4  | Rail timing for 4 phase SCRL                                                       | 47  |

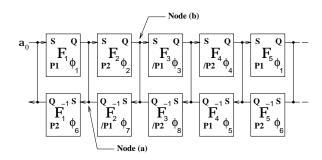

| 4.5  | Two-Phase SCRL pipeline                                                            | 48  |

| 4.6  | Rail timing for 2 phase SCRL                                                       | 48  |

| 4.7  | Three-Phase SCRL Pipeline                                                          | 49  |

| 4.8  | Rail timing for 3 phase SCRL                                                       | 49  |

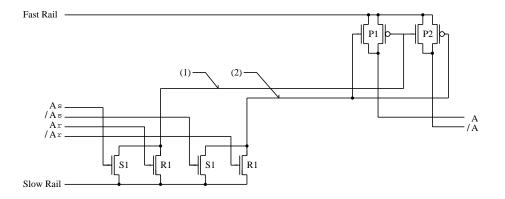

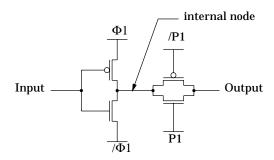

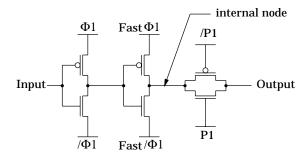

| 4.9  | Non-Inverting SCRL Gate                                                            | 50  |

| 4.10 | Timing diagram of Two-phase SCRL with fast rails for non-inverting stages.         | 51  |

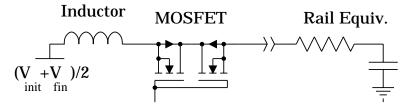

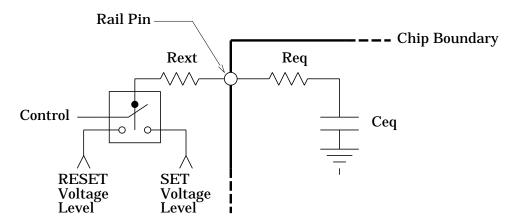

| 4.11 | Inductive rail driver circuit                                                      | 52  |

| 4.12 |                                                                                    | 53  |

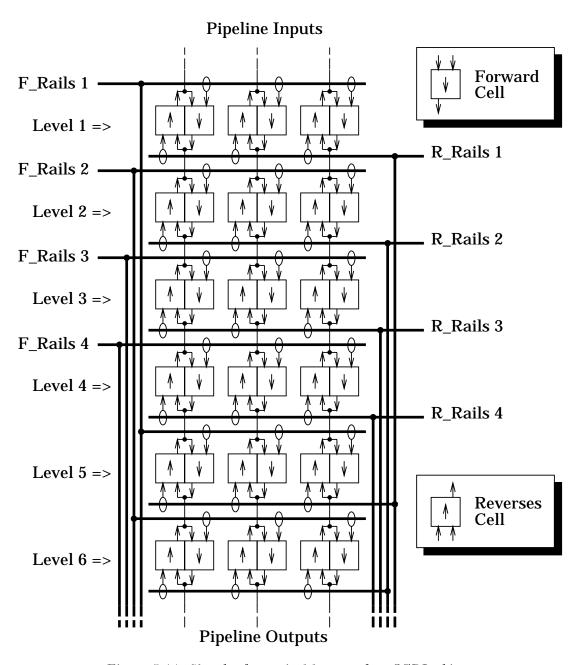

| 5.1  | Block diagram of a 4-Bit SCRL multiplier                                           | 56  |

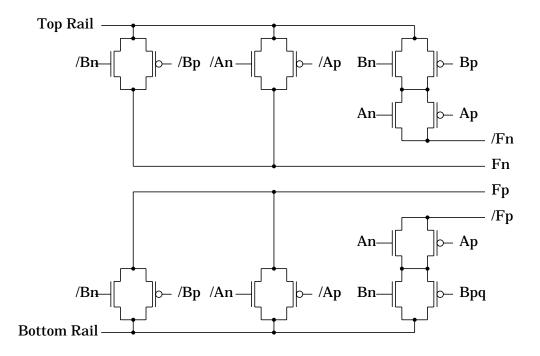

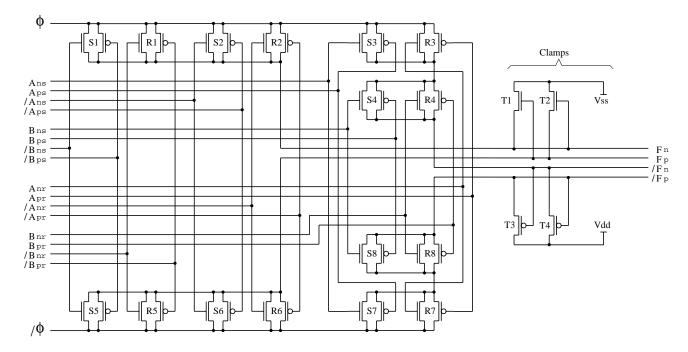

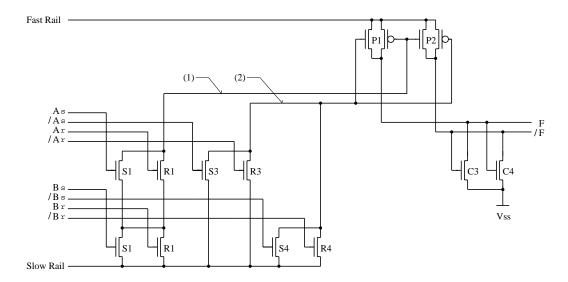

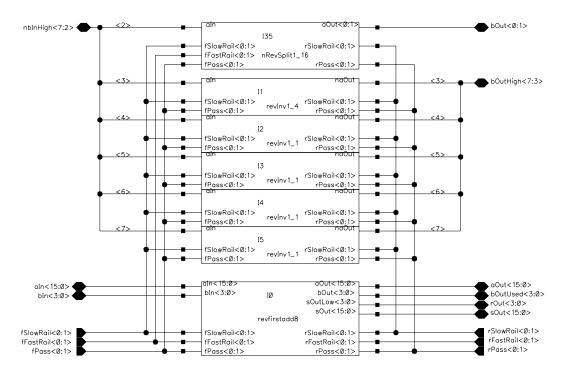

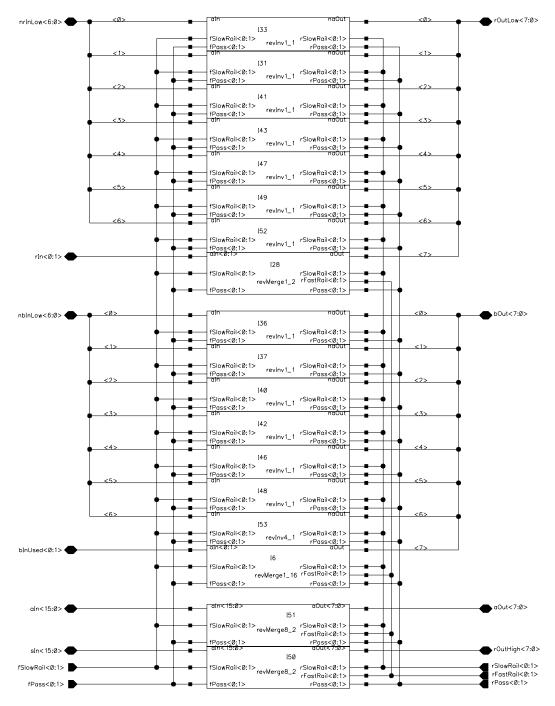

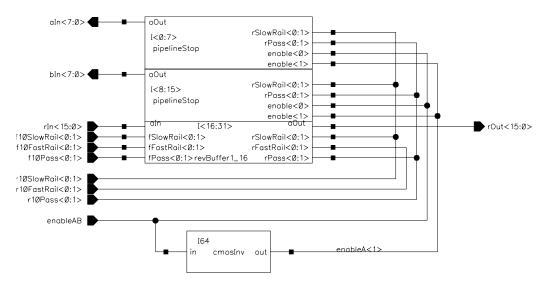

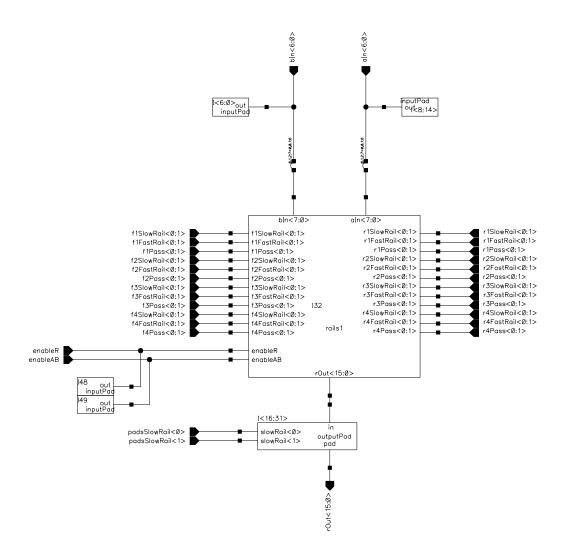

| 5.2  | Schematic diagram of reversible level 1                                            | 59  |

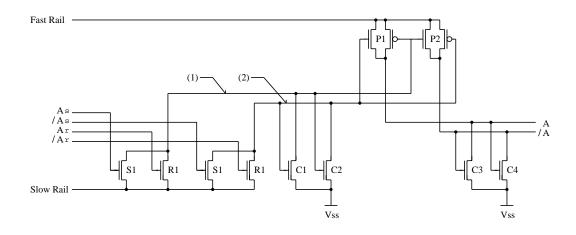

| 5.3  | Schematic diagram of splitReg1_16 module                                           | 59  |

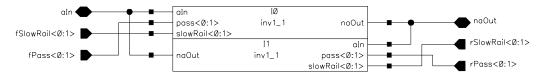

| 5.4  | Schematic diagram of reversible level 2                                            | 61  |

| 5.5  | Schematic diagram of revInv1_1 module                                              | 61  |

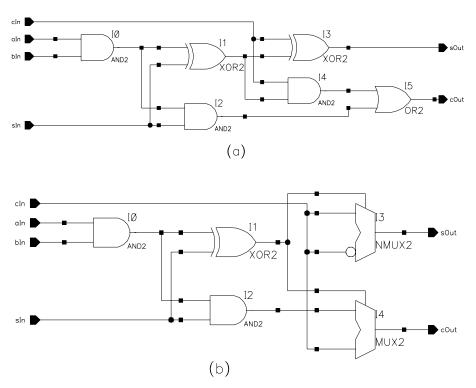

| 5.6  | (a) Schematic Diagram of a generic 1-bit propagate-generate full adder. (b)        |     |

|      | Diagram of the 2-level 1-bit adder that are used in SCRL-1 chip                    | 62  |

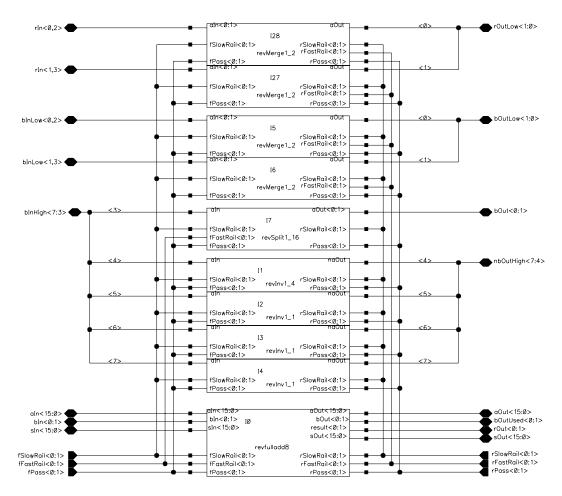

| 5.7  | Schematic diagram of reversible level 3 module                                     | 63  |

| 5.8  | Schematic diagram of reversible level 9 module                                     | 65  |

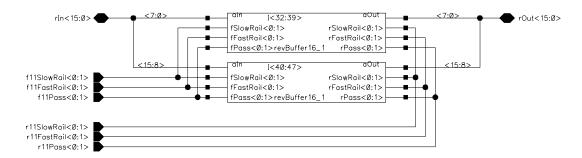

| 5.9  | Schematic diagram of reversible level 10 module                                    | 66  |

| 5.10 | Schematic diagram of reversible level 11 module                                    | 67  |

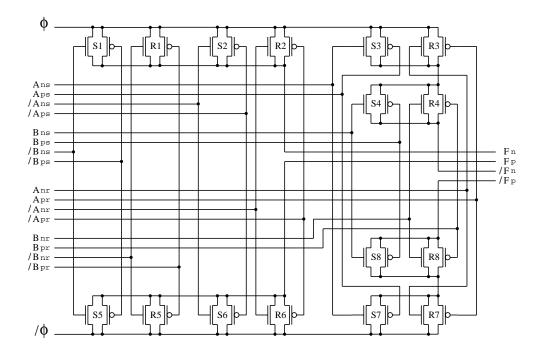

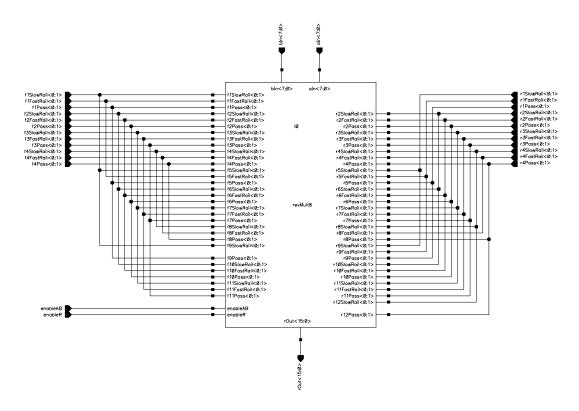

| 5.11 | Schematic diagram illustrating the connection of the rails in SCRL-1               | 68  |

| 5.12 | Schematic diagram illustrating the I/O connections in SCRL-1                       | 69  |

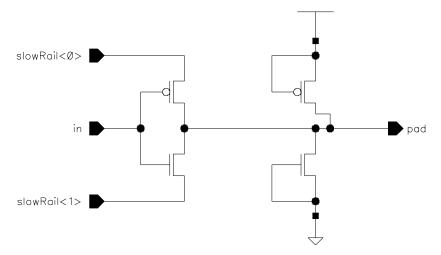

| 5.13 | Schematic diagram of SCRL-1 output pad circuit                                     | 71  |

| 5.14 | Sketch of a typical layout of an SCRL chip                                         | 72  |

| 6.1  | Block diagram the high speed DAC module                                            | 77  |

| 6.2  | Block diagram of the components of the $RC$ -controlled voltage step testing       |     |

|      | approach                                                                           | 79  |

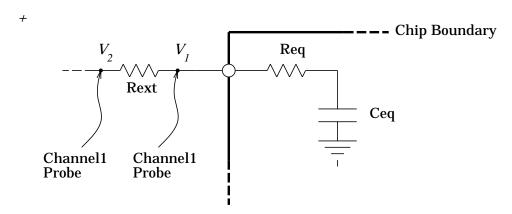

| 6.3  | Scope probe locations during energy dissipation measurement                        | 81  |

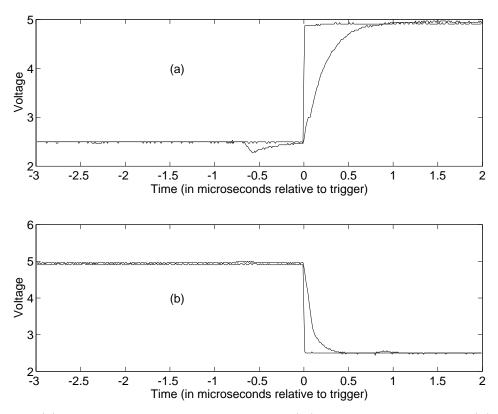

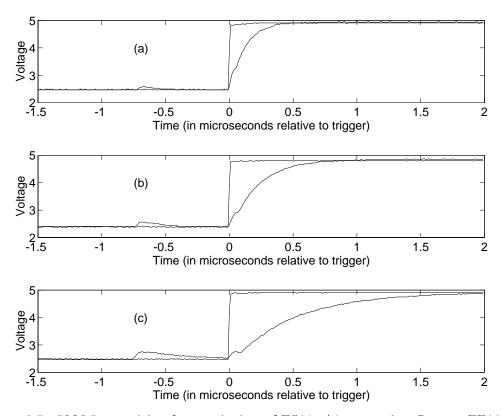

| 6.4  | (a) Scope trace of the rise time of FF1(+) with $2777.5\Omega$ resistor. (b) Scope |     |

|      | trace of the rise time of FF1(+) with $2777.5\Omega$ resistor                      | 85  |

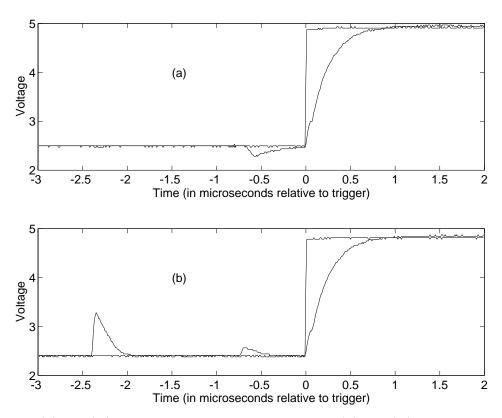

| 6.5  | (a) FF1(+) waveform under SCRL operation. (b) FF1(+) waveform with                 |     |

|      | the reverse pipeline disabled                                                      | 86  |

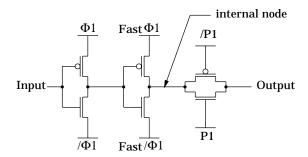

| 6.6  | Non-Inverting SCRL Gate                                                            | 86  |

| 6.7  | CMOS capacitive from swinging of FS1(+/-) at varying $R_{ext}$ on FF1(+).          | 87  |

| B.1  | Pinout map of the PGA84 package of SCRL-1                                          | 100 |

## List of Tables

| 6.1 | Energy measurements for rail $FF1(+)$ in $SCRL-1$        | 83 |

|-----|----------------------------------------------------------|----|

| 6.2 | Energy measurements for rail FF3(-) and RF4(-) in SCRL-1 | 84 |

# $$\operatorname{Part} \ I$$ Introduction and Background

#### 1.1 New Ideas, Old Physics

In principle, a computing engine need not dissipate any energy as shown in the work of Bennett, Feynman, and Landauer [3] [11] [27]. Although these authors approach the problem from different disciplines and use different physical as well as theoretical models, they all conclude that the transfer of energy through a dissipative medium dissipates arbitrarily small amounts of energy if that transfer is made sufficiently slowly.

In CMOS based circuits, the node voltages represent one of two logical values. During operation, the logical values of these nodes, and their voltage levels, repeatedly toggle between the two valid levels. Given the capacitances of these nodes, we can view performing computation using CMOS circuits as moving charge from one node to another. In other words, to perform useful work in CMOS, we are continuously forced to place and remove charge from various nodes in the circuit. Charge transfer between nodes of differing potentials is similar to shuttling heat between two heat baths at differing temperatures.

Thermodynamically, we know that all real energy transfer operations are invariably irreversible. Fortunately, however as much an idealization reversible processes are, they are still of extreme importance since it is possible in many situations to achieve them to a very high degree of approximation.

As an example, it is possible to shuttle energy between two heat baths at different temperatures while losing arbitrarily small amounts of energy. This is done by inserting an infinite number of heat baths between the two original ones such that the temperature difference between any two adjacent baths becomes infinitesimally small. Shuttling heat packets reversibly between the baths at the two extremes following this gradual temperature staircase results in arbitrarily small energy loss.

In general, if lossless reversibility is to be achieved, a process must be carried out at a slow enough rate so that in effect, the system is always in equilibrium. In this light, the reversible process may be regarded as a series of *quasistatic changes* along a sequence of neighboring equilibrium states.

#### 1.2 Quasistatic Switching

Currently the power consumption of CMOS circuits drops linearly with lower operating frequency. This means that the energy consumed per cycle is constant since the cycle is inversely proportional to frequency. Typically in CMOS, each cycle contains the same amount of computational work and on the average the same amount of charge shuttling. This suggests that in conventional CMOS, the energy consumed per charge movement is always constant. This is analogous to the the worst case scenario in our thermal example in which there were no additional intermediate thermal baths and the transfers between

the two baths were done in one step. The reason for the high dynamic dissipation of conventional CMOS is the fact that charge transfer within them happens abruptly, *i.e.*, not quasistatically. The time constant associated with charging a gate through a similar transistor is RC, where R is the ON resistance of the device and C its input capacitance. However, the cycle time can be, and usually is, much larger than RC. An obvious conclusion is that energy consumption can be reduced by spreading the transitions over the whole cycle thus making them closer to quasistatic processes rather than "squeezing" them all inside one RC.

To asymptotically reduce the energy dissipation in CMOS all of the charge movements through the circuits must proceed quasistatically. To achieve this quasistatic operation, one has to guarantee absolute adherence to two conditions. The first is to guarantee that charge flow between any two nodes in the circuit occurs in a gradual and externally controlled manner. This means that we forbid any device in our circuit from turning on while there is a potential difference across it. It also means that once the device is turned on, the movement of charge through it must be done in a gradual and controlled manner so as to prevent a potential difference from developing. The second is to guarantee that the path followed by the charge does not contain any parts that violate quasistatic behavior. This means that the circuit should not contain any non-linear dissipative elements, e.g., diodes. Once these conditions are guaranteed, the dissipation could be set to a level or asymptotically reduced through external control of the rate of charge movement. This is true since the two conditions assure quasistatic energy transfer and it is only through that that asymptotic energy reduction is possible. We want to state here that there is no way to guarantee the two conditions stated above without employing reversible logic.

In a CMOS circuit, we can always determine and control the potential on one side of a CMOS device since it is usually connected to a power supply rail. The potential on the other side, however, depends solely on the result of the computation. To perform a non-dissipative transition of the output, we must know the state of the output prior to and during this output transition. The reason for the need to know the previous state of a node before moving it is quite simple. Suppose that we needed to set the voltage on an internal node to  $V_{dd}$ . To do it quasistatically, we connect it to a rail that is currently at the same voltage, then we slowly ramp the voltage on the rail to  $V_{dd}$ , setting the voltage on the internal node to  $V_{dd}$  in the process. If the node was at GND, our rail would swing from GND to  $V_{dd}$ . In contrast, if the node was at  $V_{dd}$ , we would connect the node to a rail that is always anchored to  $V_{dd}$ . To determine which rail to connect to, we have to know the previous value as well as the desired final value of the node voltage. Furthermore, we have to hold on to this information throughout the transition. Stated more clearly, to non-dissipatively set the state of the output we must at all times have a copy of it. The only way out of this circle is to use reversible logic.

Recent and independent work by Hall [16] and Merkle [33] showed how to connect Retractile Cascade stages to eliminate the power dissipation in the latches that were used to hold on to past values. These two proposals are worthy of note since they are the only ones that conform to the two conditions of quasistatic operation outlined above, however both proposals were rather sketchy when it came to the details of the physical implementation of their proposed logic.

#### 1.3 What is Reversible Logic

Reversible logic is a way to perform computation where information entropy is strictly conserved, or in some implementations mostly conserved. In our context we define constant information entropy as always keeping enough information around to be able to accurately retrace all the events, or steps, of the past. The main drive for implementing reversible logic is that of drastically reducing the energy dissipation of computing circuits. As is widely established by now, information entropy and thermodynamic entropy are linked. One cannot increase information entropy without dissipating energy. Fortunately the reverse is just as true. That is, if information entropy is not increased, it is theoretically possible, and as shown here practical, to perform computation while dissipating asymptotically vanishing amounts of energy if the computation is carried out asymptotically slowly. A trivial way of not increasing the information entropy of the system would be to store a copy of every transaction of the system forever. This obviously requires an infinite amount of storage space. A more practical approach to maintaining constant information entropy would be to undo, or reverse, the effect of a computation once the results of that computation had been utilized, i.e., to perform reversible logic operations. To resign oneself to perform computation reversibly, is to empower oneself to perform them while dissipating orders of magnitude less energy than would be dissipated by conventional methods. This is because reversible computation provides us with the needed information to make the correct connection to the restoring swinging rail and thus allows us to restore nodes quasistatically. We define the term asymptotic energy reduction as the ability to perform a computation while consuming asymptotically less and less energy as the computation is performed slower and slower with no theoretical limit on how small the consumption can get. If there was a limit, we do not consider that operation to be asymptotic in energy reduction. In other words, the theoretical line for energy dissipation associated with the process must in the limit reach zero.

It is the fact that dissipation could be reduced by orders of magnitude using reversible logic that convinced us of the need for it. We note here that reversible logic is less restrictive than conservative logic that was proposed by Fredkin and Toffoli in [13]. In addition to preserving the information content, conservative logic also preserves the total number of ones and zeros of the system. As it turns out, conservative logic simplifies some mechanical implementation of reversible logic, due to its dual polarity signaling. However, only reversibility is needed for reducing the energy consumption. In a sense our implementations share their reversible aspect with the reversible and conservative Fredkin gate. Our implementations however differ in their lack of conservation for ones and zeros.

Intuitively, and in contrast to the above, a circuit that has no means of computing the logical inverses of its functions has no means of preserving the information content of its nodes and hence should not be thought of as reversible logic.

#### 1.4 Temporal Reversibility

A number of other proposals sought to lower the energy dissipation by charging and discharging the internal nodes of their circuits in a gradual and controlled manner. In their

work, Koller and Athas [26] were largely concerned with reducing the energy consumption of bus drivers. Since in their circuits, the input to the bus driver was held stable during the SETting and RESETting of the gate, reversibility was in effect performed temporally and hence they were able to achieve asymptotic energy reduction for their bus driver without needing reversible logic. The key here is that the circuit holding the input stable during SETting and RESETting of the rails provided the "infinite storage space" within which the history of the computation is recorded. Koller and Athas however, correctly recognized and reported that when the entire circuit was considered, there was an unavoidable energy dissipation in the pipeline registers. This of course was a consequence of not being able to satisfy the first condition in the pipeline registers due to the absence of reversible logic. We do acknowledge that achieving asymptotic energy reduction in selective parts of the circuit as Koller and Athas have demonstrated could go a long way towards reducing the power consumption of a system. But we note however that the reduced energy consumption would have a lower bound.

#### 1.5 Diode Based Proposals

Previously, we stated the importance of knowing the previous value of a node while we are affecting it in order to achieve quasistatic switching of that node. The previous value was needed so that we can make the correct decision of which rail to connect the node to in order to affect quasistatic charge transfer. A simple diode can however correctly make that decision for us. Recently two separate proposals have been forwarded that achieve energy reduction in CMOS circuits through using diodes. The first is by Denker et al. [9] while the second is by Hinman and Schlecht [17]. Using a diode however violates the second of the two condition we have stated above. The fact is that charge transfer in a forward biased diode is not a quasistatic process even if the charge transfer proceeds slowly.

This becomes evident when we trace the path of an electron through the diode. In a forward biased diode, the energy of electrons on the N side of the P-N junction is elevated by the forward voltage to a level that permits them to overcome the built-in potential barrier and diffuse over to the P side of the junction. Once on the P side, they rapidly fall down the potential hill to equalize with the energy of the electrons on the P side. It is this rapid and uncontrollable falling down the potential hill that is not quasistatic in the P-N junction. The fact that the "height" of the fall is always constant irrespective of the rate at which charge is allowed to flow through the diode is the reason for the constant and nonlinear value of the diode's  $V_{be}$ . From this we see that charging a node with a capacitance C through a diode dissipates an amount of energy,  $E_{diode}$  that is equal to  $CV_{dd}V_{be}$ , where  $V_{be}$  is the forward potential drop of the diode. At best, diode based methods can reduce the energy consumption by a factor equal to  $V_{dd}/V_{be}$ . This puts a limit on the energy reduction ratio over conventional CMOS circuit, usually no more than 10. Further, with the current technology push to reduce  $V_{dd}$  for CMOS circuits, in some cases below 200mV [4], the energy saving factor of diode based circuits will only get smaller or disappear entirely.

#### 1.6 Charge Sharing versus Quasistatic Operation

Some of the proposed low energy circuits techniques suffer from allowing charge sharing among the internal nodes, which violates the first condition for quasistatic operation.

I stress here that the construction of quasistatic circuits should at all cost avoid charge sharing among the internal nodes since with charge sharing, the energy saving over conventional CMOS could easily be wiped out for all but the simplest of circuits. The point behind quasistatic switching is to recover most of the energy that at one point was deposited on the internal nodes of the circuit. Except for simple circuits, the effective capacitance of the internal nodes of a circuit becomes comparable to the capacitance of the output node. To allow charge sharing to occur on the internal nodes, is to allow a large and undetermined amount of the stored energy to be wasted. This could be as high as 50% of the total charge leading to a poor energy saving factor of less than 2. Furthermore, the indeterminacy of energy loss reflects itself in a variable effective capacitance of the circuit thus nullifing the advantage of constant supply capacitance that is provided by dual polarity designs.

#### 1.7 Logic Families and Universality

For a circuit technique to be classified as a computing logic family, it must be universal. This means that it should contain at least one member that is non-monotonic and it must support negation. This is usually overlooked by new proposals for low energy circuits. As we have illustrates in a paper published earlier [41] and will revisit again in Section 3.2.1, initial attempts at quasistatic circuits usually need augmentation in order to support logical negation and hence be eligible to be considered a logic family. In practice new proposals that do not attempt to construct multiple stage pipelines with stages that are more complex than simple buffers or inverters do not detect the absence of universality in their "logic families". A powerful check to see if a new computing circuit technique is universal is to try and design a circuit that takes in a logical value at its input and that is able at a later stage in the pipeline to produce both the true and the complement copies of that input. Furthermore the circuit must be able to have them arrive simultaneously at a given stage in the pipeline. The power of this test is that in quasistatic circuits, one cannot insert an inverter inline with a signal to get its complement, as is frequently done in CMOS. An inserted gate would also have to be a controlled pipeline stage and that forces the proposed circuit technique to fail the test I have outline above. Experience will show that proposed logic families passing this test, are universal.

The subject of this work is to try and apply the principles of reversible logic to CMOS circuits to achieve full quasistatic operation throughout the system and thus significantly reduce its energy consumption.

#### 1.8 Contributions of this Work

In this document I present a number of new techniques for constructing non-dissipative quasistatic CMOS circuits. We feel that these techniques have a number of distinct advantages which warrant their use in future circuits.

In Section 2, I start by examining the ways in which the energy consumed for each charge transfer in CMOS circuits is made arbitrarily small as the process proceeds quasistatically. Initially, I will start by examining the energy dissipation mechanisms in CMOS circuits. I will then attempt to analyze them more closely to identify ways in which charge transfer, and hence computation, can be done quasistatically. The discussion will include the dissipation in the computing circuits as well as the dissipation caused by the action of the semiconductor switches in the power supplies of the system.

In Section 3, I describe a number of early implementations of Charge Recovery Logic (CRL) circuits. The common property of all of these circuits is their ability to do computations quasistatically thus consuming arbitrarily small amounts of energy when clocked sufficiently slowly. The discussion will include both Fully-Symmetric CRL as well as N-Channel CRL. It will also show how to string multiple CRL gates in a non-retracting pipeline [41]. Both Fully-Symmetric and N-Channel CRL were abandoned however in favor of our more recently discovered and much improved form of CRL which is examined in Section 4.

In Section 4, I present a much improved family of CRL called Split-Level CRL (SCRL). This form uses 2 times as many devices as conventional CMOS, requires only one wire for every signal, and actively drives all outputs during sampling. Further, I will show how to construct Split-Level CRL circuits using only 2 external inductors for every chip. SCRL serves as the corner stone of our research since we based our demonstration chip design on its techniques.

Conceptually, Split-Level CRL differs from earlier CRL in two ways. The first is the use of Split-Level voltages. The second is the elimination of the RESET devices and delegating the action of restoring the voltage on SET nodes to gates in the reverse pipeline. As in the previous Section, the discussion will include how to string multiple SCRL gates in a non-retracting pipeline [42].

The circuit techniques in these new CRL and SCRL logic families rely on constructing an explicitly reversible pipelined logic gate, where the information necessary to recover the energy used to compute a value is provided by computing its logical inverse. Information necessary to uncompute the inverse is available from the subsequent inverse logic stage.

To verify the quasistatic operation and behavior of Split-Level CRL, we have fabricated and tested an  $8\times 8$  CMOS multiplier chip, labeled SCRL-1, that employed the circuit techniques of Split-Level Charge Recovery Logic. In Section 5, I describe the design of this demonstration chip. Following that, in Section 6, I describe the measurement techniques and their results that verified the lower energy consumption of SCRL-1 as a consequence of quasistatic operation through reversibility.

To my knowledge, SCRL-1 is the first working implementation of a pipelined, reversible logic based, asymptotically zero energy circuit. As such, I am certain that there is a lot more for us to discover and refine than what we have reported so far. In Section 7, I try to give some suggestions about directions of future work that could further improve the applicability of SCRL. These include CAD and architecture issues, as well as the design of better quasistatic power supply switches. My opinion is that as far as quasistatic reversible computation is concerned, we've only just begun...

#### 2.1 Introduction

The subject of this section is to show ways in which the energy consumed per charge transfer is made arbitrarily small as the process proceeds quasistatically.

Initially, we will start by examining the energy dissipation mechanisms in CMOS circuits. We will then attempt to analyze them more closely to identify ways in which charge transfer, and hence computation, can be done quasistatically.

#### 2.2 Energy Dissipation in CMOS

As is widely known, the internal energy dissipation of conventional CMOS circuits is attributable to three major components. The first is due to the static leakage currents between the terminals of MOS devices. The second is due to the brief short between  $V_{dd}$  and  $V_{ss}$  during switching which is caused by both N-Channel and P-Channel devices being simultaneously ON for a brief time during a swing of  $V_{dd} \geq 2V_T$ . The third is due to the transient current associated with charging and discharging the gate capacitance C through a device with ON resistance R.

#### 2.2.1 Dissipation Due to Leakage

Dissipative leakage currents occur anytime circuit nodes at differing potentials are separated by slightly conductive mediums. Such dissipative "sandwiching" is present in a number of locations in CMOS circuits. These locations can be grouped according to their leakage mechanisms into two groups. The first is the leakage due to the reverse current of PN junctions. The second is the subthreshold conduction current between the source and drain of any MOS device.

The reverse current of a PN junction depends exponentially on temperature. Hence operating at lower temperatures greatly lowers this form of dissipation. In addition, a number of reversed biased junctions that are currently used for device isolation will become unnecessary with the advent of silicon-on-insulator fabrication technology (SOI).

The case for subthreshold conduction is more complicated. Increasing the threshold voltage of the devices in the circuit reduces subthreshold conduction, thus lowering quiescent power consumption. Unfortunately, this increases the ON resistance of the devices as the difference between  $V_T$  and the supply voltages decreases. To maintain the same speed performance, the devices must be made wider leading to higher dynamic dissipation. We will discuss dynamic dissipation in Section 2.2.3. Here, we stress the fact that in the case that subthreshold conduction becomes appreciable, we can trade some of it for higher

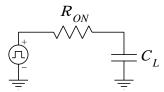

Figure 2.1: Energy analysis model of CMOS circuits.

dynamic dissipation. Having done that, this thesis will show how to significantly lower dynamic dissipation of CMOS circuits leading to lower overall energy dissipation.

#### 2.2.2 Dissipation due to $V_{dd}$ to $V_{ss}$ Shorting

During switching, a short occurs between  $V_{dd}$  and  $V_{ss}$  caused by both N-Channel and P-Channel devices being simultaneously ON for a brief time for swings where  $V_{dd} \geq 2V_T$  [5]. We can approximate this switching dissipation by

$$V_{dd} \times \frac{1}{2} \frac{V_{dd}}{2R} \times \frac{V_{dd} - 2V_T}{V_{dd}} \times 2RC \tag{2.1}$$

which for a typical  $V_{dd} = 4V_T$  simplifies to  $\frac{1}{4}CV_{dd}^2$ . As  $V_{dd}$  drops below  $2V_T$  this switching dissipation becomes negligible. Unfortunately, the transfer curve begins to exhibit hysteresis thus limiting the utility of the gate at these power supply voltages. In addition, operating with  $V_{dd} \leq 2V_T$  increases subthreshold conduction and increases propagation delays.

In Sections 3 and 4 we will see how this form of dissipation is completely eliminated in the family of CMOS circuits that we are proposing in this work.

#### 2.2.3 Dynamic Dissipation

It is widely known that the energy dissipation that is associated with charging and discharging the node capacitance, C, of a CMOS gate through a device of ON resistance R is equal to  $C V_{dd}^2$  per period for a rail-to-rail voltage equal to  $V_{dd}$ . We will rederive this result to gain an insight for the real reason of this dissipation. We use as our model the familiar circuit in Figure 2.1. The C in the figure is the capacitance of the driven node while the R is the ON resistance of the driving gate. We start with the capacitor voltage at zero. Using the voltage source we apply a step voltage of  $V_{dd}$ . This mimics the action of turning on a MOSFET that drives the gate of another. The current in this circuit follows  $i(t) = \frac{V_{dd}}{R} e^{-t/RC}$  and hence the power consumed is  $P = \frac{V_{dd}}{R} e^{-2t/RC}$ . Integrating over the charging time we get

$$E_{dyna\,mic} = -\frac{V_{dd}^2}{R} \int_{t=0}^{\infty} e^{-2t/RC} dt = \frac{CV_{dd}^2}{2}$$

(2.2)

From the above we see that in order to charge the load to  $V_{dd}$  we need  $CV_{dd}^2$  Joules of energy. Half of it is dissipated in the resistor during charging, and the other half is stored in the charged capacitor. The later part is not lost yet but would be if we discharge the capacitor in a similar fashion, *i.e.*, by a voltage step in the voltage source.

#### 2.3 Quasistatic Charge Transfer

In essence the first two dissipation mechanisms discussed, leakage and  $V_{dd}$ -to- $V_{ss}$  short, are related to the particular implementation of CMOS circuits. In general dissipation due to leakage is considerably smaller than dissipation by the other means. In addition, it could be made even smaller if needed, e.g., operating at lower temperature or using SOI. Furthermore, we will illustrate how to eliminate the occurrence of  $V_{dd}$ -to- $V_{ss}$  shorting using a number of circuit topologies in Section 3 and Section 4. Elimination of the dissipation associated with the repeated charging and discharging of internal nodes, dynamic dissipation, is more complicated. This is because it relates directly to the movement of energy packets between nodes at different potentials, which is governed and limited by the laws of thermodynamics. It is also by far the dominant dissipative mechanism at typical operating frequencies. For this reason, we conclude that to achieve non-dissipative computation we must direct our efforts to reducing dynamic dissipation.

At this point we like to emphasize that the  $CV_{dd}^2$  dissipation is a direct consequence of the way we perform the cycling of the load C and is not an irreducible minimum associated with charging and discharging a capacitive node. Charging a node to  $V_{dd}$  from 0 in a period T only requires a current, i(t) such that

$$\int_{t=0}^{T} i(t)dt = Q = CV_{dd}$$

(2.3)

However, the energy dissipation is related to the integral of the square of the current

$$E = R \int_{t=0}^{T} i^{2}(t)dt$$

(2.4)

It therefore follows that minimum dissipation results if we charge the load using a current function i(t) that minimized the integral in Equation 2.4 while obeying equation 2.3. Intuitively we can see that this minimum function is none other than

$$i(t) = Q/T = CV_{dd}/T (2.5)$$

To prove that we add the perturbation v(t) to Q/T such that i(t) becomes equal to (Q/T) + v(t). Using Equation 2.4 we calculate the energy dissipation as

$$E = R \left( \int_{t=0}^{T} \left( \frac{Q}{T} \right)^{2} dt + \frac{2Q}{T} \int_{t=0}^{T} v(t) dt + \int_{t=0}^{T} v^{2}(t) dt \right)$$

(2.6)

For i(t) to satisfy Equation 2.3, the second integral in Equation 2.6 must equal zero. With  $v^2(t)$  always positive, we see that any perturbation of i(t) = Q/T leads to increased dissipation. From the above we see that minimum energy dissipation results when the step function of the voltage source is replaced with a current source with a step of  $I = CV_{dd}/T$  and which is turned ON for T seconds. This should not come as a surprise since as T gets larger, the process of charging and discharging the load with constant I becomes more quasistatic.

#### 2.3.1 Energy Dissipation with Current Sources

In the previous section we stated that energy dissipation is minimized by using current steps instead of voltage steps. In this section we will calculate this minimum. The energy dissipated in charging the capacitor using a current step I for T seconds is

$$E = I^2 R \times T = CV_{dd}^2 \times \frac{RC}{T}$$

(2.7)

Therefore the energy dissipated in one cycle equals

$$E_{currentsource} = CV_{dd}^2 \times \frac{2RC}{T}$$

(2.8)

We see that with a current source, the energy dissipated is less than that with a voltage step by a factor of 2RC/T for T>2RC. Since the minimum period for one cycle is 2T we see that dissipation with a current source per cycle is  $CV_{dd}^24RCf$ . And hence the power dissipation of this circuit becomes

$$P_{currentsource} = CV_{dd}^2 \times 4RC\underline{f^2} \tag{2.9}$$

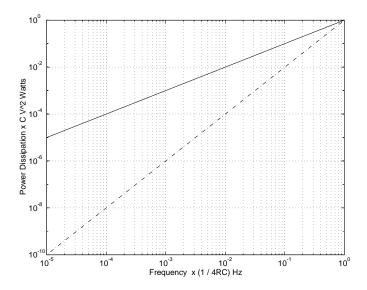

The quadratic dependence of the power on frequency is in sharp contrast to the familiar linear dependence in conventional CMOS,  $P = CV_{dd}^2f$ . Figure 2.2 plots the power dissipation associated with a the voltage step, solid line, and that of the current step, dashed line, as a function of operating frequency. Depending on the operating frequency, constant current cycling of capacitive loads results in orders of magnitude less power consumption when compared to constant voltage cycling method. We note here that quadratic dependence of power on frequency leads to linear dependence on frequency of the energy consumed per operation. This gives rise to the possibility of performing computation while consuming asymptotically zero energy.

#### 2.3.2 Multiple Capacitive Loads

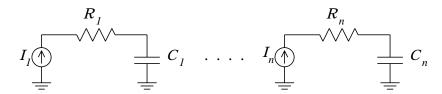

The above analysis applied to a single capacitive node. To be useful we must generalize the analysis to a number of simultaneously switching nodes as is the case in actual CMOS circuits. Ideally, each RC circuit that models a CMOS gate driving a capacitive load would have its own separate current source as shown in Figure 2.3. This is not practical with current technology.

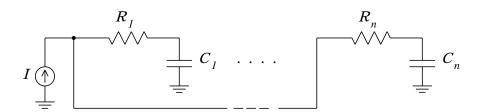

Instead, we use the circuit topology in Figure 2.4. Here a single current source provides the current that is needed by all the loads. If the RC time constant is the same for all the branches of the circuit then the voltages on all the capacitors will rise in unison and the above circuit will simplify to one with only one equivalent capacitor equal to the sum of all the capacitors in the circuit and one resistor equal to the parallel combination of the resistors in the circuit. The magnitude of the current in Figure 2.4 being equal to the magnitude of the sum of currents in Figure 2.3.

In practice however, the RC time constants of the separate branches are different. Using a common source, the circuit branches with faster time constants will track the voltage of

Figure 2.2: Normalized power dissipation plot for a voltage step, solid line, and for a current step, dashed line.

Figure 2.3: Model of CMOS circuit with separate driving current sources.

Figure 2.4: Model of CMOS circuit with common driving current source.

Figure 2.5: Voltage waveform at the terminals of a constant current source driving a capacitive load C.

the current source more closely than branches with slower RC time constants. Under such conditions, the slower branches would lag behind the fast ones and hence the voltages on the loads of different branches would grow apart. With this in mind, the point at which we must turn off the current source is not very well defined. Turning the source off when the fast branches reach  $V_{dd}$  leaves the slow branches not completely charged and in time, the loads in the slow branches will pull the voltages of all the branches to some voltage below  $V_{dd}$ . Waiting for the slow branches to completely charge up results in voltages larger than  $V_{dd}$  on the fast branches and thus making the circuit susceptible to latch-up and/or breakdown in most VLSI technologies.

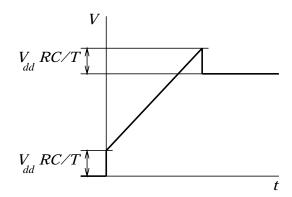

Provided that the capacitive loads are linear, the common current source could be replaced with voltage source that has the waveform shown in Figure 2.5. The initial and final jumps in the voltage of this source are equal to  $V_{dd}RC/T$ . We observe that for  $T\gg RC$  the current source could be replaced by a voltage source that outputs a linear ramp such that

$$V_{source} = \begin{cases} tV_{dd}/T & , \text{ for } 0 < t < T \\ V_{dd} & , \text{ for } t > T \end{cases}$$

(2.10)

With this source, the current at the start of the ramp is not constant but exponentially builds to the desired constant level with RC time constant. The current also exponentially drops off as soon as the voltage of the source levels off at  $V_{dd}$ . Given enough time, the voltage on all the nodes would reach  $V_{dd}$  regardless of their branch time constant. Because of the above we choose this source as a good compromise for approximating the desired ideal current source driver.

#### 2.3.3 Energy Dissipation with Voltage Ramps

In the previous section we saw how a voltage ramp can approximate a current source. Here we will examine the added energy dissipation of a voltage ramp resulting from its divergence from the ideal current source at the end of the ramp. For a voltage ramp, that follow Equation 2.10, the current i(t), is equal to

$$i(t) = \begin{cases} I(1 - e^{-t/RC}) &, \text{ for } 0 < t < T \\ I(e^{-(t-T)/RC} - e^{-t/RC}) &, \text{ for } T < t \end{cases}$$

(2.11)

where  $I = V_{dd}C/T$ . To get the dissipation associated with charging a load with a ramp we integrate the power dissipated by the above current into the resistor R over the charging period. We now stress the following two observations. The first is that unlike the case in current sources, load charging in voltage ramps continues after the ramp reaches  $V_{dd}$ . For this reason, a voltage ramp must have a higher slope than the one in Equation 2.10 in order to yield the same effective charging time of a current source with  $I = CV_{dd}/T$ . The second observation is that carrying the time of integration until all transients have settled, *i.e.*,  $t = \infty$ , for a voltage ramp in Equation 2.10 we find that the dissipated energy is the same as for the current source, *i.e.*,  $E = CV_{dd}^2RC/T$ .

From the above observations we see that the energy lost using a ramp equivalent to the current source,  $E_{ramp}$  is

$$E_{ramp} = CV_{dd}^2 \left(\frac{2RC}{T - nRC}\right) \tag{2.12}$$

where n is the number of RC time constants needed after the end of the ramp for the voltages on the nodes to reach  $V_{dd}$ , within acceptable tolerance.

As expected, the energy dissipation of the voltage ramp rapidly approaches that of an ideal current source, which is the minimum possible, as T becomes  $\gg RC$ .

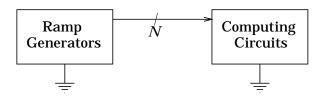

#### 2.4 Ramp Generators

We have seen how the energy dissipated in charging and discharging a capacitive load is directly proportional to the slope of the input ramp. In truth however, using a ramp does not reduce the power consumption of the whole system, it merely relocates it. If we are not careful about the design of the ramp generator, it is possible to dissipate in the generator much more energy than that saved in the circuit. Simple ramp generators continuously vary the conduction ratio of the pull-up and pull-down devices in their driving stage to produce the required intermediate voltage values of the ramp. The ramp produced will lower the energy dissipated in the circuit it drives, but the constant current path through the pull-up and pull-down devices will waste much more energy.

Note that merely relocating the dissipation from the computing circuit to the supplies still has some advantages. One advantage is to increase packaging density in systems that are otherwise limited by heat removal constraints. In conventional computing circuits, electrical energy is supplied to the circuit by copper wires and waste heat is removed by other mediums, such as forced air or circulating refrigerants. Since copper wires can transfer energy with much higher power densities than other mediums, dense packaging in supercomputers is usually limited by energy removal constraints, not by energy supply constraints. Using quasistatic computing elements, even those with dissipative ramp generators, the same copper wire injecting energy into a dense package is the one used

Figure 2.6: The two places of system dissipation.

to remove a high percentage of it out of the package thus greatly simplifying cooling and increasing density. Another advantage is that we might be able to use more exotic devices or technologies in the power supplies than in our circuits. This is because power supplies have fewer components and hence their components do not need to be densely packaged or numerously and cheaply produced like circuit components.

If the concern is to lower the overall energy dissipation of the system however, then we have to consider the dissipation occurring in the ramp generators. Currently there are two ways of building ramp generators with little dissipation. The first approximates a ramp by generating a sinusoidal waveform. The second approximates the ramp with a stepping staircase waveform.

In the next sections we will examine the dissipation associated with using either of the two methods. In our examination, we will distinguish between dissipation that happens in the computing circuits, from the dissipation that occurs within the ramp generator. In essence, we divide our system according to the energy dissipation mechanisms into the two parts shown in Figure 2.6. We do this to emphasize the fact that the dissipation in the computing circuits is purely a function of the ramp shape, while the dissipation in the ramp generator depends on both the shape of the ramp and the devices used to construct the generator. If in the future we are able to invent a less dissipative generator, we can then calculate the minimum overall dissipation of the system relatively easily. In addition, treating the two separately will more clearly illustrate how one can trade more of one dissipation for less of the other.

#### 2.5 Sinusoidal Ramp Generator

In this section we will examine the dissipation of a ramp generator that approximates the linear ramp with a sinusoid. The reason for this approximation is that it is easy to build energy efficient sinusoidal generators using inductors.

In this section we will show how to build a non-dissipative sinusoidal load driver. We will then calculate the energy dissipated in charging and discharging a capacitive load through conducting but slightly resistive device.

#### 2.5.1 Circuit Dissipation for Sinusoidal Ramps

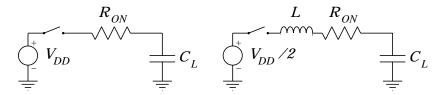

As we have assumed so far, we model the CMOS circuit performing computation by a resistor R in series with a load capacitor C. The model is based on a lumped element

Figure 2.7: Conventional and non-dissipative circuit analysis models.

approximation where the R and C are the effective R and C as seen from the supply terminals of the chip. For appropriately sized circuits, i.e., circuits where all the branches have the same time constant, we can assume that the gate voltages have roughly the same rise time and therefore we can approximate R by  $R_{device}/N$  and C by  $C_{device} \times N$  for an N branch chip. Note that R and C depend only on N and the fabrication process technology. We saw that when driven by a linear voltage ramp, as shown in Figure 2.7-a, this equivalent circuit dissipates  $CV_{dd}^2(2RC)/T$ . A sinusoidal ramp generator replaces the voltage source with the inductor circuit as shown in Figure 2.7-b. To cycle a load capacitor starting at 0 volts through  $V_{dd}$  and back to 0, we

- 1. connect the RC circuit through the inductor to  $V_{dd}/2$ ,

- 2. we keep the inductor connected until the current reaches zero, signaling a complete polarity inversion in the load capacitor,

- 3. we disconnect the rail from the inductor and connect it to the  $V_{dd}$  to compensate for leakage and noise,

- 4. and finally we reverse the above steps to return the load voltage to 0.

The inductor in the above circuit acts as an electrical "flywheel" that forces the shuttling of energy between the capacitor and the  $V_{dd}/2$  supply. For now, assume the switch connecting the rail to the inductor is external to the chip. We will revisit this in a later section.

We now examine the dissipation of our proposed circuit. To simplify the algebra, we let  $V_{dd} = +V_0$  and  $V_{ss} = -V_0$  so that  $V_0$  is equal to half the rail-to-rail voltage  $V_{dd}$ . Our R, L, C circuit is described by

$$\frac{d^2V_C}{dt^2} + 2\alpha \frac{dV_C}{dt} + \frac{V_C}{\omega_0^2} = 0 {(2.13)}$$

where  $V_C$  is the capacitor voltage,  $\alpha = R/2L$ , and  $\omega_0 = 1/\sqrt{LC}$ . For the solution to oscillate, the circuit must be underdamped, requiring that

$$2\sqrt{LC} > RC \tag{2.14}$$

and we find that the frequency of oscillation,  $\omega_d$ , is given by

$$\omega_d = \sqrt{{\omega_0}^2 - \alpha^2} \tag{2.15}$$

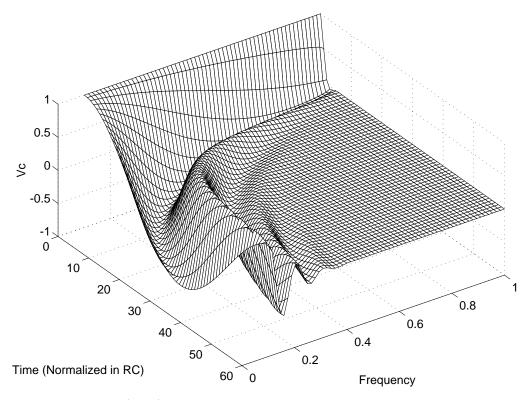

Figure 2.8: Plot of  $V_c(t, \omega_d)$  showing the effect of fast rise and fall times on energy loss.

where  $\omega_d$  is the frequency of operation and is equal to  $\pi/T$ . Since R and C are fixed for a given chip, we can only adjust L to affect  $\omega_d$ . Examining the formula for  $\omega_d$  we discover that  $\omega_d$  steadily increases as L decreases up to a maximum,  $\omega_{dmax}$ , and then sharply decreases as the circuit approaches the *critically damped* point. We find that

$$\omega_{d\,ma\,x} = \frac{1}{RC} = \frac{1}{R_{device}C_{device}} \tag{2.16}$$

and the smallest inductance we would ever need,  $L_{min}$ , is found by

$$L_{min} = R^2 C/2 = R_{device}^2 C_{device}/2N$$

(2.17)

For  $V_C(0) = V_0$  and  $i_C(0) = 0$  we find

$$V_C(t) = V_0 e^{-\alpha t} (\cos \omega_d t + \frac{\alpha}{\omega_d} \sin \omega_d t)$$

(2.18)

and

$$i_C(t) = V_0 C \frac{{\omega_0}^2}{\omega_d} e^{-\alpha t} \sin \omega_d t \tag{2.19}$$

Figure 2.8 shows a plot of normalized  $V_c$  as function of time and normalized  $\omega_d$ . Initially  $V_C(0) = 1$ . With  $\omega_d$  close to  $\omega_{d_{max}}$  the voltage drops rapidly, dissipating most of the

capacitor energy on the way down. The reclaimed energy is insufficient to fully charge the capacitor back to the negative rail. As  $\omega_d$  moves away from  $\omega_{d \, ma \, x}$  we in effect spread each oscillation over a longer period of time. We see from the plot that the capacitor retains most of its energy since  $V_C$  comes close to the bottom rail. With  $\omega_d$  only an order of magnitude lower than the maximum, the capacitor recovers most of its energy.

The power dissipated in a single rail-to-rail swing for our gate consists of two components. The first is the power dissipated in R during the swing,  $E_s$ , which results in a final voltage that is lower than  $|V_0|$ . Using Equation 2.18 we find that

$$E_s = \frac{1}{2}C \ V_0^2 \ (1 - e^{\frac{-2\pi\alpha}{\omega d}}) \tag{2.20}$$

The second is the energy lost in R while charging C to the rail to compensate for the lower peak voltage due to  $E_s$ . We will do this by simply connecting the line to the rail and losing some energy in R,  $E_c$ , during this process. We find that

$$E_c = \frac{1}{2}C \ V_0^2 \ (1 - e^{\frac{-\pi\alpha}{\omega_d}})^2 \tag{2.21}$$

adding these two terms and multiplying by two to allow for both directions of swing, we find that

$$E_{loss} = 2C V_0^2 \left(1 - e^{\frac{-\pi\alpha}{\omega_d}}\right) \tag{2.22}$$

per period.

Using Equation 2.22, we compute the ratio of the power consumption per period of conventional CMOS to that of a sinusoidally driven gate,  $F_{saving}$ , as

$$F_{saving} = \frac{2}{(1 - e^{\frac{-\pi\alpha}{\omega_d}})} \tag{2.23}$$

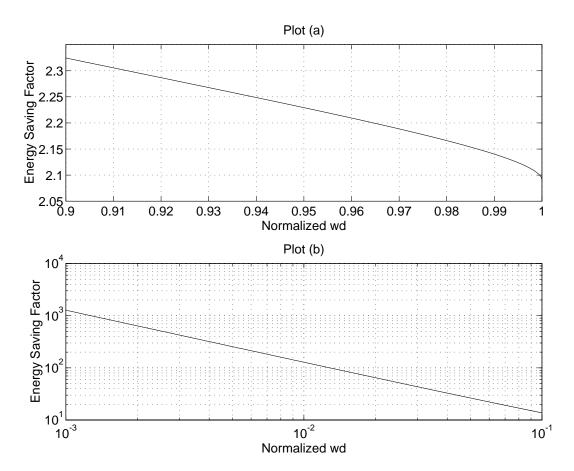

Figure 2.9a shows a linear plot of  $F_{saving}$  near  $\omega_{dmax}$ . In this region, the circuit's performance is close to conventional CMOS but improves rapidly with lower  $\omega_d$ . As we get away from  $\omega_{dmax}$ , the graph attains a nearly constant slope as shown in Figure 2.9b and  $\omega_0 \simeq \omega_d$ . Substituting R/2L for  $\alpha$ ,  $\pi/T$  for  $\omega_d$  or  $\omega_0$ , we approximate  $\frac{\pi\alpha}{\omega_d}$  with

$$\frac{\pi\alpha}{\omega_d} = \frac{\pi(R/2L)}{(\pi/T)} \simeq \frac{TRC\omega_0^2}{2} \simeq \frac{\pi^2 RC}{2T}$$

(2.24)

Expanding the exponential, we get

$$F_{saving} \simeq \frac{4T}{\pi^2 RC} \tag{2.25}$$

for one charging and discharging cycle.

We see that sinusoidal ramps are worse than ideal linear ramps, Equation 2.12, by a factor of  $\pi^2/8$  owing to the sinusoidal, instead of the constant, nature of the current in the circuit.

Figure 2.9: (a) Linear plot of  $F_{saving}$  factor vs.  $\omega_d$ . (b) Log-Log plot of  $F_{saving}$  factor vs.  $\omega_d$ . In both plots  $\omega_d$  is normalized to  $\omega_{dmax}$ .

#### 2.5.2 Generator Dissipation for Sinusoidal Ramps

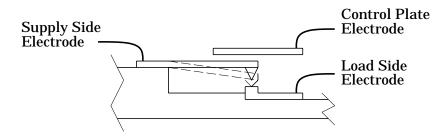

Examining Figure 2.7-b, we see that the only component that could dissipate energy in a sinusoidal generator is the switch. This includes energy dissipated because of the switch's non-zero on resistance as well as energy dissipated in the action of turning it on or off. The case we will analyze is when the switch is made out of MOS devices. The resistance of an N-Channel MOSFET,  $R_{ON}$ , is equal to

$$R_{ON} = \frac{V_{DS}}{I_D} = \frac{L}{W\overline{\mu_n}C_o\left[(V_{GS} - V_{TH}) - \frac{V_{DS}}{2}\right]}$$

(2.26)

where W and L are the gate width and length of the device,  $C_o$  is the gate capacitance per area, and  $\overline{\mu_n}$  is the average mobility of the carriers in the channel [35]. In quasistatic switching, we always attempt to minimize  $V_{DS}$  to reduce dissipation so that in general  $|V_{DS}| \ll |V_{GS} - V_T|$ . With this in mind and substituting  $C_p$ , the gate capacitance, for

$WLC_o$ , we get

$$R_{ON} = \frac{L^2}{\overline{\mu_n} C_p (V_{GS} - V_{TH})}$$

(2.27)

The on resistance of a MOSFET depends on the difference between the gate voltage and the channel. In a sinusoidal generator, this voltage varies with time as the load charges. By using a pair of complementary devices for the switch we are able to minimize this dependence since the variation due to the N-Channel device cancels that due to the P-Channel device. This makes  $R_{ON}$  almost constant over the period of the ramp.  $R_{ON}$  now becomes

$$R_{ON} = \frac{L^2}{\overline{\mu_{ave}}C_s(V_{dd} - V_{THave})} = \frac{\tau_s}{C_s}$$

(2.28)

where  $\overline{\mu_{ave}}$  is a weighted average of  $\overline{\mu_n}$  and  $\overline{\mu_n}$  and  $V_{THave}$  is the weighted average of the threshold voltages of the N-Channel and P-Channel devices. The energy dissipated in the switch during a single ramp swing has two components. The first is the dissipation due to charging and discharging the gate of the switch and is equal to  $2C_sV_{dd}^2$  for a conventionally driven pass gate. The second is the dissipation due to the finite on resistance of the switch. From Equation 2.25 and Equation 2.28 we see that the total dissipation in the switch,  $E_{switch}$ , is equal to

$$E_{switch} = 2C_s V_{dd}^2 + \frac{1}{2} C_L V_{dd}^2 \frac{\pi^2}{4} \frac{R_{ON} C_L}{T}$$

(2.29)

where  $C_L$  is the effective load capacitance of the computing circuit be driven.

Finding the minimum with respect to  $C_s$ , we find that the optimal gate capacitance of the switch is

$$C_s = C_L \frac{\pi}{4} \sqrt{\frac{\tau_s}{T}} \tag{2.30}$$

and the minimum dissipation in the switch becomes

$$E_{switch} = CV_{dd}^2 \pi \sqrt{\frac{\tau_s}{T}}$$

(2.31)

The above analysis agrees with that reported by Koller and Athas [1] albeit with some modification because of differing definition of the process time constant of the switch,  $\tau_s$ .

Adding the dissipation in the computing circuits, the total minimum dissipated energy in the system,  $E_{total}$ , becomes

$$E_{total} = C_L V_{dd}^2 \left( \pi \sqrt{\frac{\tau_s}{T}} + \frac{\pi^2}{8} \frac{\tau_c}{T} \right)$$

(2.32)

where  $\tau_c$  is the time constant for the circuit branches of the computing part of the system. We see that after accounting for the switch dissipation, the overall energy consumption of the system now drops as  $1/\sqrt{T}$  instead of the thermodynamic limit of 1/T. In general,  $\tau_s \simeq \tau c$  when both the switch and the computing circuits use the same process technology. Since T is always greater than  $\tau_s$  and  $\tau_c$  for proper operation, we see that the switch dissipation always dominates the dissipation characteristics of the total system.

#### 2.5.3 Nested Sinusoidal Drivers

The above analysis assumed that the switch is driven conventionally and hence dissipated  $2C_sV_{dd}^2$  for every switching cycle. The factor of 2 is there because the switch has to turn on and off for both the rising and the falling parts of the driven signal. Koller and Athas [1] have suggested driving the switch with yet another sinusoidal ramp circuit which itself is driven sinusoidally and so on. They report that for N nested drivers, the minimum dissipation would follow  $1/T^{(1-2^{-N})}$ . They caution that since every driving stage have to be faster than the stage it is driving, we quickly get to the point at which driving the preceding stage sinusoidally, adds overhead but saves no energy. Add to that the fact that each switch must be smaller than the one it drives, which quickly limits the useful nesting when the switch reaches the minimum size device of the technology. They report that with current CMOS technologies, N would not exceed 2 or 3 unless T is very large "on the order of milliseconds or seconds".

#### 2.5.4 Inductor Quality factor

So far we have assumed that the inductor in our RLC circuit enjoyed an infinite quality factor, Q. However, the Q's of commercially available inductors seldom reach higher than 100. The Q identifies the fraction of energy that is dissipated by the inductor in a RLC circuit during one cycle. Attempts to reduce the energy dissipation of the system below Q fold will fail as the inductor irreducible inductor dissipation becomes the dominant factor. This means that the maximum attainable energy saving factor is limited to about Q. We can dramatically improve this limit by using high-temperature superconducting coils. These usually have Q's in excess of several thousands. Unfortunately, such coils require cooling, typically by liquid nitrogen, which increases the cost as well as decreases utility in some application, e.g. portable equipment. The hope however is the discovery of superconducting material that will work at, or slightly below, room temperature. For a more detailed discussion of low temperature operation please see appendix A.

#### 2.6 Stepwise Ramp Generator

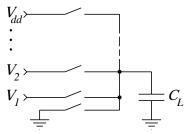

Inductors are not the only way to produce a gradual voltage ramp. Another way to produce the gradual charge transfer from one potential to the other is to move the charge one small voltage step at a time. This mimics the situation with the two heat baths at differing temperatures separated by a number of heat baths at intermediate temperatures. We start with a load,  $C_L$ , at zero volts that needs to be charged to  $V_{DD}$ . We provide N voltage sources each with a voltage that is  $V_{DD}/N$  volts greater than the previous one. We also provide a switch connected between the load and each voltage source as shown in Figure 2.10.

To charge the load, we momentarily connect it to each voltage source, using the provided switches, in a sequence from the source with the lowest voltage,  $V_{DD}/N$  for N voltage steps, to the one with the highest value,  $V_{DD}$ . Reversing the switching sequence brings the load back to zero. Advantages of using a stepwise generator include elimination of inductors

Figure 2.10: Typical stepwise ramp generator circuit driving a capacitive load  $C_L$ .

Figure 2.11: Model of a CMOS computing circuit driven by a stepwise source.

with their non-linear effects and more control over the rise and fall time of the ramp since this rise time is now not related to the load capacitance.

Following the same organization used for the sinusoidal case, I will first examine the dissipation of a computing circuit when driven by a stepwise ramp. After that I will examine the dissipation in the stepwise ramp generator itself. For the analysis, I'll use a MOSFET implementation of the stepwise generator.

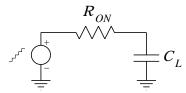

#### 2.6.1 Circuit Dissipation for Stepwise Ramps

To account for only the dissipation in the computing circuit, we use the model shown in Figure 2.11. The model consists of a load capacitor,  $C_L$ , representing the effective capacitance of the computing circuit and a resistance,  $R_{ON}$ , representing the effective ON resistances of the MOSFET's in the circuit paths to the loads. The driving voltage source in the circuit generates a staircase waveform starting at zero volts and rising towards  $V_{DD}$  with  $V_{DD}/N$  increments and with n times the RC time constants between the steps.

We begin by assuming that the time provided between each step is much longer than the RC time constant of the circuit in Figure 2.11. This will insure enough time between steps for the circuit to settle. From Equation 2.2 we see that each step in the voltage source dissipated  $C_L \Delta V^2/2$  joules of energy where  $\Delta V = V_{DD}/N$ . Since there are N steps during the rise and another N steps during the fall of the ramp voltage, the total dissipation a computing circuit that is driven by a stepwise ramp,  $E_{stepwise}$ ,

$$E_{stepwise} = 2N \times \frac{C_L V_{DD}^2}{2N^2} = \frac{C_L V_{DD}^2}{N}$$

(2.33)

The above result should not come as a surprise. Given that the time between steps is always fixed at the value that allows enough time for the most part of the transients to

settle, i.e., a few RC's, we see that increasing N is identical to increasing T. Said differently

$$N \simeq \frac{T}{nRC} \tag{2.34}$$

and we see that Equation 2.33 is very analogous to Equation 2.8.

#### 2.6.2 Generator Dissipation for Stepwise Ramps

Svensson and Koller [38] have studied the dissipation in a MOSFET implementation of a stepwise ramp generator. Their generator consisted of a number of large capacitors with each charged to one of the step voltages and each separated from the output by a NMOS switch. Shorting these large capacitors to the output via the MOSFET devices in ascending order produced the stepwise ramp. In their work they show that the optimal number of steps is

$$N_{opt} = \sqrt[3]{\frac{T}{4m\overline{\rho}}} \tag{2.35}$$

where m is the number of process time constants between steps and  $\overline{\rho}$  is the weighted average of  $(R_{ON} \times C_{gate})$  of the MOSFET devices used. Given this, they calculate the minimum energy dissipated in the control of these switched and due to their non-zero ON resistance,  $E_{opt}$ , to be

$$E_{opt} = \frac{3}{2} \sqrt[3]{\frac{4m\overline{\rho}}{T}} C_L V_{DD}^2 \tag{2.36}$$

We note that even though the dissipation in the computing circuit driven by a stepwise generator followed 1/T, the energy dissipated in a MOSFET implementation of the stepwise ramp generator optimally follows  $1/\sqrt[3]{T}$ . This means that the energy dissipation by the overall system would track  $1/\sqrt[3]{T}$ . This is worse than the performance of a sinusoidal generator using a MOSFET switch which tracked  $1/\sqrt{T}$ .

#### 2.7 Alternate Power Switches

The above derivations assumed that the power switch, or switches in the stepwise case, was built out of the same device technology as that of the computing circuit. In both the sinusoidal ramp generator and the stepwise generator cases, the energy dissipation of the computing circuit followed the theoretical line of 1/T. We saw how this impressive energy saving behavior deteriorated, to  $1/\sqrt{T}$  for the sinusoidal case and to  $1/\sqrt[3]{T}$  in the stepwise case, due to the non-ideal properties of the MOSFET's used in the generators. However, the economics of the VLSI computing circuit of the system are very different from those of the power supplies, or ramp generators. The technologies for both the computing circuits and the power switches in the ramp generators need not, and as we will show should not, be the same. In the coming analysis we will concentrate on the power switch for the sinusoidal ramp generator. Even though the proposed methods could be equally applied to the stepwise case, we will focus on the sinusoidal generator because of its more attractive energy dissipation curve.

To illustrate the point of using alternate technologies in the ramp generators, let us assume that  $\tau_s < \tau_c$ . We rearrange Equation 2.32 to find the value of normalized T,  $T/\tau_c$ , at which the energy dissipation in the switch,  $E_{switch}$ , becomes equal to dissipation in the circuit  $E_{circuit}$ . We find that

$\frac{T}{\tau_c} = \left(\frac{\pi}{8}\right)^2 \frac{\tau_c}{\tau_s} \tag{2.37}$