## Closing the Window of Vulnerability in Multiphase Memory Transactions: The Alewife Transaction Store

by

#### John David Kubiatowicz

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### February 1993

© Massachusetts Institute of Technology, 1993

The author hereby grants to MIT permission to reproduce and to distribute copies of this thesis document in whole or in part.

| $\operatorname{Signat}$ | ure of Author                                                  |

|-------------------------|----------------------------------------------------------------|

|                         | Department of Electrical Engineering and Computer Science      |

|                         | February 1, 1993                                               |

| Certifi                 | ed by                                                          |

|                         | Anant Agarwal                                                  |

| Assoc                   | ciate Professor of Computer Science and Electrical Engineering |

|                         | Thesis Supervisor                                              |

| Ассер                   | ted by                                                         |

| -                       | Campbell L. Searle                                             |

|                         | Chairman, Departmental Committee on Graduate Students          |

## Closing the Window of Vulnerability in Multiphase Memory Transactions: The Alewife Transaction Store

by

#### John David Kubiatowicz

Submitted to the Department of Electrical Engineering and Computer Science on February 1, 1993, in partial fulfillment of the requirements for the degree of Master of Science

#### Abstract

Multiprocessor architects have begun to explore several mechanisms such as prefetching, context-switching and software-assisted dynamic cache-coherence, which transform single-phase memory transactions in conventional memory systems into multiphase operations. Multiphase operations introduce a window of vulnerability in which data can be invalidated before it is used. Losing data due to invalidations introduces damaging livelock situations. This thesis discusses the origins of the window of vulnerability and proposes an architectural framework that closes it. The framework employs fully-associative transaction-buffers and an algorithm called thrashlock. It has been implemented as one facet of the Alewife machine, a large-scale cache-coherent multiprocessor.

**Keywords:** multiprocessor, context-switching, cache-coherence, multi-phase memory transaction, transaction-buffer, victim caching, Alewife machine

Thesis Supervisor: Anant Agarwal

Title: Associate Professor of Computer Science and Electrical Engineering

#### Acknowledgments

Much of the act of writing academic papers and theses is an exercise in revisionist history. I hope that the motivations, interfaces, mechanisms, and justifications given in the following pages give the impression that the Alewife cache controller was designed from first principles. I, of course, know better . . .

I would like to acknowledge Pizzeria Uno for being open until 12:30am most evenings. This permitted me to spend long hours designing the hardware described within. I have never designed a system as large (and some would stress as complicated) as the Alewife cache controller. Many mistakes and false starts are forever burned into my memory.

Many thanks to my advisor, Anant Agarwal, for giving me the chance to design my first machine. It has been a learning experience, to say the least.

Also, many thanks to the members of the Alewife team. Their opinions, sometimes voiced loudly, led me to develop better arguments in support of my design choices. Occasionally, they even led to the development of better solutions. A project as large as the Alewife machine is certainly a team effort. Without the support of simulators and other software systems written by them, I would not as close as I am to a working A-1000 cache controller. The next few months should be an exciting period.

Finally, special thanks to David Chaiken for groveling though early implementations of the cache controller. He has all but suspended his academic career for the last year and a half to write a high-level simulation of the A-1000. When all is said and done, we make a good team.

## Contents

| 1        | Intr                        | roduct | ion                                              | 10 |

|----------|-----------------------------|--------|--------------------------------------------------|----|

|          | 1.1                         | Multi- | -phase Memory Transactions                       | 11 |

|          | 1.2                         | High-  | Availability Interrupts                          | 13 |

|          | 1.3                         | The F  | Tramework                                        | 13 |

| <b>2</b> | Har                         | rdware | Mechanisms for Shared Memory Support             | 15 |

|          | 2.1                         | Coher  | rent Caches with Multiple Outstanding Requests   | 16 |

|          | 2.2                         | Atom   | icity and Context Switching                      | 16 |

|          | 2.3                         | High-  | Availability Interrupts                          | 17 |

| 3        | $\operatorname{Th}\epsilon$ | Wind   | low of Vulnerability                             | 19 |

|          | 3.1                         | Prelin | ninaries                                         | 19 |

|          |                             | 3.1.1  | Forward Progress                                 | 19 |

|          |                             | 3.1.2  | Primary and Secondary Transactions               | 20 |

|          |                             | 3.1.3  | Forward Progress and the Window of Vulnerability | 21 |

|          | 3.2                         | Four 1 | Different Livelock Scenarios                     | 22 |

|          |                             | 3.2.1  | Invalidation Thrashing                           | 22 |

|          |                             | 3.2.2  | Replacement Thrashing                            | 23 |

|          |                             | 3.2.3  | High-Availability Interrupt Thrashing            | 24 |

|          |                             | 3.2.4  | Instruction-Data Thrashing                       | 25 |

|          |                             | 3.2.5  | Completeness                                     | 26 |

|          | 3 3                         | Severi | ity of the Window of Vulnerability               | 27 |

| 4        | Clo | sing th | ne Window                                    | 30 |

|----------|-----|---------|----------------------------------------------|----|

|          | 4.1 | Lockii  | ng (Partial Solution)                        | 31 |

|          |     | 4.1.1   | The Transaction-In-Progress State            | 32 |

|          |     | 4.1.2   | Premature Lock Release                       | 32 |

|          |     | 4.1.3   | Deadlock Problems                            | 32 |

|          | 4.2 | Assoc   | iative Locking                               | 35 |

|          | 4.3 | Thras   | hwait                                        | 36 |

|          |     | 4.3.1   | Multiple Primary Transactions                | 38 |

|          |     | 4.3.2   | Elimination of Thrashing                     | 40 |

|          |     | 4.3.3   | Freedom From Deadlock                        | 40 |

|          |     | 4.3.4   | Thrashwait and High-Availability Interrupts  | 42 |

|          | 4.4 | Assoc   | iative Thrashwait (Partial Solution)         | 43 |

|          | 4.5 | Assoc   | iative Thrashlock                            | 43 |

| <b>5</b> | Imp | olemen  | atation of the Framework                     | 46 |

|          | 5.1 | Alewi   | fe and the A-1000 CMMU                       | 46 |

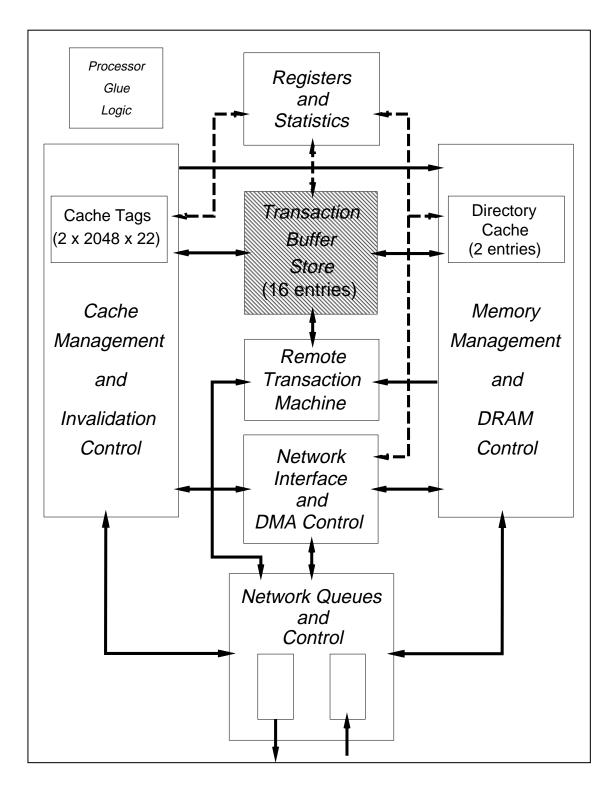

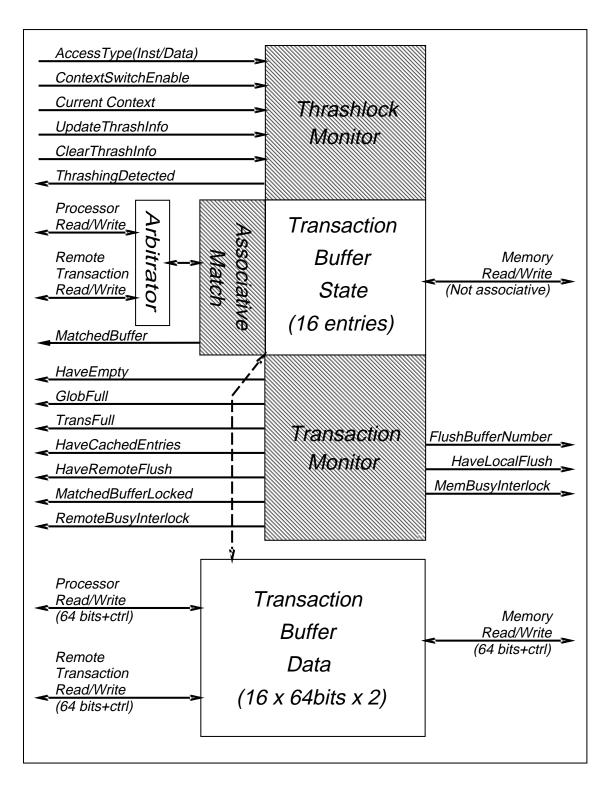

|          | 5.2 | Transa  | action Store                                 | 50 |

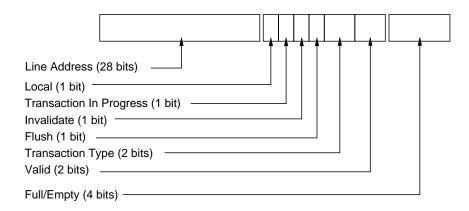

|          | 5.3 | Transa  | action State                                 | 53 |

|          |     | 5.3.1   | The Transaction Store as a Cache             | 57 |

|          |     | 5.3.2   | Transaction in Progress States               | 58 |

|          |     | 5.3.3   | Transient States                             | 58 |

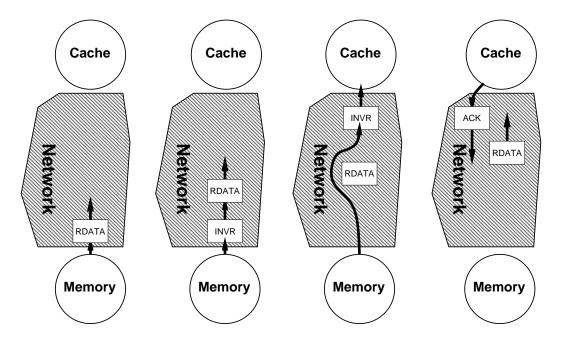

|          |     | 5.3.4   | Insensitivity to Network Reordering          | 60 |

|          | 5.4 | Associ  | iative Matching Port                         | 65 |

|          | 5.5 | Thras   | hlock Monitor                                | 66 |

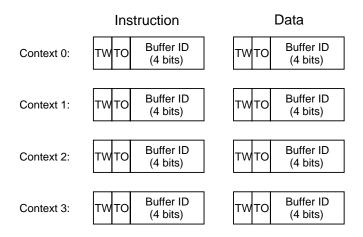

|          |     | 5.5.1   | Tracking Vectors                             | 67 |

|          |     | 5.5.2   | Buffer Locks                                 | 69 |

|          |     | 5.5.3   | Protection of Primary Transaction Buffers    | 70 |

|          |     | 5.5.4   | Thrash Detection and the Processor Interface | 71 |

|          |     | 5.5.5   | Pipeline Reordering                          | 73 |

|          | 5.6 | Transa  | action Monitor                               | 75 |

|   |                | 5.6.1            | Buffer Allocation Constraints                      | 76       |

|---|----------------|------------------|----------------------------------------------------|----------|

|   |                | 5.6.2            | Allocation of Empty Buffers                        | 78       |

|   |                | 5.6.3            | Identification of Buffers for Garbage Collection   | 78       |

|   |                | 5.6.4            | Scheduling of Transient States                     | 79       |

|   | 5.7            | Transa           | action Data                                        | 80       |

|   |                |                  |                                                    |          |

| 6 | Clo            | sing tl          | ne Window of Vulnerability: The Signaling Approach | 81       |

| 6 | <b>Clo</b> 6.1 | O                | ne Window of Vulnerability: The Signaling Approach |          |

| 6 |                | Retair           | , , , , , , , , , , , , , , , , , , , ,            | 81       |

| 6 | 6.1            | Retain<br>Signal | ning Invalidated Read Data                         | 81<br>83 |

## List of Figures

| 1-1 | Multiple outstanding requests                                              | 12 |

|-----|----------------------------------------------------------------------------|----|

| 2-1 | The need for high-availability interrupts                                  | 17 |

| 3-1 | Treat the memory system (complete with network, coherence protocol, and    |    |

|     | other nodes) as a "black box"                                              | 20 |

| 3-2 | Time-line illustration of invalidation thrashing. The shaded area is the   |    |

|     | window of vulnerability.                                                   | 24 |

| 3-3 | Diagram of cache coherence invalidation.                                   | 24 |

| 3-4 | Time-line illustration of replacement thrashing                            | 24 |

| 3-5 | Diagram of cache replacement                                               | 25 |

| 3-6 | Time-line illustration of high-availability interrupt thrashing            | 25 |

| 3-7 | Time-line illustration of instruction-data thrashing                       | 26 |

| 3-8 | Window of vulnerability: 64 processors, 4 contexts                         | 28 |

| 4-1 | Deadlocks that result from pure locking. $(X \equiv Y, X \neq Z)$          | 33 |

| 4-2 | Elimination of instruction-data thrashing through Thrashwait. At the point |    |

|     | marked with (†), Thrashwait is invoked since Data_TO[0] is set             | 39 |

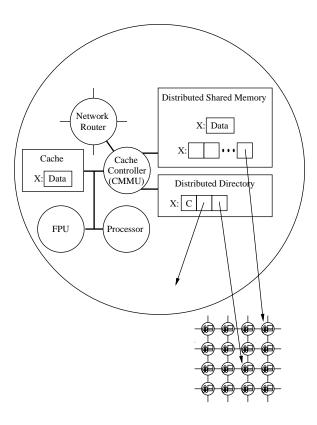

| 5-1 | An Alewife Processing Node                                                 | 47 |

| 5-2 | Internals of the A-1000 Communications and Memory Management Unit .        | 48 |

| 5-3 | The transaction store                                                      | 52 |

| 5-4 | The state of a transaction buffer                                          | 54 |

| 5-5 | The effect of network reordering on an uncompensated protocol              | 60 |

| 5-6 | Tracking vectors for implementing the thrashlock mechanism                 | 67 |

## List of Tables

| 4.1 | Window of Vulnerability closure techniques. Multi represents coherent                                    |    |

|-----|----------------------------------------------------------------------------------------------------------|----|

|     | ${\it caches and multiple \ requests.}\ {\it Disable \ represents \ disabling \ of \ context \ switch-}$ |    |

|     | ing. $\mathit{HAI}$ represents high-availability interrupts                                              | 30 |

| 4.2 | Properties of window of vulnerability closure techniques with respect to                                 |    |

|     | the complete set of features                                                                             | 31 |

| 5.1 | Legal combinations of buffer state bits. Missing states are illegal                                      | 56 |

## Chapter 1

### Introduction

One of the major thrusts of multiprocessor research has been the exploration of mechanisms that provide ease of programming, yet are amenable to cost-effective implementation. To this end, a substantial effort has been expended in providing efficient shared memory for systems with large numbers of processors. Many of the mechanisms that have been proposed for use with shared memory, such as rapid-context switching, software prefetch, fast message-handling, and software-assisted dynamic cache-coherence enhance different aspects of multiprocessor performance; thus, combining them into a single architectural framework is a desirable goal. Unfortunately, this combination of features introduces a window of vulnerability in which data requested by a processor can be lost before it is consumed, either through remote invalidation or through cache conflicts.

This thesis investigates several methods of closing the window of vulnerability, culminating in a unifying architectural framework, the transaction store. As described in Chapter 5, the complete framework has been implemented in the MIT Alewife machine [3]; however, other multiprocessor architects may choose to implement a subset of this framework. To this end, Chapter 4 discusses several partial solutions, each of which are appropriate to a different subset of mechanisms.

#### 1.1 Multi-phase Memory Transactions

Many of the mechanisms associated with shared memory attempt to address a central problem: access to global memory may require a large number of cycles. To fetch data through the interconnection network, the processor transmits a request, then waits for a response. The request may be satisfied by a single memory node, or may require the interaction of several nodes in the system. In either case, many processor cycles may be lost waiting for a response.

In a traditional shared-memory multiprocessor, remote memory requests can be viewed as *split-phase* transactions, consisting of a request and a response. The time between request and response may be composed of a number of factors, including communication delay, protocol delay, and queueing delay. Since a simple single-threaded processor can typically make no forward progress until its requested data word arrives, it spins while waiting. When the data word arrives, the processor consumes the data immediately, possibly placing it in a local cache.

Rather than spinning, a processor might choose to do other useful work. To tolerate long access latencies, architects have proposed a number of mechanisms such as prefetching, weak ordering, multithreading, and software-enforced coherence. All are variations on a central theme: they allow processors to have multiple outstanding requests to the memory system. A processor launches a number of requests into the memory system and performs other work while awaiting responses. This capability reduces processor idle time and allows the system to increase its utilization of the network.

The ability to handle multiple outstanding requests may be implemented with either polling or signaling mechanisms. Polling involves retrying memory requests until they are satisfied. This is the behavior of simple RISC pipelines which implement non-binding prefetch or context-switching through synchronous memory faults. Signaling involves additional hardware mechanisms that permit data to be consumed immediately upon its arrival. Such signaling mechanisms would be similar to those used when implementing binding prefetch or out-of-order completion of loads and

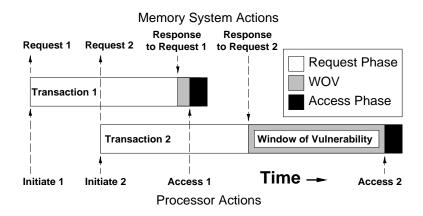

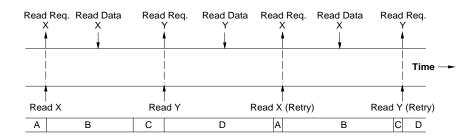

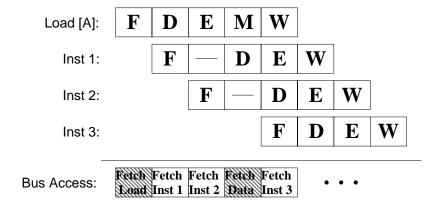

Figure 1-1: Multiple outstanding requests.

stores. This thesis explores the problems involved in closing the window of vulnerability in polled, context-switching processors. Signaling leads to related approaches; these are touched upon in Chapter 6.

Figure 1-1 illustrates the timing involved in overlapping access latency using a polling mechanism. The figure shows a time-line of events for two memory transactions that occur on a single processing node. Time flows from left to right in the diagram. Events on the lower line are associated with the processor, and events on the upper line are associated with the memory system. In the figure, a processor initiates a memory transaction (Initiate 1), and instead of waiting for a response from the memory system, it continues to perform useful work. During the course of this work, it might initiate yet another memory transaction (Initiate 2). At some later time, the memory system responds to the original request (Response to Request 1). Finally, the processor completes the transaction (Access 1).

Since a processor continues working while it awaits responses from the memory system, it might not use returning data immediately. Such is the case in the scenario in Figure 1-1. When the processor receives the response to its second request (Response to Request 2), it is busy with some (possibly unrelated) computation. Eventually, the processor completes the memory transaction (Access 2).

Thus, we can identify three distinct phases of a transaction:

Request Phase – The time between the transmission of a request for data and the arrival of this data from memory.

- 2. Window of Vulnerability The time between the arrival of data from memory and the initiation of a successful access of this data by the processor.

- 3. Access Phase The period during which the processor atomically accesses and commits the data.

The window of vulnerability results from the fact that the processor does not consume data immediately upon its arrival. During this period, the data must be placed somewhere, perhaps in the cache or a temporary buffer. Note that a simple split-phase transaction can be seen as a degenerate multiphase transaction with zero cycles between response and access. The period between the response and access phases of a transaction is crucial to forward progress. Should the data be invalidated or lost due to cache conflicts during this period, the transaction is terminated before the requesting thread can make forward progress.

#### 1.2 High-Availability Interrupts

The window of vulnerability is also opened by another class of mechanisms. This class contains a number of mechanisms including fast I/O, interprocessor messages, synchronization primitives, and extensions of the memory system through software. When implementing such mechanisms, the successful completion of a spinning load or store to memory may depend on the execution of network interrupts. These asynchronous events must be able to fault an instruction which is in progress, thereby opening a window of vulnerability. The term high-availability interrupt is applied to such externally initiated pipeline interruptions.

#### 1.3 The Framework

Closing the window of vulnerability involves ensuring forward progress for multiphase memory transactions. The consequences of lost data are more subtle and perilous than simple squandering of memory resources. The window of vulnerability allows scenarios in which processors repeatedly attempt to initiate transactions only to have them canceled during the window of vulnerability. In certain pathological cases, individual processors are prevented from making forward progress by cyclic *thrashing* situations. While such situations may be rare, they are as fatal as any other livelock or deadlock situation.

This thesis describes a framework that eliminates livelock problems associated with the window of vulnerability for systems with multiple outstanding requests and high-availability interrupts. The system keeps track of pending memory transactions in such a way that it can dynamically detect and eliminate pathological thrashing behavior. The framework consists of three major components: a small, associative set of transaction buffers that keep track of outstanding memory requests, an algorithm called thrashwait that detects and eliminates livelock scenarios that are caused by the window of vulnerability, and a buffer locking scheme that prevents livelock in the presence of high-availability interrupts.

Not all architects will need to implement the full gamut of mechanisms described in this thesis. For this reason, we describe the different subsets of the framework and the mechanisms that each subset will support. In order to motivate the architectural framework that we propose, Chapter 2 presents examples of shared memory mechanisms. Chapter 3 then shows how the window of vulnerability can impede a system's forward progress. Chapter 4 explores several components of the framework, each of which provides part of the solution for ensuring forward progress. Chapter 4 concludes with a hybrid architecture, called ThrashLock, that combines these components to implement all of the mechanisms. Chapter 5 describes how the issues discussed in earlier sections of this paper are reflected in the actual implementation of Alewife. As is shown in that chapter, the principle component of the implementation, the transaction store, is an important centralized resource and has many benefits over and above those which are developed by the earlier chapters. Chapter 6 discusses alternatives to the ThrashLock architecture which would be possible with more significant modifications to the processor pipeline. Finally, Chapter 7 concludes by examining the implications of the window of vulnerability on the design of shared memory systems.

## Chapter 2

# Hardware Mechanisms for Shared Memory Support

Three general classes of hardware support for efficient implementation of distributed shared memory are:

- 1. Coherent caches to automatically replicate data close to where it is needed, and a mechanism to allow multiple outstanding requests to memory.

- 2. Atomic operations on critical system resources.

- 3. High-availability interrupts for response to high-priority asynchronous events, such as message arrival.

This section presents examples of some of the mechanisms that belong to these classes and makes a case for incorporating them into distributed shared memory machines.

The following section describes how each of these mechanisms leads to the same window of vulnerability problem. A given system might implement only a small subset of these mechanisms, in which case only a portion of our architectural framework would need to be implemented.

## 2.1 Coherent Caches with Multiple Outstanding Requests

Coherent caches are widely recognized as a promising approach to reducing the bandwidth requirements of the shared-memory programming model. Because they automatically replicate data close to where it is being used, caches convert temporal locality of access into physical locality. That is, after a first-time fetch of data from a remote node, subsequent accesses of the data are satisfied entirely within the node. The resulting cache coherence problem can be solved using a variety of directory based schemes [15, 23, 9].

In a cache-based system, memory and processor resources are wasted if no processing is done while waiting for memory transactions to complete. Such transactions include first-time data fetches and invalidations required to enforce coherence. Applying basic pipelining ideas, resource utilization can be improved by allowing a processor to transmit more than one memory request at a time. Multiple outstanding transactions can be supported using software prefetch [7, 24], rapid context switching [28, 4], or weak ordering [1]. Studies have shown that the utilization of the network, processor, and memory systems can be improved almost in proportion to the number of outstanding transactions allowed [22, 16].

Allowing multiple outstanding transactions in a cache-based multiprocessor opens the window of vulnerability and leads to situations involving livelock.

#### 2.2 Atomicity and Context Switching

In a system that supports multiple outstanding requests through context switching, the ability to perform complex atomic actions efficiently requires the occasional disabling of context switching. For example, we have observed that disabling is essential for performance in the presence of critical sections in a non-preemptive task scheduler. Furthermore, if a thread locks a critical system resource and then is forced to switch out, then performance suffers because many other tasks must wait for the context to

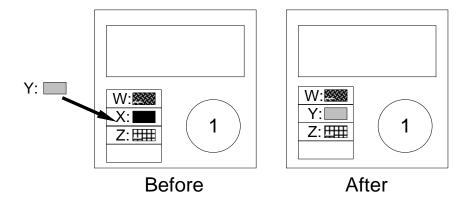

Figure 2-1: The need for high-availability interrupts.

release the lock. Thus, software on a context-switching machine should be able to disable context-switching temporarily. However, as explained in Section 4, this ability places a serious constraint on mechanisms that can be used to prevent livelock.

#### 2.3 High-Availability Interrupts

The third class of mechanisms provides the ability to handle asynchronous, time-critical events under circumstances in which normal interrupts would be ignored. Such *high-availability* interrupts violate instruction atomicity by faulting loads or stores which are in progress. This class of interrupts allows migration of hardware functionality into software.

Figure 2-1 illustrates the need for high-availability interrupts in an architecture that supports fast message handling. In the figure, the processor is spinning while waiting to access a remote memory block. Several messages have entered the processor's input queue before the desired memory response. Consequently, the processor will not make forward progress unless a high-availability interrupt is invoked to process these messages.

In Alewife, for example, high-availability interrupts are used to implement the LimitLESS coherence protocol [9], a fast user and system-level messaging facility, and network deadlock recovery. LimitLESS interrupts must be able to occur under

most circumstances, because they can affect forward progress in the machine, both by deadlocking the protocol and by blocking the network. Since the message passing interface relies on software for queueing, network queueing interrupts must be able to run under most circumstances. The network overflow interrupt relieves potential deadlock situations by redirecting input packets into local memory and relaunching them when the situation has abated.

## Chapter 3

## The Window of Vulnerability

This chapter examines the window of vulnerability in more detail. It first defines several terms, then introduces four distinct types of thrashing which can arise. Finally, it explores the severity of this problem through simulation.

#### 3.1 Preliminaries

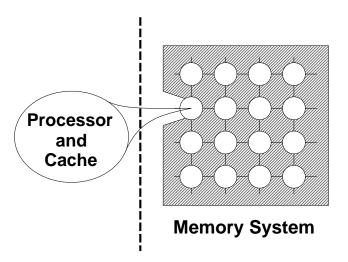

As shown in Figure 3-1, we will consider the memory system, complete with interconnection network, to be a black-box that satisfies memory requests. While this

abstracts away the details of the memory-side of the cache-coherence protocol and

ignores the fact that memory is physically distributed with the processors, it permits

us to focus on the processor-side of the system, where the window of vulnerability

arises. Let us assume, for the sake of discussion, that all requests which are made

to the memory-system are eventually satisfied. Note that this stipulation is difficult

to guarantee in practice and is an interesting topic in its own right; it is, however,

outside the scope of the current discussion.

#### 3.1.1 Forward Progress

Consequently, when we say that a processor (or hardware thread) does or does not make forward progress, we are referring to properties of its local hardware and software, assuming that the remote memory system always satisfies requests.

Figure 3-1: Treat the memory system (complete with network, coherence protocol, and other nodes) as a "black box".

To be more precise, a processor thread makes forward progress whenever it commits an instruction. Given a processor with precise interrupts, we can think of this as advancing the instruction pointer. A load or store instruction can be said to make forward progress if the instruction pointer is advanced beyond it.

#### 3.1.2 Primary and Secondary Transactions

Given this definition of forward progress, we can identify two distinct classes of transactions, *primary* and *secondary*. Primary transactions are those which must complete before some hardware thread in the system can make forward progress. Secondary transactions, on the other hand, are not essential to the forward progress of any thread in the system.

The categories of primary and secondary transactions distinguish between binding memory operations (normal loads and stores) and non-binding memory operations (prefetches). Non-binding prefetches are hints to the memory-system; they specify data items which may be needed in the future. As hints, they can be ignored without affecting the correctness of the computation.

Thus, when handling a prefetch, the memory system may initiate a secondary transaction. Should this transaction be aborted prematurely, it will not affect the forward progress of the processor. However, if the processor later attempts to access

prefetched data via a binding load or store, one of two things can happen:

- 1. The original transaction has been aborted. In this case the memory system will initiate a new, primary transaction. This is as if the prefetch never occurred.

- 2. The secondary transaction is still in progress. Since the forward progress of the processor now depends on the successful completion of the transaction, it is effectively "upgraded" to primary status.

This primary-secondary distinction will appear in later discussion.

#### 3.1.3 Forward Progress and the Window of Vulnerability

Memory models differ in the degree to which they require primary transactions to complete before the associated loads or stores commit. Sequentially consistent machines, for instance, require write transactions (associated with store instructions) to advance beyond the request phase before their associated threads make forward progress. Weakly-ordered machines, on the other hand, permit store instructions to commit before the end of the request phase. In a sense, the cache system promises to ensure that store accesses complete. Therefore, for weakly-ordered machines, write transactions have no window of vulnerability. In contrast, most memory models require a read transaction to receive a response from memory before committing the associated load instruction.

As an example, the Alewife multiprocessor uses memory exception traps to cause context switches. Consequently, data instructions are restarted by "returning from trap," or refetching the faulted instruction. If this instruction has been lost due to cache conflicts, then the context may need to fetch it again before making forward progress. Thus, each context can have *both* a primary instruction transaction and a primary data transaction. In contrast, a processor that saves its pipeline state when context-switching (thereby saving its faulting instruction) would retry only the

<sup>&</sup>lt;sup>1</sup>Note that factoring instructions into this situation also has some interesting pipeline consequences which will be examined in Chapter 5.

faulted data access. Each context in such a processor would have at most one primary transaction at a time.

Unless otherwise noted, this thesis will assume that a hardware context can have no more than one primary data transaction. This assumption has two implications. First, any weakly ordered writes that have not yet been seen by the memory system are committed from the standpoint of the processor. Second, a single context cannot have multiple uncommitted load instructions (as in a processor with register reservation bits). Similarly, we allow no more than one primary instruction transaction at a time. In actuality, these restrictions are not necessary for one of our more important results, the thrashwait algorithm of Section 4.3, but they are required for the thrashlock mechanism of Section 4.5.

#### 3.2 Four Different Livelock Scenarios

This section introduces the four distinct types of livelock or data thrashing which can occur in the processor's cache system. One of these, invalidation thrashing, arises from protocol invalidation for highly contended memory lines. The remaining three result from replacement in a direct-mapped cache. In intercontext thrashing, different contexts on the same processor can invalidate each ether's data. High-availability interrupt thrashing occurs when interrupt handlers replace a context's data in the cache. The last, instruction-data thrashing, appears for processors that context-switch by polling and which must refetch load or store instructions before checking for the arrival of data. Chapter 4 will discuss methods of eliminating these livelock situations.

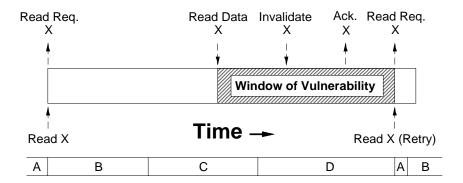

#### 3.2.1 Invalidation Thrashing

Figure 3-2 illustrates the interaction between the window of vulnerability and cache coherence that leads to livelock. The figure gives the currently enabled context in the bar shown under the time-line. The scenario may be interpreted as follows: First, context A of the processor attempts to access memory block X (Read X). Since

the data word is not currently in the processor's cache, the memory system issues a request (Read Req. X) and causes the processor to switch contexts. When the response to the request (Read Data X) returns to the processing node, context C is active. The shaded region indicates the window of vulnerability between the memory system response and the instant that context A is reenabled. During the window, the memory system causes block X to be invalidated from the processor's cache.

Figure 3-3 shows the multi-node scenario that causes this invalidation. There are three processing nodes in the figure: node 1 is the node associated with the time-line in Figure 3-2; node 2 is the home node for block X; and node 3 is the node that causes the interference. Some time after the home node has serviced the request, node 3 issues a write request for block X to node 2. In response, node 2 transmits an invalidation message to node 1, waits for an acknowledgment message, and eventually transmits write permission to node 3. As a result, node 1 must repeat its read request when it reenables context A at the end of the time-line in Figure 3-2.

There is no reason to expect that node 3 will actually complete the write to block X before node 1 repeats its read request! If this is the case, it is possible for node 2 to invalidate block X in node 3 before the write is finished. Given an unfortunate coincidence in timing, this vicious cycle of *invalidation* or *internode* thrashing can continue forever. Our simulations indicate that this thrashing is an infrequent event, but it does happen at some point during the execution of most programs. Without a solution to the thrashing scenario, the system would livelock (effectively causing the machine to crash).

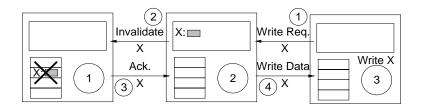

#### 3.2.2 Replacement Thrashing

Due to the limited set-associativity of a processor's cache, different contexts on the same processor can interfere with each other. Figure 3-4 uses a time-line to illustrate this thrashing scenario. Contexts A and C try to access blocks X and Y, respectively. Since blocks X and Y are congruent with respect to the cache mapping (see Figure 3-5), when the data for block Y arrives, it knocks the data for block X out of the cache. Each context prevents the other from making forward progress by replacing cached

Figure 3-2: Time-line illustration of invalidation thrashing. The shaded area is the window of vulnerability.

Figure 3-3: Diagram of cache coherence invalidation.

data during the window of vulnerability. As a consequence of this replacement or intercontext thrashing, a context-switching processor can livelock itself.

#### 3.2.3 High-Availability Interrupt Thrashing

Figure 3-6 demonstrates a special case of replacement thrashing that is caused by high-availability interrupt handlers, rather than by a context-switching processor. The figure shows user code attempting to access memory block X and interrupt code accessing block Y, which maps to the same cache line as X. During a normal memory access, the user code would spin-wait until it received the data associated with block

Figure 3-4: Time-line illustration of replacement thrashing.

Figure 3-5: Diagram of cache replacement.

Figure 3-6: Time-line illustration of high-availability interrupt thrashing.

X. However in this pathological scenario, the user code is interrupted by a high-availability interrupt and forced to execute an interrupt handler. While the processor is handling the interrupt, data block X arrives, but is subsequently replaced when an instruction in the handler references block Y.

Note that all interrupt code can cause this type of thrashing. High-availability interrupt thrashing is particularly important because it can occur even when context-switching has been disabled. This will be revisited in Chapter 4.

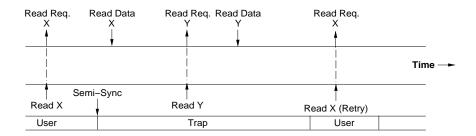

#### 3.2.4 Instruction-Data Thrashing

As discussed in Section 3.1.3, instructions may need to be refetched whenever the processor reenables a context. Figure 3-7 shows a replacement scenario caused by a cache conflict between a load instruction and its data. Here, both the instruction and its data are congruent in the cache. Initial fetching of the instruction proceeds normally. However, when the processor subsequently requests data (Read Data D), it contexts switches, later returning to find that the data has displaced the instruc-

Figure 3-7: Time-line illustration of instruction-data thrashing.

tion. The re-requested instruction, in turn, displaces the data, and a thrashing cycle commences.

Note that instruction-data thrashing is independent of timing, since a single context is competing with itself for resources. Consequently, if an instruction and its data are congruent in the cache and context-switching is permitted on all cache-misses, then instruction-data thrashing will cause deadlock. This is in marked contrast to uniprocessor instruction-data thrashing, which does not cause deadlock but rather degrades performance.

#### 3.2.5 Completeness

The four types of thrashing presented above represent interference to the forward progress of a given context from four different sources:

- A remote processor (invalidation thrashing)

- Another context (intercontext thrashing)

- Interrupt-code (high-availability interrupt thrashing)

- Itself (instruction-data thrashing).

The later three represent all possible instruction-stream related interference on a context-switching processor. Assuming that invalidation is the only vehicle for external interference, our four types of thrashing represent a complete set. Should we discover ways of limiting each of these types of thrashing, then we will be able to guarantee that each processor context is able to make forward progress (assuming that all available cycles are not consumed by interrupt code).

#### 3.3 Severity of the Window of Vulnerability

This section supports the claim that the window of vulnerability poses a significant problem in shared memory architectures. To evaluate our proposed architecture, the Alewife research group constructed a cycle-by-cycle simulation of the processor, network, and cache controller (now called the communications and memory management unit). This simulation environment, called ASIM<sup>2</sup> permits parallel programs that are written in C or LISP (and soon FORTRAN) to be compiled, linked, and executed on a virtual Alewife machine. A copious set of statistics-gathering facilities permit post-mortem analysis of the behavior of the program and machine.

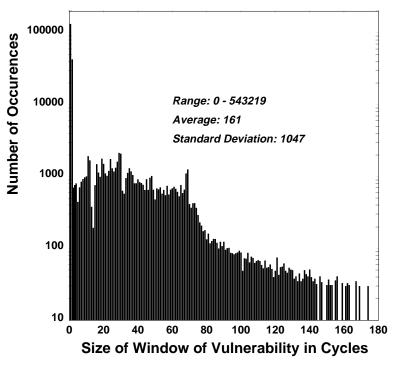

As an example of one of the statistics, the Alewife simulator calculates the time between the instant that a data block becomes valid in a cache due to a response from memory and the first subsequent access to the cached data. The simulator measures this period of time only for the fraction of memory accesses that generate network traffic and are thus susceptible to the window of vulnerability. Figure 3-8 shows typical measurements of the window of vulnerability. The graph is a histogram of window of vulnerability sizes, with the size on the horizontal axis and the number of occurrences on the vertical axis. The graph was produced by a simulation of a 64 processor machine (with 4 contexts per processor) running 1,415,308 cycles of a numerical integration program.

For the most part, memory accesses are delayed for only a short period of time between cache fill and cache access: 90% of memory accesses that generate network traffic have windows that are less than 65 cycles long. However, a small number of accesses encounter pathologically long windows of vulnerability. To make the interesting features of the graph visible, it was necessary to plot the data on a logarithmic scale and to eliminate events having a frequency of less than 30 occurrences. Due to a few extremely long context run-lengths, the tail of this particular graph actually runs out to 543,219 cycles! The high standard deviation provides another measure of

<sup>&</sup>lt;sup>2</sup>For Alewife SIMulator. This simulator has now be supplanted by a simulator which is more faithful to implementation details. ASIM remains a good research tool, however.

Figure 3-8: Window of vulnerability: 64 processors, 4 contexts.

the importance of the graph's tail.

The sharp spike at zero cycles illustrates the role of context switching and high availability interrupts in causing the window of vulnerability. The spike is caused by certain critical sections of the task scheduler that disable context switching, as described in Section 2. When context switching is disabled, a processor will spinwait for memory accesses to complete, rather than attempting to tolerate the access latency by doing other work. In this case, the processor accesses the cache on the same cycle that the data becomes available. Such an event corresponds to a zero-size window of vulnerability. The window becomes a problem only when context switching is enabled or when high availability interrupts interfere with memory accesses.

The window of vulnerability histogram in Figure 3-8 is qualitatively similar to other measurements made for a variety of programs and architectural parameters. The time between cache fill and cache access is usually short, but a small fraction of memory transactions always suffer from long windows of vulnerability. In general, both the average window size and the standard deviation increase with the number of contexts per processor. The window size and standard deviation also grow when the

context switch time is increased. We have observed that high-availability interrupts cause the same type of behavior although their effects are not quite as dramatic as the effect of multiple contexts.

For the purposes of our argument, it does not matter whether the window of vulnerability is large or small, common or uncommon. Even if a window of vulnerability is only tens or hundreds of cycles long, it introduces the possibility of livelock that can prevent an application from making forward progress. The architectural framework described in the next section is necessary merely because the window *exists*.

## Chapter 4

## Closing the Window

This section discusses a range of solutions for eliminating the livelock associated with the window of vulnerability. Three self-contained solutions are discussed, namely associative locking, thrashwait, and associative thrashlock. Each is appropriate for a different combination of the mechanisms of Chapter 2. As summarized in Table 4.1, a system with coherent caches and multiple outstanding requests (Multi) is assumed in all cases. To this is added either the ability to disable context switching (Disable), the presence of high-availability interrupts (HAI), or a combination of both. A Yes in Table 4.1 indicates that a given solution is appropriate for the specified combination of mechanisms. During the exposition, two partial solutions are also discussed, namely locking and associative thrashwait.

|                  |              |         |             | Multi +                  |

|------------------|--------------|---------|-------------|--------------------------|

|                  |              | Multi + | Multi +     | HAI +                    |

|                  | ${ m Multi}$ | Disable | $_{ m HAI}$ | $\operatorname{Disable}$ |

| Assoc Locking    | Yes          | No      | Yes         | No                       |

| Thrashwait       | Yes          | Yes     | No          | No                       |

| Assoc Thrashlock | Yes          | Yes     | Yes         | Yes                      |

Table 4.1: Window of Vulnerability closure techniques. *Multi* represents coherent caches and multiple requests. *Disable* represents disabling of context switching. *HAI* represents high-availability interrupts.

|                  | Prevents     | Prevents     | Prevents    | Prevents  | Deadlock Free  | Free From  |

|------------------|--------------|--------------|-------------|-----------|----------------|------------|

| Technique        | Invalidation | Intercontext | $_{ m HAI}$ | Inst-Data | Context Switch | Cache line |

|                  | Thrashing    | Thrashing    | Thrashing   | Thrashing | Disable        | Starvation |

| Locking          | Ye s         | Yes          | Yes         | Deadlock  | No             | No         |

| Assoc Locking    | Ye s         | Yes          | Ye s        | Yes       | No             | Yes        |

| Thrashwait       | No           | Yes          | No          | Yes       | Yes            | Yes        |

| Assoc TW         | No           | Yes          | Ye s        | Yes       | Yes            | Yes        |

| Assoc Thrashlock | Ye s         | Yes          | Ye s        | Yes       | Yes            | Yes        |

Table 4.2: Properties of window of vulnerability closure techniques with respect to the complete set of features.

Locking involves freezing external protocol actions during the window of vulnerability by deferring invalidations. Thrashwait is a heuristic that dynamically detects thrashing situations and selectively disables context-switching in order to prevent livelock. Associativity can be added to each of these techniques by supplementing the cache with an associative buffer for transactions. This yields associative locking and associative thrashwait. Table 4.2 summarizes the deficiencies of each of these mechanisms with respect to supporting the complete set of mechanisms. Associative thrashlock is a hybrid technique, and is discussed in Section 4.5. Note that only associative thrashlock permits the full set of mechanisms.

#### 4.1 Locking (Partial Solution)

One approach to closing the window involves locking transactions during their window of vulnerability. For the moment, we will assume that returning data (responses) are placed in the cache; later, we consider the addition of an extra set of buffers for memory transactions.

Locking involves two state bits for each line in the cache. To prevent intercontext and high-availability interrupt thrashing, the system needs a *lock* bit to signal that a cache line is locked and cannot be replaced. When the line is accessed, the lock bit associated with the line is cleared. To prevent invalidation thrashing, we need a *deferred invalidate* bit; invalidations to locked lines are deferred by setting this bit. Deferred invalidation is performed (and acknowledged) when the requesting context returns and clears the lock bit.

#### 4.1.1 The Transaction-In-Progress State

One of the consequences of locking cache lines during a transaction's window of vulnerability is that we must also restrict transactions during their request phase. Since each cache line can store only one outstanding request at a time, multiple requests could force the memory system to discard one locked line for another, defeating the purpose of locking. Thus, we supplement the state of a cache line with a transaction-in-progress state to prevent multiple outstanding requests to this line. The transaction-in-progress state restricts creation of new transactions, but does not affect data currently in the cache in order to minimize the interference of memory transactions in the cache. Also, the transaction-in-progress state allows a processing node to consolidate accesses from different contexts to the same memory block.

We refer to this scheme as *touchwait*, because data blocks are held until the requesting context returns to "touch" it. Touchwait eliminates the livelock scenarios of the previous section, because the cache retains data blocks until the requesting context returns to access them.

#### 4.1.2 Premature Lock Release

As described, the above scheme does not quite eliminate all intercontext thrashing, because one context can unlock or touch the data requested by another context. This is called *premature lock release*. Locking can, however, be supplemented with additional bits of state to keep track of which context holds a given lock; then, only the locking context is permitted to free this lock. This can get quite expensive with the simple locking scheme, because these bit must be included in tags-file. However, for other schemes, the cost is less significant; more details will be given in Chapter 5.

#### 4.1.3 Deadlock Problems

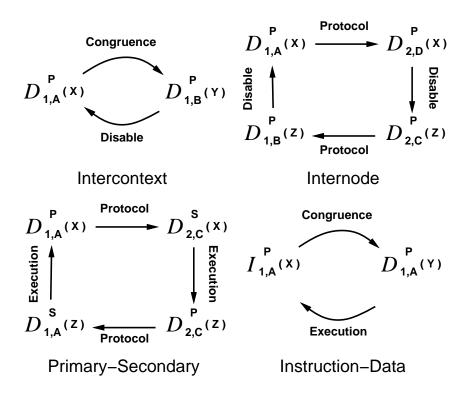

Unfortunately, the locking mechanism can lead to four distinct types of deadlock, illustrated in Figure 4-1. This figure contains four different waits-for graphs [6], which represent dependencies between transactions. In these graphs, the large italic letters

Figure 4-1: Deadlocks that result from pure locking.  $(X \equiv Y, X \neq Z)$

represent transactions: "D" for data transactions and "I" for instruction transactions. The superscripts – either "P" or "S" – represent primary or secondary transactions, respectively. The subscripts form a pair consisting of processor number (as an arabic number) and context number (as a letter). The address is given in parentheses; in these examples, X and Y are congruent in the cache ( $X \equiv Y$ ), while X and X are not equal ( $X \neq Z$ ).

The labeled arcs represent dependencies; a transaction at the tail of an arc cannot complete before the transaction at the head has completed (in other words, the tail transaction waits-for the head transaction). Labels indicate the sources of dependencies: A congruence arc arises from finite associativity in the cache; the transaction at its head is locked, preventing the transaction at its tail from being initiated. An execution arc arises from execution order. Disable arcs arise from disabling context-switching; the transactions at their heads belong to active contexts with context-switching disabled; the tails are from other contexts. Finally, a protocol arc results from the coherence protocol; the transaction at its head is locked, deferring invali-

dations, while the transaction at its tail awaits acknowledgment of the invalidation. An example of such a dependence is a locked write transaction at the head of the arc with a read transaction at the tail. Since completion of the write transaction could result in modification of the data, the read transaction cannot proceed until the write has finished. These arcs represent three classes of dependencies: those that prevent launching of transactions (congruence), those that prevent completion of a transaction's request phase (protocol), and those that prevent final completion (execution and disable).

Now we describe these deadlocks in more detail. Note that larger cycles can be constructed by combining the basic deadlocks.

- intercontext: The context that has entered a critical section (and disabled context-switching) may need to use a cache line that is locked by another context.

- internode: This deadlock occurs between two nodes with context-switching disabled. Here, context A on processor 1 is spinning while waiting for variable X, which is locked in context D on processor 2. Context C on processor 2 is also spinning, waiting for variable Z, which is locked by context B on processor 1.

- **primary-secondary:** This is a variant of the internode deadlock problem that arises if secondary transactions (software prefetches) can be locked. Data blocks from secondary transactions are accessed after those from primary ones.

- instruction-data: Thrashing between a remote instruction and its data yields a deadlock in the presence of locks. This occurs after a load or store instruction has been successfully fetched for the first time. Then, a request is sent for the data, causing a context-switch. When the data block finally returns, it replaces the instruction and becomes locked. However, the data will not be accessed until after the processor refetches the instruction.

Primary-secondary deadlock is easily removed by recognizing that secondary trans-

actions are merely hints; locking them is not necessary to ensure forward progress. Unfortunately, the remaining deadlocks have no obvious solution. Due to these deadlock problems, pure locking cannot be used to close the window of vulnerability.

#### 4.2 Associative Locking

A variant of the locking scheme that does not restrict the use of the cache or launching of congruent transactions is locking with associativity. This scheme supplements the cache with a fully associative set of transaction buffers. Each of these buffers contains an address, state bits, and space for a memory line's data. Locking is performed in the transaction buffer, rather than the cache. As discussed above, invalidations to locked buffers are deferred until the data word is accessed. Buffer allocation can be as simple as reserving a fixed set of buffers for each context. More general schemes might keep track of the context that owns each buffer to prevent premature lock release (see Section 4.1.2). The use of a transaction buffer architecture has been presented in several milieux, such as lockup-free caching [18], victim caching [17], and the remote-access cache of the DASH multiprocessor [23].

The need for an associative match on the address stems from several factors. First, protocol traffic is tagged by address rather than by context number. While requests and responses could be tagged with a context identifier inexpensively, tagging invalidations would increase the cost of the directory used to guarantee cache coherence. Second, associativity removes the intercontext and instruction-data deadlocks of Figure 4-1, because it eliminates all of the *congruence* arcs of Figure 4-1.

Third, the associative match permits consolidation of requests from different contexts to the same memory-line; before launching a new request, the cache first checks for outstanding transactions from any context to the desired memory line. Should a match be detected, generation of a new request is suppressed.

Finally, the associative matching mechanism can permit contexts to access buffers that are locked by other contexts. Such accesses would have to be performed directly to and from the buffers in question, since placing them into the cache would effectively unlock them. This optimization is useful in a machine with medium-grained threads, since different threads often execute similar code and access the same synchronization variables.

The augmentation of basic locking with associativity appears to be close to a solution for the window of vulnerability. All four thrashing scenarios of Section 3.2 are eliminated. Further, the cache is not bogged down by persistent holes. Access to the cache is unrestricted for both user and system code. However, this approach still suffers from internode deadlock when context-switching is disabled. Consequently, as shown in Table 4.1, associative locking is sufficient for systems which do not permit context-switching to be disabled.

#### 4.3 Thrashwait

Locking transactions prevents livelock by making data invulnerable during a transaction's window of vulnerability. To attack the window from another angle, we note that the window is eliminated when the processor is spinning while waiting for data: when the data word arrives, it can be consumed immediately. This observation does not seem to be useful in a machine with context-switching processors, since it requires spinning rather than switching. However, if the processors could context-switch "most of the time," spinning only to prevent thrashing, the system could guarantee forward progress. We call this strategy thrashwait (as opposed to touchwait). The trick in implementing thrashwait lies in dynamically detecting thrashing situations. The thrashwait detection algorithm is based on an assumption that the frequency of thrashing is low. Thus, the recovery from a thrashing scenario need not be extremely efficient.

For the purpose of describing the thrashwait scheme, assume that the system has some method for consolidating transactions from different contexts. To implement this feature, either each cache line or the transaction buffers needs a transaction-in-progress state. If the transaction-in-progress state is in the cache, as in the pure locking scheme, the system allows only one outstanding transaction per cache line.

Consider, for simplicity, a processor with a maximum of one outstanding primary transaction per context; multiple primary transactions will be addressed in the next section. Each context requires a bit of state called a tried-once bit. The memory system sets the bit when the context initiates primary transactions and clears the bit when the context completes a global load or store. Note that global accesses, which involve shared locations and the cache-coherence protocol, are distinguished here from local accesses which are unshared and do not involve the network or the protocol. In addition, there is a single thrash-wait bit which is used to retain the fact that thrashing has been detected on the current access. The algorithm can be described in pseudo-code as follows<sup>1</sup>:

```

Do_Global_Processor_Request(Address, Context)

if (data is ready for Address) \Rightarrow cache hit

2

then clear tried_once[Context]

3

clear thrash_wait

return READY

if (Transaction-in-progress [Address]) \Rightarrow still waiting for transaction

6

then if (thrash_wait or context-switching disabled)

7

then return WAIT

8

else return SWITCH

if (tried\_once[Context]) \Rightarrow detected thrashing!

10

then send RREQ or WREQ

set thrash_wait

11

12

return WAIT

13

\Rightarrow normal cache miss

14

send RREQ or WREQ

set tried\_once[Context]

15

16

if (context-switching disabled)

17

then return WAIT

18

else return SWITCH

```

This function is executed by the cache controller each cycle. The return codes (**READY**, **SWITCH**, and **WAIT**) refer to a successful cache hit, a context-switch request, and a pipeline freeze respectively. **RREQ** is a read request and **WREQ** is a write request.

<sup>&</sup>lt;sup>1</sup>Adapted from Chaiken [10]. The pseudocode notation is borrowed from [11]

The key to the detecting of thrashing is in line 9. This says that the memory system detects a thrashing situation when:

- 1. The context requests a global load or store that misses in the cache.

- 2. There is no associated transaction-in-progress state, because the transaction has completed.

- 3. The context's tried-once bit is set.

The fact that the tried-once bit is set indicates that this context has recently launched a primary transaction but has not successfully completed a global load or store in the interim. Thus, the context has *not* made forward progress.

In particular, the current load or store request must be the same one that launched the original transaction. The fact that transaction-in-progress is clear indicates that the transaction had completed its request phase (data was returned). Consequently, the fact that the access missed in the cache means that a data block has been lost. Once thrashing has been detected, the thrashwait algorithm requests the data for a second time and disables context-switching, causing the processor to wait for the data to arrive.

## 4.3.1 Multiple Primary Transactions

Systems requiring two primary transactions can be accommodated by providing two tried-once bits per context, one for instructions and the other for data. Only a single thrash-wait bit is required. To see why a single tried-once bit is not sufficient, consider an instruction-data thrashing situation. Assuming that a processor has successfully fetched the load or store instruction, it proceeds to send a request for the data, sets the tried-once bit, and switches contexts. When the data block finally arrives, it displaces the instruction; consequently, when the context returns to retry the instruction, it concludes that it is thrashing on the instruction fetch. Context-switching will be disabled until the instruction returns, at which point the tried-once bit is cleared. Thus, the algorithm fails to detect thrashing on the data line.

| Context | Processor Request                                                 | Cache Response         | Cache Actions                                          |

|---------|-------------------------------------------------------------------|------------------------|--------------------------------------------------------|

| 0       | Fetch Load Inst(A)                                                | SWITCH                 | set Inst_TO[0], Send Request (RREQ[A]).                |

| Other   | :                                                                 |                        |                                                        |

| ÷       |                                                                   | :                      | $Cache[A] \leftarrow Instruction$                      |

| Other   | :                                                                 |                        |                                                        |

| 0       | Fetch Load Inst[A]                                                | READY                  | clear Inst_TO[0]                                       |

| 0       | Read Data (B $\equiv$ A)                                          | SWITCH                 | set $Data\_TO[0]$ , $Send Request (RREQ[A])$           |

| Other   | :                                                                 |                        |                                                        |

| :       |                                                                   | :                      | $Cache[B] \leftarrow Read Data (Displace Instruction)$ |

| Other   | :                                                                 |                        |                                                        |

| 0       | $\operatorname{Fetch} \operatorname{Load} \operatorname{Inst}(A)$ | SWITCH                 | set Inst_ $TO[0]$ , Send Request ( $RREQ[A]$ )         |

| Other   | :                                                                 |                        |                                                        |

| :       |                                                                   | :                      | $Cache[B] \leftarrow Instruction \ (Displace \ Data)$  |

| Other   | :                                                                 |                        |                                                        |

| 0       | $\operatorname{Fetch} \operatorname{Load} \operatorname{Inst}(A)$ | READY                  | clear Inst_TO[0]                                       |

| 0       | Read Data (B)                                                     | $\mathbf{WAIT}\dagger$ | Send Request $(RREQ[A])$                               |

| 0       | :                                                                 | WAIT                   |                                                        |

| 0       | Read Data (B)                                                     | WAIT                   | $Cache[B] \leftarrow Read Data (Displace Instruction)$ |

| 0       | Read Data (B)                                                     | READY                  | clear Data_TO[0]                                       |

| 0       | :                                                                 | :                      |                                                        |

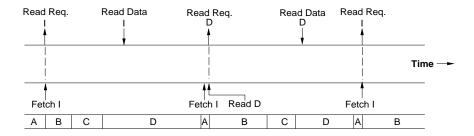

Figure 4-2: Elimination of instruction-data thrashing through Thrashwait. At the point marked with (†), Thrashwait is invoked since Data\_TO[0] is set.

As shown in Figure 4-2, the presence of two separate tried-once bits per context (Inst\_TO and Data\_TO) solves this problem. This figure shows cache requests from context zero (0) during the fetching and execution of a load instruction which is subject to instruction-data thrashing. Note that this ignores pipeline reordering, which will be considered in Chapter 5. The instruction and data accesses are handled independently, according to the above algorithm. In fact, this two-bit solution can be generalized to a system with an arbitrary number of primary transactions. The only requirement for multiple transactions is that each primary transaction must have a unique tried-once bit that can be associated with it each time the context returns to begin reexecution. (This can become somewhat complex in the face of deep pipelining or multiple-issue architectures.)

## 4.3.2 Elimination of Thrashing

The thrashwait algorithm identifies primary transactions that are likely to be terminated prematurely; that is, before the requesting thread makes forward progress. Assuming that there are no high-availability interrupts, thrashwait removes livelock by breaking the thrashing cycle. Thrashwait permits each primary transaction to be aborted only once before it disables the context-switching mechanism and closes the window of vulnerability.

In a system with multiple primary transactions, livelock removal occurs because primary transactions are ordered by the processor pipeline. A context begins execution by requesting data from the cache system in a deterministic order. Consequently, under worst-case conditions – when all transactions are thrashing, the processor will work its way through the implicit order, invoking thrashwait on each primary transaction in turn. Although a context-switch may flush its pipeline state, the tried-once bits remain, forcing a pipeline freeze (rather than a switch) when thrashing occurs.

An example of this would be seen in Figure 4-2 by replacing the first two **READY** responses (both on instructions) into **WAITs** by causing the instruction data to be lost do to conflict with another context. In this absolute worst-case scenario, the instruction would be requested four times and the data would be requested twice; the context would make forward progress, however.

#### 4.3.3 Freedom From Deadlock

In this section, we prove that the thrashwait algorithm does not suffer from any of the deadlocks illustrated in Figure 4-1. We assume (for now) that a processor launches only one primary transaction at a time. Multiple primary transactions, which must complete to make forward progress, are allowed; multiple simultaneous transactions, which are caused by a system that presents several addresses to the memory system at once, are not allowed. At the end of the proof, we discuss a modification to the thrashwait algorithm that is necessary for handling multiple functional units and address buses.

The proof of the deadlock-free property proceeds by contradiction. We assume that the thrashwait algorithm can result in a deadlock. Such a deadlock must be caused by a cycle of primary transactions, linked by the dependencies defined in Section 4.1.3: disable, execution, congruence, and protocol arcs. Since the memory transactions involved in the deadlock loop are frozen, it is correct to view the state of transactions simultaneously, even if they reside on different processors. By examining the types of arcs and the associated transactions, we show that such a cycle cannot exist, thereby contradicting the assumption that thrashwait can result in a deadlock.

Disable and execution arcs cannot participate in a deadlock cycle because these dependencies occur only in systems that use a locking scheme. Since thrashwait avoids locking, it immediately eliminates two forms of dependency arcs. This is the key property that gives thrashwait its deadlock-free property. To complete the proof, we only need to show that congruence and protocol arcs cannot couple to form a deadlock.

A deadlock cycle consisting of congruence and protocol arcs can take only one of three possible forms: a loop consisting only of congruence arcs, a loop consisting of both congruence arcs and protocol arcs, or a loop consisting of only protocol arcs. The next three paragraphs show that none of these types of loops are possible. Congruence and protocol arcs cannot be linked together, due to type conflicts between the head and tail of congruence and protocol arcs.

First, we show that cycles consisting only of congruence arcs cannot occur. Recall that a congruence arc arises when an existing transaction blocks the initiation of a new transaction due to limited cache associativity. A congruence arc requires an existing transaction at its head and a new transaction at its tail. It is therefore impossible for the tail of a congruence arc (a new transaction) to also be the head of a different congruence arc (an existing transaction). Thus, it is impossible to have a loop consisting only of congruence arcs, because the types of a congruence arc's head and tail do not match.

Second, a cycle consisting only of protocol arcs cannot exist. By definition, the head of a protocol arc is a transaction in its window of vulnerability, which is locked

so that invalidations are deferred. The tail of a protocol arc is a transaction in its request phase, waiting for the invalidation to complete. Since a transaction in its request phase cannot be at the head of a protocol arc, protocol arcs cannot be linked together, thereby preventing a loop of protocol arcs.

Finally, the tail of a congruence arc cannot be linked to the head of a protocol arc due to another type conflict: the tail of a congruence arc must be a new transaction, while the head of a protocol arc is an existing transaction in its window of vulnerability. Thus, deadlock loops cannot be constructed from combinations of protocol and congruence loops. The fact that congruence arcs and protocol arcs cannot combine to produce a loop contradicts the assumption that thrashwait can result in a deadlock, completing the proof.

The above proof of the deadlock-free property allows only one primary transaction to be transmitted simultaneously. In order to permit multiple functional units to issue several memory transactions at a time, the memory system must provide sufficient associativity to permit all such transactions to be launched. Also, if the memory system stalls the processor pipeline while multiple transactions are requested, then the processor must access a data word as soon as it arrives. These modifications prevent dependencies between simultaneous transactions and make sure that the window of vulnerability remains closed.

# 4.3.4 Thrashwait and High-Availability Interrupts

Despite its success in detecting thrashing in systems without high-availability interrupts, thrashwait fails to guarantee forward progress in the presence of such interrupts. This is a result of the method by which thrashwait closes the window of vulnerability: by causing the processor to spin. This corresponds to asserting the memory-hold line and freezing the pipeline. High-availability interrupts defeat this interlock by faulting the load or store in progress so that interrupt code can be executed. Viewing the execution of high-availability interrupt handlers as occurring in an independent "context" reveals that the presence of such interrupts reintroduces three of the four types of thrashing mentioned in Section 3.2. Instruction-data and

high-availability interrupt thrashing arise from interactions between the thrashwaiting context and interrupt code. Invalidation thrashing arises because high-availability interrupts open the window of vulnerability, even for transactions that are targeted for thrashwaiting. Only intercontext thrashing is avoided, since software conventions can require high-availability interrupt handlers to return to the interrupted context. Consequently, a system with high-availability interrupts must implement more than the simple thrashwait scheme.

# 4.4 Associative Thrashwait (Partial Solution)

In an attempt to solve the problems introduced by high-availability interrupts, we supplement the thrashwait scheme with associative transaction buffers. As described in Section 4.2, transaction buffers eliminate restrictions on transaction launches. Further, instruction-data and high-availability interrupt thrashing are eliminated. This effect is produced entirely by increased associativity: since transactions are not placed in the cache during their window of vulnerability, they cannot be lost through conflict. Thus, the associative thrashwait scheme with high-availability interrupts is only vulnerable to invalidation thrashing. The framework proposed in the next section solves this last remaining problem.

# 4.5 Associative Thrashlock

Now that we have analyzed the benefits and deficiencies of the components of our architectural framework, we are ready to present a hybrid approach, called *associative thrashlock*. This framework solves the problems inherent in each of the independent components.

Assume, for the moment, that we have a single primary transaction per context. As discussed above, thrashwait with associativity has a flaw. Once the processor has begun thrashwaiting on a particular transaction, it is unable to protect this transaction from invalidation during high-availability interrupts. To prevent high-

availability interrupts from breaking the thrashwait scheme, associative thrashlock augments associative thrashwait with a *single* buffer lock. This lock is invoked when the processor begins thrashwaiting, and is released when the processor completes *any* global access. Should the processor respond to a high-availability interrupt in the interim, the data will be protected from invalidation.

It is important to stress that this solution provides *one* lock per processor. The scheme avoids deadlock by requiring that all high-availability interrupt handlers:

- 1. Make no references to global memory locations, and

- 2. Return to the interrupted context.

These two software conventions guarantee that the processor will always return to access this buffer, and that no additional dependencies are introduced<sup>2</sup>. Thus, associative thrashlock has the same transaction dependency graph as thrashwait without high-availability interrupts (as in Section 4.3.3). Processor access to the locked buffer is delayed – but not impeded – by the execution of high-availability interrupts.

Application of the above solution in the face of multiple primary transactions (such as instruction and data) is not as straightforward as it might seem. We provide a lock for both instructions and data (in addition to the two tried-once bits specified in Section 4.3.1). When thrashing is detected, the appropriate lock is invoked.

This locking scheme reintroduces a deadlock loop similar to the primary-secondary problem discussed earlier. Fortunately, in this case the loop is rather unnatural: it corresponds to two processors, each trying to fetch instruction words that are locked as data in the other node. To prevent this particular kind of deadlock, a software convention disallows the execution of instructions that are simultaneously being written. Prohibiting modifications to code segments is a common restriction in RISC architectures. Another method for preventing this type of deadlock is to make instruction accesses incoherent. Since invalidations are never generated for instructions, the effect of the lock is nullified (no protocol arcs).

<sup>&</sup>lt;sup>2</sup>As will be shown in Chapter 5, the first condition can be relaxed somewhat, easing the burden of the runtime system.