## Compiler Analysis to Implement Point-to-Point Synchronization in Parallel Programs

by John Nguyen

S.B., Computer Science S.B., Mathematics Massachusetts Institute of Technology (1987)

S.M., Electrical Engineering and Computer Science Massachusetts Institute of Technology (1989)

Submitted to the Department of

ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

August 1993

All rights reserved

© 1993 Massachusetts Institute of Technology

| Signature of Author: _ |                                                                                       |

|------------------------|---------------------------------------------------------------------------------------|

|                        | Department of Electrical Engineering and Computer Science<br>August 13, 1993          |

| Certified by:          |                                                                                       |

| J                      | Stephen A. Ward<br>Professor of Computer Science and Engineering<br>Thesis Supervisor |

| Accepted by:           |                                                                                       |

| - 1000ptou 25.         | Frederic R. Morgenthaler                                                              |

Chairman, Department Committee on Graduate Students

## Compiler Analysis to Implement Point-to-Point Synchronization in Parallel Programs

by John Nguyen

Submitted to the Department of Electrical Engineering and Computer Science on August 13, 1993 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

## **Abstract**

The shared-memory data-parallel model presents an attractive interface for programming multiprocessors by allowing for easy management of parallel tasks while hiding details of the underlying machine architecture. Unfortunately, the shared-memory abstraction requires synchronization in order to maintain data consistency. Present compilers provide consistency between parallel code sections by enforcing a global point of synchrony with a barrier synchronization. Such a simple mechanism possesses several disadvantages. First, the required global collection of information generates significant overhead which leads machine designers to employ special hardware to support barriers. Second, global synchronization reduces parallelism by requiring needless serialization of independent tasks. This work aims to reduce the costs associated with these disadvantages by generating pairwise point-to-point synchronization between specific tasks.

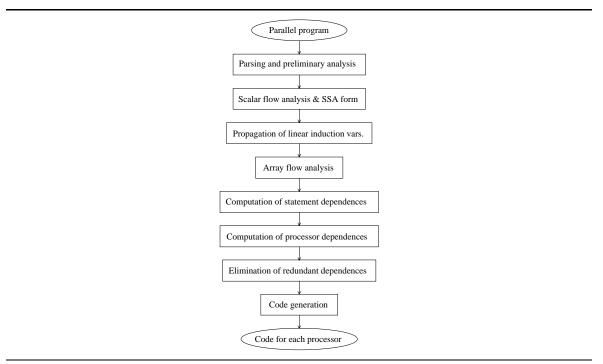

Implementation of point-to-point synchronization demands extensive analysis of program dependences. A compiler must perform flow analysis and dependence testing in order to compute lexical dependences between program statements. In addition, dynamic dependences between processors must be computed by examining array references and statement contexts. The final synchronization scheme must support any dependences that arise in the program while ensuring that no deadlock scenarios can occur. This work proposes algorithms that satisfy such requirements and presents some encouraging results from a preliminary implementation.

Thesis Supervisor: Stephen A. Ward

Title: Professor of Electrical Engineering and Computer Science

# Acknowledgments

In finishing a work that represents the culmination of my many years at MIT, I owe my gratitude to many people whose contributions range from technical advice to non-academic diversions to general support and encouragement.

I thank my advisor, Steve Ward, for his constructive questions that have enabled me to more clearly grasp my thoughts, for his attitude that has made the NuMesh group such a fun and interesting place to work, and for his support that has allowed me to grow as a person during my years with the group.

My readers, Anant Agarwal and Greg Papadopoulos, have helped me greatly to focus on a thesis topic and provided advice and encouragement which have made the process much smoother.

Many members of the NuMesh group and the Computer Architecture Group have contributed to make the last six years enjoyable. In particular, I would like to thank Gill Pratt for supplying some interesting collaborations, Andy Ayers for providing thesis discussion and commiseration, and my officemate Milan Singh for putting up with my thesis ramblings. I would also like to thank the group assistant, Anne McCarthy, for tackling the bureaucracy in my behalf.

The people who have been a part of the Vile Servers volleyball team through the years have provided a great source for camaraderie, friendly competition, and steady release from the pressures of work.

My roommate of many years, Bill Schmitt, and Tony Bogner have supplied numerous interesting diversions ranging from road trips to the many late-night card games. I would also like to thank the New House IV alumni who comprise the "gang" e-mail list for the jokes, brain teasers, and reunions.

I would like to thank my fiance, Tricia, for being an endless source of support and encouragement, for making the best of a long-distance relationship with a graduate student, and for her friendship.

Finally, I would like to thank my parents for their guidance, generosity, and love through the years. My accomplishments would not have been possible without their support.

This work has been sponsored in part by a National Science Foundation Fellowship, in part by DARPA contract #DABT63-93-C-0008, and in part by Texas Instruments.

# **Table of Contents**

| 1. | Intro | oduction                                         | 15 |

|----|-------|--------------------------------------------------|----|

|    | 1.1.  | Related work                                     | 16 |

|    | 1.2.  | Problem identification                           | 18 |

|    | 1.3.  | Approach                                         |    |

|    |       | 1.3.1. Synchronization variables                 |    |

|    |       | 1.3.2. Computing statement dependences           |    |

|    |       | 1.3.3. Computing processor dependences           |    |

|    |       | 1.3.4. Optimizing point-to-point synchronization |    |

|    |       | 1.3.5. Variable replication                      | ۷4 |

|    | 1.4.  | Thesis outline                                   | 26 |

|    |       |                                                  |    |

| 2. | Back  | ground                                           | 29 |

|    | 2.1.  | Language description                             | 29 |

|    | 2.2.  | Control flow graph                               | 30 |

|    | 2.3.  | Machine model                                    | 33 |

|    |       |                                                  |    |

| 3. | State | ement dependences                                | 35 |

|    | 3.1.  | Introduction                                     | 35 |

|    | 3.2.  | Propagation of linear induction variables        | 35 |

|    |       | 3.2.1. Value lattices                            | 36 |

|    |       | 3.2.2. Propagation of linear induction variables | 39 |

|    | 3.3.  | Flow analysis on arrays                          | 43 |

|    |       | 3.3.1. Linear integer sequences                  | 44 |

|    |       | 3.3.2. Summary of array index approximations     |    |

|    |       | 3.3.3. Subarrays                                 |    |

|    |       | 3.3.4. Array flow analysis algorithm             |    |

|    |       | 3.3.5. Flow analysis on multi-dimensional arrays |    |

|    |      | 3.3.6.  | Related work                                    | 54 |

|----|------|---------|-------------------------------------------------|----|

|    | 3.4. | Detect  | ion of dependences                              | 54 |

|    |      | 3.4.1.  | Invariant expressions                           | 58 |

|    | 3.5. | Interp  | rocedural support                               | 59 |

|    | 3.6. | Other   | applications of array flow analysis             | 60 |

|    |      | 3.6.1.  | Parallelism detection                           | 61 |

|    |      | 3.6.2.  | Private variable detection                      | 61 |

|    |      | 3.6.3.  | Data and loop partitioning                      | 62 |

|    |      | 3.6.4.  | Static routing of data                          | 63 |

|    | 3.7. | Summ    | ary                                             | 63 |

| 4. | Proc | essor d | lependences and synchronization                 | 65 |

|    | 4.1. | Introd  | uction                                          | 65 |

|    | 4.2. | Motiva  | ation                                           | 65 |

|    |      | 4.2.1.  | Synchronization model                           | 66 |

|    |      |         | Implementation issues                           |    |

|    |      | 4.2.3.  | Termination issues                              | 70 |

|    | 4.3. | Overv   | iew of processor dependences                    | 71 |

|    | 4.4. | Dynan   | nic instances of statements                     | 73 |

|    | 4.5. | Derivi  | ng synchronization relationships                | 75 |

|    |      | 4.5.1.  | The problem                                     | 75 |

|    |      | 4.5.2.  | Orthogonal derivation of instance relationships | 76 |

|    |      | 4.5.3.  | Instance relationships                          | 77 |

|    |      | 4.5.4.  | Related work                                    | 79 |

|    | 4.6. | Execut  | tion model of parallel loops                    | 80 |

|    | 4.7. | Execut  | tion order of statement instances               | 85 |

|    | 4.8. | -       | utation of synchronization targets              |    |

|    |      |         | Motivation                                      |    |

|    |      |         | Static computation of synchronization targets   |    |

|    |      |         | Framework for deducing processor targets        |    |

|    |      | 484     | Computation of processor targets                | 94 |

|    |       | 4.8.5. Computation of temporal targets4.8.6. An example                                                                                                                                                                  |                          |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|    | 4.9.  | Implementation issues                                                                                                                                                                                                    | 102                      |

|    | 4.10. | Deadlock avoidance                                                                                                                                                                                                       | 105                      |

|    | 4.11. | DOACROSS loops                                                                                                                                                                                                           | 109                      |

|    | 4.12. | Summary                                                                                                                                                                                                                  | 110                      |

| 5. | Opti  | mizations                                                                                                                                                                                                                | 113                      |

|    | 5.1.  | Introduction                                                                                                                                                                                                             | 113                      |

|    | 5.2.  | Synchronization by message-passing                                                                                                                                                                                       | 113                      |

|    | 5.3.  | Redundant dependences  5.3.1. Motivation  5.3.2. Problem definition  5.3.3. A solution for a simple problem domain  5.3.4. General removal of redundant dependences  5.3.5. Redundant dependences in structured programs | 117<br>117<br>119<br>125 |

|    | 5.4.  | Eliminating false dependences                                                                                                                                                                                            | 130                      |

|    | 5.5.  | Summary                                                                                                                                                                                                                  | 135                      |

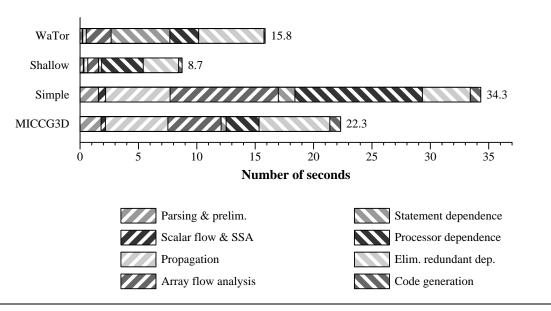

| 6. | Resu  | ılts                                                                                                                                                                                                                     | 137                      |

|    | 6.1.  | Applications                                                                                                                                                                                                             | 137                      |

|    | 6.2.  | Simulation environment                                                                                                                                                                                                   | 139                      |

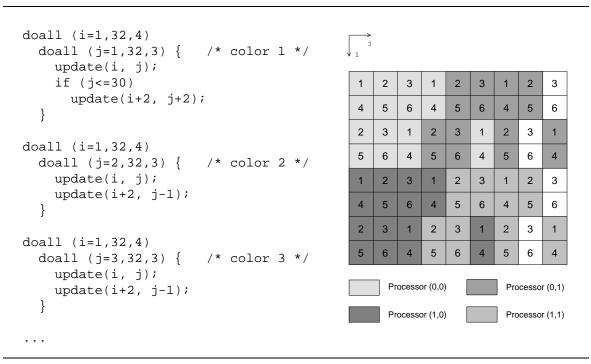

|    | 6.3.  | An example                                                                                                                                                                                                               | 141                      |

|    | 6.4.  | General application study                                                                                                                                                                                                | 147                      |

|    | 6.5   | Summary                                                                                                                                                                                                                  | 152                      |

| 7. | Future work                       | 153 |

|----|-----------------------------------|-----|

|    | 7.1. Introduction                 | 153 |

|    | 7.2. Multiple loop indices        | 153 |

|    | 7.3. Interprocedural analysis     | 154 |

|    | 7.4. Synchronization groups       | 155 |

|    | 7.5. Partitioning                 | 157 |

|    |                                   |     |

| 8. | Conclusion                        | 161 |

|    | 8.1. Summary                      | 161 |

|    | 8.2. Contributions of this thesis | 163 |

|    |                                   |     |

|    | Bibliography                      | 165 |

|    | Index of terms                    | 175 |

|    | muex of terms                     | 1/5 |

|    | Index of notation                 | 177 |

# **Table of Figures**

| Figure 1.1  | 17 |

|-------------|----|

| Figure 1.2  | 18 |

| Figure 1.3  | 18 |

| Figure 1.4  | 20 |

| Figure 1.5  | 21 |

| Figure 1.6  | 21 |

| Figure 1.7  | 23 |

| Figure 1.8  | 25 |

| Figure 1.9  | 25 |

| Figure 1.10 |    |

|             |    |

| Figure 2.1  | 29 |

| Figure 2.2  | 30 |

| Figure 2.3  | 31 |

|             |    |

| Figure 3.1  | 36 |

| Figure 3.2  | 37 |

| Figure 3.3  | 38 |

| Figure 3.4  | 39 |

| Figure 3.5  | 41 |

| Figure 3.6  | 42 |

| Figure 3.7  | 44 |

| Figure 3.8  | 47 |

| Figure 3.9  | 50 |

| Figure 3.10 | 51 |

| Figure 3.11 |    |

| Figure 3.12 |    |

| Figure 3.13 |    |

| Figure 3.14 |    |

| Figure 3.15 |    |

| Figure 3.16 |    |

| Figure 3.17 |    |

| rigure 5.17 | 10 |

| Figure 3.18 | 62          |

|-------------|-------------|

| Figure 4.1  | 67          |

| Figure 4.2  | 68          |

| Figure 4.3  | 69          |

| Figure 4.4  | 69          |

| Figure 4.5  | 70          |

| Figure 4.6  | 71          |

| Figure 4.7  | 72          |

| Figure 4.8  | 78          |

| Figure 4.9  | 80          |

| Figure 4.10 | 81          |

| Figure 4.11 | 83          |

| Figure 4.12 | 85          |

| Figure 4.13 | 88          |

| Figure 4.14 | 90          |

| Figure 4.15 | 98          |

| Figure 4.16 | 100         |

| Figure 4.17 | 103         |

| Figure 4.18 | l <b>04</b> |

| Figure 4.19 | 108         |

| Figure 5.1  | l 14        |

| Figure 5.2  | l 15        |

| Figure 5.3  | l 17        |

| Figure 5.4  | 118         |

| Figure 5.5  | 119         |

| Figure 5.6  | 121         |

| Figure 5.7  | 123         |

| Figure 5.8  | 124         |

| Figure 5.9  | 127         |

| Figure 5.10 | 128         |

| Figure 5.11 | 130         |

| Figure 5.12 | 131         |

| Figure 5.13 | 132         |

| Figure 5.14 | 132         |

| Figure 5.15    |

|----------------|

| Figure 5.16    |

| Figure 6.1     |

| Figure 6.2     |

| Figure 6.3     |

| Figure 6.4     |

| Figure 6.5     |

| Figure 6.6     |

| Figure 6.7     |

| Figure 6.8     |

| Figure 6.9     |

| Figure 6.10    |

| Figure 6.11    |

| Figure 7.1 153 |

| Figure 7.2     |

| Figure 7.3     |

| Figure 7.4     |

| Figure 7.5     |

| Figure 7.6     |

# **Chapter 1**

## Introduction

The concept of devoting many processing elements to one task in order to increase performance has existed for several decades. Implementations of this concept vary from early array processors such as the Illiac IV [Bou72] to the more decoupled MIMD machines of today [Smi78][Sei85][Thi91]. Early array processors and SIMD machines allow parallelism through repeated application of a single computation or instruction to different data. Though this sort of concurrency is effective for certain program domains, the inability to follow different instructions and control paths in parallel reduces its generality. On the other hand, MIMD machines allow each processor to follow independent asynchronous programs with a data communication network forming the only link between processors. However, this independence comes at a price: Explicit synchronization must be performed to ensure correct ordering of accesses to shared memory.

This thesis focuses on the domain of programs that make extensive use of parallel loops and arrays to express data parallelism. The common model for invoking such programs on multiprocessors involves two modes of execution: sequential and parallel. Sequential code segments are executed on a single processor or host, while parallel code can be executed on all processors. Sections of code containing parallel instructions can be represented as DOALL loop statements which specify that all iterations can be executed in parallel. On array and SIMD machines, the transition between parallel and sequential sections comes at no additional cost since all processors execute in lock-step. On MIMD machines, a barrier synchronization is typically performed between parallel and sequential sections to ensure correctness of results. When a barrier synchronization appears in a program, no processors can proceed past the barrier point until all processors have reached that point.

The barrier synchronization allows MIMD machines to follow the SIMD model of program execution by requiring all processors to wait at the barrier point until all other processors have arrived at that point. On machines with many processors, this global propagation of information can require a significant amount of time to execute. Equally importantly, barrier synchronizations can force serialization of operations on different

processors even when no dependences exist between them. If parallel loop iterations possess fairly dynamic control flow, this can result in unnecessary idling and imply that the time required to execute each loop is equal to the maximum time required by any processor [DH88]. With a more decoupled synchronization scheme, consecutive loops can be allowed to stagger, thus providing higher processor utilization. The above disadvantages can be addressed by employing a point-to-point synchronization scheme in which processors synchronize individually with other processors.

#### 1.1 Related work

Barrier synchronization has become popular as a necessary tool for implementing the SPMD (Single Program Multiple Data) model on MIMD machines. Consequently, many efforts have been made to reduce the potentially high expense of this operation [Pol88][AJ87]. However, many of these schemes still rely on global propagation and do not address the problem of processor idling at barrier points.

"Fuzzy" barriers [Gup89] reduce idling by breaking barrier synchronization into two phases: signaling and waiting. In conventional execution, a processor arrives at the barrier point, signals that it has arrived at that point, then waits until all other processors have signaled their arrival. In the fuzzy barrier scheme, a processor can signal ahead of its arrival at the barrier point, thus allowing it to execute instructions before waiting. A compiler can schedule signals at the earliest possible point in order to maximize processor utilization. Although fuzzy barriers offer improved performance, they still suffer from some of the same disadvantages of barrier synchronization. The overhead of accumulating and transmitting information globally still scales as the log of the number of processors. In addition, the number of instructions that can be scheduled between signaling and waiting is dependent on the particular program. If accesses that require the barrier cannot be moved very far apart at compilation, then processors still spend a large amount of time idle.

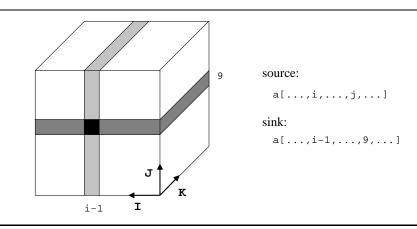

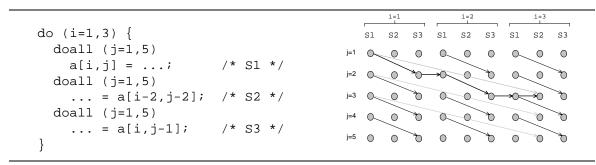

A point-to-point synchronization scheme for DOACROSS loops is presented in [MP87]. Even though all iterations of a DOACROSS loop can be executed in parallel, dependences can exist between iterations. In Figure 1-1a, the definition and use of elements of array a in different iterations imply that synchronization must be performed between those iterations. A compiler can automatically insert synchronization primitives (represented as boldface pseudocode) for any such dependences and thereby allow all loop iterations

to be executed in parallel without implicit scheduling constraints. The same dependence patterns that exist between iterations of DOACROSS loops can also occur with DOALL loops as shown in Figure 1-1b. Before reading an element of the array a, a processor must synchronize with the write event of that element which occurs in a previous iteration of i. Consequently, the analysis done in this thesis must deal with all the issues that arise in synchronization within DOACROSS loops. In addition, synchronization across DOALL loops requires consideration of dependences between separate loops, which is not considered in [MP87].

```

do (i=1,100) {

doall (j=1,50)

a[i] = ...;

a[i] = ...;

doall (j=1,50) {

synch with iteration i-5

... = a[i-5];

}

(a)    (b)

```

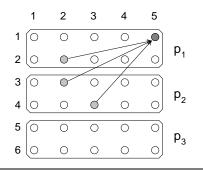

Figure 1-1

While synchronization for DOACROSS loops requires study of dependences across loop iterations, dependences within a loop iteration or within a general sequence of statements are considered in [CHH89]. A sequence of statements can be mapped into a directed acyclic graph of code blocks with edges representing dependences between blocks. Since each block can be executed by a different processor, synchronization must be performed for each edge in the graph. In Figure 1-2a, the definition and use of variable a by different processors requires synchronization between the writing and reading statement blocks. Such dependences between different statements in a sequence also arise when one considers DOALL loops. As shown in Figure 1-2b, the definition and use of array a also requires synchronization between two different statements in a sequence. In general, for any situation that arises in DAG dependences, an equivalent scenario exists in the context of DOALL loops. In addition, synchronization between DOALL loops must be concerned with groups of processors that execute each loop rather than merely synchronizing between single processors that execute each node in a DAG.

Figure 1-2

#### 1.2 Problem identification

Despite its disadvantages, the barrier synchronization is the simplest and most general method of forcing correct ordering of execution in parallel programs. However, many loop-based programs contain array references that are generally linear functions of loop indices, thus providing statically-obtainable dependence information between individual elements [SLY89]. This thesis aims to use that dependence information to implement point-to-point synchronization schemes which can reduce the costs associated with barrier synchronization.

Figure 1-3

Consider the code fragment in Figure 1-3. Let us assume that each DOALL iteration j is performed on a separate processor  $P_j$  on a shared-memory machine and arrays A and B are partitioned similarly. If no synchronization is performed, one can imagine the scenario where processor  $P_1$  assigns to B[1], then assigns to A[1], then assigns to B[1] again before processor  $P_2$  can read the first value of B[1]. Consequently, the result of a program can be incorrect due to data dependence violations. To rectify this problem, a barrier synchronization is typically inserted after each DOALL loop as indicated in the above example. This solution has the effect of serializing the execution of DOALL loops,

thus providing correct if not efficient execution. In order to place synchronizations more strategically, data dependence analysis must be performed.

A data dependence arises when the order of two accesses to a memory location must be preserved in order to ensure correctness. Since two read accesses do not require an ordering, a dependence only occurs when one of the accesses is a write to memory. Dependences can be classified into three types:

- Flow dependence: a write must be performed before a read.

- Anti-dependence: a read must be performed before a write.

- Output dependence: a write must be performed before another write.

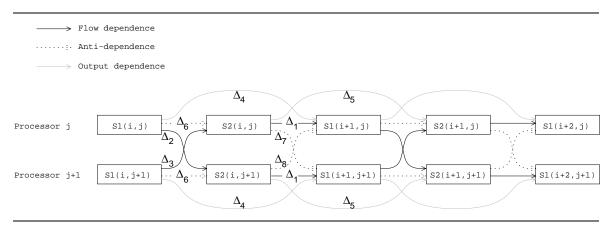

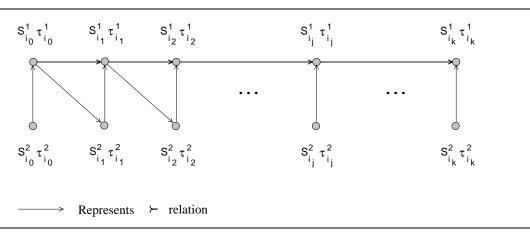

In order to specify exact iterations of the program, invocations of statements will be labeled by the value of loop indices. For example, the invocation of statement S1 in Figure 1-3 with I=5 and J=6 will be labeled as S1(5,6). A statement invocation S1(*i*) that is flow-dependent on S2(*i'*) is written as S1(*i*)  $\delta^f$  S2(*i'*), an output dependence is indicated as S1(*i*)  $\delta^o$  S2(*i'*), while S1(*i*)  $\overline{\delta}$  S2(*i'*) represents an anti-dependence. The following dependences exist for Figure 1-3 and are illustrated in Figure 1-4.

$$S2(i,j) \delta^f S1(i+1,j)$$

( $\Delta_1$ )

$$S1(i, j) \delta^f S2(i, j+1)$$

( $\Delta_2$ )

$$S1(i, j) \delta^f S2(i, j-1)$$

( $\Delta_3$ )

$$S1(i, j) \delta^o S1(i+1, j)$$

( $\Delta_4$ )

$$S2(i, j) \delta^{o} S2(i+1, j)$$

(\Delta\_{5})

$$S1(i, j) \overline{\delta} S2(i, j)$$

( $\Delta_6$ )

$$S2(i, j) \overline{\delta} S1(i+1, j+1)$$

(\Delta\_7)

$$S2(i,j) \overline{\delta} S1(i+1,j-1)$$

( $\Delta_8$ )

For a particular processor partitioning scheme, there exists an ordering on the execution of some statement invocations. When two statement invocations are assigned to the same processor, the order of their execution is predetermined. Let S1(i,j) < S2(i',j') denote the fact that S1(i,j) must execute before S2(i',j'). Note that the < relation is anti-reflexive and transitive. If we assume that each DOALL iteration j

Figure 1-4: Dependence graph for Figure 1-3

of the current example is assigned to processor  $P_j$ , then the following ordering arises:

$$S1(i, j) < S2(i, j)$$

$S2(i, j) < S1(i + 1, j)$

When processor execution obeys this ordering, some dependences are automatically satisfied, such as  $\Delta_1$ ,  $\Delta_4$ ,  $\Delta_5$ , and  $\Delta_6$  in the current example. The remaining dependences  $\Delta_2$  and  $\Delta_3$  are satisfied by barrier #1 and  $\Delta_7$  and  $\Delta_8$  are satisfied by barrier #2. If point-to-point synchronization can be performed for those dependences, then the barrier synchronizations can be eliminated.

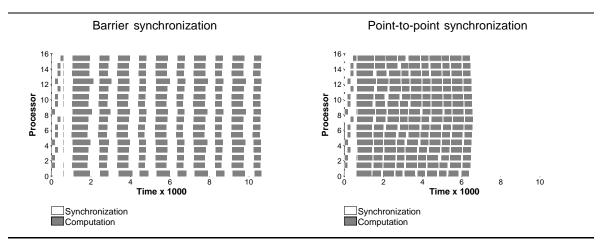

Figure 1-5

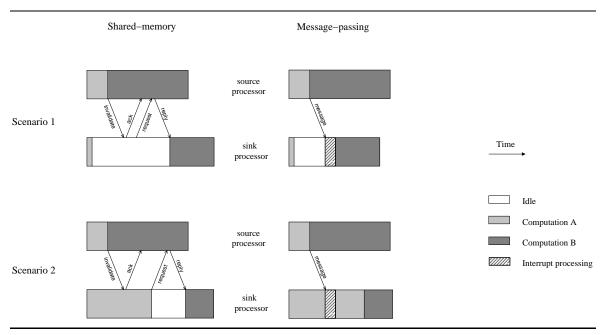

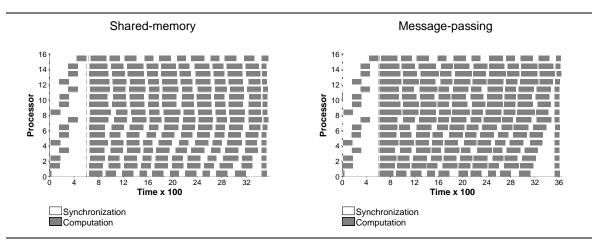

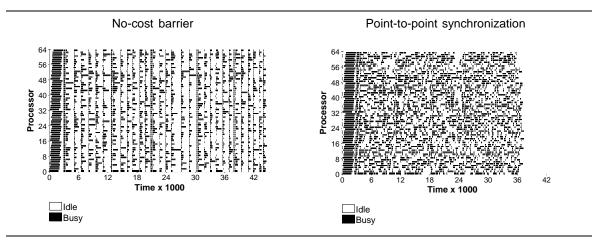

shows execution profiles of the above example on a 16-processor machine. The barrier-synchronization profile uses a tree-based software barrier which requires around 450 cycles. Dark areas represent non-synchronization processing while light areas represent idle time waiting for or performing synchronization. One can see that the 450-cycle overhead for global propagation adds significantly to the overall running time of the application. Moreover, one can also observe that the point-to-point scheme allows for more computation skew among processors which can improve performance in other applications.

## 1.3 Approach

In order to reduce synchronization costs in loop-based parallel programs, this thesis proposes replacing barrier synchronizations with point-to-point synchronization schemes. The realization of this goal involves careful study of the topics outlined below.

SECTION 1.3: APPROACH 21

Figure 1-5: Execution of 5 iterations of Figure 1-3

## 1.3.1 Synchronization variables

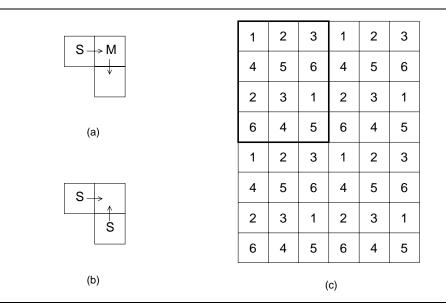

Point-to-point synchronization can be implemented by the use of a shared variable which indicates the current loop iteration of each processor as in [MP87]. Before fully completing each DOALL iteration in the previous example, each processor updates a synchronization variable to indicate that it has finished that particular iteration.

Figure 1-6

In Figure 1-6, the synchronization arrays sync1 and sync2 are partitioned like the arrays a and b, so for example, processor  $P_j$  "owns" element sync1[j]. For any dependence, a processor executing the statement that is on the right of the dependence must wait until a processor has executed the statement on the left of the dependence. This is accomplished by setting and waiting for appropriate values in the sync arrays. Although there is a spin-locking action on elements of the sync arrays, no extra network

traffic is induced on machines with caching schemes that allow shared copies of variables.

#### 1.3.2 Computing statement dependences

In order to determine processor synchronization requirements, dependences between statements of a program need to be computed. The calculation of such data dependence information can be adapted primarily from two areas of research: sequential data-flow analysis and array-dependence analysis for parallelizing DO loops.

Standard data-flow analysis techniques [ASU86] can provide definition-use chains for computing flow dependences. The algorithms can also be adapted to generate information necessary for calculating output and anti-dependences. Unfortunately, these techniques are primarily concerned with scalar variables and pay little attention to flow information on individual array elements. In order to effectively compute dependence information for point-to-point synchronizations, the scalar flow analysis framework must be augmented to operate on arrays and subsets of arrays as specified by linear index functions. Although questions involving relations on such sets requires the application of linear diophantine equation theory, previous work in the field of array-dependence analysis can be used to provide the answers.

A large amount of work has been done on calculating dependences between arrays for loop parallelization [Ban88][Wol89]. However, such works are primarily concerned with dependences within a loop body rather than dependences between separate loops that require more detailed attention to program control flow. In addition, these works are only concerned with the question of whether a dependence exists between two statements. In order to compute point-to-point synchronizations, this question needs to be extended to include the calculation of the exact data elements that are involved in a dependence, as discussed in the following section.

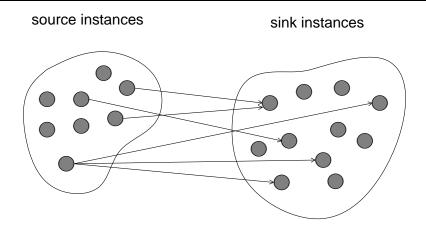

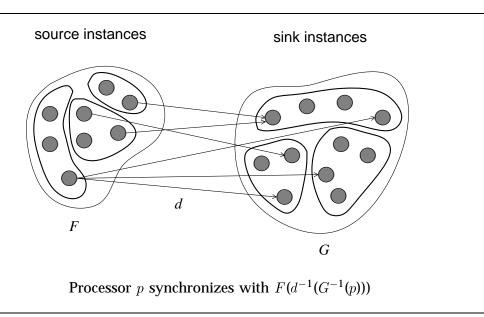

#### 1.3.3 Computing processor dependences

Point-to-point synchronization can replace barrier synchronization effectively in cases where data dependences can be determined at compile time. In other words, synchronization should only be inserted when the source and sink processors can be computed efficiently. Although the above array data flow analysis provides the information on dependences between statements, it does not yield information on dependences between

SECTION 1.3: APPROACH 23

processors. In order to compute interprocessor dependence relations, more analysis must be done on array access patterns.

In the examples presented thus far, dependence relations between processor can be derived in a straightforward manner from the array accesses. Indeed, when two array indices contain linear functions of the same loop index, dependence relations can be computed easily from the linear functions. However, more difficult cases exist. Array access patterns can relate loop indices that occur at different nesting levels and in different loop nests. Loop indices can occur multiply in some array references and not at all in others. Some of these situations are illustrated in Figure 1-7.

```

do (i=1,100) {

do (j=1,100) {

doall (k=1,100)

a[i,i,k+1] = ...;

...

doall (k=1,100)

... = a[i-3,k,x];

}

}

```

Figure 1-7

## 1.3.4 Optimizing point-to-point synchronization

Point-to-point synchronization can be inserted once dependence information is obtained. However, this insertion process must be done intelligently to maintain the ultimate goal of faster program execution. Since testing of synchronization variables can result in additional network traffic and increased latency, synchronizations produced by redundant dependences must be eliminated.

To reduce execution time, the checking of synchronizations must result in as little delay as possible. Consequently, setting the values of synchronization variables should be done at the earliest possible point. With straight-line code, this problem seems trivial since one could easily enforce the constraint that synchronizations be set immediately after the source of the dependence is satisfied. However, in the presence of conditionals, each synchronization variable must be set in every control path to any check of that variable. In other words, if the source of a dependence does not dominate the sink, then

the corresponding synchronization variable must be set in other paths to the sink. Any scheme to reduce idle time must obey this condition for correctness.

In previous examples, synchronization is performed for every dependence that exists in the program. Several steps can be taken to reduce the number of synchronization operations required. In typical programs, many dependences are automatically satisfied by synchronization provided for other dependences. As an example, assume that  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  are statements in a straight-line program such that each  $S_i$  precedes  $S_{i+1}$ . If a dependence  $\Delta_1$  exists between  $S_2$  and  $S_3$  and another dependence  $\Delta_2$  exists between  $S_1$  and  $S_4$ , and  $\Delta_1$  and  $\Delta_2$  have the same processor relationships, then there is no need to support  $\Delta_2$  with synchronization since the processors are already synchronized due to  $\Delta_1$ . Thus when two processors are already synchronized due to other dependences, then a dependence between the two processors is redundant and can be eliminated. Reduction of redundant synchronization has been studied in the context of DOACROSS loops in [MP87] and [KS91]. In these works, redundant dependences can be defined as duplicate edges in the transitive closure of the dependence graph. Again, as applied to this thesis, the analysis is required to be more complex due to interactions between data dependences and control flow. In this context, calculating the minimum number of dependences for a given program is a problem of both theoretical and practical interest. A related optimization to the above involves replicating variables to cause output and anti-dependences to become redundant, as discussed in the following section.

### 1.3.5 Variable replication

In a single-assignment language, output and anti-dependences cannot occur because variables can hold only one value. In an imperative language, variables can be renamed or replicated to avoid these dependences in certain circumstances, although at a cost in memory usage [Kum87].

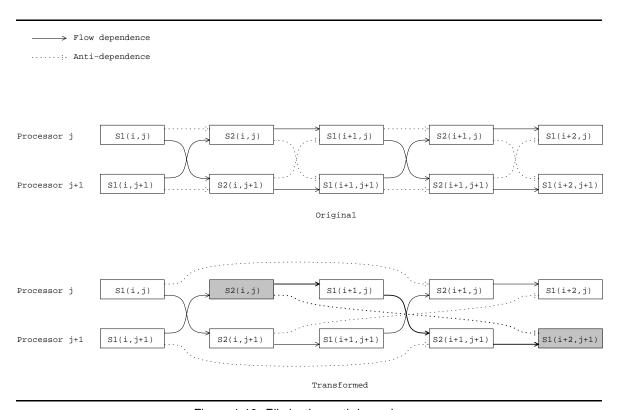

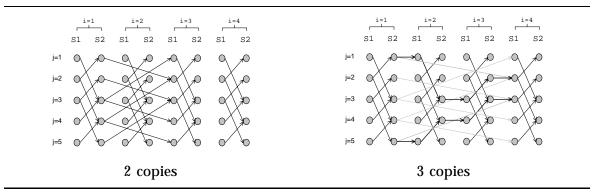

An example is presented here to illustrate variable replication as well as removal of redundant dependences. Consider a transformation of the program of Figure 1-3 as illustrated by Figure 1-8. In this version, a different version of each array is kept for each outer iteration, thus resulting in each array element being assigned a value only once. The anti-dependences from S2 to S1 ( $\Delta_7$  and  $\Delta_8$ ) no longer appear since each update of the array b changes a different location. Therefore the second barrier synchronization can be eliminated altogether. In addition, if the target machine supports full/empty bit

SECTION 1.3: APPROACH 25

synchronization, then the flow dependences from S1 to S2 ( $\Delta_2$  and  $\Delta_3$ ) also do not require additional synchronization.

Figure 1-8

Instead of maintaining many different versions of the arrays, consider now the possibility of obtaining the same benefits from a smaller number of replicated arrays. With the current example, the same result can be achieved by using only two different copies of each array, as illustrated by Figure 1-9.

Figure 1-9

The following dependences are introduced:

$$S1(i, j) \delta^{o} S1(i+2, j)$$

( $\Delta_{4}$ )

$$S2(i, j) \delta^{o} S2(i+2, j)$$

( $\Delta_{5}$ )

$$S1(i, j) \overline{\delta} S2(i+1, j)$$

( $\Delta_6$ )

S2(i, j)

$$\overline{\delta}$$

S1(i + 2, j + 1) ( $\Delta_7$ )

$$S2(i, j) \overline{\delta} S1(i+2, j-1)$$

( $\Delta_8$ )

Dependences  $\Delta_1$ ,  $\Delta_2$ , and  $\Delta_3$  remain unchanged from the original version. And once again, dependences  $\Delta_4$ ,  $\Delta_5$ , and  $\Delta_6$  are satisfied by sequential execution of statements

on each processor. However, dependence  $\Delta_7$  is redundant as illustrated by Figure 1-10. S2(i,j) < S1(i+1,j) due to execution ordering, S1(i+1,j) < S2(i+1,j+1) because  $\Delta_2$  is satisfied, and S2(i+1,j+1) < S1(i+2,j+1) due to execution ordering. Therefore, S2(i,j) < S1(i+2,j+1) and  $\Delta_7$  is automatically satisfied. Intuitively, it is impossible for S2(i,j) to execute after S1(i+2,j+1) because an earlier statement in processor  $P_j$  depends on output from S2(i,j). Likewise,  $\Delta_8$  is satisfied, and synchronization only needs to be performed for dependences  $\Delta_2$  and  $\Delta_3$ . Therefore, doubling the storage requirements of the arrays results in the elimination of the anti-dependences in this example. Note that the same results can be obtained by only replicating array b since elements of array a are never shared.

Figure 1-10: Eliminating anti-dependences

#### 1.4 Thesis outline

The remainder of the thesis is organized as follows: Chapter 2 presents the background and assumptions used in the rest of the thesis. Chapter 3 shows how array flow analysis and dependence testing can be used to compute dependences between statements. Chapter 4 then presents schemes for detecting dependences between processors

SECTION 1.4: THESIS OUTLINE 27

and deriving synchronization to support such dependences. Chapter 5 discusses several optimizations to remove redundant dependences through dynamic programming techniques and eliminating false dependences by array replication. Finally, some results of an implementation are presented in Chapter 6, followed by a discussion of future topics and the conclusion.

# **Chapter 2**

# **Background**

## 2.1 Language description

In order to illustrate the optimizations presented in this thesis, a skeletal language is now introduced. However, it is important to note that these optimizations are applicable to the general array-based data-parallel programming style rather than any particular language. Indeed, a program using such a style in any language can probably benefit from these synchronization-reduction techniques if the proper compilation mechanisms are added to support salient features of the particular language.

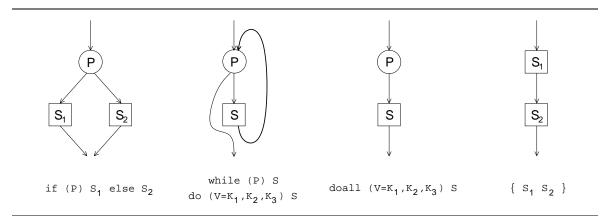

```

S := V = E;

| if (V) S else S

| while (V) S

| do (V = K, K, K) S

| doall (V = K, K, K) S

| \{S, S\}

```

Figure 2-1: Language syntax

The syntax of the language is shown in Figure 2-1. The terminal V is assumed to be a variable, K is an integer variable or constant, and E is an expression. Although the sequential looping constructs DO and WHILE are semantically very similar, they are both included since a large amount of analysis is done on indices of DO loops. On the other hand, the WHILE statement represents a more general looping construct with a terminating condition and without explicitly specified indices. The sequence operator  $\{S,S\}$  is restricted to contain two statements for ease of proofs in later chapters. A general sequence of many statements can be viewed as a cascade of many two-statement sequences.

In addition to standard control-flow constructs, the DOALL construct is provided for

30 CHAPTER 2: BACKGROUND

specification of explicit parallelism. The use of a DOALL statement is a declaration that all iterations of the loop can be executed in parallel. Semantically, DOALL execution behaves as if barrier synchronizations existed before and after the DOALL. Furthermore, the body of each DOALL is not assumed to be atomic. All iterations can be invoked simultaneously and can compete for the same resources. Consequently, the program shown in Figure 2-2 is incorrect since other iterations can be started and finished between the fetch and assignment of sum in a particular iteration. Although alternate models of executing DOALL loops exist in the literature which allow atomicity of iterations or copy-in/copy-out semantics [CHH89], this thesis focuses only on the simpler semantics presented above. For simplicity of presentation, the DOACROSS construct is omitted in most of the discussion of this thesis.

```

sum = 0;

doall (i=1,100,1)

sum = sum + a[i];

```

Figure 2-2: Sum the elements of an array

In this thesis, DOALL loops are assumed to be partitioned at compile time. Thus for a particular loop with index variable i, it is assumed that the mapping from the value domain of i to the processor space has been done either by the programmer or by an earlier phase of the compiler. The automatic partitioning of loop iterations into processors is a topic of active research [Sar87][AH91]. In certain situations including those where the index set of a loop cannot be determined statically, a dynamic scheduling scheme must be used. However, such cases are not considered here. A detailed specification of the execution of statically-scheduled DOALL loops is given in Chapter 4.

## 2.2 Control flow graph

The *control flow graph* of a program can be defined to form a framework for managing relationships between statements. Each node in the graph represents a statement in the program. If it is possible that execution of statement  $S_1$  can be followed by statement  $S_2$ , then a directed edge exists from  $S_1$  to  $S_2$ . Figure 2-3 shows how a flow graph can be constructed from sequential constructs in the language.

From [ASU86], an edge in the control-flow graph is a *forward edge* if it is part of a spanning tree formed from a particular depth-first traversal of the graph. Forward edges

Figure 2-3: Control flow graph for language constructs

are represented by solid arrows in the figure. A statement S precedes or is a predecessor another statement S' if there is a path composed of forward edges from S to S'. The statement S' is said to be a successor of S. A back edge is an edge from a statement S to a predecessor of S. The back edges are represented by highlighted arrows in the figure. Since forward edges form a tree, no forward edge can be a back edge. In a general program, cross edges also exist that are neither forward nor back edges, but they do not occur in programs that use the above syntax. A cross edge can be produced by a forward jump such as a non-local loop exit.

A statement S dominates or is a dominator of S' if any path from the start of the program to S' must pass through S. If S dominates S', then S precedes S'. Likewise, S post-dominates S' if any path from S' to the end of the program must pass through S. If S post-dominates S', then S is a successor of S'. We introduce the concept of relative dominance, a more general notion of dominance. A statement S dominates S' relative to S'' if any path from S'' to S' must pass through S. A statement S post-dominates S' relative to S'' if it dominates S' relative to the start of the program and S post-dominates S' if it post-dominates S' relative to the end of the program.

A DOALL statement can be viewed as specifying a collection of statements with an entry node S and an exit node S' such that the collection is composed of exactly the statements that are dominated by S and post-dominated by S'. Clearly, S is a predecessor and S' is a successor of all other nodes in the collection. The collection of nodes is executed once for each iteration value of the loop. Note that there is not a back edge from S' to S since all iterations of a DOALL can be all executed in parallel.

32 CHAPTER 2: BACKGROUND

Using the structure of the program, we define the *child* of a statement as the inner statement of conditional, loop, or sequence statements. Each of those statements in turn is a *parent* of the inner statement. A statement S is an *ancestor* of S' if there are statements  $\{S_1, \ldots, S_n\}$  such that  $S = S_1$ , each  $S_{i+1}$  is a child of  $S_i$ , and  $S' = S_n$ . Each statement S is also an ancestor of itself. S is a *descendant* of S' if S' is an ancestor of S. Note that if S is a parent of S', then S dominates S' and S precedes S' since the predicates of conditionals and loops are executed before the body. We also use the term S *encloses* S' if S is an ancestor of S'.

The above definitions can be used to show that if two statements do not precede each other, then there must be a conditional that encloses them:

<u>Lemma 2.1</u>: If  $S_1$  and  $S_2$  are statements such that  $S_1 \neq S_2$ ,  $S_1$  does not precede  $S_2$  and  $S_2$  does not precede  $S_1$ , then there exists a statement S such that  $S_1$  and  $S_2$  are descendants of S and S is a conditional.

<u>Proof:</u> Let  $\{S_1^k, \ldots, S_{n_k}^k\}$  be ancestors of  $S_k$  such that  $S_i^k$  is a parent of  $S_{i+1}^k$ . Then  $S_1^1 = S_1^2$  since they are both equal to the outermost program statement. Let j be the highest integer such that  $S_j^1 = S_j^2$ . Let  $S = S_j^1$ . Then  $S_1$  and  $S_2$  are both descendants of S. If  $S = S_1$ , then  $S \neq S_2$  and S precedes  $S_2$ , which implies a contradiction. Likewise,  $S \neq S_2$ . Therefore  $S_{j+1}^1$  and  $S_{j+1}^2$  are distinct statements that are children of S, which implies that S is either a conditional or a sequence. If S is a sequence, then a precedence relationship exists between  $S_{j+1}^1$  and  $S_{j+1}^2$ , which implies that one exists between  $S_1$  and  $S_2$ . Therefore S is a conditional.  $\square$

A *partial ordering* is a relation < on a set A with the following properties on set elements:

$$a \not< a$$

(anti-reflexive)  $a < b \Rightarrow b \not< a$  (anti-symmetric)  $a < b$  and  $b < c \Rightarrow a < c$  (transitive)

This relation is sometimes known as a strict partial ordering. As an example, the precedence of statements above is a partial ordering: It is anti-reflexive because there are no forward edges from a node to itself, anti-symmetric because there are no cycles in the tree of forward edges, and transitive because the concatenation of two paths of forward edges is itself a path.

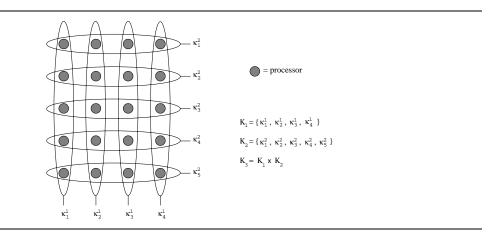

#### 2.3 Machine model

This thesis assumes a cache-coherent shared-memory interface found on machines such as Alewife [Aga91] and Dash [Len92]. Such a multiprocessor can be modeled as a collection of processors  $P = \{p_1, \dots p_n\}$  and a shared pool of memory units that can be accessed through a network. In addition, each processor is associated with a data cache to reduce memory-access latency. The resolution and maintenance of multiply-cached copies of data is performed by a cache-coherence protocol [CFKA90]. Processors are completely independent from each other in the sense that they are able to execute completely different programs from each other. However, the execution model assumed here is one in which all processors execute the same program, although on different data. This is commonly called the Single-Program-Multiple-Data (SPMD) model in the literature.

# **Chapter 3**

# **Statement dependences**

#### 3.1 Introduction

Pursuing the goal of replacing barrier synchronizations with point-to-point synchronizations requires that detailed information about data dependences be computed. This knowledge can be derived from array data flow analysis, an adaptation of conventional scalar data flow analysis. Since this thesis focuses primarily on the domain of array and loop-based data-parallel programs, it is very important that accurate information on array usage be obtained. Conventional data flow analysis techniques [ASU86] tend to treat arrays as single variables. A reference to any element of an array is considered a reference to the entire array. Clearly, such conservative analysis cannot be used to derive dependences needed for point-to-point synchronization. Instead, the array data flow analysis technique can be used to monitor accesses to individual elements of an array. Accurate approximations of values of array indices must be available to yield needed information on array usage. Consequently, the important topic of deducing values of array indices is outlined in the first section. Subsequent sections discuss array flow analysis and its potential uses, as well as its application to dependence detection.

## 3.2 Propagation of linear induction variables

The flow analysis technique outlined in this chapter focuses on arrays whose indices are linear loop induction variables. In other words, relevant array accesses are those whose indices can be represented by linear functions of loop indices. A constant array index can be viewed as a linear function with a multiplicative factor of zero. However, detecting whether an expression is a linear function of a loop index is not a trivial problem. Consider the program in Figure 3-1. It is obvious in this case that the assignment to array b in statement S1 uses an array index that is linear with respect to the loop index i. Furthermore, the value of the array index k is always equal to 2i+5. However, it is not clear how this information can be deduced in a general manner. Fortunately, existing value propagation algorithms can be adapted to propagate linear loop induction variables. In the literature [PW86], this optimization is known as *forward substitution*.

Figure 3-1

#### 3.2.1 Value lattices

For each lexical expression in a program, let the *value set* of the expression be the set of values that it can take on during program execution. Since we are primarily interested in deducing information on array indices that are linear functions of loop indices, value sets are subsets of the integer space and are derived only for scalar variables. A value set can be viewed as an approximation  $\mathcal{A}(E)$  of the value of an expression E and represented as an element on a value lattice. Propagation of both constants and linear induction variables can then be viewed as propagation of value sets using different lattices.

A *lattice* is defined as a partial ordering on a set such that there exists an element that is greater than all others  $(\top)$  and an element that is less than all others  $(\bot)$ . In the current context, lattice elements correspond to value sets and each lattice represents a partial ordering on the set of value sets. A value set  $e_1$  is greater than another set  $e_2$  if  $e_1$  is a superset of  $e_2$ . In constant propagation,  $\top_c$  can be viewed as the set of all integers and  $\bot_c$  can be viewed as the empty set.

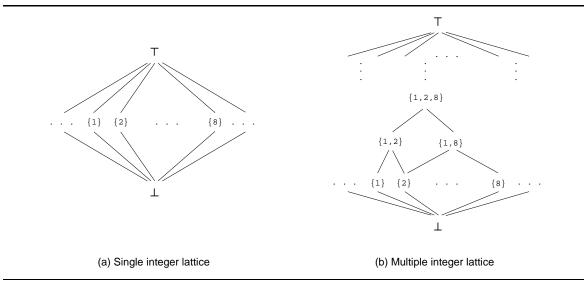

As illustrated in Figure 3-2a, the *single integer lattice* for conventional constant propagation consists of three levels: a bottom element ( $\bot_c$ ) which indicates that no approximation exists for an expression, a top element ( $\top_c$ ) which indicates that the expression can take on any possible value, and sets of single integers that correspond to constant values. Conventionally, constant propagation is performed in order to avoid computing and fetching values that are known to be constants at compilation. If a value is not constant, then the compiler does not benefit from any additional information and the value approximation can be set to  $\top_c$ . However, the optimizations presented in this thesis can make use of approximations that represent the union of several values. Consider the following code segment:

In conventional constant propagation, the value of a after the conditional is deduced to be  $\top_c$  since it is neither always 1 nor always 2. By allowing unions of constants in the lattice, the value of a can be deduced to be "1 or 2" which is a much more accurate approximation than  $\top_c$ . A *multiple integer lattice* is a single integer lattice augmented with unions of constants and is shown in Figure 3-2b. The height of this lattice can be forced to be finite by imposing the restriction that the size of each set cannot exceed some limit H. Any expression whose value set requires more than H integers can be approximated as  $\top_c$ . This restriction enables propagation algorithms that use the lattice to terminate after each variable has gone through O(H) approximations.

Figure 3-2: Constant propagation lattices

For typical programs, the representation of value sets as sets of integers can quickly become unwieldy for expressions that take on many values. Since multiple executions of a single array reference can access a region of an array, it may be possible to abbreviate a value set as an integer range. Indeed, this sort of analysis has been studied in the context of eliminating unnecessary array-bounds checking [Har77][MCM82][Gup90]. If an array index can be approximated by a range that is within the array bounds, there is no need to perform a bounds check. Using integer ranges as lattice elements is ideal

for this kind of optimization since the only information required are the minimum and maximum values of each array index.

Although integer ranges can form an effective representation of lattice elements, such approximations do not model effectively the case when an array is being accessed with a stride greater than 1. If an array reference accesses odd indices in an array and another accesses even indices, the two accesses do not interfere with each other. In addition, two accesses with stride 1 may not interfere even if their ranges intersect. Consider the code fragment in Figure 3-3. Since statement S2 uses an old element of array a and not the one that is defined in S1, there are no flow dependences from S1 to S2 even though the ranges corresponding to j and j+2 intersect. Clearly, information about loop indices must be stored to detect these dependences.

Figure 3-3

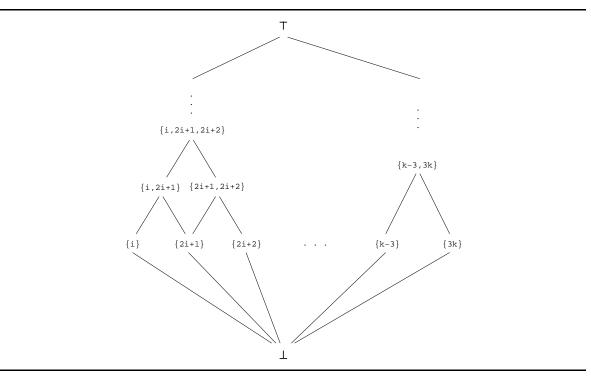

A linear induction variable lattice can be defined with a structure that is similar to the multiple integer lattice. Parts of such a lattice are shown in Figure 3-4. Immediately above  $\perp_{iv}$  are single linear functions of various loop indices and above those linear induction variables are sets of multiple induction variables. The element  $\top_{iv}$  can be viewed as the collection of all linear induction variables. From this point on, linear induction variables will form the basic elements in a value set. Note that for a value set  $e_1$  to be a strict superset of another lattice element  $e_2$  and thus be higher in the lattice than  $e_2$ ,  $e_1$  must have more induction variables than  $e_2$ . Again, we can put a limit H on the number of induction variables allowed in a value set, thus forming a lattice of height H+2.

Note that functions of only one loop index are present in the linear induction variable lattice. Linear functions of multiple loop indices are not supported. Also, detection of induction variables that are not defined directly from loop indices [Wol92] is not done. These topics are viewed as somewhat orthogonal to the approach outlined here. Thus their inclusion in these algorithms can be made in a real system by incorporating relevant

techniques in the literature.

Figure 3-4: Linear induction variable lattice

## 3.2.2 Propagation of linear induction variables

The algorithm presented here for the propagation of linear induction variables is based on previous work on symbolic value propagation done by Reif and Lewis [RL86]. Wegman and Zadeck [WZ91] show that in the context of constant propagation, derived constant information can aid in the flow analysis as well. In this section, an algorithm is shown for propagation of linear induction variables on scalars using a sparse flow graph representation.

Compiler analysis to discover linear relationships among variables was first studied by Karr [Kar76]. Linear relationships among variables can also be shown to be derivable in the general framework of abstract interpretation [CH78][CC77]. These approaches focus towards a general treatment of the problem rather than developing an efficient algorithm for the language features used here.

#### 3.2.2.1 SSA form

Value propagation can be done efficiently on a sparse flow graph representation using static single assignment form. The term *single assignment* is typically used to represent an execution model where only one assignment is done for each variable during the entire program execution. Similarly, a program is in *static single assignment* form when each variable is assigned by only one statement [Cyt91]. Note that each variable can still be assigned many times dynamically due to the presence of loops. However, each of those assignments is done in the same statement.

A program in SSA form has at most one assignment statement for each variable. Any program can be transformed into SSA form by observing the following rules:

- 1. At the beginning of the program, assignments are inserted for each variable to initialize the variable to its default value at program startup.

- 2. Each assignment to a variable v is replaced by an assignment to a renamed variable  $v_i$  where i is different for every assignment to v.

- 3. For each join point in a program flow graph, if several different names  $v_i$  and  $v_j$  of the same variable reach the join point, then a new assignment is inserted after the join point of the form  $v_k = \phi(v_i, v_j)$ . Again, k is distinct from all other renamings of v in the program. The  $\phi$  form can be viewed as a merge of variable definitions.

- 4. Each use of a variable is renamed to the name of the definition of the variable that reaches it. This definition is unique since  $\phi$  assignments are inserted at every join point where multiple reaching definitions can arise.

Algorithms for computing SSA form in general are given in [Cyt91] and for structured programs in [RWZ88]. An illustration of the SSA transformation is shown in Figure 3-5.

A *definition-use graph* can be defined as a directed graph with statements as vertices and edges from definitions of variables to their uses. For  $\mathcal{N}$  occurrences of a variable in a general program, there can be potentially  $O(\mathcal{N}^2)$  definition-use edges corresponding to that variable. In a program transformed to SSA form, definition-use edges can be easily computed by matching each use of a variable with its corresponding definition. The number of def-use edges for each variable in an SSA program is at most  $\mathcal{E} + \mathcal{N}$  where

```

doall (i = 1,99,2) {

doall (i1 = 1,99,2) {

j = i * 2;

j1 = i1 * 2;

if (a[i] > 0)

if (a[i1] > 0)

j = j + 1;

j2 = j1 + 1;

j3 = \phi(j1, j2);

b[j] = b[j] / 3;

b[j3] = b[j3] / 3;

doall (i = 2,100,2)

c[i] = b[i*2];

doall (i2 = 2,100,2)

c[i2] = b[i2*2];

Original program

Transformed program

```

Figure 3-5

$\mathcal{E}$  is the number of edges in the program control flow graph [RL86]. The def-use graph of a program in SSA form can thus be viewed as a sparse representation of the general definition-use graph.

#### 3.2.2.2 Propagation algorithm

After a program has been transformed into SSA form, linear induction variables can be propagated over the definition-use graph. Throughout the execution of the algorithm, outstanding propagation values are maintained in a work-list of def-use edges. An edge is in the work-list if its definition variable v has approximation  $\mathcal{A}(v) \neq \bot_{iv}$  and if the definition has been changed since the last examination of the edge. Associated with each expression E in the program is its lattice element approximation  $\mathcal{A}(E)$  which traverses up the lattice as the algorithm proceeds and new values are discovered for the expression.

Recall that a value set is the set of values that an expression may have at run time and that value sets are represented as linear functions of loop indices. Through the propagation process, calculations are performed on these linear functions according to the program text. For a linear function of a loop index of the form  $(\alpha i + \beta)$ , a list of rules for linear function calculations is given in Figure 3-6. Constant expressions  $(\gamma)$  can also be viewed as linear functions with  $\alpha = 0$ . All arithmetic operations with  $\top_{iv}$  yield  $\top_{iv}$  and all arithmetic operations with  $\bot_{iv}$  yield  $\bot_{iv}$ .

At initialization, the approximation  $\mathcal{A}(E)$  of each expression E is set to the lattice element that can be derived immediately from its text. Thus constant expressions and loop index variables are approximated to be the respective constant or loop index. If the value set of the expression text is inconclusive, then  $\mathcal{A}(E)$  is set to  $\perp_{iv}$ . If the value

$$(\alpha_1 i + \beta_1) "+" (\alpha_1 i + \beta_2) = ((\alpha_1 + \alpha_2) i + \beta_1 + \beta_2)$$

(1)

$$(\alpha_1 i + \beta_1) "-" (\alpha_1 i + \beta_2) = ((\alpha_1 - \alpha_2) i + \beta_1 - \beta_2)$$

(2)

$$(\alpha \mathbf{i} + \beta) \text{ "*"} \gamma = \alpha \gamma \mathbf{i} + \beta \gamma \tag{3}$$

$$(\alpha i + \beta) "/" \gamma = \alpha/\gamma i + \beta/\gamma$$

(4)

$$\phi(e, \perp_{iv}) = e \tag{5}$$

$$\phi(\perp_{iv}, e) = e \tag{6}$$

$$\phi(e_1, e_2) = \begin{cases} \top_{iv} & \text{if } |e_1| + |e_2| > H \\ e_1 \cup e_2 & \text{otherwise} \end{cases}$$

(7)

Figure 3-6: Rules for operations on linear index functions

set cannot be represented by any lattice element, then the expression is approximated as  $\top_{iv}$ . Note that if E contains no free variables, then  $\mathcal{A}(E)$  cannot be  $\bot_{iv}$  since its approximation can be determined at compile time. The work-list is then initialized to contain all def-use edges with definition variable v such that  $\mathcal{A}(v) \neq \bot_{iv}$ . The algorithm then proceeds as follows:

- 1. Remove a def-use edge from the work-list. If the work-list is empty, then terminate.

- 2. Let V be the variable corresponding to the removed edge. Let S be the statement where V is used (pointed to by the def-use edge). For each expression E in S, a new approximation of the value of E can be made using the approximation of V at the definition.

- 3. If S is an assignment statement to a variable V' and its right-hand-side approximation changes in step 2, then all def-use edges for which V' is a definition are added to the work-list.

The following statement proves that the propagation algorithm is correct by showing that any value that can occur at run time for an expression is included in the approximation for that expression.

<u>Claim 3.1</u>: For each expression E, if  $\omega(E)$  is the set of values that E can take on at run time, then  $\omega(E) \subseteq \mathcal{A}(E)$ .

<u>Proof</u>: By contradiction, suppose that for some expression E',  $\omega(E') \not\subseteq \mathcal{A}(E')$  during program execution. Then there some earliest execution of an expression E such that  $\omega(E) \not\subseteq \mathcal{A}(E)$ . Let  $V_1, \ldots, V_n$  be free variables in V. Then each previous definition of each  $V_i$  produces a value that is in  $\mathcal{A}(V_i)$  since E is the earliest execution that violates the subset relation. But then the value of E is in  $\mathcal{A}(E)$  because the rules in Figure 3-6 preserve the subset relation.  $\square$

<u>Corollary 3.2</u>: At algorithm termination, there can be no executable expression E such that  $A(E) = \bot_{iv}$ .

<u>Proof</u>: Since E has a run-time value,  $\omega(E) \neq \emptyset$  and thus  $\mathcal{A}(E) \neq \bot_{iv}$  due to Claim 3.1.  $\Box$

The running-time analysis of this algorithm makes use of the height of the lattice. Recall that for a lattice element  $e_1$  to be higher in the lattice than another element  $e_2$ ,  $e_1$  must have more linear functions than  $e_2$ . The key to studying running time involves examining the number of times that each statement is invoked by step 3. For each assignment statement with variable V, step 3 can generate new edges at most H+2 times since each change in the approximation of the  $\phi$  expression involves moving up one level in the lattice. Overall, the number of times that an edge can be placed in the work-list corresponds to the number of def-use edges in the SSA graph times H. From [RL86], there are at most  $\mathcal E$  def-use edges for each variable in an SSA graph where  $\mathcal E$  is the number of edges in the control flow graph. Hence, the worst-case running time for the propagation algorithm is  $O(H \times \mathcal N \times \mathcal E)$  where  $\mathcal N$  is the number of variables in a program. From [WZ91], empirical evidence suggests that constant propagation runs in time linear to program size. The typical running time of linear induction variable propagation is expected to also be linear but with an additional multiplicative factor of H.

After all induction variables have been propagated, most expressions that are linear functions of loop indices can be detected. The next compiler phase can then use this information to perform data flow analysis on sections of arrays.

## 3.3 Flow analysis on arrays

Data flow analysis involves the study of data interaction between different points in a program. In the context of data dependence detection, interactions between definitions and uses of variables are analyzed to determine whether dependences exist. Flow dependences and output dependences arise when previous definitions conflict with current uses and current definitions, respectively. Anti-dependences arise from conflicts between previous uses and current definitions. Consequently, accurate information on the previous uses and definitions that reach a statement is needed to generate useful dependence information. An algorithm is presented in the following section to determine the set of reaching uses and definitions for each statement in a program.

## 3.3.1 Linear integer sequences

When array flow analysis is performed, there are many operations that need to be performed on value sets such as union, intersection, subtraction, and comparison. Unfortunately, the linear induction variable representation presented in the previous section is unwieldy for certain operations. In Figure 3-7, the definition of a in statement s1 should not progress past the second loop since it is killed by the definitions of a in statements s2 and s3. Intuitively, statement s2 modifies odd indices of a and statement s3 modifies even indices of a. However, it is hard to extrapolate the fact that the two definitions cover all indices of a from the linear induction variable representation.

Figure 3-7

An alternate representation for linear induction variables is needed to manage array subsets to support cases similar to the previous example. Although dependence analysis requires the preservation of linear induction variables, such a representation is not necessary for the purposes of strictly performing flow analysis. Instead, each array index expression can be approximated by a less specific linear sequence of integers with an associated range. A *linear integer sequence* can be represented as a 3-tuple  $\langle\langle n_{lo}, n_{hi}, n_{step} \rangle\rangle$  where  $n_{lo}$  and  $n_{hi}$  are the low and high limits of the sequence and  $n_{step}$  is the stride of the sequence. Such a tuple represents the set of all integers n of the form  $n_{lo} + k n_{step}$  such that  $k \geq 0$  and  $n \leq n_{hi}$ . For example, the 3-tuple  $\langle\langle 10, 98, 2 \rangle\rangle$  represents all even

2-digit integers. Note that the high value of the tuple must itself be in the representative set. In Figure 3-7, the tuples for statements S2 and S3 are  $\langle (1,199,2) \rangle$  and  $\langle (2,200,2) \rangle$ , respectively. Their union forms the tuple  $\langle (1,200,1) \rangle$  which is a superset of the tuple in statement S1.

A set-inclusion ordering on linear integer sequences can be defined as follows:

$$\langle\langle m_{lo}, m_{hi}, m_{step} \rangle\rangle \subseteq \langle\langle n_{lo}, n_{hi}, n_{step} \rangle\rangle \iff$$

$m_{step} = k_1 n_{step} \text{ and } m_{lo} = n_{lo} + k_2 n_{step} \text{ and } m_{hi} \leq n_{hi} \text{ for integers } k_1, k_2 \geq 0$

The ordering defines a lattice with  $T_{is}$  as all integers and  $L_{is}$  as the empty set.

In order to convert value sets that consist of linear induction variables into linear integer sequences, mappings need to be introduced between the two domains. For singleton linear induction variables whose loop index bounds are known statically, the mapping  $\mathcal{L}'$  from a linear induction variable to a linear integer sequence can be defined as:

$$\mathcal{L}'(\alpha i + \beta) = \langle \langle \alpha k_1 + \beta, \alpha k_2 + \beta, \alpha k_3 \rangle \rangle$$

for loop index bounds (i=k<sub>1</sub>, k<sub>2</sub>, k<sub>3</sub>)

Additionally, a straightforward modification needs to be performed to ensure that the high bound for the tuple is an element of the integer sequence.

The complication of mapping value sets into integer sequences arises either when the loop bounds are not known or when multiple linear induction variables occur in a value set. In these cases, it is important to keep in mind the question one is asking when performing the comparison. Since the eventual optimizations that use array flow analysis do not require exact answers, an approximation can be used as long as it is inaccurate in the right direction. Consider the case where a response of "yes" causes an optimization to be performed and a response of "no" results in no transformations to the program. Then answering "no" all the time would produce a correct although slow program whereas answering "yes" falsely results in a fast but incorrect program. Since the entire goal of this chapter is dependence analysis, the conservative view states that every dependence that can exist should be detected. Even if additional false dependences are detected, the resulting program would still work.

In consideration of the above principles, the conversion of linear induction variables into linear integer sequences requires both an under-approximation and an over-

approximation. The two cases arise from different uses of flow elements that contain linear induction variables as indices, and will be discussed in a later section.

In one case, we desire a linear integer sequence that is the smallest computable superset of the integers in a value set. The superset mapping  $\mathcal{L}_{\supset}$  from value sets into linear integer sequences is introduced for this case. For each linear induction variable  $e \equiv \alpha \mathbf{i} + \beta$  in the value set, the mapping  $\mathcal{L}'_{\supset}$  can be defined to yield an integer sequence that is a superset of the integers represented by e. When a linear induction variable contains a loop index whose bounds are not known, then  $\mathcal{L}'_{\supset}(e)$  yields  $\mathcal{L}'(e)$  on a superset of the loop space of  $\mathbf{i}$ . For a value set of several linear induction variables  $\{e_1, e_2, \ldots, e_n\}$ , the superset mapping is defined as:

$$\mathcal{L}_{\supset}(\{e_1, e_2, \ldots\}) = \bigcup_{i=1}^n \mathcal{L}'_{\supset}(e_i)$$

Although one would prefer the smallest possible superset from this mapping, a very conservative implementation of  $\mathcal{L}_{\supset}$  can always return  $\top_{is}$  and still produce a correct result. Indeed, one can view the treatment of arrays in conventional scalar flow analysis as using such an approximation function.

In the other case, we desire a linear integer sequence that is the largest computable subset of the value set. Likewise, for a linear induction variable  $e \equiv \alpha \mathbf{i} + \beta$ , the mapping  $\mathcal{L}'_{\subset}$  can be introduced to yield  $\mathcal{L}'(e)$  on a subset of the loop space of  $\mathbf{i}$ . The subset mapping can then be defined as:

$$\mathcal{L}_{\subset}(\{e_1, e_2, \ldots\}) = \bigcap_{i=1}^{n} \mathcal{L}'_{\subset}(e_i)$$

Again, a very conservative implementation of  $\mathcal{L}_{\subset}$  can always return  $\perp_{is}$  and still be correct.

The above equations require union and intersection operations on linear integer sequences which can be defined by a set of rules. Again, it is important to note that the union and intersection operations only need to be conservative and not absolutely correct. Thus the union operation listed above can actually return a superset of the actual union while the intersection operation can return a subset of the actual intersection. An ambitious implementation can trade off compiler time for execution of complex rules to increase accuracy of dependence information. A small and by no means exhaustive set of rules is given in Figure 3-8.

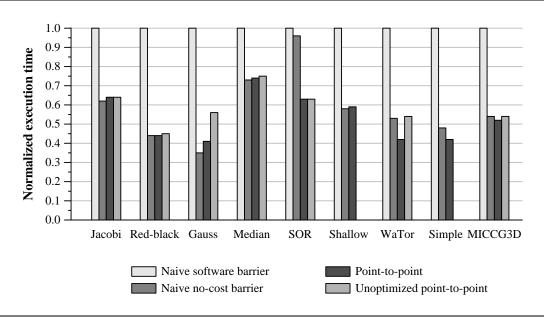

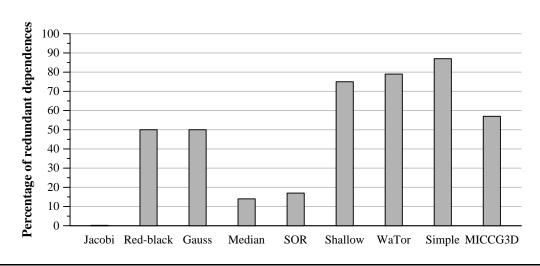

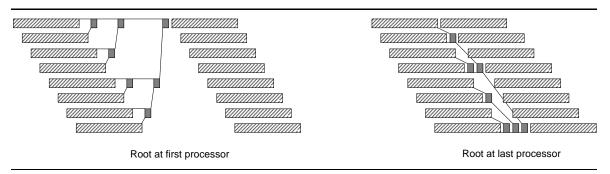

```