## MIT/LCS/TR-64

### A GRAPH MODEL FOR PARALLEL COMPUTATIONS

Jorge E. Rodriguez

September 1969

# A GRAPH MODEL FOR PARALLEL COMPUTATIONS

by

Jorge E. Rodriguez

The work reported in this document has been jointly supported by the Air Force Manufacturing Technology Laboratory, RTD, Wright-Patterson Air Force Base under Contract F33615-67-C-1530, M.I.T. DSR Project 70429, Electronic Systems Laboratory and by Project MAC an M.I.T. research program sponsored by the Advanced Research Projects Agency, Department of Defense, under Office of Naval Research Contract Nonr-4102(01). Reproduction in whole or in part is permitted for any purpose of the United States Government.

Electronic Systems Laboratory

Department of Electrical Engineering

Project MAC

545 Technology Square

Massachusetts Institute of Technology Cambridge, Massachusetts 02139 This empty page was substituted for a blank page in the original document.

#### ABSTRACT

This report presents a computational model called program graphs which makes possible a precise description of parallel computations of arbitrary complexity on non-structured data. In the model, the computation steps are represented by the nodes of a directed graph whose links represent the elements of storage and transmission of data and/or control information. The activation of the computation represented by a node depends only on the control information residing in each of the links incident into and out of the node. At any given time any number of nodes may be active, and there are no assumptions in the model regarding either the length of time required to perform the computation represented by a node or the length of time required to transmit data or control information from one node to another. Data dependent decisions are incorporated in the model in a novel way which makes a sharp distinction between the local sequencing requirements arising from the data dependency of the computation steps and the global sequencing requirements determined by the logical structure of the algorithm.

The concept of the state of a program graph is introduced and it is proved that every program graph represents a deterministic computation, i.e., that the final state of each computation started from the same initial state is unique. Computations which do not terminate properly are defined in terms of the concept of hang-up state. Methods of analysis are developed and necessary and sufficient conditions for the absence of hang-up states are obtained. These conditions are interpreted in terms of the structure of the graph and the manner in which the decision elements are imbedded in that structure. Finally, an equivalence problem for program graphs is formulated and a solution to this problem is presented.

#### ACKNOWLEDGEMENT

This report is the unaltered thesis submitted by Jorge E. Rodriguez in September, 1967, in partial fulfillment of the requirements for the degree of Doctor of Science in Electrical Engineering at the Massachusetts Institute of Technology.

The author wishes to thank the following: Professor Jack B. Dennis who, as thesis supervisor, provided invaluable advice and guidance throughout the course of this research; Professor Joseph Weizenbaum, Professor Chung L. Liu, and Mr. Douglas T. Ross for their assistance and suggestions as readers. (Mr. Ross was also Head of the Computer Applications Group at the Electronic Systems Laboratory, where the author worked as a Research Assistant, who throughout the years had supplied much insight, help, and encouragement); Professor Leonard A. Gould who, as his faculty advisor since his early days at the Graduate School, had provided invaluable academic and personal advice; Dr. Jacob Katzenelson for his timely help and encouragement.

## TABLE OF CONTENTS

|         |      |                                               | Page |

|---------|------|-----------------------------------------------|------|

| CHAPTER | I    | INTRODUCTION                                  | l    |

|         | A.   | SUMMARY                                       | 1    |

|         | в.   | REVIEW OF RELATED WORK                        | 2    |

|         | c.   | OUTLINE                                       | 6    |

| CHAPTER | II . | "THE MODEL                                    | 7    |

|         | Α.   | INTRODUCTION                                  | 7    |

|         | в.   | BACKGROUND AND VIEWPOINT                      | .7   |

|         | c.   | THE CONSTITUENTS OF PROGRAM GRAPHS            | 12   |

|         | D.   | THE CONSTRUCTION OF PROGRAM GRAPHS            | 17   |

|         | E.   | THE EXECUTION OF PROGRAM GRAPHS               | 21   |

|         | F.   | THE DETERMINISM OF PROGRAM GRAPHS             | 27   |

| CHAPTER | ш    | ANALYSIS OF PROGRAM GRAPHS                    | 40   |

|         | A.   | INTRODUCTION                                  | 40   |

|         | в.   | NOTATION AND TERMINOLOGY                      | 41   |

|         |      | 1. Notation                                   | 41   |

|         |      | 2. Paths, Cycles, and Connectivity            | 41   |

|         |      | 3. Normal Sequences and Hang-Up States        | 42   |

|         | c.   | EXAMPLES OF PROGRAM GRAPHS                    | 43   |

|         |      | 1. Properties of Program Graphs               | 43   |

|         |      | 2. The Case of Selectors and Junctions        | 45   |

|         |      | 3. The Use of Loop Junctions and Loop Outputs | 47   |

|         | D.   | ANALYSIS OF CYCLE FREE GRAPHS                 | 52   |

|         |      | 1. The Role of Cycle Free Graphs              | 52   |

|         |      | 2. Properties of Execution Sequences          | 52   |

|         |      | 3. The Enabling Function                      | 57   |

## TABLE OF CONTENTS (CONT.)

|              |                                                     | Page       |

|--------------|-----------------------------------------------------|------------|

| E.           | ANALYSIS OF CYCLIC GRAPHS                           | 60         |

|              | 1. Cycle Decomposition                              | 60         |

|              | 2. Simple Cyclic Graphs                             | 65         |

|              | 3. Graphs of Type I                                 | 75         |

| CHAPTER IV   | AN EQUIVALENCE PROBLEM                              | 82         |

| Α.           | INTRODUCTION                                        | 82         |

| В.           | A SIMPLE EQUIVALENCE PROBLEM                        | 83         |

| С.           | THE EQUIVALENCE PROBLEM FOR ARBIT                   | RARY<br>86 |

| D.           | SIMPLE TRANSFORMATIONS                              | 100        |

| CHAPTER V    | CONCLUSIONS AND RECOMMENDATIONS                     | 106        |

| APPENDIX A   | AN ALGORITHM TO GENERATE BASE SEQUENCES             | 109        |

| APPENDIX B   | VERIFICATION OF PROPERTIES OF THE TRANSITION TABLES | 114        |

| BIBLIOGRAPHY |                                                     | 118        |

| : | LIST | OF | FIGURES |

|---|------|----|---------|

|   |      |    |         |

| Chapte | er II                                                             | Page       |

|--------|-------------------------------------------------------------------|------------|

| 2. 1   | Representation of an Algebraic Computation by a Program Graph     | 9          |

| 2.2    | Representation of a Conditional Expression by a Program Graph     | 10         |

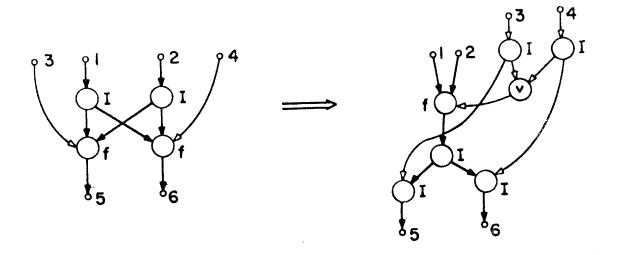

| 2.3    | Functional Composition in a Program Graph                         | 19         |

| 2.4    | A Simple Iterative Process                                        | 20         |

| 2.5    | Program Graph and Flow Chart of an Iterative Process              | 22         |

| 2.6    | A Single Loop with Multiple Loop Junctions                        | 23         |

| 2.7    | States During the Execution of a Cycle Free Program Graph         | <b>2</b> 5 |

| 2.8    | States During the Execution of a Cyclic Program Graph             | 26         |

| 2.9    | The Possible Configurations of Two Active Nodes Sharing a Link    | 31         |

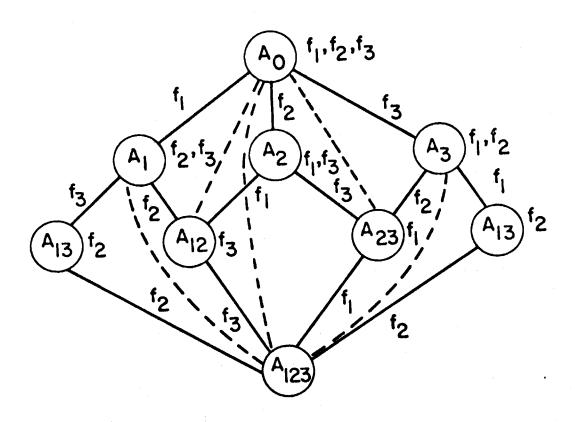

| 2.10   | The Relation among the 'Next' States of a State $A_0$             | 33         |

| 2.11   | The Three Cases in the Proof of Theorem 2.2                       | 35         |

| 2.12   | The Three Cases in the Proof of Theorem 2.3                       | 38         |

| Chapt  | er III                                                            |            |

| 3.1    | Use of Selectors and Junctions                                    | 46         |

| 3.2    | Junctions Creating Hang-Up States                                 | 46         |

| 3.3    | Single and Parallel Cycles                                        | 49         |

| 3.4    | Nested Cycles with and without Loop Output Nodes                  | 51         |

| 3.5    | The Proper Way of Connecting Loop Junctions and Loop Outputs      | 55         |

| 3.6    | Initial States of Program Graphs that do not Satisfy Theorem 3, 2 | 55         |

| 3.7    | A Cycle that does not Pass Through a Loop Junction                | 55         |

| 3.8    | Example of the Cycle Decomposition Procedure                      | 64         |

| 3. 9   | The Link Names of Loop Junction-Loop Output Pairs                 | 67         |

| 3.10   | The Link Names of Operators, Selectors, and Junctions             | 67         |

# LIST OF FIGURES (CONTINUED)

|        |                                                                                            | Page      |

|--------|--------------------------------------------------------------------------------------------|-----------|

| 3.11   | The Link Names in the Iteration Step of Lemma 3.5                                          | 72        |

| 3. 12  | Dingram of Paths Between mscs's which May Cause<br>Hang-Up States                          | 74        |

| 3.13   | The Enabling Functions of a Cyclic Graph                                                   | 77        |

| 3.14   | A Possible Hang-Up State Arising from mscs with Different<br>Feedback Enabling Functions   | 79        |

| Chapte | r IV                                                                                       |           |

| 4.1    | Cyclic Graphs with the Same Cycle Structure                                                | 84        |

| 4.2    | The Two Program Graphs of Example 1                                                        | 94        |

| 4.3    | The Two Program Graphs of Example 2                                                        | 96        |

| 4.4    | Transformations to Identify Common Subgraphs Disregarding<br>Selectors and Junctions       | 98        |

| 4.5    | Transformations to Identify Common Subgraphs Including Selectors and Junctions             | 99        |

| 4.6    | Alternative Form of a Transformation Scheme which Does                                     | 101       |

|        | not Preserve Equivalence                                                                   |           |

| 4.7    | Subgraph in which the Transformation of Figure 4. 6 Introduce a Cycle                      | es<br>102 |

| 4.8    | Two Equivalent Program Graphs Differing on the Way a Control Link is Applied to Operators. | 104       |

#### PREFACE

The goals of generalized computer-aided design, being synonymous with generalized man-machine problem-solving, place the most stringent requirements on underlying foundations and implementation techniques. As increasingly elaborate and complex applications are contemplated, it becomes clear that substantial inroads must be made to deepen our fundamental understanding of computation itself. Ultimately it must be possible to prove the correctness of a program, for no conceivable technique can provide an adequate basis for debugging; it must be possible to transform a proposed computation automatically from one formulation to another radically different formulation, with firm knowledge that the two forms are in a useful way equivalent; it must be possible to design, analyze, and compute using entire computational processes themselves as data, for manual composition of constructs of such vast complexity will be beyond human comprehension. It was in the spirit of these convictions that the research described in this report was undertaken.

Early in the preliminary investigation, it became clear that before any questions of equivalence or operations of transformation could meaningfully be posed, a rigorous, deterministic, and elegant model of a computational process itself was required. The model had to be independent of any artifacts of existing programming language characteristics and had to exhibit in an inherently simple and natural form only the essential relations between data and operators on data, from which any computational process is composed. The "program graph" model introduced here is a major contribution which meets the most basic criteria. Since the model is based directly upon 'data dependency' relations, it enjoys the essential simplicity needed to assure its adequacy as a general model. Also, the rigorous formulation enables determinism of the model to be proved. Finally, some initial attempts to address questions of equivalence and transformation lend credence to the viewpoint that further elaborations and refinements can lead toward the desired basis for a mathematics for computational processes. Already the trends in this direction are taking shape in a number of related theses and studies listed at the end of this preface.

#### PREFACE (Contd.)

In view of the abstract nature of the model, and the fact that such important features as data structures are included only in the most degenerate form, it is clear that it still will be some time before these developments can have a direct impact on the practical matters of constructing man-machine systems. Many aspects can, however, be extracted and can be cast in terms compatible with some of the more advanced aspects of programming language semantics and compilation of optimized machine code. Hopefully such application attempts combined with the theoretical advancements will accelerate the pace at which these vital matters can be pursued.

Douglas T. Ross

Head, Computer Applications Group January, 1969

ouglas T. Ross

- 1. Dennis, J.B. Programming Generality, Parallelism and Computer Achitecture. (Submitted for publication to the Journal of ACM)

- 2. Luconi, F.L. Asynchronous Computational Structures. MAC-TR-49, Project MAC, MIT (1968)

- 3. Slutz, D.R. The Flow Graph Schemata Model of Parallel Computation. MAC-TR-53, Project MAC, MIT (1969)

#### I. INTRODUCTION

#### A. SUMMARY

This paper presents a computational model called program graphs which makes possible a precise description of parallel computations of arbitrary complexity on non-structured data. In the model, the computation steps are represented by the nodes of a directed graph whose links represent the elements of storage and transmission of data and/or control information. The activation of the computation represented by a node depends only on the control information residing in each of the links incident into and out of the node. At any given time any number of nodes may be active, and there are no assumptions in the model regarding either the length of time required to perform the computation represented by a node or the length of time required to transmit data or control information from one node to another. Data dependent decisions are incorporated in the model in a novel way which makes a sharp distinction between the local sequencing requirements arising from the data dependency of the computation steps and the global sequencing requirements determined by the logical structure of the algorithm.

The concept of the state of a program graph is introduced and it is proved that every program graph represents a deterministic computation, i.e. that the final state of each computation started from the same initial state is unique. Computations which do not terminate properly are defined in terms of the concept of hang-up state. Methods of analysis are developed, and necessary and sufficient conditions for the absence of hang-up states are obtained. These conditions are interpreted in terms of the structure of the graph and the manner in which the decision elements are

imbedded in that structure. Finally, an equivalence problem for program graphs is formulated and a solution to this problem is presented.

The model may be useful in a variety of problems including: the analysis and transformation of computer programs to meet some desired criterion, e.g. reduce the amount of space required, or increase the speed of operation, or both of these objectives; the assignment and sequencing of computations in parallel processor computer systems; and the design of sequencing and control units for parallel computation, in particular, the results of this paper are directly applicable to the design of macro-modular systems. 3, 18, 22

#### B. REVIEW OF RELATED WORK

Graphs have been used to represent computations since the early days of computers. Most of these representations are strictly sequential and can be generally classified as flow charts. In a flow chart, a node represents either an operational element or a decision element, and an arc of the graph denotes flow of control from one node to another. At any one point, control resides in precisely one of the nodes. Flow charts have been studied by a number of workers in the field. 2, 4, 5, 8, 9, 11, 13, 20 In the context of this paper, these studies are not directly relevant and therefore we proceed to review only those models which have a direct bearing on the subject of parallel computations.

C. A. Petri 19 has proposed an approach to the description of transmission and transformation of information in discrete systems in which time is introduced only as a local relation among local states. In Petri's formalism, a system is represented by an undirected graph in which each node is a connecting element which binds together (relates) objects contained in places. Each arc of the graph is a place. A node

represents a switching element of a type given by its label. The behavior of each type of element is given by a transition table and is influenced only by those objects assigned to places attached to the node. Petri claims that it is possible to construct conflict-free, deterministic networks corresponding to Turing machines using switching elements defined over the objects 0 and 1.

A. W. Holt has introduced a formalism called -theory for describing discrete information systems. In a -theory the characteristics and behavior of a system are expressed by means of relations of parts. The state of a system is formalized as a finite undirected graph. The nodes of the graph represent system parts and every node is labelled with a node type. The arcs represent relations between two parts. A -theory consists of a -grammar, a list of event types, and a list of observables. The grammar establishes the laws of local context for the node types, i.e. what node types must or may relate and how. The list of event types establishes the laws of local change, i. e. which relations of parts bring about which changes in relations of parts. The list of observables defines which relations of parts are capable of conditioning events in the environment of a system of the class. Changes on the state of a system are defined by means of a simulation rule which effects the changes specified by an admissible subset of applicable event types. A subset of applicable event types is admissible if it is consistent and lossless which means that the state resulting from the changes obeys the rules of the grammar, no two events bring about conflicting changes, and every applicable event not contained in the admissible subset remains applicable after the changes are effected.

E. C. Van Horn<sup>23</sup> has proposed a class of abstract machines for coordinated multi-processing or MCM. An MCM consists of a set of <u>cells</u>, a scheduler, and a count matrix. The state of an MCM is defined to be the

behave either like a passive memory element or an active computing element. An active cell, called a clerk, may perform a sequence of transactions under the control of the scheduler. Each cell has its own table of transactions. There are five types of transactions; two transactions read and write on cells, three transactions modify the count matrix. Reading of the count matrix is performed by the scheduler to determine which clerk cells are enabled, i. e. can perform one transaction. Van Horn has shown that the behavior of any MCM is asynchronously reproducible.

R. M. Karp and R. E. Miller  $^{10}$  have introduced a model for parallel computations, called computation graphs. A computation graph is a directed graph in which nodes denote operations and branches denote storage elements where results are placed in first-in-first-out queues. Associated with each branch are four non-negative integers  $A_p$ ,  $U_p$ ,  $W_p$ , and  $T_p$  where  $T_p \geq W_p$ . For a branch directed from node  $n_i$  to node  $n_j$ , these parameters are interpreted as follows:  $A_p$  is the number of data words initially in the queues;  $U_p$  is the number of words added to the queue upon completion of the operation associated with  $n_i$ ; and  $T_p$  is a threshold giving the minimum queue length of the branch before the operation of  $n_j$  is initiated. Karp and Miller show that computations represented by these graphs are deterministic. They also give a test to determine whether a computation terminates, and study properties of the data queues associated with the branches, deriving conditions for the queue lengths to remain bounded.

G. Estrin and R. Turn, and D. Martin 14 have introduced a directed graph model for computer programs in which the vertices represent computational tasks and the arcs represent data dependency between nodes. In this model, the conditions for the initiation of the computation denoted by a vertex is expressed by writing a boolean expression in terms of boolean variables associated with the arcs incident into the node. A boolean variable associated with an arc is true when the data in that arc becomes available. A computation may be initiated when the boolean expression of the corresponding node called the vertex input control, is true. There are three types of vertex input control: 1) Conjunctive, 2) disjunctive, and 3) compound. Vertices with conjunctive input control may be initiated only when all input data are available. Vertices with disjunctive input control may be initiated only when precisely one set of input data (i.e. one arc) becomes available. The compound input control is a combination of the other two. Vertices also have output control which is used to specify the program flow from a vertex to a subset of its immediate successors. A vertex with conjunctive output control simultaneously makes data available at all of the arcs incident out of the vertex. A vertex with disjunctive output control makes data available at precisely one of its output arcs. Thus, it may be seen that vertices with disjunctive output control effectively perform data dependent decisions to control the program flow. The model can 'properly represent ' only cycle free graphs. It has been used primarily as a tool for the a-priori assignment and sequencing of computation in parallel processor systems.

The model presented in this paper is a direct extension and formalization of the model of Estrin and Turn using notational techniques introduced by Petri. In extending the model of Estrin and Turn, the concept of pure control information is introduced so that decision elements do not transmit any data but only enabled or disable computations. Furthermore, node types have been introduced which make possible the unambiguous specification of cycles. The notational techniques of Petri have been very useful for precisely describing the behavior of the model in terms of local information alone. In this respect, the similarities between this form of specification of events and that proposed by Holt should be noticed.

D. Muller and W. Bartky 17 have developed methods for the analysis of asynchronous sequential circuits. These methods proved of considerable value in the analysis of the determinism of program graphs.

#### C. OUTLINE

The material is organized as follows: in Chapter II the model is presented and it is proved that every computation represented by the model is deterministic. Chapter III begins with a detailed consideration of the function of each type of node together with reasons for the choices made in the specification of their behavior. This is followed with the introduction of the concept of hang-up state and a study of the conditions which give rise to these states. Chapter IV formulates an equivalence problem and presents a solution to it. This is followed with a brief consideration of some simple equivalence preserving transformations. Finally, Chapter V contains the conclusions and recommendations of this research.

#### II. THE MODEL

#### A. INTRODUCTION

This chapter presents a model for computational processes called program graphs. A program graph is both a denotation of an algorithm and a realization of this algorithm by a process. The linguistic device used to denote operations and the links of the graph denote data and/or control flow among the operations. The realization of the algorithm by a process is accomplished by assigning certain rules of behavior to the program graph elements (nodes and links). These rules of behavior are such that each program graph is a special-purpose deterministic machine which realizes an algorithmic process. The term deterministic machine as used in this paper means that the behavior of the machine is always the same whenever identical data is presented to it at its input terminals.

The material is organized as follows: Section B gives background for the model and the general viewpoint adopted in its formulation. Section C gives some necessary notation and introduces the elements used in constructing program graphs. Section D specifies the syntax for constructing program graphs. Section E specifies the interpretation of program graphs and gives illustrative examples. Finally Section F contains a proof of the determinism of program graphs.

### B. BACKGROUND AND VIEWPOINT

The formulation of program graphs as a computational model has been motivated by the common observation that a large fraction of the sequential constraints of a process can be completely specified by explicitly indicating the data dependency among the different parts of the process.

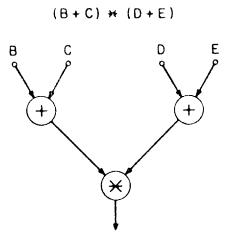

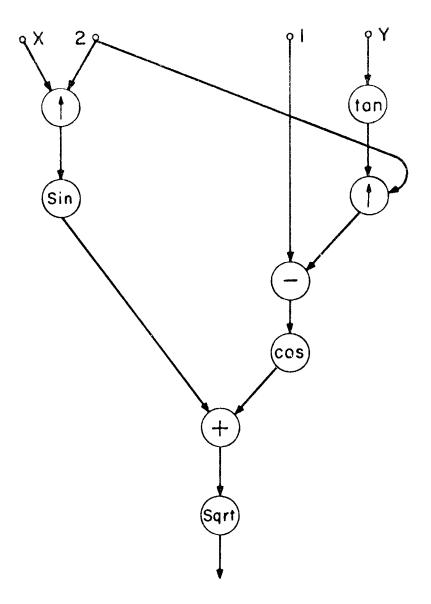

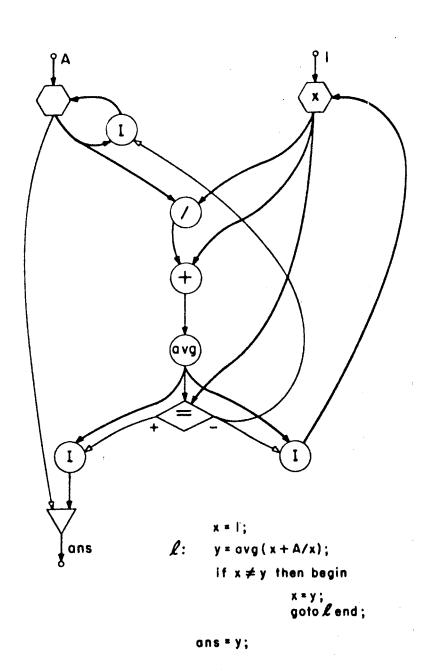

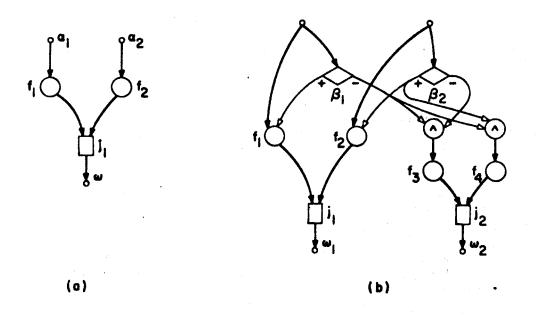

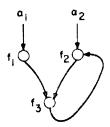

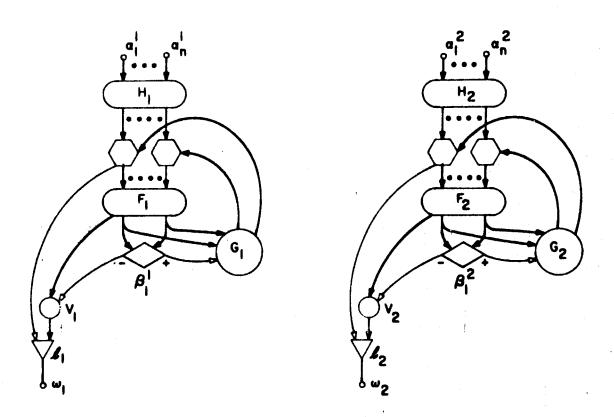

In other words, if the results of sub-process A are data for sub-process B, then A must be performed before B. If control is defined as that quantity which determines the sequencing aspects of a process, then data flow always carries with it control flow information. An obvious advantage of this manner of process specification is the absence of unnecessary sequential constraints, and thus the immediate appearance of any parallelism inherent in the process. This can be seen in the example of Figure 2.1 which shows the representation of an algebraic computation by means of a directed graph in which the nodes denote operations and the directed links denote the data dependency. The potential parallelism of the two !+' nodes is clearly evident.

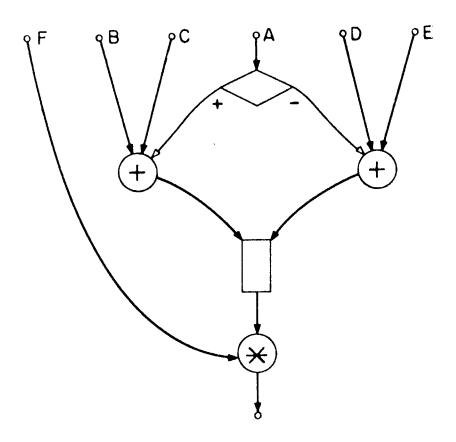

Data dependency is not sufficient to specify all the sequential constraints of a process, however. Most computations include decisions which affect the sequencing of the process without introducing explicit data dependency. We can think of the simplest form of decision, a binary decision, as generating pure control information which selects one out of two possible sequences. The decision does not affect the result of the computations of either sequence but only whether or not the sequences of any parts of them should be performed. Figure 2.2 shows how we might represent an ALGOL conditional expression. The diamond-shaped node denotes a decision selecting one of the additions to be performed as a prelude to the multiplication operation. (Open arrowheads denote pure control flow.)

A computational model which exploits the control aspects of data dependency and thereby places in sharp contrast the unique functions of pure control information is a potentially useful base for exploring transformations of algorithms which preserve input/output relations, logical design of asynchronous machines, and similar areas.

Fig. 2.1 Representation of an Algebraic Computation by a Program Graph

# F \* IF A THEN B+C ELSE D+E

Fig. 2.2 Representation of a Conditional Expression . by a Program Graph

Directed graphs are a natural choice for representing the dependency relations we are interested in, but the static relationships represented by a graph are not sufficient to unambiguously determine dynamic behavior, particularly when dealing with cycles. Dynamic behavior of the process represented by a graph is a crucial question which cannot adequately be handled by introducing a series of ad hoc global rules of interpretation. Therefore, it was decided to formalize a program graph as a formal machine, by having well-defined rules of behavior associated with each element of the graph, i. e. the nodes and links. By making these rules depend only on local information, i. e. by making them independent of the over-all structure of the graph, we achieve two things:

- 1. Any graph constructed following a minimum of local interconnection rules represents a process with unambiguous behavior.

- 2. Each operation proceeds asynchronously with all others, so that any degree of parallelism, anticipating computations or control, can be expressed by the formalism.

#### C. THE CONSTITUENTS OF PROGRAM GRAPHS

A program graph formally represents a computing machine. The computational elements of the machine are represented by the nodes of the graph, and elements for storage and transmission of data and control information are represented by the links of the graph. In what follows node shall be synonymous with computational element and link shall be synonymous with storage-and-transmission element.

There are two types of links - a data link and a control link.

Associated with both data and control links is a quantity called the linkstatus. At any given time the link-status of a link assumes precisely one

out of the four possible values -1, 0, 1, 2. These values will be called

disabled, idle, enabled, and blocked, respectively.

Data links have in addition to link status, a property called data contents. No restrictions are placed on the nature of the data contents of a link. In the representation of program graphs data links are shown as heavy lines with black arrows, while control links are shown as light lines with open arrows.

There are seven types of nodes differing from each other either in the kind of computation performed or in the logic used to activate the node.

Nodes have specific points of attachment called connectors. The connectors of a node are distinguished as being either input or output connectors.

Furthermore an input or output connector may be a data connector or a control connector. Data connectors are attached only to data links.

Similarly, control connectors are attached only to control links.

When the computation represented by a node is being performed, we say that the node is active. The activation of a node is determined by the link status of the data and control links attached to the connectors of the node. For brevity we often refer to the 'status of a connector' meaning the

link status of the link attached to the connector, even though a connector does not properly have a status.

A node is in an active configuration when the statuses of its connectors is such that the node becomes active. The occurrence of an active configuration initiates a transition of arbitrary time length. Upon completion of the transition, the status of each connector (and perhaps the data contents of attached data links as well) are changed in a way specified by the transition table for that type of node.

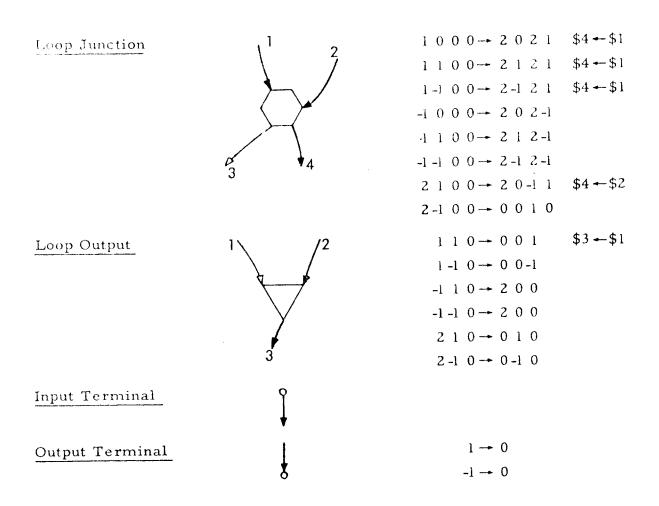

The transition table for a type of node specifies all of the active configurations of the node in terms of the statuses of the input and output connectors. For each active configuration the transition table also specifies the <u>final configuration</u> i.e., the status of each connector after completion of the transition, and the change, if any, of the data contents of output data links.

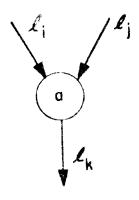

The specification of the transition table is simplified by certain conventions and a notation adopted from the work of Petri. Peach connector of the node is assigned a sequential number. A configuration is then represented by writing the link status values from left to right in the sequence determined by the ordering assigned to the set of connectors. Thus the configuration 1 1 0 corresponds to a node with three connectors in which connector number 1 is in status 1, connector number 2 is in status 1, and connector number 3 is in status 0. A transition is denoted by writing the active configuration followed by  $' \rightarrow '$ , followed by the final configuration. If a transition changes the data contents of some link, an expression is written after the final configuration defining the new new value. Thus the expression  $$1 \leftarrow f_1$  (\$2, \$3) means that the data contents of connector 1 is replaced with the result of applying function  $f_1$  to the data contents of connectors 2 and 3.

### Operator Data operator \$3-f(\$1,\$2) $1 \ 1 \ 0 \rightarrow 0 \ 0 \ 1$ Function $1-1 0 \rightarrow 0 0-1$ -1 1 0 $\rightarrow$ 0 0 -1 $-1 -1 0 \rightarrow 0 0 -1$ \$2,\$3-\$1 $1\ 0\ 0 \rightarrow 0\ 1\ 1$ Identity $-1 0 0 \rightarrow 0 -1 -1$ Control operator $1 \ 1 \ 0 \rightarrow 0 \ 0 \ 1$ And $1-1 0 \rightarrow 0 0-1$ $-1 \ 1 \ 0 \rightarrow 0 \ 0 -1$ $-1 -1 0 \rightarrow 0 0 -1$ $1\ 1\ 0 \rightarrow 0\ 0\ 1$ Or $1-1 0 \rightarrow 0 0 1$ $-1 \ 1 \ 0 \rightarrow 0 \ 0 \ 1$ $-1 -1 0 \rightarrow 0 0 -1$ Selector $1-1 \ 0 \ 0 \rightarrow 0 \ 0-1-1$ -1 1 0 0 $\rightarrow$ 0 0 -1 -1 $-1 -1 0 0 \rightarrow 0 0 -1 -1$ $1-1 0 \rightarrow 0 0 1$ **\$3**<del>-</del>-\$1 Junction \$3--\$2 -1 1 0 $\rightarrow$ 0 0 1 $-1 -1 0 \rightarrow 0 0 -1$

Table 2.1 The Transition Tables of Program Graph Nodes

Table 2.1 The Transition Tables of Program Graph Nodes

Table 2.1 contains the transition tables for each type of node. A brief description of the characteristics of each type follows.

#### 1. Operators

Operator nodes denote functions of one or more input arguments and one or more output values. An operator node all of whose inputs and outputs are data links is called a data operator. Similarly an operator all of whose inputs and outputs are control links is called a control operator.

Every operator is either a data or a control operator. The data operator representing the identity function will always be denoted by the symbol 'I'. The control operators representing logical disjunction and conjunction will always be denoted by the symbols 'V' and 'A' respectively. These are the only control operators allowed in a program graph.

#### 2. Selectors

Selector nodes denote decision-making elements. A selector is associated with a predicate function. All inputs of a selector are data links and there are precisely two control outputs. When the predicate associated with a selector is applied to the data contents of the inputs the result is to place one output connector in enabled status and the other in disabled status.

Selectors and data operators may have a control input connector in addition to their data connectors. The function denoted by a selector or data operator is applied only for those active configurations in which all input connectors are in enabled status.

### 3. Junctions

Junction nodes merge two or more sources of data. A junction transmits the data contents of at most one of its data inputs to its unique data output.

#### 4. Loop Junction

Loop junction nodes are used to form cyclic structures in a program graph. Their function can be roughly described as follows: Suppose one has an iterative process and A, B, C represent the quantities on which the iteration depends, then to every one of these variables there will correspond a loop junction. Input connector 1 is used to 'assign' the initial value of the variable and input connector 2 is used to 'assign' the new value of the variable on every iteration. I shall often refer to input connectors 1 and 2 as the initial and feedback connectors of the loop junction.

#### 5. Loop Output

Loop output nodes are used in conjunction with loop junctions to precisely define what is to be considered the result of an iterative process. Proper usage of loop output nodes requires that their control input connector be attached to the control output connector of a loop junction. Some of the examples in the next section will serve to clarify the relationship between loop junctions and loop outputs.

#### 6. Input Terminals

Input terminals are nodes with no inputs and precisely one output.

#### 7. Output Terminals

Output terminals are nodes with no outputs and precisely one input.

#### D. THE CONSTRUCTION OF PROGRAM GRAPHS

This section sets forth the rules for constructing program graphs and provides a few examples of the use and abuse of these rules.

A program graph is a finite set of input terminals, output terminals, and nodes interconnected by data links and control links according to the following rules:

- 1. The root of a data link must be attached to an input terminal or to a data output connector and its tip must be attached to an output terminal or to a data input connector.

- 2. The root of a control link must be attached to a control output connector and its tip must be attached to a control input connector.

- 3. Every input connector of a node must be attached to some link.

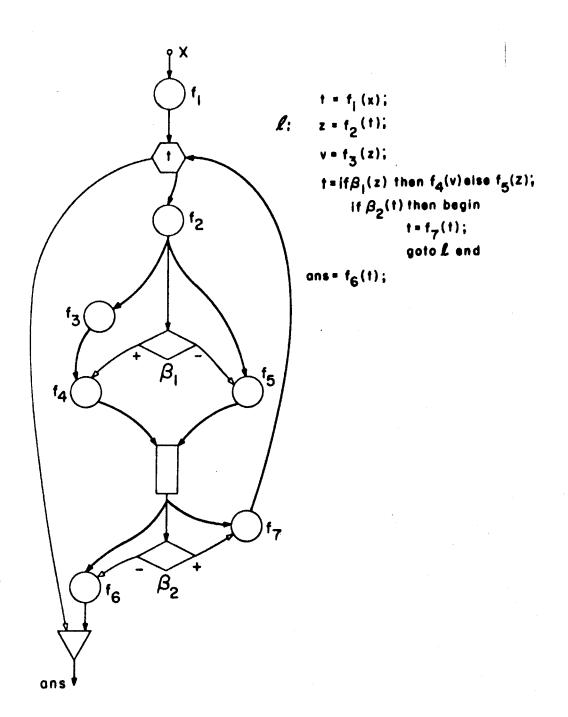

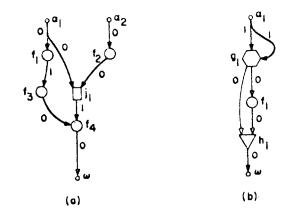

Figures 2. 3, 2. 4, 2. 5, and 2. 6 are examples of program graphs.

Each example is provided with an Algol-like description of the algorithm.

Figure 2. 3 illustrates how functional composition is represented by the interconnection of data operators. Figure 2.4 illustrates the use of loop junctions and loop outputs in a simple iterative process. The arrangement illustrated in the figure is used whenever an output value, e.g. "ans" is desired only upon completion of the iterative process. Quite often iterative processes are used which do not behave this way, but instead output values are produced on every iteration. A common example of this type of iteration is that of a program producing lines of output. Figure 2.5 shows another example of this situation which is perhaps not as obvious as the 'output feeder' case. The flow chart representation of this algorithm shows a single loop however, upon separating the data flow from the control flow in the program graph representation, two distinct loops arise: a counting loop (loop junction labelled i) and a summation loop (loop junction labellet t) with the counting loop effectively controlling the iterations of the summation loop. It should be noted that this type of relationship between two or more loops often gives a clue to one of two forms of parallelism among sub-parts of the process:

Sqrt  $(\sin(x \mid 2) + \cos(1 - \tan(y) \mid 2))$

Fig. 2.3 Functional Composition in a Program Graph

Fig. 2.4 A Simple Iterative Process

- 1. <u>Horizontal parallelism</u> meaning simultaneous operation of individual computations without imposing requirements on the sequence of using the results.

- 2. Vertical parallelism meaning simultaneous computations with certain sequential constraints as to the use of the results of each computation.

In the example of Figure 2.5 horizontal parallelism will be possible given the extra knowledge that addition is commutative and associative, otherwise we have to be content with vertical parallelism, i.e. initiation of as many functions as possible, but adding them in the specified sequence.

The final example of this section, shown in Figure 2.6, illustrates one single loop (in the flow chart sense) with more than one loop junction. Recall that each loop junction represents one variable of the iterative process and a loop junction is required even for those quantities which are not changed within the loop because there is no permanent storage in a program graph, as is the case with the quantity denoted by A in Figure 2.6.

## E. THE EXECUTION OF PROGRAM GRAPHS

The transition tables for program graph nodes determine the dynamic behavior of a program graph by specifying whether or not a node should be activated, and if it is activated, whether or not certain data transformations should take place.

Unless otherwise specified, all links are initially in the IDLE(0) status. Execution of a program graph begins when enough input terminals have been placed in ENABLED(1) status to produce an active configuration on some node of the graph. For simplicity, however, we usually assume that there is time,  $t_0$ , at which all input terminals are placed in ENABLED status simultaneously.

Program Graph and Flow Chart of an Iterative Process Fig. 2.5

Fig. 2.6 A Single Loop with Multiple Loop Junctions

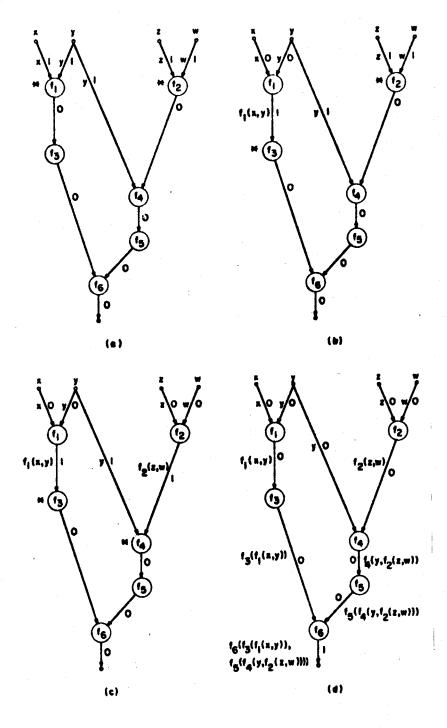

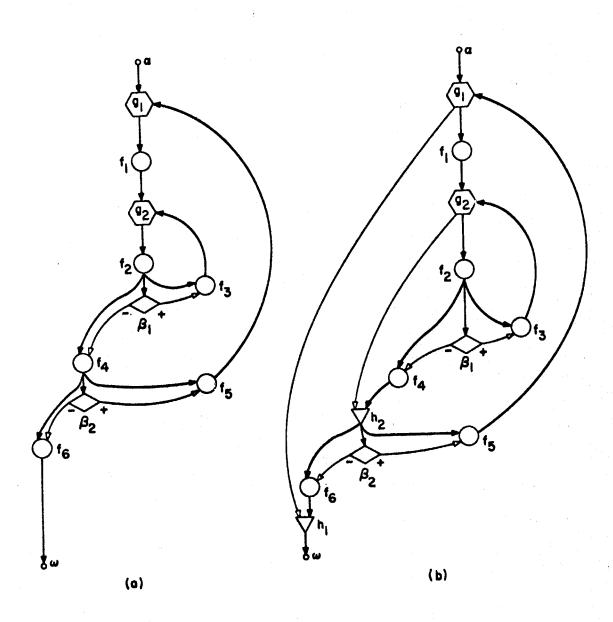

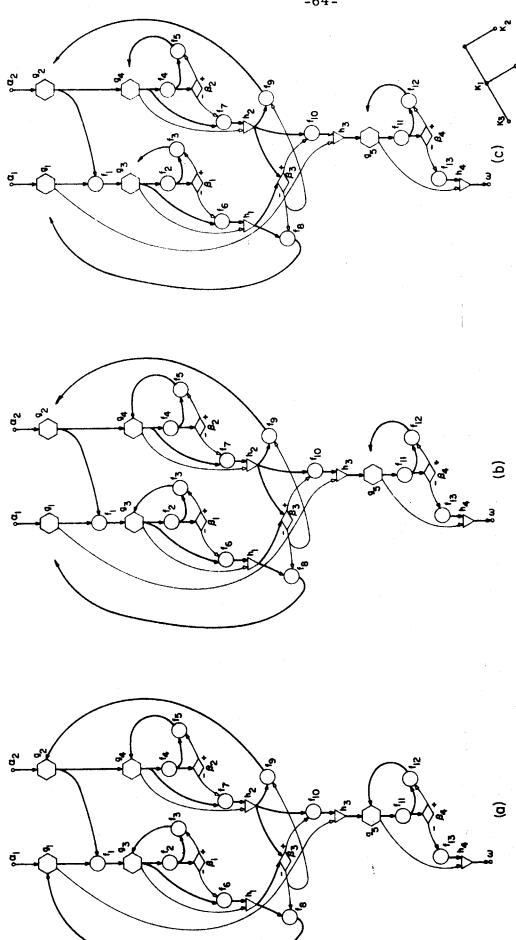

A simple example will serve to illustrate how the execution of a graph takes place. Figure 2.7 shows a program graph at various stages of execution. In these figures, the number written to the right of each link is the link-status at the time of the snapshot; the data contents of the link is written to the left of the link as a functional expression. A '\*' next to a node signifies that the node is in an active configuration.

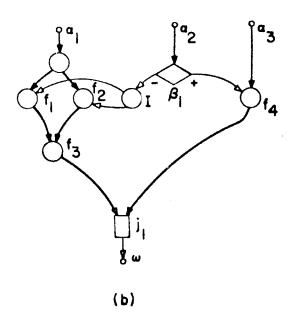

Figure 2. 7a shows the state of the graph shortly after time,  $t_0$ , with operators labelled  $f_1$  and  $f_2$  active. In Figure 2.7b operator  $f_1$  has completed its transition enabling  $f_3$  to become active while  $f_2$  still has not finished. The final snapshot Figure 2.7d shows the state of the graph upon operator  $f_6$  having completed its transition. Note that all links have been restored to the IDLE status.

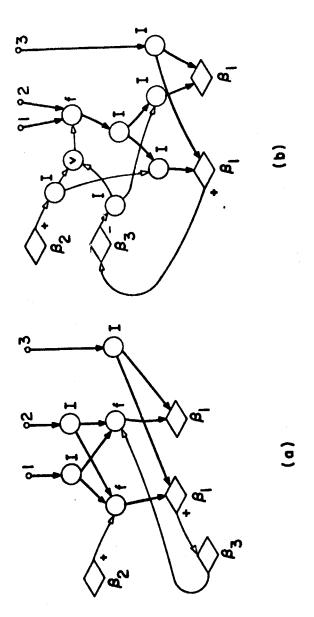

Figure 2.8 shows a complex situation, arising due to the presence of a loop. Figure 2.8a, b, c are snapshots during the execution of a nonfinal iteration showing the state of the graph before the activation of selector  $\beta_2$  at two successive time intervals after the completion of the selector transition which enables the output link labelled '-'. Figure 2.8d, e, and f is a similar sequence, but in this case  $\beta_2$  has enabled the output link labelled '+' signalling the end of the iterative loop. These sequences serve to clarify the purpose of the link-status value blocked which only affects loop junctions and loop outputs. While the loop is in progress, the initial connector of the loop junction is in blocked status, effectively blocking any attempt to initiate a new loop before finishing the current one. In the meantime the loop output blocks any signals to the outside world. When the loop junction receives an indication that the cycle has finished (DISABLED status of the feedback connector), it signals the loop output that it is alright to allow an output to be produced. Again, note in Figure 2.8f that upon completion of the iterative process all link-status values have been restored to the IDLE status.

Fig. 2.7 States During the Execution of a Cycle Free Program Graph

States During the Execution of a Cyclic Program Graph Fig. 2.8

## F. THE DETERMINISM OF PROGRAM GRAPHS

The rules for interconnecting nodes set forth in Section D do not place any restriction on the topology of the resulting program graph.

Furthermore, it has been specifically assumed that we have no knowledge of the time elapsed between the initiation and the completion of a transition. These two situations combined can result in the specification of a process whose behavior is unpredictable in the sense that two distinct executions of the process with the same set of data values supplied at the input terminals may produce a different set of results.

The behavior of a program graph is determined by the link-status and the data contents of the links of the graph. We shall denote these two properties of a data link by an ordered pair (s, d) where  $\underline{s}$  can take any of the link-status values -1, 0, 1, 2 and  $\underline{d}$  is a functional expression, e.g.  $f_1(x, f_2(y, z))$  denoting the value of the data contents. In the case of a control link, data contents is not defined so that only the link-status value  $\underline{s}$  will be used.

If n is the number of links in a graph, then the state of the graph is an ordered n-tuple  $A = (a_1, a_2, \dots a_n)$  where each state variable  $a_i$  is either an (s,d) pair or an s depending on whether  $a_i$  is associated with a data link or a control link. Two states A and B are equal if and only if for all  $1 \le i \le n$ ,  $s_{a_i} = s_{b_i}$  and  $d_{a_i} = d_{b_i}$ . The state determines which nodes of the graph are in an active configuration. We make this explicit by associating with each node an n-tuple as follows:

The ith element of the n-tuple for a node f is zero unless the link associated with the corresponding element of the state is attached to f. In this case the ith element is the number of the connector of f to which the link is attached. For example if the third, fourth, and sixth links of the state vector are attached to the second, third, and first connectors of f, the n-tuple for f is  $(0,0,2,3,0,1,0,\ldots)$ . The n-tuple associated with a node f will be called the connectivity vector of f and is denoted by  $C_{f}$ .

A state A changes into a state A' upon completion of the transition of one of the active nodes of A. The components of the new state A' are determined by those of the old state A and the transition table for the node. If f is any node, the notation  $A' = A \times C_f$  is interpreted as follows:

- If the ith element of C<sub>f</sub> is zero then the ith element of A' is the same as the corresponding element of A.

- 2. If elements of A corresponding to non-zero elements of C<sub>f</sub> form an active configuration of f, the corresponding elements of A' are obtained by using the applicable transition of f.

- 3. Otherwise these elements are not changed and A' = A.

We now introduce the concept of the possible 'next' states A' of a state A by means of the relation  $\mathcal R$ .

Definition 2.1 A state A' follows a state A iff A' results from the completion of the transition of none, one, or more active nodes of A. If A' follows A we write ARA'. We say A' is a next state of A.

Definition 2.2 A final state of a program graph is a state in which no node is active.

From the definition of  $\mathcal{R}$  and final state it is clear that a state A is final if and only if  $A\mathcal{R}$  A' implies A = A'.

During execution, a program graph passes successively from one state to one of its next states.

Definition 2.3 An execution sequence of a graph is a sequence of states  $A_0$ ,  $A_1$ ...  $A_k$  such that  $A_i \mathcal{R} A_{i+1}$  and  $A_i \neq A_{i+1}$ .

Definition 2.4 An execution sequence  $A_0$ ,  $A_1$ ...  $A_k$  is terminal if  $A_k$  is a final state. If  $\sigma$  is an execution sequence, the length of  $\sigma$  denoted by  $\ell(\sigma)$  is the number of states in the sequence.

For a given initial state, a program graph may exhibit several execution sequences depending on the relative speeds of the nodes. The problem of the speed-independence of the final state (when it exists) of a program graph with respect to an initial state  $A_0$  is crucial to the justification of the model. The only requirement that we place on the behavior of a program graph is that every node transition is an indivisible operation, i.e., once a transition begins the indicated changes of status take place simultaneously. This assumption does not say that a node placed in active configuration performs the corresponding transition immediately. Quite to the contrary, we do not place any restrictions in the time interval elapsed from the time an active configuration occurs to the time a transition is actually performed. This of course raises, among others, the possibility of a node entering and leaving an active configuration without performing any transition.

Theorem 2.1 establishes a property of the  $\mathcal{R}$  relation which, as we shall see, is sufficient to guarantee the uniqueness of the final state of a program graph for any assignment of elapsed times to the nodes of the graph. This property of the  $\mathcal{R}$  relation is closely connected to that existing among the states of semimodular asynchronous circuits as described by Muller and Bartky.

Lemma 2.1 Let  $A_0$  be a non-final state of a program graph P and let  $A_1$  and  $A_2$  be any two states of P such that  $A_1 = A_0 \times C_{f_1}$ ,  $A_2 = A_0 \times C_{f_2}$ . Then, there exists a state  $A_3$  such that  $A_i \not\in A_3$   $0 \le i \le 2$ .

Proof: From the definition of the  $\mathcal{A}$  relation, if  $A_0 = A_1 = A_2$  then  $A_0$  satisfies the requirements for  $A_3$ . Similarly if  $A_0 \neq A_1 = A_2$  then  $A_1 = A_2 = A_3$  satisfies the conditions of the lemma. Therefore assume that  $A_0$ ,  $A_1$ , and  $A_2$  are distinct. This means that there are at least two active nodes  $f_1$  and  $f_2$  in  $A_0$ . We claim that the state arising from the simultaneous completion of the transitions of  $f_1$  and  $f_2$  satisfies the conditions for  $A_3$ .

First we note that the active configurations of program graph nodes as shown in Table 2.1 place certain restrictions on the possible interconnection of nodes which are simultaneously active. Specifically, we have the following:

- The status of an output connector is IDLE for any active configuration.

- 2. The only input connector which can be in IDLE status when a node is active is the feedback connector of a loop junction.

These two observations tell us that if two nodes are in an active configuration in the same state then either they do not have a common link or they have a common link which is attached to the feedback connector of a loop junction.

If the nodes  $f_1$  and  $f_2$  in  $A_0$  do not have a common link it is clear that the state  $A_3$  resulting from the simultaneous completion of their transitions is identical to the states  $A_1 \times C_{f_2}$  and  $A_2 \times C_{f_3}$ .

Thus all it remains to show is that when  $f_1$  or  $f_2$  or both are loop junctions sharing a link, the order in which these nodes complete their transitions does not matter. Figure 2. 9a and 2. 9b show the two possible connections that may exist between  $f_1$  and  $f_2$  up to symmetry. In both of these cases an output of  $f_1$  is attached to the feedback connector of  $f_2$  and since  $f_1$  is active this link must be in idle status. The only active

Fig. 2.9 The Possible Configurations of Two Active Nodes Sharing a Link

configurations of loop junctions with a feedback link in idle status are, from Table 2.1, 1000 and -1000. By a straightforward use of Table 2.1 it can now be checked that the value and status of all links attached to  $f_1$  and  $f_2$  are identical independently of the sequence in which their transitions are completed.

Q. E. D.

Lemma 2.2 Let  $A_0$  be a non-final state of a program graph P and let  $A_i = A_0 \times C_{f_i}$ ,  $A_i \neq A_0$  for  $1 \leq i \leq k$ . Then there exists a state  $A_{k+1}$  such that  $A_i \in A_{k+1}$ ,  $0 \leq i \leq k$ .

Proof: Since  $A_i \neq A_0$ ,  $A_0$  has at least k-active nodes  $f_1$ ,  $f_2$ ,... $f_k$ . From the proof of Lemma 2.1, the completion of a transition of an active node cannot place any other active node in a non-active configuration. We claim that state resulting from the simultaneous transitions of  $f_1$ ,  $f_2$ ,... $f_k$  satisfies the conditions of the state  $A_{k+1}$ .

From Lemma 2. 1, there exists a state  $A_{nm}$  such that  $A_0 \mathcal{R} A_{nm}$ ,  $A_n \mathcal{R} A_{nm}$ , and  $A_m \mathcal{R} A_{nm}$  for all  $1 \le n$ ,  $m \le k$  and  $n \ne m$ . States  $A_{ni}$  and  $A_{im}$  are obtained from state  $A_i$  by the completion of precisely one transition, consequently by Lemma 2. 1 we again conclude that there exists a state  $A_{nim}$  such that  $A_0 \mathcal{R} A_{nim}$ ,  $A_n \mathcal{R} A_{nim}$ ,  $A_m \mathcal{R} A_{nim}$ ,  $A_n \mathcal{R} A_{nim}$ , and  $A_{im} \mathcal{R} A_{nim}$  for all  $1 \le i \le k$ ,  $i \ne n$ ,  $i \ne m$ , and n + m. By repeating this process, we must eventually reach a state  $A_{1,2...k}$  satisfying the conditions of the theorem.

Q. E. D.

The construction of Lemma 2.2 is illustrated in Figure 2.10 for the case k = 3. In the process of proving this lemma we also proved the following.

Theorem 2.1 Let  $A_0$  be a non-final state of a program graph P and let  $A_1$ ,  $A_2$ ,...  $A_k$  be states of P such that  $A_0 \mathcal{P} A_i$ ,  $1 \le i \le k$ . Then there exists a state  $A_{k+1}$  such that  $A_i \mathcal{P} A_{k+1}$  for  $0 \le i \le k$ .

Fig. 2.10 The Relation Among the 'Next' States of a State A

Theorem 2.2 Let  $A_0$  be the initial state of a program graph. If there exists an execution sequence  $\sigma_1 = A_0 A_1 \dots A_k$  such that  $A_k$  is a final state then  $A_k$  is unique.

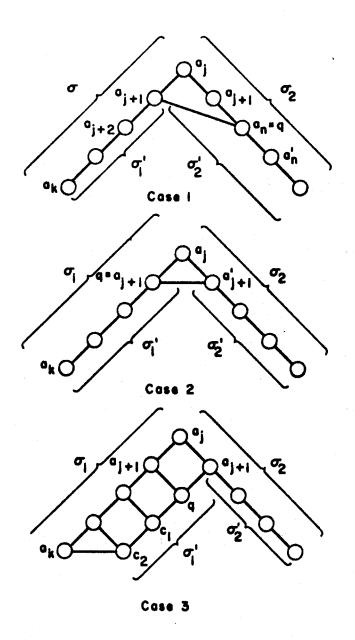

Proof: To prove the theorem we will show that for any other execution sequence with the same initial state as  $\sigma_1$ , e.g.  $\sigma_2 = A_0 B_1 \dots B_m$ , if  $B_m \neq A_k$  then  $B_m$  is not a final state.

The proof consists of constructing two new execution sequences  $\sigma_1'$  and  $\sigma_2'$  such that  $\ell(\sigma_2') < \ell(\sigma_2)$  and every state in  $\sigma_2'$  is also a state of  $\sigma_2$ . Since  $\sigma_2$  is a finite sequence, successive applications of the construction yields sequences  $\sigma_1'$ ,  $\sigma_2'$ ,  $\sigma_1''$ ,  $\sigma_2''$ , ...  $\sigma_1^r$ ,  $\sigma_2^r$  with  $\sigma_1^r = B_m A_1^r \dots A_k$ ,  $\sigma_2^r = B_m$ , i. e.  $A_1^r$  is a next state of  $B_m$ .

To construct the execution sequences  $\sigma_1^{'}$  and  $\sigma_2^{'}$  we proceed as follows:

Let  $A_j$  be the last state in  $\sigma_1$  which also appears in  $\sigma_2$ . There is at least one such common state, namely  $A_0$ .

$$A_{j} R A_{j+1} \text{ in } \sigma_{1}$$

and

$$A_i \mathcal{R} B_{i+1}$$

in  $\sigma_2$

From Theorem 2.1, there exists a state q such that  $A_{j+1} \mathcal{R} q$  and  $B_{n+1} \mathcal{R} q$ . The state q can be either in sequence  $\sigma_2$  or in sequence  $\sigma_1$  or in neither sequence. Specifically, we must consider the following three cases, (Figure 2.11):

1.

$$q = B_n$$

for some  $n \mid 1 \le n \le m$

2.

$$q = A_n$$

for some  $n \neq 1 \leq n \leq k$

3.

$$q \neq A_n$$

,  $q \neq B_n$  for any n.

Fig. 2.11 The Three Cases in the Proof of Theorem 2.2

Set

$$\sigma'_1 = A_{j+1} A_{j+2} \dots A_k$$

$\ell(\sigma'_1) < \ell(\sigma_1)$

$$\sigma'_2 = A_{j+1} B_n B_{n+1} \dots B_m$$

$\ell(\sigma'_2) \le \ell(\sigma_2)$

This case cannot occur indefinitely for if it did we could find two sequences  $\sigma_1^p,\ \sigma_2^p$  such that

$$\sigma_1^p = A_k$$

$$\sigma_2^p = A_k \dots B_m$$

which contradicts the assumption that Ak is a final state.

### Case 2

Set

$$\sigma_1' = B_{j+1} A_n \dots A_k$$

$\ell(\sigma_1') \leq \ell(\sigma_1)$

$\sigma_2' = B_{j+1} B_{j+2} \dots B_m$   $\ell(\sigma_2') \leq \ell(\sigma_2)$

### Case 3

By repeated application of Theorem 2.1 there must exist states  $C_1, C_2, \ldots$  such that

$$q \mathcal{R} C_1 \mathcal{R} C_2 \dots \mathcal{R} A_k$$

where  $C_1$  is a state such that  $A_{j+2} \mathcal{R} C_1$ ,  $q \mathcal{R} C_1$   $C_2 \text{ is a state such that } A_{j+3} \mathcal{R} C_2$ ,  $C_1 \mathcal{R} C_2 \text{ etc.}$  This must stop at  $A_k$  because it is terminal.

Thus we set

$$\sigma'_{1} = B_{j+1} q C_{1} C_{2} ... A_{k}$$

$$\sigma'_{2} = B_{j+1} B_{j+2} ... B_{m} \qquad \ell(\sigma'_{2}) < \ell(\sigma_{2})$$

Since Case 1 must eventually produce sequences  $\sigma_1'$ ,  $\sigma_2'$  such that either Case 2 or Case 3 applies, and in both cases  $\ell(\sigma_2') < \ell(\sigma_2)$  we conclude that eventually sequence  $\sigma_2^r$  will be  $B_m$  alone.

Theorem 2.3 Let  $A_0$  be the initial state of a program graph. If there exists an execution sequence  $\sigma_1 = A_0 A_1 A_2 \dots A_k$  such that  $A_k$  is a final state, then every sequence with initial state  $A_0$  is terminal on  $A_k$ .

Proof: All we need to show is that every execution sequence is terminal and by Theorem 2.2 it will follow that the final state is A<sub>k</sub>.

Assume that there exists a non-terminal execution sequence

$$\sigma_2 = A_0 A_1' A_2' \ldots A_n' \ldots$$

Then we construct two new execution sequences  $\sigma_1'$  and  $\sigma_2'$  such that  $\ell(\sigma_1') < \ell(\sigma_1)$  and  $\sigma_1'$  and  $\sigma_2'$  have the same initial state. Successive applications of the construction yields sequences  $\sigma_1^r = A_k$  and  $\sigma_2^r = A_k \dots A_\ell' \dots$  contradicting the assumption that  $A_k$  is a final state.

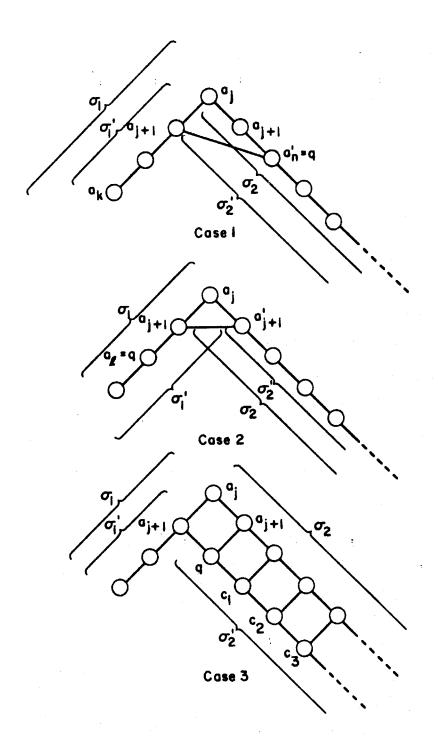

To construct the execution sequences  $\sigma_1'$  and  $\sigma_2'$  we proceed in a similar way as in the proof of Theorem 2.2.

Let  $A_j$  be the last state common to sequences  $\sigma_1$  and  $\sigma_2$ .

$$A_{j} \mathcal{R} A_{j+1} \text{ in } \sigma_{1}$$

$$A_{j} \mathcal{R} A'_{j+1} \text{ in } \sigma_{2}$$

By Theorem 2.1 there exists state q such that  $A_{j+1}$   $\mathcal{A}_q$  and  $A_{j+1}'$   $\mathcal{A}_q$  consider the three cases (Figure 2.12):

1.

$$q = A'_n$$

for some  $n, j+1 \le n$

2.

$$q = A_n$$

for some  $n, j+1 \le n \le k$

3.

$$q \neq A_n q \neq A_n'$$

for any n

### Case 1

Set

$$\sigma_1' = A_{j+1} A_{j+2} \dots A_k$$

$$\sigma_2' = A_{j+1} A_n' A_{n+1}' \dots$$

$A_{j+1} \neq A'_n$  since  $A_j$  is the last common state in both sequences.

Fig. 2.12 The Three Cases in the Proof of Theorem 2.3

Set

$$\sigma'_1 = A'_{j+1} A_{\ell} \dots A_k$$

$\ell(\sigma'_1) \leq \ell(\sigma_2)$

$\sigma'_2 = A'_{j+1} A'_{j+2} \dots$

$A'_{j+1} \neq A_{\ell}$  since  $A_j$  is the last common state in both sequences.

# Case 3

By Theorem 2.1, there exists states  $C_1$ ,  $C_2$ ,... such that  $q \mathcal{R}_{C_1} \mathcal{R}_{C_2} \dots$  Therefore, set:  $\sigma_1' = A_{j+1} A_{j+2} \dots A_k \qquad \ell(\sigma_1') < \ell(\sigma_1)$

$$\sigma'_{2} = A_{j+1} q C_{1} C_{2} \dots$$

To complete the proof, we show that the condition  $\ell(\sigma_1') = \ell(\sigma_1)$  in Case 2 cannot occur indefinitely. From the construction of the sequences  $\sigma_1'$  and  $\sigma_2'$ . if  $\ell(\sigma_1') = \ell(\sigma_1)$  indefinitely, then there exists a state  $A_{j+1}$  in  $\sigma_1$ , and states  $A_{j+1}'$ ,  $A_{j+2}'$ ... in  $\sigma_2$  such that  $A_j \mathcal{A}_{j+1}$ ,  $A_j \mathcal{A}_{j+1}'$ ,  $A_{j+1}' \mathcal{A}_{j+1} \mathcal{A}_{j+1}$ ,  $A_{j+1}' \mathcal{A}_{j+1} \mathcal$

Q. E. D.

#### III. ANALYSIS OF PROGRAM GRAPHS

### A. INTRODUCTION

The results of Chapter II tell us that every program graph represents a deterministic process. It is possible, however, to construct program graphs such that for some or all sets of input values no complete set of output values is ever produced, even when all execution sequences are terminal. If we view a useful computational process as a transformation of a set of input values into a set of output values, then not every program graph represents a useful computation.

The failure of a program graph to produce output values may be caused either by a never-ending cycle or by entering a final state prematurely. It is this second condition, which we call a hang-up state, that we are interested in because it is peculiar to program graphs, and because a study of the structure of graphs where it occurs provides insight into the properties of the model.

The occurrence of a hang-up state during an execution sequence is due to structural anomalies of the graph. These anomalies can arise from obvious misuse of a node for a purpose for which it was not intended, e.g. connecting a loop output control connector to a node other than a loop junction. Less obvious and more interesting structural anomalies arise in connection with communicating cycles. Section B introduces terminology and notation. In Section C we present several examples illustrating the proper use and the misuse of the various node types. Section D considers hang-up states in cycle free graphs. Finally Section E studies hang-up states in cyclic graphs.

# B. NOTATION AND TERMINOLOGY

#### 1. Notation

In this and subsequent chapters we will use the following notation when referring to nodes of program graphs:

Input terminals will be denoted by the letter  $\underline{a}$ .

Output terminals will be denoted by the letter w.

Data operators will be denoted by the letter f.

Selectors will be denoted by the letter  $\beta$ . The output connectors of a selector will be distinguished by writing  $\beta^{\dagger}$  or  $\beta^{-}$ .

Junctions will be denoted by the letter j.

Loop junctions will be denoted by the letter g.

Loop outputs will be denoted by the letter h.

Links will be denoted by the letter 1.

Each of the above symbols will be used with a number subscripts when it is necessary to distinguish among two or more instances of a type, e.g.  $f_1$ ,  $f_2$ ,  $\beta_1$ ,  $\beta_2$ . The letter <u>a</u> will be used to denote a node without specification of its type.

# 2. Paths, Cycles, and Connectivity

The following concepts and terms associated with directed graphs have been adapted from Busacker and Saaty.  $^{\rm l}$

A finite sequence of links  $l_1, l_2, \ldots l_k$  is said to constitute a path of length k in a program graph P if there are nodes  $a_1, a_2, \ldots a_{k+1}$  in P such that  $l_i$  is a link from an output connector of  $a_i$  to an input connector of  $a_{i+1}$ . The path is said to pass through the nodes  $a_1, a_2, \ldots a_{k+1}$ . The nodes  $a_1$  and  $a_{k+1}$  are said to be the initial and final nodes of the path respectively, and it is said that there is a path from  $a_1$  to  $a_{k+1}$ . If  $a_1 = a_{k+1}$  the path is said to be a cycle. If all the k+1 nodes are distinct,

the path is called a proper path. If  $a_1 = a_{k+1}$ , but otherwise all nodes are distinct, the path is said to be a proper cycle. Clearly, all links of a proper path or cycle are distinct. If all the k links are data links the path is called a data path. Similarly, a control path consists solely of control links. A program graph is said to be cyclic if it contains at least one cycle and cycle free otherwise.

Given two nodes  $a_i$  and  $a_j$  of a cycle free program graph P, it is said that  $a_i$  is an ancestor of  $a_j$ , or alternatively that  $a_j$  is a descendant of  $a_i$ , if there exists a proper path from  $a_i$  to  $a_j$ . If  $a_i$  is an ancestor (descendant) of  $a_j$  and there is a path of length 1 from  $a_i(a_j)$  to  $a_j(a_i)$  it is said that  $a_i$  is a direct ancestor (descendant) of  $a_j$ .

A subgraph P' of a graph P is a subset of the set of nodes of P together with all the links connected to these nodes. If for every pair of distinct nodes a and a of P' there is a path from a to a as well as one from a to a, it is said that the subgraph is strongly connected. If, in addition, this condition is not satisfied for any pair of nodes a and a when a but not a is contained in P', then it is said that P' is a maximal strongly connected subgraph (abbreviated mscs).

Two subgraphs P' and P'' of a program graph P are said to be disjoint if they do not share a common node.

# 3. Normal Sequences and Hang-up States

The last two definitions in this section are concerned with certain properties of the initial and final state of execution sequences of a program graph. In order to study the behavior of program graphs it is convenient to concentrate our attention to a limited, yet useful, class of execution sequences by normalizing the initial state of these sequences as follows:

Definition 3.1 A normal execution sequence of a program graph is an execution sequence with an initial state in which all links of the graph are in idle status except for those links attached to the input terminals. Henceforth, execution sequence will be used interchangeably with normal execution sequence. Furthermore, unless otherwise specified we will assume that the links attached to the input terminals are in enabled status in the initial state.

The final state of a terminal execution sequence will be called a <a href="hang-up">hang-up</a> state or a normal state according to whether or not it satisfies the following:

Definition 3.2 A state of a program graph is a hang-up state if

- 1. No node is in an active configuration.

- 2. At least one link is not in idle status.

### C. EXAMPLES OF PROGRAM GRAPHS

# 1. Properties of Transition Tables

In this section we will consider in detail several examples of program graphs. We do this with a dual purpose. First, we want to acquaint the reader as much as possible with the manner of execution of a program graph. Second, we want to provide a better understanding of the properties of each type of node and how they should and should not be used. Concurrently we will indicate some of the reasons for the choices made in the specification of the transition tables.

During execution, the state of a graph changes as a result of the transitions specified by the active configurations of each type of node.

The active configurations of a node are determined only by the status of the input and output connectors of the node. Upon completion of any transition these statuses are always changed. For some transitions the value of the output connectors may also be changed.

An examination of Table 2.1 reveals the following facts:

- 1. In all active configurations of every node type except loop junctions the status of every input connector is never IDLE(0).

- 2. In all active configurations the status of every output connector is always IDLE.

- 3. Upon completion of each transition, except for loop outputs, the status of every output connector is always non-IDLE.

- 4. Upon completion of each transition, except for loop junctions, the status of every input connector is always IDLE.

- 5. Selectors are the only nodes which place one of their output connectors in disabled status when none of their inputs are DISABLED.

- 6. The function and predicate associated with operators and selectors respectively are applied to the input values only if no input is DISABLED.

- 7. The application of the function associated with a data operator to obtain a new value for an output link always results in placing the link in ENABLED status.

Items 1 and 3 suggest viewing the execution of a graph as effecting the flow of status and data information from one node to another in the direction indicated by the oriented links. The IDLE status signifies either that no activity has taken place on a link or that previous activity on a link has been properly accounted for. As a rule, activity must occur at each input to a node before the node can perform any action. The only exception to this rule is the loop junction which under some circumstances, only requires one of its input connectors to be in non-IDLE status to become active. Effectively this means that each node waits to receive information from each of its ancestors before it takes any action.

Items 2, 3, and 4 point out that new activation of a node cannot occur until the information transmitted to the immediate descendants of the node has been used by these descendants. This observation together with items 6 and 7 imply that, as a rule, both the status and data of a link attached to an input connector of a node are effective for precisely one activation of the node. The only exception to this rule can be found in loop junctions and loop outputs both of which have provisions for 'remembering' status and data information. This property of loop junctions and outputs appears to be needed in order to obtain a deterministic model in the presence of cycles.

Finally, items 5 and 6 point out the unique function of selectors as the arbiters which determine the functions and predicates that should be applied during the course of an execution sequence. Note that application of a function or predicate requires that the associated node be active, however the converse is not true. In fact, most of the active configurations shown in Table 2.1 do not require application of a function, predicate, or effecting a data transmission operation. Instead, their only purpose is to propagate through the graph the necessary status information. The enable and disable statuses get their names from the effect that a link exhibiting these statuses have on the data transformation and transmission action of the nodes to which the link is attached.

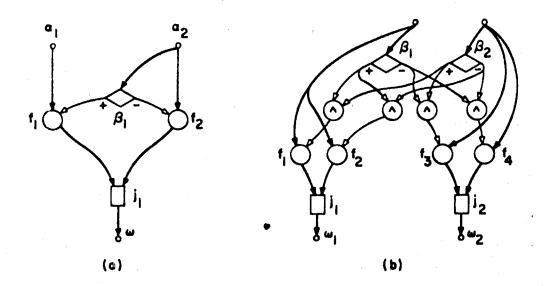

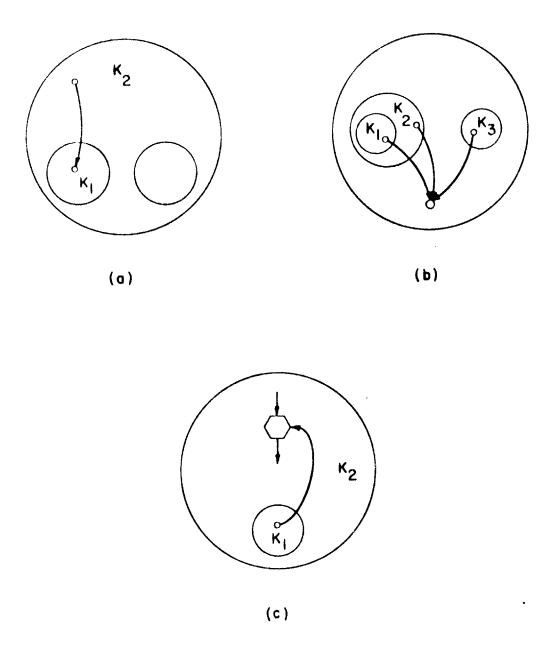

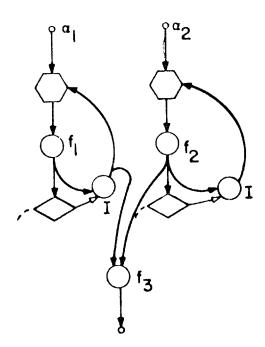

### 2. The Use of Selectors and Junctions

Selectors and junctions have complementary functions. If we view the action of a selector as choosing between two alternative sequences of data transformations, then the purpose of a junction is to transmit the result of whichever sequence was chosen to succeeding computations.

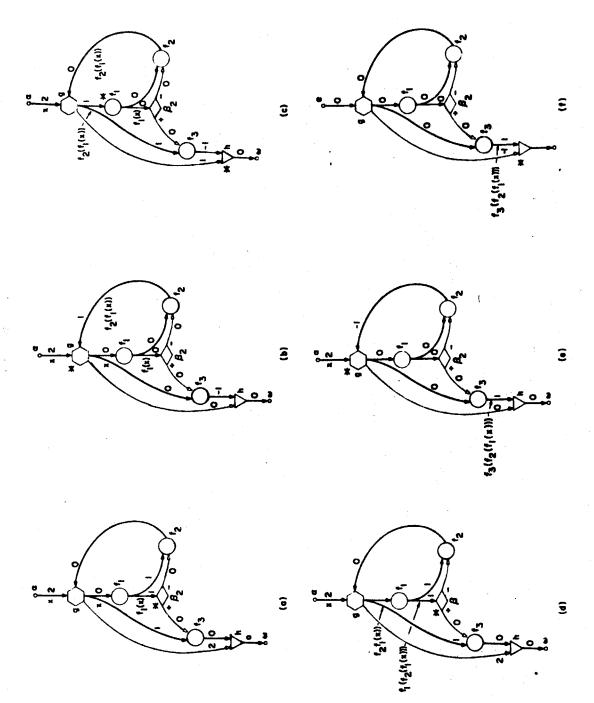

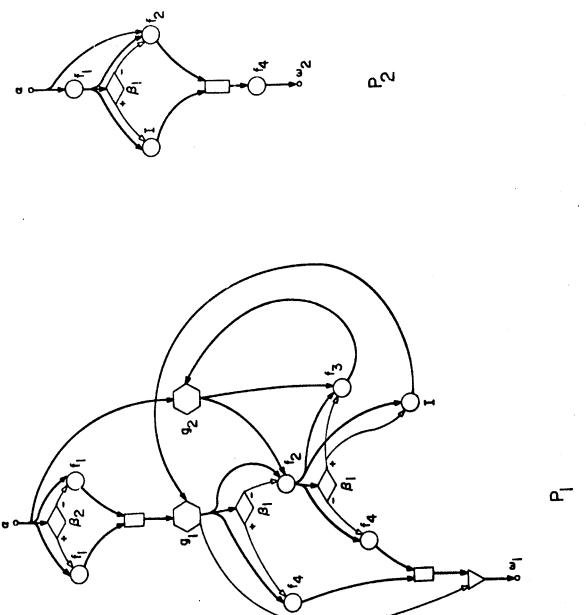

Figure 3. la illustrates the simplest form that this relationship between

Fig. 3.1 Use of Selectors and Junctions

Fig. 3.2 Junctions Creating Hang-Up States

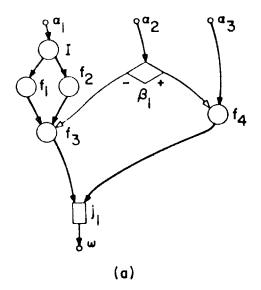

selectors and junctions can take. Clearly one selector can be used to choose one alternative from any number of pairs of sequences. Furthermore, several selectors may have to be invoked, either sequentially or in parallel, when more than two alternatives exist or when complex decision rules are needed. Figure 3.1b illustrates some of these points.

Figure 3. 2a illustrates a typical misuse of a junction. In this graph, data junction  $j_1$  will never become active, since Table 2. 1 requires that one or the other (or both) of its inputs be in the disabled status for any active configuration. Note that if the junction transition table did not have this characteristic, then the output of junction  $j_1$  would depend on the relative speed of operators  $f_1$  and  $f_2$ . Figure 3. 2b shows another example of this situation. In this case, junction  $j_1$  is placed in a hang-up configuration if during an execution sequence the parallel selectors  $\beta_1$  and  $\beta_2$  enable their respective '+' connectors. Compare this with the arrangement of selectors  $\beta_1$  and  $\beta_2$  in Figure 3. 1b where no hang-up configuration arises.

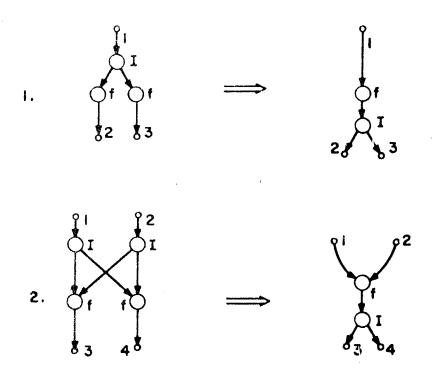

The need for this type of behavior in junctions imply that in order to guarantee determinism we have to:

- 1. have three distinct link status values.

- 2. propagate a disable status throughout the graph.

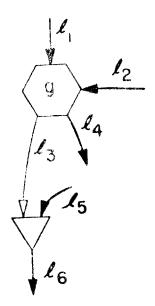

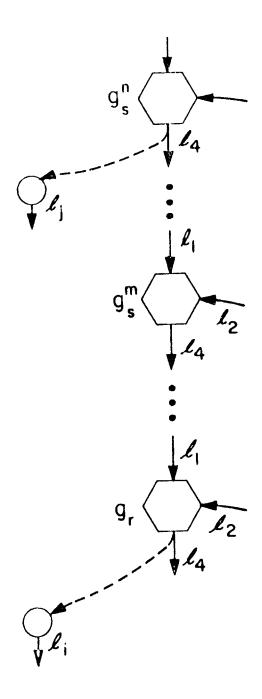

- 3. The Use of Loop Junctions and Loop Outputs

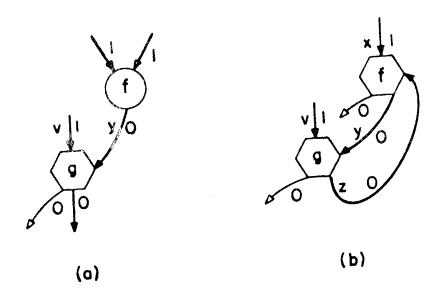

Now let us turn our attention to the use of loop junctions and loop outputs. Loop junctions allow us to construct cycles in a program graph without necessarily introducing hang-up states. To see the necessity of loop junctions, consider the graph in Figure 3.7. If all links are initially in idle status, operators  $f_2$  and  $f_3$  will never become active because the idle output status of each prevents activation of the other. Clearly what is needed is a type of node which does not require each of its inputs to be

in non-idle status before it can become active. We have already seen in the case of junctions that if the inputs of such a node were symmetric, non-deterministic behavior would arise even in the absence of cycles. It is not hard to convince ourselves that in order to have deterministic behavior given an n input node with an asymmetric transition table, the inputs must be arranged in a priority scheme. This priority must effectively dictate that an input cannot place the node in an active configuration unless the node had been previously activated by an input with a higher priority. For, unless this condition is satisfied the sequences of values at the outputs of the node would depend on the sequence of arrival of values at each of the inputs.

In order to implement this priority in a transition table it is necessary to introduce a fourth link status whose function is to remember the history of the activations of the node until such a time as this history becomes irrelevant. The link status blocked(2) serves this purpose in a program graph. Examination of the transition table for loop junctions reveals that the high priority input is the one labelled 1 which we call the initial input. The low priority input, labelled 2 will be called the feedback input. The behavior of a loop junction can be described as follows: The node becomes active as soon as the initial input becomes enabled or disabled independently of what the status of the feedback input is. The next active configuration of the node must be one in which the feedback input is enabled or disabled while the initial input is blocked.

Now we have to make a choice as to when to forget the history of activations of a loop junction. Since we want to allow an arbitrary number of repetitions of a cycle, the cue for this transition must come from the feedback input to the loop junction. The only two information

Fig. 3.3 Single and Parallel Cycles

statuses possible on a link attached to the feedback input are enabled and disabled. The obvious choice is the disabled status.

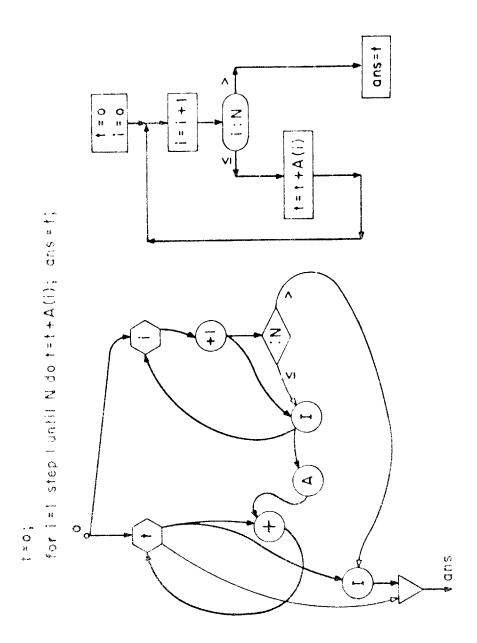

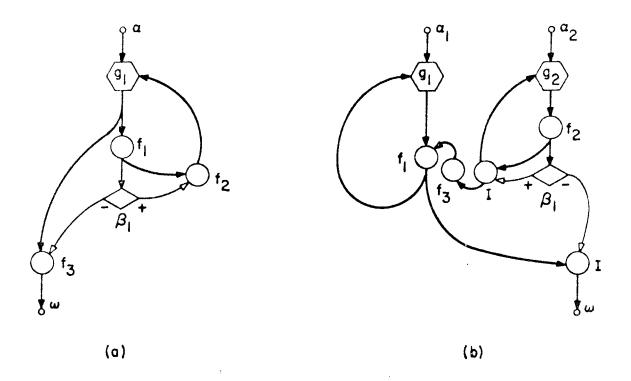

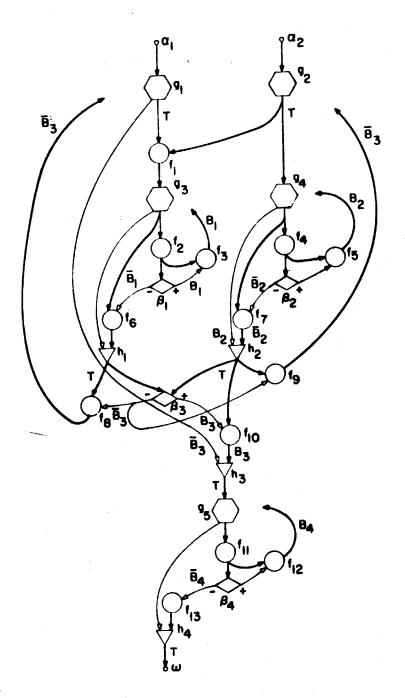

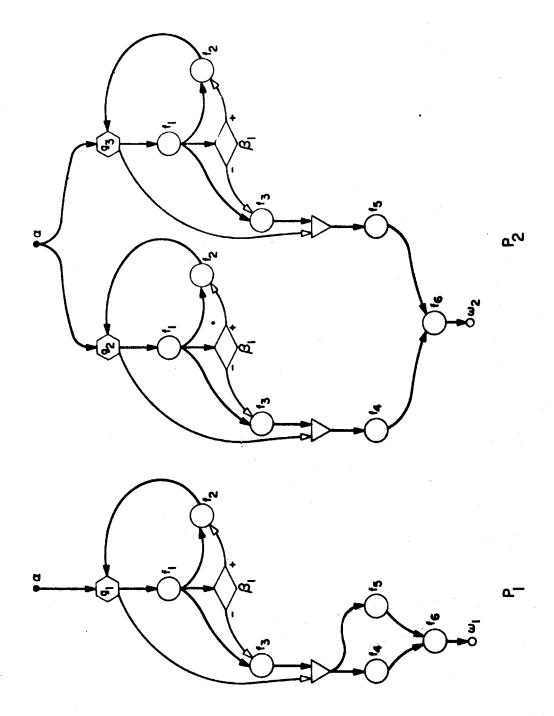

Figure 3. 3a shows a simple example of a cyclic graph. Loop junction g<sub>1</sub> forms a cycle together with operators f<sub>1</sub> and f<sub>2</sub>, and selector  $\beta_1$ . The cycle is initiated by enabling the input terminal a. Each time  $\beta_1^{\dagger}$ is enabled,  $f_2$ ,  $g_2$ ,  $f_1$ , and  $\beta_1$  are reactivated. Note that since enabling  $\beta_1^+$  implies disabling  $\beta_1^-$ , operator  $\beta_3^-$ , which is not a part of the cycle, will be activated on every iteration as well. This secondary effect may or may not be desirable. Figure 3.3b illustrates a cyclic graph with two parallel cycles. The cycle on the left, nodes g1 and f1, receives inputs from the cycle on the right. Both cycles repeat as long as  $\beta_1^+$  is enabled. When  $\beta_1^+$ is disabled, both cycles terminate. Operator f3 is in neither cycle, yet it becomes active during each iteration, in this case performing a useful function. In the example of Figure 3.3a, the repeated activation of f3 causes a sequence of disable statuses to appear at the output terminal  $\underline{\omega}$ . Upon termination of the cycle, the output terminal is enabled. In this instance, it is desirable to prevent the activation of f<sub>3</sub> while the cycle is in progress. In fact, if it is not possible to exert this type of control, we cannot construct graphs with nested cycles which are free of hang-up states. This difficulty is illustrated in Figure 3.4a where after four repetitions of the 'inner' cycle, formed by nodes  $g_2$ ,  $f_2$ ,  $\beta_1$ , and  $f_3$ , every node is unable to enter an active configuration because the output of  $\beta_1^{(+)}$ ,  $f_4$ ,  $f_5$  are in non-idle status and the initial input of g<sub>1</sub> is in idle status.

Loop output nodes have been introduced to avoid such situations.

Figure 3.4b shows the proper use of loop outputs to avoid hang-up states in the example of Figure 3.4a. A loop output should be connected only to a loop junction. The proper form of this connection is illustrated in Figure 3.5.

Fig. 3.4 Nested Cycles with and without Loop Output Nodes

By examining Table 2.1 we can verify that in this arrangement the output link of a loop output becomes non-idle only when the feedback input of the loop junction becomes disabled (provided the initial input had been enabled or disabled), i.e. when the cycle formed by the loop junction terminates.

#### D. ANALYSIS OF CYCLE FREE GRAPHS

## 1. The Role of Cycle Free Graphs

In this section we study certain properties of cycle free program graphs. The simplicity of this class of graphs relative to cyclic graphs makes them a natural starting point in the analysis of program graphs.

Furthermore, some of the questions about cyclic graphs raised in the next section can be satisfactorily resolved by reducing them to similar questions about cycle free graphs.

### 2. Properties of Execution Sequences

Intuitively we expect each execution sequence of a cycle free graph to be terminal. In fact, at this point such a statement should not take us by surprise. However, the method we have chosen to specify the behavior of each node, i. e. the transition table, does not make this property obvious or even necessary. The following theorem and its corollaries are a justification for the choice of directed graphs for our representation.

Theorem 3.1 Every execution sequence of a cycle free program graph is a subsequence of a terminal sequence.

<u>Proof:</u> Assume that the theorem is false. Then we can find an execution sequence which never terminates. Since the number of active configurations in the transition table of each node is finite, it follows that there is at least one node which is placed in the same active configuration an infinite number of times. An examination of Table 2.1 indicates that after completion of the transition of most active configurations of a node, a new active configuration can occur only if the status of the input