Security Classification

| DOCUMENT CONTROL DATA - R & D                                    |                                  |                                             |  |  |  |  |  |

|------------------------------------------------------------------|----------------------------------|---------------------------------------------|--|--|--|--|--|

| (Security classification of title, body of abstract and indexing | annotation must be entered       | when the overall report is classified)      |  |  |  |  |  |

| 1. ORIGINATING ACTIVITY (Corporate author)                       | 2 <b>a.</b> R                    | 28. REPORT SECURITY CLASSIFICATION          |  |  |  |  |  |

| MASSACHUSETTS INSTITUTE OF TECHNOLOGY                            |                                  | UNCLASSIFIED                                |  |  |  |  |  |

| PROJECT MA <b>C</b>                                              | 2 <i>b</i> . G                   | 2b. GROUP                                   |  |  |  |  |  |

|                                                                  |                                  | NONE                                        |  |  |  |  |  |

| 3. REPORT TITLE                                                  |                                  |                                             |  |  |  |  |  |

| STORAGE HIERARCHY SYSTEMS                                        |                                  |                                             |  |  |  |  |  |

| 4. DESCRIPTIVE NOTES (Type of report and inclusive dates)        |                                  |                                             |  |  |  |  |  |

| INTERIM SCIENTIFIC REPORT                                        |                                  |                                             |  |  |  |  |  |

| 5- AUTHOR(S) (First name, middle initial, last name)             |                                  |                                             |  |  |  |  |  |

| STUART E. MADNICK                                                |                                  |                                             |  |  |  |  |  |

| 6. REPORT DATE                                                   | 78, TOTAL NO. OF PAG             | ES 7b, NO. OF REFS                          |  |  |  |  |  |

| APRIL, 1973                                                      | 155                              | 90                                          |  |  |  |  |  |

| BB. CONTRACT OR GRANT NO.                                        | 9a. ORIGINATOR'S REPO            | ORT NUMBER(S)                               |  |  |  |  |  |

| N00014-70-A-0362-0006                                            |                                  |                                             |  |  |  |  |  |

| b. PROJECT NO.                                                   | MAC TR-                          | ·107                                        |  |  |  |  |  |

| c.                                                               | 9b. OTHER REPORT NO this report) | (5) (Any other numbers that may be assigned |  |  |  |  |  |

| d.                                                               | NONE                             |                                             |  |  |  |  |  |

| 10. DISTRIBUTION STATEMENT                                       | <u></u>                          |                                             |  |  |  |  |  |

| DISTRIBUTION OF THIS DOCUMENT IS UNLIM                           | ITED                             |                                             |  |  |  |  |  |

| 11. SUPPLEMENTARY NOTES                                          | 12. SPONSORING MILITA            | ARY ACTIVITY                                |  |  |  |  |  |

| PH.D. THESIS, DEPT. OF                                           |                                  |                                             |  |  |  |  |  |

| ELECTRICAL ENGINEERING,                                          | OFFICE OF                        | ' NAVAL RESEARCH                            |  |  |  |  |  |

| MAY 15, 1972                                                     |                                  |                                             |  |  |  |  |  |

| 13. ABSTRACT                                                     | <u> </u>                         |                                             |  |  |  |  |  |

The relationship between the page size, program behavior, and page fetch frequency in storage hierarchy systems is formalized and analyzed. It is proven that there exist cyclic program reference patterns that can cause page fetch frequency to increase significantly if the page size used is decreased (e.g., reduced by half). Furthermore, it is proven in Theorem 3 that the limit to this increase is a linear function of primary store size. Thus, for example, on a typical current-day paging system with a large primary store, the number of page fetches encountered during the execution of a program could increase 200-fold if the page size were reduced by half.

The concept of temporal locality versus spatial locality is postulated to explain the relationship between page size and program behavior in actual systems. This concept is used to develop a technique called the "tuple-coupling" approach.

Consistent with the results above and by generalizing conventional two-level storage systems, a design for a general multiple level storage hierarchy system is presented. Particular algorithms and implementation techniques to be used are discussed.

DD FORM 1473 (PAGE 1)

UNCLASSIFIED

Security Classification

| Security Classification    |      |      |             |      |        |    |  |  |  |  |

|----------------------------|------|------|-------------|------|--------|----|--|--|--|--|

| 14. KEY WORDS              |      | IK A | <del></del> | IK B | LINK C |    |  |  |  |  |

|                            | ROLE | WT   | ROLE        | WT   | ROLE   | WT |  |  |  |  |

| Storage Hierarchy          |      |      |             |      |        |    |  |  |  |  |

| Virtual Mem <b>o</b> ry    |      |      |             |      |        |    |  |  |  |  |

| Dynamic Storage Allocation |      |      |             |      |        |    |  |  |  |  |

| Operating Systems          |      |      |             |      |        |    |  |  |  |  |

| Paging                     |      |      |             |      |        |    |  |  |  |  |

| Page Size                  |      |      |             |      |        |    |  |  |  |  |

| Replacement Algorithms     |      |      |             |      |        |    |  |  |  |  |

| Computer Architecture      |      |      |             |      |        |    |  |  |  |  |

| Multi-level Memoires       |      |      |             | Ī    |        |    |  |  |  |  |

| Spatial Locality           |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      | i    |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

|                            |      |      |             |      |        |    |  |  |  |  |

DD FORM 1473 (BACK)

(PAGE 2)

UNCLASSIFIED

Security Classification

## STORAGE HIERARCHY SYSTEMS

Stuart E. Madnick

April 1973

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY PROJECT MAC

CAMBRIDGE

MASSACHUSETTS 02139

#### STORAGE HIERARCHY SYSTEMS

by

## STUART ELLIOT MADNICK

Submitted to the Department of Electrical Engineering on May 15, 1972, in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### ABSTRACT

The relationship between page size, program behavior, and page fetch frequency in storage hierarchy systems is formalized and analyzed. It is proven that there exist cyclic program reference patterns that can cause page fetch frequency to increase significantly if the page size used is decreased (e.g., reduced by half). Furthermore, it is proven in Theorem 3 that the limit to this increase is a linear function of primary store size. Thus, for example, on a typical current-day paging system with a large primary store, the number of page fetches encountered during the execution of a program could increase 200-fold if the page size were reduced by half.

The concept of temporal locality versus spatial locality is postulated to explain the relationship between page size and program behavior in actual systems. This concept is used to develop a technique called the "tuple-coupling" approach. It is proven in Theorem 5 that when used in conjunction with conventional hierarchical storage system replacement algorithms, tuple-coupling yields the benefits of smaller page sizes without the dangers of explosive page fetch activity.

Consistent with the results above and by generalizing conventional two-level storage systems, a design for a general multiple level storage hierarchy system is presented. Particular algorithms and implementation techniques to be used are discussed.

THESIS SUPERVISOR: John J. Donovan

FITLE: Associate Professor of Electrical Engineering

#### **ACKNOWLEDGEMENT**

This thesis describes research done at M.I.T. in conjunction with Project MAC and the Department of Electrical Engineering, both of whose support and encouragement are gratefully acknowledged. During the course of this research, I have been fortunate to have had the cooperation of the IBM Cambridge Scientific Center and the Honeywell Information Sciences Center.

I have also benefited greatly from conversations with numerous colleagues. In particular, special mention must be made of Professor J. H. Saltzer, Don Hatfield, Harold Schwenk, Paul Wood, Steve Zilles, Leonard Goodman, and Jerry Johnson, who provided receptive ears and were helpful in unraveling many of the important issues.

By agreeing to be Readers, presumably at a weak moment, Professor J. C. R. Licklider and Dr. Ugo Gagliardi were inflicted upon by this thesis and the associated chaos. I appreciate their cooperation and understanding and look forward to their assistance in the continuation of this research.

I am obligated to acknowledge Professor John Donovan as my supervisor for this thesis. But, during my studies as a graduate student student, he has been much more than just a tnesis supervisor. He has been my teacher, advisor, colleague, and friend. His cooperation and assistance, not to meation his enthusiasm, have had a profound affect upon my research and I am truly grateful.

Most importantly, I thank my wife, Ethel, for striggling through and surviving the tortures of being married to a graduate student for countless years (I'm sure that she has counted them). The same commendations are extended to my sons, Howard and Michael. Unfortunately, I fear that the damage to them might be more permanent. I realized this recently when I learned that in response to a first-grade assignment to write about what you want to be when you grow up, Howard had written: "When I grow up I want to be a student like my daddy".

Work reported herein was supported, in part, by Project MAC, an M.I.T. research project sponsored by the Advance Research Projects Agency, Department of Defense, under Office of Naval Research Contract Nonr-4102(01).

# CONTENTS

| ABSTR  | CT                                     | • • • •                                    | • • • •                              | • • • •                                             | • • •                   | • • • •      | • • • •       | • • • • | • • • • • | • • • • •                             | • • • • • • • •                         | 2                                            |

|--------|----------------------------------------|--------------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------------|--------------|---------------|---------|-----------|---------------------------------------|-----------------------------------------|----------------------------------------------|

| ACKNOW | ILED:                                  | GEME                                       | NT.                                  | • • • •                                             | • • •                   | • • • •      | • • • •       | ••••    | • • • • • | • • • • •                             | • • • • • • • • • • • • • • • • • • • • | 3                                            |

| 1. INI | 1.0<br>1.1<br>1.2                      | Intr<br>Sign                               | cođu<br>lifi<br>cifi                 | ctio<br>canc<br>c Go                                | n .<br>e o              | f Pr         | oble<br>l Acc | ompl    | ishme     | nts                                   |                                         | 9<br>9<br>9<br>10<br>11                      |

| 2. THE | 2.0<br>2.1                             | Intr                                       | odu<br>age                           | ctio<br>Hie                                         | n .<br>rare             | on y         | Obje          | ctive   | es        |                                       |                                         |                                              |

| 3. POS | 3.0<br>3.1<br>3.2<br>3.3               | Intr<br>Majo<br>The<br>Perf                | odu<br>or Po<br>Sto<br>orm           | ctio<br>aram<br>rage<br>ance                        | n<br>eter<br>Hie<br>Mea | cs .<br>erar | chy           | Model   |           | • • • • • •                           |                                         | 39<br>39<br>39<br>44<br>49<br>55             |

|        | 4.0<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Introduction Shad Direction Read Stor Auto | inucious sector se Benati            | ctio<br>ous<br>Stor<br>Fran<br>coug<br>shin<br>ic M | n Hier age sfer n i     | and          | hy Pag        | e Spl   | litti     | ng                                    | Design .                                | 62<br>62<br>64<br>71<br>73<br>77<br>80<br>85 |

|        | 5.0<br>5.1<br>5.2<br>5.3<br>5.4        | Intr<br>The<br>Anom<br>The<br>Sign         | oduc<br>Page<br>alie<br>Page<br>ific | ctio<br>Si<br>S<br>Sicanc                           | ze I<br>ze I<br>ze A    | ssu<br>nom   | e aly e Pa    | qe Si   |           | o o o o o o o o o o o o o o o o o o o |                                         | 86<br>86<br>86<br>88<br>89<br>99             |

# Storije Hierarchy Systems

| 6.          | SPATI   | AL V          | s.   | T EM  | POR      | L        | Loc   | ALI   | ΤY  | MOI     | EL    |         |       | • • • |       |       | • • | 120 |

|-------------|---------|---------------|------|-------|----------|----------|-------|-------|-----|---------|-------|---------|-------|-------|-------|-------|-----|-----|

| -           | 6.      | 0 In          | tro  | duci  | tion     | ١.       |       |       |     |         |       |         |       |       |       |       | • • | 120 |

|             | 6.      | 1 Ty          | pes  | o£    | Pro      | ) JE     | a.m   | Ref   | er  | ence    | Le    | oca 1   | it    |       |       |       |     | 120 |

|             |         |               | ive  |       |          |          |       |       |     |         |       |         |       |       |       |       |     | 122 |

|             |         |               | cal  |       |          |          |       |       |     |         |       |         |       |       |       |       |     | 122 |

|             |         |               | cal  |       |          |          |       |       |     |         |       |         |       |       |       |       |     | 123 |

|             |         |               | ati  |       |          |          |       |       |     |         |       |         |       |       |       |       |     | 124 |

|             |         |               | mae  |       |          |          |       |       |     |         |       |         |       |       |       |       |     | 125 |

|             |         |               |      |       |          |          |       |       |     |         |       |         |       |       |       |       |     |     |

| <b>7.</b> . | SPATI   |               |      |       |          |          |       |       |     |         |       |         |       |       |       |       |     | 126 |

|             | 7.      | O In          | itro | d uc  | tio      | <b>.</b> | • • • |       | • • | • • • • |       |         |       | • • • | • • • | • • • |     | 126 |

|             | 7.      | 1 Tu          | ple  | - Coi | ıpli     | ing      | Ap    | pro   | ac  | h       |       |         |       |       | • • • |       | • • | 126 |

|             | 7.      | 2 E f         | fec  | tiv   | enes     | SS       | of    | Tup   | le  | -Coı    | ipl:  | ing     | • • • | • • • | • • • | • • • | • • | 135 |

| <u>.</u>    | DISCU   | ee <b>r</b> n | N A  | M ID  | י מי חיד | 111      | STO   | NS    |     |         |       |         |       |       |       |       |     | 137 |

| o •         |         |               |      |       |          |          |       |       |     |         |       |         |       |       |       |       |     |     |

|             |         |               | tro  |       |          |          |       |       |     |         |       |         |       |       |       |       |     | 137 |

|             |         |               | ınna | _     |          |          |       |       |     |         |       |         |       |       |       |       |     |     |

|             | 8.      | 2 Fu          | ırth | er    | Mork     | •        | • • • | • • • | • • | • • • • | • • • | • • • • | • • • | • • • | • • • | • • • | • • | 139 |

| REI         | FERENC  | ES A          | ND   | BIB:  | LIO      | RAI      | PHY   | • •   | • • | •••     | • • • | • • • • | • • • | • • • | • • • | • • • | ••  | 141 |

| BLO         | OGRAPH. | ICAI          | . NO | ΤE    |          |          |       |       |     |         | • • • |         |       |       |       |       | • • | 154 |

# ILLUSTRATIONS

| 1.          | Structu  | re of  | a Sto  | rage H    | ierarchy        | System   | • • • • • • • • • • • • • • • • • • • • | 41   |

|-------------|----------|--------|--------|-----------|-----------------|----------|-----------------------------------------|------|

| 2.          | Format   | of Log | rical  | Addres    | s               |          |                                         | 46   |

| 3.          | Example  | of Pa  | ge Tr  | ice Si    | mulation        |          | • • • • • • • • • • • •                 | 53   |

| 4.          | Paje Sp. | littin | g and  | Shado     | w Storag        | e        |                                         | 69   |

| 5.          | Read Thi | rough  | Struc  | ture.     |                 |          |                                         | 75   |

| <b>5.</b> . | Example  | of Ca  | se 1   | • • • • • | • • • • • • • • |          |                                         | 90   |

| 7.          | Example  | of Ca  | se 2   | • • • • • |                 |          | • • • • • • • • • • •                   | 93   |

| 8.          | Example  | of Ca  | se 3   |           |                 |          |                                         | 94   |

| 9.          | Example  | of Ca  | se 3   | (for L    | RU Remov        | al)      |                                         | 98   |

| 1).         | Cyclic   | Page   | Trace  | with      | M 1   = 2       |          |                                         | 10 3 |

| 11.         | Cyclic   | Page   | Trace  | with      | M1  = 3         | •••••    |                                         | 106  |

| 12.         | Cyclic   | Page   | Trace  | with 1    | FIFO Rem        | oval     |                                         | 118  |

| 13.         | Example  | e of L | RU Rei | oval i    | with Tup        | le-Coupl | ing                                     | 128  |

| 14.         | Example  | e of F | IFO R  | moval     | with Tu         | ple-Coup | ling                                    | 131  |

# TABLES

| •• | Representative Storage mieratchy                   | 28  |

|----|----------------------------------------------------|-----|

| 2. | Major Parameters of Storage Hierarchy              | 40  |

| 3, | Marginal Increase in Page Transfer Times           | 66  |

|    |                                                    |     |

|    |                                                    |     |

|    | MAJOR THEOREMS                                     |     |

|    |                                                    |     |

| 1. | Page Size Anomaly Existence Theorem (FIFO)         | 95  |

| 2. | Page Size Anomaly Existence Theorem (LRU)          | 97  |

| 3. | Steady-State Page Fetch Ratio (LRU), $/r/= H^1 +1$ | 105 |

| 4. | Steady-State Page Fetch Ratio (FIFO)               | 119 |

| 5  | WTanle-Counling# Limite r to 2                     | 122 |

#### CHAPTER 1.

#### INTRODUCTION AND PLAN OF THESIS

#### 1.0 Introduction

The primary goal of this thesis is to provide insight into and shed additional light on several key problems in the design and analysis of general storage hierarchy systems.

#### 1.1 Significance of Problem

The importance of research in storage hierarchy systems has been pointed out by Prof. F. J. Corbato recently in the MIT Project MAC Progress Report VIII (July 1971):

"By now, it has become accepted lore in the computer system field that use of automatic management algorithms for memory systems, constructed of several levels with different access times, can provide a significant simplification of programming effort. ... Unfortunately, behind the mask of acceptance hides a worrisome lack of knowledge behind how to engineer a multilevel memory system with appropriate algorithms which are matched to the load and hardware characteristics."

On multiple level storage hierarchies, Prot. J. H.

Saltzer was even more explicit (subject notes on "Information Systems", MIF, 1972, p. 4-58):

"An interesting problem arises if one has three or more technologies to deal with. ... The problem of predicting the performance of a three level, automatically managed system is not at all well understood. ... Although the need for more than one level has already been argued, there is currently no known criterion for introducing three, four, or N levels for a given system. ... Although there are by now many implementations of two level memory systems, the dynamic management of a three or more level memory system is such an uncharted area that there do not yet exist examples of practical algorithms which one can examine."

## 1.2 Specific Goals and Accomplishments

The specific goals and accomplishments of this thesis, which are further elaborated later, are:

- Analyze the affect of certain parameters, such as page size, upon the performance of a storage system.

- Develop a concept of locality based upon both spatial and temporal adjacency in address reference patterns that explains certain anomalies discovered in actual paging systems.

- Propose, formalize, and measure the performance of new "spatial-removal" storage management algorithms, in particular "tuple-coupling".

- Design a practical algorithm for effective

management of multiple level storage hierarchy systems and demonstrate its effectiveness under some simulated system loads.

# 1.3 Ganeral Structure of Thesis

The key plan of this thesis is to investigate several crucial problems and requirements of multiple level storage hierarchy systems. Particular areas are identified and corresponding theories developed and proven. A new and general design for storage hierarchy systems is also presented and evaluated. Finally, empirical measurements are presented to validate and calibrate the overall design and specific theoretical conjectures.

This thesis is organizationally divided into 8 chapters. The structure can be best introduced by outlining the content of the following chapters in the sections below.

# 1.3.1 Chapter 2: Motivation for Storage Hierarchy Systems

This chapter presents a perspective on the storage hierarchy problem and the motivation for such systems. It is primarily written for the benefit of people knowledgeable in the general computer field but who are not especially experienced in storage hierarchy systems. For the expert

reader, this chapter exposes the biases and orientations of the author and thus sets the tone for the remainder of the thesis. This chapter also briefly reviews the history of research in storage systems and cites numerous references.

## 1.3.2 Chapter 3: Formalization of Storage Hierarchy Systems

A description and formalization of the basic characteristics of storage hierarchy systems is presented in this chapter. This is followed by a summary and critical analysis of research that directly relates to the specific yeals of this thesis.

## 1.3.3 Chapter 4: A Storage Hierarchy System

In this chapter the key concepts of the proposed storage hierarchy system are presented and discussed. The principle and novel techniques are briefly described below:

## 1.3.3.1 Continuous Hierarchy

The ratio of performance between adjacent levels is kept moderate (e.g., a factor of 100 or less) to minimize discontinuities or awkward special-case algorithms. This is in contrast to many current systems with inter-level ratios of 1000 or more.

## 1.3.3.2 Shadow Storage and Page Splitting

Information is transferred in decreasing smaller size blocks as it is passed up from low performance levels of the hierarchy toward the "request generator" at the uppermost level. Thus, the information that is finally received by the request generator has left a "shadow" behind in the lower levels. The significance and rationale for this technique is further elaborated in Chapter 6.

## 1.3.3.3 Automatic Management

In order to reduce the load on the central processor and provide for more efficient and parallel operations, the storage management function will be distributed and incorporated into the storage levels (e.g., "intelligent" device controllers [1], etc.). This technique also reduces the complexity of the operating system software.

#### 1.3.3.4 Direct Transfer

Storage transfers between two adjacent levels need not have any effect upon nor require the assistance of any other levels (e.g., there is no need to move information from

level n to level 1 and then from level 1 to level n-1 if only level n to level n-1 was needed; this two step process is often required on contemporary systems). Direct transfer is accomplished by synchronizing non-mechanical storage levices or by using "rubber-band" buffers [33] between electro-mechanical storage devices.

## 1.3.3.5 Read Through

Storage transfers, as noted above, are only made between adjacent levels of the hierarchy, such as from level n to level n-1. But, each level, such as level n-1, can connect its input bus (from lower level n) to its output bus (to higher level n-2) so that the data can be <u>read through</u> (i.e., transferred to level n-2 while being stored in level n-1). A similar, though specialized, technique is already used in certain systems, such as the IBM System/370 Models 155 and 165 cache systems [52].

This results in performance similar to a direct connection from each level to the request generator but it provides much more control in the storage levels and a much simpler structure.

#### 1.3.3.6 Store Behind

By using the excess capacity of the inter-level clannels, there is a continual flow of altered data from the higher levels to the lowest level permanent storage. Thus, the actual updated information is stored behind (after) the store initiation from the request generator. The updated information is propagated down, level by level. Whenever information is altered at a particular level, it is tagged as altered and is scheduled for a "store behind" operation.

## 1.3.4 Chapter 5: Analysis of Page Size Considerations

One of the most important parameters of a storage hierarchy system is the page size chosen as the unit of transfer between two levels of the hierarchy. In this chapter, the factors influencing page size are examined from the device characteristics viewpoint and the program behavior viewpoint.

Of particular concern, it has been noticed by Hatfield [47] and Seligman [78] and formalized in Chapter 5 that:

"There exists a page trace, P, and demand-retch FIFO-removal or LRU-removal inter-level storage systems, S and S', with page sizes N and N'=N/2, respectively, such that the ratio, r, of fetch frequency f' to f exceeds 2."

This result runs counter to the hoped for behavior of decreased page sizes as noted by Denning [25]:

"... small pages permit a great deal of compression without loss of efficiency. Small page sizes will yield significant improvements in storage utilization..."

In this chapter the significance of this problem is demonstrated by proving that even "well-behaved" removal algorithms, such as stack algorithms [63], are not immune to this adverse performance behavior. Furthermore, the nature of this phenomenon is analyzed and bounds on its behavior are developed.

1.3.5 Chapter 6: Spatial vs. Temporal Locality Model of Program Behavior

A primary rationale for hierarchical storage systems is based upon the "Principle of Locality". Unfortunately, this principle is still a poorly understood, or at least controversial, phenomenon. It is difficult to determine the original "discoverer" of this principle but it is interesting to note that its definition has changed in time. For example, Denning [29, p.3], in 1968 loosely described locality as:

"the idea that a computation will, during an interval of time, favor a subset of the information available to it."

Later, in 1970, Denning [26, p.180] defined it more precisely based upon the concepts of "working set" and "reference density", which for a page i at time k:

a(i,k) = Pr[reference r(k)=i],

sica that R(k) is the ranking of all n pages based upon a(i,k); thus:

"PRINCIPLE OF LOCALITY: The rankings R(k) are strict and the expected ranking lifetimes long."

This is a much more restrictive definition of locality than his earlier general concept.

In fact, many current storage management systems were devised first, a general model was then constructed to describe the system, and finally a "formal" definition of locality was developed to be consistent with the storage management model. This is a reasonable strategy as long as the underlying concepts of "the principle of locality" are not lost in the process. Unfortunately, this appears to have happened on several occasions. In particular, most popular definitions of locality tend to be useless for analyzing or explaining either the relationship of page size upon program behavior or the impact of generalizing from

two-level storage systems to multiple level hierarchical storage systems.

In this chapter a new view of locality is presented (or an old-view resurrected since it most closely resembles some of the very early descriptions of locality). In particular, it is shown that the general concept of locality can be subdivided into two separate factors, temporal locality and spatial locality. These concepts are defined and justified and then used to explain some peculiar phenomena ("anomalies") observed in actual two-level storage systems.

By means of address traces and storage system simplifications, the temporal and spatial locality behavior of actual programs is emperically measured. These results are used to reinforce and calibrate the storage hierarchy system design presented in Chapter 4.

1.3.6 Chapter 7: Spatial Removal Storage Management Algorithms

Various hierarchy storage management algorithms, such as fetch (e.g., demand-fetch) and temporal removal (e.g., first-in first-out (FIFO), least recently used (LRU), etc.) have been developed, primarily for two-level hierarchies. There appear to be no spatial removal algorithms described

in the literature. Based upon Chapter 6, several spatial algorithms are proposed and analyzed.

It is also shown that some cf the problems described in Chapter 5 can be solved by spatial removal algorithms. In particular, Hatfield [48] noted that:

"is yet we have been unable to prove that there is a replacement algorithm using only the past history of page requests which cannot generate more than twice the exceptions with half size pages."

In this chapter a new algorithm, named <u>tuple-coupling</u>, is presented. It is formally proven that it satisfies Hatfield's requirements above.

Furthermore, the operational behavior of tuple-coupling is analyzed by measuring the performance of actual programs.

# 1.3.7 Chapter 8: Discussion and Conclusions

In addition to a general summary of the significant aspects of the thesis, this charter also outlines important areas for future research.

#### CHAPTER 2.

#### THE STORAGE HIERARCHY PROBLEM

## 2.0 Introduction

The evolution of computer systems has been marked by a continually increasing demand for faster, larger, and more economical storage ficilities. In addition to the obvious concern for better performance, the organization of a computer system's storage plays a key role in program development and programmer efficiency. It has often been claimed that "any software design blunder can be overcome by adding more memory".

It has become generally recognized that the conflicting requirements of high-performance yet low-cost storage may be best satisfied by a mixture of technologies combing expensive high-performance devices with inexpensive lower-performance devices. This strategy has been given several names, such as "hierarchical storage system", "automatic multilevel storage management", "virtual memory", and the inevitable "virtual memory system for the automatic multilevel management of a hierarchy of storage devices". In this thesis the somewhat shorter term storage hierarchy

system will be used.

Investigations into automated storage hierarchy techniques can be traced back more than a decade. If we ware to include manual techniques, we would find storage hierarchies at the very dawn of the "computer age". Unfortunately, there are still many unsolved and poorly understood problems. This situation can be partly explained by the fact that these systems tend to be (1) extremely complex, (2) ill-suited to most conventional analytical techiques, and (3) deeply influenced by the rapidly evolving computer technology which keeps "changing the ground rules" at often frightening rates. In spite of these challenging stumbling blocks, a successful storage hierarchy system is so important to the future usefulness of computer systems that we cannot afford to abandon the search.

## 2.1 Storage Hierarchy Objectives

Before delving into details, it is worthwhile to briefly consider the needs and uses for an effective storage hierarchy.

## 2.1.1 System Performance and Economics

AS logic tecanology a nd computer architecture tecaniques have advanced, we have found it possible to produce systems of incredible speed. Such systems are often rated, rather crudely, in terms of MIPS (millions of instructions per second). Experimental system of over 100 MIPS have been developed (e.g., ILLIAC IV and CDC STAR). Even "conventional" large-scale systems have passed the 5 or 1) MIPS mark (e.g., CDC 7600 and IBM 370/195). It has long been observed that the input/output (I/O) requirements, especially for "seconlary storage", of a conventional system tend to be strongly related to the processor's speed. fact, based upon several empirical measurements, it has been postulated that a computer system averages 1 bit of I/O for every instruction executed (this is often referred to Andahl's Constant [ref]). As a result, many of these high-performance systems have been confronted with massive bottleneck problems in the I/O area, especially since these I/O demands tend to occur in bursts. An effective storage hierarchy system could go a long way toward reducing this problem.

At the other end of the spectrum we find that mediumand low-cost processors, the latter are usually called minimomputers, have made substantial advances in recent

The term "mini" can be quite misleading. years. processors are typically hundreds of times faster than the early commercial computers at a fraction of the cost (e.g., the UNIVAC I, circa 1951, could perform about 2000 12-digit additions per second whereas contemporary mini-computers operate at around 1,000,000 5-digit additions per second). Although these mini-processors may be midgets compared to the computational problems attacked by their "big brothers" described above, they are more than adequate for the vast majority of infomation processing problems which have modest computational requirements. Due to technological advances and economies of scale resulting from large-scale production, some minicomputers are available for less than \$2000 with slightly slower micro-computers being offered for little as \$66 [18]. In spite of these technological alvances, these processors have not had much impact on most information system needs due to the continuing economic problem of producing large capacity inexpensive storage devices even at the modest performance required. A \$66 processor is largely irrelevant if the storage costs are in the \$100,000 or more range. By developing an effective storage hierarchy system, we can go a long way toward bringing the storage costs down to the level or these inexpensive processors. As a result, a tremendous number of currently known technical solutions to information processing problems will finally become economically

feasible solutions.

## 2.1.2 Simplify and Automate Programming

As noted earlier, the organization of a computer's storage system has a considerable impact upon program development and programmer efficiency. To a large extent, this potential increase in productivity is obtained by reducing or eliminating constraints normally imposed by the storage system. These constraints often distract the programmer to the extent that he devotes a substantial amount of his time to overcoming the system's limitations rather than solving the intrinsic problems. Shooman [80] noted that:

"The inherent error content of some programs is claimed to be related to the excess memory capacity available. The theory here is that if the memory is very cramped, the software writers will have to resort to overlays and other coding "tricks" to squeeze the desired functions into the allocated memory space. It is assumed that these tricks introduce great complexity and are the seat of many errors. This effect is cited by designers of airborne computers where the allocation of another block of 4k of memory is a major design decision."

For example, the programmer often has to worry about:

# 2.1.2.1 Programming language code efficiency.

If a higher-level language compiler tends to produce programs that are at all larger than those produced by a low-level language translator, it may be necessary to use the low-level language to conserve storage. This constraint is contrary to the generally accepted fact that high-level languages enhance programming productivity.

## 2.1.2.2 Program size.

For any specific storage size, there are programs that cannot be easily written to fit into that size constraint.

Yet, programmers frequently try - with considerable effort.

## 2.1.2.3 Data structures.

The programmer is often faced with the need to choose between a data structure representation that is convenient to use and another representation that "saves storage". This saving may require the use of an awkward or unnecessarily complex data structure representation.

## 2.1.2.4 Specific equipment characteristics.

If the programmer must get the "most" out of his storage system in terms of capacity and performance, he may resort to techniques that are peculiar to his specific storage system equipment. If the equipment is changed, there may be a considerable impact upon his software.

We would like to develop storage hierarchy techniques that eliminate, automate, or at least minimize the programming problems described above.

## 2.1.3 Integrate New Technologies and Applications

Although there has been continual evolution, the basic storage device technologies in commercial use have not changed dramatically in the past decade. As a result, there has been a tendency, motivated by actual need, to relate applications to the specific available technologies. This has caused certain application areas to be abandoned as "infeasible" and many storage management strategies to be discredited as "irrelevant" or "inefficient". In the passage of time we remember the applications and techniques in use but frequently forget or ignore the alternatives possible and the reasons for bypassing these alternatives.

After this rather long "rest", it appears that we are on the verge of some major "awakenings" in applications and technology. It is hard to quantify the new application needs other than requiring more and faster storage for less money. Section 1.1.2 presents some of these motivations, the revitalized interests in time-sharing, artificial intelligence and automatic programming are also "fanning the fire".

Due to the uncertainty of advanced research in storage device technologies, it is difficult to forsee accurately which of the many active efforts will succeed (see for example, Ayling [7], Best [15], Bobeck [16], Camras [17], Dell [24], Fields [35], Gardner [39], Howard [50], Matick [8Matick.], Myers [69], Rector [74], Shahbender [79], Thompson [85]). Considering the technical advances clearly demonstrated in the laboratory and the driving "profit" motivation, it is reasonable to expect some dramatic changes in the next few years. Even if we don't know what or when, we would be foolhearty to totally ignore this situation.

Table 1 below indicates the performance and price characteristics of typical current-day storage technologies. The two entries marked by question marks (?), Bulk Store and Giant Store, indicate new technologies that have already

(ft1)

| Davica                                   | Random<br>Access<br>Time<br><u>(seconds)</u> | Rate                  |                             | Capacity<br>( <u>bytes</u> ) |

|------------------------------------------|----------------------------------------------|-----------------------|-----------------------------|------------------------------|

| 1. Cache Store<br>(IBM 3165)             | 1.6x10 <sup>-7</sup><br>(16) ns)             | 1x10a<br>(100M b/s)   | 8.8x10°<br>(\$8.80)         | 1.6x10*<br>(16K)             |

| 2. Main Store (IBM 3360)                 | 1.44x10-6<br>(1.44 us)                       | 1.6x107<br>(16M b/s)  |                             | 5.12x10 <sup>\$</sup> (512K) |

| 3. Bulk Store? (AMS SSU[35])             |                                              | 8x106<br>(8 M b/s)    | 8.8x10 <sup>-2</sup> (8.8¢) | 2x106<br>(2M)                |

| 4. Large Store (IBM 2305-2)              | 5x10-3<br>(5 ms)                             | 1.5x106<br>(1.5M b/s) |                             | 1.1x107<br>(11M)             |

| 5. Mass Store (IBM 3330)                 | 3.8x10-2<br>(38 ms)                          | 8x 105<br>(800K b/s)  | 4.5x10-4<br>(.045¢)         | 2x108<br>(200M)              |

| 6. Giant Store?<br>(Grumman<br>MASSTAPE) | 6x10°<br>(6 sec)                             | 6x105<br>(600K b/s)   | 2.2x10-5<br>(.0022¢)        | 1.6x1010<br>(16B)            |

Table 1.

Representative Storage Hierarchy

limited Since these peen placed in use. two cost/performance positions were nct part our "traditional" technologies, we are faced with the problem of possible modifying our applications and developing new strategies to efficiently, effectively, and, hopefully optimally, integrate them into our overall hierarchical storage system.

As the entire spectrum of computer architectures, as well as storage device technologies, undergoes reshufflings, both evolution as well as revolutions, it is worthwhile to review and reconsider our current concepts on storage system design. Table 1, although a simplified summary of current storage technologies, illustrates the fact that there exists a spectrum of devices that span about 6 orders of magnitude price/performance (100,000,000%). This issignificant in the light of the excitement that normally accompanies an improvement of 10-20% in performance or a decrease of 10-20% in price in current-day systems. The participants in this "storage sweepstakes" may change in time, but with such large price/performance stakes, there will be continuing benefits to "playing the game" better.

## 2.1.4 Understanding of Program and System Behavior

As noted earlier, the detailed operational behavior of computer systems is often extremely complex. Thus, decisions on hardware, software, and system design must often be made in spite of insufficient knowledge. A better understanding of program and system behavior is essential to the intelligent and efficient development of future systems.

It is hoped that the research to be conducted as part of this thesis will shed considerable light on these matters.

#### 2.2 Storage Hierarchy Approaches

"Storage hierarchy system" and similar terms have been used in many contexts. Consistent with the objectives outlined in the previous section, certain particular contexts are assumed in this research.

## 2.2.1 Spectrum of Approaches

The problems of storage hierarchy management have been attacked by a host of approaches. We can loosely characterize these efforts into three categories:

## 2.2.1.1 Manual Hierarchy Management

Siven a specific ensemble of storage device technologies, after considerable thought the programmer can explicitly or implicitly specify how his information (i.e., programs and data) should be organized and distributed within the hierarchy and how and when his information should be re-arranged. Having determined the distribution, he must also specify his access to specify information accordingly.

When a programmer is directly operating upon his information at the lowest level (e.g., using machine language, direct I/O requests, etc.), he is explicitly controlling the storage hierarchy, this is explicit manual mierarchy management. In most conventional systems, the programmer communicates with the system via programming languages and control cards. Although this can relieve much of the tedious or intricate details of storage management, the overall control of the storage hierarchy is still primarily the responsibility of the programmer. This is implicit manual hierarchy management.

Manual storage management can be very economical since it usually requires no special hardware features nor special system software. Furthermore, it places the control of the

storage hierarchy in the hands of the programmer who is presumably the one most familiar with his needs. Manual storage management, in its many manifestations, is the most common storage hierarchy approach in use today.

Manual storage management has many disadvantages, though. The amount of detail that the programmer must understand and use can add significant complexity to this task. This then introduces additional areas of error and decreased productivity. Furthermore, the assumption that the programmer is the best judge of optimal storage organization is often wrong. The complexities and dynamics common to modern systems are often beyond the understanding of most application programmers.

Multiprogramming, an almost universal technique in current systems, necessitates strategies for global optimization which usually differ substantially from the individual local optimizations of each program. For these reasons there has been continual search for "a better way".

## 2.2.1.2 Semi-Automatic Hierarchy Management

Many techniques have been developed to minimize the amount of effort required of the programmer and to provide feedback to him. The programmer still has the ultimate

control in such a <u>semi-automatic hierarchy management</u> system.

Certain of these techniques are based upon the concept of the programmer providing "hints" to the system. These hints form the basis for a partially automated, partially manual storage management system. Although not especially widespread, this approach has been used in several systems (e.g., Jensen et al [53], O'Neill et al [70], etc.).

If there is a single application that is quite large and complex, techniques have been developed to analyze the actual performance and provide feedback to the programmer. This approach is primarily used in specialized, dedicated, predictable, high-performance systems, such as an airline reservations system. Numerous attempts have been reported, such as Arora et al [5], Ramamoorthy et al [72], etc.

The various semi-automatic hierarchy management approaches help to reduce the programmer's effort and to attain a better local optimization. Although useful for certain applications, these strategies do not remove the disadvantages already noted with manual hierarchy management systems.

## 2.2.1.3 Automatic Hierarchy Management

inherent in a programmer's basic algorithm. In an <u>automatic</u> <u>hierarchy management</u> system, all aspects of the physical information organization and distribution that are irrelevant to the underlying logical structure should be removed from the programmer's responsibility. The programmer may wish to, maybe even be encouraged to, use algorithms that are known to perform well in conjunction with the automated hierarchy management. But, the central responsibility of the storage hierarchy management is removed from the programmer.

Since this approach directly focuses on the storage hierarchy objectives presented earlier, it will be the primary approach to be pursued in this thesis.

# 2.2.2 Spectrum of Analysis Efforts

Each of the storage hierarchy approaches mentioned above, primarily semi-automatic and automatic, have been subjected to various forms of analysis. In this section we briefly outline the principal deficiencies of these efforts.

#### 2.2.2.1 Generalized Models

and popular form of analysis is to assume a generalized model for hardware, software, and system behavior. If one is careful in choosing the characteristics of the model (e.g., Poisson arrival and service times, etc.), it is possible to develop precise analytical solutions. Unfortunately, it is usually difficult to validate these models except for rather simple solutions. Furthermore, since there are few truly automatic storage hierarchy systems in general use, it is extremely difficult to even determine realistic parameters for these generalized models even if the models were valid.

Generalized models have been reported in several papers, such as Aho et al [2] and Denning [25] in the Bibliography.

#### 2.2.2.2 Constrained Models

Another variation on the generalized model scheme is to analyze a particular program and then model its relationship to the rest of the system. There are at least two shortcomings in this approach. Pirst, as in the generalized model case, it is difficult to realistically model the relationship between a program and the rest of the system. Second, the analysis and measurement of the particular

program is normally converted into some form of probability matrix or probabalistic reference pattern. In either case, significant effort is required to accurately measure the program's behavior. Furthermore, the probabalistic characteristics are usually aggregated to reflect the overall behavior of the program and, as a result, the dynamic nature of the program and its impact on the storage hierarchy are often lost.

Example analyses of constrained models can be found in references: Arora and Gallo [5], Hatfield and Gerald [47], Lawis and Yue [60], and Ramamoorthy and Chandy [72].

## 2.2.2.3 Limited Environment

A common deficiency of most previous research is that only a limited environment was considered, in particular automatic hierarchy management over only two levels using a single page size. Of course, most current-day computers have only employed automatic hierarchy management in either Cache Systems (cache store - main store) or Paging Systems (main store - large store). Unfortunately, there is definite reasons to believe that many of the conclusions and techniques demonstrated for a two-level hierarchy do not necessarily generalize to handle the spectrum of program detail and device characteristics encountered in a truly

multiple level storage hierarchy. Furthermore, many of the papers that attempted to investigate general storage nierarchies assumed techniques and approaches that are primarily based upon two-level hierarchy assumptions.

Phis limited environment has been studied by numerous people, such as Aho et al [2], Belady et al [10,11,12], Coffman and Varian [19,86], Conti et al [21,22], Denning [25], Fotheringham [33], Guertin [45], Kilburn et al [57], Mattson et al [63], Seligman [78], Smith [81], and Wilkes [88].

## 2.2.2.4 General Hierarchy Environment

The studies of limited two-level storage hierarchies have been quite successful in many actual systems. A reasonable strategy would be to extend these techniques to a more general storage hierarchy environment. There have been a few attempts along these lines, but as mentioned in the previous section, most were hampered by:

- (1) attempting to directly apply two-level hierarchy techniques without carefully considering their applicability,

- (2) attempting to generalize techniques which were not even fully understood in a two-level environment.

The major thrust of this thesis is to provide insight into and shed additional light on these problems.

#### CHAPTER 3.

## FORMALIZATION OF STORAGE HIERARCHIES AND RELATED RESEARCH

## 3.0 Introduction

In this chapter a formalization of the key characteristics of storage hierarchies is presented and performance measures are derived. The reported performance of actual systems is reviewed.

#### 3.1 Major Parameters of a General Storage System

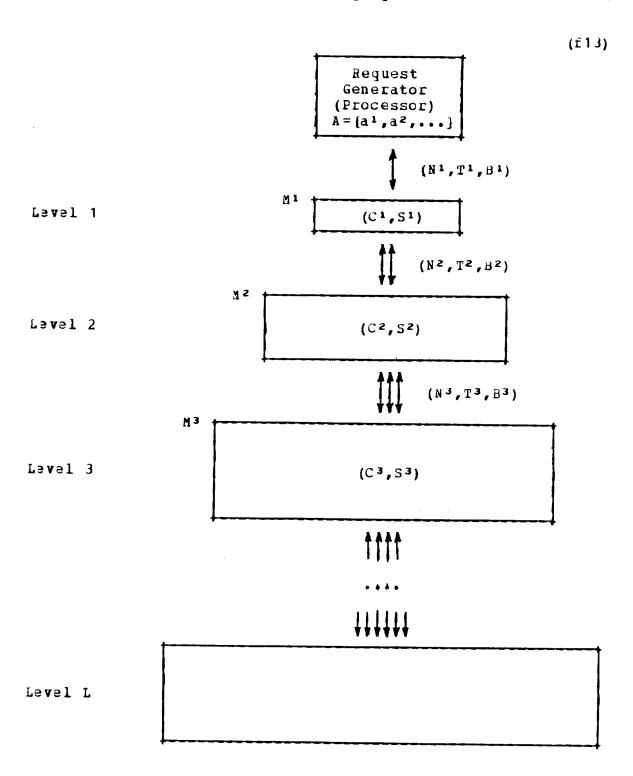

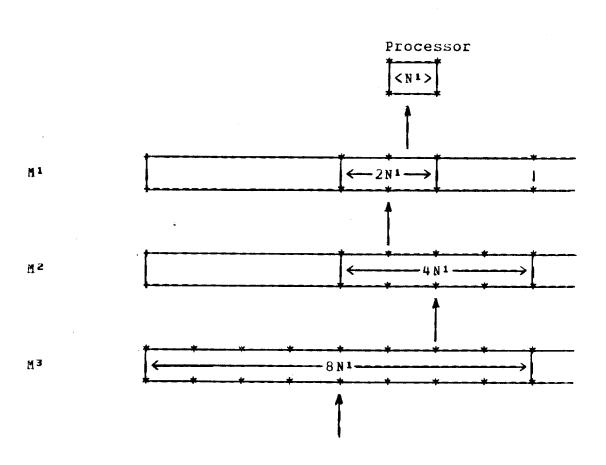

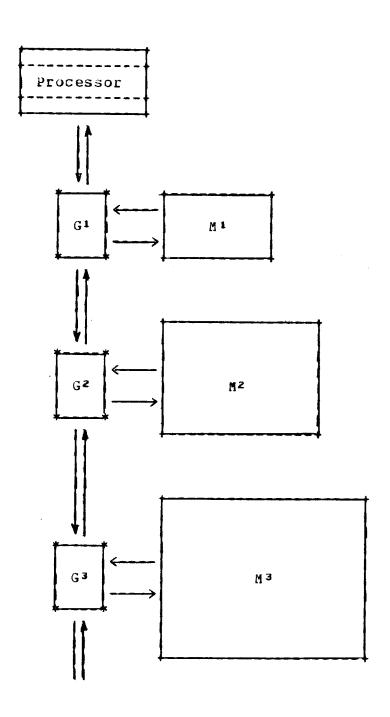

Table 2 and Figure 1 illustrate the major parameters of a storage hierarchy system. These parameters can be grouped into four categories: (1) basic technology, (2) configuration, (3) algorithm, and (4) program behavior.

#### 3.1.1 Basic Technology

The basic technology parameters, <u>cost/byte</u>, C, and <u>average access time</u>, T, are primarily dependent upon the physical properties of the storage device technology. At any given time the state-of-the-art offers only a limited number of (C,T) alternatives that the system designer can select.

(ft2)

## Basic Technology

- C cost/byte

- T average access time

## Configuration

- L number of levels

- I interconnection of levels

- S size (capacity)

- B transfer rate (bandwidth)

- N number of bytes in page (page size)

## Program Behavior

• A address trace

## Algorithm

- F tetch

- P placement

- R replacement

Table 2.

Major Parameters of a Storage Hierarchy System

Figure 1.

Structure of a Storage Hierarchy System

#### 3.1.2 Configuration

The system designer does have flexibility in crganizing these storage devices. By serial and/or parallel structuring of the components of a given level of storage device technology, it is possible to specify, over a wide range of values, the <u>size</u> (storage capacity), S, and the <u>maximum transfer rate</u> (data bandwidth), B, of the system. For example, if a particular technology provides a basic device with S=s and B=b, connecting n of these devices in parallel produces a storage level with S=ns and B=nb. (To some extent the mechanism and cost of the organizational structure does influence the overall cost/byte and average access time of a level, this effect is usually minimal for small values of a).

On a more global basis, the designer must determine the number of <u>levels</u>, L, in the storage system, the <u>interconnections</u> of <u>the levels</u>, I, and the size, N, of a <u>page</u> (the unit of information moved between levels).

#### 3.1.3 Program Behavior

The <u>processor</u>, under program control, produces a sequential series of references to the storage system. These processor references are in the form of <u>logical</u> <u>address</u>

references which serve to uniquely identify each individual unit of stored informatation (e.g., an 8-bit <u>byte</u>) independent of its location (i.e., M¹, M², M³, ...). The time sequence of logical address references, A, is called an <u>aldress trace</u> or <u>address reference pattern</u>. In general, each unique program and its input data will result in a different processor address trace. For purposes of analyzing the effectiveness of the storage hierarchy, the address trace is the primary characterization of a program that is needed (e.g., we don't care what the program's purpose is or what language it is written in, etc., we only care about its aldress trace). Thus, the address trace describes the <u>program's behavior</u> as observed by the storage hierarchy.

#### 3.1.4 Algorithm

There are three basic decision algorithms that must be employed by an automatic storage management system. <u>Fetch</u>, P, decides when and which information should be moved up a level (e.g., from M<sup>2</sup> to M<sup>1</sup>). <u>Flacement</u>, P, decides where information should be placed in a level. <u>Removal</u> or <u>replacement</u>, R, decides when and which information should be transferred down a level (e.g., from M<sup>1</sup> to M<sup>2</sup>).

## 3.2 The Storage Hierarchy Model

A completely general storage hierarchy algorithm, H, must consider all the parameters described above:

## H = f(<Technology>, <Configuration>, <Program>, <Algorithm>)

H = f(<C,T>, <L, I, S, B, N>, <A>, <F, P, R>)

Clearly, attempting to optimize a system with sc many parameters is difficult. Fortunately, it is possible to eliminate from concern or at least simplify certain parameters as explained below.

## 3.2.1 Configuration

Consistent with the title of this thesis, we shall consider only hierarchical interconnections of levels as illustrated in Figure 1, where  $T^1 < T^2 < T^3 <$  etc. and  $N^1 < N^2 < N^3 <$  etc. The rationale for this decision is elaborated in the thesis.

There are three basic strategies for information movement sizes: (1) select a single page size value, N, which is always used throughout the hierarchy - this approach is used on most contemporary automatic multilevel storage systems (e.g., Multics), (2) allow an arbitrary range of values for N to be used - this approach is primarily used on manually managed storage systems, and (3)

select L values of N, a specific unit of transfer is used between any two levels of the hierarchy - this approach will be pursued and justified in this thesis.

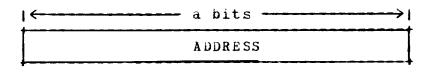

## 3.2.2 Program Behavior

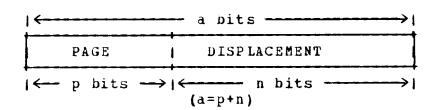

Each logical address can be represented as a bits as shown in Figure 2(a). If the page sizes, N, are chosen to be powers of 2, the set of 2\*\*a possible addresses can be partitioned into 2\*\*p pages of N=2\*\*n consecutive logical addresses each as shown in Figure 2(b). [Note: the notation "2\*\*a" means 2 raised to the power a]. Since the information movement between storage levels is accomplished by transferring pages, we can analyze this interlevel movement by merely considering the time sequence of logical pages references, Ap, called a page trace.

since we allow the page size to be different between each level and requests are only passed down to a given level if they cannot be satisfied by any higher level, each level will usually experience a different page trace though all are algorithmically derivable from the same address trace. In fact, if all address references were broadcast to all storage levels, the page traces can be determined by a simple mapping from logical addresses into logical pages:

page address = integer( logical address/N )

(£2)

# (a) Logical Address

(b) Logical Address (Divided into Page Address and Displacement)

Figure 2. Format of Logical Address

where N is the page size for that level.

3.2.3 Algorithm

The placement decision, P, is usually unconstrained or minimally constrained and, as a result, has relatively little impact upon performance.

A <u>demand fetch</u> policy will be used. Assume that at time t a request for logical address a (or, equivalently,  $p^1$ =integer(a/N<sup>1</sup>)) arrives at level M<sup>1</sup>. At that instant the information may currently reside in M1, otherwise it must be found in a lower level. Under demand fetch, if p1 is in M1, the reference proceeds, the information is passed back to the processor, and no other page movement occurs in the hierarchy. If p1 is not in M1, a request for  $p^2 = integer (a/N^2)$  is sent from M<sup>1</sup> to M<sup>2</sup>. If  $p^2$  is in M<sup>2</sup>, the page is transferred to M¹ and processing continues as described above, otherwise a request for  $p^3$ =integer(a/N<sup>3</sup>) is sent from M2 to M3, etc. Note that under the demand fetch policy, information is only moved up in the hierarchy when and if it is explicitly <u>demanded</u> (i.e., requested) by the processor.

Although demand fetch is only one possible fetch algorithm, it can be shown [63] that for hierarchically structured storage systems:

"... given any trace and replacement algorithm (not necessarily using demand paging) another replacement algorithm exist that uses demand paging and causes the same or fewer total number of pages to be transferred ..."

In other words, as you might intuitively suspect, moving pages only when necessary results in the minimal number of page movements. Of course, if page movement is required and the higher level that is to receive the page is already full, the removal algorithm must be employed to provide space for the new page.

#### 3.2.4 Revised Storage Hierarchy Model

Based upon the discussion above, we can slightly simplify the parameters remaining for consideration in the storage hierarchy algorithm, H, so that it need consider only:

H = f(<Tecnnology>, <Tonfiguration>, <Program>, <Algorithm>)

$$H = f(\langle C, T \rangle, \langle L, S, B, N \rangle, \langle A \rangle, \langle R \rangle)$$

In this thesis all of these parameters will be considered and investigated. Special emphasis will be placed on analyzing and understanding the relationship between the pages sizes, N, and the removal algorithm, R, required for efficient operation of the storage hierarchy.

# 3.3 Performance Measures

There are various performance measures that we could consider. For an overall point of view, system measures, such as job throughput, job turn-arcund time, and processor utilization, are quite significant. Unfortunately, it is extremely difficult to directly relate these measures to the performance of the storage system, even an approximation would require consideration of many more parameters. Thus, we will only consider measures that relate to the effective performance of the storage hierarchy.

#### 3.3.1 Performance Measurement Notation

Due to the strict hierarchical structure of our storage system and the demand fetch policy, we can analyze the performance of the system by separately considering the levels of the hierarchy starting with M<sup>1</sup>. Since a given level only receives a page fetch request if the information has not been found at a higher level, each level usually sees a different page trace, Ap<sup>1</sup>, Ap<sup>2</sup>, Ap<sup>3</sup>, etc.

There are several important properties of page traces. If P is a particular page trace (e.g., Ap1) of a program, we define:

• |P| length of the page trace sequence

- Q set of distinct pages referenced in P

- 101 number of pages in Q

For example, in the page trace

$$P = a, b, a, c, b, a$$

we observe that

$$|P| = 6$$

$$Q = \{a, b, c\}$$

$$101 = 3$$

(Lower case letters will be used to represent logical page aldresses instead of page numbers).

For a specific storage hierarchy, we define |M| to be the size of M in units of pages receivable from the next lower level. For example,  $|M^1| = S^1/N^2$ ,  $|M^2| = S^2/N^3$ , etc.

For a specific page trace, P, storage level, M, and removal algorithm, R, we define the <u>result page trace</u> or <u>fetch page trace</u>, P', as the time sequenced page references of P that were not found in M. We shall call page references that are found in M <u>successes</u>. The <u>success</u> <u>function</u>, Sf, is the number of references satisfied by M and can be computed as |P|-|P'|. By analogy to the success function, the number of references not satisfied by M, |P'|, is called the <u>failure function</u>, Ff. In general, we wish to maximize the success function or, equivalently, minimize the failure function. It is convenient to normalize the failure

function by defining the failure frequency function, f,

$$f = |P'|/|P|$$

The <u>success frequency function</u>, s, can be easily computed as 1-f; it is often called the <u>hit rate</u> on a two-level storage system. We also define the <u>system failure frequency function</u>, fo, of a level to be:

$$\hat{\mathbf{r}}^{0} = |\mathbf{P}^{1}|/|\mathbf{A}|$$

where A is the address trace generated by the processor and |A| is the length of the address trace (it is also true that |A| always equals  $|P^1|$ , thus they may be used interchangeably). The <u>system success frequency function</u> is correspondingly defined as  $s^0=1-f^0$ .

If we apply the definitions above to the processor generated page trace, P¹, received by M¹, we note that the result page trace, P¹, is essentially the page trace, P², received by M². There is a minor relabeling required to adjust for the difference in page size used by M², p²=p¹(N¹/N²). By repeating this process recursively, we can develop the effective page traces, failure and success functions, and failure and success frequency functions for each level of the hierarchy. Since we assume that all referenced information exists in the storage hierarchy, the sum of the system success frequency functions must be 1.

One general measure of a storage hierarchy's

performance is its effective access time, T\*, and effective cost, C\*, which are defined as follows:

$T^1 = T^1S^{01} + T^2S^{02} + T^3S^{03} + \dots$

$C' = (C^1S^1 + C^2S^2 + C^3S^3 + ...) / (S^1 + S^2 + S^3 + ...)$

$\Gamma'$  and C' can be viewed as characterizing the entire storage hierarchy according to a corresponding one-level system. From a cost/performance point of view, one should be indifferent between a single-level single-technology storage device with average access time,  $\Gamma'$ , and average cost/byte, C', and a storage hierarchy system with performance parameters  $(\Gamma',C')$ . In particular, if the system designer needs a storage performance (T,C) and no such basic technology exists, he must attempt to develop a storage hierarchy such that  $(\Gamma',C') = (T,C)$ .

#### 3.3.2 Page Trace Simulation

One way to determine the success frequency function and the result page trace for a specific page trace is to simulate the storage management algorithms and note the contents of M at each step of the page trace. Clearly, these results depend upon numerous parameters (e.g., specific trace, removal algorithm, size of M, etc.). Figure 3 illustrates this step by step simulation assuming demand paging, FIFO (first-in first-out) removal, and |M| = 2 pages. For simplicity, the page trace, P, has been

(£3)

## Parameters

- P = a, b, b, c, b, a, d, c, a, a

- |P| = 10

- $Q = \{a, b, c, d\}$

- 121 = 4

- $\bullet \quad |M| = 2$

- FIFO Removal

## Simulation |

| Page Frace,P                            |   |   |     |        |   |        |   |        |   |        |   |        |     |        |   |        | - |        | - |        |   |         |

|-----------------------------------------|---|---|-----|--------|---|--------|---|--------|---|--------|---|--------|-----|--------|---|--------|---|--------|---|--------|---|---------|

| Fetch                                   | 1 | * | 1   | ×      | 1 |        | 1 | *      | i |        | ı | *      | 1   | *      | 1 | *      | 1 | *      | 1 |        | 1 |         |

| M Contents<br>(after each<br>reference) | 1 | a | 1 1 | b<br>a | 1 | b<br>a | 1 | c<br>b | 1 | c<br>b | 1 | a<br>C | 1 1 | d<br>a | 1 | c<br>á | 1 | a<br>C | 1 | a<br>C | 1 | <-mold* |

| Page frace, P                           |   |   |     |        |   |        |   |        |   |        |   |        |     |        |   |        |   |        |   |        |   |         |

## Results

- $Pf = |P^*| = 7$

- Sf = |P| |P'| = 3

- f = 70%

- s = 30%

- P' = a, b, c, a, d, c, a

Figure 3. Example of Page Trace Simulation

normalized to be expressed in units of receivable pages. In particular, if M is M¹, then |M|=S¹/N² and p=integer(a/N²) where a is a logical address reference and p is corresponding page reference. The pages in M are shown as ordered to indicate the PiFO ordering, the top page is the "last" ("latest") page fetched into M, whereas the bottom page is the "first" ("oldest") page in M and is the page selected for replacement when necessary. The asterisk (\*) indicates that a retch was required from a lower level of the hierarchy, the page reference is thus noted as part of the result page trace, P¹.

It is normally assumed that all levels, except level L, are empty initially, thus there is a transient stage during which pages are loaded into M without any replacements needed. Since there are so few pages in M during this start-up stage, there are many fetches required. We will find it useful to separate out this transient phenomenon. This transient consists of the page trace up to the first | M | unique page references, in the example of Figure 3 this is the first 2 page references (i.e., a, b). Consider the case if |Q| \leq |M|, there would be no further fetches into this level after the initial transient that loads the |Q| pages into M. In this case, |P'| = |Q| exactly, independent of |P|, and s tends toward 1 as |P| increases.

In the particular example illustrated in Figure 3, we note that there were 3 'hits' and 7 'misses' out of 10 page references, so that s=30%. Thus, P' only consists of 7 page references to the lower levels.

#### 3.4 Related Research

As noted above, we wish to develop a storage hierarchy with attractive cost/performance,  $(C^{\bullet},T^{\bullet})$ , characteristics. It is clear that we can arbitrarily decrease the cost/byte by making the size of each level, S, increasingly larger as we go from the high-performance high-cost to the low-performance low-cost levels (i.e.,  $C^{1}>C^{2}>C^{3}>...$  and  $S^{1}<S^{2}<S^{3}<...$ ). In fact, this approach is the basic motivation for storage hierarchies.

Unfortunately, if the processor generated address references that were uniformly distributed in time and address, each byte would be equally likely to be referenced at any instant. This probability would be:

$Pr[reference a] = 1/(S^1+S^2+S^3+...)$

Thus, the expected system success function, so, for each level is proportional to the size of the level. For example,

$$S^{01} = S^{1}/(S^{1}+S^{2}+S^{3}+...)$$

.

But, since we have assumed that  $S^{1} < S^{2} < S^{3} < ...$ , we find that

Lth level dominates (i.e., is approximately 1) since we have assumed that it is the largest level. Referring back to our definition of effective access time, we find that T' would be approximately equal to the lowest performance level (level L) since all the other terms would be negligible. If this analysis were true, our storage hierarchy would result in a performance just slightly better than our lowest performance level at a moderate increase in price - not an especially exciting result. Fortunately, actual storage hierarchies do not behave this way. We will briefly review some related research on this subject.

## 3.4.1 Locality

It has been empirically observed that actual programs cluster their references so that, during any interval of time, only a subset of the information available is actually used. A detailed discussion of this phenomenon will be presented in the thesis.

It is important to note that due to our basic rankings of page sizes and access times in the storage hierarchy, each level "sees" a different view of the program. The high levels of the hierarchy must follow the microscopic instruction by instruction reference pattern whereas the

middle levels follow a more gross subroutine by subroutine pattern. The very low levels are primarily concerned about the processor's references as it moves from subsystem to subsystem. We do not have any a priori guarantee that locality of reference holds equally true for all of these views, but we do have some reported evidence to encourage us. Most of these studies have been based upon two-level storage systems or restricted forms of three-level nierarchies.

#### 3.4.2 Paging Systems

The earliest automatic storage systems were based upon two-level core-drum hierarchies (devices 2 and 4 of Table 1). This technique was introduced in the Atlas system [38,57] during the early 1960's. It has since been used on many contemporary systems.

The performance of paging systems has been studied by various researchers, such as Belady [12], Coffman and Varian [19,86], Hatfield [48], and Sayre [77]. In Coffman's results, for example, it was noted that even though  $S^1/(S^1+S^2)=0.25$ ,  $S^1$  often exceeded 95%. Hatfield studied the performance of system programs that had been carefully designed and found that for  $S^1/(S^1+S^2)$  ratios as low as 0.25, it was possible for  $S^1$  to often exceed 99.99%.

#### 3.4.3 Cache Systems

Tache systems are based upon two-level cache-main hierarchies (devices 1 and 2 of Table 1). Although they have been proposed as early as 1965 (see Wilkes [88]), the major commercial use of cache systems did not occur until the introduction of the IBM System/360 Model 85 [21,61]. More recently, this technique has been used in several contemporary systems, such as the IEM System/370 Model 155 and Model 165 [52].

In these cache systems, IBM found that it was possible to drastically reduce  $5^1/(S^1+S^2)$  to as low as 1% and still keep the hit ratio,  $s^1$ , above 90%. Similar findings were also reported by Bell and Casasent [13], Mattson [64], Meade [55], and Seligman [78].

#### 3.4.4 Three-level Systems

There have been a few three-level systems reported in the literature, unfortunately they have all been somewhat ad hoc in design and the results are far from conclusive. There have been at least three types of such hierarchies studied.

## 3.4.4.1 Main-Bulk-Mass Store Hierarchy

There have been several systems devised based upon devices 2, 3, and 5 of Table 1. The Bulk Store actually used, called Large Core Store (LCS), had a much lower access time (around 8 us) and a much higher price (about 25¢/byte). In order to compensate for peculiarties in the hardware structure and out of considerable concern for the extreme cost of LCS, these systems tended to become much more manually managed hierarchies than automatically managed. Although they were found to be effective, it is difficult to generalize the results. The most ambitious attempt reported was undertaken by Carnegie-Mellon University [36]. Results have also been reported by Durae [31], Williams [89], and others.

#### 3.4.4.2 Main-Large-Mass Store Hierarchy

There does not appear to be any automatically managed systems of this type published in the general literature. The Multics system at MIT Project MAC has recently introduced a "page-multilevel" strategy based upon devices 2, 4, and 5 of Table 1. There has only been limited finding reported to date but it has been stated in the March 1972 issue of the MIT Information Processing Services <u>Bulletin</u>

#### (p. 11) that it

"... does pay off since it meets fluctuating demands on the system, reduces the workload for the disks to an efficient level, is inexpensive, and keeps pages on the drum for an acceptable length of time."