# LAYOUTS FOR THE SHUFFLE-EXCHANGE GRAPH AND LOWER BOUND TECHNIQUES FOR VLSI

FRANK THOMSON LEIGHTON

Laboratory for Computer Science Massachusetts Institute of Technology Cambridge, Massachusetts 02139

June 1982

This report was prepared with the assistance of a National Science Foundation Graduate Fellowship and grant #N00014-80-C-0622 from the Defense Advanced Research Projects Agency.

This empty page was substituted for a blank page in the original document.

# LOWER BOUND TECHNIQUES FOR VLSI

by

#### Frank Thomson Leighton

Submitted to the Department of Mathematics on August 7, 1981 in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **ABSTRACT**

The thesis is divided into two parts. In the first part, we describe and analyze several new VLSI layouts for the shuffle-exchange graph. These include

1) an asymptotically optimal,  $\Theta(N^2/\log^2 N)$ -area layout for the N-node shuffle-exchange graph, and

2) several practical layouts for small shuffle-exchange graphs.

The new layouts require substantially less area than previously known layouts and can serve as the basis for designing large scale shuffle-exchange chips.

In the second part of the thesis, we develop general methods for proving lower bounds on the layout area, crossing number, bisection width and maximum edge length of VLSI networks. Among other things, we use these methods to find

- 1) an N-node planar graph which has layout area  $\Theta(N\log N)$  and maximum edge length  $\Theta(N^{1/2}/\log^{1/2}N)$ ,

- 2) an N-node graph with an  $O(N^{1/2})$ -separator which has layout area  $\Theta(N\log^2 N)$  and maximum edge length  $\Theta(N^{1/2}\log N/\log\log N)$ , and

- 3) an N-node graph with an  $O(N^{\alpha})$ -separator (for  $\alpha > 1/2$ ) which has maximum edge length  $O(N^{\alpha})$ .

The area results indicate that some graphs with  $O(N^{1/2})$ -separators (and, in particular, some planar graphs) do *not* have linear-area layouts, thus disproving a popular conjecture. The edge length bounds indicate that the layouts of some networks must have very long wires (possibly as long as the width of the layout).

Key words: crossing number, graph separator, layout area, maximum wire length, parallel computation, shuffle-exchange graph, Thompson model, Very Large Scale Integration (VLSI)

Thesis supervisor: Gary L. Miller

Title: Associate Professor of Mathematics

#### **ACKNOWLEDGEMENT**

In what follows, I give thanks to the many individuals who have contributed so much, both professionally and personally, to the completion of this thesis. First, I would like to thank Dan Kleitman, Gary Miller and Ron Rivest for serving on my thesis committee. They have each been of great help in preparing this document. In particular, I would like to thank Gary Miller for the extraordinary amount of time he has devoted to me during my tenure at M.I.T. He has been a great source of inspiration and encouragement, and has always made himself available for discussion of my work.

During the course of the last year, several other people have also contributed to the content and writing of the thesis. In particular, I would like to thank Sandeep Bhatt, Dan Hoey, Paris Kanellakis, Margaret Lepley, Charles Leiserson, John Reif, Michael Rodeh, Arnold Rosenberg, Jim Shearer, Clark Thompson and Les Valiant for their helpful remarks and suggestions.

This research was primarily funded through a graduate fellowship from the National Science Foundation. I am deeply indebted to them for their support during the last three years. Additional support was provided by the Defense Advanced Research Projects Agency under Contract #N00014-80-C-0622.

I would also like to take this opportunity to thank some of the many people who have, in the past, gone out of their way to further my educational development. In particular, I would like to recognize the efforts of Forman Acton, Len Adleman, Elva Aucklund, Alan Goldman, Charles Johnson, Phoebe Knipling, Steve Maurer, Dorothy Nelson, Frank Peterson and Dorothy Shriver. I would especially like to thank Carl Hammer, David Labovitz and Morris Newman for sacrificing many hours of their valuable time in order to advise, teach and encourage me.

Lastly, I would like to thank my wife Joanne for her support during the writing of the thesis and my entire family for the lifetime of sacrifices that they have made in order to insure that I obtained the best education available. Without their endless love and support, this thesis would not have been possible.

# **CONTENTS**

| Introduction                                                                                                                        | 2         |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------|

| PART I: LAYOUTS FOR THE SHUFFLE-EXCHANGE GRAPH                                                                                      | 7         |

| Chapter 1: Review of Known Layouts                                                                                                  | 8         |

| 1.1 Thompson's Layout                                                                                                               | 8         |

| 1.2 Hoey and Leiserson's Complex Plane Diagram                                                                                      | 9         |

| 1.2.1 Definition                                                                                                                    | 9         |

| 1.2.2 Properties                                                                                                                    | 10        |

| 1.2.3 An $O(N^2/logN)$ -Area Layout                                                                                                 | 11        |

| Chapter 2: Layouts Based on the Complex Plane Diagram                                                                               | 12        |

| 2.1 A Straightforward O(N <sup>2</sup> /logN)-Area Layout                                                                           | . 12      |

| 2.2 An Improved $O(N^2/\log^{3/2}N)$ -Area Layout                                                                                   | 15        |

| 2.3 Other Layouts                                                                                                                   | 18        |

| Chapter 3: More Sophisticated Layouts                                                                                               | 19        |

| 3.1 Preliminaries                                                                                                                   | 19        |

| 3.2 A Near-Optimal Layout                                                                                                           | 22        |

| 3.2.1 Location of the Nodes                                                                                                         | 22        |

| 3.2.2 Insertion of the Edges                                                                                                        | 23        |

| (a) Exchange Edges Which Link Nodes in Different Rows                                                                               | 24        |

| (b) Exchange Edges Which Link Nodes in the Same Row                                                                                 | 24        |

| 3.3 An Optimal $O(N^2/log^2N)$ -Area Layout                                                                                         | 26        |

| 3.3.1 More Definitions                                                                                                              | 26        |

| 3.3.2 Location of the Nodes                                                                                                         | 27        |

| 3.3.3 Insertion of the Edges (a) Eventuage Edges Which Link Nodes in Different Rows                                                 | ·28<br>28 |

| <ul><li>(a) Exchange Edges Which Link Nodes in Different Rows</li><li>(b) Exchange Edges Which Link Nodes in the Same Row</li></ul> | 29        |

| 3.3.4 Comments                                                                                                                      | 30        |

| 3.4 Layouts With Additional Edges                                                                                                   | 30        |

| 3.4.1 Shift Edges                                                                                                                   | 30        |

| 3.4.2 Reverse Edges                                                                                                                 | 31        |

| 3.4.3 Transpose Edges                                                                                                               | 32        |

| Appendix: Proofs of Lemmas 3-1 Through 3-4                                                                                          | 33        |

| Chapter 4: Practical Layouts                                                                                                        | 40        |

| 4.1 Preliminaries                                                                                                                   | 40        |

| 411 A Closer Look at the Thompson Model                                                                                             | 41        |

| <ul> <li>4.1.2 A Class of Practical Layouts</li> <li>4.2 Optimization Techniques</li> <li>4.2.1 Ordering the Necklaces</li> <li>4.2.2 Inserting the Exchange Edges</li> <li>4.2.3 Additional Savings</li> <li>4.3 Optimal Layouts</li> <li>4.4 Other Layouts</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42<br>42<br>43<br>44<br>46<br>46<br>49                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| PART II: LOWER BOUND TECHNIQUES FOR VLSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                                                                           |

| Chapter 5: Review of Known Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                                           |

| 5.1 Area Bounds 5.2 Edge Length Bounds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51<br>55                                                                                     |

| Chapter 6: Network Constructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59                                                                                           |

| <ul> <li>6.1 The 2-Dimensional Mesh of Trees</li> <li>6.1.1 Definition</li> <li>6.1.2 Properties</li> <li>6.1.3 Applications <ul> <li>(a) Matrix-Vector Multiplication</li> <li>(b) Sorting</li> <li>(c) Switching</li> </ul> </li> <li>6.2 The r-Dimensional Mesh of Trees</li> <li>6.2.1 Definition</li> <li>6.2.2 Properties</li> <li>6.2.3 Application to Matrix Multiplication</li> <li>6.2.4 A Further Generalization</li> </ul> <li>6.3 The Tree of Meshes <ul> <li>6.3.1 Definition</li> <li>6.3.2 Properties</li> <li>6.3.3 Applications</li> <li>(a) Embeddings of Planar Graphs</li> <li>(b) Embedding of M<sub>2,n</sub> in T<sub>n</sub></li> </ul> </li> <li>6.4 The Augmented Mesh of Trees</li> | 59<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>64<br>64<br>65<br>65<br>65<br>67<br>70<br>72 |

| Chapter 7: Crossing Number Arguments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 74                                                                                           |

| <ul> <li>7.1 The Relationship Between Crossing Number and Layout Area</li> <li>7.2 A General Method for Proving Lower Bounds</li> <li>7.3 Applications</li> <li>7.3.1 Lower Bounds for the Shuffle-Exchange Graph</li> <li>7.3.2 Lower Bounds for the 2-Dimensional Mesh of Trees</li> <li>7.3.3 Lower Bounds for the r-Dimensional Mesh of Trees</li> </ul>                                                                                                                                                                                                                                                                                                                                                    | 74<br>75<br>77<br>77<br>79<br>82                                                             |

| 7.4 Further Methods                                            | 83   |

|----------------------------------------------------------------|------|

| 7.4.1 A Combinatorial Lower Bound for Crossing Numbers         | 83   |

| 7.4.2 Applications                                             | . 85 |

| 7.4.3 An Upper Bound for Crossing Numbers                      | 87   |

| Chapter 8: Wire Area Arguments                                 | 89   |

| 8.1 Lower Bounds for the 2-Dimensional Mesh of Trees           | 89   |

| 8.2 Lower Bounds for the Tree of Meshes                        | 93   |

| 8.3 Lower Bounds for a Restricted Class of Binary Tree Layouts | 94   |

| Conclusion                                                     | 97   |

| Index                                                          | 98   |

| References                                                     | 100  |

| Addendum                                                       | 104  |

This empty page was substituted for a blank page in the original document.

# LAYOUTS FOR THE SHUFFLE-EXCHANGE GRAPH

# AND

LOWER BOUND TECHNIQUES FOR VLSI

This empty page was substituted for a blank page in the original document.

#### INTRODUCTION

The recent engineering advances in Very Large Scale Integrated (VLSI) circuitry have made it possible to wire tens of thousands of transistors onto a single chip. In the near future, it is expected that fabrication of chips containing *millions* of transistors will be commonplace [MC80]. In order that this massive computational resource be efficiently utilized, theoretical researchers have been actively trying to answer such questions such as:

- 1) "What is a good model for VLSI chip design and computation?,"

- 2) "What communications networks can best perform important operations such as sorting, matrix multiplication and discrete Fourier transform?" and

- 3) "What is the best method of laying out a network on a chip?."

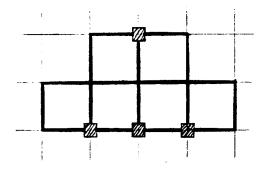

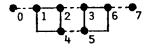

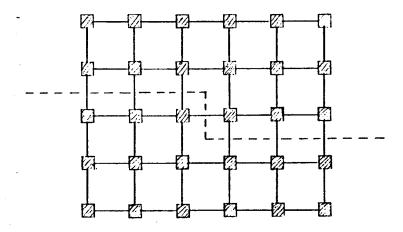

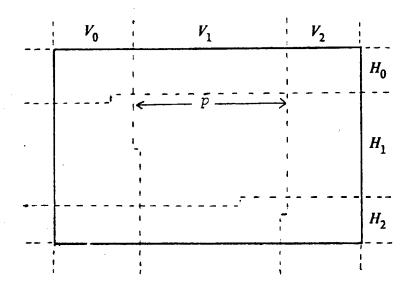

Several models have been proposed for VLSI computation [T80,LS81,CM81]. The most widely accepted is due to Thompson and is known as the *Thompson model* [T79,T80]. Thompson's model of a VLSI chip is quite simple. The chip is presumed to consist of a grid of vertical and horizontal *tracks* which are spaced apart by unit intervals. Processors are viewed as points and are located only at the intersection of grid tracks. Wires are routed through the tracks in order to connect pairs of processors. Although a wire in a horizontal track is allowed to cross a wire in a vertical track, pairs of wires are not allowed to overlap for any distance (i.e., in they cannot overlap in the same track). Further, wires are not allowed to overlap processors to which they are not linked. As an example, we have drawn a Thompson model layout of a 4-processor network in Figure 1.

Figure 1: A Thompson model layout of a 4-processor network in which each processor is linked to every other processor.

Much has also been accomplished in the way of finding good communications networks for VLSI. For example, the complete binary tree [MC80], the 2-dimensional mesh [TK77,KL78,MC80], the cube-connected-cycles graph [PV79] and the shuffle-exchange graph [S71,L75,L76,NS79,P80,S80,SR80a,T79,T80] are all known to be capable of performing a wide range of operations. The shuffle-exchange graph, in particular, is an incredibly powerful and efficient communications network. Among other things, it can be used to compute discrete Fourier transforms, multiply matrices, sort lists and evaluate polynomials. Except for sorting (which requires  $O(log^2N)$  time), these operations require no more than logarithmic time and constant space per processor. This is *exponentially* faster than the running times of the corresponding sequential algorithms and the corresponding parallel algorithms on networks such as the 2-dimensional mesh. As, in addition, the processors required for these operations are quite simple, the shuffle-exchange network is very well suited for VLSI implementation on a chip.

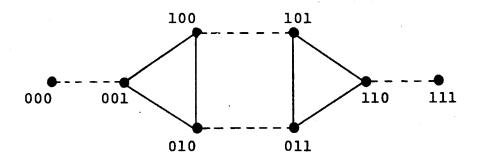

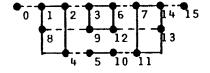

The shuffle-exchange graph comes in various sizes. In particular, there is an N-node shuffle-exchange graph for every N which is a power of two. Each node of the  $(N=2^k)$ -node shuffle-exchange graph is associated with a unique k-bit binary string  $a_{k-1}\cdots a_0$ . Two nodes w and w' are linked via a shuffle edge if w' is a left or right cyclic shift of w (i.e., if  $w=a_{k-1}\cdots a_0$  and  $w'=a_{k-2}\cdots a_0a_{k-1}$  or  $w'=a_0\cdots a_{k-1}a_1$ , respectively). Two nodes w and w' are linked via an exchange edge if w and w' differ only in the last bit (i.e., if  $w=a_{k-1}\cdots a_10$  and  $w'=a_{k-1}\cdots a_11$  or vice-versa). As an example, we have drawn the k-node shuffle-exchange graph in Figure 2. Note that the shuffle edges are drawn with solid lines while the exchange edges are drawn with dashed lines. We shall follow this convention throughout the thesis.

Figure 2: The 8-node shuffle-exchange graph.

The third question of interest to VLSI researchers ("What is the best method of laying out a network on a chip?") has proved to be, by far, the most difficult. It is also the subject of this thesis. In order to answer the question for a particular network, we must do the following three things:

- 1) decide what it means for a layout to be "good,"

- 2) find a "good" layout for the network, and

- 3) prove that the layout is as "good" as possible.

Most people agree that a "good" layout is one which does not require much area. This is quite reasonable since small layouts are easier to wire on a chip, cost less and have far higher yields than layouts with larger amounts of area. Recently, there has also been interest in designing layouts with short wires. Although wire length considerations are not as important as area considerations, it is possible that layouts with long wires may be less efficient and run slower (due to longer transmission times) than layouts with shorter wires. Both quantities are easily expressed in terms of the Thompson model, which is nice from a mathematical point of view. For example, the *layout area* of a network is the minimum amount of area required to lay out the network in the Thompson model. (The *area of a layout* in the Thompson model is defined to be the product of the number of vertical tracks and the number of horizontal tracks which contain a processor or wire segment of the layout.) Similarly, the *maximum edge length* of a network is the minimum amount of wire which is needed to embed the longest *edge* in any Thompson model layout of the network.

Good layouts are known for several communications networks; including the complete binary tree [MR79,PRS81,BL81], the 2-dimensional mesh and the cube-connected-cycles graph [PV79]. The known layouts for the shuffle-exchange graph, however, are not very good. Thompson [T80] was the first to find a nontrivial layout for the shuffle-exchange graph. In particular, he found an  $O(N^2/log^{1/2}N)$ -area layout of the N-node shuffle-exchange graph. He also showed that any layout for the N-node shuffle-exchange graph must have at least  $\Omega(N^2/log^2N)$  area. Hoey and Leiserson [HL80] improved the upper bound by finding an  $O(N^2/logN)$ -area layout for the N-node shuffle-exchange graph. Neither Thompson's nor Hoey and Leiserson's layouts are practical, however, and neither meets Thompson's asymptotic lower bound.

In Part I of the thesis, we find good layouts for the shuffle-exchange graph. In particular, we describe an asymptotically optimal  $O(N^2/log^2N)$ -area layout for the N-node shuffle-exchange graph. Although the layout is not optimal for small values of N, we show how it can be modified in order to produce good layouts for small shuffle-exchange graphs. As these layouts *are* practical, it should now be possible to build a shuffle-exchange chip.

Finally, we are left with the task of proving that a layout which appears to be good is, in fact, optimal. Although Thompson [T79,T80], Vuillemin [V80] and Lipton and Sedgewick [LS81] have all shown how to prove area lower bounds for certain computationally useful networks (such as the shuffle-exchange graph), it is not known how to prove such lower bounds in general. For example, no nontrivial lower bounds have been found for the class of graphs which have  $O(N^{1/2})$ -separators. (This class includes the very important class of planar graphs.) Nor have any methods been discovered for proving nontrivial lower bounds on the maximum edge length of a network.

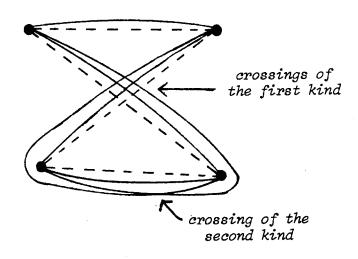

In Part II of the thesis, we describe several techniques for proving good layout area and maximum edge length lower bounds. In particular, we concentrate on finding good lower bounds for the crossing number, wire area and maximum edge crossing of a network. The crossing number of a graph is the minimum number of pairs of edges which must cross in any drawing of the graph in the plane. The maximum edge crossing of a graph is the largest number of edges which must be crossed by some edge in any drawing of the graph. The wire area of a network is simply the minimum amount of wire which must be used to embed the network in the Thompson model. It is clear that for any network,

crossing number ≤ wire area ≤ layout area

and also that

$maximum\ edge\ crossing\ \leq\ maximum\ edge\ length\ .$

In addition, the crossing number, wire area and maximum edge crossing are worth minimizing independent of layout area and maximum edge length considerations. This is due to the fact that

1) chips with a large number of wire crossings (and, in particular, those with wires which cross many other wires) have substantially more problems with

- capacitive coupling (i.e., interference between overlapping wires) than do chips with fewer crossings, and

- 2) chips with high wire area cost more and experience lower yields than do chips with lesser wire area.

Unfortunately, the results of Part II indicate that the crossing number and wire area are usually as large (up to a constant factor) as the layout area. In addition, the maximum edge crossing is often nearly as large as the side length of the chip. More importantly, however, crossing number and wire area arguments can be used to prove better lower bounds on the layout area and maximum edge length than were possible with existing techniques. In particular, we will use such arguments to find

- 1) an N-node planar graph which has layout area  $\Theta(NlogN)$  and maximum edge length  $\Theta(N^{1/2}/log^{1/2}N)$ ,

- 2) an N-node graph with an  $O(N^{1/2})$ -separator which has layout area  $\Theta(N\log^2 N)$  and maximum edge length  $\Theta(N^{1/2}\log N/\log\log N)$ , and

- 3) an N-node graph with an  $O(N^{\alpha})$ -separator (for  $\alpha > 1/2$ ) which has maximum edge length  $\Theta(N^{\alpha})$ .

The area results indicate that not all graphs with  $O(N^{1/2})$ -separators (and, in particular, not all planar graphs) can be laid out in linear area, thus disproving a popular conjecture. The edge length bounds indicate that layouts of certain networks must have some very long wires (possibly even as long as the side length of the layout). Taken together, these results answer all of the previously open questions concerning layout area and maximum edge length of VLSI networks with known separators.

This empty page was substituted for a blank page in the original document.

# PART I

LAYOUTS FOR THE SHUFFLE-EXCHANGE GRAPH

#### CHAPTER 1

#### REVIEW OF KNOWN LAYOUTS

In this chapter, we review the known layouts of the shuffle-exchange graph. In section 1.1, we describe Thompson's [T80] straightforward  $O(N^2/log^{1/2}N)$ -area layout. This is followed in section 1.2 by a detailed description of Hoey and Leiserson's complex plane diagram. The complex plane diagram is very helpful in finding good layouts for the shuffle-exchange graph. For example, Hoey and Leiserson [HL80] have used the diagram to find an  $O(N^2/logN)$ -area layout for the N-node shuffle-exchange graph. In Chapter 2, we will use the diagram to find a variety of layouts for the N-node shuffle-exchange graph including one which requires only  $O(N^2/log^{3/2}N)$  area. (Such a layout has also recently been found independently by Steinberg and Rodeh [SR80b].) The complex plane diagram will also be used in Chapter 4 as an aide in the construction of good practical layouts for small shuffle-exchange graphs.

# 1.1 Thompson's Layout

Thompson was the first to investigate VLSI layouts for the shuffle-exchange graph. In his thesis [T80], he showed that any layout for the N-node shuffle-exchange graph requires at least  $\Omega(N^2/\log^2 N)$  area. (We reprove this fact using crossing number arguments in Part II of the thesis.) In addition, he described a layout requiring only  $O(N^2/\log^{1/2} N)$  area. In what follows, we present Thompson's layout and give a simple proof that it does, in fact, require just  $O(N^2/\log^{1/2} N)$  area.

Given any k-bit string w, define the size of w to be the number of 1-bits it contains. For example, the size of 10110 is 3. Thompson's idea was to lay out the  $N=2^k$  nodes of the shuffle-exchange graph on a straight line in order of nondecreasing size. It is easily seen that shuffle edges link nodes which have the same size and that exchange edges link nodes which have sizes differing by one. Thus the edges of such a layout are relatively short. In particular, the number of horizontal tracks needed to embed all of the edges is at most  $O(\max_{l \le 5 \le k} B_s)$  where

$B_s$  is the number of nodes of size s. This is due to the fact that at most  $O(B_{s-1} + B_s + B_{s+1})$  edges can cross any vertical cut of the layout which is located between a pair of nodes of size s.

It is easy to show that  $B_s = C(k,s)$  for each s where

$$C(k,s) = k!/[s!(k-s)!]$$

is the well-known function for binomial coefficients. It is also well-known that C(k,s) achieves its maximum value at s=k/2 for any k. Using standard asymptotic analysis, it is easily shown that  $C(k,k/2) \sim \Theta(2^k/k^{1/2})$  for large k. (For a good review of such techniques, see Bender and Orszag's book [BO78].) Thus Thompson's layout requires only  $O(N/\log^{1/2}N)$  horizontal tracks. Since at most 3 vertical tracks are needed to embed the vertical portions of the edges incident to any given node, we can conclude that Thompson's layout has area  $\Theta(N^2/\log^{1/2}N)$ .

#### 1.2 Hoey and Leiserson's Complex Plane Diagram

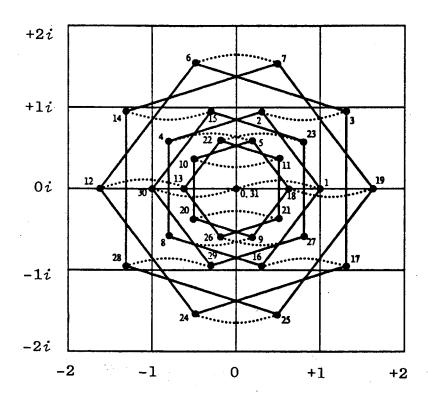

In [HL80], Hoey and Leiserson observed that there is a very natural embedding of the shuffle-exchange graph in the complex plane. In what follows, we describe this embedding (henceforth referred to as the *complex plane diagram*) and point out some of its more important properties. In addition, we give a brief description of the method used by Hoey and Leiserson to transform the diagram into an  $O(N^2/logN)$ -area layout for the N-node shuffle-exchange graph.

#### 1.2.1 Definition

Let  $\delta_k = e^{2\pi i v^k}$  denote the *kth* primitive root of unity. Given any *k*-bit binary string  $w = a_{k-1} \cdot \cdot \cdot a_0$ , let p(w) be the map which sends w to the point

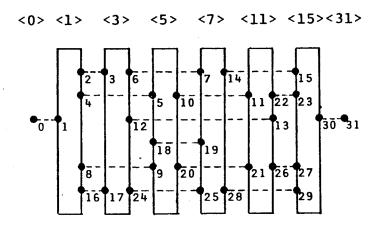

$$p(w) = a_{k-1}\delta_k^{k-1} + \cdots + a_1\delta_k + a_0$$

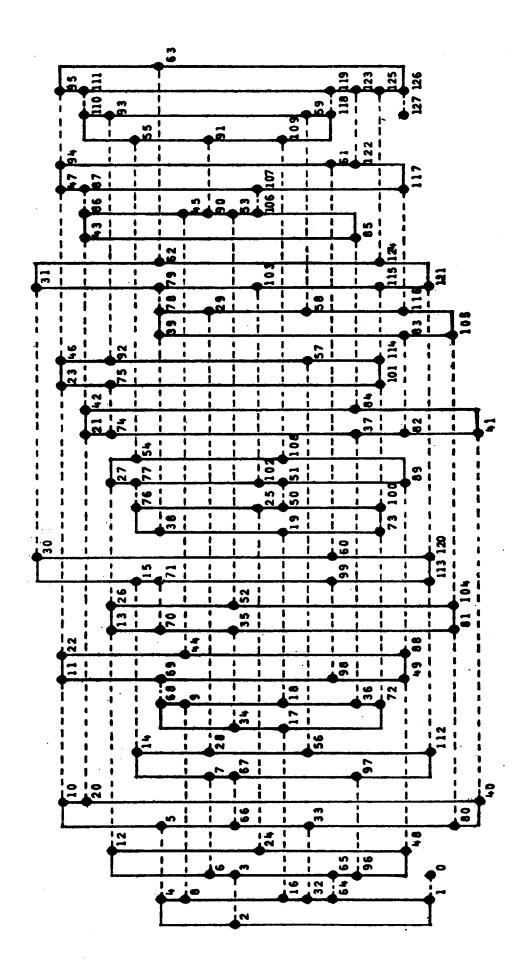

in the complex plane. As each node of the  $(N=2^k)$ -node shuffle-exchange graph corresponds to a k-bit binary string, it is possible to use the map to embed the shuffle-exchange graph in the complex plane. For example, we have done this for the 32-node shuffle-exchange graph (whence k=5) in Figure 1-1. As is usual, we have drawn the shuffle edges with solid lines and the exchange edges with dashed lines. For simplicity, each node is labeled with its value instead of its 5-bit binary string. (By the value of a node, we mean the numerical value of the associated k-bit binary string.)

Figure 1-1: The complex plane diagram for the 32-node shuffle-exchange graph. (Taken from [HL80].)

#### 1.2.2 Properties

Examination of Figure 1-1 indicates that the complex plane diagram has some very interesting properties. First, it is apparent that the shuffle edges occur in cycles (which we call *necklaces*) which are symmetrically placed about the origin. This phenomenon is easily explained by the following identity:

$$\delta_{k} p(a_{k-1} \cdots a_{0}) = a_{k-1} \delta_{k}^{k} + a_{k-2} \delta_{k}^{k-1} + \cdots + a_{1} \delta_{k}^{2} + a_{0} \delta_{k}$$

$$= a_{k-2} \delta_{k}^{k-1} + \cdots + a_{0} \delta_{k} + a_{k-1}$$

$$= p(a_{k-2} \cdots a_{0} a_{k-1}).$$

Thus traversal of a shuffle edge corresponds to a  $2\pi/k$  rotation in the complex plane.

Except for degenerate cases, the preceding identity also indicates that each necklace is composed of k nodes, each a cyclic shift of the other. Such necklaces are called *full necklaces*. Degenerate necklaces contain fewer than k nodes and, because they must have some symmetry, are mapped entirely to the origin of the

complex plane diagram. For example,  $\{00000\}$  and  $\{0101, 1010\}$  are degenerate necklaces while both  $\{101, 011, 110\}$  and  $\{11100, 11001, 10011, 00111, 01110\}$  are full.

It will often be convenient to refer to a necklace by one of its nodes. In particular, we will use the notation  $\langle w \rangle$  to indicate the *necklace generated by w*. This is simply the collection of cyclic shifts if w. For example, the necklace generated by 101 is  $\langle 101 \rangle = \{101, 011, 110\}$ .

Exchange edges are also embedded in a very regular fashion by the complex plane diagram. In fact, each exchange edge is embedded as a horizontal line segment of unit length. This phenomenon is explained by the identity

$$p(a_{k-1}...a_10) + 1 = a_{k-1}\delta_k^{k-1} + ... + a_1\delta_k + 1$$

$$= p(a_{k-1}...a_11).$$

In some cases, several exchange edges are contained in the same horizontal line of the diagram. Such lines are called *levels*. For example, there are 9 levels in the diagram of the 32-node shuffle-exchange graph shown in Figure 1-1. We will use the properties of levels in Chapter 2 to find an  $O(N^2/log^{3/2}N)$ -area layout for the N-node shuffle-exchange graph. They will also be used in Chapter 4 to find good practical layouts for small shuffle-exchange graphs.

# 1.2.3 An $O(N^2/logN)$ -Area Layout

In [HL80], Hoey and Leiserson showed how to use the complex plane diagram to construct an  $O(N^2/logN)$ -area layout for the N-node shuffle-exchange graph. Their method was very involved, however, and we have chosen not to include it here. The basic idea is to use the structural properties of the complex plane diagram to find an  $O(N/log^{1/2}N)$ -separator for the N-node shuffle-exchange graph whenever N is of the form  $2^{2^r}$  for some  $r \ge 0$ . The separator can then used to construct an  $O(N^2/logN)$ -area layout by using Leiserson's general layout technique for graphs with known separators [L80a].

Shortly after writing [HL80], Hoey and Leiserson found a far simpler  $O(N^2/logN)$ -area layout for the N-node shuffle exchange graph which was, in addition, valid for all N. By the that time, however, we (as well as several others) had also observed that the complex plane diagram could be used to find a simple layout for the shuffle-exchange graph. This layout is described in Chapter 2.

#### CHAPTER 2

#### LAYOUTS BASED ON THE COMPLEX PLANE DIAGRAM

In this chapter, we present several layouts of the shuffle-exchange graph which are based on Hoey and Leiserson's complex plane diagram. We commence in section 2.1 with a straightforward  $O(N^2/logN)$ -area layout of the N-node shuffle-exchange graph. As we mentioned in Chapter 1, this layout has also been discovered by many others (including Hoey and Leiserson). In section 2.2, we show how the layout can be modified so as to require only  $O(N^2/log^{3/2}N)$  area. The latter layout was also discovered independently by Steinberg and Rodeh [SR80b]. We conclude the chapter by mentioning an additional  $O(N^2/log^{3/2}N)$ -area layout as well as a layout which might require even less area.

# 2.1 A Straightforward O(N<sup>2</sup>/logN)-Area Layout

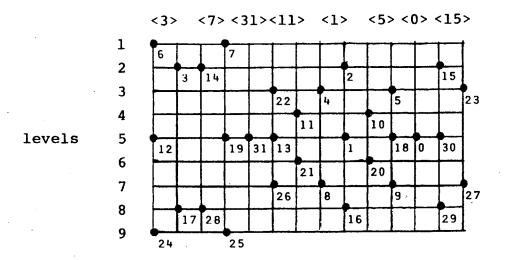

In this section, we describe a straightforward layout of the shuffle-exchange graph which requires only  $O(N^2/logN)$  area. The layout is formed from a grid of levels and necklaces which we refer to as the *level-necklace grid*. Each row of the grid corresponds to a level of the complex plane diagram. The columns are divided into consecutive column pairs, each pair corresponding to a necklace. In particular, the leftmost column of each column pair corresponds to that part of the necklace which is contained in the left half of the complex plane. Similarly, the rightmost column corresponds to the part of the necklace contained in the right half of the complex plane. We assume that the rows are ordered from top to bottom so as to be consistent with the natural ordering of the levels in the complex plane but (for the time being) place no restrictions on the left-to-right order of the necklaces.

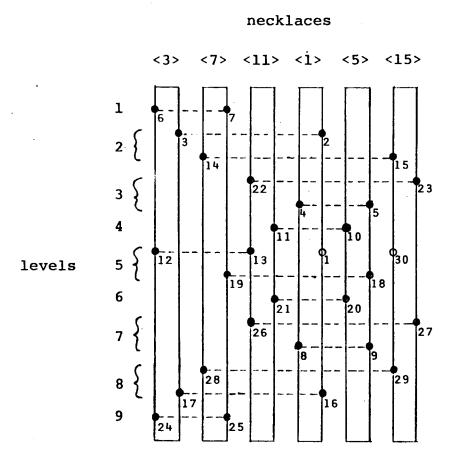

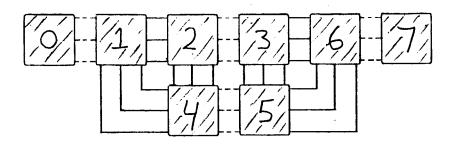

Each node of the shuffle-exchange graph is placed at the intersection of the row and column of the grid which correspond to the level and part of the necklace (left half or right half) to which it belongs in the complex plane diagram. For example, we have done this for a random ordering of the necklaces of the 32-node shuffle-exchange graph in Figure 2-1.

#### necklaces

Figure 2-1: A level-necklace grid for the 32-node shuffle-exchange graph.

Notice that we used just one vertical track to embed the necklaces  $\langle 0 \rangle$  and  $\langle 31 \rangle$  in the grid. As each necklace contains just one node, it is clear that this is sufficient. In general, necklaces which are mapped to the origin by the complex plane diagram are a nuisance since they become lumped together in a single point of the level-necklace grid. Fortunately, there are relatively few such nodes. In particular, Hoey and Leiserson showed the following.

Lemma 2-1 (Hoey and Leiserson [HL80]): At most O(N/logN) nodes of the N-node shuffle-exchange graph are mapped to the origin of the complex plane diagram.

**Proof:** Every node which is mapped to the origin of the complex plane diagram is adjacent (via an exchange edge) to a node at position (1,0) or (-1,0). Any node which is not mapped to the origin is contained in some full necklace, at most two nodes of which are contained in positions (1,0) or (-1,0). Thus for every pair of nodes which are mapped to the origin, there are at least k = logN nodes which are not mapped to the origin. Thus at most O(N/k) = O(N/logN) nodes can be mapped to the origin  $\square$

Since at most O(N/logN) nodes are mapped to the origin, we can (for the time being) ignore them. They can always be inserted later at a cost of at most O(N/logN) additional vertical and horizontal tracks. Since any layout of the shuffle-exchange graph which we will consider will have at least  $\Omega(N/logN)$  vertical

and horizontal tracks, the added tracks can increase the area of the final layout by at most a constant factor. We will also use this strategy in Chapter 3 when we ignore several O(N/logN)-sized sets of nodes.

Since each full necklace contains at most k = logN nodes, it is easy to see that the N-node shuffle-exchange graph has at most O(N/logN) full necklaces. Thus at most O(N/logN) vertical tracks are needed to embed all of the shuffle edges in the level-necklace grid. It is also easy to show that at most N horizontal tracks are needed to embed all of the exchange edges (one track is used for each exchange edge). Thus the total area of the layout for the N-node shuffle-exchange graph is  $O(N^2/logN)$ . As an example, we have added the edges of the 32-node shuffle-exchange graph to the level-necklace grid in Figure 2-1 to produce the layout shown in Figure 2-2. Note that we have omitted  $\langle 0 \rangle$  and  $\langle 31 \rangle$  in this layout since they are mapped to the origin of the complex plane diagram.

Figure 2-2: Layout produced from the level-necklace grid shown in Figure 2-1.

# 2.2 An Improved $O(N^2/log^{3/2}N)$ -Area Layout

It is possible to improve the layout described in section 2.1 by reducing the number of horizontal tracks needed to embed the exchange edges. This can be done in two ways. First, exchange edges which are in the same level of the complex plane diagram but which do not overlap in the level-necklace grid can be inserted on the same horizontal track. As more exchange edges are inserted on the same track, fewer total tracks will be needed to embed all of the exchange edges. Secondly, the necklaces can be re-ordered so as to increase the average number of exchange exchange edges which can be inserted on each horizontal track.

Although we do not know how to best order the necklaces in general, we have found several orderings which yield  $O(N^2/\log^{3/2}N)$ -area layouts for the N-node shuffle-exchange graph. For instance, we will show in what follows that such a layout can be constructed by arranging the necklaces from left to right in order of nondecreasing size. (The size of a necklace is simply defined to be the size of any of its nodes.) This observation has also been made by Steinberg and Rodeh in [SR80b].

In order to bound the number of horizontal tracks needed to insert the exchange edges, we will show that the maximum overlap of exchange edges on each level occurs in between necklaces of size k/2. Since the maximum overlap of exchange edges on each level is an upper bound on the number of horizontal tracks needed to insert the exchange edges on that level, we can thus conclude that the total number of horizontal tracks needed to insert all of the exchange edges is at most

$$O(B_{k/2}) \sim O(N/\log^{1/2}N)$$

.

Thus the resulting layout will have area at most  $O(N^2/\log^{3/2}N)$ .

It is not immediately clear why the maximum overlap on each level occurs between nodes of size k/2, however. In what follows, we break up each level into sublevels (for which the analysis is easier) and show that the maximum overlap on each sublevel occurs between necklaces of size k/2. Before doing this, however, we must introduce some further notation.

Consider a node of the form  $a_{k-1} \cdots a_1 0$  for which either  $a_{k-i} = 0$  or  $a_i = 0$  or both for each  $i \le k$ . We will refer to such a node as basis node. A node  $b_{k-1} \cdots b_0$  is said to be generated by the basis node  $a_{k-1} \cdots a_0$  if

- 1)  $b_{k-i} = a_{k-i}$  and  $b_i = a_i$  whenever  $a_{k-i} = a_i$  for  $1 \le i \le k$ , and

- 2)  $b_{k-i} = b_i$  whenever  $a_{k-i} = a_i = 0$  for  $1 \le i \le k$ .

For example, 10000 generates 10001, 11100 and 11101 but not 11111.

It is not difficult to show that if u generates v, then both u and v are on the same level of the complex plane diagram. For example, let  $u = a_{k-1} \cdots a_0$  and  $v = b_{k-1} \cdots b_0$  and observe that

$$p(v) - p(u) = (b_{k-1} - a_{k-1}) \delta_k^{k-1} + \dots + (b_1 - a_1) \delta_k + (b_0 - a_0)$$

$$= c_{k-1} \delta_k^{k-1} + \dots + c_1 \delta_k + c_0$$

where  $c_{k-i} = c_i$  for each i,  $1 \le i \le k$ . Since  $\delta_k^{k-i}$  is the complex conjugate of  $\delta_k^i$  for  $1 \le i \le k$ , we can conclude that p(v) - p(u) is a real number and thus that u and v are in the same level of the complex plane diagram.

It is also easy to show that each node of the shuffle-exchange graph is generated by a unique basis node. In particular, the node which generates  $b_{k-1} \cdots b_0$  can be found by

- 1) setting  $b_0 = 0$  and (if k is even) setting  $b_{k/2} = 0$ , and

- 2) setting  $b_i = b_{k-i} = 0$  for each i such that (originally)  $b_i = b_{k-i} = 1$ .

Since exchange edges link nodes which are in the same sublevel, we can conclude from the preceding arguments that it is possible to partition each level of the complex plane diagram into sublevels so that the nodes in each sublevel are precisely the nodes generated by some basis node. We will now show that the maximum overlap at each sublevel occurs between necklaces of size k/2.

Since the necklaces have been arranged from left to right in order of nondecreasing size, we can use arguments similar to those of section 1.1 to conclude that the overlap of exchange edges between two nodes of size s in any sublevel is at most  $O(\max_{1 \le s \le k} B_s')$  where  $B_s'$  is the number of nodes in that sublevel with size s. A straightforward counting argument shows that each basis node of size r generates

- 1) C(k/2 r, i) nodes of size s=r+2i for any  $i \le k/2 r$ , and

- 2) C(k/2 r, i) nodes of size s = r + 2i + 1 for any  $i \le k/2 r$

when k is odd, and

- 1) C(k/2 r 1, i) + C(k/2 r 1, i 1) = C(k/2 r, i) nodes of size s = r + 2i for any  $i \le k/2 r$ , and

- 2) 2C(k/2 r 1, i) nodes of size s = r + 2i + 1 for any  $i \le k/2 r 1$  when k is even. We can therefore conclude that in *all cases*, the maximum value of  $B_s$ ' occurs when i = (k 2r)/4 and thus when s = k/2. This concludes the proof.

As an example, we have drawn such a layout for the 32-node shuffle-exchange graph in Figure 2-3. Note that far fewer horizontal tracks are needed for this layout than are used for the layout in Figure 2-2. For completeness, we have included the necklaces  $\langle 0 \rangle$  and  $\langle 31 \rangle$  even though they are degenerate.

Figure 2-3: An improved layout for the 32-node shuffle-exchange graph.

#### 2.3 Other Layouts

It is not difficult to find other orderings of the necklaces which produce  $O(N^2/log^{3/2}N)$ -area layouts for the N-node shuffle-exchange graph. For example, Lepley [LLM81] used standard statistical methods to show that the arrangement of necklaces from left to right in order of nondecreasing radius produces such a layout. (By the radius of a necklace, we mean the radius of the circle in the complex plane which contains the necklace.) The proof is similar to the one in section 2.2. In particular, it is shown that the maximum overlap in most levels occurs in the same place and that the total overlap of all of the levels at that point is  $\Theta(N/log^{1/2}N)$ .

Although we consider it likely that better orderings of the necklaces exist, we do not know of any ordering which (provably) results in a layout with less than  $o(N^2/log^{3/2}N)$  area. There is another ordering of interest, however. That is the ordering of the necklaces according to the minimal number represented by each necklace. (The minimum number represented by a necklace is simply the smallest value of any node in the necklace.) Coincidentally, the layout displayed in Figure 2-3 has such an ordering. Using techniques which are developed in Chapter 3, it is possible to show that the combined maximum overlap of exchange edges in all levels is at most O(NloglogN/logN) for this ordering. This is substantially better than the  $O(N/\log^{1/2}N)$  overlap found in previous orderings and also very close to the lower bound of  $\Omega(N/\log N)$ . Unfortunately, we do not know how to show that the maximum overlap at each level occurs in the same place. In fact, it appears that this may not be the case. (We are deeply indebted to Kleitman for pointing out the possibility of such an improvement. Although we were not able use his idea in the context of complex plane diagram layouts, it was crucial to the development of the asymptotically optimal layout described in Chapter 3.)

For orderings which have a small combined maximal overlap but for which the maximal overlap at each level is difficult to compute (such as the ordering by minimal value represented), it may be possible to improve the situation by altering the level structure. As Miller pointed out to us, there are many possible levelings of the exchange edges. (By a *leveling*, we mean any arrangement of the exchange edges in levels which is consistent with the necklace structure of the complex plane diagram.) Although we have investigated several levelings, we have not found any (provably) better layouts for the shuffle-exchange graph by this method.

#### CHAPTER 3

# MORE SOPHISTICATED LAYOUTS

In section 3.3 of this chapter, we describe an asymptotically optimal  $O(N^2/log^2N)$ -area layout for the N-node shuffle-exchange graph. Unlike the previously described layouts, the optimal layout is fairly sophisticated and requires a substantial amount of preliminary machinery. Most of the necessary definitions and lemmas are included in section 3.1. In section 3.2, we describe and analyze a near-optimal preliminary version of the optimal layout. The optimal layout is then described in section 3.3. In section 3.4, we extend the methods developed in earlier sections in order to show that certain useful supergraphs of the N-node shuffle-exchange graph can also be laid out in  $O(N^2/log^2N)$  area. We have also included an appendix to the chapter in which we prove Lemmas 3-1 through 3-4.

#### 3.1 Preliminaries

The layouts described in this chapter are based on some important combinatorial properties of strings which contain long blocks of consecutive zeros. Before describing the layouts, however, it is useful to review some of these properties. In this section, we mention several combinatorial lemmas and definitions which will be heavily used in the analysis which follows later. As the proofs of the lemmas are somewhat complicated, they have been included in the appendix.

In what follows, we will be particularly interested in the size and location of the longest block of consecutive  $\theta$ -bits in the k-bit binary string associated with each node. In order that the size of this block be the same for all nodes within a necklace, we allow blocks to begin at the end and end at the beginning of a string. For example, the longest block of zeros in the string 01010 starts at the fifth bit and has length two.

Let  $\Psi_k(t)$  denote the number of k-bit strings for which the longest block of consecutive zeros has length t. For example,  $\Psi_3(2)=3$ . The following combinatorial lemma provides a good asymptotic bound on the growth of  $\Psi_k(t)$ .

Lemma 3-1: For

$$(\log k)/2 + \log \ln k \le t << k$$

and  $k \to \infty$ ,  $\Psi_k(t) \sim 2^k (e^{-k2^{-(t+2)}} - e^{-k2^{-(t+1)}})$ .

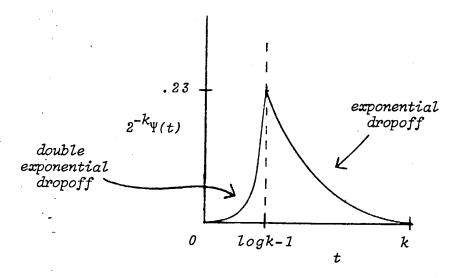

In order to illustrate the important features of the function in Lemma 3-1, we have sketched a graph of  $2^{-k}\Psi_k(t)$  versus t in Figure 3-1. The maximum of  $2^{-k}\Psi_k(t)$  occurs at t = logk-1 whence

$$2^{k}\Psi_{k}(t) = (e^{1/2} - 1)/e$$

$$\approx .23865.$$

For t > logk - 1,  $2^{-k}\Psi_k(t)$  decreases exponentially as t increases. For  $t \leq logk - 1$ ,  $2^{-k}\Psi_k(t)$  decreases doubly exponentially as t decreases.

Figure 3-1: Density of k-bit binary strings for which the longest block of consecutive zeros has length t.

Roughly speaking, Lemma 3-1 states that the longest block of consecutive zeros in nearly 1/4 of all k-bit strings has length precisely logk - 1. Further, there are not many strings of length k with substantially more than logk consecutive zeros and even fewer strings for which the longest block of consecutive zeros has length substantially less than logk. This information is further quantified in the following lemma.

Lemma 3-2: The number of k-bit strings for which the longest block of consecutive zeros has length less than logk - loglnk - 1 or length greater than 2logk

is at most  $O(2^k/k) = O(N/\log N)$ .

As we mentioned in Chapter 2, we may ignore O(N/logN)-sized sets of nodes which have undesirable properties. As such nodes can be inserted with the addition of at most O(N/logN) vertical and horizontal tracks, we can always add them later without increasing the total area by more than a constant factor. By Lemma 3-2, we can thus henceforth consider only those nodes for which the longest block of zeros has length between logk - loglnk - 1 and 2logk.

We will also be interested in the size of the second longest block of consecutive zeros in each string. Usually, the size of the second longest block of zeros will be very close to the size of the longest block of zeros. We state this observation more precisely in the following lemma.

Lemma 3-3: The sum over all necklaces of the difference in length between the longest and second longest blocks of consecutive zeros is at most  $O(N/\log N)$ .

Using information about the size and location of blocks of zeros within the necklace, it is possible to distinguish one particular node in the necklace. More precisely, we define the *distinguished node of a necklace* to be the node containing the longest leading block of zeros. For example, 00101 is the distinguished node of <01010>. Should two or more nodes of a necklace begin with equal and maximal length blocks of zeros, then each node of the necklace contains at least two blocks of zeros of maximal length. In such cases, we distinguish that node for which the leading block of zeros is maximal and for which the second occurence of a maximal length block of zeros is as near as possible to the beginning of the string. For example, 01011 (not 01101) is the distinguished node of the necklace <10101>. For some necklaces, such as <111> and <1010101>, there is no uniquely distinguished node. As we show in the following lemma, such necklaces are sufficiently rare that we need not consider them further.

Lemma 3-4: At most O(N/logN) nodes are contained in necklaces which fail to have a uniquely distinguished node.

We refer to the leading block of zeros of a distinguished node as the *primary* block of zeros. If a distinguished node has two or more maximal length blocks of zeros, then the maximal length block following the primary block is referred to as the secondary block of zeros. These definitions can be easily extended to any node contained in a necklace which has a uniquely distinguished node. For example,

the primary block of zeros of 01010 starts in the fifth bit and has length two. Note that this string does not have a secondary block of zeros. As another example, we note that the secondary block of zeros in the string 11010 consists solely of the fifth bit. Note that the secondary block of zeros (if it exists) always has the same length as the primary block of zeros.

If the last bit of a node occurs in the primary block of zeros, we call that node a primary node. Similarly, if the last bit of a node occurs in the secondary block of zeros, we call the node a secondary node. For example, 10110 is a primary node, 11010 is a secondary node and 10010 is neither primary nor secondary.

Note that all primary and secondary nodes are necessarily even. (We say that a node is *even* if its last bit is 0 and *odd* if its last bit is 1.) Note also that, by Lemma 3-2, we need only consider necklaces which contain between *logk* - *loglnk* - 1 and *2logk* primary nodes. Such necklaces will also have at most *2logk* secondary nodes.

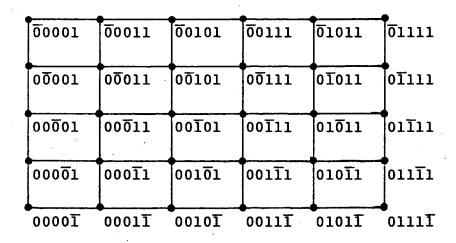

In what follows, we will represent nodes in terms of their corresponding distinguished nodes. More precisely, we use the notation  $a_{k-1} \cdots a_{i+1} \overline{a_i} a_{i-1} \cdots a_0$  to denote the node  $a_{i-1} \cdots a_0 a_{k-1} \cdots a_i$ . For example,  $001\overline{0}1$  denotes the node 10010. Using this notation, a primary node has the form  $0 \cdots \overline{0} \cdots 0 w$  while a secondary node has the form  $0 \cdots 0 w' 0 \cdots \overline{0} \cdots 0 w''$  where  $0 \cdots 0 w$  and  $0 \cdots 0 w' 0 \cdots 0 w''$  are assumed to be distinguished nodes.

### 3.2 A Near-Optimal Layout

We are now prepared to describe a near-optimal preliminary version of the optimal layout. In section 3.3, we will show how to modify this layout in order to construct an optimal  $O(N^2/log^2N)$ -area layout for the N-node shuffle-exchange graph.

#### 3.2.1 Location of the Nodes

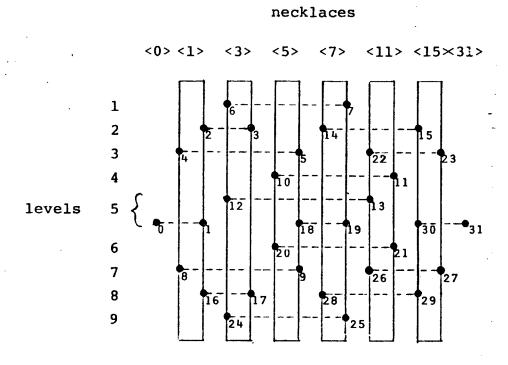

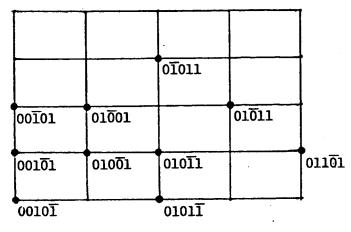

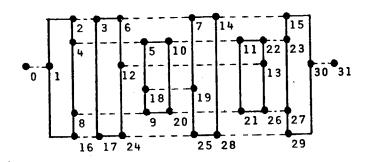

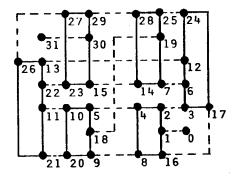

The near-optimal layout is constructed from a  $logN \times O(N/logN)$  grid of nodes. Each column of the grid corresponds to a necklace of the shuffle-exchange graph. The nodes of each necklace are ordered from top to bottom so that the *ith* node is a left cyclic shift of the (i-1)st node for each i and so that the distinguished node is placed in the bottom row. The necklaces are ordered from left to right so that the values of the distinguished nodes form an increasing sequence. For

example, we have constructed such a grid for the 32-node shuffle-exchange graph in Figure 3-2. In the figure, we have represented each node in terms of the associated distinguished node. This representation readily illustrates the fact that the last bit of any node in the *ith* row corresponds to the *ith* bit of the associated distinguished node. Note that the necklaces <00000> and <11111> have not been included since they are degenerate.

Figure 3-2: The grid of nodes for the 32-node shuffle-exchange graph.

#### 3.2.2 Insertion of the Edges

It is easily observed that the shuffle edges can be inserted in the grid with the addition of O(N/logN) vertical and 2 horizontal tracks. In the following, we will show that the exchange edges can be inserted with the addition of O(NloglogN/logN) vertical and horizontal tracks. Thus the total area of the layout is  $O(N^2(loglogN)^2/log^2N)$ . This is only a factor of  $O((loglogN)^2)$  off from the lower bound of  $O(N^2/log^2N)$ .

The analysis is divided into two parts. In part (a), we show that only O(NloglogN/logN) exchange edges link nodes which are in different rows of the grid. Thus such edges can be inserted with the addition of at most O(NloglogN/logN) vertical and horizontal tracks. In part (b), we conclude the analysis by showing that at most O(N/logN) horizontal tracks are needed to insert the exchange edges which link two nodes in the same row.

#### (a) Exchange Edges Which Link Nodes in Different Rows

Consider an exchange edge which links two nodes that are in different rows of the grid. In particular, assume that the edge is incident to an even node in the ith row for some i. By definition, the even node can be represented as  $w\overline{\partial}w'$  where |w|=i-1 and w0w' is the distinguished node of  $\langle w0w' \rangle$ . The exchange edge is also incident to the odd node wIw'. By assumption, wIw' is not located in the *ith* row and thus wlw' is not a distinguished node. Since wow' is a distinguished node, we know that the ith bit of w0w' (the bit that was changed in order to produce wlw') must be in the primary or secondary block of zeros of w0w'. Otherwise, the primary and (if it exists) secondary blocks of zeros of wlw' would be identical in location and size to the primary and secondary blocks of w0w'. This would imply that wIw' is also distinguished, a contradiction. Thus  $w\overline{O}w'$ must be a primary or secondary node. As was previously mentioned, we can assume that each necklace has at most 2logk = 2loglogN primary and 2loglogNsecondary nodes. Thus at most 4loglogN nodes in each necklace are both even and incident to an exchange edge which links nodes in different rows. Since every exchange edge is incident to an even node and since there are O(N/logN)necklaces, we can conclude that there are at most O(NloglogN/logN) exchange edges which link nodes in different rows.

#### (b) Exchange Edges Which Link Nodes in the Same Row

We next show that those exchange edges which link two nodes that are in the same row can be inserted with the addition of at most O(N/logN) horizontal tracks. Once again, the analysis is divided into two parts. In the first part, we show that at most O(N/logN) exchange edges are contained in the first logk rows. Such edges can be trivially inserted with the addition of O(N/logN) horizontal tracks. In the second part, we show that only  $2^{k-i}$  horizontal tracks are needed to insert the exchange edges in the *ith* row for any i > logk. Since  $\sum_{k=1,2,3,1}^{K} 2^{k-i} \le 2^k/k = N/logN$ , this will be sufficient to show that at most O(N/logN) additional horizontal tracks are necessary to insert the remaining exchange edges.

Consider a necklace which has t primary nodes for some  $t \le log k$ . By definition, the nodes in the first t rows of such a necklace are all even. Thus, such a necklace can have at most r = log k - t odd nodes in the first log k rows. By Lemma 3-1, we know that there are

$$\Psi_k(t)/k \sim (2^k/k)(e^{-k2^{-t/2}}-e^{-k2^{-t/2}})$$

such necklaces for  $(logk)/2 + loglnk \le t \le k$ . By Lemma 3-2, we can assume that  $t \ge logk - loglnk - 1$  and thus the total number of odd nodes occurring in the first logk rows is at most

$$\sim \sum_{k=1}^{\log k} (\log k - t) (2^{k}/k) (e^{-k2^{-k2}} - e^{-k2^{-k1}})$$

$$= (2^{k}/k) \sum_{r=0}^{\log \ln k + 1} r (e^{-k2^{r-2} - \log k} - e^{-k2^{r-1} - \log k})$$

$$= (2^{k}/k) \sum_{r=0}^{\log \ln k + 1} r (e^{-2^{r-2}} - e^{-2^{r-1}})$$

$$= (2^{k}/k) \sum_{r=0}^{\log \ln k + 1} r (e^{-2^{r-2}} - e^{-2^{r-1}})$$

$$= (2^{k}/k) \sum_{r=0}^{\infty} e^{-2^{r-2}}$$

$$\leq (2^{k}/k) \sum_{r=0}^{\infty} e^{-2^{r-2}}$$

$$= O(N/\log N).$$

Since every exchange edge is incident to an odd node, the above bound implies that at most O(N/logN) exchange edges are contained in the first logk rows.

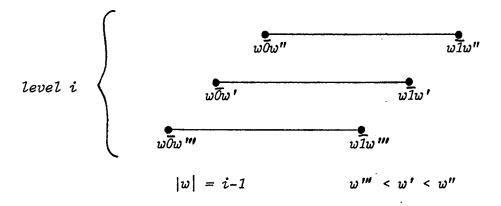

We next consider the number of horizontal tracks necessary to insert the exhange edges contained in the *ith* row for *i>logk*. This number is identical to the maximum number of exchange edges that can overlap each other at a single point of the *ith* row. In Figure 3-3, we illustrate the necessary conditions for two exchange edges to overlap in the *ith* row. All representations are in terms of distinguished nodes.

Figure 3-3: Necessary conditions for exchange edges to overlap in the ith row.

Note that the even end of an exchange edge is always to the left of the odd end. Also note that any node which occurs between  $w\overline{0}w'$  and  $w\overline{I}w'$  must be represented as  $w\overline{0}w''$  where w''>w' or as  $w\overline{I}w'''$  where  $w'''\leq w'$ . In either case, the exchange edge incident to the overlapped node extends beyond the exchange edge linking  $w\overline{0}w'$  to  $w\overline{I}w'$ . Since there are at most  $2^{k-i}-1$  nodes between  $w\overline{0}w'$  and  $w\overline{I}w'$ , these facts imply that at most  $2^{k-i}$  exchange edges can overlap at any point of the *ith* row. This observation completes the argument that the near optimal layout requires only  $O(N^2(loglogN)^2/log^2N)$  area.

# 3.3 An Optimal $O(N^2/log^2N)$ -Area Layout

In this section, we will modify the layout described in section 3.2 in order to produce an optimal  $O(N^2/log^2N)$ -area layout for the N-node shuffle-exchange graph. In particular, we will relocate the primary and secondary nodes of each necklace so that they are closer to and in the same row as the nodes to which they are linked via an exchange edge. Before going into the details of this relocation, however, it is necessary to introduce some additional terminology.

#### 3.3.1 More Definitions

In order to construct an optimal layout for the shuffle-exchange graph, we have found it necessary to break up each necklace into two or, possibly, three pieces. The *basic piece* of each necklace consists of all those nodes which are neither primary nor secondary. The *primary piece* of each necklace consists of the primary nodes while the *secondary piece* consists of the secondary nodes (if there are any). For example, the basic piece of  $\langle 01011 \rangle$  is  $\{01011, 01011, 01011\}$ , the primary piece is  $\{01011\}$ , and the secondary piece is  $\{01011\}$ .

It is also necessary to extend the notion of a distinguished node to include pieces of necklaces. The distinguished node of a basic piece is the same as the distinguished node of the associated necklace. The distinguished node of a primary piece of a necklace is that node of the necklace which becomes distinguished when we ignore the primary block of zeros (i.e., when we temporarily replace the primary block of zeros in each node of the necklace with an equal-length block of ones). Similarly, the distinguished node of a secondary piece of a necklace is that node which becomes distinguished when we ignore the secondary block of zeros. For example, 010110111 is the distinguished node of the basic piece of <010110111>, 011011101 is the distinguished node of the primary piece, and

011101011 is the distinguished node of the secondary piece. Note that the distinguished nodes of the primary and secondary pieces of any necklaces are necessarily odd nodes and thus are contained in the basic piece of the necklace.

It is important to note that some necklaces (such as  $\langle 01111\rangle$ ) have a distinguished node but do not have a distinguished node for the primary or secondary piece of the necklace. Fortunately, arguments such as those used to prove Lemmas 3-3 and 3-4 can be used to show that at most O(N/logN) nodes are contained in such necklaces. Thus, we can assume henceforth that every piece of every necklace has an associated distinguished node.

#### 3.3.2 Location of the Nodes

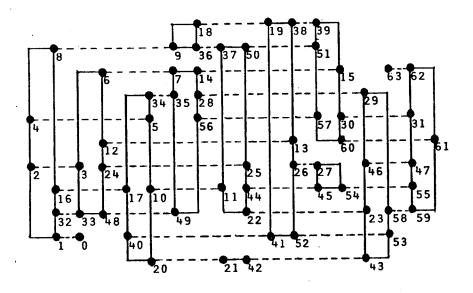

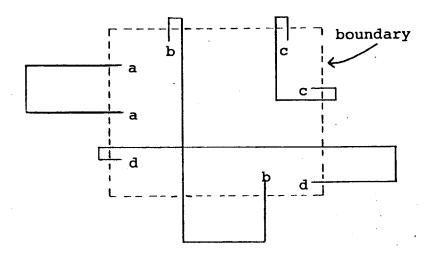

As in section 3.2, the layout is constructed from a  $logN \times O(N/logN)$  grid of nodes. Each column of the grid corresponds to a piece of a necklace. The nodes of each piece are arranged within a column so that a node of the form  $a_{k-1} \cdots \overline{a_{k-i}} \cdots a_0$  (where  $a_{k-1} \cdots a_0$  is assumed to be the distinguished node of the associated piece) is placed in the *ith* row of the grid. Note that nodes in the basic piece of any necklace (these include all odd nodes) are in the same row as they were in the near-optimal layout described in section 3.2. The columns are ordered from left to right so that the values of the distinguished nodes of the associated pieces form a nondecreasing sequence. For example, we have constructed such a grid for k=5 in Figure 3-4.

basic primary basic secondary primary <00101> <00101> <01011> <01011> <01011>

Figure 3-4: Relocated nodes for the 32-node shuffle-exchange graph.

Note that the necklaces <00001>, <00011>, <00111>, and <01111> have not been included in Figure 3-4 since their associated primary pieces do not have distinguished nodes.

#### 3.3.3 Insertion of the Edges

As each necklace is broken up into at most four *contiguous* pieces in the modified grid (the basic piece may have been broken up into two contiguous pieces), the shuffle edges can be inserted with the addition of at most O(N/logN) vertical and horizontal tracks. In what follows, we will show that at most O(N/logN) vertical and horizontal tracks are needed to insert all of the exchange edges as well. Thus the area of the layout will be  $O(N^2/log^2N)$ , which is optimal.

As before, we divide the analysis of the exchange edges into two parts. We first show that at most O(N/logN) exchange edges link nodes which are in different rows of the grid. Such edges can thus be trivially inserted with the addition of at most O(N/logN) vertical and horizontal tracks. We then show that those exchange edges which link two nodes in the same row can be inserted with the addition of only O(N/logN) horizontal tracks. The arguments will be very similar to those in section 3.2.2.

## (a) Exchange Edges Which Link Nodes in Different Rows

Consider an exchange edge which links two nodes which are in different rows of the grid. Since only primary and secondary nodes have been relocated, we can conclude from the arguments of section 3.2.2a that the even node which is incident to the edge is either a primary or secondary node. In what follows, we will show that the even node is, in fact, a primary node.

Assume for the purposes of contradiction that the even node is a secondary node. Then this node can be represented as  $w \overline{O}w'$  where w Ow' is the distinguished node of the secondary piece of  $\langle w Ow' \rangle$  and |w|=i-1 for some i. By definition,  $w \overline{O}w'$  is located in the *ith* row of the grid and is linked to  $w \overline{I}w'$  via the exchange edge. Since  $w \overline{I}w'$  is odd, it is contained in the basic piece of  $\langle w Iw' \rangle$ . By assumption,  $w \overline{I}w'$  is not also in the *ith* row and thus  $w \overline{I}w'$  cannot be the distinguished node of  $\langle w \overline{I}w' \rangle$ . Since the lengths of the two blocks of zeros in  $w \overline{I}w'$  created by switching the *ith* bit from 0 to 1 are less than the length of the primary block of zeros (in fact, the sum of their lengths is precisely one less than the length of the primary block),  $w \overline{I}w'$  will be the distinguished node of  $\langle w \overline{I}w' \rangle$

precisely when w0w' is the node distinguished in  $\langle w0w' \rangle$  by ignoring the secondary block of zeros. By definition, this is the case precisely when w0w' is the distinguished node of the secondary piece of  $\langle w0w' \rangle$ . By assumption, w0w' is the distinguished node of the secondary piece of  $\langle w0w' \rangle$  and thus we can conclude that w1w' is the distinguished node of  $\langle w1w' \rangle$ , a contradiction.

Next consider a primary node which is incident to an exchange edge linking two nodes in different rows of the grid. By the preceding arguments, this node must be of the form  $w10\cdots000\cdots01w'$  where  $w10\cdots01w'$  is the distinguished node of the primary piece of  $\langle w10\cdots01w' \rangle$  and either  $t_1$  or  $t_2$  is larger than or equal to the length of the longest block of zeros in w11w'. Otherwise,  $w10\cdots010\cdots01w'$  would (by definition) be the distinguished node of  $\langle w10\cdots010\cdots01w' \rangle$  and thus  $w10\cdots010\cdots01w'$  would be on the same row as  $w10\cdots010\cdots01w'$ , a contradiction. Each necklace contains at most 2r such primary nodes where r is the difference between the lengths of the longest and second longest block of zeros in any string of the necklace. By Lemma 2-3, we can conclude that there are at most O(N/logN) such primary nodes in the entire shuffle-exchange graph. Thus, at most O(N/logN) exchange edges link nodes which are in different rows.

# (b) Exchange Edges Which Link Nodes in the Same Row

Using the analysis developed in section 3.2.2b, it is not difficult to show that at most O(N/logN) horizontal tracks are needed to insert the exchange edges which link two nodes that are in the same row. In particular, there are still only O(N/logN) odd nodes in the top logk rows of the grid and thus at most O(N/logN) exchange edges are contained in the top logk rows. These can be trivially inserted with the addition of just O(N/logN) horizontal tracks.

Again following the methods of section 3.2.2b, it is not difficult to show that two exchange edges overlap on the *ith* row only if the first *i* bits of the associated nodes are identical. Thus at most  $2^{k-i}$  tracks are needed to insert all of the exchange edges in the *ith* row for all i > log k. Summing, we can again conclude that at most O(N / log N) additional horizontal tracks are needed to insert the remaining exchange edges.

#### 3.3.4 Comments

The methods developed in this chapter can be used to find several other optimal layouts for the shuffle-exchange graph. The key variant is the method by which a node is distinguished. In particular, this method must be impervious to small alterations in the necklace. (This is so that most exchange edges will link nodes which are in the same row of the grid.) Only by changing the value of a bit in a small segment of the necklace (such as in the primary or secondary block of zeros) should we be able to globally change the distinguished node.

Another method of distinguishing a node is to select that node in the necklace which has the minimal value. Although the proof is very difficult, it can be shown that the layout for the N-node shuffle-exchange graph constructed in this manner has at most  $O(N^2/\log^2 N)$  area. In the following section we will desribe additional methods of distinguishing nodes.

At this point, we should also note that the layout just described is *not known* to have optimal maximum edge length. In Part II of the thesis, we show that every layout of the N-node shuffle-exchange graph must have some edge of length at least  $\Omega(N/\log^2 N)$ . All the layouts we have considered thus far contain wires of length  $\Theta(N/\log N)$ .

# 3.4 Layouts With Additional Edges

For some applications (such as the calculation of the discrete Fourier transform), it is useful to consider networks which have more than just shuffle and exchange edges. In particular, we will be interested in layouts for the shuffle-exchange graph which also include shift, reverse and transpose edges. In what follows, we will show how to modify the optimal layout for the shuffle-exchange graph so that these additional edges can be inserted without increasing the total area by more than a constant factor.

# 3.4.1 Shift Edges

Shift edges link the *ith* node to the (i+1)st node for all odd *i*. When combined with the exchange edges, the resulting network will have links between the *ith* and the (i+1)st nodes for all *i*. The inclusion of such edges facilitates the computation of discrete Fourier transforms at sequential intervals of a continuous signal. In

such applications, the input data contained in the *ith* processor is shifted to the (i+1)st processor for each *i* after each computation of a discrete Fourier transform. The graph consisting of shuffle, exchange and shift edges is known as the *shuffle-shift graph*.

Using the methods developed in section 3.3, it is not difficult to show that the N-node shuffle-exchange graph can be laid out using only  $O(N^2/log^2N)$  area. As before, the necklaces are broken into two or three pieces and placed in a grid according to the value of the associated distinguished node. Thus the shuffle edges can be inserted as before using only O(N/logN) vertical and horizontal tracks.

For most odd nodes, adding a l to the value of the node changes only a relatively small number of bits at the end of the string. Thus it can be shown that at most O(N/logN) shift edges link nodes which are in different rows. These can be easily inserted using only O(N/logN) vertical and horizontal tracks. Of those edges which link nodes in the same row, at most O(N/logN) are contained in the first logk rows. For logk, at most logk shift edges overlap at any point of the logh row. By introducing an extra vertical track for each necklace piece, it is possible to separate the layout of the shift edges on each level from that of the exchange edges. Thus both can be inserted simultaneously in the logh row using only logh total horizontal tracks. By the arguments of section 3.3, this means that at most logh additional horizontal tracks are needed to embed all of the remaining shift and exchange edges, thus completing the argument.

## 3.4.2 Reverse Edges

Reverse edges link pairs of nodes that are associated with binary strings which are reverses of each other. For example,  $a_{k-1} \cdots a_0$  is linked to  $a_0 \cdots a_{k-1}$  via a reverse edge. Since the algorithm which computes discrete Fourier transforms on the shuffle-exchange network leaves the output for node  $a_{k-1} \cdots a_0$  in node  $a_0 \cdots a_{k-1}$ , reverse edges provide a fast and convenient way of straightening out the solution. The graph consisting of shuffle, exchange, shift and reverse edges will be referred to as the shuffle-shift-reverse graph.

Using the techniques developed in section 3.3, it is also possible to show that the N-node shuffle-shift-reverse graph can be laid out in  $O(N^2/log^2N)$  area. The basic idea is to modify the layout described in section 3.4.1 so that

- 1) pieces of necklaces which are reverses of each other are paired together in the left-to-right ordering, and

- 2) pieces of necklaces are folded in half.

The first constraint insures that the maximal overlaps of the reverse edges in each row will be small while the second constraint insures that most reverse edges link nodes which are in the same row. Although it is not immediately obvious, it can be checked that these modifications do not substantially change the procedure for inserting the shuffle, shift and exchange edges which was described in section 3.4.1. Thus all of the edges can be inserted using at most O(N/logN) vertical and horizontal tracks.

#### 3.4.3 Transpose Edges

Transpose edges link the *ith* node to the (N-1-i)th node for each *i*. Viewed in terms of binary strings, transpose edges link each node to its complement. Although we do not know of any specific applications of transpose edges, they would be useful for problems that require frequent transposition of the data.

By further modifying the optimal layout for the shuffle-shift-reverse graph, it is possible to add transpose edges without increasing the total area by more than a constant factor. In particular, the layout should be modified so that

- 1) pieces of necklaces which are complements of each other are paired together in the left-to-right ordering, and

- 2) the distinguished node is selected on the basis of the location of the longest block of consecutive identical bits (be they zeros or ones).

The first constraint insures that the maximal overlaps of the transpose edges in each row are small while the second constraint insures that most transpose edges link nodes which are on the same row. Although we do not present the details here, it is possible to show that such a layout can be constructed using only  $O(N^2/\log^2 N)$  area, the least possible.

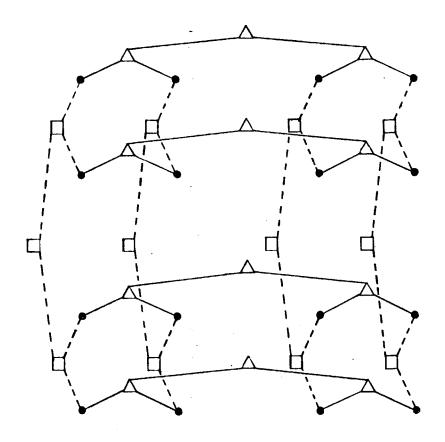

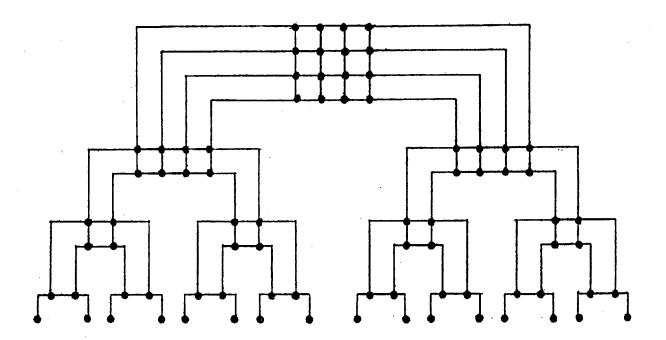

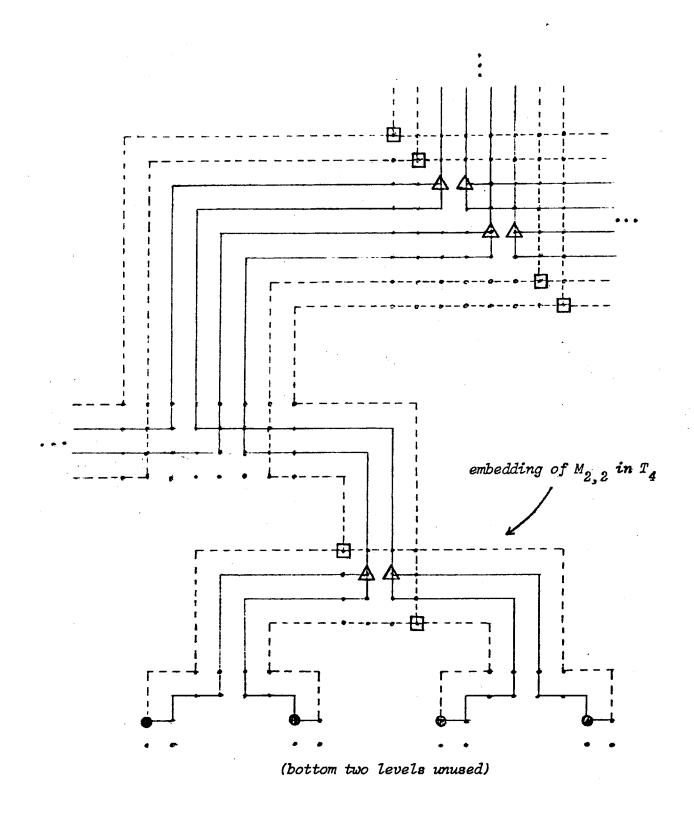

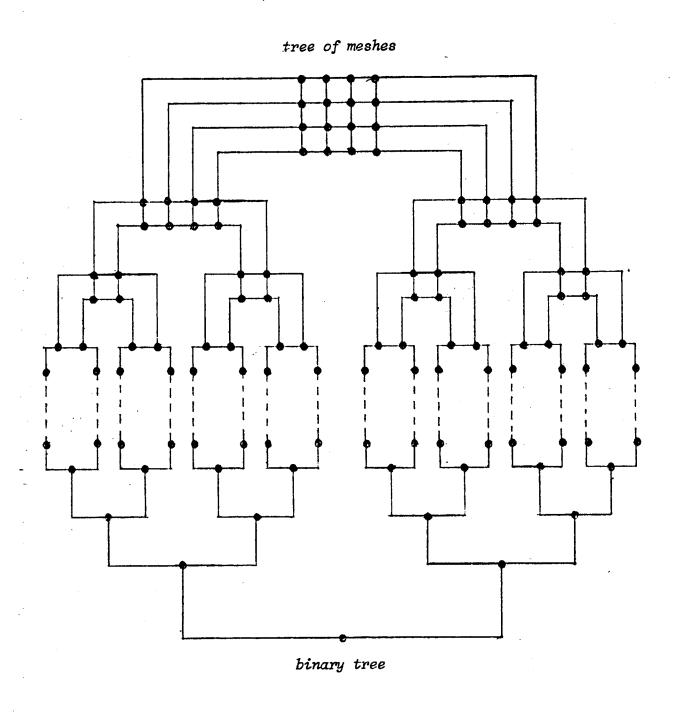

# Appendix: Proofs of Lemmas 3-1 Through 3-4