# LABORATORY FOR COMPUTER SCIENCE

MIT/LCS/TR-393

# SYNTHESIS OF SELF-TIMED VLSI CIRCUITS FROM GRAPH-THEORETIC SPECIFICATIONS

Tam-Anh Chu

June 1987

# Synthesis of Self-timed VLSI Circuits from Graph-theoretic Specifications

by

#### Tam-Anh Chu

B.S.E.E. Catholic University, Washington, D.C. (1979)

S.M. Massachusetts Institute of Technology (1981)

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy at the Massachusetts Institute of Technology

June, 1987

© Tam-Anh Chu

The author hereby grants to M.I.T. permission to reproduce and to distribute copies of this thesis document in whole or in part

| Signature of Author |                                                                           |

|---------------------|---------------------------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science<br>May 11, 1987 |

| Certified by        |                                                                           |

|                     | Jack B. Dennis<br>Thesis Supervisor                                       |

| Accepted by         |                                                                           |

|                     | Arthur C. Smith Chairman, Department Committee on Graduate Students       |

# Synthesis of Self-timed VLSI Circuits from Graph-theoretic Specifications

#### by **Tam-Anh Chu**

Submitted to the Department of Electrical Engineering and Computer Science on May 11, 1987 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

#### Abstract

This thesis presents an approach for direct and efficient synthesis of self-timed (asynchronous) control circuits from formal specifications called Signal Transition Graphs (STGs). Control circuits synthesized from this graph model are speed-independent and capable of performing concurrent operation. The property of speed-independence means that the circuit operates correctly regardless of variations in delays of logic gates, thus implying that the circuit is hazard-free under any combination of gate delays. The capability of STGs for explicitly specifying concurrent operations internal to a control circuit is unique to this model, unlike other approaches based on Finite State Machines.

STGs are a form of interpreted Petri nets, in which transitions in a net are interpreted as transitions of signals in a control circuit. While other synthesis approaches based on Petri nets have not been very successful, we have developed a number of analytical results which establish the equivalence between the static structure of nets (their syntax) and their underlying firing sequence semantics—an analytical approach called structure theory of Petri nets. This equivalence permits the characterization of the low-level properties of control circuits in terms of STG syntax: the properties of deadlock-free and hazard-free of circuits are characterized as syntactic propeties of liveness and persistency of STGs. A preliminary STG specification of a control circuit can be modified into one which is live and persistent, from which a deadlock-free and hazard-free logic implementation can be derived mechanically.

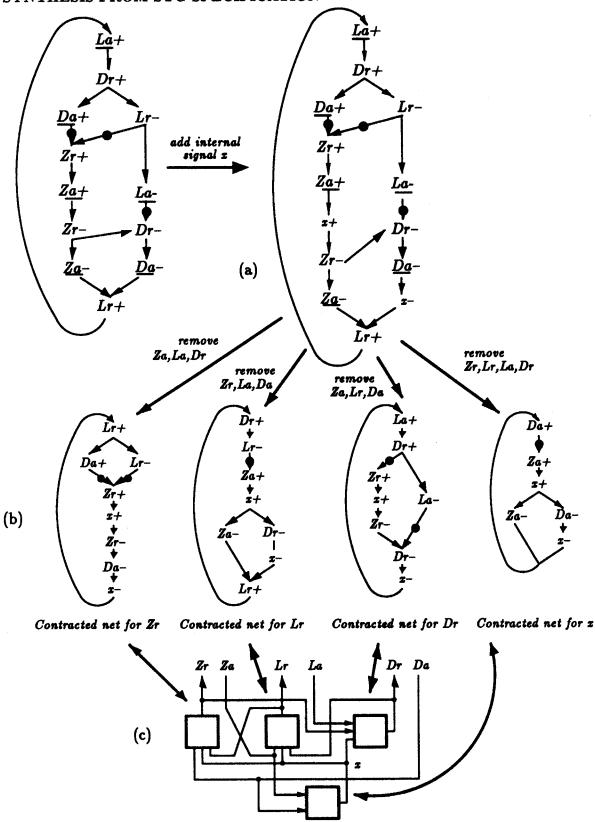

STGs allow efficient synthesis of control circuits by using a method of decomposition based on a graph-theoretic technique called *contraction*. Instead of implementing a logic circuit from a STG directly, it can first be decomposed into a number of contracted nets, one for each signal generated by the control circuit. A logic element can then be determined from each contracted net, and the composition of logic elements produces the final circuit implementation.

Thesis supervisor: Jack B. Dennis

Title: Professor of Computer Science and Engineering

Keywords: Asynchronous, self-timed speed-independent circuits; VLSI; Petri nets; structure theory; concurrency; finite automata.

#### Acknowledgments

I would like to thank Jack Dennis, my thesis supervisor, for providing invaluable guidance during the course of my thesis research. He had helped me formalize my ideas and guided me through the maze of my own confusion. I have learned a great deal about research, among many other things, from him.

Lance Glasser and Bill Dally, my thesis readers, deserve a lot of credits in shaping my research. Lance taught me VLSI circuit design, and the importance of always reasoning from first principles. Bill provided me with many useful comments and fresh perspectives about the problem.

Special thanks to my friend Clement Leung who has over the years given me advice and guidance; his friendship and help have made my life much easier. The ideas in this thesis originated from our early collaboration, and he deserves a share of them.

Many present and past members of the Computation Structures Group have helped me and made my stay at MIT more fun; I would like to mention a few: Arvind, Bill Ackerman, Andy Boughton, Suresh Jagannathan, Willie Lim, Guang-Rong Gao, Suhas Patil, Natalie Tarbet, Kevin Theobald, Tom Wanuga, Earl Waldin.

My Vietnamese friends at MIT and Harvard have provided me with a second home away from home, and I appreciate their support. Among them: Minh Hoàng for being a good old buddy; Bích-Ngọc Trần for her friendship, and also for her proofreading part of the early draft of this thesis.

This thesis could not have been completed without the love and support of my parents, my brother Nhị-Anh and sisters Nhất-Anh and Tú-Anh. To them, I would like to dedicate this thesis.

The major part of this research was carried out under financial assistance from the Hughes Doctoral Fellowship Program. This document was prepared using LATEX and equipments at the MIT Laboratory for Computer Science.

# Contents

| 1 | Intr | Introduction |                                                            |     |  |

|---|------|--------------|------------------------------------------------------------|-----|--|

|   | 1.1  | Object       | tives                                                      | 1   |  |

|   | 1.2  | Backg        | round                                                      | 2   |  |

|   | 1.3  | Proble       | ems with some previous models                              | 5   |  |

|   | 1.4  | Main e       | contributions of this work                                 | 7   |  |

|   | 1.5  | Exper        | imental results                                            | 8   |  |

|   | 1.6  | Organ        | ization of thesis                                          | 1   |  |

| 2 | An   | Inform       | nal Introduction 1                                         | 6   |  |

|   | 2.1  | Petri l      | Nets and Signal Transition Graphs                          | 8   |  |

|   |      | 2.1.1        | Petri nets                                                 | 8   |  |

|   |      | 2.1.2        | Signal Transition Graphs                                   | :3  |  |

|   |      | 2.1.3        | Relation between Petri nets and Signal Transition Graphs 2 | :5  |  |

|   | 2.2  | Seman        | ntics of nets/Behavioral equivalence                       | :7  |  |

|   |      | 2.2.1        | Behavioral Equivalence                                     | 3:  |  |

|   |      | 2.2.2        | Important Analytical Results for Nets                      | 95  |  |

|   | 2.3  | Prope        | rties of State graphs                                      | \$4 |  |

|   |      | 2.3.1        | State Graphs and Network Functions                         | 14  |  |

|   |      | 2.3.2        | Liveness and Consistent State Assignment                   | 15  |  |

|   |      | 2.3.3                                | Persistency                                                                  | 36         |

|---|------|--------------------------------------|------------------------------------------------------------------------------|------------|

|   |      | 2.3.4                                | A synthesis procedure                                                        | <b>3</b> 8 |

|   | 2.4  | .4 Decomposition by Net Contraction  |                                                                              |            |

|   | 2.5  | 2.5 A problem with state assignment  |                                                                              |            |

|   | 2.6  | Summ                                 | uary                                                                         | 45         |

| 3 | Sen  | nantics                              | and Temporal Relations of Nets                                               | 46         |

|   | 3.1  | Petri l                              | Nets                                                                         | 47         |

|   |      | 3.1.1                                | A Brief Introduction                                                         | 47         |

|   |      | 3.1.2                                | Previous Results for Free-Choice nets                                        | <b>5</b> 0 |

|   | 3.2  | Firing                               | Sequence Semantics of Free-Choice nets                                       | 53         |

|   |      | 3.2.1                                | Semantics                                                                    | 53         |

|   |      | 3.2.2                                | An algorithm for constructing reachability graphs                            | 55         |

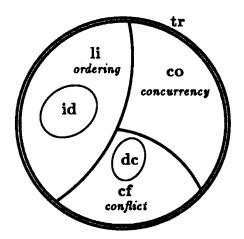

|   | 3.3  | Tempe                                | oral Relations: Ordering, Concurrency and Conflict                           | 58         |

|   |      | 3.3.1                                | Syntactic Characterization                                                   | 58         |

|   |      | 3.3.2                                | Partition of the Temporal Relation and Correspondence to Reachability Graphs | 62         |

| 4 | Sign | nal Tra                              | ansition Graphs                                                              | 68         |

|   | 4.1  | Synta                                | x and Semantics                                                              | <b>6</b> 8 |

|   |      | 4.1.1                                | Signal Transition Graphs                                                     | 69         |

|   |      | 4.1.2                                | State Graphs                                                                 | 70         |

|   |      | 4.1.3                                | Network functions: Implementations of state graphs                           | 72         |

|   |      | 4.1.4                                | An Example                                                                   | 73         |

|   | 4.2  | 4.2 Obtaining state graphs from STGs |                                                                              |            |

|   | 4 3  |                                      |                                                                              |            |

CONTENTS

| 5                                   | Properties of State Graphs 8        |                      |                                         | 83    |  |  |

|-------------------------------------|-------------------------------------|----------------------|-----------------------------------------|-------|--|--|

|                                     | 5.1                                 | 1 Liveness           |                                         |       |  |  |

|                                     | 5.2                                 | Persist              | tency                                   | . 84  |  |  |

|                                     |                                     | 5.2.1                | Definition of Persistency               | . 85  |  |  |

|                                     |                                     | 5.2.2                | Characterization of Persistency in STGs | . 89  |  |  |

|                                     | 5.3                                 | A prol               | blem with state-assignment              | . 94  |  |  |

| 6                                   | Decomposition by Net Contraction 9' |                      |                                         |       |  |  |

|                                     | 6.1                                 | Contra               | action Algorithms                       | . 98  |  |  |

|                                     |                                     | 6.1.1                | Contraction of Petri nets               | . 98  |  |  |

|                                     |                                     | 6.1.2                | Contraction of Finite Automata          | . 101 |  |  |

|                                     | 6.2                                 | Proper               | rties of Contraction                    | . 104 |  |  |

|                                     | 6.3                                 | Decom                | position by net contraction             | . 110 |  |  |

|                                     | 6.4                                 | Applic               | eation to Signal Transition Graphs      | . 118 |  |  |

| 7                                   | A I                                 | A Design Example 121 |                                         |       |  |  |

| 7.1 Specification of the Controller |                                     |                      |                                         |       |  |  |

|                                     |                                     | 7.1.1                | Behavior Specification                  | 123   |  |  |

|                                     |                                     | 7.1.2                | STG specifications                      | . 124 |  |  |

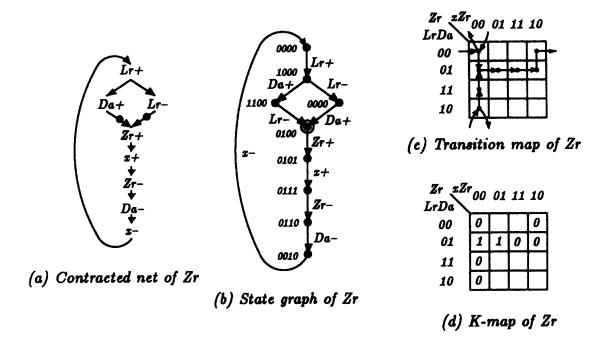

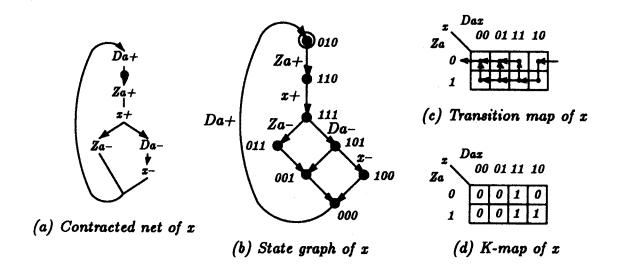

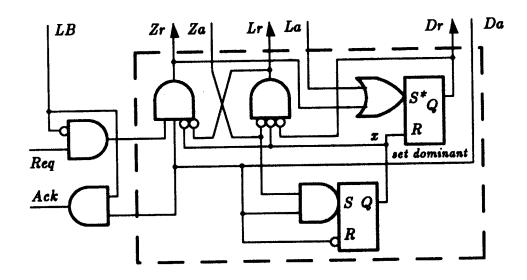

|                                     | 7.2                                 | Synthe               | esis from STG Specification             | . 126 |  |  |

|                                     |                                     | 7.2.1                | Meeting liveness and persistency        | . 126 |  |  |

|                                     |                                     | 7.2.2                | Implementation using decomposition      | . 130 |  |  |

|                                     | 7.3                                 | Summ                 | ary                                     | . 136 |  |  |

| 8                                   | ST                                  | Gs witl              | h Non-input Choices                     | 138   |  |  |

|                                     | 8.1                                 | Introd               | uction                                  | . 138 |  |  |

|                                     | 8.2                                 | The B                | asic Idea                               | . 140 |  |  |

|    |     | 8.2.1   | A fundamental problem with specifying non-input choices in state graphs. | . 141 |

|----|-----|---------|--------------------------------------------------------------------------|-------|

|    |     | 8.2.2   | Specifying non-input choices in state graphs                             | . 142 |

|    | 8.3 | STGs    | with non-input choices                                                   | . 145 |

|    |     | 8.3.1   | Syntax                                                                   | . 145 |

|    |     | 8.3.2   | Firing rule                                                              | . 146 |

|    | 8.4 | An ex   | ample: a two-cycle FIFO controller                                       | . 147 |

| 9  | The | Ехра    | nsion Algorithm                                                          | 152   |

|    | 9.1 | Occur   | rence nets and Processes of nets                                         | . 153 |

|    |     | 9.1.1   | Occurrence nets                                                          | . 153 |

|    |     | 9.1.2   | Processes of nets                                                        | . 154 |

|    |     | 9.1.3   | A few results for processes of LSFC nets                                 | . 157 |

|    |     | 9.1.4   | Processes of STGs                                                        | . 158 |

|    | 9.2 | The ex  | xpansion algorithm for STG/NCs                                           | . 161 |

|    |     | 9.2.1   | Unfolding and folding of free-choice nets                                | . 162 |

|    |     | 9.2.2   | The Expansion Algorithm                                                  | . 165 |

|    |     | 9.2.3   | An example                                                               | . 169 |

|    | 9.3 | Proper  | rties of STG/NCs                                                         | . 172 |

|    | 9.4 | Summ    | ary                                                                      | 179   |

| 10 | Sug | gestion | as for further research                                                  | 180   |

... All things entail rising and falling timing. You must be able to discern this. In strategy there are various timing considerations. From the outset you must know the applicable timing and the inapplicable timing, and from among the large and small things and the fast and slow timings find the relevant timing, first seeing the distance timing and the background timing. This is the main thing in strategy. It is especially important to know the background timing, otherwise your strategy will become uncertain.

A Book of Five Rings Miyamoto Musashi ... All Signal Transition Graphs entail rising and falling signal transitions. You must be able to discern this. In our design method, there are various timing considerations. From the initial specification, you must know the allowed timing and the disallowed timing, and from among the large and small circuits and the fast and slow logic gates find the relevant timing, first seeing the distance timing and the timing protocol at the interface. This is the main thing in our design method. It is especially important to know the timing protocol, otherwise your circuits will not work.

## Chapter 1

## Introduction

#### 1.1 Objectives

The main objective of this research is the development of a design approach for asynchronous self-timed VLSI digital systems. The core of our approach is a graph model called Signal Transition Graphs (STGs). STGs allow the specification and efficient synthesis of self-timed control circuits. Our approach produces speed-independent logic circuits which can perform concurrent operations.

In the realm of VLSI, exploiting concurrency is a prerequisite to high-performance: as systems become larger and more complex, one can no longer afford to ignore the parallelism in control operations. The *central control* discipline which is well-accepted in present approaches creates difficulties in high-performance systems by imposing an unnecessary sequential order on the execution of control operations. In choosing a control discipline which allows for parallel execution of unrelated operations, one naturally moves toward a *distributed control* organization. Thus, instead of a large central controller, one has numerous distributed control modules which can operate concurrently. STGs allow the specification and synthesis of these types of control modules—not only that they can operate concurrently, but also each module itself can perform several control operations in parallel.

By speed-independent circuits, we mean those circuits whose correct operation is independent of the delays of logic gates composing the circuits. One immediate consequence

of this property is that speed-independent circuits are always hazard-free. These types of circuits are desirable in VLSI systems because it is usually difficult to fine-tune the delays of logic gates to make an asynchronous digital circuit work properly. Perhaps most importantly, the use of speed-independent circuits enables the separation of the correctness of systems from timing considerations (which inextricably depend on many physical factors and phenomena in VLSI circuits). It is no coincidence that a number of research efforts in silicon compilation have utilized speed-independent circuits as a basis for hardware implementation [1,42].

STGs allow the direct and efficient synthesis of control circuits from formal specifications. Unlike previous efforts, the approach based on STGs produces a specification which closely reflects the designer's intuition. Moreover, this approach produces efficient circuit realizations by using a number of decomposition techniques. While speed-independent circuits have been criticized for their inefficiency in implementation (and therefore speed and performance), our experiences with applying this graph model to designing VLSI chips have been much more encouraging.

#### 1.2 Background

We can categorize research works in self-timed systems according to two attributes: the theoretical models on which the research is based, and the particular aspects chosen for study. In terms of models, there are finite automata and Petri nets [39,41], and variations of the two. With regard to aspects of study, the two chief areas of concern are composition of systems from modular descriptions, and synthesis of modules from specifications. The study of composition of systems from self-timed modules usually assumes the presence of a set of modules with a certain uniform communication discipline, and the investigation takes a system point of view in exploring properties of systems composed from the modules. The other area of concern concentrates on techniques for synthesis of control modules rather than on the composition and communication aspect of systems.

Two prevalent concepts describing the properties of self-timed systems are delay-insensitivity and speed-independence [35,36,37]. While these are commonly used interchangeably, we often find that delay-insensitivity has connoted a stress on the communication aspect and hence, the composition of systems. Thus, this terminology denotes an external prop-

1.2. BACKGROUND 3

erty of control modules. On the other hand, speed-independence is usually understood as a property of control circuits which operate correctly regardless of variation in delays of logic gates. Speed-independence emphasizes the synthesis aspect, hence is a property internal to control modules.

Regardless of the emphasis of these research works—whether on composition or on synthesis—they require a formal specification which must rest on the theoretical model chosen. We have found that Petri nets provide a better starting point for formally specifying self-timed circuits, since Petri nets per se have capabilities for explicitly modeling concurrency. Also, automata theory originally concentrated on sequential systems. Not until recently was the basic theory extended to cover aspects of concurrency, and not until even later was it applied to the area of logic design.

Below, we briefly review some of the relevant works according to the outline above. In short, each proposal identifies a basic model which also serves as its formal tool for specification, and a focus of study (i.e. composition or synthesis). Interestingly, most of the works deal with only one of the two areas; and none of them provides a coherent framework for treating both synthesis and composition at the same time. This survey is by no means exhaustive; it only serves to highlight the more relevant results which fit more into our classification.

Most techniques for synthesis of asynchronous logic are based on either some form of finite automata such as the Finite State Machine (FSM) model, or Petri nets. The most outstanding work based on finite automata models can be traced back to Muller [35,36,37], who originated the idea of speed-independent circuits. Recent work in trace theory [42,53,51] can be considered as a systematic reformulation of Muller's idea: this refinement is made possible because of the recent attempts to extend automata theory to cover concurrent behavior of systems.

Concerning synthesis approaches based on Petri nets, one of the most important early contributions was made by Patil and Dennis at MIT [15,17,16,38]. Patil invented asynchronous logic arrays as a systematic method of directly implementing Petri nets [38]. In an asynchronous logic array, columns of wires are connected to storage elements to simulate the places of a net, while rows of wires decode the state of the columns to simulate the occurrence of transitions. Thus, this method of implementation transfers the structure of a net directly to hardware. Dennis has shown that Petri nets can be used to model

asynchronous hardware systems at many levels of description in a very clear and easily understood manner [15]. Dennis' description of the control logic of the Control Data 6600 computer, which embodied instruction look-ahead and interleaved execution, demonstrated this technique. Dennis and Patil also elucidated an organization principle for asynchronous hardware systems in which a system is partitioned into data paths and distributed control structures, the latter organized as asynchronous modules which communicate with each other using certain signaling protocols [17,16]. Based on this organization principle, we have successfully designed and fabricated a self-timed two-by-two packet router, a basic component of a packet communication network [10].

Works at Washington University have also made important contributions to the study of self-timed systems, most importantly the use of macromodules proposed by Clark [11], and experimental proof of metastability problem in synchronizers, together with design techniques for alleviating this problem [7,13,47]. Most recently, Molnar et al. [34] proposed the use of a form of Petri nets called I-nets for specifying behavior of control circuits, from which Interface State Graphs (ISG) are derived by simulating the I-nets. ISGs can then be encoded with binary states and serve as the basis for implementation of control circuits as standard Huffman asynchronous state machines. This idea was inspired by Seitz's Machine-nets [46] but contained a number of improvements.

Work at CalTech by Seitz resurrected interest in self-timed systems in the VLSI era, as reported in a chapter of Mead and Conway's book Introduction to VLSI systems [32]. Currently, Martin [30] at CalTech proposed a design approach using constructs for non-deterministic programming to specify hardware modules whose behaviors exhibit only sequencing and arbitration requirements. This approach uses a subset of Dijkstra's guarded command language [18] to specify each process; concurrently cooperating processes are described using notations similar to Hoare's CSP [25]. Heuristic procedures are used to "compile" a hardware implementation from a module specification into an interconnection of standard hardware templates such as And, Or, C-elements, etc. During the compilation, the technique of reordering signal transitions in a sequence is used to improve implementation efficiency.

Recently, there have been works which use *trace theory* as a formalism for specifying delay-insensitive circuits. Trace theory was pioneered by Mazurkievicz, who has recently made further contributions to this theory [31]. Trace theory has been used in the *COSY*

formalism invented by Campbell and Habermann [6] and in CSP. Rem, Snepscheut and Udding at Eindhoven have demonstrated the use of trace theory for classifying and reasoning about composition of delay-insensitive circuits [42,53,51]. Trace theory has laid a firm theoretical foundation for further investigation of properties of concurrent circuits, as evidenced through recent works [5,45]. Perhaps one novel aspect of these works in comparison with the others is a method for classification of delay-insensitive circuits according to properties of their trace structures [51].

There are a number of earlier works concerning the composition of systems from asynchronous hardware modules; many were reported at the Project MAC Conference on Concurrent Systems and Parallel Computation (ACM, 1970). One notable study was made by Keller at University of Utah, in which he proposed the use of a set of "universal" control modules from which any control network can be constructed [28].

One of the important related works to self-timed systems is the use of temporal logic for verification of asynchronous hardware structures [19]. Such techniques can be used fruitfully for correctness validation of self-timed circuits and systems composed from circuits. It may also be a candidate for a formalism for specification and synthesis of self-timed circuits.

## 1.3 Problems with some previous models

Below, we describe a number of well-known difficulties with some traditional approaches for designing asynchronous circuits. In particular, we discuss problems with the FSM model and with earlier attempts to apply Petri nets. By identifying these problems, we hope to illustrate the difficult practice of designing asynchronous circuits; this will motivate the search for remedies, some of which are provided by the approach we present in the following chapters.

Traditionally, asynchronous circuits are designed using the FSM model. A method for realization devised by Huffman uses a *flow-table* and a circuit model for implementing the state machine, as described in textbooks such as [20]. This design approach is very difficult to use, especially for synthesizing circuits with many input variables. So far, it has limited applications because of problems caused by variations in gate delays, particular in the

feedback paths of the circuit. Some of the frequently cited disadvantages and limitations of this implementation model are:

- The Huffman state machine cannot handle unrestricted input changes. It was discovered by Unger [52] that in the Huffman state machine, if two input transitions occur within a time interval (i) less than  $min(D_L + D_f)$ , then they can be considered as simultaneous, if (ii) greater than  $max(D_L + D_f)$  then they can be considered separate, and if (iii) less that  $max(D_L + D_f)$  and greater than  $min(D_L + D_f)$ , then the secondary state variable will not have settled and the circuit malfunctions;  $maxD_L$ ,  $minD_L$  denote the maximum and minimum delays of the combinational logic, and  $maxD_f$ ,  $minD_f$  denote those of the feedback delays. (In general,  $minD_f$  has to be greater than zero.)

- The FSM model cannot describe concurrent behaviors directly. The FSM model and the Huffman state machine are based on the use of central states. At any moment, the machine resides in one state and it reacts to input excitations in different ways depending on which state it is in. A serious drawback of this state-based approach is that it is incapable of describing concurrency directly. The reason is that the notion of concurrency is more conveniently expressed in terms of occurrences of events; at the level of description of the FSM model, this phenomenon is difficult to see.

- The state assignment problem. Since it is difficult to match gate delays to achieve simultaneous transition of state signals, one has to make sure that simultaneous changes in state signals do not occur, or if they do, the circuit must be designed such that it behaves the same no matter which sequences of state changes take place. Hence most state assignment techniques only allow at most one signal change between states. This is a well-known hard problem for which many heuristic techniques have been proposed. State assignments serve another purpose in the implementation of state machines, that of decomposition. This further complicates the issue, as an optimal state assignment for decomposition may be in conflict with the requirement for single signal changes between states.

- The exponential dependence of the number of entries in the flow table on the number of input signals. Due to the absence of a controlling signal called a "clock", a Huffman asynchronous state machine continuously senses the changes in the input and produces changes at the output and the state variables. Therefore, in contrast to a synchronous implementation of a state machine, an asynchronous implementa-

tion requires the listing of all input combinations in the flow table, resulting in the exponential increase in the number of entries in the table.

There are a few early proposals for implementation of asynchronous circuits from Petri net specifications, most notably Patil's asynchronous logic array and Seitz's Machine-nets. Patil's proposal is more correctly viewed as a hardware implementation of Petri nets, rather than implementation of asynchronous circuits from net specifications, because his technique basically replaces an element in a net with a hardware circuit which simulates the behavior of that element. Hence the structure of the net is transferred directly to hardware and there is no direct way to ensure that the resulting asynchronous machine meets all timing requirements. The operation of this type of asynchronous logic arrays depend greatly on local timing, and meeting these timing constraints can sometimes be difficult.

Seitz's Machine-nets, on the other hand, serve only as specifications from which FSM descriptions can be derived. The synthesis of a Huffman state machine from such a description still requires the standard techniques and therefore faces the same difficulties.

#### 1.4 Main contributions of this work

We have developed a synthesis approach for self-timed control circuits from graph-theoretic specifications called *Signal Transition Graphs*, a form of interpreted Petri nets. As will be described in the rest of the thesis, our original contributions are the following.

- A set of new analytical results for Petri nets which allows the study of net properties purely from the syntax (or structure) of nets; we call this the structure theory approach.

- The development of Signal Transition Graphs, a formal model for specification and direct synthesis of self-timed control circuits with concurrent deterministic operation and input choices.

- A decomposition technique of nets based on a graph-theoretic notion called *contraction*. This technique can be applied directly to Signal Transition Graphs, thus allowing highly efficient implementations.

• An extension of the Signal Transition Graph model to allow the specification and synthesis of data-dependent control circuits.

### 1.5 Experimental results

In early 1984, we set out to test our Signal Transition Graph model by designing and fabricating two self-timed chips through MOSIS. The first chip is a two-by-two packet router [10], a basic component of a communication network for a dataflow computer envisioned at MIT [14]. The router was implemented in 3 micron CMOS technology with 2456 transistors and a layout area of  $3.1 \times 2.3mm^2$ . A total of 46 routers were tested and 30 of them were fully operational with a maximum throughput rate of approximately 22 Mbytes/sec. The other chip fabricated was a self-timed ring buffer, a FIFO buffer with an interesting distributed organization which reduces the latency of the buffer to one stage delay [9]. This ring buffer consists of 8 stages and 9-bit wide data paths. It was fabricated in 4 micron NMOS technology and consumed an area of  $3.15 \times 2.25mm^2$ , including pads. Six chips were received from MOSIS and tested; five were fully functional at a throughput rate of approximately 4 MBytes/sec. These encouraging results indicate that our proposed approach produces systems which are efficient both in terms of the amount of hardware and speed, perhaps comparable to synchronous implementations.

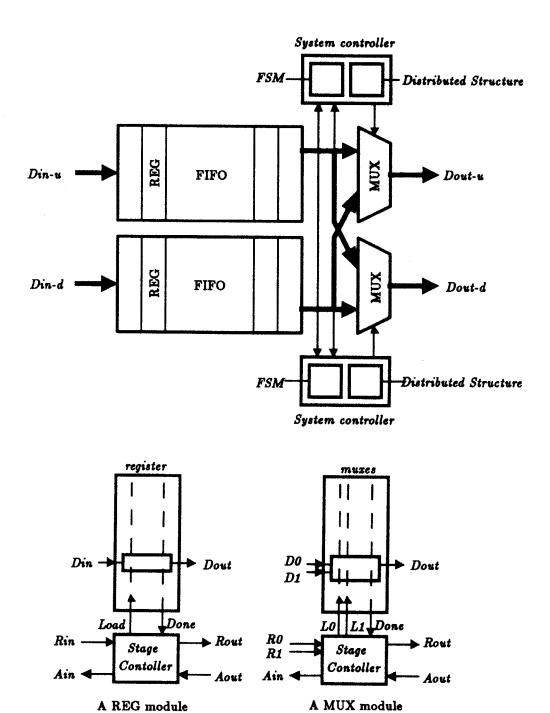

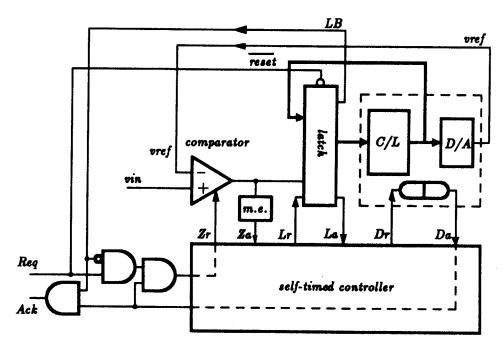

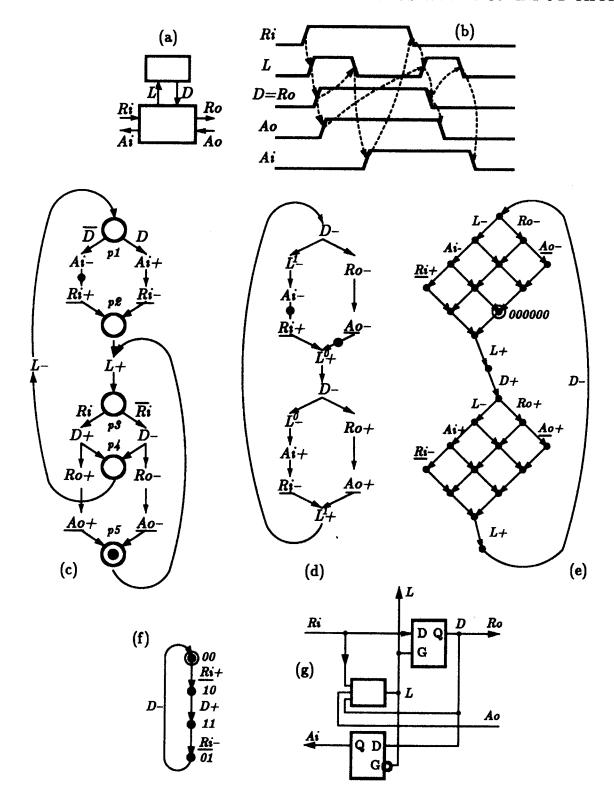

#### Description of the Router

The block diagram of the router is shown in Fig. 1.1. It contains two FIFO queues to hold packets sent in byte-serial format. Packets are of variable length, and an extra bit called Last-byte is appended to each byte to delimit the packet boundary. This bit is "1" for the last byte of a packet and "0" for all others. The first byte of a packet contains the address information. The router decodes the address and forwards the packet to the desired output port; an address bit of "0" will form a link from the current input port to the upper output port, a "1" will form a link to the lower output port. There are two system controllers, each consisting of a FSM and a distributed control structure. The

<sup>&</sup>lt;sup>1</sup>In [10], the maximum throughput rate for the routers was reported to be 11 Mbytes/sec. This figure is for one input port. The above figure of 22 MBytes/sec reflects the fact that two input ports can process packets concurrently.

system controllers read the address and the *Last-byte* signals, and generate control signals for the output multiplexors. These control signals are determined from the first byte of a packet and recycled for the remaining bytes. The two controllers also communicate with each other, since packets from one input port may need to go to the opposite output port. If packets from both input ports require the same output port at the same time, an arbiter is used to resolve conflicts.

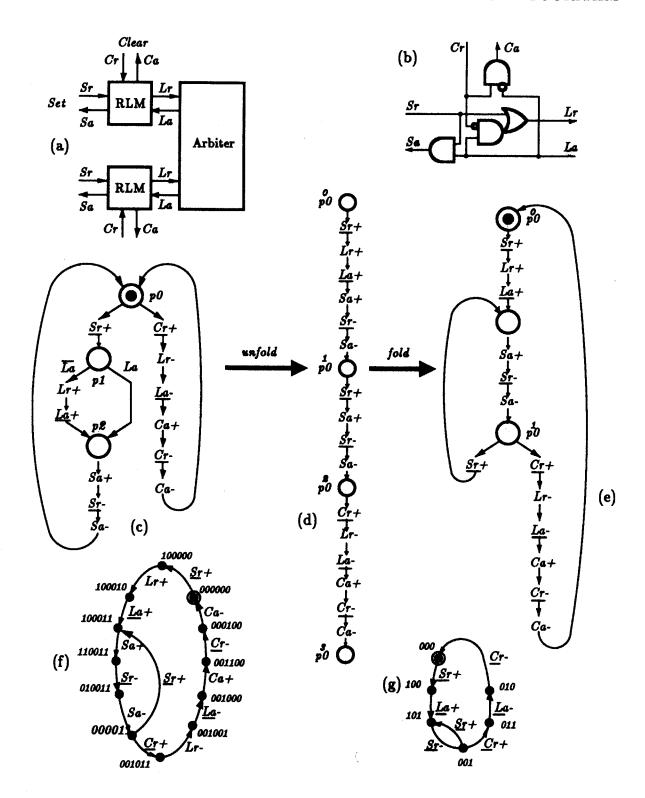

Two main data path modules are the multiplexors, and the self-timed registers which constitute the FIFO's. These modules consist of a data circuit and a stage controller which handles the timing and signaling protocol. These stage controllers are specified using STGs from which speed-independent realizations can be obtained using our synthesis techniques. The controllers contains control circuits which are also synthesized using the same techniques. The Resource Locking Module (RLM), a control module with data-dependent operation is treated in an example in Chapter 9. This module is used together with an arbiter [32] to control the access of the FIFO queues to the output multiplexors.

#### Description of the Ring buffer

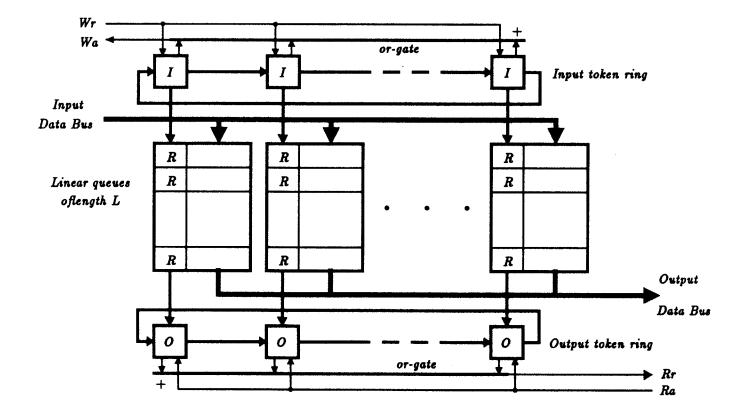

The ring buffer is a FIFO queue organized in a two-dimensional or ring organization, as shown in Fig. 1.2. This queue consists of M linear queues, each of L stages, and two token rings for controlling input/output operation. The capacity of the queue is  $M \times L$  and the latency is proportional to L.

Writing into the FIFO queue is controlled by an Input token ring, formed by connecting I-modules together into a ring. The ring is initialized such that only one I-module contains the token, marking the next available empty register stage. Since the Write-request signal, carried on wire  $W_r$ , is connected to all I-modules, an important timing restriction is that the token should not be passed on to the next module in the ring if the Write-request signal is still active. The Write-acknowledge on wire  $W_a$  is the output of an OR gate (shown as a heavy bar with a + sign) whose inputs are acknowledge wires from all I-modules. Similarly, reading from the FIFO is controlled by an Output token ring, formed by connecting O-modules together. Data written into the linear queues ripple to their output side, ready to be gated onto the output bus. The Output ring is initialized such that only one O-module contains the token. This module then controls the timing and

Figure 1.1: Block diagram of the two-by-two packet router.

signaling for gating of data to the output bus. The Read-request signal on wire  $R_r$  is the output of an OR gate whose inputs are request wires from all O-modules. Another timing restriction exists for the Output token ring: since the Read-acknowledge signal, carried on wire  $R_a$  is broadcast to all O-modules, the token should not be passed on to the next module while Read-acknowledge is still active.

Our FIFO queue design makes use of distributed control structures and local communication. There are only a few types of modules in this design, with modules of each type replicated as necessary to construct complete FIFO queues. The distributed control structure allows the exploitation of concurrency. Concurrent read/write supports a higher throughput rate. The FIFO queue is also completely data driven, hence no potential read/write conflict exists and there is no need for any arbiter. The distributed control organization of the FIFO lends itself naturally to a design using asynchronous, self-timed hardware modules. These control modules are specified using STGs and synthesized from such specifications. The Ring buffer which we fabricated is one with minimal latency (L=1), with each of the linear queues containing exactly one stage. Registers in each stage have inputs connected to the input data bus, and outputs connected to the output data bus.

## 1.6 Organization of thesis

After the two introductory Chapters 1 and 2, this thesis is organized into three parts.

Part I consists of Chapters 3-5, in which the basic theory of STGs is developed. This part gives an introduction to Petri net theory, discusses a number of relevant new results and shows how this theory is applied to STGs, a form of interpreted Petri nets. This is followed by an investigation of properties of speed-independent circuits, which translate to the properties of liveness and persistency in STGs. The material developed in this part allows the specification and synthesis of a basic type of speed-independent control circuit from STG specifications; these circuits can perform concurrent deterministic operation and (nondeterministic) input choices.

Part II, consisting of Chapters 6 and 7, discusses a novel technique for decomposition of systems based on a notion called contraction. Here, the theoretical results for Petri nets

Figure 1.2: Block diagram of the Ring buffer.

are developed and then applied to STGs, as demonstrated through a design example.

Part III, consisting of Chapters 8 and 9, discusses an extension to the basic STG model to allow the specification and synthesis of control circuits with data-dependent operation. The main ideas are presented informally in Chapter 8, together with an example. Chapter 9 develops the formal theory for our extension.

Chapter 2 contains a summary of the STG model and the main theoretical results of Parts I and II. This chapter gives a broad outline of the detailed description which follows in Chapters 3 to 6. It is intended to provide enough knowledge of our methodology for immediate applications. Chapter 7 contains a substantial design example which can be studied without having to go through the technical details presented in Chapters 3–6. Chapter 8 gives an informal presentation of the main idea of our extension of STGs to allow the specification of data-dependent circuits. Thus, after Chapters 2 and 7, Chapter 8 can be read to provide an understanding of the extension.

The following is a more detailed description of each chapter.

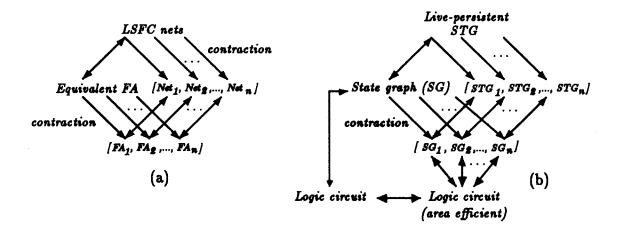

Chapter 3. A number of new results are developed for a useful class of Petri nets called live-safe free-choice nets; they constitute the theoretical basis for further investigation of our STG model. First, relevant works in Petri nets theory are reviewed, with particular emphasis on the study of structure theory, which is mainly concerned with the relationship between the syntax (structure) and the underlying semantics of nets. This chapter develops two new results: (a) It is demonstrated that the behavior of a free-choice net, as characterized by its set of transition sequences, can be obtained by concurrently composing the behavior of its component subnets. As a consequence, an algorithm is devised, allowing the construction of finite automata directly from the structure of nets by composing finite automata of subnets. (b) A relation called the temporal relation on the set of transitions of a net is defined. This relation is characterized based on the structure of nets and it allows for the syntactic determination of whether two transitions are ordered, concurrent or in conflict.

Chapter 4. The materials developed in Chapter 3 are part of a formal theory based on Petri nets, and they may be useful for other applications as well. For our purposes,

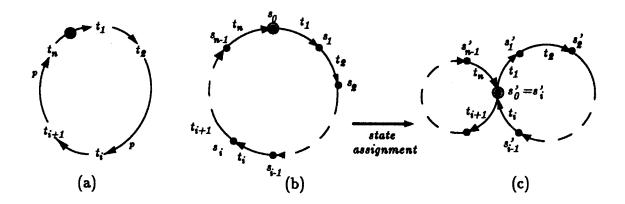

we interpret elements of nets as physical entities of digital circuits: transitions of nets are identified with rising and falling transitions of signals in circuits—hence the name Signal Transition Graphs. In this chapter, we introduce the STG model, its syntax and semantics, and our design approach for direct synthesis based on STGs. We introduce state graphs and their properties related to physical switching circuits. The third concept in this chapter is network functions, defined as the sets of logic functions describing the operation of the circuits. Network functions can be determined directly from state graphs. We also discuss state assignment, being the process of assigning binary values to states in a finite automaton to produce a state graph. Although this is a well-known difficult problem in the classical approach based on the Finite-State Machine (FSM) model, for STGs it is done automatically for STGs by satisfying certain syntactic conditions.

Chapter 5. We discuss two important properties of state graphs and STGs called liveness and persistency. Liveness is related to the continuous operation without deadlock of circuits; persistency is related to hazard-free operation of circuits. Persistency is strongly tied to the notion of speed-independence: a circuit is speed-independent iff its STG specification is persistent. The equivalent syntactic characterization of liveness and persistency are developed for STGs.

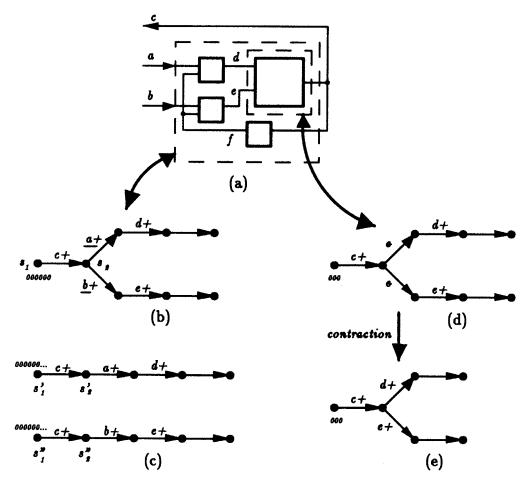

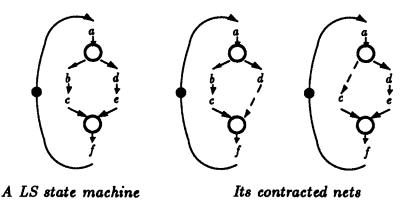

Chapter 6. A method of decomposition for nets called *contraction* is introduced. This allows the decomposition of state graphs through decomposition of their STGs. The purpose of decomposition of state graphs is to produce efficient implementations by minimizing the interaction between variables in the state graphs. While there exist only complex heuristic procedures for FSM approach, for STGs this can be carried easily using net contraction based on some structural information from the STGs.

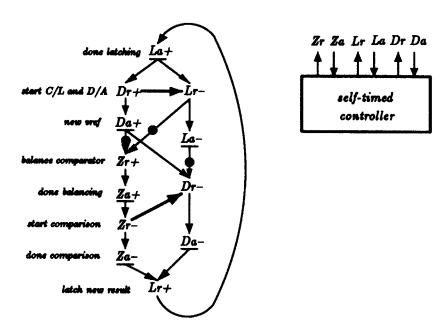

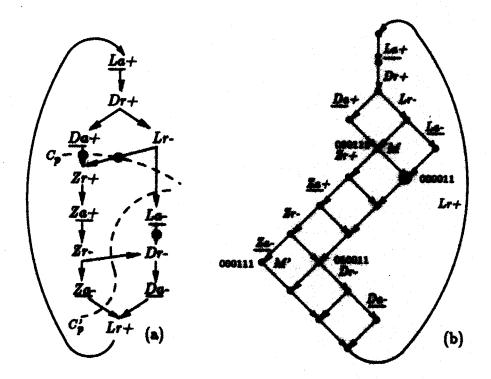

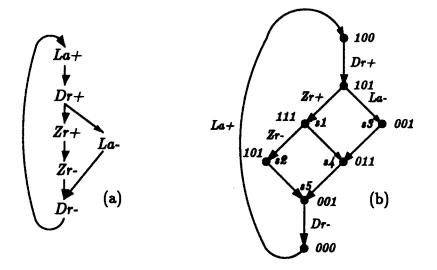

Chapter 7. This chapter concludes the second part of the thesis by providing a detailed design example of a self-timed controller for a successive-approximation A-to-D converter. We will go through the synthesis steps and illustrate the principles developed earlier. We also discuss a number of design choices available during certain steps of the synthesis process.

Chapter 8. Parts I and II of the thesis provide the ground work which allows one to specify circuit behavior in terms of STGs, obtain their state graphs and finally, produce a correct and efficient implementation by satisfying liveness and persistency. However, since STGs are based on free-choice nets, their expressive power is limited to that of free-choice nets. Since free-choice nets can specify concurrent operations and free-choices (nondeterministic choices), correspondingly, STGs can only specify concurrent operations and input choices (The reason for considering free choices in nets as input choices in STGs is that internally to a control circuit module, input choices appear nondeterministic.) In order to specify circuit operation with internal choices (data-dependent operation), one will need to rely on a more expressive class of Petri nets.

In Chapter 8, we consider an extension to the STG model which allows the specification and synthesis of circuits with data-dependent operations. This extension marks a slight departure from net theory, as it is a notational extension in STG to represent an aspect of flow-control in state graphs, i.e., the ability to make a decision based on a priori knowledge when arriving at a state with conflicts. We discuss this extension and its semantics in terms of state graphs. Lastly, a design example of a two-cycle controller for first-in first-out (FIFO) circuits is presented. This controller is a data-dependent circuit which can perform concurrent control operations.

Chapter 9. Chapter 9 describes an algorithm called *expansion* algorithm which allows the transformation of a STG specifying data-dependent operation into one which has only input choices. Another design example is given: the *Resource Locking Module* which is a part of the controller of the Router discussed earlier.

Chapter 10. We discuss areas for further investigation with the aim toward a comprehensive approach for automatically compiling self-timed VLSI systems from high-level descriptions. Another area of interest is that of optimization of asynchronous circuits based on particular implementation technologies and design methodologies.

## Chapter 2

# Signal Transition Graphs: An Informal Introduction

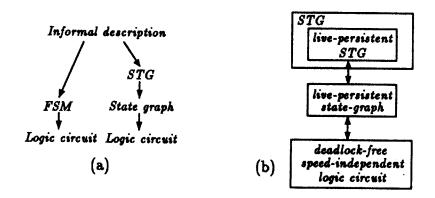

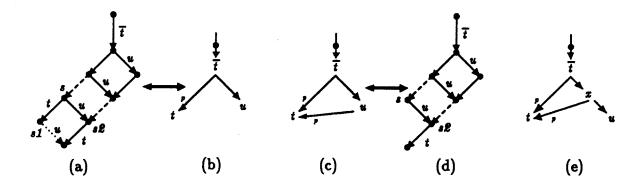

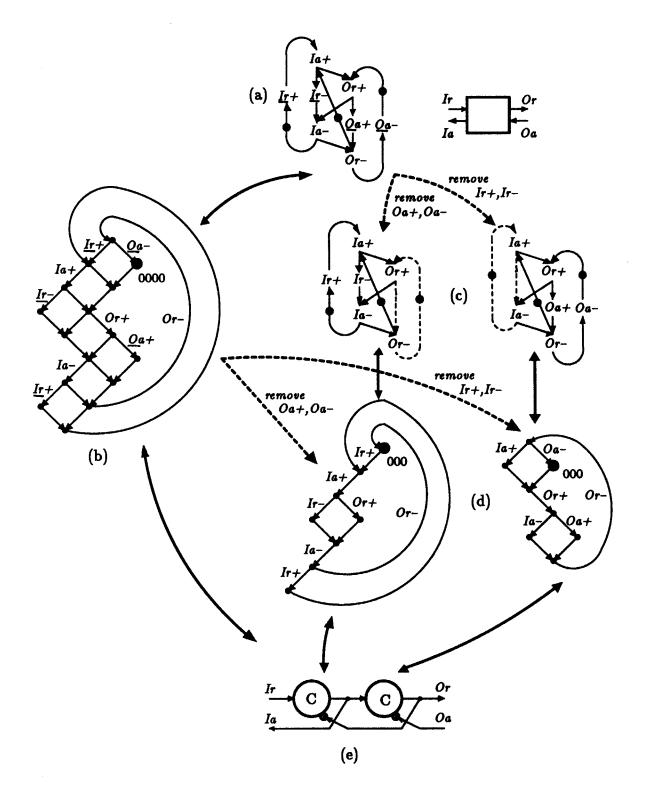

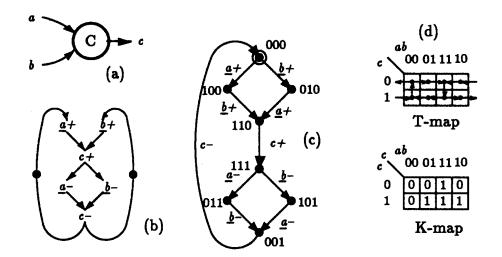

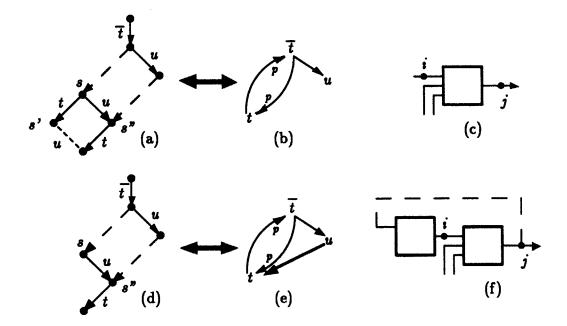

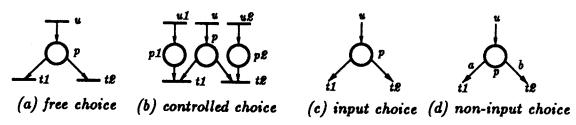

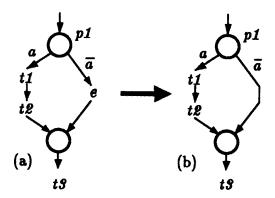

This thesis presents an approach for the synthesis of self-timed control circuits from formal graph-theoretic specifications. The conventional approach consists of constructing a Finite State Machine (FSM) from some informal (e.g. textual) description and determining the logic equations for state and output variables from the FSM, as illustrated in the left branch of Fig. 2.1a. Unlike this approach, the basic idea of our approach can be described as follows. From an informal description, we construct a formal specification in terms of graphs called Signal Transition Graphs (STGs), a form of interpreted Petri nets. STGs can be considered as a higher level form of representation compared to FSMs in the following sense: from a STG, one can obtain a set of sequences of signal transitions which represent the behavior of a circuit; each transition in every sequence corresponds to a control event of a system. Under certain conditions, such a set of sequences forms a regular set, that is, it has an equivalent representation by a finite automaton. This finite automaton can be used as a basis for implementation, as illustrated in the right branch of Fig. 2.1a. Thus, STGs serve as a more abstract and succinct way of representing finite automata with certain desirable properties. STGs are more abstract because these representations use transitions and a binary relation called the causal relation between transitions to describe behavior; the concept of state does not appear explicitly. Because of this, concurrency and other control situations can be described in very compact form. STGs are more succinct because they do not require a large number of states to describe concurrent occurrences of control events, in contrast to the case of finite automata.

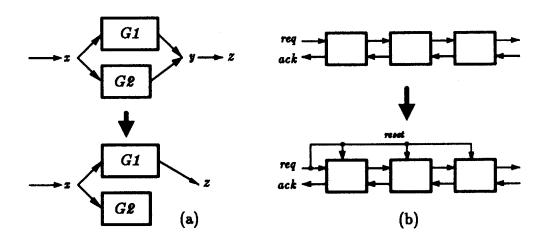

Figure 2.1: (a) Two approaches for synthesis of control circuits. (b) A technique for guaranteeing correctness of implementation from high level specifications.

The finite automata derived from STGs are a form of interpreted finite automata called state graphs, in which states are interpreted as binary vectors of signal values and transitions between states as signal transitions. State graphs can capture fundamental properties of logic circuits—most importantly the deadlock-free and hazard-free properties. These correspond to the properties of liveness and persistency, respectively. Since at the higher level of representation of STGs, we do not deal with these low level issues directly, we need to develop some method to ensure correct implementation. Our strategy is as follows: First, we study how fundamental properties of digital circuits can be characterized in terms of state graphs. Then, by establishing a unique correspondence between STGs and their state graph representations, these properties can be formalized as syntactic properties of STGs, which can in turns be verified and satisfied at this level of specification. Hence, by developing corresponding syntactic conditions for liveness and persistency for STGs, we have a means for ensuring the correctness of an implementation from an abstract level of specification. This idea is illustrated in Fig. 2.1b.

Another basic notion of our approach is that of behavioral equivalence. Some of the previous approaches have used Petri nets not only as a specification but also as a direct basis for implementation, in the sense that the structure of a net is directly transferred to hardware. In constrast, we use nets only as a behavioral specification from which a set of transition sequences with certain properties can be derived. Thus nets are considered as language generating devices. Even though this idea has often been studied from the viewpoint of formal language theory, our concern is much more focused and limited to direct and practical applications.

This chapter gives an informal introduction to Petri net theory and summarizes a number of new results, including a simple method for determining the set of transition sequences and its equivalent finite automaton directly from the structure of a net, and a syntactic characterization of the temporal relation between transitions in a net. These results can be applied to STGs as they are merely a form of interpreted Petri nets. The chapter describes properties of state graphs, liveness and persistency, and their equivalent characterization in STGs. Lastly, it presents a method of decomposition based on the notion of contraction; such a decomposition technique is the key to efficient implementation.

## 2.1 Petri Nets and Signal Transition Graphs

#### 2.1.1 Petri nets

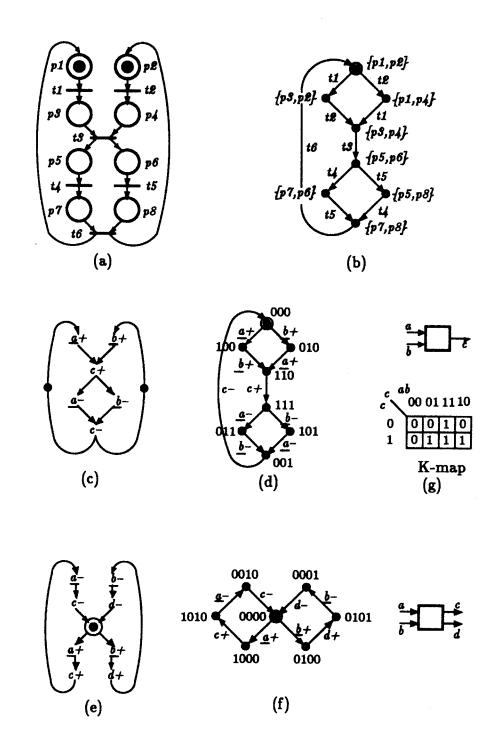

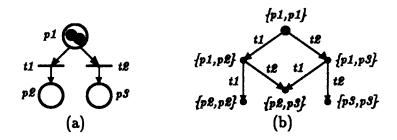

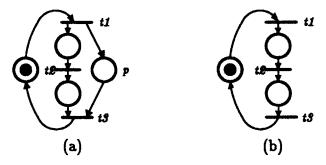

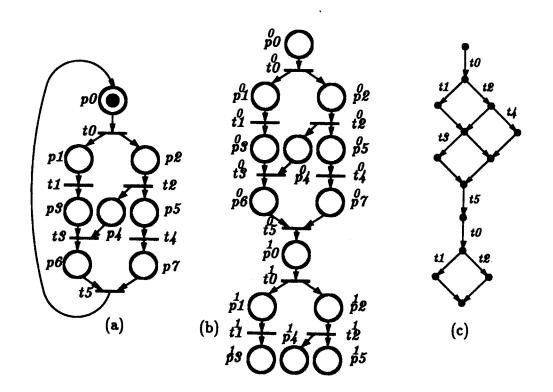

A Petri net is a bipartite directed graph, consisting of a finite set of transitions T, a finite set of places P and a flow relation  $F \subseteq P \times T \cup T \times P$  specifying a binary relation between transitions and places. A net is shown in Fig. 2.2a, in which transitions are drawn as bars, places as circles, and the flow relation as directed arcs. One common restriction is that a net be strongly connected in the graph-theoretic sense.

Transitions can usually be interpreted as certain events in a control system, while places as the local conditions which become true or cease to be true due to the occurrence of some actions, as specified by the flow relation. A transition has input and output places, e.g.  $p_3$ ,  $p_4$  are input places of  $t_3$ ;  $p_5$ ,  $p_6$  its output places. Similarly, a place has input and output transitions, e.g.  $t_1$  is the only input transition of  $p_3$ ,  $t_3$  its only output transition. The net in Fig. 2.2a is a particular instance of an important subclass of nets called marked graphs, capable of describing systems with deterministic concurrent operation.

A net as presented above describes the static structure of a control system. Its dynamic behavior is captured by its markings and the firing rule which transforms one marking to another. A marking M is a collection of places corresponding to the local conditions which hold at a particular moment; it is represented graphically as solid circles called tokens residing in these places. The initial marking is denoted as  $M_0$ ; in Fig. 2.2a,  $M_0$  corresponds to  $\{p_1, p_2\}$ . The firing rule is the rule for "executing" a net: A transition is enabled if each of its input places contains at least one token. An enabled transition may

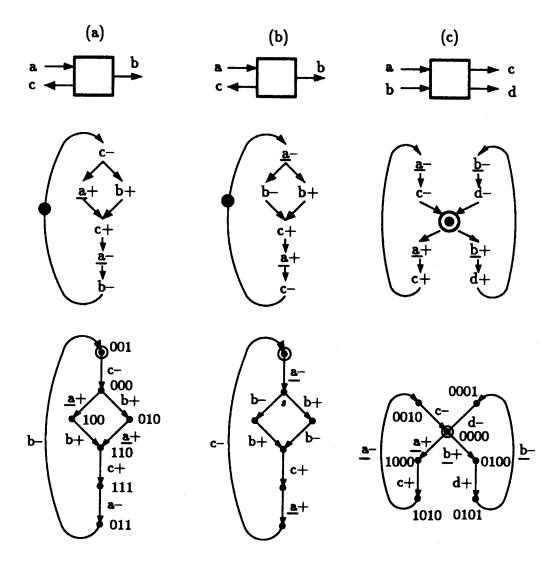

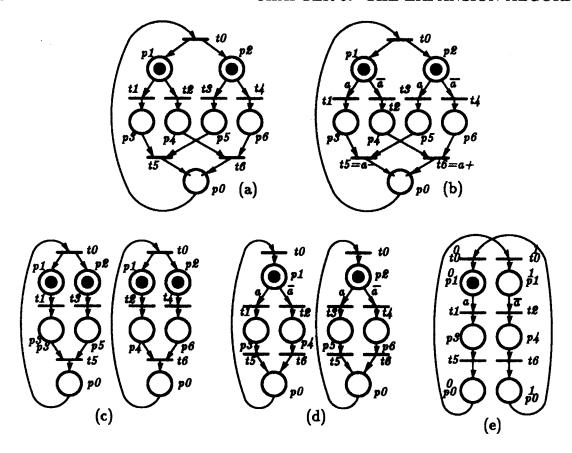

Figure 2.2: (a) A Petri net and (b) its reachability graph. (c) A STG which is an interpreted net of the net in (a), and (d) its state graph. (e) A STG of a circuit with input choices and (f) its state graph.

occur or fire; its firing consumes one token from each input place and puts one token in each output place. In Fig. 2.2a, both transitions  $t_1, t_2$  are enabled in the initial marking  $M_0$ , the firing of  $t_1$  moves the token from  $p_1$  to  $p_3$ , the firing of  $t_2$  moves the token from  $p_2$  to  $p_4$ .

The result of the execution of the net can be described by a form of interpreted finite automata called reachability graphs, as shown in Fig. 2.2b. Each node represents a state corresponding to a marking of the net; a labeled arc between nodes indicates the transition from one marking to another due to the firing of an enabled transition. Also, the initial state (corresponding to the initial marking of the net) is circled.

This example illustrates two important points. First, unlike the FSM model, nets can specify concurrent control actions: if two transitions are enabled in the same marking and the firing of one does not interfere with the enabling condition of the other, given enough time, both transitions will eventually fire. In Fig. 2.2a, the fact that  $t_1$  and  $t_2$  are concurrent means that both transition sequences (or firing sequences) ...  $t_1t_2$ ... and ...  $t_2t_1$ ... are possible; they show up in the reachability graph of the net. Secondly, the net's operation is totally asynchronous, as the firing of transitions depends solely on the availabity of tokens at their input places.

We will stress the transition sequence semantics of nets: a net defines a set of transition sequences. For example, the set of sequences specified by the net in Fig. 2.2a can be given by a regular expression

$$((t_1||t_2)t_3(t_4||t_5)t_6)^*,$$

where for transitions a and b, a||b (concurrent composition) denotes the set  $\{ab, ba\}$ , ab (concatenation) denotes  $\{ab\}$  and  $a^*$  (Kleene closure) denotes  $\{\epsilon, a, aa, \ldots\}$ ;  $\epsilon$  is the *empty* sequence.

#### Properties of nets

Two important behavioral properties of a net with an initial marking are safeness and liveness, defined as follows. For a net with an initial marking  $M_0$ , it is safe iff in any marking reachable from  $M_0$ , every place contains no more than one token. For our purpose, only finite safe nets are of practical interest. A finite safe net is live iff its reachability graph is strongly connected and each transition in T is enabled in some marking of the reachability

Figure 2.3: (a) An unsafe net and (b) its reachability graph.

graph. Note that this restrictive notion of liveness applies only to finite safe nets, and further it requires that all markings be reproducible.<sup>1</sup> The purpose of this requirement is to permit one to disregard the transient behavior during initialization of nets.

We consider safeness as a fundamental restriction on nets; without it one cannot relate the structure of a net to the actual behavior which the net intends to describe. Fig. 2.3a is a simple example of an unsafe net, whose structure is intended to specify a choice between control actions  $t_1$  and  $t_2$ . This would have been the case had place  $p_1$  contained only one token. However, due to the fact that place  $p_1$  contains two tokens,  $t_1$  and  $t_2$  each can fire twice consecutively, or both of them can fire concurrently. This behavior is recorded in the reachability graph shown in Fig.2.3b, with each marking described by a multiset of marked places (instead of a set) due to the multiplicity of tokens in the places.

Unsafe nets create another fundamental problem in that the set of transition sequences derived from an unsafe net may not have an equivalent finite automata (FA) representation in case the number of tokens in any place grows without bound.

#### Subclasses of nets and Structure theory

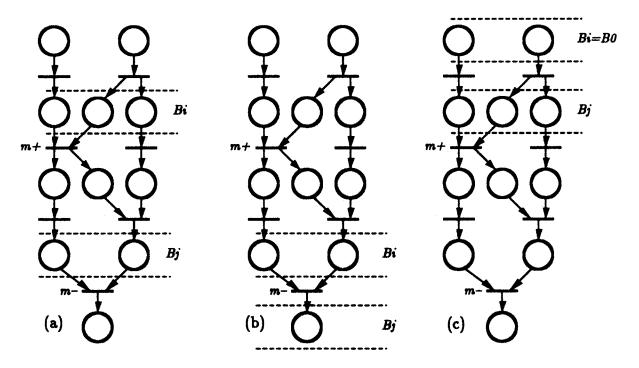

We will be concerned with three important subclasses of nets called marked graphs (MG), state machines (SM) and free-choice (FC) nets. A marked graph is a net in which each place has at most one input transition and at most one output transition. Marked graphs represent the structure of deterministic concurrent systems. The dual notion of marked graphs is that of state machines. A state machine is a net in which each transition has at most one input place and at most one output place. State machines represent the

In Fig. 2.4a, the initial marking  $\{p_1, p_4\}$  is a live-safe one; however, this marking is not reproducible.

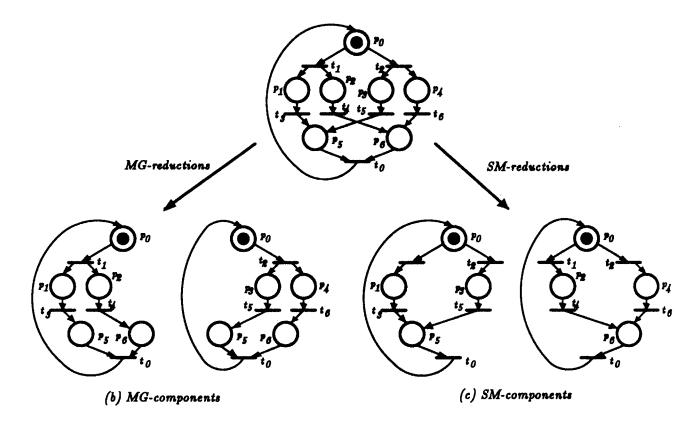

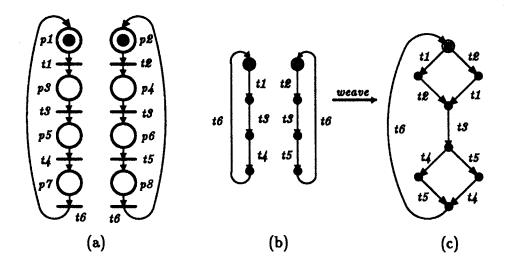

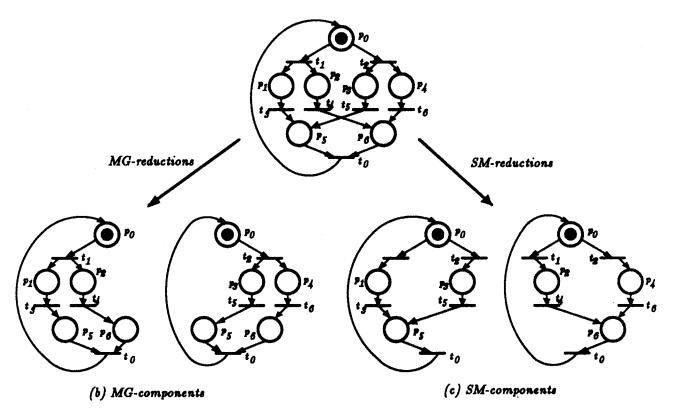

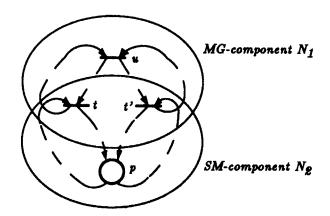

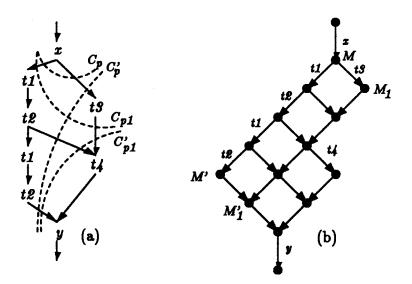

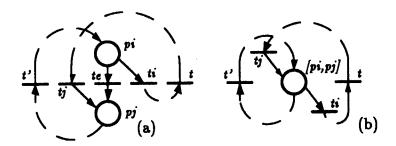

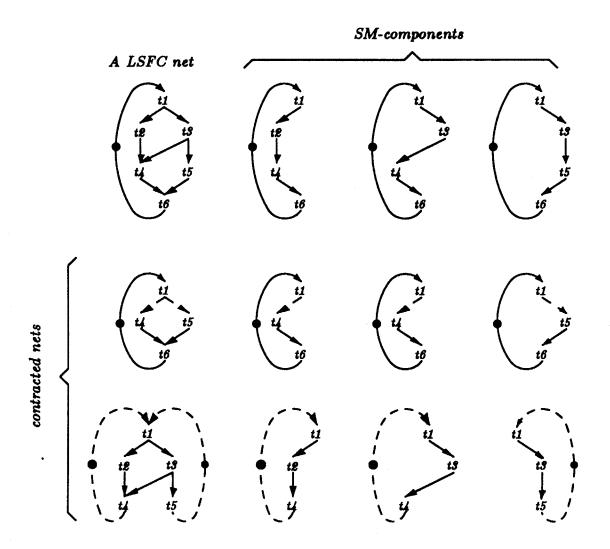

Figure 2.4: (a) A LSFC net, (b) its MG-components resulting from MG-reductions and (c) its SM-components resulting from SM-reductions.

structure of nondeterministic sequential systems. A free-choice net is a net such that if any two transitions  $t_1$  and  $t_2$  share the same input place p, then p is the unique input place of both  $t_1$  and  $t_2$ . Examples are shown in Fig. 2.4, where (a) is a FC net, (b) consists of marked graphs and (c) of state machines. We will restrict ourselves to a subclass of FC Petri nets as specifications of control systems which exhibit concurrent operations. FC nets represent an appropriate blend of concurrency and choice in specifying behaviors of circuits, and at the same time can be analyzed without much difficulty.

Structure theory is a branch of net theory which emphasizes the relationship between the structure (syntax) of nets and their behavior (semantics). In our view, structure theory is vital to the practical use of nets, for it allows the characterization of dynamic properties of nets in terms of static (syntactic) ones. Hack [24] has devised a reduction algorithm which allows the decomposition of a free-choice net into sets of structural components: a FC net can be decomposed into a set of state-machine (SM) components or a set of

marked graph (MG) components, as shown in Fig. 2.4. An important theorem developed by Hack which is the cornerstone of the structure theory of Petri nets can be informally stated as follows. If a FC net is live and safe, then the set of MG-components resulting from MG-reductions covers the net. Alternatively, the set of SM-components resulting from SM-reductions also covers the net. On the other hand, if a FC net is either nonlive or unsafe, then some reduction does not cover the net or is empty, or some component is not strongly connected. For example, the FC net in Fig.2.4 is live-safe and its SM-and MG-components both cover the net.

Hence, by using this theorem, we can determine if a net is live-safe by decomposing it into structural components. Later chapters describe more fully other important applications of this theorem. Specifically, by using Hack's theorem, we developed techniques for constructing a finite automaton directly from the structure of a net, and a syntactic characterization of the temporal relation, as will be described below.

#### 2.1.2 Signal Transition Graphs

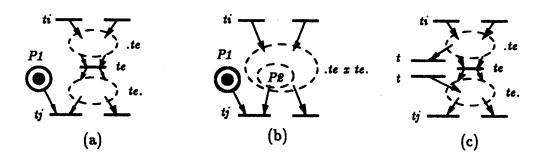

For the purpose of specifying behaviors of digital control circuits, we use a form of interpreted Petri nets called Signal Transition Graphs (STGs), which are nets with transitions interpreted as rising and falling transitions of signals of a control circuit. Fig. 2.4c shows an example of a STG of a circuit with the set of signals denoted by  $J = \{a, b, c\}$ . This STG is one interpretation of the net in Fig. 2.2a, where the set of transitions T is interpreted as the set of signal transitions  $J \times \{+, -\}$ . Since a control circuit has input, internal and output signals, we partition the set of signal transitions in the same way, and in the graphical representation, transitions of input signals are underlined. The fundamental difference between transitions of input and non-input (= internal + output) signals is that the former are caused by the external environment while the latter by the system.

For simplicity, in a STG, we represent each transition by its name instead of using a bar with a label. Another important graphical abbreviation for STGs is that every place with one input and one output transition is not drawn explicitly; instead an arc is drawn directly between these transitions. Such an arc directly represents an instance of the causal relation, denoted by R, between transitions; informally,  $t_1Rt_2$  (read  $t_1$  causes  $t_2$ ) can be understood as: the firing of  $t_1$  brings the system into a state (marking) in which  $t_2$  is

enabled (and hence may fire).

The reason for using the causal relation and ignoring places with one input and one output transitions is that, from the viewpoint of firing sequence semantics, the behavior of a net (or STG) is adequately defined by its set of transition sequences. For a sufficiently expressive class of nets called live-safe free-choice (LSFC) nets, we will be able to show that their sets of firing sequences are regular in the sense that the latter have equivalent finite automata representations. For example, the STG in Fig. 2.2c defines a set of sequences which has the equivalent finite automaton (FA) shown in Fig. 2.2d, which is isomorphic to the reachability graph of Fig. 2.2b. This FA can be interpreted into a state graph by (i) identifying transitions between states with signal transitions and (ii) assigning binary vectors representing the values of signals in the circuit to nodes. For state graphs, this state assignment is very simple and can be carried out mechanically, as will be described later.

The STG in Fig. 2.2c specifies the behavior of a control circuit with deterministic concurrent operation. Fig. 2.2e shows another STG specification of a trivial circuit with *input choices*; its state graph is shown in Fig. 2.2f. The input choice is specified by a place with two output transitions  $a_+$  and  $b_+$ , which are transitions of input signals a and b. Whenever p is marked, then both output transitions are enabled and one is chosen nondeterministically to fire; its firing will *disable* the other transition. In Petri nets, such a situation is called a *free choice*. In STGs, we limit output transitions of a free-choice place to those of input signals because internal to a system, a choice made externally would appear as if it is nondeterministic.

We have the following important remarks concerning the formalization of STGs as interpreted Petri nets.

First, STGs are nets with interpreted transitions but places have no interpretation; in particular, we do not interpret places as states of signals resulting from the firing of signal transitions. The reason is illustrated in the following example. In Fig. 2.2a, transition  $t_1$  is interpreted as  $a_+$ . Suppose further that its output place  $p_3$  is interpreted as signal a becoming a logical "1". Then whenever  $t_1$  fires, indicating a positive transition of a, place  $p_3$  is marked with a token indicating that signal a has become 1. Note, however, than when  $t_3$  fires subsequently, this token is taken away, implying that signal a is no longer at value 1. In reality this is not true because the value of a will not change until  $a_-$  occurs.

This is an important observation to which we shall return later.

Second, despite the fact that STGs are interpreted nets, we have chosen to call our graph model Signal Transition *Graphs*, rather than *Nets*, in order to emphasize the important role of the static structure of nets in our application. A Petri net can be viewed as consisting of an underlying structure which is a graph, and a marking which indicates the distribution of tokens in the graph at some moment. Structure theory, as mentioned earlier, allows the direct association of static net structures to their underlying semantics. This thesis develops a number of techniques for manipulating the structure of nets (with little concerns about markings) which allow direct synthesis of the underlying finite automata.

## 2.1.3 Relation between Petri nets and Signal Transition Graphs

It is important to note that STGs can be considered simply as a class of LSFC nets with certain structural restrictions due to the interpretation of transitions. One such restriction is that STGs always contain an even number of transitions due to the fact that associated with every signal is a pair of signal transitions. Another restriction arises from the need to simulate the interface behavior of a control circuit: in a STG, if t is a transition of an input signal, then we require that t have exactly one transition, say t', which causes it: t'Rt; furthermore, t' must be a transition of an output signal. In Fig. 2.2c, each transition of input signals a, b is caused by exactly one transition of output signal c. There are other restrictions which we will present later.

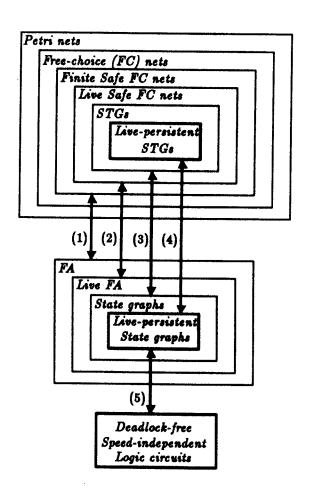

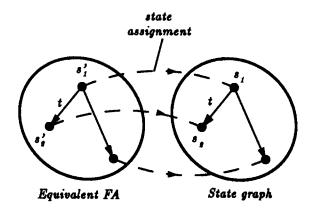

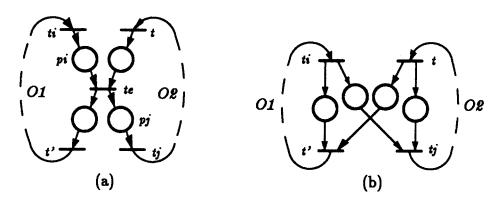

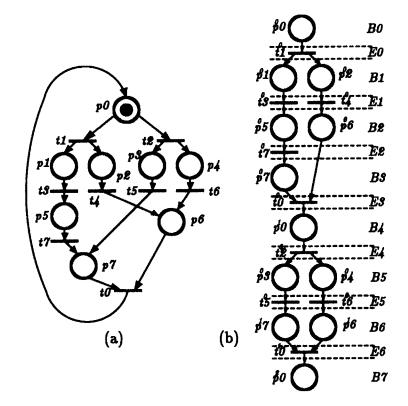

Just as a STG is an interpreted net, its state graph is an interpreted FA which can be obtained in a similar fashion as reachability graphs. The relationship between nets, STGs and state graphs is depicted in Fig. 2.5. The top part of this figure is a syntactic or structural classification of nets. For instance, the class of FC nets is a subset of the class of Petri nets, and so on. LSFC nets are a subclass of FC nets, with the properties of live-safeness characterized structurally by Hack's reduction theorem mentioned at the end of Section 2.1.1. STGs constitute a subclass of LSFC nets. The subset of live-persistent STGs corresponds to those STGs whose state graphs are live and persistent. Live and persistent state graphs can be transformed into deadlock-free and hazard-free (speed-independent) logic circuits, as indicated by arrow (5).

The middle part of Fig. 2.5 contains classes of finite automata, which can be considered

Figure 2.5: Structural classification of classes of nets and their equivalent finite automata.

as the low-level semantics of nets. The two-headed arrows indicate the equivalence between them and classes of nets. Earlier, we stated that safe nets have equivalent FA representations; such an equivalence is indicated by arrow (1) for finite safe FC nets. The class of LSFC nets have equivalent FA which are live, as indicated by arrow (2), this equivalence is the subject of investigation of Section 2. Of main interest in Fig. 2.5 is the equivalence indicated by arrow (4) between live-persistent STGs and state graphs; this equivalence is studied in Section 3.

It is crucial to realize that while safeness can be considered purely as a net-syntactic property, liveness and persistency are defined as properties of finite automata. Thus, live-safe FC nets are safe FC nets whose FA are live; similarly, live-persistent STGs are STGs whose state graphs are live and persistent. The important point is that even though liveness and persistency are defined as properties of state graphs, one can derive the equivalent syntactic conditions for STGs, just as in the case of LSFC nets. For LSFC nets, the syntactic conditions for live and safeness are stated in Hack's decomposition theorem.

# 2.2 Semantics of nets/Behavioral equivalence

There are two approaches to defining the semantics of Petri nets: one based on sequences of transitions (firing sequences), the other on partial orders of transitions and places. For safe nets, their semantics can be given both in terms of firing sequences and partial orders: By using the firing rule and an initial marking, one can simulate the operation of a Petri net to obtain the firing sequences; on the other hand, Petri nets can be unfolded into partial orders called *processes* [23].

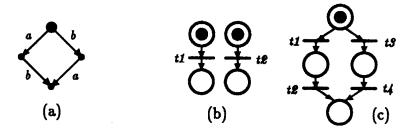

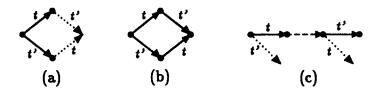

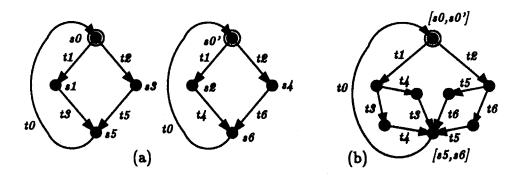

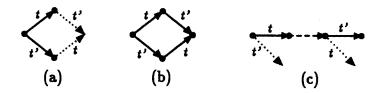

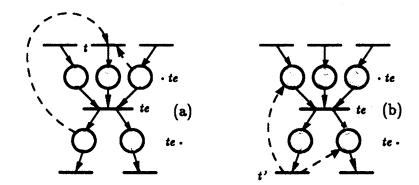

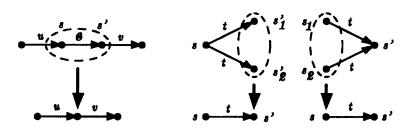

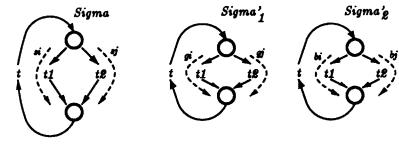

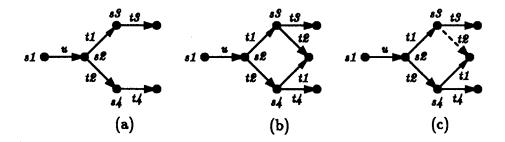

We will be mainly interested in the firing sequence semantics of Petri nets. One frequently cited problem with using firing sequence semantics is illustrated in the following: Given a set of firing sequences describing the behavior of a very simple system  $\{ab, ba\}$  (Fig. 2.6a), it is unclear whether this set corresponds to a net in which a and b are concurrent (Fig. 2.6b) or in conflict (Fig. 2.6c), where all transitions are labeled.

It is clear that this problem arises due to the labeling of two transitions with the same labels in Fig. 2.6c. If such a labeling is disallowed, problems of this kind will never arise and the system  $\{ab, ba\}$  always corresponds to the case of *concurrency*. Hence we allow

Figure 2.6: (a) The equivalent FA of the set  $\{ab, ba\}$  and two interpretations: (b) concurrency, where  $\gamma(t_1) = a$ ,  $\gamma(t_2) = b$ ;  $\gamma$  is a *labeling* function, (c) conflict, where  $\gamma(t_1) = \gamma(t_4) = a$ ,  $\gamma(t_2) = \gamma(t_3) = b$ .

only unlabeled transition sequences. In the formulation of STGs, instead of using a labeling function to label transitions of a net with signal transitions, i.e.  $\gamma: T \to J \times \{+, -\}$ , we have chosen to make a direct interpretation:  $T = J \times \{+, -\}$  to avoid the problem just mentioned.

# 2.2.1 Behavioral Equivalence

For our purpose of synthesis from net specifications, the main advantage of using sequence semantics is that it allows freedom in the implementation from a specification. Given a net specification of a control systems, any other net which exhibits the same set of transition sequences as the original one is considered equivalent to it; this is the notion of behavioral equivalence. The like notion of "structural equivalence" is not a particular useful one, as it requires two nets which are equivalent in this sense to have identical structures. The simple example in Fig. 2.7 shows two nets which are behavioral equivalent but not so structurally. If one is concerned only about the behavior (in terms of transition sequences), then the net in Fig. 2.7a contains a redundant place which can be removed without altering the net's behavior.

From a technical point of view, sequence semantics are easier to handle than semantics based on processes. As will be made clear in this thesis, most results for LSFC nets are proven by considering their sets of transition sequences. These include important properties such as liveness, and properties concerning the composition and decomposition of nets.

Figure 2.7: Two nets which are behaviorally equivalent.

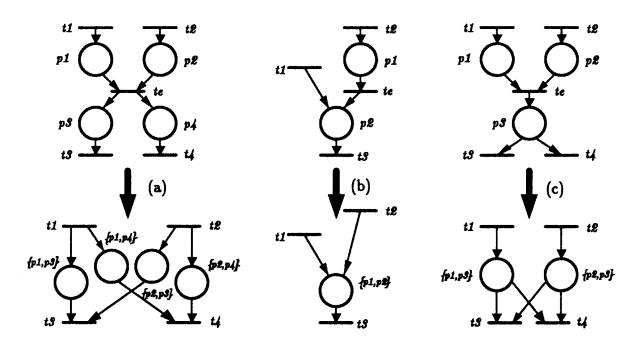

### 2.2.2 Important Analytical Results for Nets

In this section, we summarize a number of fundamental results which are proven in Chapter 3. These results serve as the basis for later developments. One important result is the following

The set of firing sequences of a LSFC net is regular, i.e. it has an equivalent finite automata representation.

### Algorithm for constructing finite automata for LSFC nets

The above result is proven by demonstrating a procedure for constructing an equivalent automaton from a LSFC net; the basis for such a construction algorithm is given by the following result (Theorem 3.8):

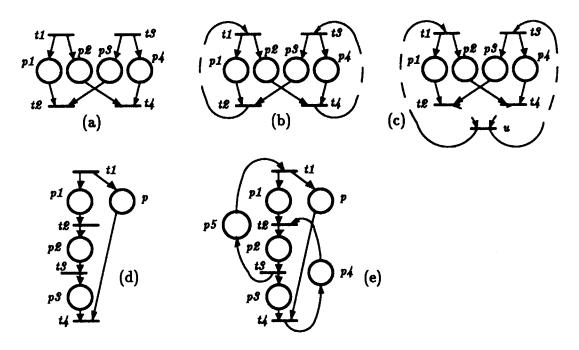

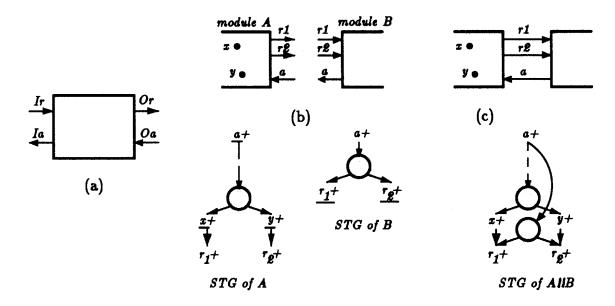

The equivalent finite automaton of a LSFC net is obtained by weaving (concurrent-composing) the finite automata of a set of SM-components which cover the net.

Note that a FA equivalent to a state machine is identical to the state machine itself and hence, can be readily derived from the SM-components of a LSFC net. Let  $FS_1$  and  $FS_2$  denote sets of transition sequences of two finite automata  $FA_1$  and  $FA_2$ , respectively. The weave of  $FS_1$  and  $FS_2$  is defined as (Def. 3.7)

$$FS_1||FS_2 = \{\sigma \in (T_1 \cup T_2)^* \mid \sigma \lceil T_1 \in FS_1 \land \sigma \lceil T_2 \in FS_2 \},$$

Figure 2.8: (a) The set of covering SM-components for the net in Fig. 2.2a. (b) The equivalent FA of the SM-components and (c) their weave, which results in the equivalent FA of the net in Fig. 2.2a.

where  $T_1$  and  $T_2$  are sets of transitions of the FA;  $\sigma \lceil T_i \rceil$  denotes the *projection* of a sequence  $\sigma$  onto the set  $T_i$ . The weave of two FA,  $FA_1 || FA_2$ , is defined as a FA whose set of transition sequences is given by  $FS_1 || FS_2$ .

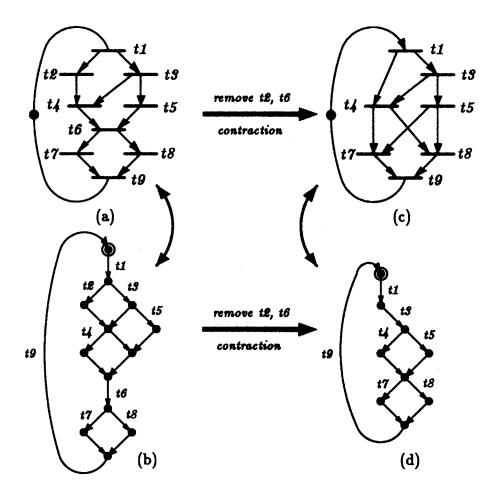

The marked graph in Fig. 2.2a is a special case of LSFC nets, which can be decomposed into a set of covering SM-components (Fig. 2.8a), each being a simple cycle containing one token. The FA corresponding to these SM-components are shown in Fig. 2.8b; their weave results in the FA for the marked graph, as indicated in Fig. 2.8c.

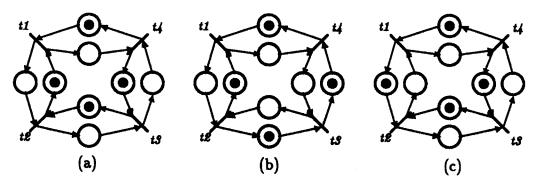

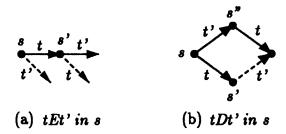

#### Temporal relation in LSFC nets

Another result of fundamental importance developed in this thesis could be categorized as a result in the structure theory of Petri nets. Given a LSFC net, it is generally not possible to tell whether two transitions are ordered or concurrent merely by inspecting the structure of the net. For instance, the marked graph shown in Fig. 2.9 (called a *necklace* of length 4) has three different initial markings as indicated, each resulting in a distinct set of firing sequences; that is, this net has three equivalent classes of live-safe markings—every two markings in each class are mutually reachable. In case (a), the set of firing sequences is given by the expression  $(t_1t_2t_3t_4)^*$ ; in case (b), it is  $(t_1t_4t_3t_2)^*$ ; lastly in case (c), it is

Figure 2.9: (a) A FC net with three different equivalent classes of live-safe markings. Some of its SM-components contain two or three tokens.

$t_2((t_1||t_3)(t_2||t_4))^*$ . In cases (a) and (b) all transitions are ordered, even though they are ordered in different ways. In case (c),  $t_1$  and  $t_3$  are concurrent, and so are  $t_2$  and  $t_4$ . For each of these cases, there exists a set of covering SM-components which are simple cycles with one token. Note, however, that there are also cycles with two or three tokens. Since by definition a state machine net must contains exactly one token, such a cycle with two tokens is not a legitimate SM-component.

In order to allow for syntactic characterization of the temporal relation between transitions in a net, we shall make the following fundamental restriction. The original result by Hack, as described in his Well-formedness theorem, states that a FC net is live-safe iff when SM-reductions are applied to it (i) every SM-reduction is a collection of one or more marked SM-components and (ii) the reductions cover the net. Note that this condition does not require that every SM-component of the net contains one token each; it is possible for some SM-components to contain more than one token, as illustrated by the example above.

Our temporal characterization based on syntax only works for nets which satisfy the one-token SM restriction:

Every SM-component of a LSFC net contains exactly one token.

Hence, if net satisfies this restriction, any of its SM-components containing more than one token is unsafe and will cause the net to be unsafe. In this thesis, we will be mainly interested in LSFC nets which meet this restriction. This is not as restrictive as it seems: