#### MIT/LCS/TR-644

## Mechanisms and Interfaces for Software-Extended Coherent Shared Memory

by

## David L. Chaiken

Sc.B., Brown University (1986) S.M., Massachusetts Institute of Technology (1990)

Submitted to the

Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 1994

| Massachusetts Institute of Technology 1994, 1995. All rights reserved. |

|------------------------------------------------------------------------|

|                                                                        |

|                                                                        |

|                                                                        |

| uthor                                                                  |

| Department of Electrical Engineering and Computer Science              |

| September 1, 1994                                                      |

| ertified by                                                            |

| Anant Agarwal                                                          |

| Associate Professor of Electrical Engineering and Computer Science     |

| Thesis Supervisor                                                      |

| accepted by                                                            |

| •                                                                      |

| Frederic R. Morgenthaler                                               |

Chair, Department Committee on Graduate Students

# Mechanisms and Interfaces for Software-Extended Coherent Shared Memory

by

David L. Chaiken

#### **Abstract**

Software-extended systems use a combination of hardware and software to implement shared memory on large-scale multiprocessors. Hardware mechanisms accelerate common-case accesses, while software handles exceptional events. In order to provide fast memory access, this design strategy requires appropriate hardware mechanisms including caches, location-independent addressing, limited directories, processor access to the network, and a memory-system interrupt. Software-extended systems benefit from the flexibility of software, but they require a well-designed interface between their hardware and software components to do so.

This dissertation proposes, designs, tests, measures, and models the novel software-extended memory system of Alewife, a large-scale multiprocessor architecture. A working Alewife machine validates the design, and detailed simulations of the architecture (with up to 256 processors) show the cost versus performance trade-offs involved in building distributed shared memory. The architecture with a five-pointer LimitLESS directory achieves between 71% and 100% of full-map directory performance at a constant cost per processing element.

A worker-set model uses a description of application behavior and architectural mechanisms to predict the performance of software-extended systems. The model shows that software-extended systems exhibit little sensitivity to trap latency and memory-system code efficiency, as long as they implement a minimum of one directory pointer in hardware. Low-cost, software-only directories with no hardware pointers are very sensitive to trap latency and code efficiency, even in systems that implement special optimizations for intranode accesses.

Alewife's *flexible coherence interface* facilitates the development of memory-system software and enables a smart memory system, which uses intelligence to help improve performance. This type of system uses information about applications' dynamic use of shared memory to optimize performance, with and without help from programmers. An automatic optimization technique transmits information about memory usage from the runtime system to the compiler. The compiler uses this information to optimize accesses to widely-shared, read-only data and improves one benchmark's performance by 22%. Other smart memory features include human-readable profiles of shared-memory accesses and protocols that adapt dynamically to memory reference patterns.

**Keywords:** multiprocessor, parallel processing, shared memory, cache coherence, computer architecture simulation, worker set, smart memory

Thesis Supervisor: Anant Agarwal

Title: Associate Professor of Electrical Engineering and Computer Science

### Acknowledgments

When I entered MIT, Anant Agarwal was a young, enthusiastic professor and I was a young, naïve graduate student. Six years later, Anant is still a young, enthusiastic professor. I feel privileged to have been one of his first students at MIT and attribute much of my success to his guidance.

Frans Kaashoek and Greg Papadopoulos served on my thesis committee, and gave helpful comments, criticism, and encouragement throughout the process. Their insistence that I understand the design space led me to develop the model in Chapter 7. Frans has helped me improve my understanding and documentation of the flexible coherence interface. Greg has voiced the concerns of industry that I attempt to address in this dissertation.

The members of the Alewife group have been work-mates and friends for the last six years. John Kubiatowicz and I worked head-to-head on the Alewife architecture for the majority of that time. Kubi designed and implemented the A-1000 CMMU, which is the heart of the LimitLESS system. As the compiler guru of the Alewife project, David Kranz taught me a lot about building the software for a large system. I thoroughly enjoyed hacking NWO and the Alewife kernel with David. Beng-Hong Lim has shared an office with me during our entire stay at MIT. He often provided the only calm voice in Alewife design meetings. I will miss Beng when we part ways. Dan Nussbaum tried his best to convey his system-building experience to the younger members of the group, and to restrain our over-enthusiastic ambitions. David, Beng-Hong, and Dan were responsible for the Sparcle simulator modules of ASIM and NWO.

Kirk Johnson and Chris Metcalf created a stable computation environment for the entire Computer Architecture Group. Since they provided this essential service, I can almost forgive them for getting me addicted to netrek. On many occasions, Kirk has given me helpful insight into designing systems and evaluating their performance.

Ken Mackenzie and Don Yeung designed Alewife's packaging and built the system's hardware. They humored me by allowing me to plug together some components every now and then. Gino Maa showed me the ropes at MIT and helped me start the early phases of this research. Anne McCarthy has run the Alewife group for several years. Her administration allows the rest of the group to concentrate on research rather than logistics. Ricardo Bianchini has provided useful suggestions from the point of view of Alewife's most prolific user. Sramana Mitra motivated me to improve the functionality in NWO and tested the simulator as she wrote the statistics interface for Alewife. Vijayaraghavan Soundararajan and Rajeev Barua shared the office with Beng and me: I thank them for putting up with me!

Kirk Johnson wrote and stabilized the programming environment for NWOP, the CM-5 version of NWO. Thanks go to Alan Mainwaring, Dave Douglas, and Thinking Machines Corporation for their generosity and assistance in porting NWO to the CM-5. Additional thanks to Thinking Machines Corporation (especially the folks who maintain the in-house machines) for allowing me to use many late-night CM-5 cycles during the results-generation phase of this research. Project Scout at MIT also provided a platform for some of the simulations.

A discussion with Johnny Piscitello during the summer of 1993 proved to be instru-

mental in the construction of the flexible coherence interface. Margo Seltzer suggested the comparison between Mach pmaps and the flexible coherence interface.

The notation for the transition state diagram in Chapter 4 borrows from the doctoral thesis of James Archibald at the University of Washington, Seattle, and from work done by Ingmar Vuong-Adlerberg at MIT.

It is no secret within the computer architecture community that similar, high-quality research is being conducted at Stanford University and the University of Wisconsin–Madison. The graduate students and professors in the research groups at these universities have kept me on my toes, reviewed my papers, given me good feedback on my work, and been fun companions at meals and baseball games.

If there is any text in this document that I did not write, it is in Sections 2.1.3 and 3.2.2. Section 2.1.3 describes the notation for software-extended protocols. Anant and I agonized over this notation, and he eventually wrote the documentation. This section is probably the most controversial in the dissertation. One reviewer expressed concern that "future protocol designers will extend this scheme in bizarre ways to name new protocols." However, the notation is the best that we could produce. It is terse, convenient, and expressive. The ability to extend a language construct in bizarre ways is possibly a feature, not a bug.

Section 3.2.2 documents the applications used to experiment with Alewife's software-extended memory system. Two researchers deserve much credit for making these benchmarks available: Beng-Hong Lim of MIT gathered and documented the application suite for Alewife, and J.P. Singh of Stanford compiled the SPLASH benchmark suite. In addition, Dan Nussbaum wrote TSP; Kirk Johnson wrote AQ; Beng-Hong Lim and Dan Nussbaum wrote SMGRID; and Anshu Aggarwal wrote EVOLVE.

The workloads used in Chapter 4 came from different sources. Harold Stone and Kimming So helped obtain the SIMPLE and Weather traces. The post-mortem scheduler was implemented by Mathews Cherian with Kimming So at IBM. It was extended by Kiyoshi Kurihara, who found the hot-spot variable in Weather. Gino Maa wrote the ASIM network simulator. G.N.S. Prasanna wrote and analyzed Matexpr.

Dick Larson invited me to visit MIT in 1987 and deserves credit for attracting me to the Institute.

Thanks to Digital Equipment Corporation and the members of the Systems Research Center for giving me a great reason to get on with my life.

Ema and Aba sat me down in front of a key-punch at the age of 4, and I haven't stopped hacking since then. I would like to thank them for teaching me the value of an education and the persistence needed to pursue my goals.

My deepest gratitude to Ora for support, encouragement, friendship, and love.

Praised are You, the Eternal, our God, Ruler of the Universe, who has graced us with life, sustained us, and allowed us to reach this season.

Machines used for simulations were provided by Digital Equipment Corporation, SUN Microsystems, and Thinking Machines Corporation. This research has been supported by NSF grant #MIP-9012773, ARPA grant #N00014-91-J-1698, and a fellowship from the Computer Measurement Group.

## **Contents**

| 1 | Sha  | red Mei | mory Design                                   | 14 |

|---|------|---------|-----------------------------------------------|----|

|   | 1.1  | Contri  | ibutions                                      | 16 |

|   | 1.2  | Organ   | ization                                       | 17 |

| 2 | Dist | ributed | Shared Memory                                 | 18 |

|   | 2.1  | Cache   | Coherence Protocols                           | 19 |

|   |      | 2.1.1   | The Processor Side                            | 20 |

|   |      | 2.1.2   | The Memory Side                               | 20 |

|   |      | 2.1.3   | A Spectrum of Protocols                       | 22 |

|   | 2.2  | Flexib  | le and Smart Memory Systems                   | 25 |

|   | 2.3  | Under   | standing Memory System Performance            | 26 |

| 3 | An A | Archite | ct's Workbench                                | 27 |

|   | 3.1  | The A   | lewife Architecture                           | 29 |

|   |      | 3.1.1   | ASIM: the Preliminary Simulator               | 30 |

|   |      | 3.1.2   | A-1000: the Alewife Machine                   | 32 |

|   |      | 3.1.3   | NWO: the Alewife Simulator                    | 33 |

|   |      | 3.1.4   | Comparing the Implementations                 | 35 |

|   | 3.2  | Applic  | cations                                       | 36 |

|   |      | 3.2.1   | WORKER: a Synthetic Workload                  | 36 |

|   |      | 3.2.2   | NWO/A-1000 Benchmarks                         | 38 |

| 4 | Cac  | he Coh  | erence in Alewife                             | 41 |

|   | 4.1  | Implei  | menting Directory Protocols                   | 41 |

|   |      | 4.1.1   | LimitLESS Cache Coherence                     | 42 |

|   |      | 4.1.2   | A Simple Model of the LimitLESS Protocol      | 42 |

|   |      | 4.1.3   | Background: Implementing a Full-Map Directory | 43 |

|   |      | 4.1.4   | Specification of the LimitLESS Scheme         | 45 |

|   |      | 4.1.5   | Second-Order Considerations                   | 48 |

|   |      | 4.1.6   | Evaluation of Secondary Protocol Features     | 50 |

|   | 4.2  | Prelim  | ninary Evaluation                             |    |

|   |      | 4.2.1   | Results                                       |    |

|   |      | 4.2.2   | Conclusion                                    |    |

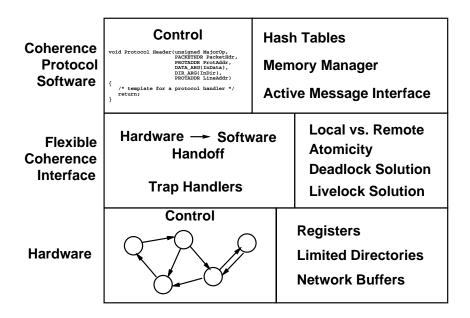

| 5 | Flex | ible Coherence Interface 55           |

|---|------|---------------------------------------|

|   | 5.1  | Challenges and Solutions              |

|   |      | 5.1.1 Representations                 |

|   |      | 5.1.2 Atomicity                       |

|   |      | 5.1.3 Livelock and Deadlock 61        |

|   | 5.2  | Experience with the Interface         |

|   | 5.3  | The Price of Flexibility              |

| 6 | Cost | t, Flexibility, and Performance 65    |

|   | 6.1  | Flexibility and Performance           |

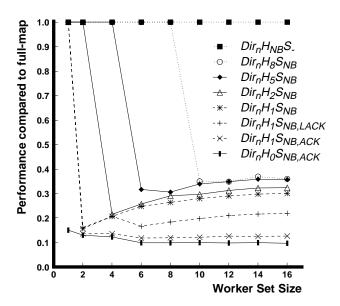

|   | 6.2  | Worker Sets and Performance           |

|   | 6.3  | Application Case Studies              |

|   | 6.4  | A-1000 Performance                    |

|   | 6.5  | Conclusions                           |

| 7 | The  | Worker-Set Model 78                   |

|   | 7.1  | Model Inputs and Outputs              |

|   |      | 7.1.1 Notation                        |

|   |      | 7.1.2 Application Parameters          |

|   |      | 7.1.3 Architecture Parameters         |

|   |      | 7.1.4 Performance Metric              |

|   | 7.2  | Model Calculations                    |

|   |      | 7.2.1 Calculating Utilization         |

|   |      | 7.2.2 Counting Events and Cycles      |

|   |      | 7.2.3 Restrictions and Inaccuracies   |

|   | 7.3  | Validating the Model                  |

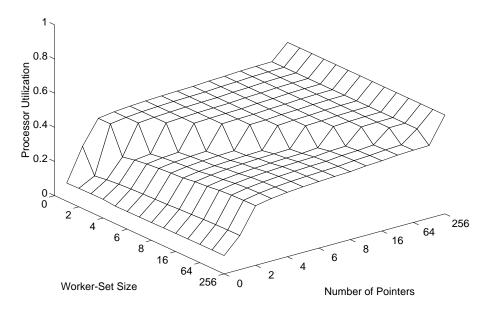

|   |      | 7.3.1 The WORKER Synthetic Workload   |

|   |      | 7.3.2 The Benchmarks                  |

|   | 7.4  | Model Predictions                     |

|   |      | 7.4.1 Trap Latency                    |

|   |      | 7.4.2 Code Efficiency                 |

|   |      | 7.4.3 Dedicated Memory Processors     |

|   |      | 7.4.4 Network Speed                   |

|   |      | 7.4.5 Protocol Implementation Details |

|   | 7.5  | Node Architecture                     |

|   |      | 7.5.1 Superscalar Processors          |

|   |      | 7.5.2 Multiple Processors per Node    |

|   | 7.6  | The Workload Space                    |

|   | 7.7  | Conclusions and an Open Question      |

| 8 | Sma  | art Memory Systems 119                |

|   | 8.1  | Challenges                            |

|   | 8.2  | Adaptive Broadcast Protocols          |

|   | 8.3  | The LimitLESS Profiler                |

|   |      | 8.3.1 The Profiler Interface          |

|   |                  | 8.3.2 Example of Use                          | 6 |

|---|------------------|-----------------------------------------------|---|

|   |                  | 8.3.3 Implementation                          | 6 |

|   | 8.4              | Profile, Detect, and Optimize                 | 7 |

|   |                  | 8.4.1 The PRODO Interface                     | 8 |

|   |                  | 8.4.2 Implementation                          | 8 |

|   |                  | 8.4.3 A Case Study                            | 0 |

|   |                  | 8.4.4 Architectural Mechanisms                | 1 |

|   | 8.5              | Hardware-Accelerated Coherent Shared Memory   | 2 |

| 9 | Con              | clusions 13                                   | 4 |

|   | 9.1              | Recommendations for Distributed Shared Memory | 4 |

|   | 9.2              | Future Work                                   | 5 |

| A | Exp              | erimental Data 13'                            | 7 |

|   | $A.\overline{1}$ | Simulation Measurements                       | 7 |

|   | A.2              | Model Parameters                              | 0 |

# **List of Figures**

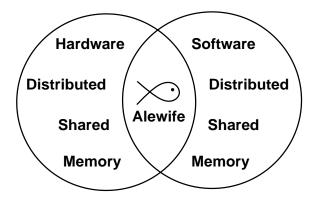

| 2-1                                                         | Alewife uses a hybrid approach to implement distributed shared memory.                                                                                                                                                                                                                                                                                                   | 19                                     |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5                             | Alewife node, with a $Dir_nH_2S_{NB}$ memory block. Diagram of ASIM, the Alewife system simulator. A-1000 node board: $12\text{cm} \times 22\text{cm}$ The hybrid simulation technique. The circular worker-set data structure for 8 nodes.                                                                                                                              | 29<br>31<br>32<br>34<br>37             |

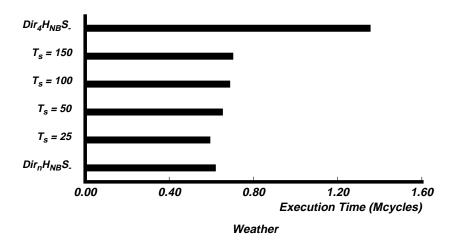

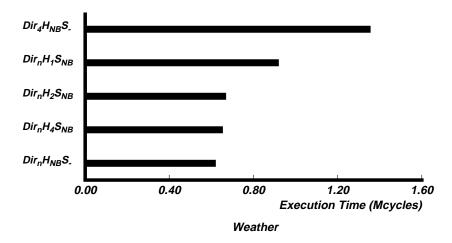

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5                             | Full-map and limited directory entries                                                                                                                                                                                                                                                                                                                                   | 44<br>47<br>53<br>53<br>54             |

| 5-1<br>5-2                                                  | Hardware, interface, and software layers of a memory system Sample protocol message handler                                                                                                                                                                                                                                                                              | 56<br>58                               |

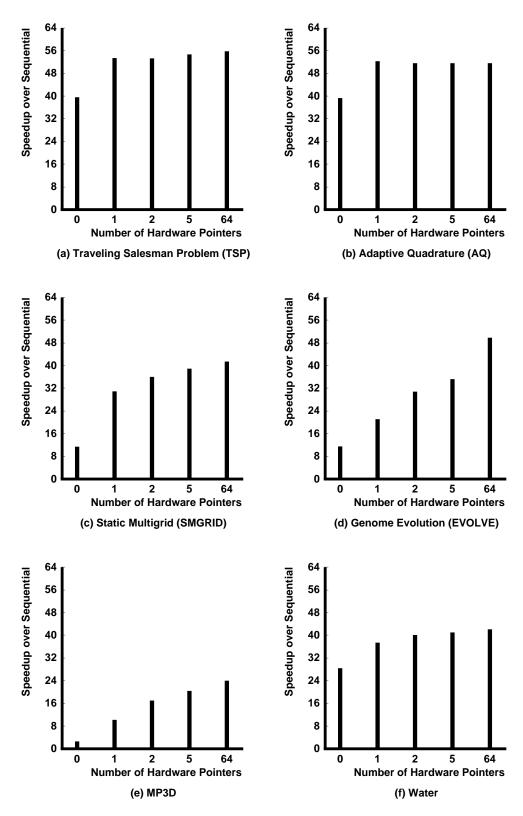

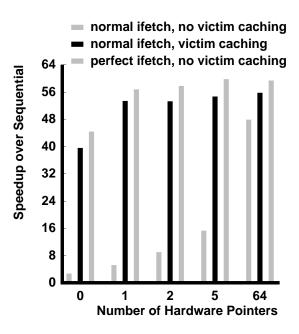

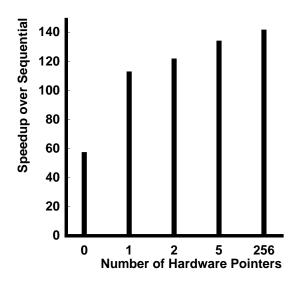

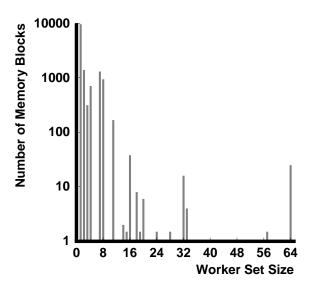

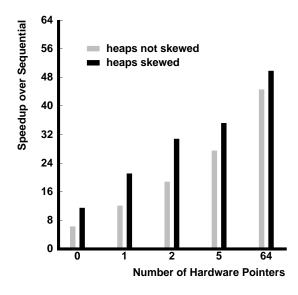

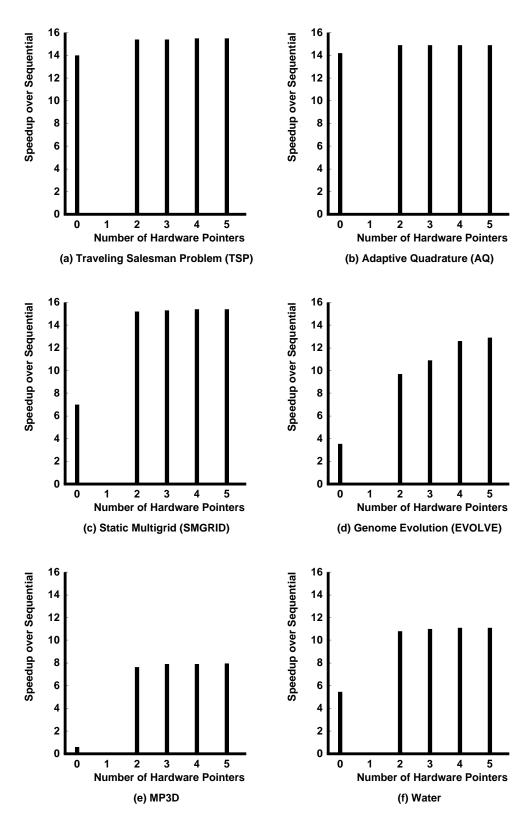

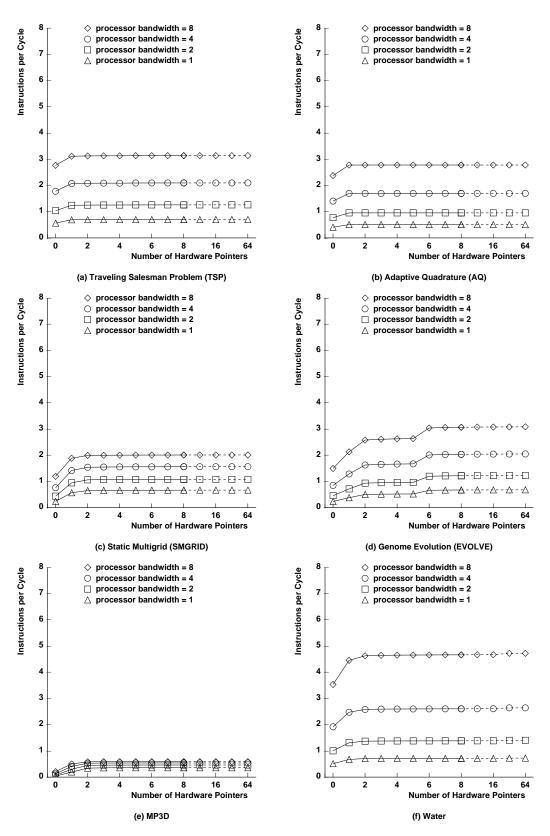

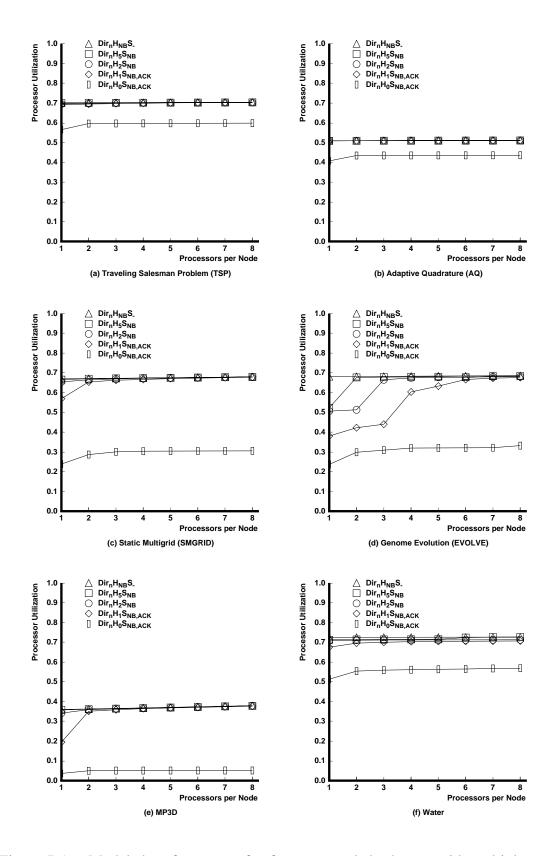

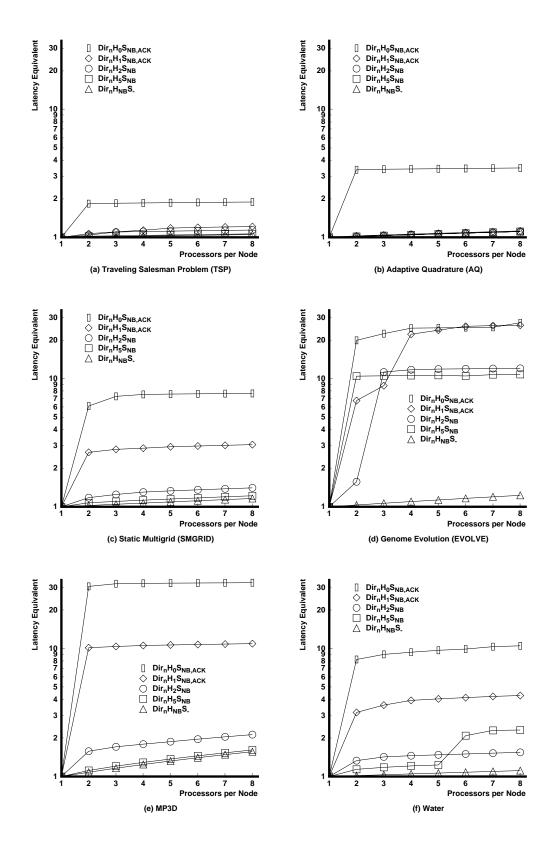

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7               | Protocol performance and worker-set size.  Application speedups over sequential, 64 NWO nodes.  TSP: detailed performance analysis on 64 NWO nodes.  TSP running on 256 NWO nodes.  Histogram of worker-set sizes for EVOLVE, running on 64 NWO nodes.  EVOLVE performance with and without heap skew.  Application speedups over sequential, 16 A-1000 nodes.           | 68<br>70<br>71<br>72<br>74<br>74<br>76 |

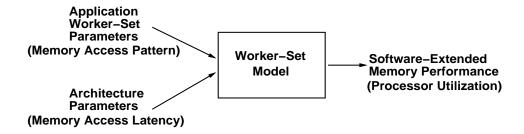

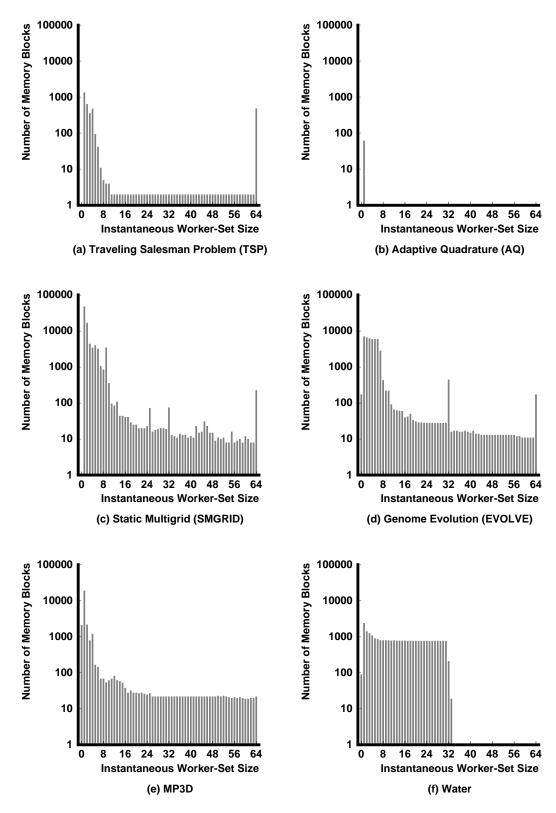

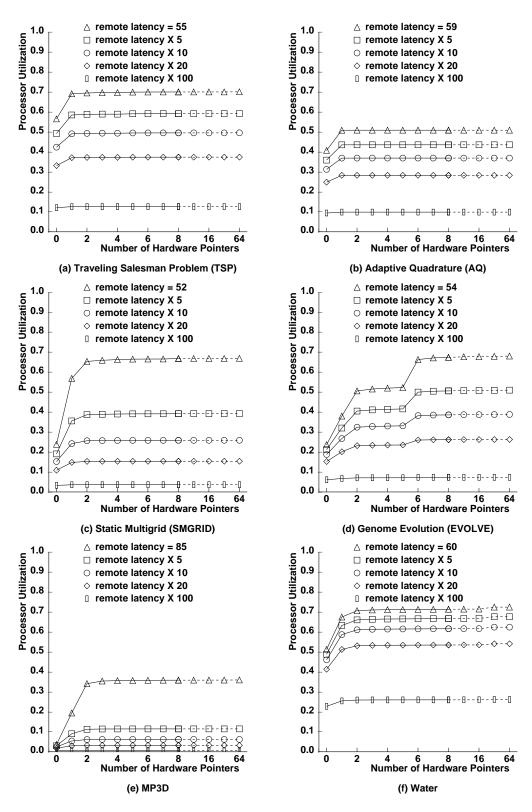

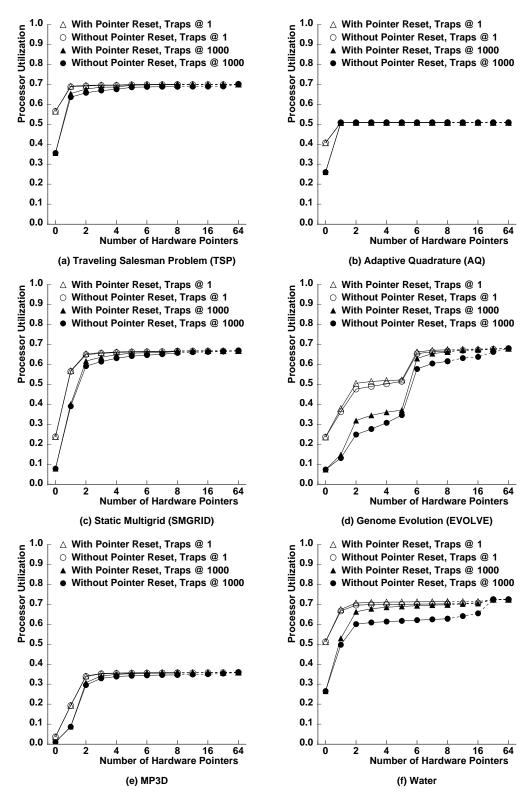

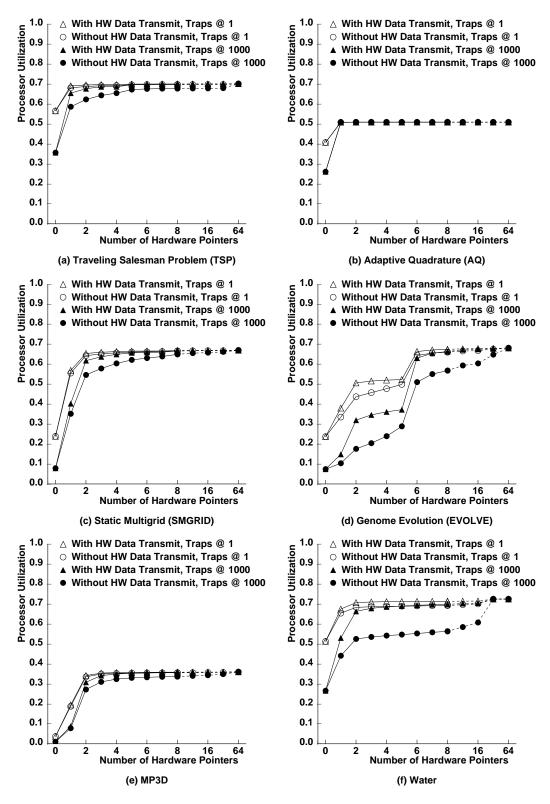

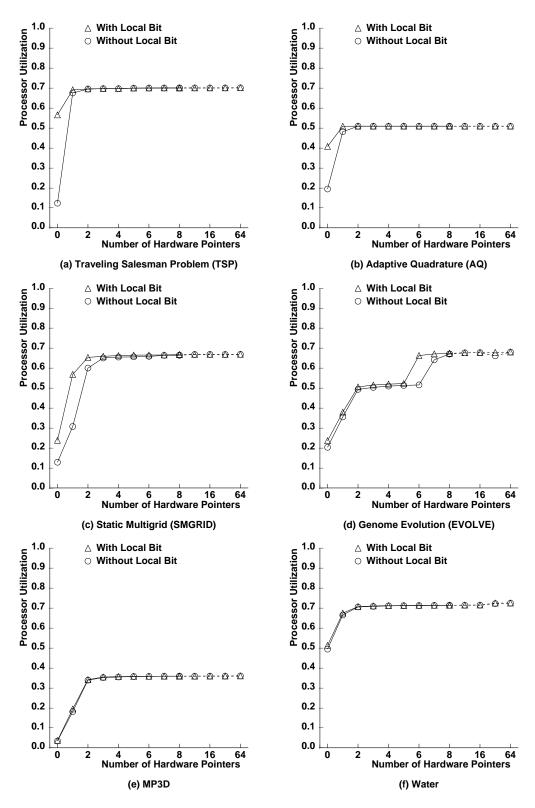

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6<br>7-7<br>7-8<br>7-9 | The worker-set model.  Read access instantaneous worker-set histograms.  Write access worker-set histograms.  Model validation: synthetic workload.  Model error in predictions of synthetic workload performance.  Model error in predictions of benchmark performance.  Model validation: benchmark applications.  Effect of trap latency.  Effect of code efficiency. |                                        |

| 7-11                                                        | Performance of three different architectures                                                                                                                                                                                                                                                                                                                             | 104                                    |

| 7-12                                                        | Effect of hardware directory reset                                                                                                                                                                                                                                                                                                                                       | 105                                    |

| 7-13 | Effect of hardware transmit                         |

|------|-----------------------------------------------------|

| 7-14 | Effect of one-bit pointer                           |

| 7-15 | Effect of superscalar processors                    |

| 7-16 | Effect of multiple processors per node              |

| 7-17 | Latency equivalent for multiple processors per node |

| 7-18 | Effect of worker-set size                           |

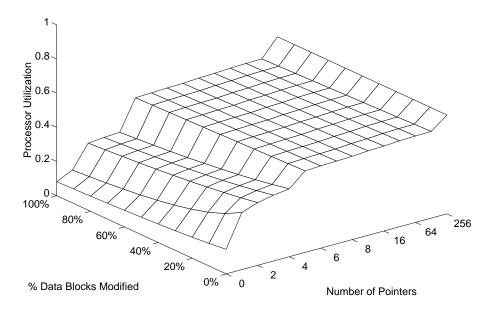

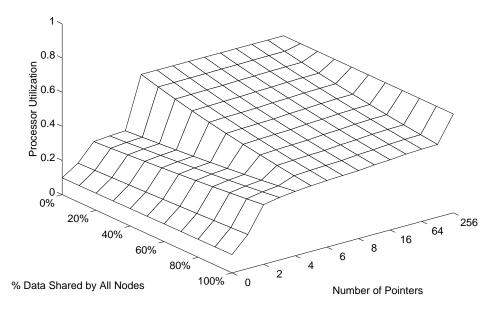

| 7-19 | Effect of modified data                             |

| 7-20 | Effect of worker-set mix                            |

| 8-1  | Performance of broadcast protocols                  |

| 8-2  | LimitLESS profile report                            |

|      | Hardware-accelerated coherent shared memory         |

## **List of Tables**

| 3.1  | Sequential time required to run six benchmarks on NWO and the A-1000. Characteristics of applications | 36<br>38 |

|------|-------------------------------------------------------------------------------------------------------|----------|

| 4.1  | Directory states.                                                                                     | 44       |

| 4.2  | Annotation of the state transition diagram.                                                           | 47       |

| 4.3  | Cache coherence protocol messages                                                                     | 48       |

| 4.4  | Optional protocol messages                                                                            | 48       |

| 4.5  | Performance for three coherence schemes, in terms of millions of cycles.                              | 52       |

| 5.1  | Functionality related to FCI                                                                          | 59       |

| 5.2  | FCI operations for manipulating local data state                                                      | 60       |

| 5.3  | FCI operations for transmitting and receiving packets                                                 | 60       |

| 5.4  | FCI operations for manipulating hardware directory entries                                            | 62       |

| 5.5  | FCI operations for livelock and deadlock avoidance                                                    | 62       |

| 6.1  | Software-extension latencies for C and assembly language                                              | 66       |

| 6.2  | Breakdown of execution cycles                                                                         | 66       |

| 7.1  | Notation for the analytical model                                                                     | 80       |

| 7.2  | Inputs to the analytical model from applications.                                                     | 81       |

| 7.3  | Inputs to the analytical model from protocol measurements                                             | 85       |

| 7.4  | Derived parameters of the analytical model                                                            | 86       |

| 7.5  | Summary of error in analytical model                                                                  | 95       |

| 8.1  | PRODO macros                                                                                          |          |

| 8.2  | Performance of different versions of EVOLVE                                                           | 130      |

| A.1  | ASIM execution times for Weather.                                                                     |          |

| A.2  | NWO: WORKER performance, 16 nodes                                                                     |          |

| A.3  | NWO: Speedup over sequential                                                                          |          |

| A.4  | NWO: Detailed TSP measurements                                                                        |          |

| A.5  | NWO: EVOLVE worker-set sizes                                                                          |          |

| A.6  | NWO: Detailed EVOLVE measurements.                                                                    |          |

| A.7  | A-1000: Speedup over sequential                                                                       |          |

| A.8  | NWO: EVOLVE with broadcasts.                                                                          |          |

| A.9  | Additional model parameters for the Alewife memory hierarchy.                                         |          |

| A.10 | Model input parameters for six benchmarks                                                             | 141      |

| A.11 Read access worker-set histograms: 0 – 31 nodes  | . 142 |

|-------------------------------------------------------|-------|

| A.12 Read access worker-set histograms: 32 – 64 nodes | . 143 |

| A.13 Write access worker-set histograms               | . 144 |

| A.14 Model synthetic input parameters                 | . 144 |

## Chapter 1

## **Shared Memory Design**

The search for inexpensive parallel computing continues. Computer manufacturers would like to tell consumers that processing is as easy to add to a system as memory. A system should be able to start with a single processor and grow arbitrarily large, as its owner's need for processing increases. The task of adding processors to a system should require only commodity components — packaged modularly — and perhaps some extra floor space in a computer room.

To a certain extent, this goal has already been achieved. Most workstation vendors market a product line that ranges from single-processor machines to high-end servers containing up to sixteen processors. The structure, or architecture, of these parallel systems keeps costs relatively low. Each processor's packaging looks much the same as in a standard workstation, and a bus (a set of up to 256 wires) connects the processors together. This combination of commodity processing elements and an inexpensive communication substrate keeps costs low.

Many of these multiprocessor systems offer a shared memory programming model that allows all processors to access the same linearly-addressed memory. Since this model is close to the one used for single-processor systems, it provides a convenient abstraction for writing multiprocessor applications: processors can store information for themselves or communicate information to others using a single mechanism.

Physical limitations restrict the ability of these computer architectures to scale past a small number of processors. Communication delay and bandwidth are the primary culprits. If every access to shared memory required interprocessor communication, the latency caused by reading and writing data would be prohibitive. Given the high rate of memory accesses required by today's fast processors, a bus simply can not move enough data to satisfy the number of requests generated by more than a few processors.

Cache memories solve part of the latency problem, just as they do in single-processor systems. By storing copies of frequently accessed data physically close to processors, caches provide fast average memory access times. In multiprocessors, caches also reduce the bandwidth that processors require from their communication substrate. The memory accesses that caches handle do not require round-trips on a system's bus.

Unfortunately, making copies of data causes the cache coherence problem: one processor's modifications of the data in shared memory must become visible to others. Small multiprocessors solve this problem by using the fact that all of the processors on a

bus can receive all of the messages transmitted on it. This broadcast capability is at once liberating and constraining. By watching each other's transmissions, caches can keep themselves coherent. On the other hand, physical media that broadcast information have limited bandwidth. Even with caches, current technology limits inexpensive parallel computing to less than twenty high-performance processors.

Researchers who work beyond this limit strive instead for cost-effective parallel computing. A cost-effective system solves a customer's problem in the least expensive (and sometimes the only available) way, taking into account programming time, system cost, and computation time. The definition of a cost-effective system depends on each customer's application, but it typically requires a cost-efficient system: a cost-efficient system's price grows approximately linearly with the number of processors.

For the reasons discussed above, the decision to abandon a bus when designing a large, cost-efficient system is mandatory. The other choices involved in building a larger system are much more difficult. One possibility is to build a system without shared memory, and let programmers suffer the consequences. This strategy works for computing applications that consist of many large, independent tasks. Another possibility is to build a system without caches. This strategy requires an extremely high-bandwidth and expensive interconnection network, and might work well for applications that require so much computation that the system can effectively hide the latency of communication. A final possibility is to implement shared memory and caches without a broadcast mechanism.

An appropriate combination of hardware and software yields a cost-efficient system that provides coherent, fast, shared memory access for tens or hundreds of processors. The following chapters prove this thesis by demonstrating such a system and analyzing its performance.

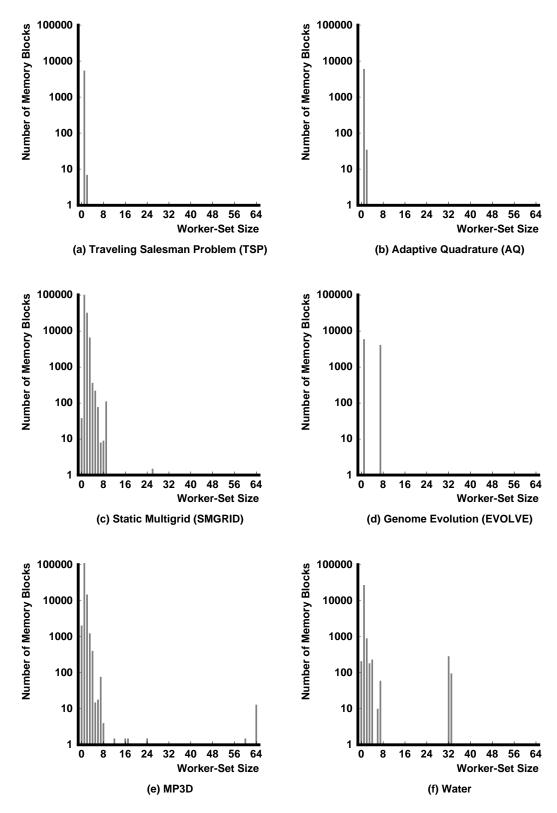

There are two challenges involved in building coherent shared memory for a large-scale multiprocessor. First, the architecture requires an appropriate balance of hardware and software. The integrated systems approach provides the cost-management strategy for achieving this goal: implement common case operations in hardware to make them fast and relegate less common activities to software. Examining the access patterns of shared memory applications reveals that a typical *worker set* (the set of processors that simultaneously access a unit of data) tends to be small. In fact, most blocks of shared memory are accessed by exactly one processor; other blocks are shared by a few processors; and a small number of blocks are shared by many (or all) processors.

This observation leads to a family of shared-memory systems that handle small worker sets in hardware and use software to handle more complex scenarios. Such *software-extended* memory systems require a number of architectural mechanisms. The shared memory hardware must handle as many requests as possible; it must be able to invoke extension software on the processor; and the processor must have complete access to the memory and network. The balancing act is tricky, because the architect must control hardware complexity and cost without sacrificing performance.

The second challenge involves designing the software component of a memory system. As in any software system, there is a trade-off between abstraction and raw performance. If the system is to perform well as a whole, the software must execute efficiently; if the system is to benefit from the flexibility of software, it must facilitate

rapid code development. A software-extended system requires an interface between the memory-system hardware and software that achieves both of these goals.

The ability to extend the hardware provides the opportunity for software to take an active role in improving system performance. At a minimum, the software can measure its own performance. Appropriate data collection and information feedback techniques can allow the software to help programmers understand their applications, enable compilers to generate better code, and tune the system as it runs. Thus, not only does the software-extension approach lead to a cost-efficient machine, it enables the synergy between components of a multiprocessing system that high performance requires.

A software-extended memory system has been proposed, designed, tested, measured, and analyzed during the construction of Alewife [2], a shared-memory architecture that scales to 512 processors. Alewife serves as both a proof-of-concept for the software-extension approach and as a platform for investigating shared-memory design and programming. Since the study has been conducted in the context of a real system, it focuses on simple solutions to practical problems. This engineering process has resulted in a multiprocessor that is both scalable and programmable.

Experience with Alewife shows that software-extended memory systems achieve high performance at a per-processor cost that is close to standard workstations. A combination of minimal hardware and intelligent software realizes performance comparable to expensive shared memory implementations. By adopting this design strategy, computer vendors can build truly scalable product lines.

### 1.1 Contributions

This dissertation:

- Proposes the software-extension approach and develops algorithms for hybrid hardware/software cache coherence protocols.

- Measures and analyzes the performance of the first software-extended memory system, using two complete implementations of the Alewife multiprocessor: a physical machine proves the viability of the design, and a simulation system allows experimentation with a spectrum of memory systems.

- Describes a flexible coherence interface that expedites development of memory system software. Detailed performance measurements of the software show the trade-off between flexibility and performance.

- Constructs and validates an analytical model of software-extended systems. This

model surveys the design space and predicts the performance impact of a variety

of architectural mechanisms.

- Demonstrates examples of smart memory systems that use the flexibility of software to help improve system performance. One of these systems implements a novel technique for optimizing the use of shared memory.

## 1.2 Organization

The next chapter elaborates on the design of large-scale shared memory systems. It reviews the work related to this dissertation and defines the terms used in the following chapters. Chapter 3 describes the tools used to perform the study of software-extended systems: models, simulators, hardware, and applications. Chapter 4 summarizes the study that shows that large-scale multiprocessors need a software-extended memory system. The study also specifies the coherence algorithms used by Alewife's memory system hardware. Chapter 5 describes the software side of Alewife's memory system, including the flexible coherence interface. Chapter 6 presents the results of an empirical study of Alewife's software-extended system. The study examines the trade-offs between cost, flexibility, and performance. Chapter 7 uses the empirical study to validate a mathematical model of the performance of software-extended systems. The chapter then uses the model to explore the space of shared memory designs. Chapter 8 describes the user interfaces, implementations, and benefits of three smart memory systems. Finally, Chapter 9 concludes by specifying a minimal software-extended shared memory architecture.

## Chapter 2

## **Distributed Shared Memory**

Contemporary research on implementing scalable shared memory focuses on distributed shared memory architectures. Rather than partitioning memory and processors into separate modules, these architectures distribute memory throughout a machine along with the system's processors. A processing element — also called a node — contains a processor, a bank of memory, and usually a cache. Each processor can access memory in its own node or transmit a request through the interconnection substrate to access memory in a remote node. Intranode accesses proceed just as memory accesses do in a normal single-processor system; internode memory accesses require much more substantial architectural mechanisms.

A distributed shared memory architecture must service processors' internode requests for data and maintain the coherence of shared memory. Before the work on software-extended shared memory, systems used either software or hardware to implement protocols that perform these functions.

Software distributed shared memory architectures [20, 57, 24, 11, 9, 8, 41] implement truly inexpensive parallel computing. They provide a shared memory interface for workstations and networks, using only standard virtual memory and communication mechanisms. In order to reduce the effects of the overhead of software support and long communication delays, these systems transfer large blocks of data (typically thousands of bytes) and amortize the overhead over many memory accesses. Accordingly, applications achieve good performance if their subtasks share large data objects and communicate data in bursts.

Recent developments in software distributed shared memory use a combination of programmer annotations and protocol optimizations to allow systems to transmit kilobytes of data at a time, and only as much data as is needed to maintain coherence. These techniques use weaker memory consistency models [1] than sequential consistency [52] (a convenient model of shared memory), but provide synchronization mechanisms that allow programmers to write correct applications. In addition, some software memory systems make intelligent choices about data transfer and coherence policies. The latest software implementations of distributed shared memory exhibit good parallelism for small systems running large problem sizes.

Hardware implementations of distributed shared memory [55, 33, 45] attempt to provide cost-effective implementations of larger systems. These systems accommodate

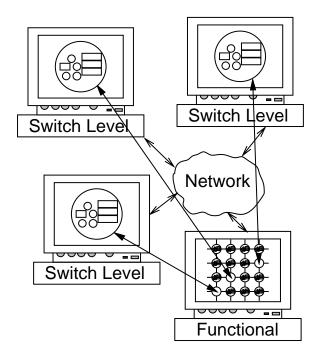

Figure 2-1: Alewife uses a hybrid approach to implement distributed shared memory.

applications with subtasks that share data in units of tens or hundreds of bytes, and make use of the high bandwidth and low latency provided by high-performance interconnection networks. Weak consistency models may also be applied to the design of these systems, but they are not absolutely essential for good performance: weak consistency is just one of a number of available latency-tolerance techniques [31]. Existing hardware implementations of distributed shared memory have expensive and complex memory systems. They are cost-effective solutions for applications when they are the only solution.

The software-extension approach, illustrated in Figure 2-1, bridges the gap between these two design styles [16, 34, 81]. By implementing basic transfer and coherence functions in hardware, software-extended systems provide efficient access to small units of data. The software part of these systems helps manage costs by using intelligent transfer and coherence policies when the hard-wired mechanisms require assistance. For historical reasons, software-extended systems are viewed as hardware implementations of distributed shared memory with software support. Section 8.5 examines the design approach from the opposite viewpoint.

Two parallel architectures [79, 23] combine the hardware and software approaches in a different way. These hybrid systems use bus-based coherence protocols for small clusters of processors, and software distributed shared memory techniques to enforce coherence between clusters. Each individual cluster can handle subtasks that share small objects and synchronize often; but for these systems to perform well, tasks located in different clusters must share large data objects and synchronize infrequently.

### 2.1 Cache Coherence Protocols

There are two logical sides of a shared memory system: the processor (request) side and the memory (response) side. In distributed systems, each node contains its own part of both sides of the system. The request side fields memory accesses from a processor, determines whether each access can be satisfied within the local node, and transmits messages into the network to initiate internode memory requests. The memory side receives intranode and internode requests, transmits data to requesting processors, and

maintains coherence.

The software-extended approach may be applied to either side of the memory system. While the processor side and the memory side of a memory system are inextricably linked in the design of a cache coherence protocol, they may be treated separately when considering a software-extension methodology. Each side of the protocol has its own, separate finite-state specification. Exactly which states and transitions happen to be implemented in software should be decided independently for each machine.

#### 2.1.1 The Processor Side

Each node must provide support for location-independent addressing, which is a fundamental requirement of shared memory. Hardware support for location-independent addressing permits application software to issue an address that refers to an object without knowledge of where it is resident. This hardware support includes an associative matching mechanism to detect if the object is cached, a mechanism to translate the object address and identify its location if it is not cached, and a mechanism to issue a message to fetch the object from a remote location if it is not in local memory.

As nodes are added to a multiprocessor, the total of all of the processor-side structures in the system grows at most linearly. Curiously, it is possible to argue that the cost of the processor side might grow sublinearly with the number of nodes: while holding problem size constant, cache working sets decrease as the number of nodes increases. Thus, smaller caches might be used in large multiprocessors than in small ones.

Since this research concentrates on the problem of cost management, it does not address the processor side of cache coherence protocols. It is certainly possible that — for reasons of flexibility, if not cost — a system designer might choose to implement part of the processor-side state machine in software. While this decision process may benefit from the experience described in the following chapters, it will hinge on a different set of constraints, such as processor cycle time and cache hit rates.

In addition, there are a host of techniques used to tolerate the latency of communication between nodes, including multiple-context support, prefetching, and weak consistency models. Since these techniques primarily impact the design of the processor side of the interface, they are not critical in the decision to extend part of the memory-side state machine into software. Therefore, this dissertation does not study the cost or performance implications of these mechanisms.

### 2.1.2 The Memory Side

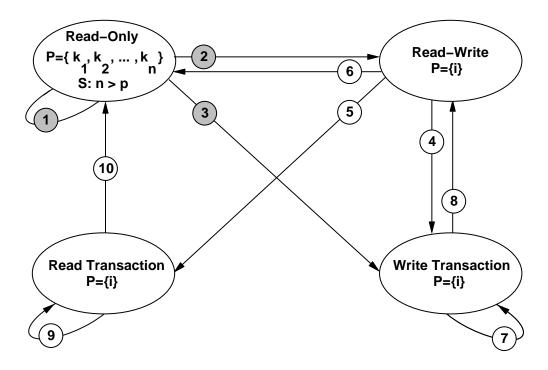

Implementing memory coherence for a large number of processors requires the system to keep track of the locations of cached copies of data. A *directory* is a structure that helps enforce the coherence of cached data by maintaining pointers to the locations of cached copies of each memory block. When one node modifies a block of data, the memory system uses the information stored in the directory to enforce a coherent view of the data. At least one company has designed a centralized directory for small, bus-based systems [26]. For larger systems, directories are not monolithic structures: they are distributed to the processing nodes along with a system's shared memory.

A cache coherence protocol consists of the directory states, the cache states, and the internode messages that maintain coherence: request messages ask for data; response messages transmit data; invalidation messages ask caches to destroy (or to return) copies of data; and acknowledgment messages indicate completed invalidations. Using a directory to implement cache coherence eliminates the need for a broadcast mechanism, which becomes a serious performance bottleneck for systems with more than sixteen processors.

The DASH multiprocessor [55] implements a distributed full-map directory [12, 73, 54], which uses hardware to track up to the maximum number of copies for every block of data in a system. Such an implementation becomes prohibitively expensive for systems with more than 64 processors. This strategy implicitly assumes that every block of data has a home location that contains both the block's data and an associated directory *entry*, which holds the *pointers* to cached copies.

Hierarchical directories [33, 45] implement the directory as a tree-like structure that is distributed throughout the system. This implementation strategy eliminates the need for a home location, and allows application data and directory information to migrate throughout the machine. This policy is both more intelligent and more complex than other directory schemes. Recent studies indicate that the increased data locality afforded by hierarchical directories improves performance marginally over lower-cost schemes [62, 37].

Another decentralized scheme [36, 7] uses home locations but distributes directory information to caches along with copies of data. Coherence information is stored in linked-lists; each link of a chain resides in a different cache. While these chained directories have reasonable storage requirements, they are relatively complicated and suffer from long write latencies.

It is also possible to design hardware to implement a cost-efficient limited directory [5], which only permits a small number of copies of any block of data. However, the performance of limited directories falls dramatically when many processors attempt to share a single block of data [14].

The software-extension approach leads to the family of LimitLESS protocols, which achieve close to the performance of a full-map directory with the hardware of a limited directory [16]. This scheme, described by Chapter 4 in detail, implements a small number of pointers in a hardware directory (zero through five in Alewife), so that the hardware can track a few copies of any memory block. When these pointers are exhausted, the memory system hardware interrupts a local processor, thereby requesting it to maintain correct shared memory behavior by extending the hardware directory with software.

Another set of software-extended protocols (termed Dir<sub>1</sub>SW) were proposed in [34] and [81]. These protocols use only one hardware pointer, rely on software to broadcast invalidates, and use hardware to accumulate the acknowledgments. In addition, they allow the programmer or compiler to insert Check-In/Check-Out (CICO) directives into programs to minimize the number of software traps.

All software-extended memory systems require a battery of architectural mechanisms to permit a designer to make the cost versus performance trade-off. First, the shared memory hardware must be able to invoke extension software on the processor, and the processor must have complete access to the memory and network hardware [16, 47, 81].

Second, the hardware must guarantee forward progress in the face of protocol thrashing scenarios and high-availability interrupts [48]. The system must also implement the processor-side support described in the previous section. Since these mechanisms comprise the bulk of the complexity of a software-extended system, it is important to note that the benefits of these mechanisms extend far beyond the implementation of shared memory [42, 29]: integrating message passing and shared memory promises to be an active topic of research in the coming years.

Alternative scalable approaches to implementing shared memory proposed in [61, 69, 77] use hardware mechanisms that allocate directory pointers dynamically. These schemes do not require some of the mechanisms listed above, but they lack the flexibility of protocol and application software design. Section 8.2 gives an example of how to incorporate scalable coherence algorithms into a software-extended system.

### 2.1.3 A Spectrum of Protocols

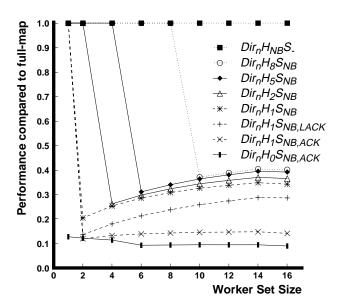

The number of directory pointers that are implemented in hardware is an important design decision involved in building a software-extended shared memory system. More hardware pointers mean fewer situations in which a system must rely on software to enforce coherence, thereby increasing performance. Having fewer hardware pointers means a lower implementation cost, at the expense of reduced performance. This trade-off suggests a whole spectrum of protocols, ranging from zero pointers to n pointers, where n is the number of nodes in the system.

#### The n pointer protocol

The full-map protocol uses n pointers for every block of memory in the system and requires no software extension. Although this protocol permits an efficient implementation that uses only one bit for each pointer, the sheer number of pointers makes it extremely expensive for systems with large numbers of nodes. Even though the cost of the full-map protocol makes it impractical, it serves as a good performance goal for the software-extended schemes.

#### $2 \leftrightarrow (n-1)$ pointer protocols

There is a range of protocols that use a software-extended coherence scheme to implement shared memory. It is this range of protocols that allows the designer to balance hardware cost and system performance. From the point of view of implementation complexity, the protocols that implement between 2 and n-1 pointers in hardware are homogeneous. Of course, the n-1 pointer protocol would be even more expensive to implement than the full-map protocol, but it still requires exactly the same hardware and software mechanisms as the protocols at the other end of the spectrum.

In a load/store architecture, the software for protocol extension needs to service only two kinds of messages: read and write requests. It handles read requests by allocating an extended directory entry (if necessary), emptying all of the hardware pointers into the software structure, and recording a pointer to the node that caused the directory overflow.

Subsequent requests may be handled by the hardware until the next overflow occurs. For all of these protocols, the hardware can return the appropriate data to requesting nodes; the software only needs to record requests that overflow the hardware directory.

To handle write requests after an overflow, the software transmits invalidation messages to every node with a pointer in the hardware directory or in the software directory extension. The software then returns the hardware directory to a mode that collects one acknowledgment message for each transmitted invalidation.

#### **Zero-pointer protocols**

The zero-pointer LimitLESS scheme, termed a *software-only directory architecture*, provides an interesting design point between software and hardware distributed shared memory. It uses hardware to support the processor-side functions, but implements the entire memory side in software.

Since the software-only directory has no directory memory, it requires substantially different software than the  $2 \leftrightarrow (n-1)$  range of protocols. This software must implement all coherence protocol state transitions for internode accesses [64].

#### **One-pointer protocols**

The one-pointer protocols are a hybrid of the protocols discussed above. Chapter 6 studies the performance of three variations of this class of protocols. All three use the same software routine to transmit data invalidations sequentially, but they differ in the way that they collect the messages that acknowledge receipt of the invalidations. The first variation handles the acknowledgments completely in software, requiring a trap from the hardware upon the receipt of each message. During the invalidation/acknowledgment process, the hardware pointer is unused.

The second protocol handles all but the last of a sequence of acknowledgments in hardware. If a node transmits 64 invalidations for a memory block, then the hardware will process the first 63 invalidations. This variation uses the hardware pointer to store a count of the number of acknowledgments that are still outstanding. Upon receiving the 64<sup>th</sup> acknowledgment, the hardware invokes the software, which takes care of transmitting data to the requesting node.

The third protocol handles all acknowledgment messages in hardware. This protocol requires storage for two hardware pointers: one pointer to store the requesting node's identifier and another to count acknowledgments. Although a designer would always choose to implement a two-pointer protocol over this variation of the one-pointer protocol, it still provides a useful baseline for measuring the performance of the other two variations.

#### A notation for the spectrum

This section introduces a notation that clearly specifies the differences between various implementations and facilitates a precise cost comparison. The notation is derived from a nomenclature for directory-based coherence protocols introduced in [5]. In the previous

notation, a protocol was represented as  $Dir_iX$ , where i represented the number of explicit copies tracked, and X was B or NB depending on whether or not the protocol issued broadcasts. Notice that this nomenclature does not distinguish between the functionality implemented in the software and in the hardware. The new notation attempts to capture the spectrum of features of software-extended protocols that have evolved over the past several years, and previously termed LimitLESS<sub>1</sub>, LimitLESS<sub>4</sub>, and others in [16], and  $Dir_1SW$ ,  $Dir_1SW+$ , and others in [34, 81].

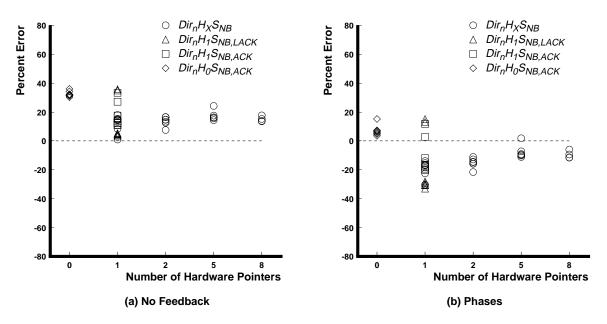

For both hardware and software, the new notation divides the mechanisms into two classes: those that dictate directory actions upon receipt of processor requests, and those that dictate directory actions for acknowledgments. Accordingly, the notation specifies a protocol as:  $\mathbf{Dir_iH_XS_{Y,A}}$ , where i is the number of explicit pointers recorded by the system — in hardware or in software — for a given block of data.

The parameter X is the number of pointers recorded in a hardware directory when a software extension exists. X is NB if the number of hardware pointers is i and no more than i shared copies are allowed, and is B if the number of hardware pointers is i and broadcasts are used when more than i shared copies exist. Thus the full-map protocol in DASH [55] is termed  $Dir_n H_{NB}S_-$ .

The parameter Y is NB if the hardware-software combination records i explicit pointers and allows no more than i copies. Y is B if the software resorts to a broadcast when more than i copies exist.

The A parameter is ACK if a software trap is invoked on every acknowledgment. A missing A field implies that the hardware keeps an updated count of acknowledgments received. Finally, the A parameter is LACK if a software trap is invoked only on the last acknowledgment.

According to this notation, the LimitLESS<sub>1</sub> protocol defined in [16] is termed  $Dir_nH_1S_{NB}$ , denoting that it records n pointers, of which only one is in hardware. The hardware handles all acknowledgments and the software issues invalidations to shared copies when a write request occurs after an overflow. In the new notation, the three one-pointer protocols defined above are  $Dir_nH_1S_{NB,ACK}$ ,  $Dir_nH_1S_{NB,LACK}$ , and  $Dir_nH_1S_{NB}$ , respectively.

The set of software-extended protocols introduced in [34] and [81] can also be expressed in terms of the notation. The Dir<sub>1</sub>SW protocol maintains one pointer in hardware, resorts to software broadcasts when more than one copy exists, and counts acknowledgments in hardware. In addition, the protocol traps into software on the last acknowledgment [80]. In the notation, this protocol is represented as  $Dir_1H_1S_{B,LACK}$ . This protocol is different from  $Dir_nH_1S_{NB,LACK}$  in that  $Dir_1H_1S_{B,LACK}$  maintains only one explicit pointer, while  $Dir_nH_1S_{NB,LACK}$  maintains one pointer in hardware and extends the directory to n pointers in software. An important consequence of this difference is that  $Dir_nH_1S_{NB,LACK}$  potentially interrupts processors on read requests, while  $Dir_1H_1S_{B,LACK}$  does not. Unlike  $Dir_nH_1S_{NB,LACK}$ ,  $Dir_1H_1S_{B,LACK}$  must issue broadcasts on write requests to memory blocks that are cached by multiple nodes.

## 2.2 Flexible and Smart Memory Systems

Virtual memory designers know well the benefits of flexible interfaces in memory systems. The CMU Mach Operating System uses an interface that separates the machine-dependent and machine-independent parts of a virtual memory implementation [65]. This pmap interface allows the Mach memory system to run efficiently on a wide range of architectures. Some of the features of this interface are remarkably similar to Alewife's flexible coherence interface, which separates the hardware and software components of the software-extended memory system.

Flexible virtual memory systems can implement a number of mechanisms that are useful to higher-level software [6]. In fact, software distributed shared memory architectures use such mechanisms to implement smart memory systems, which use intelligence to optimize memory performance. DUnX [53] uses heuristics to place and to migrate pages of virtual memory on the BBN GP1000. Munin [11] allows programmers to annotate code with data types and handles each type of data differently. Orca [8] uses a compiler to analyze access to data objects statically. Based on the analysis, the compiler selects an appropriate memory for each object.

Similar optimization techniques work for software-extended implementations of distributed shared memory. Lilja and Yew demonstrate a compiler annotation scheme for optimizing the performance of protocols that dynamically allocate directory pointers [58]. Hill, Wood, and others propose and evaluate a programmer-directed method for improving the performance of software-extended shared memory [34, 81]. The studies show that given appropriate annotations, a large class of applications can perform well on  $Dir_1H_1S_{B,LACK}$ . Cachier [21] takes this methodology one step further by using dynamic information about a program's behavior to produce new annotations, thereby improving performance. Cachier requires the programmer to label all shared data structures and to run the program on a simulator.

The profile-detect-optimize technique implemented for Alewife (in Section 8.4) is similar to Cachier, except that it runs entirely on a real software-extended system and requires no simulation. This technique was inspired by the Multiflow trace-scheduling compiler [22].

The LimitLESS profiler in Section 8.3 and Mtool [30] both attempt to provide information about shared memory usage. The two systems' implementations are very different, however. Mtool instruments code on the processor side and presents information in terms of memory access overhead in procedures. The LimitLESS profiler instruments the memory side and reports the worker-set behavior of important data objects.

FLASH [51] and Typhoon [66] explore alternative methods for building flexible memory systems. These architectures dedicate processors to implement scalable shared memory. Section 7.4.3 explores the differences in performance between these architectures and Alewife. Hand-crafted protocols that can optimize access for specific types of data have been developed for FLASH and Typhoon [18, 66].

## 2.3 Understanding Memory System Performance

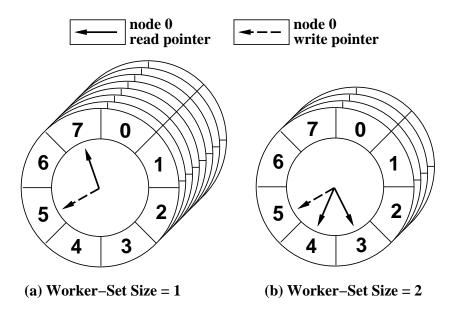

A worker set is the set of processors that access a block of memory between subsequent modifications of the block's data. The notion of a worker set is loosely based on working sets, which specify the portions of memory accessed by a single processor over an interval of time. In the working-set definition, the time interval is artificially defined for the sake of measurement. Conversely, worker sets specify the processors that access a block of data over an interval of time. The worker-set time interval is defined implicitly by the reference pattern of each object.

Denning [27] writes that "...the working set is not a model for programs, but for a class of procedures that measure the memory demands of a program." This model predicts the appropriate amount of memory or cache required by each process using a virtual memory system. Similarly, the worker-set behavior of shared memory programs specifies the demands on a software-extended system. The worker-set model predicts the appropriate mix of hardware and software for running a multiprocessor application.

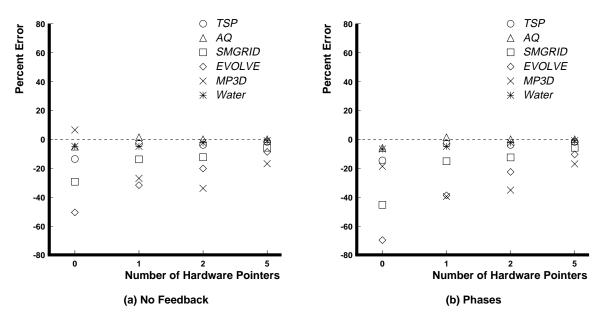

Measuring access patterns in terms of worker sets is certainly not new. The worker-set invalidation profiles in Figure 7-3 are virtually identical to the ones studied by Weber in [78]. Simoni and Horowitz used stochastic models to predict similar invalidation patterns, cache miss statistics, and transaction latencies for directory-based protocols [70]. Simoni completed this work with an analysis of scalable hardware directory schemes [68]. He also presented a simple analysis that translated data sharing patterns into processor utilization. Tsai and Agarwal derived sharing patterns and cache miss ratios directly from parallel algorithms [75].

The inputs to the worker-set model in Chapter 7 are similar to the outputs of the preceding studies: it predicts the performance of software-extended systems from worker-set behavior and cache access statistics. The model is validated by an empirical study of Alewife's software-extended memory system and its performance, which is the subject of the next four chapters.

## Chapter 3

## An Architect's Workbench

A primary goal of the research on software-extended shared memory was to build a large, working multiprocessor system with a convenient programming interface. This chapter describes the methodology for achieving this goal and the various tools used during the life-cycle of the Alewife project.

The life-cycle began with initial studies using mathematical models and simple simulation techniques that determined the basic features of the multiprocessor's architecture. These studies investigated a wide range of design options, including the programming model, the practical number of processors, the balance of communication and computation, cache coherence protocols, and the type of interconnection network.

The tools used during this stage of the project did not model the intricate details of the architecture, and therefore could be constructed quickly. In practice, the models and simulators either produced their results instantaneously or simulated long executions in a relatively short amount of time. Due to the lack of detail, the tools measured quantities such as component utilization, transaction latency, and system throughput. While these metrics did not indicate end-to-end performance, they measured the relative benefits of different design alternatives.

The next stage consisted of a preliminary system design at the functional level. The Alewife simulator, called ASIM, modeled large system components and their internal structure at the level of state machines, data repositories, and objects communicated between components. This simulator took considerable effort to build, because it implemented the cross-product of a wide range of design options, at a more detailed level than the tools of the previous stage. The additional detail supported the development of the first software for Alewife, including compilers and task schedulers. It also allowed performance to be measured directly in terms of the number of cycles required to run a program, and the speedup when using multiple processors instead of a sequential system.

While ASIM could still measure utilization, latency, and throughput, these quantities typically were used only to explain behavior observed with the higher-level metrics. ASIM simulated about 20,000 cycles per second. Given some patience, this speed permitted the development of small applications and the investigation of design trade-offs. The preliminary evaluation of software-extended shared memory took place at this stage of the project.

The first two stages provided the foundation for the next — and longest — phase of

development: the implementation of the architecture, dubbed the A-1000. The design of Alewife's hardware and software required two complementary simulation systems. One simulator, provided by LSI Logic, directly executed the gate-level specification of the hardware implementation. Such a simulation was integral to the hardware fabrication process, but it modeled the system at such a low level of detail that it barely reached speeds of one clock cycle per second.

The other simulator, called NWO, modeled the system at a high enough level that it reached speeds of 3,000 clock cycles per second but could still run all of the same programs as the A-1000. NWOP, a parallel version of NWO, executed tens of thousands of cycles per second on the CM-5, a parallel computer built by Thinking Machines. The dual LSI/NWO simulation approach decoupled Alewife's hardware and software efforts, allowing the development of compilers, operating systems, and applications to advance in parallel with the physical system's design, test, layout, and fabrication.

During this phase of development, the standard metrics used in previous stages helped refine the design and fine-tune the performance of the system as a whole. At this stage, the correct operation of the system was just as important as the projected speed. The rate that hardware bugs were found (and removed) served as a measure of the stability of the system and gated the decision to fabricate the components.

The development phase also included the finalization of the hardware-software interface and the design of abstractions within the the software system. A qualitative metric used during this process was the time required to write code for the system. There were two types of programmers who had to be satisfied: the application programmer, who works for the multiprocessor's end-user; and the operating system programmer, who works closely with architects and compiler writers. The flexible coherence interface grew out of the need for a rich environment that reduced the effort required for operating system programmers to write modules of the memory-system software.

Fabricating the A-1000 culminated the development phase of the project. While the simulators from the previous stage remained important, the abstract workbench turned into a physical one with the real tools required to assemble Alewife machines. The working machines validated the simulation and modeling techniques used to define the architecture. Hardware running at millions of cycles per second enabled research using applications with real data sets and operating systems with a full complement of functionality.

The final stage of the project reexamined the design space in light of the lessons learned from designing and implementing the architecture. The tools used for the analysis were the same as those used in the initial studies: mathematical models quantified the importance of features of the architecture with utilization, latency, and throughput. It was somewhat satisfying to use the metrics from the preliminary studies of the Alewife memory system. The analysis with these metrics closed the research life-cycle by using the specific implementation to help evaluate a wide range of design options.

The next section describes the Alewife architecture, ASIM, and the two implementations of Alewife: the A-1000 and NWO. This chapter also describes a synthetic workload and the benchmarks that drive the performance analysis.

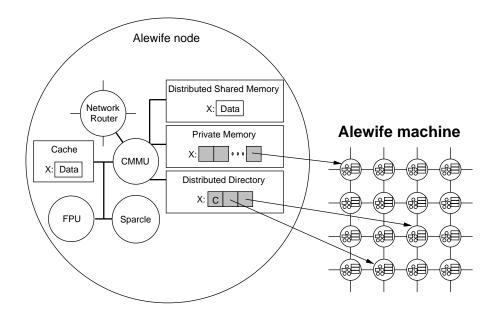

Figure 3-1: Alewife node, with a  $Dir_nH_2S_{NB}$  memory block.

### 3.1 The Alewife Architecture

Alewife provides a proof-of-concept for software-extended memory systems and a platform for experimenting with many aspects of multiprocessor design and programming. The Alewife architecture scales up to 512 processing elements with distributed shared memory. It uses caches to implement fast memory access, and a software-extended memory system to enforce sequential consistency.

Figure 3-1 shows an enlarged view of a node in the Alewife machine. The processor on each node consists of a Sparcle processor [3], which is based on the 32-bit SPARC architecture [72], and a floating-point coprocessor. The nodes communicate via messages through a direct network [67] with a mesh topology. Alewife's memory system includes a cache, a bank of private memory, a portion of the globally-shared main memory, and the corresponding portion of the hardware limited directory. A single-chip communications and memory management (CMMU) on each node holds the cache tags and implements the memory coherence protocol by synthesizing messages to other nodes.

The 512 node restriction is primarily a function of Sparcle's 32-bit address, which contains enough space for 22 bits (4 Mbytes) of offset, a 9-bit node identifier (512), and one bit to differentiate shared addresses from private addresses.

In addition to the standard hardware directory pointers, Alewife implements a special one-bit pointer for the node that is local to the directory. Several simulations show that this extra pointer improves performance by only about 2%. Its main benefit lies in reducing the complexity of the protocol hardware and software by eliminating the possibility that a node will cause its local hardware directory to overflow.

Alewife also includes a mechanism that allows a zero-pointer protocol to be optimized. This optimization may be described as follows<sup>1</sup>: the zero-pointer protocol uses

<sup>&</sup>lt;sup>1</sup>The actual implementation in Alewife is slightly different.

one extra bit per memory block to optimize the performance of purely intranode accesses. The bit indicates whether the associated memory block has been accessed at any time by a remote node. When the bit is clear (the default value), all memory accesses from the local processor are serviced without software traps, just as in a uniprocessor. When an internode request arrives, the bit is set and the extension software flushes the block from the local cache. Once the bit is set, all subsequent accesses — including intranode requests — are handled by software extension.

All of the performance results in Chapter 6 measure protocol implementations that use these one-bit optimizations. Sections 7.4.3 and 7.4.5 use the analytical model to evaluate the contribution of this architectural mechanism to the performance of the system.

There are two other features of the Alewife architecture that are relevant to the memory system, the most important of which is integrated shared memory and message passing [42, 47]. This mechanism enables software-extended memory by allowing the processor to transmit and receive any kind of network packet, including the ones that are part of the cache coherence protocol. Part of this mechanism is a direct-memory-access facility. As a result, much of the interprocessor communication — especially in the operating system, the task scheduler, and the synchronization library — uses message-passing semantics rather than shared memory. This policy improves performance and relieves the memory system of the burden of handling data accesses that would be hindered, rather than helped, by caches.

The Sparcle processor uses the SPARC register windows to implement up to four hardware contexts, each of which holds the state of an independent thread of computation. This implementation allows the processor to switch quickly between the different threads of execution, an action which is typically performed upon a remote memory access. While the context-switching mechanism is intended to help the system tolerate the latency of remote memory accesses [4, 50, 31], it also accelerates the software-extended memory system: when the processor receives an interrupt from the CMMU, it can use the registers in an empty context to process the interrupt, rather than saving and restoring state. Section 7.4.1 uses the analytical model to determine how this fast trap mechanism affects performance.

There are currently two implementations of the Alewife architecture: a working hardware prototype (A-1000) and a deterministic simulator (NWO). Both of these implementations run exactly the same binary code, including all of the operating system<sup>2</sup> and application code. In contrast, the simulation system used for preliminary studies (ASIM) implements a wide range of architectural options but can not run actual Alewife programs.

### 3.1.1 ASIM: the Preliminary Simulator

ASIM models each component of the Alewife machine — from the multiprocessor software to the switches in the interconnection network — at the functional level. This simulator, which does not represent the final definition of the Alewife architecture,

<sup>&</sup>lt;sup>2</sup>NWO does not run a few of the hardware diagnostics.

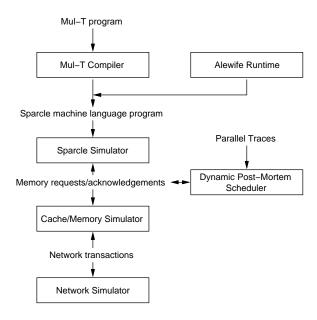

Figure 3-2: Diagram of ASIM, the Alewife system simulator.

became operational in 1990. The simulator runs programs that are written in the Mul-T language [44], optimized by the ORBIT compiler [43], and linked with a runtime system that implements both static work distribution and dynamic task partitioning and scheduling. The code generated by this process runs on a simulator consisting of processor, cache/memory, and network modules.

Although the memory accesses in ASIM are usually derived from applications running on the Sparcle processor, ASIM can alternatively derive its input from a dynamic post-mortem trace scheduler, shown on the right side of Figure 3-2. Post-mortem scheduling is a technique that generates a parallel trace from a uniprocessor execution trace with embedded synchronization information [19]. The post-mortem scheduler is coupled with the memory system simulator and incorporates feedback from the network in issuing trace requests, as described in [50]. The use of this input source is important because it allows the workload set to include large parallel applications written in a variety of styles. Section 4.2.1 describes four of the benchmarks simulated by ASIM.

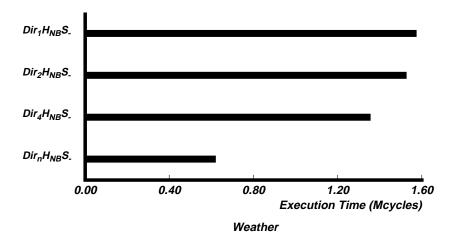

The simulation overhead for large machines forces a trade-off between application size and simulated system size. Programs with enough parallelism to execute well on a large machine take an inordinate time to simulate. When ASIM is configured with its full statistics-gathering capability, it runs at about 5,000 processor cycles per second on an unloaded SPARCserver 330 and about 20,000 on a SPARCstation 10. At 5,000 processor cycles per second, a 64 processor machine runs approximately 80 cycles per second. Most of the simulations in Chapter 4 ran for roughly one million cycles (a fraction of a second on the A-1000), and took 3.5 hours to complete.

To evaluate the potential benefits of a hybrid hardware/software design approach, ASIM models only an approximation of a software-extended memory system. Section 4.2 describes this simulation technique, which justified the effort required to build the A-1000 and NWO implementations of Alewife.

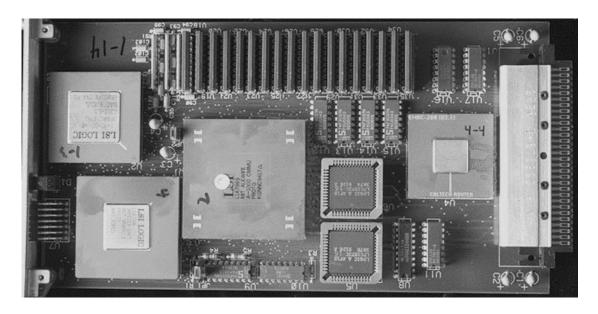

Figure 3-3: A-1000 node board:  $12cm \times 22cm$

#### 3.1.2 A-1000: the Alewife Machine

A-1000, the hardware implementation of the Alewife architecture, ran its first complete program in May, 1994. As of August, 1994, a sixteen node A-1000 and a few smaller machines have been built. Larger machines will come on-line as additional parts are fabricated.

Figure 3-3 shows an A-1000 node, packaged on a 12cm by 22cm printed circuit board. The large component in the center of the board is the A-1000 CMMU [46]. The chip on the lower left side of the CMMU is the Sparcle processor, and a SPARC-compatible floating-point unit is on the upper left corner of Sparcle. The connector on the right side of the board plugs into a back-plane that wires the nodes together. The Caltech EMRC [28] in the package next to the connector routes messages through a two-dimensional mesh network.

The two square packages on the right side of the CMMU hold SRAM chips that implement 64 Kbytes of direct-map cache, which holds both instructions and data. (Sparcle does not have on-board caches.) The bank of DRAM chips on the top of the board contains 2 Mbytes of private memory, 2 Mbytes of coherence directory memory, and 4 Mbytes of the global shared memory space. In addition to the  $512 \times 4$  Mbyte configuration, the A-1000 also implements an option for 128 nodes with 16 Mbytes each.

LSI Logic fabricated the CMMU with a hybrid gate-array process. The chip contains 100,000 memory cells (including the cache tags) and a sea of 90,000 gates of logic. Critical paths in the CMMU limit the system speed. The A-1000 runs reliably at 20 MHz and may be tuned to run close to 30 MHz.

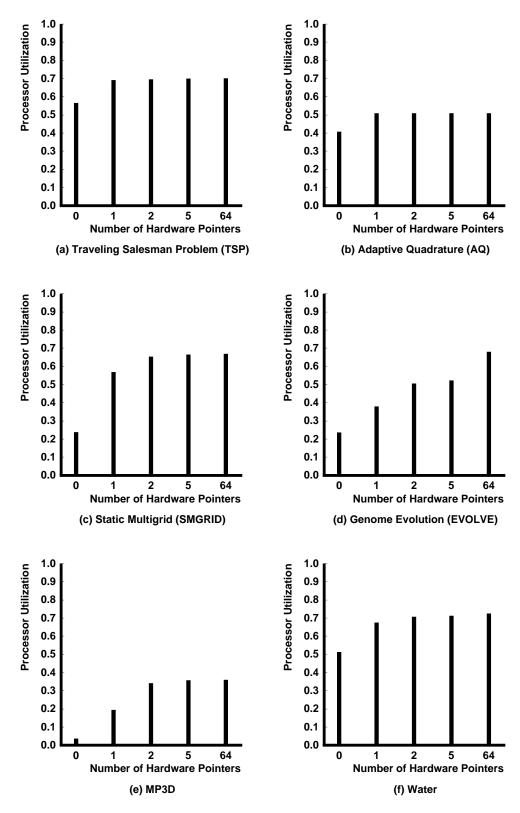

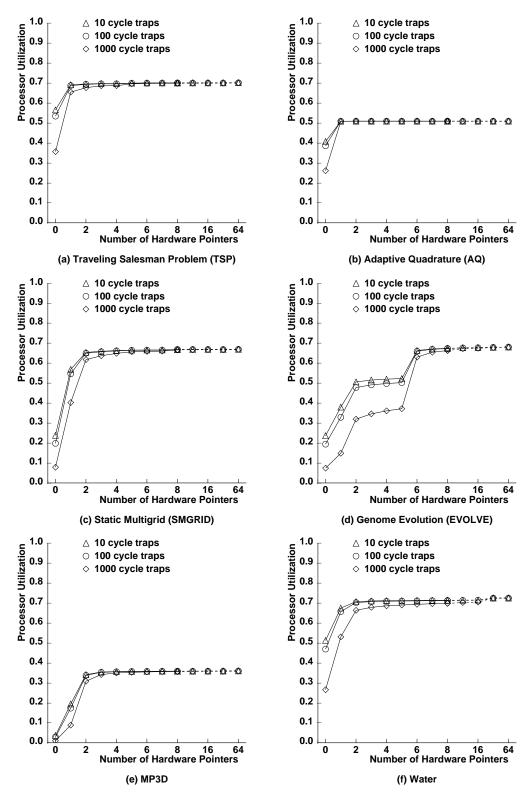

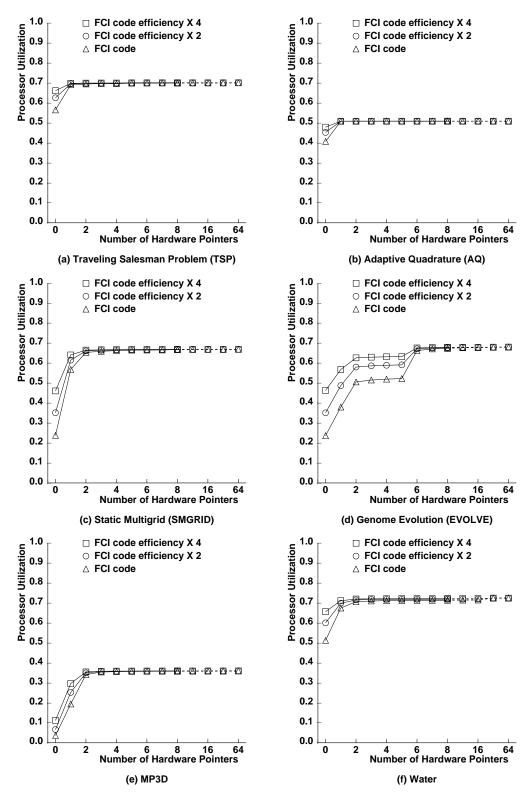

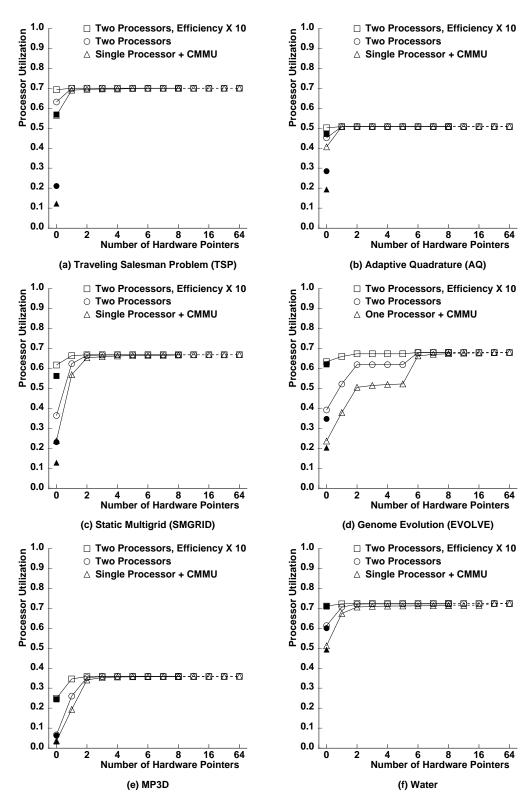

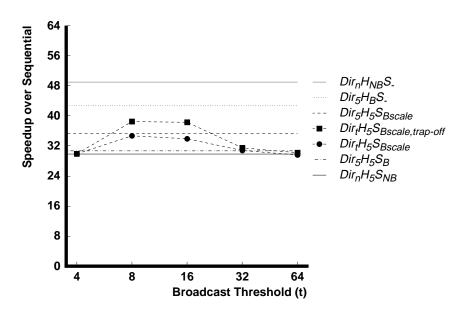

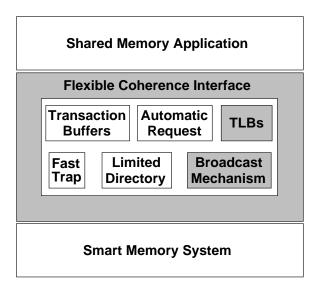

The CMMU was designed using the LSI Logic Concurrent Modular Design Environment (CMD-E). One of the outputs of CMD-E is a network file that specifies the chip's gates and connections. The LSI simulator uses switch-level models to simulate