# PDP-1 COMPUTER ELECTRICAL ENGINEERING DEPARTMENT MASSACHUSETTS INSTITUTE OF TECHNOLOGY CAMBRIDGE, MASSACHUSETTS 02139

# PDP-35

# INSTRUCTION MANUAL

PART 2 -- ADDRESS CALCULATION

December 12, 1971

#### 2.0 Address Calculation

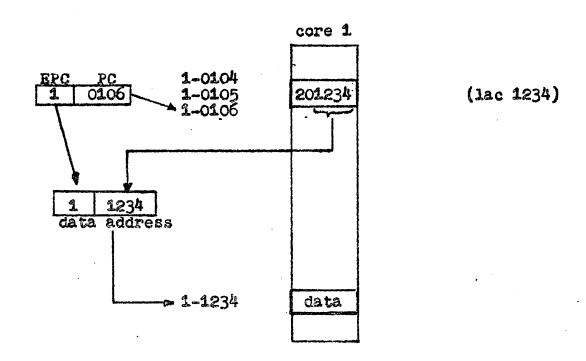

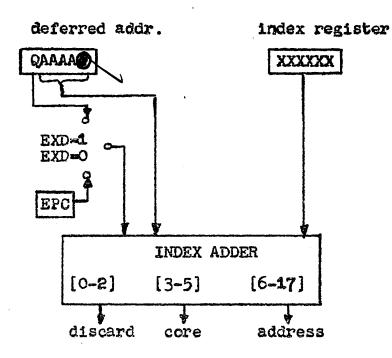

A direct or unmodified data address is calculated by concatenating the Extended Program Counter (the EPC is bits 3-5 of the Gregister) and the address part of the instruction.

Addresses may also be deferred (indirected), indexed, or both (in either order). These operations are said to modify the address specified by the address part of the instruction.

#### 2.1 Indirect Addresses

Under certain conditions an instruction may specify that its address is indirect or deferred. This means that, instead of addressing the data directly, its address part gives the address of a location which contains a "pointer" to (address of) the data location. Each defer cycle takes one extra memory cycle.

Exception: alternated index made, i-bit on

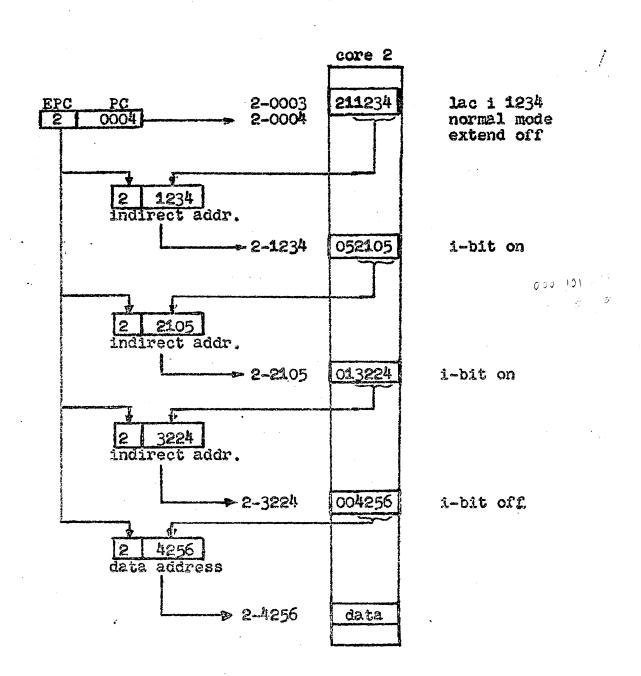

### 2.1.1 Indirect Addresses Out of Enteni Mode

If the computer is not in entend mode (EXD is off), multiple level indirect addressing may be used, but the instruction, all defer cycles, and the final encoute cycle will be in the same core memory module. After each defer cycle, the i-bit (bit 5) of the word read from memory is examined. If it is on, another defer cycle occurs at the address given by the address part of the word. If the i-bit is off, the indirect chain terminates and the address part is used as the actual data address.

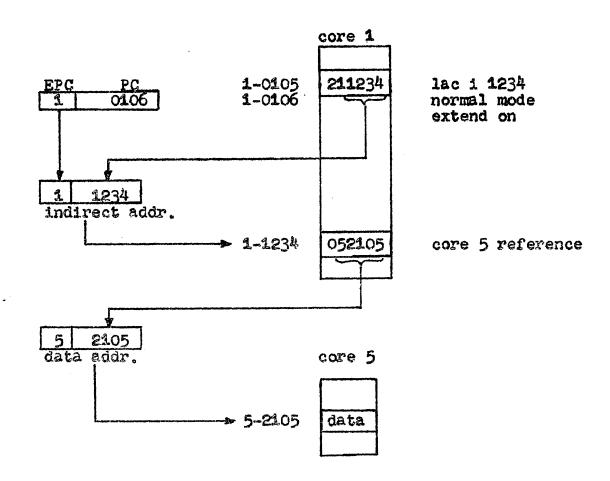

# 2.1.2 Indirect Addresses in Extend Mode

With EXD on indirect addresses are single-level only. This deferred address is taken as a 15-bit quantity which may reference another core.

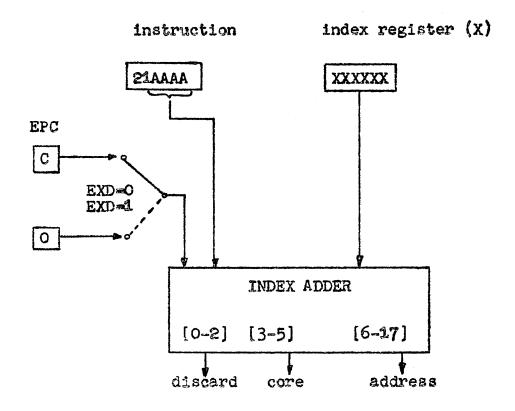

#### 2.2 Indexed Addresses

In various cases addresses will be modified by addition of the contents of the index register (X). Depending on the address mode, indexing can apply to either the address part of an instruction or the last indirect address in a defer chain. The index adder is 18 bits long, having the 18-bit index register as one input and a 15-bit address as the other. The sum is computed in the current arithmetic mode (one's or two's complement). In one's complement mode, minus zero is changed to plus zero. The sum is then truncated to 15-bits for use as the data address.

Indexing alone does not lengthen the execution time of an instruction.

# 2.2.1 Indexing an Instruction

If the machine is not in extend mode, index sums are relative to the current core. That is, the EPC is added in to bit positions 3 to 5. If EXD is on, zero is added into these positions so that the index sums are absolute (relative to core 0).

# 2.2.2 Indexing a Deferred Address

A deferred address may also be indexed. If the computer is not in extend mode, the address part of the deferred address and the EPC are used. If EXD is on, the low 15 bits of the deferred address are used.

Indexing of indirect addresses applies only on the last defer cycle.

#### 2.3 Address Modes

The PDP-1 has four address modes -- normal, base, index (first), and defer (first). The AMD and AEF flip-flops determine which mode the machine is in.

Regardless of the address mode, jump-type instructions (imp. isp. ida, idp) behave as if they are in normal mode (cf.). ida (Op. Code 17) always behaves as if its i-bit were off.

The address mode may be temporarily changed by the <u>aam</u> instruction, 770056, which turns on the address alternation flip-flop AAL is automatically cleared at the end of the following instruction. The effect of an <u>aam</u> depends on the address mode and will be discussed separately for each of the four.

Note a jdp, jda, jmp, or jsp immediately following an aam will be executed in base mode, since the nominal mode for these instructions is normal mode.

The <u>cal</u> instruction always behaves the same (goes to core 0, location 100) regardless of the address mode.

xct instructions behave like any other addressable instruction with respect to address modes and being preceded by aam instructions. The instruction xct'd is always in the nominal mode, as determined by AMD and AEF. If there were an aam over the xct, it would affect only the xct, and not the instruction xct'd.

# Two gam's in a row leave AAL off.

#### 2.3.1 Normal Mode

This is the only mode a normal PDP-1 operates in. The machine will be in this mode if any of the console buttons except STOP or CONTINUE is pressed. The timesharing system initializes processes to be in normal mode.

Normal mode is entered by executing a <u>nam</u> instruction, which clears both AMD and AEF. In normal mode addresses are direct if the i-bit is off and indirect if it is on. See section 2.4.1 for examples.

An <u>aam</u> in normal mode causes indexing to be applied regardless of whether the i-bit is on or not. Indexing happens before indirecting if both are specified. See section 2,4,2 for examples of alternated normal mode.

#### 2.3.2 Ease Mode

In base mode the index register usually points to the base of a "private block" associated with the specific process that is executing reentrant code. All addressable instructions (except jump-type instructions) are indexed into the private block.

Base mode is identical to alternated normal mode. In base mode AMD is off and AEF is on. Base mode is entered by executing a bam instruction. See section 2.4.2 for examples.

Alternated base mode is identical to normal mode. That is, never index and indirect only if the i-bit is on. See 2.4.1 for examples.

#### 2.3.3 Index and Defer Modes

An iam instruction puts the PDP-1 in index mode (AMD-1, AEF-0), and a dam instruction puts it in defer mode (AMD-1, AEF-4). The only difference in these two modes is the order in which indexing and indirecting are done if both are specified. Index mode indexes first, while defer mode defers first.

In unalternated index or defer mode addresses are direct if the i-bit is off and indexed if it is on. See section 2.4.3 for examples.

When in alternated index or defer mode, instructions always defer and if the i-bit is on, they also index. The order is determined by the mode. Section 2.4.4 contains the examples of alternated index mode, and section 2.4.5 has the alternated defer mode examples.

2,3,4 Summary of Address Modes

| Mode     | AMD    | AEF     | AAL    | Indirect                | Index                                 |

|----------|--------|---------|--------|-------------------------|---------------------------------------|

| normal   | 0      | 0       | 0      | if 1-bit on if 1-bit on | no yes (index first if both)          |

| base<br> | 0<br>0 | 8-4 9-4 | 0      | if i-bit on if i-bit on | yes (index first if both)             |

| index    | ₹<br>4 | 0       | 0      | no<br>yes               | if i-bit on (index first)             |

| defer    | I<br>I | 1       | 0<br>1 | no<br>yes               | if i-bit on if i-bit on (defer first) |

# 2,4 Examples

# 2.4.1 Normal Mode or Alternated Base Mode

|     | nam<br>lac 30 | <b>OR</b> |     | bam<br>aam<br>lac 30 |

|-----|---------------|-----------|-----|----------------------|

|     | o             |           |     | •                    |

|     | •             |           |     | •                    |

| 30/ | 105           |           | 30/ | 105                  |

The accumulator is loaded from location 30 of the current core. No index or defer happens.

|                 | nam<br>lec i 30 | OR              | bam<br>aam<br>lac i 30 |

|-----------------|-----------------|-----------------|------------------------|

|                 | •               |                 |                        |

|                 | Ġ               |                 | ð                      |

| 30/<br>105/     | 10105<br>1234   | 30/<br>105/     | 10105<br>1234          |

| 1234/<br>10105/ | 3 6             | 1234/<br>10105/ | 3                      |

If the computer is not in extend mode, A is loaded with 3 after two defers. If EXD is on, a single extended defer happens, picking up the 6 from core 1.

#### 2,4,2 Ease Mode or Alternated Normal Mode

Assume X has +10 in it.

|            | bam<br>lac 3 | 30 | OR |            | nam<br>aam<br>lac 30 |

|------------|--------------|----|----|------------|----------------------|

|            | e            |    |    |            | •                    |

|            | •            |    |    |            | <b>Q</b>             |

| 30/<br>40/ | 105<br>21    |    |    | 30/<br>40/ | 105<br>21            |

The effective address is 30+(contents of X) = 40. Thus, 21 is put into A.

Assume X contains 777770.

|                   | bam<br>lac 70     | OR |                   | nam<br>aam<br>lac 70 |

|-------------------|-------------------|----|-------------------|----------------------|

|                   | ٥                 |    |                   | o                    |

|                   | ٥                 |    |                   | 0                    |

| 60/<br>61/<br>70/ | 105<br>144<br>-10 |    | 60/<br>61/<br>70/ | 105<br>144<br>-10    |

The effective address is 70+(contents of X). This aum differs in one's and two's mode. In one's mode, the effective address is 61 and therefore 144 is put into A. In two's mode, the effective address is 60 and accordingly 105 is placed into A.

Assume X has 10100 in it and the same program is in core 2. If the machine is not in extend mode, the index address is relative to the current core (2). Thus, the effective address is 20000+10100+30=30130 or location 30 of core 3. If EXD is on, the effective address is 10130 or location 130 of core 1.

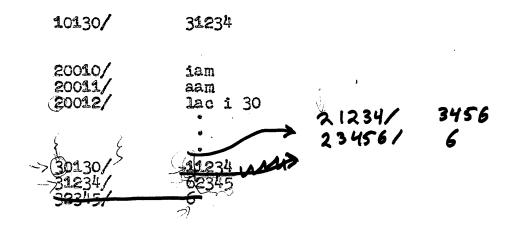

Consider the following program in case 2 with 10100 in X,

| 10130/                     | 31234               | 10130/                            | 31234                  |

|----------------------------|---------------------|-----------------------------------|------------------------|

| 20010/                     | bam<br>lac i 30     | 2000 <b>7/</b><br>200 <b>1</b> 0/ | nam<br>aam<br>lac 1 30 |

| 204221                     | 0<br>0              | 204 20 /                          | g<br>g                 |

| 30130/<br>31234/<br>32345/ | 11234<br>62345<br>6 | 30130/<br>31234/<br>32345/        | 11234<br>62345<br>6    |

Out of extend mode, a defer chain is started at (address part) + (index register) + (current core) = 130 of core 3. Two defers happen and 6 is finally loaded into the accumulator.

In extend mode a single extended defer is done through core 1 location 130. This location points to core 3 location 1234, so that 62345 is put into A.

# 2.4.3 Unalternated Index or Defer Mode

iam /or dam lac 30

No index or indirect modifications happen. The accumulator is leaded with 105.

Assume the following program is in core 2 and X has 10100 in it.

10130/ 6

20010/ iam /or dam

20011/ lac 1 30

...

30130/ 11

Only indexing can happen. Out of extend mode the effective address is (contents of X) + (address part) + (current core) = 30130 or location 130 of core 3. Eleven is put into A.

In extend mode the reference will be to 10130 or location 130 of core 1. Six will be put into A.

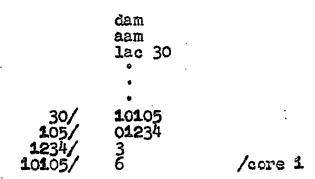

#### 2.4.4 Alternated Index Mode

iam aam lac 30 10105 01234

/core 1

No indexing occurs, but the instruction defers through location 30 of the same core. If EXD is on, this is an extended defer and the accumulator gets loaded with 6. If EXD is off, two defers happen and A picks up the 3 from location 1234.

10100 in it and the following program is in Assume X has core 2.

In index mode indexing happens before defering. Thus, out of extend mode a two-level defer chain is started at location 130 of core 3. This ends by loading the accumulator with 6. In extend mode a single extended defer is done through 130 of core 1, and A is loaded with 62345.

#### 2.4.5 Alternated Defer Mode

No indexing occurs. Out of extend mode, the instruction defers through location 30 and again through 105, resulting in 3 being put into the accumulator. In extend mode, a single defer causes the 6 in location 105 of core 1 to be loaded.

In the next program assume that core 2 is current and the index register contains 10100.

| 11234/                     | 17730                  |

|----------------------------|------------------------|

| 20010/<br>20011/<br>20012/ | dam<br>aam<br>lac i 30 |

|                            | 4                      |

| 20030/<br>21234/<br>21334/ | 11234<br>2345<br>3     |

| 32445/                     | б                      |

In alternated defer mode defers happen before indexing. Thus, out of extend mode, the lac i 30 will defer twice, resulting in 2345 which will be added to the index register and current core(2), resulting in a final effective address of core 3 location 2445. Six would be loaded into A.

With EXD on, a single defer happens through 30 of core 2. Then 11234 is added to the index register, giving a final address of 21334. Therefore, the accumulator is loaded with 3.

# 2.5 Instructions that Affect Effective Address Calculation

| Mnemonio | Op. Code | Function                                                                                                                    |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| nam      | 770052   | enter normal address mode                                                                                                   |

| bam      | 770053   | enter base address mode                                                                                                     |

| iam      | 770054   | enter index (first) address mode                                                                                            |

| dam      | 770055   | enter defer (first) address mode                                                                                            |

| aam      | 770056   | cause 1-instruction mode change                                                                                             |

| eem      | 770046   | enter extend mode                                                                                                           |

| lem      | 770047   | leave extend mode                                                                                                           |

| lpf      | 770051   | loads AMD, AEF, AAL from I[0-2].<br>See section 1.3.4<br>However- AAL will be turned off at<br>the end of this instruction. |

# 2.6 Sample Programs

The following are examples of uses of the various address modes and the index register.

# 2,6.1 Exchange Array Contents

The following program segment exchanges the contents of two arrays, named array1 and array2. Both are 400 words long. In this example the index register is used both as a counter and an increment into the arrays.

|                                     | iam or dam<br>should be considered<br>in which the program | i in the same arithmetic<br>n runs        |

|-------------------------------------|------------------------------------------------------------|-------------------------------------------|

| exchng,<br>next,                    | lxr (-400<br>lac i array1+400<br>lio i array2+400          | /minus the length to X /pick up the words |

|                                     | dio i array1+400                                           | /put back exchanged                       |

| done,                               | dac i array2+400<br>SXXZ<br>jmp next                       | /add 1 to X,skip if up to 0 /not done     |

| array1+0/<br>array1+1/<br>array1+2/ | array2-                                                    | +1/+2/                                    |

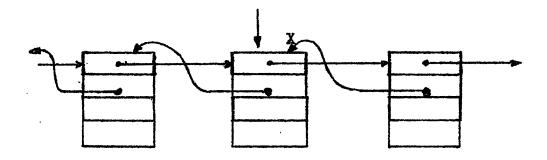

# 2.6,2 Unchain a Data Block

In a certain application data blocks are chained as shown below. Word zero is a forward pointer. Word one is a back pointer. The subroutine given below will delete the block pointed to by the index register. In this situation the index register always contains the address of the base (word 0) of a block.

block to be deleted

/jdp rmb in iam /X points to block to be deleted

| rmb. | 0         |                                        |

|------|-----------|----------------------------------------|

| -    | lio i O   | /I points to block on right            |

|      | aam       |                                        |

|      | dio i 1   | /index then indirect to fix left block |

|      | lac i 1   | /A points to left block                |

|      | TIX       | /move to right block                   |

|      | dac 1 1   | /fix back pointer                      |

|      | jmp i rmb | /return                                |