Memorandum 6M-5780

#### Sheet 1 of 15 Sheets

Division 6 — Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

SUBJECT: SOME EXAMPLES OF TX-2 PROGRAMMING

To: Distribution List

From: H. Philip Peterson H. Philip Peterson

Date: July 23, 1958

Approved: WAC

Abstract: Six short programs are presented here to illustrate many of the somewhat inscrutable features of TX-2 programming. These programs are called:

I: A Checkerboard Pattern Generator

- II: The Inchworm

- III: The Memory Mirror

IV: An Autocorrelation Program

V: The Flexo-Octal Converter

VI: A Binary Read-in Routine

Distribution List:

Group 63 Staff Arden, Dean (Barta) Arnow, J. Attridge, W. Bagley, P. R. Bailey, D. Briscoe, H. Buzzard, R. Daggett, N. Dinneen, G. P. Dustin, D. E. Forgie, Carma Vance, R. R.

Frachtman, H. E. Frick, F. Grandy, C. Hazel, F. P. Heart, F. Holmes, L. Israel, D. Mason, Wm. Pughe, E. (Servo Lab.) Rising, H. K. Thomas, L. M. Tritter, A. L. Zraket, C. A.

1. This document has been prepared for internal use only. It has not been reviewed by Office of Security Review, Department of Defense, and therefore, is not intended for public release. Further dissemination or reproduction in whole or in part of the material within this document shall not be made without the express written approval of Lincoln Laboratory (Publications Office). 2. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No AF 19 (122)-458.

## INTRODUCTORY REMARKS

The six example programs presented in this paper illustrate many of the somewhat inscrutable features of TX-2 programming. A few assumptions, however have been made by the author about the reader. These assumptions are:

- 1) that the reader knows how to program;

- 2) that the reader is familiar with TX-2 nomenclature: (this familiarity may be attained by studying "The Lincoln TX-2 Computer," (6M-4968); and

- 3) that the reader has a copy of "The TX-2 Programmer's Guide" for reference (6M-5807).

## NOTATION

The code part of each instruction is written as a group of 3 capital letters (ADD, JMP, etc.). Any superscript numbers preceding the code part refer to a <u>configuration memory</u> location, except for JPX, JNX, JMP and SKM instructions. Superscript numbers following a code refer to an <u>index memory</u> location except for SKM type instructions where this is the number of the bit in the addressed word. Lower case numbers following a code are main memory addresses.

A colon means "hold control until the next instruction." Brackets mean "defer the address" and imply that bit 2.9 of the address is a ONE. Lower case letters are hopefully self-explanatory.

To the left of many instructions will be an explanatory notation using four little lines which show the permutation involved by how they cross; the active quarters of central machine registers by arrowheads, and, when necessary, the fracture (or coupling or subwords) by little cups. This configuration will be specified by the contents of the indicated configuration memory word.

A number or word followed by "slash equals" defines the address of the instruction or constant to the right of it. A word followed by "equals slash" is the name of the register following.

An address section with a large L prefixing it, as in 763 of Program I, means the address of "a register containing what is indicated."

All numbers in programs are octal unless otherwise indicated. Numbers are punctuated with commas separating the meaningful portions of the whole 36 bit word. A single comma separates 9 bit (3 octal digit) quarters when the word is dealt with in quarters. Two consecutive commas will separate the word into 18 bit (6 octal digit) pieces.

2.

## I. A Checkerboard Pattern Generator

## The Problem

When a core memory is being checked for operating margins, a "bad" pattern of ONES and ZEROS is desired. (see Engineering Note E-488). One of the worst conditions starts with a checkerboard pattern which looks like this in each memory plane:

The complement of this pattern is also a checkerboard. The addresses increase from left to right and top to bottom beginning with address 000 at the upper left. In the case of a 256<sup>2</sup> memory plane, it takes 8 bits to address a row or a column (16 address bits in all).

If one computes the parity of the two least significant bits of the row address and the two least significant bits of the column address, one will find that if the parity of these four bits is odd, a ONE will be at that address; if even, a ZERO will be there.

The problem is to construct a program which generates this pattern in all 65,536 bits of each memory plane. The program must fit into the 16 toggle switch registers.

#### The Solution

Program I generates the checkerboard pattern by using four SKZ instructions to look at the two sets of least-significant address bits. These bits are 1.1, 1.2, 1.9 and 2.1. When any one of them is a ONE, the SKZ doesn't skip and an MKC is executed which complements bit 3.1 of the E register. After examining the four address bits, E register bit 3.1 will be ZERO for an even parity or ONE for an odd parity. The whole address is kept in index register 1 and the DPX at 751\* puts the address in the right half of the E register, leaving the left half all ZEROS since configuration 0 is used. After computing the parity, the left half of E is put in index register 2 and the LDE at 763\* puts the word at 766 in E if the parity is even, or the word at 767 if it is odd. The word in E is stored away at the address and the address is counted down. The address was reset by the RSX in 750 to 177,777. This number is kept in the A register (377,740) which is being simulated by a toggle switch register as of this writing.

\*The three most significant octal digits of addresses (377 in toggle switch addresses) will be omitted for brevity's sake.

|                  |         | 6M-5780 3 <b>.</b>                                 |

|------------------|---------|----------------------------------------------------|

| OCTAL EQUIVALENT | ADDRESS | SYMBOLIC                                           |

| 02 11 01 377,740 | 377 750 | 2RSX1 177,777                                      |

| 00 16 01 377,744 | 751     | ↓↓↓↓,°DPX1 e reg←                                  |

| 10 17 41 377,744 | 752     | SKZ <sup>2.1</sup> e reg                           |

| 03 17 61 377,744 | 753     | MKC <sup>3 • 1</sup> e reg                         |

| 10 17 31 377,744 | 754     | SKZ <sup>1,9</sup> e reg                           |

| 03 17 61 377,744 | 755     | MKC <sup>3,1</sup> e reg                           |

| 10 17 22 377,744 | 756     | SKZ <sup>1</sup> • <sup>2</sup> e reg <sub>7</sub> |

| 03 17 61 377,744 | 757     | MKC <sup>3.1</sup> e reg                           |

| 10 17 21 377,744 | 377 760 | SKZ <sup>1</sup> · <sup>1</sup> e reg              |

| 03 17 61 377,744 | 761     | MKC <sup>3</sup> ol e regi                         |

| 02 11 02 377,744 | 762     | 2RSX <sup>2</sup> e reg <sup>k</sup>               |

| 00 20 02 377,766 | 763     | 1 1 1 1 oldes [word                                |

| 00 30 01 000,000 | 764     | JJJJ, <sup>o</sup> STE <sup>1</sup> memory         |

| 36 06 01 377,751 | 765     | -1JPX <sup>1</sup> next                            |

| 00 05 00 377,750 | 766     | (word) JMP restart                                 |

| 77 72 77 400 027 | 767     | (- word)                                           |

|                  |         |                                                    |

Program I

A Checkerboard Pattern Generator

|                  |         | 6M-5780 3a                                                                                      |

|------------------|---------|-------------------------------------------------------------------------------------------------|

| OCTAL EQUIVALENT | ADDRESS | SYMBOLIC                                                                                        |

| 02 11 01 377,740 | 377 750 | ≥ 2RSX <sup>1</sup> [177,777 ←                                                                  |

| 00 16 01 377,744 | 751     | $\sqrt{1 + \sqrt{1}}^{\circ}$ DPX <sup>1</sup> e reg                                            |

| 10 17 41 377,744 | 752     | SKZ <sup>2.1</sup> e reg                                                                        |

| 03 17 61 377,744 | 753     | MKC <sup>3</sup> ·1 e reg                                                                       |

| 10 17 31 377,744 | 754     | SKZ <sup>1</sup> • <sup>9</sup> e reg                                                           |

| 03 17 61 377,744 | 755     | MKC <sup>3,1</sup> e reg                                                                        |

| 10 17 22 377,744 | 756     | SKZ <sup>1</sup> • <sup>2</sup> e reg                                                           |

| 03 17 61 377,744 | 757     | MKC <sup>3.1</sup> e reg                                                                        |

| 10 17 21 377,744 | 377 760 | SKZ <sup>1</sup> · <sup>1</sup> e reg                                                           |

| 03 17 61 377,744 | 761     | MKC <sup>3</sup> •1 e reg                                                                       |

| 02 11 02 377,744 | 762     | 2RSX <sup>2</sup> e reg                                                                         |

| 00 20 02 377,766 | 763     | ↓↓↓↓ <sup>o</sup> LDE <sup>2</sup> word                                                         |

| 00 30 01 000,000 | 764     | $\downarrow \downarrow \downarrow \downarrow \downarrow$ , <sup>o</sup> STE <sup>1</sup> memory |

| 36 06 01 377,751 | 765     | <sup>-1</sup> JPX <sup>1</sup> next                                                             |

| 00 05 00 377,750 |         | (word) JMP restart                                                                              |

| 77 72 77 400 027 | 767     | (- word)                                                                                        |

•

Program I A Checkerboard Pattern Generator

6M-5780

4.

Note that the word stored away for even parity is the JMP instruction at 766 which restarts the process after the address has been counted down through 000. If one wishes to write the pattern just once, put ALL ZEROS in 766 and ALL ONES in 767. TX-2 will halt with an illegal instruction alarm (ICSAL) if it tries to execute an instruction with 00 as the operation code. Putting +0 in 766 and -0 in 767 has the advantage that the checkerboard patterns in each digit plane will be identical.

## Exercises To Prove To Yourself That You Really Understand

By changing a single toggle switch, the checkerboard pattern will be complemented. Which switch? (Hint: any one or three of four will do.)

What would you do to put the pattern just in the lower addressed half of memory? Upper half? Middle quarter?

Two memory planes of the 38 will not have a checkerboard pattern in them. They are the parity bit plane and the meta bit (4.10) plane. What program changes will put the pattern in either plane? (Note: only an SKM can modify a meta bit.)

## 5.

## II. The Inchworm

## The Problem

A classical programming exercise is to design a routine which will move itself along through memory, carrying with it as it goes all necessary constants for repeating this "inchworm" process. The program for starting the inchworm on its way must fit into TX-2's 16 toggle switch storage registers, naturally.

## The Solution

Program II solves the problem by storing in registers 001 - 007 the program shown. This program in 001 - 007 then forms the one in 010 - 016 which duplicates itself in 017 - 025 and so on. The program in togs works like the ones in main memory except for a few special setting up instructions.

The SPF instruction in 752 specifies that configuration 34 will permute quarter 3 into quarter 1 and extend its sign into quarter 2. The RSX in 755, 1, 10, etc. uses this oddball configuration to reset index register 71 to a -6 from quarter 3 of registers 762, 6, 15, etc. This trick allows the inchworm program to avoid carrying constants per se along with it. Each "old" inchworm setment can simply "fall" into the newly formed one without jumping around some constants.

Index register 2 contains the constant necessary for the program to move itself into the next location. When moving from togs to core memory, this constant is 400 023 and the RSX in 753 fixes it up. When moving on in core memory, this constant is 000,007 and the RSX in 764 sets it up.

The RSX in 754 resets index register 3 to snap back to togs after the last address desired is reached. For illustrative purposes the address constant 577,760 was chosen. Since the JPX in 763, 7, 16 etc. jumps when the index register is positive, for our purposes it must be negative until the end is reached. Consequently 400,000 is added to 177,760 and that number (577,760) is set up in left half of 750. Each time an inchworm "segment" is executed, the corresponding JPX will subtract 7 from the contents of index register 3. When control gets to the segment in 177,757 - 766, index register 3 will have become positive and control will be transferred to togs (after a segment is written into 177,767 to 75) starting the process over again.

The routine in 755 to 763 maps itself into 000 to 007, preserving the address parts of the instructions in 757, 760 and 763 as they go to 003, 004, and 007 by the action of the SKN in 757 which skips over the ADX when bit 3.2 of a word is a ONE. These three invariant instructions refer to fixed locations so they must not be changed by the ADX as the other four are. Bit 3.2 was arranged to be ONE in the invariant instructions and ZERO in the variable instructions.

|                                             |                                       |           | 6M∞5780                               | 6.     |

|---------------------------------------------|---------------------------------------|-----------|---------------------------------------|--------|

| OCTAL EQUIVALENT                            | ADDRESS                               |           | SYMBOLIC                              | 08     |

| 577 760,,400 023                            | 377 750                               | last add  | ress,,1st co                          | nst    |

| 362                                         | 751                                   | C         | onfig 34 set                          | ; up   |

| 34 21 00 377,751                            | 752                                   | 111       | <sup>34</sup> SPF 377,                | 751    |

| 01 11 02 377,750                            | 753                                   | 11, + 1   | <sup>1</sup> RSX <sup>2</sup> 377,    | ,750   |

| 02 11 03 377,750                            | 754                                   |           | 2RSX <sup>3</sup> 377                 | ,750   |

| 74 11 71 377,762                            | 755                                   |           | : <sup>34</sup> RSX <sup>71</sup> 377 | ,762   |

| 40 20 71 377,763                            | 756                                   | 1111      | : <sup>0</sup> LDE <sup>71</sup> 377, | ,763¢  |

| 54 17 62 377,744                            | 757                                   |           | : SKN <sup>3</sup> ° <sup>2</sup> e 1 | reg    |

| 41 15 02 377,744                            | 377 760                               | 11,14     | : <sup>l</sup> ADX <sup>2</sup> e 1   | reg    |

| 40 30 71 000,007                            | 761                                   |           |                                       | ,007   |

| 41 0 771 377,756                            | 762                                   |           | : +1 JNX 71 377                       | ,756 J |

| 70 06 03 377,752                            | 763                                   |           | : <sup>-7</sup> JPX <sup>3</sup> rest | tart   |

| 41 11 02 377,761                            | 764                                   | 1111      | : <sup>1</sup> RSX <sup>2</sup> 377   | ,761   |

| 01 15 02 377,744                            | 765                                   |           | , <sup>1</sup> ADX <sup>2</sup> e 1   | reg    |

| 01 30 00 000,005                            | 766                                   | 1111      | <sup>1</sup> STE 5                    |        |

| 00 05 00 000,001                            | 377 767                               |           | JMP 1                                 |        |

|                                             |                                       |           | · · · · · · · ·                       |        |

| This program                                | then forms                            |           | this one                              |        |

| 001 : <sup>34</sup> RSX <sup>71</sup> 6     | C.                                    | )10       | : <sup>34</sup> RSX <sup>71</sup> 15  |        |

| 2 : $^{\circ}LDE^{71}$ 7                    |                                       | 11        | : <sup>0</sup> LDE <sup>71</sup> 16   | 6      |

| 3 : SKN <sup>3</sup> • <sup>2</sup> 377,744 |                                       | 12        | : SKN <sup>3</sup> ° <sup>2</sup> 37' | 7,744  |

| 4 : <sup>1</sup> ADX <sup>2</sup> 377,744   |                                       | 13        | : <sup>1</sup> ADX <sup>2</sup> 377   | ,744   |

| 5 : <sup>0</sup> STE <sup>71</sup> 16       | n<br>Maria Angla<br>A                 | 14        | : STE <sup>71</sup> 25                |        |

| 6 : <sup>41</sup> JNX <sup>71</sup> 2       |                                       | 15        | : <sup>+1</sup> JNX <sup>71</sup> 11  |        |

| 7 : <sup>-7</sup> JPX <sup>3</sup> 377,752  | د<br>د<br>۲۰ و درو در مدرود اسخ دهمده | 16        | : <sup>-7</sup> JPX <sup>3</sup> 377  | ,752   |

|                                             | and so on.                            | ,<br>p``o |                                       |        |

|                                             |                                       |           |                                       |        |

Program II The Inchworm

| and a second second<br>Second second |                        |                                               |                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------|-------------------------------------------|

| OCTAL EQUIVALENT                                                                                                                                                                                                                  | ADDRESS                |                                               | 6м-5780 ба.<br>SYMBOLIC                   |

| 577 760,,400 023                                                                                                                                                                                                                  | 377 750                | last add                                      | ress,,1st const                           |

| 362                                                                                                                                                                                                                               | 751                    | C                                             | onfig 34 set up                           |

| 34 21 00 377,751                                                                                                                                                                                                                  | 752                    | 111                                           | <sup>34</sup> SPF 377,751                 |

| 01 11 02 377,750                                                                                                                                                                                                                  | 753                    |                                               | <sup>1</sup> RSX <sup>2</sup> 377,750     |

| 02 11 03 377,750                                                                                                                                                                                                                  | 754                    |                                               | <sup>2</sup> RSX <sup>3</sup> 377,750     |

| 74 11 71 377,762                                                                                                                                                                                                                  | 755                    | ~~~                                           | : <sup>34</sup> RSX <sup>71</sup> 377,762 |

| 40 20 71 377,763                                                                                                                                                                                                                  | 756                    |                                               | : <sup>0</sup> LDE <sup>71</sup> 377,763  |

| 54 17 62 377,744                                                                                                                                                                                                                  | 757                    |                                               | : SKN <sup>3•2</sup> e reg                |

| 41 15 02 377,744                                                                                                                                                                                                                  | 377 760                | 11.11                                         | : <sup>1</sup> ADX <sup>2</sup> e reg     |

| 40 30 71 000,007                                                                                                                                                                                                                  | 761                    | $\downarrow \downarrow \downarrow \downarrow$ | : STE <sup>71</sup> 000,007               |

| 41 0 771 377,756                                                                                                                                                                                                                  | 762                    |                                               | : <sup>+1</sup> JNX <sup>71</sup> 377,756 |

| 70 06 03 377,752                                                                                                                                                                                                                  | 763                    |                                               | : <sup>-7</sup> JPX <sup>3</sup> restart  |

| 41 11 02 377,761                                                                                                                                                                                                                  | 764                    | 1111                                          | : <sup>1</sup> RSX <sup>2</sup> 377,761   |

| 01 15 02 377,744                                                                                                                                                                                                                  | 765                    |                                               | <sup>1</sup> ADX <sup>2</sup> e reg       |

| 01 30 00 000,005                                                                                                                                                                                                                  | 766                    | HILL                                          | <sup>1</sup> STE 5                        |

| 00 05 00 000,001                                                                                                                                                                                                                  | 377 767                |                                               | JMP 1                                     |

| This program                                                                                                                                                                                                                      | then form              | 8                                             | this one                                  |

| 001 : <sup>34</sup> RSX <sup>71</sup> 6                                                                                                                                                                                           |                        | 010                                           | : <sup>34</sup> RSX <sup>71</sup> 15      |

| 2 : <sup>°</sup> LDE <sup>71</sup> 7 ←                                                                                                                                                                                            |                        | 11                                            | : <sup>o</sup> LDE <sup>71</sup> 16       |

| 3 : SKN <sup>3 • 2</sup> 377,744                                                                                                                                                                                                  |                        | 12                                            | : SKN <sup>3,2</sup> 377,744              |

| 4 : <sup>1</sup> ADX <sup>2</sup> 377,744                                                                                                                                                                                         | на.<br>12<br>12 страни | 13                                            | : <sup>1</sup> ADX <sup>2</sup> 377,744   |

| 5 : <sup>o</sup> STE <sup>71</sup> 16                                                                                                                                                                                             |                        |                                               | : STE <sup>71</sup> 25                    |

| 6 : <sup>+1</sup> JNX <sup>71</sup> 2                                                                                                                                                                                             |                        | 15                                            | : +1 JNX 71 11                            |

| 7 : <sup>-7</sup> JPX <sup>3</sup> 377,752                                                                                                                                                                                        |                        | 16                                            | :- <sup>7</sup> JPX <sup>3</sup> 377,752  |

|                                                                                                                                                                                                                                   | and so on              | • • •                                         |                                           |

and so on...

Program II

.

The Inchworm

The "flaw in the ointment" is that register 005 will contain  $400_{9}023 + 000_{9}007 = 400_{9}032$  after the first mapping. The STE instruction in 005 would have a deferred (indirect) reference to 32 and this is clearly bad. It must be changed to a direct reference to 016. This is accomplished by the ADX in 765 which adds the  $000_{9}007$ , which by then is in index register 2, to the  $000_{9}007$  which remains in the right half of the E register (after the RSX in 764) resulting in an  $000_{9}016$  in the E register. The STE in 766 puts it away into 005 and the JMP transfers control to 001 continuing the process in core memory.

# Exercises To Prove To Yourself That You Really Understand

Write a program which uses another approach to the problem of what to put in the 16 toggle switch registers to make core memory look as it does above.

Is it possible to use a JPX in 762 and, if so, what would the program look like then?

## III. Through the Looking Glass

## The Problem

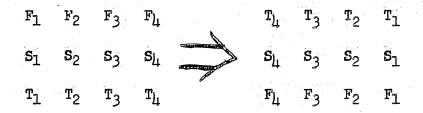

If all the registers in any block of memory registers were laid end to end, what program would put the mirror image of this mess back into the memory block? For example, if the block consisted of three 4-bit words, the transformation would look like this:

## The Solution

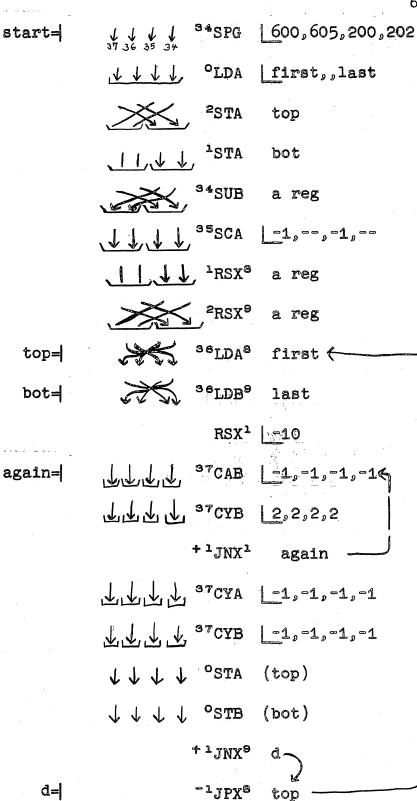

Program III, which is written with floating addresses, performs this mirroring by the use of configurations and simultaneous cycling with only 20 instructions.

Four unusual configurations are needed and these are set up in configuration memory locations 37, 36, 35 and 34 by the SPG instruction.

From some register containing the first and last addresses of the memory block, the A register is set up and the "first" is put into the address section of the LDA instruction called "top," and the "last" is put into the LDB called "bot." The general idea is to index through the block, taking a pair of words at a time and exchanging and reversing them. One word comes from the top half of the block and the other comes from the bottom half. If the block has an odd number of words in it, the first pair will be the middle word used twice. If the block has an even number of words, the first pair will be the middle two words. The last pair dealt with is always the first and last words of the block.

Index register 8 contains a positive number which counts back from the middle of the block to the first. Index register 9 contains a negative number which counts up from the middle to the last. If there are 2n+2 or 2n+1 words in the block, index 8 starts out with +n and index 9 starts out with -n. These numbers are obtained from the first and last addresses after only two instructions. The first instruction is a SUB which subtracts, simultaneously, the last from the first and the first from the last! The left half of the A register then contains -(2n+1) for even blocks and -(2n) for odd blocks. The right half of A contains the complement of the left half.

6M-5780

9.

Done, halt or something ....

Program III Memory Mirror

6M-5780 9a

Done, halt or something...

Program III Memory Mirror

The next instruction, SCA, shifts each half one place to the right, leaving -n in the left half and +n in the right half of A. Index registers 8 and 9 are then set up from the appropriate half of A.

The basic iterative loop starts now and is executed n times. The inner loop is executed 9 times for each of the n times through the outer loop. This number 9 is the number of bits in a quarter of a TX-2 word. If the reader wishes to work through an example with, let's say, 4 bit quarters, then he should go through the inner loop four times. The index register (1) is preset to -8 however, since the JNX jumps on zero.

The STA and STB instructions (at d-3) have deferred addresses which they get from "top" and "bot" respectively. This is actually inefficient timewise if n is greater than 2. Two more instructions when setting up could have put direct references to "first" and "last" in these STA and STB instructions. This would have cost 4 memory time cycles. However, each deferred address costs one memory cycle and so 2n-4 extra memory cycles are being executed in the basic loop. This illustrates how one can trade space for time or vice versa.

The two decimal numbers 8 and 9 were used to indicate general index registers. Of course, 1 is general too.

## Exercises To Prove To Yourself That You Really Understand

One need execute the inner loop only 8 times if a slightly different correction is made afterwards. What are the new correcting cycle instructions?

Configuration 35 is not really needed. What other one used by Program III would serve just as well?

# IV. 50 Million Multiplications Can't Be Wrong

## The Problem

In the analysis of electroencephalographic data, the autocorrelation function of the data is often desired (see B. G. Farley). A specific useful example is the following: about 50 thousand samples are stored away in memory. Each sample is a sign and 8 bits (9 bits in all).

We wish to find

where Sj is the j<sup>th</sup> sample. These 1000 numbers are proportional to the autocorrelation function.

## The Solution

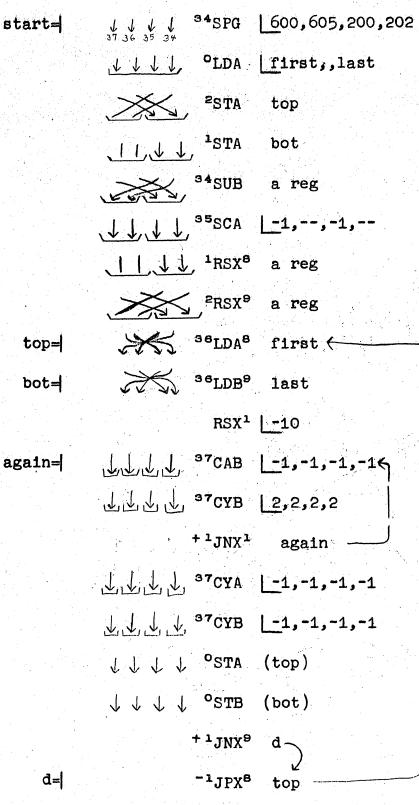

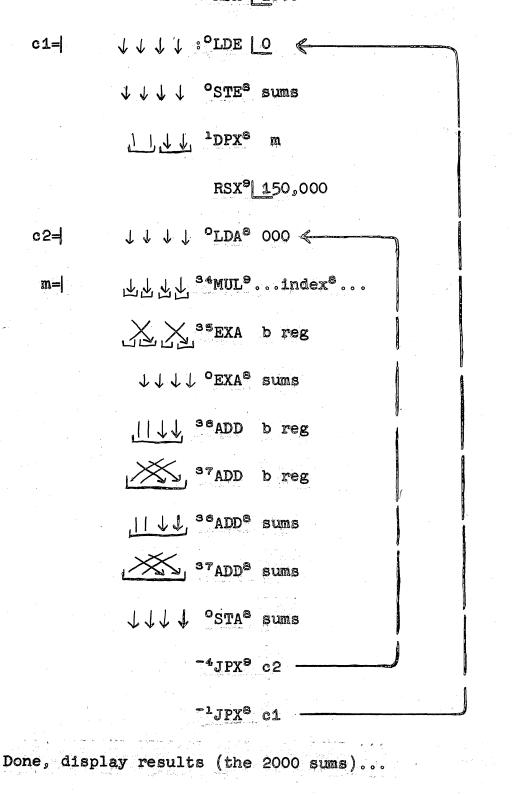

Program IV computes this function in a most efficient way timewise. The key to the speed is to do four multiplications simultaneously. The data, however, must be in memory in a particular format, namely

| 0 | 2   | $s_{1,}$                | s <sub>2</sub> ,       | s <sub>3</sub> ,        | $s_{l_4}$      |

|---|-----|-------------------------|------------------------|-------------------------|----------------|

| 1 |     | <b>s</b> <sub>2</sub> , | s <sub>3</sub> ,       | <b>s</b> 4,9            | s <sub>5</sub> |

| 2 | · . | <b>s</b> 3,             | <b>s<sub>4</sub></b> , | s <sub>5</sub> ,        | <b>s</b> 6     |

| 3 |     | $s_{\mu_9}$             | s <sub>5</sub> ,       | <b>s</b> <sub>6</sub> , | s <sub>7</sub> |

| 4 |     | <b>s</b> 5,             | <b>s</b> 69            | <b>s</b> 7,9            | <b>s</b> 8     |

| 5 |     | <b>s</b> 6,             | <b>s</b> 7,            | <b>S</b> 8,             | s <sub>9</sub> |

Note that there are four of the 9 bit samples  $(S_j)$  in each TX=2 word and that registers 0, 4, etc. and 1, 5, etc. will contain eight different successive samples.

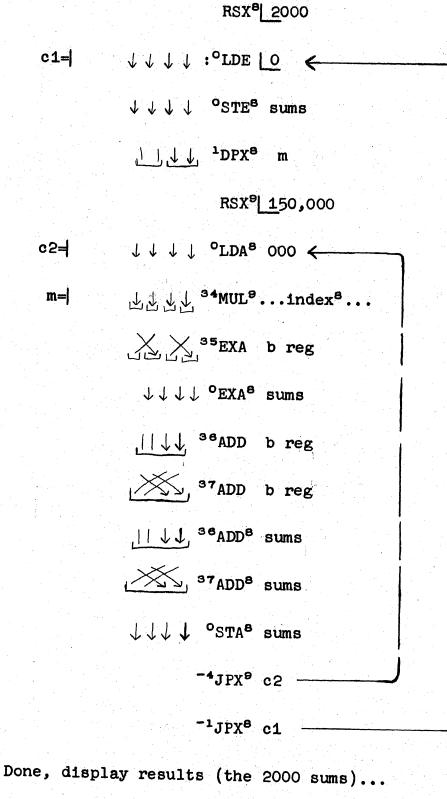

The program starts out by setting up the four special configurations needed and reseting index register 8 to 2000 octal (about 1000 decimal). Index register 8 corresponds to the subscript i in the summation above.

Program IV An Autocorrelation Program

RSX<sup>8</sup> 2000

start=  $1 \downarrow \downarrow \downarrow \downarrow \downarrow 3^{34}$ SPG 142,140,724,600

6M-5780 12.

Program IV An Autocorrelation Program

$\begin{array}{c}

\downarrow \\

\downarrow \\

37 \\

36 \\

35 \\

34

\end{array}$ <sup>34</sup>SPG <u>142,140,724,600</u> start=

6M-5780

12a.

The outer iterative loop then clears the i th current sum register and puts i into the address section of the MUL instruction at m. Index register 9 is set to 150,000 octal (about 50,000 decimal). Index 9 corresponds to the subscript j in the summation. This outer loop is executed about a thousand times.

The inner loop computes one complete summation (fixed i) taking four samples at a time. After the multiplication, the A and B registers look like this:

# $A = P_{1}, P_{2}, P_{3}, P_{4}$ $B = L_{1}, L_{2}, L_{3}, L_{4}$

where P is the most significant 9 bits of the product and L is the least significant.

To eliminate round-off errors, the sums of each whole 18 bit product are accumulated. To put the 9 bit pieces of the product together, the A register is exchanged with the B register in such a manner that the result looks like this:

$$\mathbf{A} = \mathbf{P}_1 \quad \mathbf{L}_{1^{99}} \quad \mathbf{P}_3 \quad \mathbf{L}_3$$

$$\mathbf{B} = \mathbf{P}_2 \quad \mathbf{L}_{2^{99}} \quad \mathbf{P}_{1_4} \quad \mathbf{L}_{1_4}$$

These four 18 bit numbers are then added to the current sum which is a 36 bit number. Notice how the sign extension feature allows a signed 18 bit number to be added to a signed 36 bit number.

Index register 9 is counted down by 4 (11) since only every fourth register of four samples need be multiplied. This means the inner loop is executed only about 13,000 times instead of 50,000 times.

The whole program with its 50,000,000 multiplications will take 8 minutes if the overlapped memory feature is used (i.e. if instructions and data are in different memories).

## Exercises To Prove To Yourself That You Really Understand

The data should extend to register 152,000. Why?

Write a program, using appropriate configurations (no shifting) and the TSD instruction, which will read the samples into memory in the desired format. This program would operate in the Epsco Datrac (an analog-to-digital converter) sequence. Each TSD will put a signed 9 bit number into quarter 1 of the E register. Ignore In-Out Select instructions. Nine instructions will do nicely.

Write a new inner loop to Program IV which handles data with only one sample per word. Five instructions including the JPX will do it. This inner loop will have to be executed the full 50 million times. How long will it take?

# V. The Flexo-Octal Converter

#### The Problem

In the beginning of a binary computer's programming life, it is difficult to communicate with the machine. A series of programs must be written to "bootstrap" one's way into easy communication. This bootstrap series might go like this:

First) A three (or so) word program in toggle switch storage which would allow words to be written into memory one at a time. Call this Pl.

Second) A short routine to convert programs to binary which have been typed on a flexo in a rigid, simple, fixed-address format. Call this P2. Associated with P2 is a program to punch out storage as a binary tape and a program to read in this binary tape. Pl loads P2 into memory. P2 converts the punch-out and read-in programs. The punch-out program punches out P2, the read-in routine and itself. From now on, the read-in routine can read in P2 and the punch-out routine, eliminating the need for Pl.

Third) A longer routine which converts programs typed in a symbolic code, relative-address format. Call this P3. P2 converts P3 and punches it out, eliminating the need for P2.

Fourth) A routine to convert programs typed in a symbolic code, floating address format (P4). P4 is written in P3 format and converted by P3. At this point P1, P2 or P3 aren't needed any more and communication is fairly easy. In TX-0, P4 was called TODAL. A fifth stage might be an algebraic format converter like FORTRAN.

Programs V, VI and VII are proposed examples of the second stage. The <u>octal converter</u> recognizes the eight flexo symbols  $0_{,1,2,3,4,5,6}$ and 7 takes their order into account. Some control characters are needed, such as <u>carriage return</u> to signify the end of a word and slash to allow address specifications. The <u>space</u>, <u>tab</u>, and <u>comma</u> are used to give some format control. The <u>nullify</u> is recognized so that tape "goofs" can be fixed up. The last four are ignored by the converter. A stop code signifies the end-of-tape condition.

## The Solution

The program to do the octal conversion is Program V.

To decide what action to take on each character as it is read in, an Action Table is set up as is shown beside the program. An entry is made at the address, starting at 100, whose last 2 digits correspond to the flexo code of the appropriate character. The right 18 bits of each entry tell where to transfer control when that character is read in, and the left nine bits tell what the binary equivalent is

| 6M-57 | 80 | 15. |

|-------|----|-----|

| 1     |    |     |

|                    | en e |        | 6M-5                                | 780 15.                 |

|--------------------|------------------------------------------|--------|-------------------------------------|-------------------------|

| ACTION TABLE       | Description                              | RC     | OUTINE                              | · · · · · · · · · · · · |

| 105 = 0,0,000 201  | start at $\rightarrow$                   | 200 =  | = :105 <sup>52</sup> read           | unsplayed               |

| 107 = 3,0,000 210  | if slash $\rightarrow$                   | 201    | 11 11, 1STA                         | 213                     |

| 110 = 0,0,000 204  |                                          | 202    | × 2RSX <sup>2</sup>                 | 105                     |

| 113 = 4,0,000 210  |                                          | 203    | 11111°DPX°                          | a reg 🗧                 |

| 117 = 2,0,000 210  | if ignored→                              | 204    | IOS <sup>52</sup>                   | dismiss                 |

| 123 = 5,0,000 210  |                                          | 205    | : TSD                               | e reg                   |

| 125 = 1,0,000 210  | •<br>•<br>•                              | 206    | III,↓ <sup>3</sup> RSX <sup>1</sup> | e reg                   |

| 127 = 7,0,000 210  | < COD                                    | 207    | °JMP <sup>1</sup>                   | (100)                   |

| 133  = 6,0,000 210 | if number→                               | 210    | VVV, °CYA                           | 107                     |

| 145 = 0,0,000 204  |                                          | 211    | ADD1                                | 100                     |

| 151 = 0,0,000 213  |                                          | 212    | JMP                                 | 204                     |

| 161 = 0,0,000 216  | if car/ret→                              | 213    | JUJU OSTA2                          | memory                  |

| 176 = 0,0,000 210  |                                          | 214    | AUX2                                | 125                     |

| 177 = 0,0,000 204  |                                          | 215    | JMP                                 | 203                     |

|                    | l A than a - I -                         | N OA E | ·                                   | 2 - h h h               |

if stop code⇒216

IOS<sup>52</sup>shut off

address = value,0,where to go

The Flexo-Octal Converter Program V

6M-5780

ACTION TABLE Description ROUTINE start at  $\rightarrow$  200| = :IOS<sup>52</sup>read unsplayed 105 = 0,0,000 201107 = 3,0,000 2101f slash  $\rightarrow$  201  $||_{\downarrow}\downarrow_{\downarrow}^{1}$ STA 213 2RSX<sup>2</sup> 105 202 110 = 0,0,000 204, JJJJ, <sup>o</sup>DPX<sup>o</sup> a reg < 113 = 4,0,000 210203 IOS<sup>52</sup> dismiss 117 = 2,0,000 210if ignored  $\rightarrow$  204 123 = 5,0,000 210:TSD 205 e reg 125 = 1,0,000 210III J <sup>3</sup>RSX<sup>1</sup> 206 e reg <2017 €2017 <sup>o</sup>JMP<sup>1</sup> (100) 127 = 7,0,000 210 133 = 6,0,000 210LLLL, °CYA if number  $\rightarrow$  210 107 HJ GADD1 145 = 0,0,000 204211 100 |151| = 0,0,000 213204 212 JMP 161 = 0,0,000 216if car/ret  $\rightarrow$  213  $\downarrow \downarrow \downarrow \downarrow \downarrow$  °STA<sup>2</sup> memory 214 AUX<sup>2</sup> 176 = 0,0,000 210125 177 = 0,0,000 204215 JMP 203

IOS<sup>52</sup>shut off

if stop code  $\rightarrow$  216

address = value,0,where to go

Program V The Flexo-Octal Converter

15a.

when the character is a number. Quarter 3 of each entry is not used.

The IOS in 200 sets the mode of the PETR to read one contiguous 6-bit flexo code (unsplayed) into the right 6 bits of the E register, clearing the other 3 bits in that quarter.

Starting at 203 with a DPX which clears the A register, the character is read in and placed in index register 1. The JMP then <u>defers</u> control to a location specified by the appropriate Action Table entry. Note that all instructions with deferred addresses are indexable.

If the character is a number, then control goes to 210 where the A register is cycled left 3 places and the binary equivalent of the number is added into A, returning control to 204.

If the character is a slash, control "bounces off" register 105 to register 201 where the number in A is stored in 213 and index register 2 reset to a zero. The slash then causes the number that has been built up in A to be the new address of the word which follows.

If the character is a <u>carriage return</u>, 213 has control and stores the word in A away in the proper memory location. The AUX in 214 adds a 1 to index register 2 so that the next time a <u>carriage return</u> appears, the word in A will be stored in the memory register following the last one.

The nullify, space, and tab simply return control to 204 to readin the next character. When a stop code comes along, the IOS in 216 shuts off the photo reader and dismisses the sequence.

The sequence must be dismissed after each character is read and the IOS in 204 does this. The TSD in 205 empties a buffer that has been filled by the PETR. When the buffer is filled, the sequence is activated and the character read-in is dealt with.

## Exercises To Prove To Yourself That You Really Understand

What are the implications of throwing out the IOS in 204 and not holding on the TSD which follows? In other words, let the TSD dismiss the sequence after transferring the data. Work out the new program and format rule(s).

The instructions in 210-11 are on rather shaky ground because TX-2 is an allegedly multi-sequence machine. Some lower priority sequence may have been using the A register and will be very upset at finding it disturbed. What changes will fix this up? Don't forget 20311

Is there anything fishy about the ESX in 206?

## VI. A Binary Read-In Routine

## The Problem

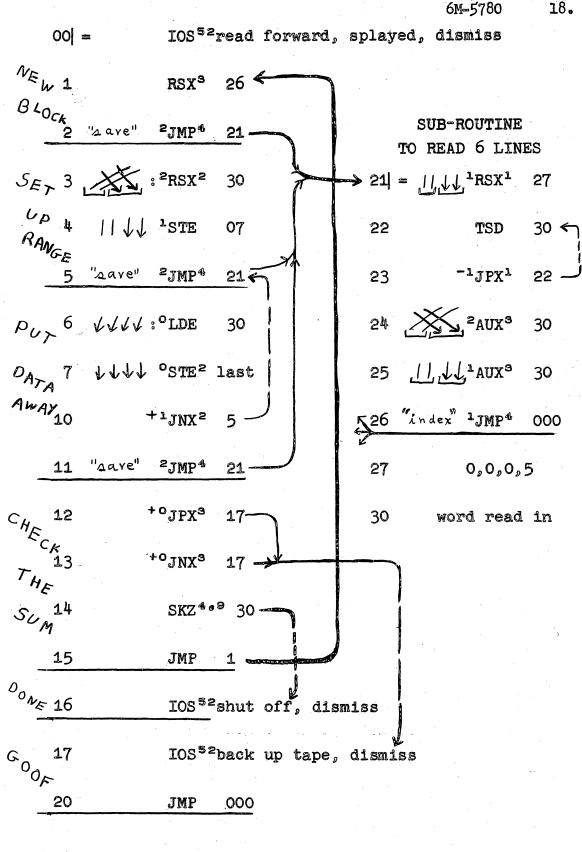

In one of its modes, the photoreader reads the six bits of a line of tape into every sixth bit of some specified word and cycles the word left one place. This is the "splayed" mode of the photoreader sequence. After reading in six lines, a full 36 bit word is assembled. This mode would usually be used to read in binary tapes.

The main problem associated with a binary read-in routine is what format to use. In general, data words are read into blocks of consecutive memory registers and three provisions are made; (1) to read in more than one block, (2) to check the sum of each block thereby detecting almost any error, (3) to specify what should happen to control after all blocks are read in.

## The Solution

Program VI uses the following format for each block of binary words:

The first word in each block consists of two 18 bit numbers (see instructions at 3 and 4) which designate the addresses of the actual data words which follow.

The right half of the last word is the complement of the sum of all the other half words in the block. In other words, if all the words in a block are added up in 18 bit pieces (instructions at 24 and 25) the sum must be zero (instructions at 12 and 13) or there has been an error. If there is an error, the tape is backed up (instruction 17) and read in again. (TX-2, as you may have guessed by now, can read paper tape in either direction and can identify the front of the tape.)

The sign bit (4.9) of the left half of the last word in a block tells whether there are more (if 4.9 is a ONE) blocks to be read in or not (if 4.9 is a ZERO, see instruction 14). If there are more

A Binary Read-in Routine Program VI

18.

6M-5780 18a. IOS<sup>52</sup>read forward, splayed, dismiss 00 = NE w 1 RSX<sup>3</sup> 26 < BLOCK 2 "2 ave" 2JMP4 21 SUB-ROUTINE TO READ 6 LINES SE, 3 :2RSX2 30  $\rightarrow$  21| =  $||_{\downarrow}\downarrow\downarrow^{1}RSX^{1}$ 27  $\frac{U_{p}}{R_{AN_{GE}}} = \frac{11 \sqrt{1} \text{ STE } 07}{5 \sqrt{2} \text{ ave}^{2} \text{ JMP}^{4} 21 \neq 1}$ 30 < TSD 22 -1JPX1 22 --23 24 24 2AUX<sup>3</sup> 30  $P_{U_{r}} = 6 \quad \forall \forall \forall \forall : \circ LDE$ 30 25 <u>[]</u> <u>[]</u> <u>AUX<sup>3</sup></u> 30  $D_{A_{T_A}}$  7  $\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{2}}}}}$  STE<sup>2</sup> last Away 10 +1JNX<sup>2</sup> 5 -526 "index" 1 JMP4 000 "save" 2JMP4 0,0,0,5 11 21 27 +°JPX<sup>3</sup> 17- $C_{H_{E_{C_{K}}}}$ 12

13  $T_{H_{E}}$   $S_{U_{M}}$ 14 12 word read in 30 <sup>+0</sup>JNX<sup>3</sup> 17 SKZ<sup>4.9</sup> 30 15 JMP 1 00NE 16 IOS<sup>52</sup>shut off, dismiss GOOF IOS<sup>52</sup>back up tape, dismiss 17 20 JMP 000

Program VI A Binary Read-in Routine

blocks, control goes to register 1 and reads in the next block, providing of course that there were no check sum errors. If there are no more blocks, instruction 16 shuts off the PETR and dismisses the sequence.

## Exercises To Prove To Yourself That You Really Understand

Note that there is no provision made in the tape format of Program VI for turning on any other sequence after the last block has been read in. There is really no necessity for a control change since the Start-Over sequence can start up the program just read in at the poke of a button.

However, pay homage to the (W. A.) Clarkian philosophy of minimal button poking and make the necessary additions of Program VI and its format which will start the program in sequence #S at a register called START if bit 4.8 of the last word in the last block is a ONE. If 4.8 is a ZERO, make Program VI do what it does now. This addition can be accomplished with eleven more words (maybe fewer).

Why are the CF bits of instruction 12 all ZEROS?

Do they need to be ZEROS in instruction 13? Why?

20.

#### VII. A Punch Out Routine

To prove to yourself that you really, really understand, write a program to punch out storage in the block format required by the read in routine (VI). Control it from a toggle switch register in the following manner:

Let the left half of the toggle switch register be the first address, and the right half, the last address of the block to be punched out.

Let the meta bit (4.10) designate whether this is the last block or not.

Let bit 4.9 be a ONE when the toggles are being changed, and a ZERO when the program can look at the register.

The author has written this program with 33 instructions. The best solution submitted by a reader, will be published in a supplement to this memo.

## CONCLUDING REMARKS

The six programs in this memo illustrate many of the characteristics of TX-2. There are other features which haven't been illustrated. For example, conditionally saving the P and/or Q register in E after a JMP; using multiple step deferred (indirect) addresses; using the Boolean instructions or the <u>skip if E is different from word</u> instruction; using the operate class commands and many sequences operating simultaneously.

There will be supplements to this memo from time to time which illustrate features such as those mentioned in the preceding paragraph. Any suggestions, improvements, discoveries, or remarks in general will be appreciated by the author and probably also by his associates.

HPP/mk

<u>Insertions:</u> Pages 3ª 6a 9a 12a 15a 18a

6м-5780

21.

# NOTES