Sheet 1 of 41

# Division 6 - Lincoln Laboratory Massachusetts Institute of Technology Lexington 73, Massachusetts

SUBJECT: The Lincoln TX-2 Computer

To:

Distribution List

From:

W.A. Clark, J.M. Frankovich, H.P. Peterson, J.W. Forgie,

R.L. Best, K.H. Olsen

Date:

1 April 1957

Approved:

W.N. Papian

Abstract:

The information contained in this report was presented at the Western Joint Computer Conference held at Los Angeles, California, in February 1957. The papers given form the sections of this memorandum and are as follows:

THE LINCOLN TX-2 COMPUTER DEVELOPMENT by Wesley A. Clark

Construction of the TX-2 computer at the Lincoln Laboratory of MIT is part of the Lincoln program for the study and development of large-scale digital computer systems. The Lincoln TX-2 incorporates several new developments in high-speed transistor circuits, large capacity magnetic-core memories, and flexibility in machine organization and is designed to work efficiently with many input-output devices of different types. In the course of development of the TX-2, Lincoln has constructed a small self-checking multiplier system which is on life test, and a complete, though skeletal, general-purpose computer known as the TX-0 which is now in operation.

A FUNCTIONAL DESCRIPTION OF THE LINCOLN TX-2 COMPUTER by John M. Frankovich and H. Philip Peterson

The Lincoln TX-2 computer is a general-purpose, binary parallel machine with a code of 64 single-address instructions and 64 index registers. The design provides for a random-access memory of 260,000 36-bit words. The instruction code includes the usual arithmetic and logic operations executed at a peak rate of 160,000 36-bit additions per second, with several interesting

variants. A unique feature of the central computer is its ability to deal with operands in one 36-bit, one 27-and one 9-bit, two 18-bit, or in four 9-bit configurations. These configurations are specified by each instruction -- a feature which permits the 9-bit quarters of the arithmetic element to be connected in various ways to the corresponding quarters of the memory. Control is exercised over the activity of the quarters during the execution of the instruction.

# THE LINCOLN TX-2 INPUT-OUTPUT SYSTEM by James W. Forgie

The Lincoln TX-2 computer design uses the "multiple-sequence program technique" to permit the concurrent operation of a number of input-output devices. A stored program (instruction) counter is associated with each input-output device. The programs referred to by these counters time-share the hardware of the central computer, giving attention to the associated input-output devices as required. A priority system ranks the devices according to speed and type for efficient operation with a minimum of programming restrictions. The multiple-sequence program technique provides an environment in which buffer storage may be considerably reduced at a small cost in machine speed within the limits set by peak and average data rate considerations.

#### MEMORY UNITS IN THE LINCOLN TX-2 by Richard L. Best

There are three random-access core memories in TX-2 -- all of which may be operated independently and concurrently. Two of these are for conventional storage of data and instructions. The third is used as a file of index registers and program counters. The three types of core memories in TX-2 are described. The largest memory contains 65,536 words 37 digits long, and has a full cycle time of  $6\,1/2\,\mu \rm sec$ . The next largest is entirely transistor driven, contains 4,096 words, 37 digits long, and has a 6- $\mu \rm sec$  cycle time. The smallest and fastest contains 64 words, 19 digits long, and uses external selection and two cores per bit to achieve a "read" cycle time of 1  $\mu \rm sec$  and a "write" cycle time of 3  $\mu \rm sec$ . Ferrite cores only 0.050 inches 0.D. are used in the two smaller memories.

# TX-2 CIRCUITRY by Kenneth H. Olsen

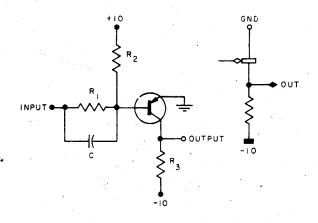

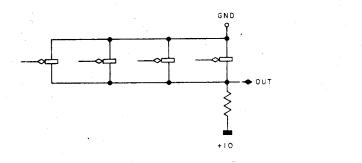

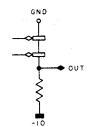

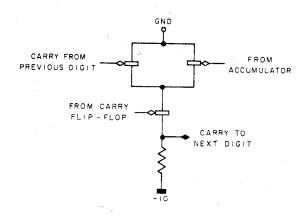

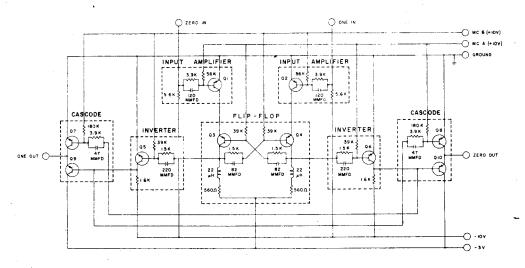

Only two basic transistor logic circuits are used in TX-2. Surface-barrier transistors in saturated emitter-follower circuits are grouped in parallel for "AND" "OR" operations; groups of inverter circuits are connected in series, parallel, or series-parallel to perform more complicated logic operations. The

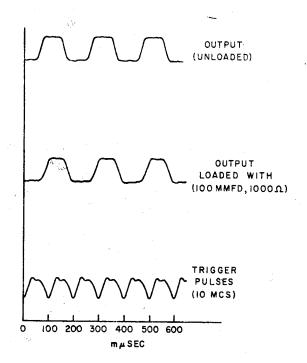

TX-2 flip-flop is assembled from saturated inverters and emitter-followers and incorporates enough amplification so that it appears to the logic designer as a simple switch over a wide range of loads.

Circuit tolerance to variations in transistor and other component characteristics, in temperature, supply voltages, and noise was studied in detail and designs were adjusted to minimize the effects of them. The study led to the selection of voltage sensitive parameters for indicating the deterioration of components with age and became the basis of the marginal checking system.

### ACKNOWLEDGMENT

We are indebted to Mr Frank P. Hazel and Miss June Karlson for their assistance in editing; to Mrs. Barbara Clark, Miss Carole Olson, Miss Elaine Tonra and Miss Ruth McDonald for their typing of the manuscripts; and to Miss Alice Griffin and her associates for the preparation of the many figures.

#### Distribution List

#### Division 6

P.R. Bagley

R.L. Best

S. Bradspies

J.H. Burrows

W.A. Clark

L.B. Collins

J.W. Forgie

J.M. Frankovich

S. Goldberg

L.L. Holmes (Barta)

N.T. Jones

G. Marnie

K.H. Olsen

R.B. Paddock

W.N. Papian (3 copies)

H.P. Peterson

E.W. Pughe

A. Rowe (Barta)

W.F. Santelmann

C.A. Zraket

#### Non-Division 6

A.V. Nedzel

E.D. Thomas

Major H.B. Farmer R. A. Nelson

### Non-Lincoln (inside addresses)

N.E. Trieste (IBM)

A.R. Marshall (RAND)

Major S. Pierce (LRP)

### Non-Lincoln (outside addresses)

Miss R. Rita Balogh

IBM, Military Products Div.

Kingston, New York

Carlo Bocciarelli

Philco Research Division

C and Tioga Streets

Philadelphia, Pennsylvania

(2 copies)

Mr. Arnold A. Cohen

Remington Rand UNIVAC

St. Paul 16, Minnesota

Mr. Abraham Katz

Commercial Electronic Products

Camden, New Jersey

Mr. Steve Levy

Lansdale Tube Co.

Church Rd.

Lansdale, Pennsylvania

Mr. Louis C. Murphy

Marchant Research

717 Los Palos Drive

Lafayette, California

Mr. A.A. Perez

National Cash Register Co.

Electronics Division

1401 East el Segundo Blvd.

Hawthorne, California

Mr. Kenneth M. Rehler, Mgr. Electronic Control Systems, Inc.

2136 Westwood Blvd.

Los Angeles 25, California

# 6**M-**4968

### Table of Contents

| I.   | THE            | LINCOLN TX-2 COMPUTER DEVELOPMENT                   | 1        |

|------|----------------|-----------------------------------------------------|----------|

|      | Α.             | Introduction                                        | 1        |

|      | В.             | U , ·                                               | 1        |

|      | C.             | Design Objectives                                   | 4        |

| II.  | A I            | FUNCTIONAL DESCRIPTION OF THE LINCOLN TX-2 COMPUTER | 7        |

|      | Α.             | Introduction                                        | 7        |

|      | В.             | General Structure of TX-2                           | 7        |

|      | C.             |                                                     | 9        |

|      | D.             | Control and Indexing                                | 11       |

|      | E.             | Arithmetic Element                                  | 13       |

|      | F.             |                                                     | 15       |

|      | G.             | · · ·                                               | 16       |

|      | н.             | , •                                                 | 17       |

|      | Į.             | ~                                                   | 29       |

|      | J.             |                                                     | 31       |

|      | К.             | Summary                                             | 31       |

| III. | TH             | E LINCOLN TX-2 INPUT-OUTPUT SYSTEM                  | 37       |

|      | Α.             | Introduction                                        | 37       |

|      | в.             | The Multiple-Sequence Program Technique             | 37       |

|      | C.             | Multiple-Sequence Operation in TX-2                 | 38       |

|      | D.             | The TX-2 Input-Output Element                       | 39<br>41 |

|      | E.             | Input-Output Instructions                           | 41       |

|      |                | 1. rdn and rds                                      | 41       |

|      |                | 2. ios                                              | 41       |

|      | $\mathbf{F}$ . | Sequence-Changing and Operation of the Sequence-    |          |

|      |                | Selector                                            | 43       |

|      | G.             | Interpretation of the Break Bit                     | 44       |

|      | H.             | Interpretation of the Dismiss Bit                   | 44       |

|      | I.             | Starting a Multiple-Sequence Computer               | 45       |

|      | J.             | The Arithmetic Element in Multiple-Sequence Opera-  |          |

|      |                | tion                                                | 45       |

|      | Κ.             | Conclusions                                         | 46       |

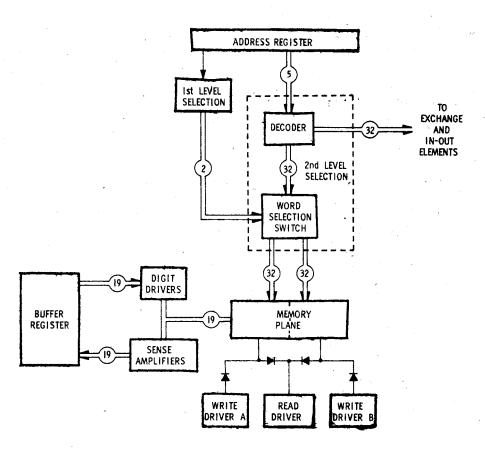

| IV.  | MEM            | MORY UNITS IN THE LINCOLN TX-2                      | 49       |

|      | Α.             | Introduction                                        | 49       |

|      | в.             | S-Memory (65,536 Words)                             | 49       |

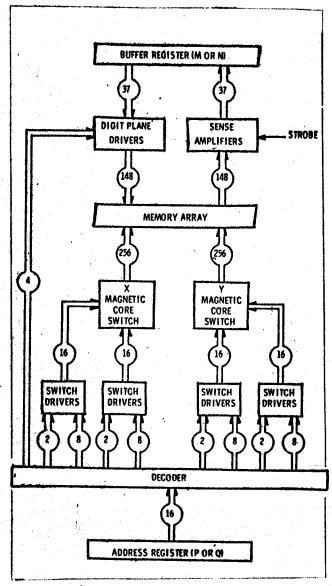

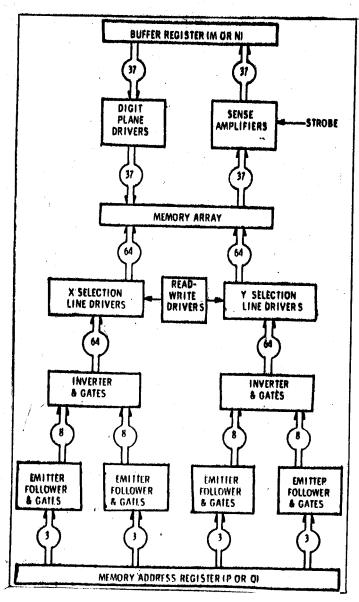

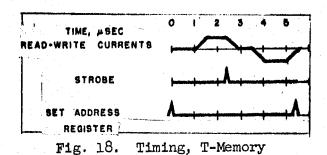

|      | С.             | T-Memory (4096 Words)                               | 51       |

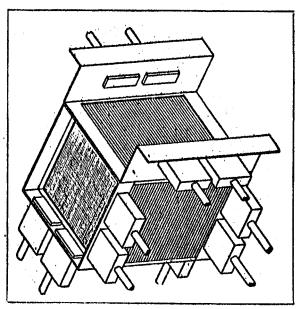

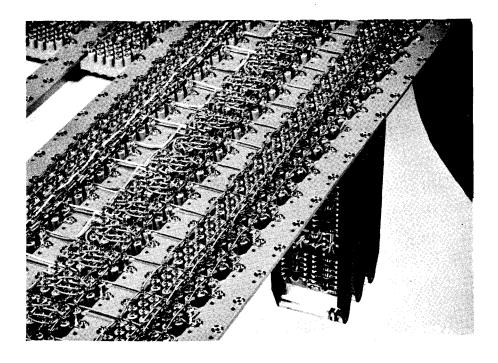

|      |                | 1. Mechanical Features                              | 52       |

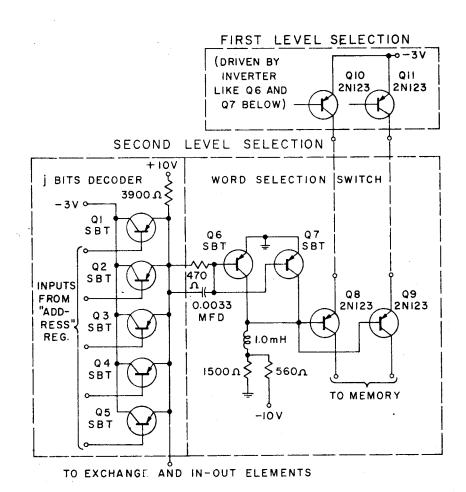

|      |                | 2. Selection Circuits                               | 52       |

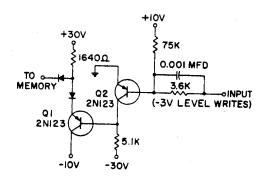

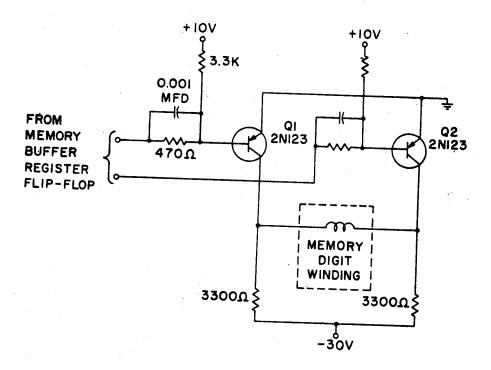

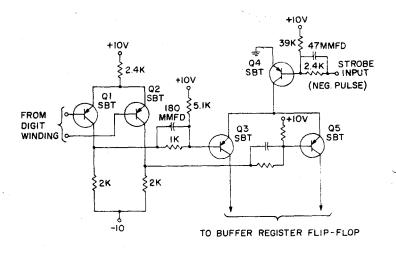

|      |                | 3. Digit Circuits                                   | 53       |

|      | D.             | Memory                                              | 53<br>56 |

|      |                | 1. Operating Principle                              | 56       |

|      |                | 2. Selection Circuits                               | 60       |

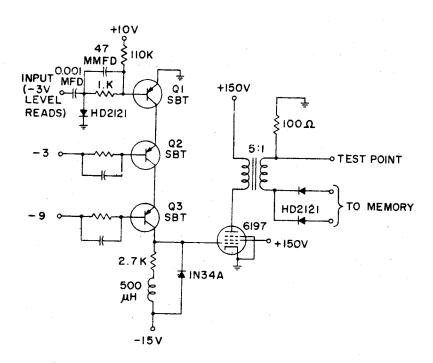

|      |                | 3. Read-Write Drivers                               | 61       |

# 6м-4968

| Tab. | Le of                      | Contents (Continued)                                                    |                                                 |

|------|----------------------------|-------------------------------------------------------------------------|-------------------------------------------------|

|      | Ε.                         | 4. Digit Circuits 5. Modes of Operation Acknowledgment                  | 63<br>63<br>64                                  |

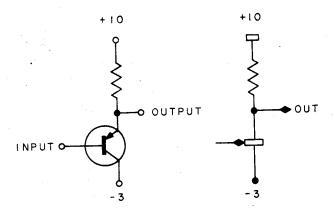

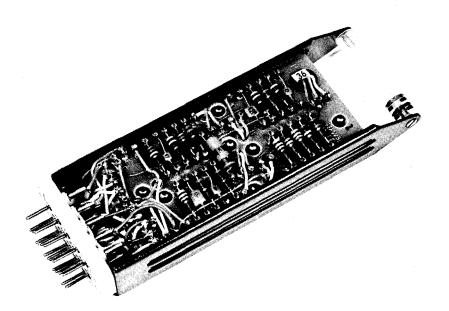

| ٧.   | T <b>X-</b> 2              | CIRCUITRY                                                               | 65                                              |

|      | A.<br>B.<br>C.<br>D.<br>E. | Circuit Configurations Flip-Flop Marginal Checking Packaging Conclusion | 65<br>68<br><b>71</b><br><b>71</b><br><b>73</b> |

# List of Illustrations

| Fig. | 1     | The Lincoln TX-2 Computer                                                                                                                                | 1        |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Fig. | 2     | Steps in the Lincoln TX-2 Development Program                                                                                                            | 4        |

| Fig. | 3     | TX-2 System Schematic                                                                                                                                    | 8        |

| Fig. | 4     | TX-2 Memory Element - Showing method of using<br>two address registers and two buffer registers<br>to simultaneously operate two out of four<br>memories | 10       |

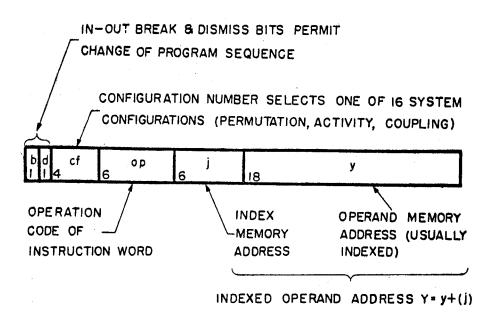

| Fig. | 5     | TX-2 Instruction Word Structure                                                                                                                          | 11       |

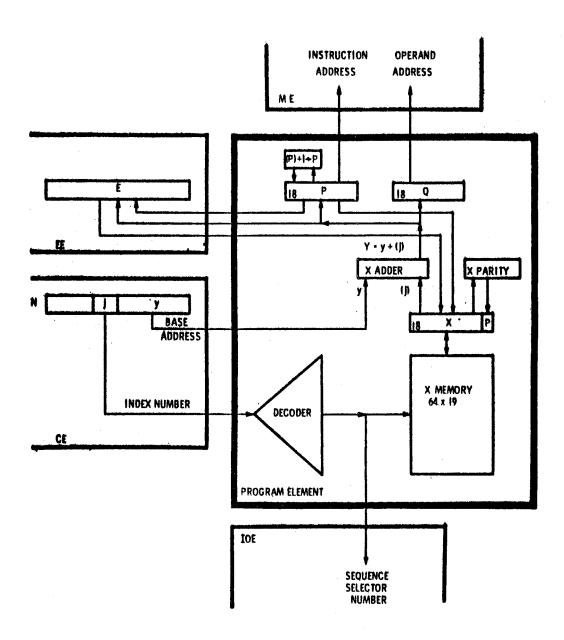

| Fig. | 6     | TX-2 Program Flement Showing paths enabling index adding and storing and loading program counter from the index memory and the exchange element          | 12       |

| Fig. | 7     | Circuits and Transfer Paths (General) of any TX-2 Arithmetic Element Forms                                                                               | 14       |

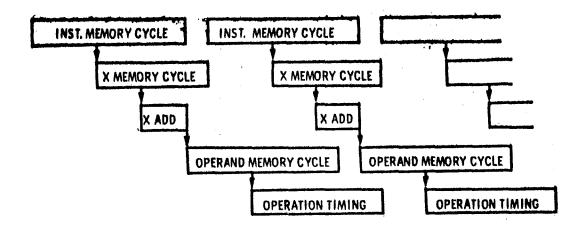

| Fig. | 8(a)  | Consecutive Load Type Instructions; Instructions and Operands in Different Memories                                                                      | 18       |

| Fig. | 8(७)  | Consecutive Store Type Instructions                                                                                                                      | 18       |

| Fig. | 8(c)  | Instruction and Operand in Same Memory                                                                                                                   | 19       |

| Fig. | 8(4)  | Change Sequence                                                                                                                                          | 19       |

| Fig. | 9     | TX-2 Configuration Selection                                                                                                                             | 20       |

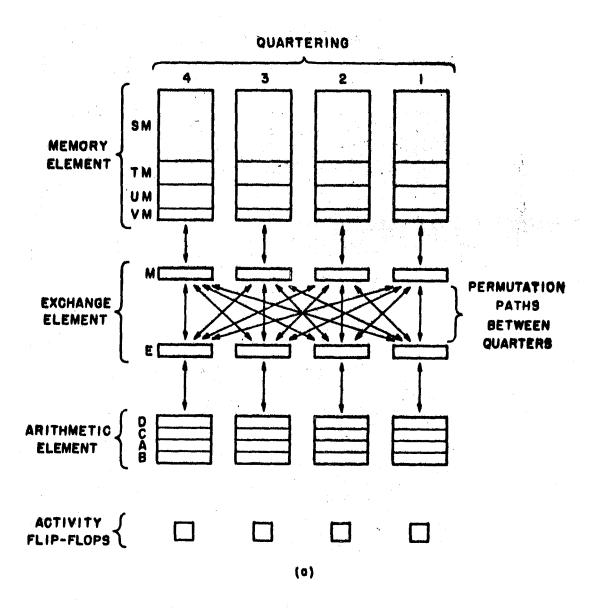

| Fig. | 10(a) | ) TX-2 Configuration; Quartering Permutation<br>Paths and Activity Flip-Flops Shown                                                                      | 22       |

| Fig. | 10(b) | TX-2 Configuration; Paths In Exchange Element                                                                                                            | 23       |

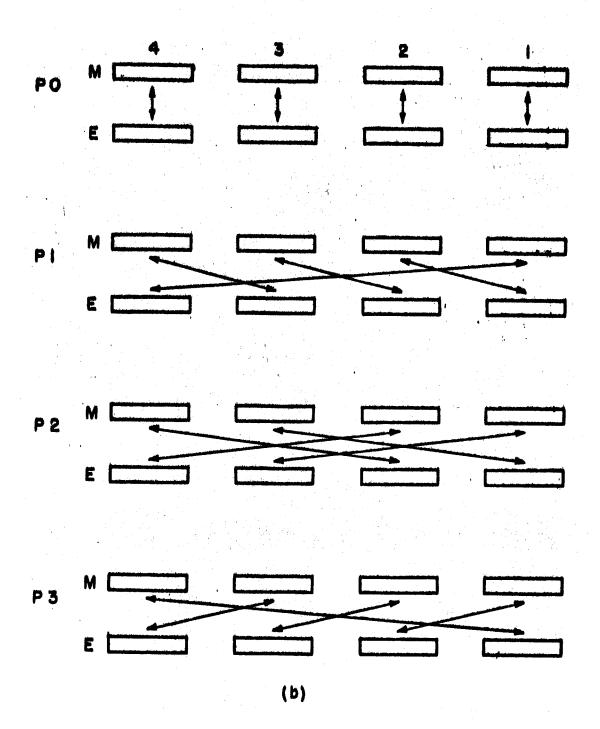

| Fig. |       | ) i <sup>th</sup> Quarter Coupling Units<br>) Coupling Unit Connections                                                                                  | 24<br>24 |

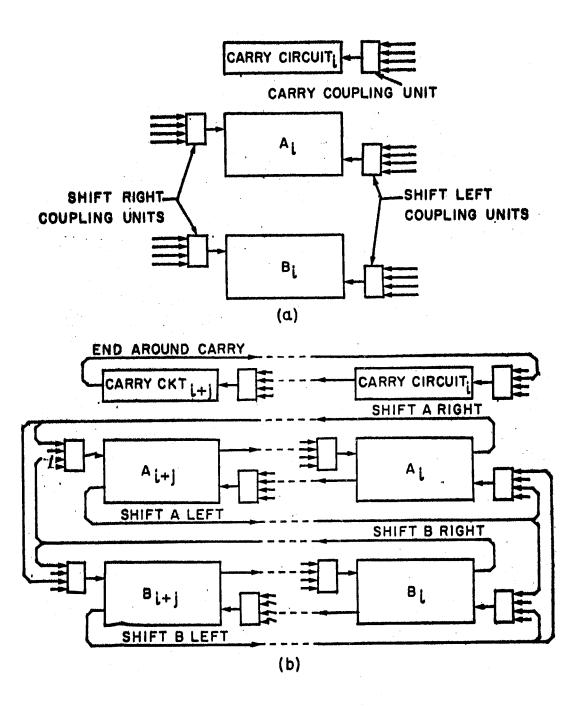

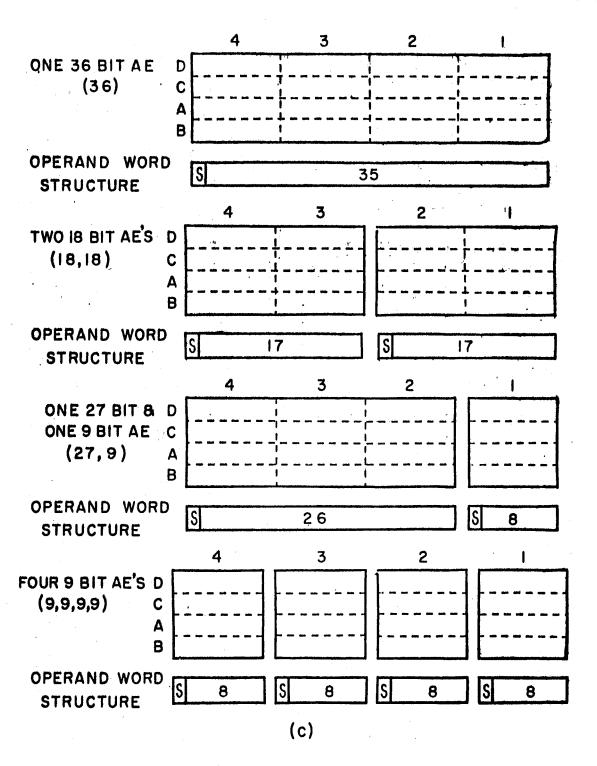

| Fig. | 11(c) | ) TX-2 Configuration; Arithmetic Elements and Operand Word Structures                                                                                    | 26       |

| _    |       | TX-2 Shift Path Arrangements                                                                                                                             | 27       |

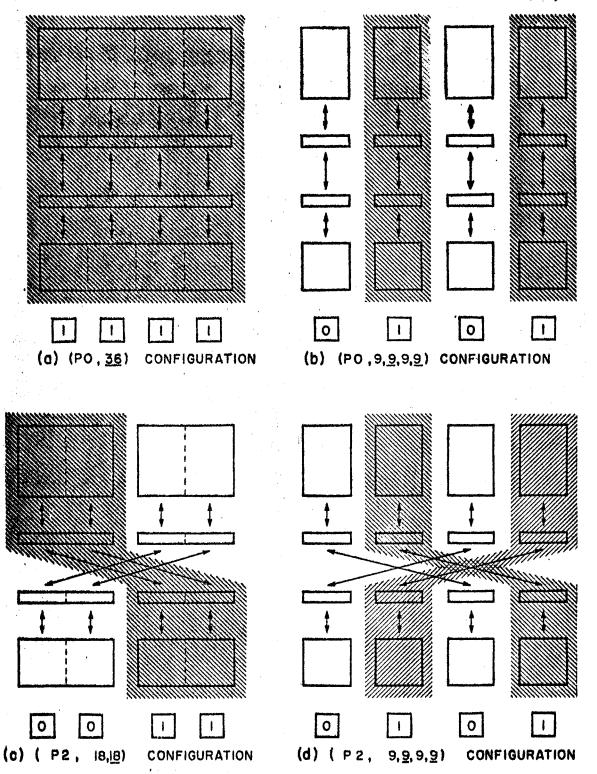

| Fig. | 12    | TX-2 Configurations; Areas of Activity During Execution of Instruction Shown Shaded. Effect of AE Couplings Illustrated by Juxtaposition of Quarters     | 28       |

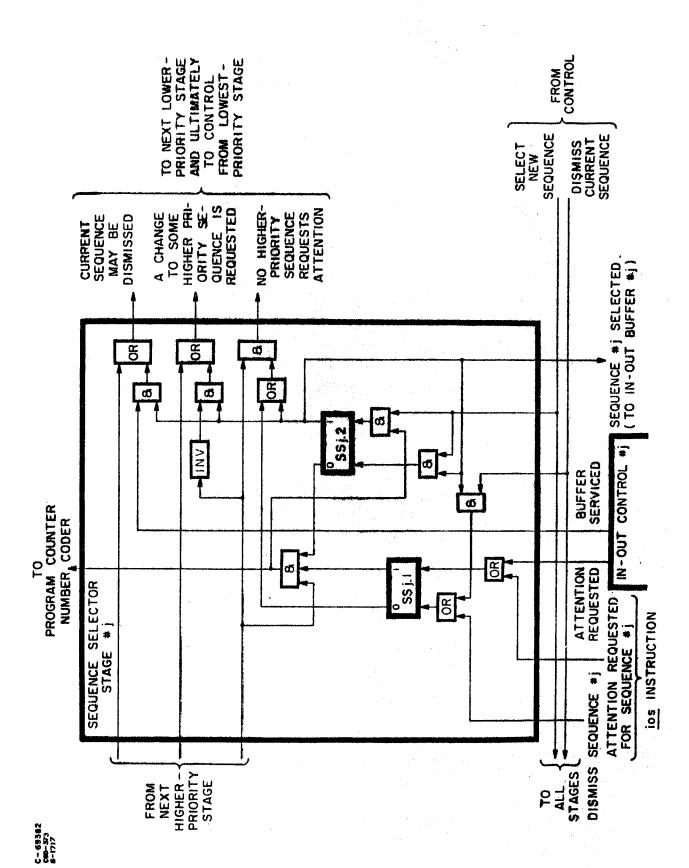

| Fig. | 13    | TX-2 Sequence Selector Stage                                                                                                                             | 40       |

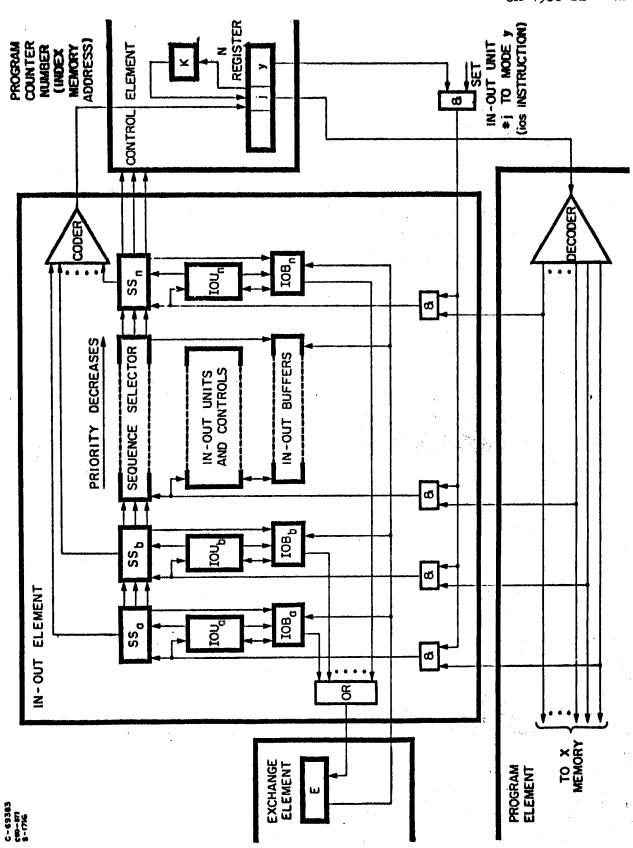

| Fig. | 14    | TX-2 In-Out Element                                                                                                                                      | 42:45    |

| Fig. | 15    | S-Memory; Coincident-current, Magnetic-Core Unit                                                                                                         | 49       |

| Fig. | 16    | Block Diagram, S-Memory                                                                                                                                  | 50       |

| Fig. | 17    | Block Diagram, T-Memory                                                                                                                                  | 51       |

| Fig. | 18 | Timing, T-Memory                                              | 52         |

|------|----|---------------------------------------------------------------|------------|

| Fig. | 19 | Pluggable Array, T-Memory                                     | 52         |

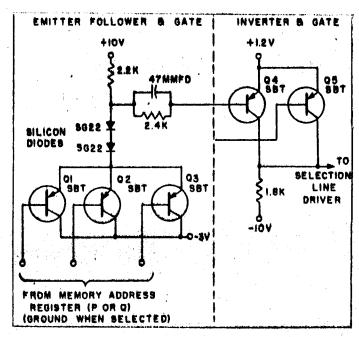

| Fig. | 20 | One Channel, Emitter follower and Inverter AND gate, T-Memory | 53         |

| Fig. | 21 | One Channel, Selection Line Driver, T-Memory                  | 54         |

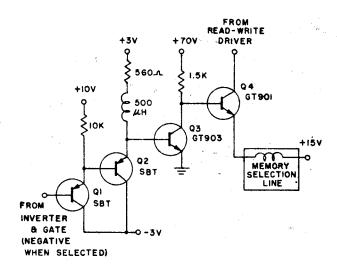

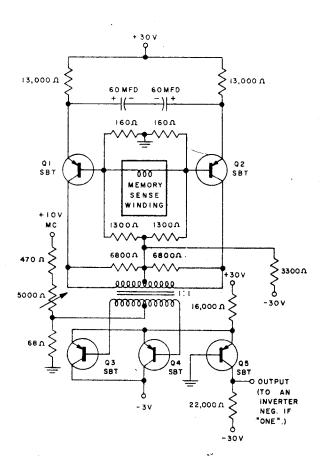

| Fig. | 22 | Read-Write Driver (2 needed), T-Memory                        | 54         |

| Fig. | 23 | Digit-Plane Driver, T-Memory                                  | 55         |

| Fig. | 24 | Sense Amplifier, T-Memory                                     | 56         |

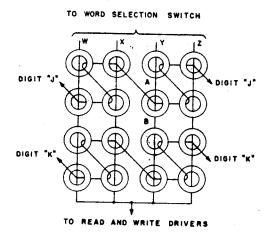

| Fig. | 25 | Winding Configuration, X-Memory                               | 5 <b>7</b> |

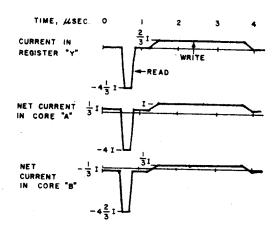

| Fig. | 26 | Timing Diagram, X-Memory                                      | 5 <b>7</b> |

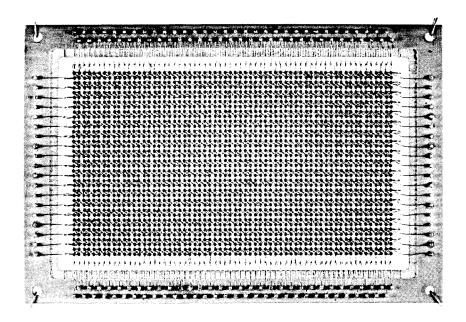

| Fig. | 27 | 64 x 38 Memory Plane, X-Memory                                | 58         |

| Fig. | 28 | Section of Memory Plane, Enlarged, X-Memory                   | 58         |

| Fig. | 29 | Block Diagram, X-Memory                                       | 59         |

| Fig. | 30 | Register Selection Circuit, X-Memory                          | 60         |

| Fig. | 31 | Read Driver, X-Memory                                         | 61         |

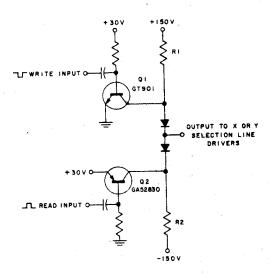

| Fig. | 32 | Write Driver, X-Memory                                        | 62         |

| Fig. | 33 | Digit Driver, X-Memory                                        | 62         |

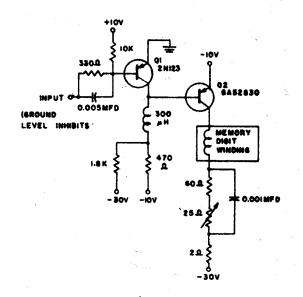

| Fig. | 34 | Sense Amplifier, X-Memory                                     | 63         |

| Fig. | 35 | Emitter Follower                                              | 65         |

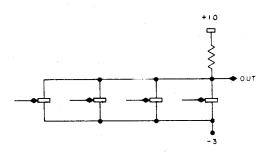

| Fig. | 36 | Parallel Emitter Follower                                     | 65         |

| Fig. | 37 | Inverter                                                      | 66         |

| Fig. | 38 | Parallel Inverters                                            | 66         |

| Fig. | 39 | Series Inverters                                              | 66         |

| Fig. | 40 | TX-2 Carry Circuits                                           | 67         |

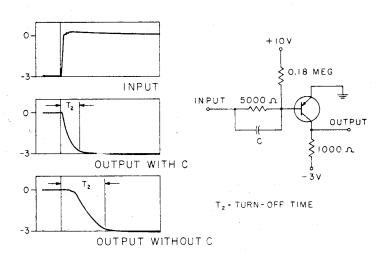

| Fig. | 41 | Turn-Off Time                                                 | 67         |

| Fig. | 42 | TX-2 Flip-Flop                                                | 68         |

| Fig. | 43 | Flip-Flop Waveforms                                           | 69         |

| Fig. | 44 | Trigger Sensitivity                                           | 69         |

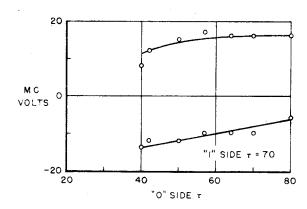

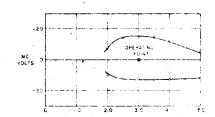

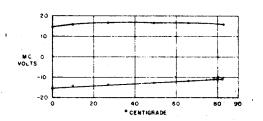

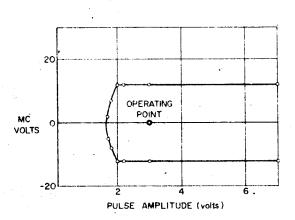

| Fig. | 45 | τ Margins                                                     | 70         |

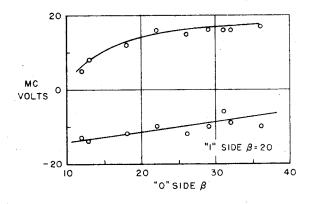

| Fig. | 46 | β Margins                                                     | 70         |

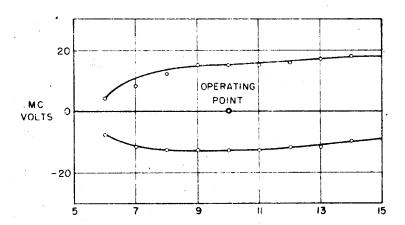

| Fig. | 47 | -10 Volt Supply Margins                                       | 72         |

| Fig. | 48 | -3 Volt Supply Margins                                        | 72         |

| Fig. | 49 | Temperature Margins                                           | 72         |

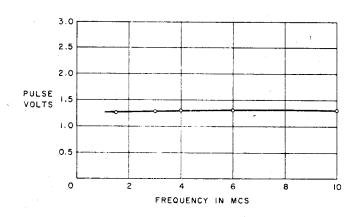

| Fig. | 50 | Pulse Margins                                                 | 72         |

| Fig. | 51 | TX-2 Plug-in Unit                                             | 73         |

| Fig. | 52 | TX-2 Back Panel                                               | 73         |

#### I. THE LINCOLN TX-2 COMPUTER DEVELOPMENT

#### A. Introduction

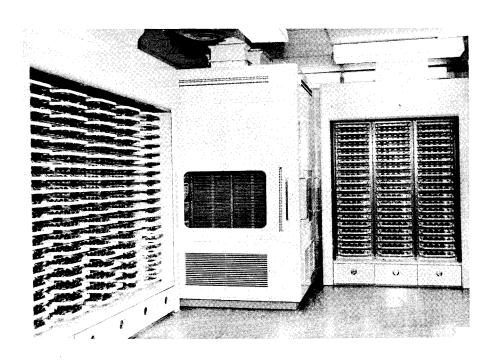

The TX-2 is the newest member of a growing family of experimental computers designed and constructed at the Lincoln Laboratory of MIT as part of the Lincoln program for the study and development of large-scale, digital computer systems suitable for control in real time. Although, in general characteristics and design philosophy, it owes a great deal to its predecessors, Whirlwind I and the Memory Test Computer, the Lincoln TX-2 incorporates several new developments in components and circuits, memories, and logical organization. It is the purpose of this paper to summarize these new features and to give some idea of the historical development and general design objectives of the TX-2 program. Fig. 1 shows TX-2 in its present development stage.

Fig. 1 The Lincoln TX-0 and TX-2 Computers

Foreground: TX-0 console

Middle center: TX-0 central computer frame

Right rear: Partially completed TX-2 frame showing plug-in

unit construction

Left rear: The 256 x 256 memory

#### B. History

With the development by Lincoln and IBM engineers of the SAGE computer for air defense, real-time control computer systems had

reached an impressive level of size, sophistication, and complexity. The highly successful 64 x 64 coincident-current, magnetic-core, memory array was in operation in the Memory Test Computer which had given up its earlier 32 x 32 array to Whirlwind. Vacuum tubes abounded in all directions. It was apparent that the further advances in system design which could be made by increasing memory size, eliminating vacuum tubes wherever possible, and organizing input-output buffering, control, and communications into more efficient forms, would be well worthwhile.

The development of a 256 x 256, switch-driven, magnetic-core memory array was begun and the Philco surface-barrier transistor made its appearance. After some very promising bench experiments with flip-flops and logic circuits, it became apparent that this transistor was potentially well-suited to use in large-scale systems and warranted further study. Accordingly, plans were laid for a succession of experimental digital systems of increasing size and complexity which would make possible the development and evaluation of circuits using the surface-barrier transistors, and which would lead to a computer of advanced design that would be capable of making efficient use of the 256 x 256 memory.

A double-rank shift register of eight stages and containing about 100 transistors was constructed and put on life-test in April 1955. It has since been circulating a fixed pattern almost continuously with no known errors and no natural transistor failures.

As the next step, it was decided to build a small, high-speed, error-detecting multiplier and incorporate marginal checking and other system features. The value of a multiplier as a preliminary model had been well demonstrated by the 5-digit system built during Whirlwind's early development. The shift, carry, count, and complement operations, under closely controlled timing conditions, were felt to be representative of all of the operations in the manipulative elements of the type of computer planned. Accordingly, an 8-bit system using 600 transistors was designed and completed in August 1955 and has been in nearly continuous operation since. Operating margins are periodically checked, and in steady state operation, the multiplier's error-rate has been about one every two months or one error per 5 x  $10^{11}$  multiplications at 105 multiplications per second. Most of these errors appear to have been caused by cracks in the printed wiring which open intermittently.

During this period, a better idea of the general characteristics of the projected computer began to develop and the engineers who were designing the  $256 \times 256$  memory were encouraged to think in terms of a word of 36 bits. The notion of a logically separate

input-output processor was examined and rejected in favor of a minimum buffering scheme in which data is transferred directly to and from the central memory of the computer. The possibility was recognized of programming these transfers by means of additional program sequences and associated program counters, thus taking advantage of the extensive facilities of the central machine itself for processing input-output data.

It was realized that another development step was desirable before attempting such an elaborate 36-bit system. The 8-bit multiplier had produced a certain measure of confidence and familiarity with circuits, packaging, and techniques of logical design, but there remained the problems associated with communicating with memory units and input-output equipment operating at vacuum-tube levels over relatively large distances from a central machine which operated at transistor levels. It appeared that the memory development, which had now entered the construction phase, would also benefit by a preliminary evaluation of the 256 x 256 array and its switching, timing, and noise problems in an operating computer of some kind, possibly with a reduced word length. It was, therefore, decided to design and build next a simple machine - in fact, the simplest reasonable machine - in order to bring about an early intermediate closure of the various efforts within the program.

After some thought about the various possible minimal machines, a design was completed in which the word length would be 18 bits - a graceful half of the projected final form. We began to refer to this computer as the TX-0 and to the projected machine as the TX-2. Because the 256 x 256 memory array required 16 bits for complete addressing, the single-address instruction word of the TX-0 was left with 2 bits in which to encode instructions. The particular set of instructions chosen included three which required a memory address (add, store, and conditional jump) and one which did not. In this last instruction, the remaining 16 bits were used to control certain necessary and useful primitive operations such as clearing and complementing the accumulator, transferring words between registers, and turning on and off input-output equipment.

The TX-O, equipped with a Flexowriter, a paper-tape reader, and a cathode-ray tube display system was completed, except for the memory, in April 1956. Twenty planes of the 256 x 256 memory array were installed the following August and the TX-O, now containing about 3600 transistors and 400 vacuum tubes, began to function as a complete computer. Since that time, it has been used to run a variety of testing and demonstration programs, and a symbolic address compiler and other utility programs have been constructed and are currently in use.

Not only has the TX-O served the evaluational purposes for which it was built, but it has also demonstrated an effectiveness as a

usable computer that is somewhat surprising in view of its simplicity. Its relatively high speed of about 80,000 instructions per second and its 65,536-word memory compensate in large measure for the limitations of its instruction code and logical structure.

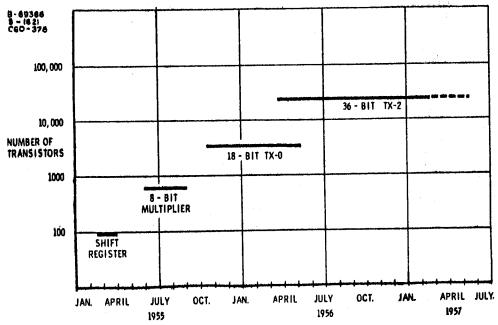

With the successful completion of the TX-O, the final steps in the development were undertaken in packaging, circuit refinement, and logical design of the TX-2. A great deal had been learned about the performance of the transistors and memory, the types of logical circuits which are practical, techniques of marginal checking, and the lesser system problems such as color scheme selection and the proper location of pencil sharpeners. As design work progressed, the TX-2 took form as a system of about 22,000 transistors and 600 vacuum tubes. It is an interesting fact that at each step of the development since the shift register, the number of transistors involved was about 6 times the number in the preceding step. This is graphically shown in Fig. 2. At the time of writing approximately 16 million transistor-hours have accumulated in the shift register, multiplier, and TX-O. There have been two natural deaths and a dozen or so violent ones, primarily due to contact shorting with clip leads and probes.

Fig. 2. Steps in the Lincoln TX-2 Development Program

#### C. Design Objectives

In describing design objectives, it should be pointed out that speed of operation was <u>not</u> the primary consideration to which all other attributes were sacrificed. It would have been

6**M-**4968 5.

possible, at the expense of a few more logic circuits, to increase the speed of multiplication, division, and shift-type operations. Similarly, the operation of the index register system could have been made more efficient at the cost of an additional small, fast memory. The principal objective was rather that of achieving a balance between the factors of speed, reliability, simplicity, flexibility and general virtue.

A key aspect is that of expandability which, in an experimental computer in an active environment, certainly ranks with the foregoing qualities in importance. The address structure in the TX-2 permits an expansion of the memory by about a factor of 4, partly to allow for new memory developments, such as the transistor-driven 64 x 64 array which was begun following the completion of TX-0. New instructions and pieces of terminal equipment will certainly be added during the course of future operation. Extra space and spare plugs have been artfully distributed about in constructing the computer frame. Finally, modular construction will permit a fairly easy physical expansion when required.

The result of all this activity has been a computer of relatively large capability. In addition to incorporating high-speed transistor circuits and a large magnetic-core memory array, the Lincoln TX-2 has two major and distinguishing design characteristics:

1. The structure of the arithmetic element can be altered under program control. Each instruction specifies a particular form of machine in which to operate, ranging from a full 36-bit computer to four 9-bit computers with many variations. Not only is such a scheme able to make more efficient use of the memory in storing data of various word lengths, but it also can be expected to result in greater over-all machine speed because of the increased parallelism of operation.

Peak operating rates must then be referred to particular configurations. For addition and multiplication, these peak rates are given in the following table:

PEAK OPERATING SPEEDS OF TX-2

| Word Lengths (in bits) | Additions<br>per second | Multiplications per second |

|------------------------|-------------------------|----------------------------|

| 7211 01007             | per become              | per become                 |

| 36                     | 150,000                 | 80,000<br>240,000          |

| 18                     | 300,000                 | 240,000                    |

| 9                      | 600,000                 | 600,000                    |

2. Instead of one instruction counter, the TX-2 has 32 such counters which are assigned separately to different users of the computer, who then compete for operating time from instruction to instruction. A special part of the machine selects a particular user based partly on a predetermined priority schedule and partly on the current needs of that user. This multiple-sequence operation, in which many essentially independent instruction sequences interrupt and interleave one another, is an extension of the breakpoint operation found in DYSEAC of the National Bureau of Standards.

The value of these features will have to be assessed during the course of future machine operation. The features themselves are discussed in more detail in the following sections of this report.

# II. A FUNCTIONAL DESCRIPTION OF THE LINCOLN TX-2 COMPUTER

#### A. Introduction

TX-2 is a large-scale digital computer, designed and built at the MIT Lincoln Laboratory, which uses new memory and circuit components and some new logical design concepts. The computer will be a research tool in scientific computations, data-handling, and real-time problems. The design of the computer reflects not only the characteristics of the components available, but also the nature of the intended applications. This section describes the functions and organization of the computer that are important from the user's point of view.

#### B. General Structure of TX-2

TX-2 is a parallel, binary computer with words 36 digits long. The internal memory is random-access and will initially consist of 69,632 registers of parity-checked, magnetic-core memory and about 24 additional toggle-switch and flip-flop registers. About 150,000 instructions can be executed per second. Instructions are indexed, single-address type and a fixed-point, signed-fraction, ONE's - complement number system is used.

Several unusual ideas incorporated in the organization of the system reduce the amount of information unnecessarily manipulated during program sequences. Furthermore, the organization facilitates the execution of several operations simultaneously, thereby increasing the effective speed of the computer.

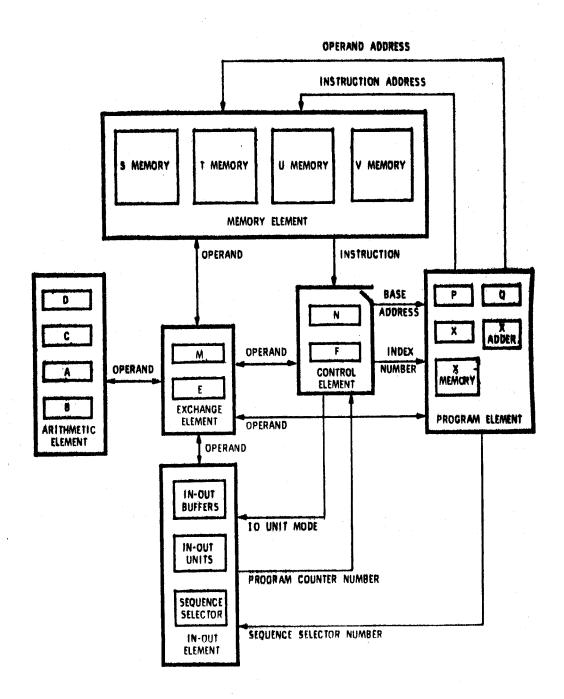

The principal registers and information paths in the computer are illustrated schematically in Fig. 3. A,B,C,D,E,F,M, and N are the 36-bit flip-flop registers in the machine. M and N are memory buffer registers, each of which has a parity flip-flop and associated circuitry used to check the parity of memory words. P,Q, and X are 18-digit registers; X also has a parity digit which is used to check the parity of words in the X-memory. Control flip-flops are not shown in Fig. 3.

Instructions are full memory words and are placed in the control element during the instruction memory cycle. During the operand memory cycle, an operand is usually transmitted between the memory element and some other element—always through the exchange element. The 36-digit configuration of the memory is not, however, maintained throughout the computer during operation timing. A programmer can, in effect, simultaneously control several independent, with operands of shorter word lengths during the execution of each

Fig. 3 TX-2 System Schematic

instruction. This flexibility is realized by specifying a particular system configuration with each instruction.

The computer communicates with the outside world through units in the in-out element, several of which can be simultaneously operated. Whenever any piece of data (input or output) is ready to be transferred between an in-out unit and a register in the memory element, signals to the program element from the in-out element automatically call into operation the instruction sequence associated with the in-out unit. This process is referred to as multiple-sequencing and will be described in Section III of this report.

#### C. Memory Element

The availability of a large, fast, core memory for TX-2 permitted an emphasis on the design of a machine with a completely random-access memory with a design capacity of 262,144 words. The homogeneous aspect of such a large memory system simplifies the programmer's coding problems and permits continued high-speed operation regardless of where the program is located in the internal memory.

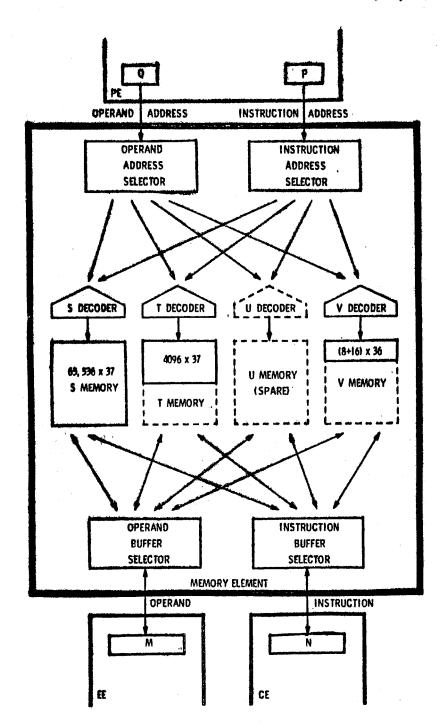

The TX-2 memory element (Fig. 4) is divided into four, independently operating memory systems, each containing up to 65,536-digit words. The operating speed of TX-2 is determined by the cycle time for the memories: The 65,536-word S-memory is expected to have a cycle time of between 6.0 and 7.0 µsecs, and the 4,096 T-memory, a cycle time between 5.0 and 6.0 µsecs. Both memories have parity checks.

Although the <u>U-memory</u> is not presently specified, it may contain a 4,096-word core memory in the initial system. The V-memory consists of 8 flip-flop registers in the central machine and 16 toggle-switch registers which contain the program sequence executed whenever the START button on the operator's console is pushed. The contents of the toggle-switch registers can be used as instructions or operands, but cannot be altered by a program. The six 36-bit registers A,B,C,D,E, and F are part of the V-memory, but their contents can be used only as operands during the execution of an instruction. The programmer has, in a limited sense, a two-address instruction machine when he refers to these registers in load and store type instructions. The other two flip-flop registers in the V-memory are a 60-cps clock and a random-number register.

When an instruction calls for the storing of an operand in memory, the operand memory cycle can be extended up to 2.0 µsecs. The extension occurs between the time that the memory register is read and the time that it is rewritten. During this extension, the contents of memory-registers in the central computer are transferred, the parity of the word read from memory is checked, and the parity of the new memory word is computed. Because the extended cycle is less than

TX-2 Memory Element - Showing method of Fig. 4. using two address registers and two buffer registers to simultaneously operate two out of four memories

the two complete cycles usually used for instructions that modify words, computing efficiency is increased.

The P-register in the program element specifies the location of an instruction in memory and the N-register in the control element holds the instruction after it has been read from memory. The first 2 digits (reading left to right) of P select the memory system from which the instruction word is to be obtained; the remaining 16 digits address the word within the memory. Similarly, the Q-register locates the operand in one of the memory systems, and the operand is placed in the M-register.

## D. Control and Indexing

An instruction word read into N has the structure shown in Fig. 5. The first 2 digits of the word specify information to the in-cut element, and the 4 cf digits specify the computer configuration. The interpretation of the b and n digits is discussed in Section III. The cf digits are discussed in subsection H, p.17.

Fig. 5. TX-2 Instruction Word Structure

The operation code for the instruction is specified by the 6 op digits. On simple load and store type instructions, these

Fig. 6. Program Element Showing paths enabling index adding and storing and loading program counter from the index memory and the exchange element

6 digits are further subdivided into two groups of three. The first group determines the operation and the second specifies the register in the central computer that is being loaded, or whose contents are being stored.

The base address for the operand, formed by the 18 y-digits, is usually modified by the contents of the index register selected by the 6 j-digits. The index-registers form a unique, 64register, parity-checked, core memory which has an access time of 1.0 µsec. The contents of the specified index register is read into the X-register of the program element via the paths indicated in Fig. 6. The base address and the index are fed into a full adder circuit which produces the sum, X = y + (j), in about 1.0 µsec. The over-all complexity of the program element was reduced by having the adder produce both the sum, Y, and the unmodified base address, y: either of these quantities can be directed to the operand memory address register, Q. Whenever the FIRST (j = 0) index register is chosen. the adder produces only the unmodified base address. The effect is the same as having that index register contain ZERO and the programmer can avoid index modification altogether.

The P-register which holds the memory address of instruction words, normally is indexed by one as each instruction is executed, but the output of the index adder is sometimes directed to P when jump instructions are executed. The adder also provides a communication path for index jump instructions from the X-memory to the memory element by way of the exchange element.

#### E. Arithmetic Element (AE)

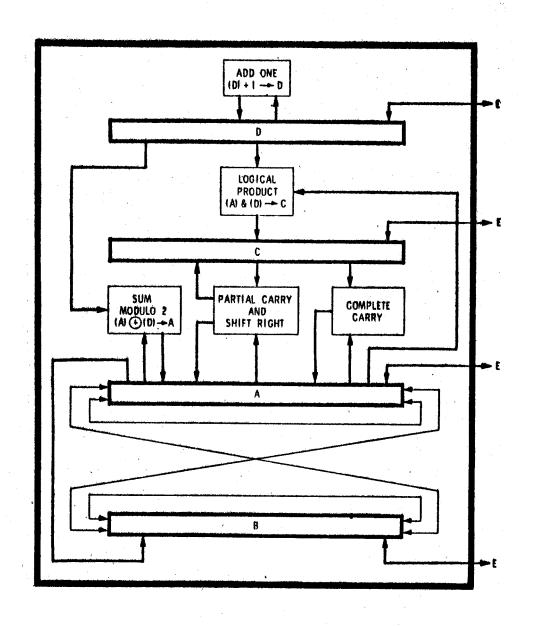

Fig. 7 shows the registers and sufficient basic operations in the arithmetic element for adding, multiplying, dividing, shifting, and executing various logic instructions. Operation timing for most of the TX-2 instructions is also performed in the arithmetic element.

The design of the AE reflects the desire to attain high-speed operation for TX-2, even when the AE is carrying out lengthy instructions. The only instructions which take longer than one memory cycle for execution are those which involve shifting. These are, for example, multiplication, division, arithmetic and cyclic shifting, and normalization. Therefore, the AE contains a sufficient number of storage registers to permit these instructions to be carried out in the AE while the remainder of TX-2 is free to execute other instructions.

The four registers in the AE can each communicate with the Eregister in the exchange element and thus with the Memory Element. As mentioned earlier, these registers are addressable

Fig. 7. Circuits and Transfer Paths (General) Of Any TX-2 Arithmetic Element Forms

as part of the V-memory system. Therefore, programmers have access to the results in any register of an AE computation.

The AE registers, designated by A, B, C, and D, are described below:

The A-Register accumulates the results of all the arithmetic operations, except division, for which it holds the remainder. It holds one of the operands and accumulates the results of the three logic operations (AND, INCLUSIVE OR, EXCLUSIVE OR) which, it should be noted, are bit-wise operations. The information in the A-register can also be shifted (i.e. multiplied by some positive or negative power of two) or cycled (i.e. shifted, without preserving the special significance of the sign bit, as in a closed ring).

The B-Register serves as an extension of A during multiplication, certain shifts and cycles, and, in a sense, during division when the least significant digits of the double-length dividend are stored in B. The resulting quotient then appears in B. Moreover, the information in B can be shifted or cycled independently of A. In multiplication, the multiplier originally in A is transferred via parallel paths directly into B (where the least significant digit then controls the operation).

The C-Register stores the partial carries during arithmetic operations, which is most important during multiplication, as described later. Since these partial carries are actually bit-wise logic products AND, C is also used to accumulate logic products.

The D-Register holds the multiplicands, divisors, addends and one of the operands for the logic operations. It also holds the numbers which control the shifting and cycling of A and B, namely the number of places, up to 62, and the direction, right or left. The ability of D to count is used also to accumulate the results of normalizing A and counting ONES in A.

Each of the AE registers can also be complemented, thus allowing subtractions to be performed.

#### F. AE Circuits

There are four <u>add-one</u> circuits on D, so that different parts of A and B can be controlled separately and simultaneously. For simplicity, just one add-one circuit is shown in Fig. 7. These add-one circuits use the simultaneous carry principle, permitting one count every 0.4  $\mu$ sec; each can count up to 127.

The logical-product (AND) circuit of A and D into C and the sum-modulo

2 (EXCLUSIVE OR) circuit of A and D into A when used at the same time are called a partial add. When the complete-carry circuit is activated after a partial add, the result is a full addition of D and A into A. The complete-carry circuit uses the high-speed carry principle and takes about 1.5  $\mu$ secs for 36 bits.

The partial-carry and shift-right circuit is also known as "multiply step" and was, we believe, first used on Whirlwind I. As it is used in multiplication, this circuit makes a full addition unnecessary for each ONE in the multiplier. Carries are extended only one stage during each step, except the last, when a complete carry is executed. The complete precess takes about 16  $\mu secs$  at most for a full, 36-digit multiplication. The process for division, on the other hand, requires a complete addition at each step and consequently takes about 72  $\mu secs$  in the worst case.

Two features of the AE control should be mentioned here. A 7-bit step counter, like the add-one circuit on D, controls multiplication and division and limits the shifting in normalizing and the cycling in counting ONE's. A flip-flop, which signifies overflow during addition and division, is also used to remember the sign of the product during multiplication and the sign of the quotient during division. If division causes an overflow, the sign is replaced by the overflow state and the quotient is lost.

Control of the arithmetic element is independent of the rest of the machine. Thus, non-AE instructions can be executed while the AE continues to perform a long shift operation or a division.

#### G. System Timing

The high speed of TX-2 is attained in part by overlapping the operation of as many components as is logically possible without incorporating large amounts of circuitry. The time-consuming cyclic operations in an indexed, single-address computer are the instruction memory cycle, the index memory cycle, the index addition time, the operand memory cycle, and the operation timing. These cycles occur in the mentioned sequence during the execution of ordinary instructions. Several asynchronous "clocks," which use a 5-megacycle pulse-source, control the cycles. The instruction and operand memory cycles can be overlapped if they take place in different memory systems.

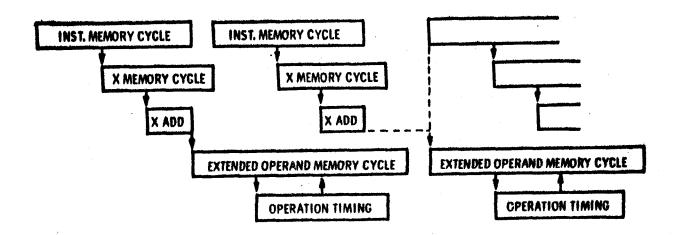

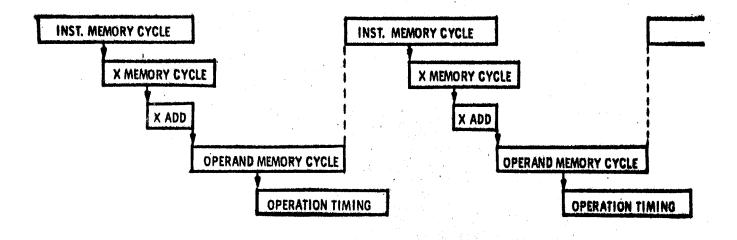

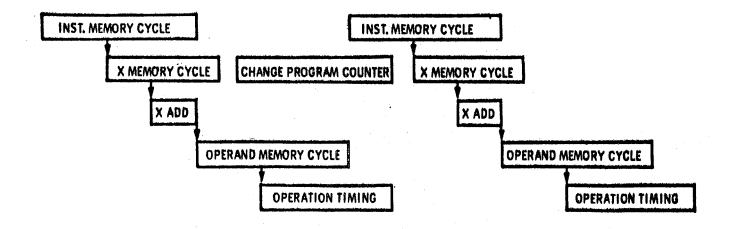

The overlap of these cycle times for a sequence of load-type instructions is illustrated in Fig. 8 (a). Here different

instruction and operand memory systems are assumed to have roughly equal cycle times. If a sequence of store-type instructions is executed which requires extended memory cycles for the operands, then the situation is as shown in Fig. 8 (b). Fig. 8 (c) shows the time used when both the instruction and the operand are in the same memory.

"Peak" operating speed for the computer is attained only when the situation is as shown in Fig. 8 (a); in the situation shown in Figs. 8 (b) and 8 (c) the operating speed could be increased by adding circuitry, but only at considerable cost. It is interesting to note that if the computer is to run at peak speeds, the address of the operand used by the present instruction must be available before the earliest moment at which the next instruction memory cycle could begin. If the total accumulated time, from the beginning of an instruction memory cycle till the time that the address of the operand is known, is greater than the instruction memory cycle time, then the computer cannot run in the ideal manner shown in Fig. 8 (a). This means that the access time of memories and the index-add time must be kept as short as possible.

Fig. 8 (d) shows the timing of events when the in-out element causes a change in program sequence by changing the contents of the P-register. The additional X-memory cycle, which must be performed, produces a timing situation similar to that of the X-memory load and store instructions.

The operation timing for an instruction is executed when the operand is available from memory. Only the arithmetic element step-counter instructions (multiply, divide, shift, etc.) require an operating timing cycle longer than a memory cycle. Since only the arithmetic element is tied up by these instructions, the control element permits any non-arithmetic element instruction to be executed while the AE is busy. Division takes up to 75  $\mu secs$ , so the programmer can write as many as 14 non-AE instructions following a divide, all of which can be executed before the division is completed.

#### H. Configuration Control

The design of a general-purpose computer must necessarily reflect the contradictory demands for both short and long words, floating and fixed-point arithmetic operations, and a multitude of logic and decision instructions. The computer should be able to process information at an optimum rate, in a variety of problems, without the need for intricately coded programs. This ability should be achieved without excessively complex and costly circuitry.

Fig. 8 (a) Consecutive Load Type Instructions Instructions and Operands in Different Memories

Fig. 8 (b) Consecutive Store Type Instructions

Fig. 8 (c) Instruction and Operand In Same Memory

Fig. 8 (d) Change Sequence

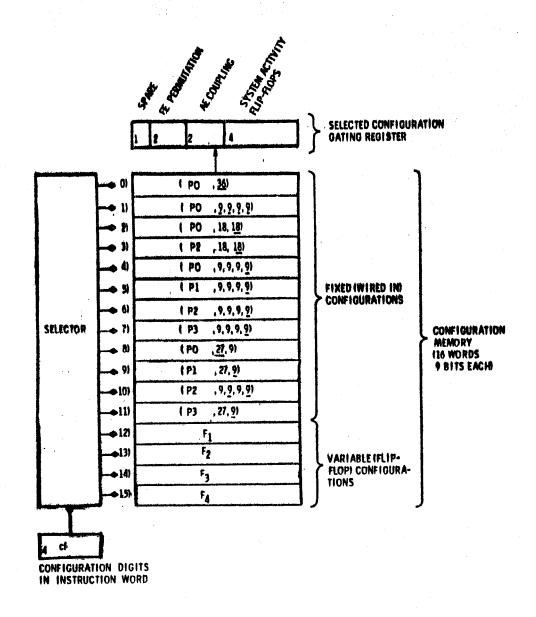

Fig. 9. TX-2 Configuration Selection

The 36-digit word of TX-2 represents a reasonable length for operands in some numerical computations, notably scientific and engineering computations. Though floating-point arithmetic operations are not included in the instruction code, both they and multiple-precision operations can be easily synthesized by means of the existing instructions. The logic instructions in the code facilitate operations on individual digits. Also, a configuration which the programmer specifies with each instruction permits him to perform arithmetic operations on operands that are less than 36 digits long. When operands are less than 36 digits, several can be manipulated simultaneously.

The four <u>cf</u> digits in an instruction word (see Fig. 5) are decoded as shown schematically in Fig. 9, selecting one of 16 configurations. The selected configuration, represented by a 9-digit word, is placed in a flip-flop register whose output levels determine a static configuration for the entire computer while the instruction is executed. The notation used to represent the contents of the first 12 registers will be clarified in the following discussion.

The full 36-digit word length is always maintained for instruction words, but during operation timing, every 36-digit register in the memory, exchange and arithmetic elements is considered as broken into 9-digit quarters, numbered from 1 to 4, right to left as in Fig. 10 (a). While the instruction is being executed, these quarters are recombined on the basis of the configuration.

Information is usually moved about in the machine by parallel transfers between registers (see Fig. 9). The <u>EE permutation</u> digits select one of the four permutations PO, Pl, P2, P3, shown in Fig. 10 (b). The chosen permutation effects the corresponding cross-communication paths between the quarters of the E- and M-registers of the exchange element. While operands are transmitted through the EE, the quarters follow the set of paths determined by the selected permutation. The result is that the operand is shifted 9n places to the left as it moves from M to E or 9n places to the right as it moves from E to M, n = 0,1,2 or 3. Thus, the programmer can have any quarter of the AE communicate with any quarter of the ME.

This ability to communicate is focused more sharply by having the configuration specify a system activity (see Fig. 9). All operation timing events, in a given quarter of the AE and EE and the quarter of the ME connected via the selected permutation path in the EE, are controlled by the activity flip-flop on that quarter. If the activity flip-flop of a given quarter is a ONE, as specified by the configuration, the operation timing

Fig. 10 (a) Quartering Permutation Paths and Activity Flip-Flops Shown

Fig. 10 (b) Paths in Exchange Element

Fig. 11 (a) ith Quarter Coupling Units

(b) Coupling Unit Connections

events of the instruction occur in that quarter. If the activity flip-flop is a ZERO, nothing happens.

During the execution of arithmetic operations, the AE coupling digits (see Fig. 9) further specify the connections of the IE teral information paths between quarters in the AE. Information flows laterally only through the shift and the carry circuits, and the connection of these circuits alone determines the word lengths of the numerical quantities manipulated in the AE.

As shown in Fig. 11 (a), every quarter of the AE has coupling units at each end which receive the shift and carry information entering the quarter. The general type of connections between several quarters is shown in Fig. 11 (b). The digit length of operands, during add and shift operations, is determined by the number of quarters coupled together. In TX-2, from 1 to 4 quarters can be coupled together to permit arithmetic operations on 9-, 18-, 27-, or 36-digit operands. The various combinations of coupling-unit connections actually chosen by the AE coupling are symbolized in Fig. 11 (c). Since A-register, B-register, and AB-register shifts are permitted in the arithmetic element, the programmer can obtain 18-, 36-, 54-, or 72-digit shifts. All the possible shift (and cycle) configurations are shown in Fig. 11 (d).

Only those inputs to the coupling units which would yield useful arithmetic element structures are realized by the AE coupling. It should be emphasized that the programmer can realize several arithmetic elements simultaneously. The coupling, (36), gives only one 36-bit arithmetic element, but the coupling, (18,18), gives two complete, independent, 18-bit arithmetic elements which are separately, but simultaneously, controlled by the instruction being executed. Two arithmetic elements are again available with the coupling, (27,9), one 27 bits and the other 9 bits long, and the (9,9,9,9) coupling gives four, 9-bit arithmetic elements. The permutation paths in the exchange element permit each arithmetic element to communicate with any quarter of a memory word and the activity flip-flops can specify just which of the realized arithmetic elements actually will be active and will communicate with the connected part of memory.

In Fig. 12, several examples are given of the different configurations which can be realized in TX-2. The most straightforward has one, 36-digit arithmetic element and communicates directly with memory. The notation, (PO, 36) signifies the permutation (no shift) and the form of the arithmetic element (one 36-digit). The underlining indicates that the whole system is active. Slightly more varied is the (PO, 9,9,9,9) configuration which specifies four, 9-digit arithmetic elements communicating directly with memory, but with only two of them active. The (P2, 9,9,9,9) configuration

Fig. 11 (c) TX-2 Configuration - Arithmetic Elements

And Operand Word Structures

| } | SEPARATE (A,B SHIFT PATHS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | COMBINED (AB SHIFT PATHS)                                          |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 1 | A4 A3 A2 A1<br>B4 B3 B2 B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A4 A3 A2 A1                                                        |

| 1 | A4 A3 A A2 A1 A1 B4 B4 B3 A B2 B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A4 A3 A2 A; B4 B3 B2 B1                                            |

| 1 | A4 i A3 i A2   [ 41 ]   [ 84 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ]   [ 81 ] | $\begin{bmatrix} A_4 & A_3 & A_2 \\ B_4 & B_3 & B_2 \end{bmatrix}$ |

|   | A4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

Fig. 11 (d) TX-2 Shift Path Arrangements

Fig. 12. **TX-**2 Configurations

Areas Of Activity During Execution Of Instruction Shown Shaded. Effect Of AE Couplings Illustrated By Juxtaposition Of Quarters

has the same arithmetic elements but with the associated memories interchanged. The (P2, 18,18) configuration illustrates an 18-digit arithmetic element which uses the "other" half of memory.

One of the digits in the 9-digit configuration is at the moment unused, but will probably be used to control the extension of the sign of numbers as they pass through the EE on the way from the ME to the AE. The scheme presently under consideration would permit programmers, for example, to add a 9-digit memory operand to an 18-digit arithmetic element. This scheme would permit closer packing of operands in memory and significantly increase the speed of solving some real-time problems, where the sign of short pieces of data must be extended so that higher precision can be maintained during computations. The working details of the scheme have yet to be fixed.

The memory from which the programmer chooses a configuration for use with each instruction was shown in Fig. 9. Twelve of the memory registers are fixed circuitry whose contents cannot be changed without changing the wiring of the computer. The configurations represented by the contents of these registers are assumed to be useful to most programmers. The last four registers in the memory consist of the 36 digits of the F-register. As will be seen, the programmer can quite simply alter the contents of this register and thereby obtain any of the possible configurations. The total number of distinct possible configurations is less than  $2^9$ .

#### I. Operation Code

Only 51 of the 64 possible operation codes are currently decoded to define instructions. In Table I the effect of each instruction is described. If the selected configuration defines several computers, the operation takes place in all of them simultaneously and independently. The notation used in the definition of the operation is described in Table II.

The instructions are grouped according to type. Load and store instructions transfer an operand between a selected register and memory. The load-complement instructions are variants which load the ONES complement into the selected registers. The Exchange instruction interchanges the contents of A and of the addressed memory register. The insert instruction allows any set of bits in A, as specified by the bits in B, to be stored in memory. The j-bits of the load and store instructions, which refer to the index memory, select the index register involved so that the operand address is not modified.

All of the add and step-counter instructions can also be classed as load type instructions, in so far as the operand memory cycle

is concerned. The multiply instruction forms the full product in the A and B registers. Division is the inverse of multiplication, the double-length divident in A and B being divided by the memory operand. The remainder is left in A and the quotient in B. Normalize instructions shift the contents of A and B left until the magnitude of the number in A is between one-half and one. The number of shifts to do this (the normalizing factor) is subtracted from the memory operand in D. Since more than 18 bits are required to specify all the possible shifts for the (9,9,9,9) configuration, the shift and cycle instructions use at the memory operand, rather than the address section of the instruction to specify the number of places to shift. The count ones instruction adds the number of ONE's bits in A to the memory operand in D, thus providing a simple means for determining bit density in areas of storage, since the ONE's count for several words can be accumulated in D.

The two replace-add instructions, using the index memory, facilitate instruction and index modification. Both require two memory-cycle times for execution.

The two in-out read instructions transmit information between the memory and the selected in-out unit. The details of these instructions and the in-out select instruction are given in Section III.

Single bits in memory can be manipulated with the three bitsetting instructions. The bit-sensing instruction facilitates the use of single bits in memory as operands. The variety of available jump instructions simplifies the coding of, logic decision functions. The two index-jump instructions permit indexed program loops to refer successively in either the forward or backward direction to operands in a data block. The unconditional-jump instruction uses the <u>cf</u> digits to specify whether the selected index register will be used to remember the previous contents of P. These contents are always transmitted to the E-register whenever a jump occurs.

Arithmetic overflows can be caused by addition, subtraction, and division instructions. Such overflows as do occur are remembered in overflow flip-flops in the arithmetic element. The overflow condition can be detected by a jump instruction, or by the in-out element in a manner described in Section III. If an overflow is anticipated, however, it can be shifted into the A register by executing a normalize instruction. A normalize usually shifts AB left. However, if an overflow exists, AB is shifted right one place and the overflow placed in the most significant digit position of A to the right of the sign digit. The memory operand is also increased by one in the D register, rather than decreased. This

interpretation of an overflow permits floating-point operations to be programmed very simply in the arithmetic element. The in-out select and operate instructions differ from all the others in the sense that the y-digits are used to specify different operations. In-out select chooses the mode in which an in-out unit will run. The operate instruction will control individual useful commands, e.g., round-off.

# J. Instruction Times

The average execution time for instructions depends upon whether one memory or two different, overlapped memory systems are used for instructions and operands. If one memory is used, the execution time is the sum of the instruction and operand cycle times; if two memories are used, the execution time is the longer of the two memory cycle time. It should be remembered that any instruction which involves storing an operand in memory has the normal operand memory cycle time extended by from 1.0 to 2.0 µsecs. Instructions which alter or transfer the contents of index memory registers require approximately two memory cycles, even when instruction and operand memory cycles are overlapped.

Successive step-counter instructions require a time which depends upon the length of the longest active arithmetic element. In the case of multiply, divide and count ONE's, this time is a function of the length of the operand word only, but the shift, cycle, and normalize times depend upon the number of places actually shifted. Divide requires about 2.0  $\mu$ secs per digit and all other step-counter instructions 0.4  $\mu$ secs per digit. These shift times become significant only when they exceed the one or two memory cycles already required. In the worst 36-digit case, about 75  $\mu$ secs are required for division and 19  $\mu$ secs for multiplication. A 72-place shift would take 32  $\mu$ secs. These are the times required for these instructions when they are written in sequence. If the operand word is shorter, then these times become proportionally less, down to the minimum memory times required.

#### K. Summary

The organization of TX-2 permits a programmer, who pays considerable attention to coding details, to receive a worthwhile reward in the form of increased efficiency of operation. The operating speed can be doubled when instruction and operands are stored in different memories. Higher speeds result from sequencing instructions so that non-AE instructions are executed concurrently with AE step-counter instructions. And the ability to choose a configuration with each instruction means not only that some instructions take less time, but also that many of them can be eliminated from a program altogether.

However, this versatility and efficiency is not accompanied by a

disastrous loss in simplicity. The system organization is such that details can be easily ignored by the naive programmer, without the details having even subtly unfavorable effects. If all the digits in an instruction word are ZERO, except for the operation code and the base address, then TX-2 appears as a simple single-address computer with operand words 36-bits long and with a single, uniformly addressed, 70,000-word memory.

If the j-bits are used, then the machine is enlarged to become an indexed, single-address, computer, with operand words 36 bits long, for which the entire instruction code is meaningful. When the b and d bits are used, the programmer can control the manner in which several in-out units, running concurrently, can cause the computer to change program sequences. And by selecting various configurations, the programmer can perform more operations simultaneously with each instruction.

The different facilities for indexing, memory overlap, instruction overlap, multiple-sequencing, and configuration can be ignored or used as the programmer desires. Ignoring them would seem to permit straight-forward coding; using them actually permits much shorter and faster codes for a given function. Each facility is represented by a clear concept of what the facility permits, the only real difficulty being the number of simultaneous actions possible with each instruction. However, higher speeds and greater system capacity are obtained by shorter cycle times, increased bit storage and greater simultaneousness of events. In TX-2, all three aspects are emphasized.

TABLE I

|        |               | TABLE I                                                                                                                                                        |                                                 |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Туре   | Mnemonic Code | Operation                                                                                                                                                      | Name                                            |

|        | lda           | (A                                                                                                                                                             | Loed into A                                     |

|        | ldb           | <b>\B</b>                                                                                                                                                      | Load into B                                     |

|        | låc           |                                                                                                                                                                | Load into C                                     |

|        | 1dd           | (Y) C                                                                                                                                                          | Load into D                                     |

| Load   | lde           | E<br>E                                                                                                                                                         | Load into E                                     |

|        | ldE           | E                                                                                                                                                              | Load into E                                     |