# MASSACHUSETTS INSTITUTE OF TECHNOLOGY LINCOLN LABORATORY

# TX-2 USERS HANDBOOK

ALEXANDER VANDERBURGH, Jr. (Ed.)

LINCOLN MANUAL NO.45

JULY 1961

The work reported in this document was performed at Lincoln Laboratory, a center for research operated by Massachusetts Institute of Technology, with the joint support of the U.S. Army, Navy and Air Force under Air Force Contract AF 19(604)-7400.

Note to TX-2 Users -

The TX-2 Users Handbook will be printed in several installments - you now have the first. There will be seven chapters - they are listed below in order of (expected) appearance:

> Chapter 4 - In-Out System - Sections 46 and 74 (Mag. Tape and Plotter) to come later. 7 - Charts 6 - M4 Utility System

> 5 - Lights and Buttons

→ Fall '61 3 - Operation Code

2 - Functional Description1 - IntroductionWho knows?

Your comments, criticisms, and (unfortunately,) corrections, are requested.

# TX-2 USERS HANDBOOK

# CHAPTER 3 - OPERATION CODE

#### TABLE OF CONTENTS

|              |           |                                            | Page          |

|--------------|-----------|--------------------------------------------|---------------|

| 3-1          | BRIEF GUI | DE TO THE ABBREVIATIONS                    | 3 <b>-</b> 3  |

| 3 <b>-</b> 2 | OP CODE D | ESCRIPTIONS - (For In Out, See Chapter 4.) | 3 <b>-</b> 5  |

|              | 3-2.1     | LOAD-STORE CLASS                           | 3 <b>-</b> 5  |

|              |           | LDA, LDB, LDC, LDD, (LDE) - LOAD           | 3-6           |

|              |           | STA, STB, STC, STD, (STE) - STORE          | 3 <b>-</b> 8  |

|              |           | EXA - EXCHANGE                             | 3-10          |

|              | 3-2.2     | INDEX REGISTER CLASS                       | 3-13          |

|              |           | RSX - Reset Index                          | 3-14          |

|              |           | DPX - Deposit Index                        | 3-16          |

|              |           | EXX - Exchange Index                       | 3-18          |

|              |           | AUX - Augment Index                        | 3-20          |

|              |           | ADX - Add Index                            | 3-22          |

|              |           | SKX - Skip on Index                        | 3-24          |

|              |           | JPX - Jump on Positive Index               | 3 <b>-</b> 26 |

|              |           | JNX - Jump on Negative Index               | 3 <b>-</b> 26 |

|              | 3-2.3     | JUMP-SKIP CLASS                            | 3-29          |

|              |           | JMP - Jump (with variations)               | 3-30          |

|              |           | JPA - Jump on Positive Accumulator         | 3-32          |

|              |           | JNA - Jump on Negative Accumulator         | 3 <b>-</b> 32 |

|              |           | JOV - Jump on Overflow                     | 3-32          |

|              |           | SKM - Skip on Bit                          | 3-34          |

|              |           | SED - Skip if E Differs                    | 3-36          |

|              | 3-2.4     | SCALE, NORMALIZE CYCLE                     | 3-37          |

|              |           | SCA, SCB, SAB - Scale                      | 3-38          |

|              |           | NOA, NAB - Normalize                       | 3-40          |

|              |           | CYA, CYB, CAB - Cycle                      | 3-42          |

|     |           |                                    | Page          |

|-----|-----------|------------------------------------|---------------|

|     | 3-2.5     | LOGIC, INSERT, COMPLEMENT/PERMUTE  | 3-45          |

|     |           | ITA, UNA, DSA, ITE - Logic         | 3 <b>-</b> 46 |

|     |           | INS - Insert                       | 3-48          |

|     |           | COM - Complement/Permute           | 3-50          |

|     | 3-2.6     | CONFIGURATION MEMORY CLASS         | 3 <b>-</b> 53 |

|     |           | SPF, SPG - Specify                 | 3-54          |

|     |           | FLF, FLG - File                    | 3 <b>-</b> 55 |

|     | 3-2.7     | ARITHMETIC CLASS                   | 3-57          |

|     |           | ADD, SUB                           | 3 <b>-</b> 58 |

|     |           | MUL                                | 3 <b>-</b> 60 |

|     |           | DIV                                | 3 <b>-</b> 62 |

|     |           | TLY                                | 3 <b>-</b> 65 |

| 3-3 | OPERATION | CODE CHART (Wesley A. Clark)       | 3-67          |

|     | 3-3.1     | NUMBER SYSTEMS                     | 3 <b>-</b> 68 |

|     | 3-3.2     | GLOSSARY OF TERMS                  | 3-68          |

|     |           | OPERATION CODE CHART               | 3-71          |

|     | 3-3-3     | NOTES ON THE CODING CHART          | 3-73          |

| - \ |           |                                    |               |

| 3-4 | CHAPTER 3 | INDEX (Alphabetical and Numerical) | 3-77          |

#### 3-1 BRIEF GUIDE TO THE ABBREVIATIONS

#### Examples:

$$^{\alpha}$$

[T] ==> A The configured contents of STUV memory register T goes into the accumulator.

Sq3(A) ==> q4A The sign of quarter 3 of A is copied into all of quarter 4 of the accumulator.

[X<sub>j</sub>] ==> L(T) The contents of X memory register j goes into the left half of STUV register T.

L[T] ==> X<sub>j</sub> The left half of STUV register T goes into X register j.

q1[T<sub>j</sub>] ==> F <sub>$\alpha$</sub>  Quarter one of the contents of STUV memory T<sub>j</sub> is copied into F memory register  $\alpha$ .

The notation below is borrowed from the M4 Utility system. (See Chapter 6.)

{w} Register Containing w

\* Deferred address

A,B,C,D,E The AE addresses: 377604, 377605, 377606, 377607, and 377610

# The current location - i.e. the location of the instruction being performed.

# 3-2 Op Code Descriptions

3-2.1 LOAD, STORE, EXCHANGE

LDA LDB

LDC LDD LDE

STA

STB

STC

STD STE

EXA

| LOAD | ΑĒ | (24-27)  |      |

|------|----|----------|------|

| LOAD | Ε  | REGISTER | (20) |

| LDA,<br>LDB,<br>LDC, | 24<br>25<br>26 | LD#<br>24 |

|----------------------|----------------|-----------|

| LDD,<br>LDE,         | 27<br>20       |           |

$$\alpha_{\text{LDA T}_{j}}$$

$\alpha_{\text{[T}_{j}]} => A$

LOAD means copy into the AE from STUV memory. STUV memory is not changed. Activity, Sign Extension, and permutation are used. ALL load instructions except LDE perform the standard  $[T_{\hat{j}}] => E$ .

EXAMPLES: \*\*(Standard F memory - Chart 7-2)

| NO. | INSTRUCTION                                               | CONFIGURATION<br>DIAGRAM    | ABBREVIATED<br>DESCRIPTION                               | COMMENT                                                                                                                     |

|-----|-----------------------------------------------------------|-----------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1.  | LDA T                                                     | T <sub>j</sub> VIIIIIIIII A | [T <sub>j</sub> ] ==> A<br>[T <sub>j</sub> ] ==> E       | Since all four quarters are active, subword form is immaterial. <sup>20</sup> LDA or <sup>30</sup> LDA would be equivalent. |

| 2.  | <sup>1</sup> LDA T <sub>j</sub>                           | T <sub>j</sub>              | R[T <sub>j</sub> ] ==> R(A) [T <sub>j</sub> ] ==> E      | The left half of A is not changed.                                                                                          |

| 3.  | ll <sub>LDA</sub> T <sub>j</sub> [F <sub>11</sub> ] = 140 | T <sub>j</sub>              | $R[T_{j}] ==> R(A)$ $SR[T_{j}] ==> L(A)$ $[T_{j}] ==> E$ | The 18 bit word from STUV is "expanded" to 36 bits through "sign extension."                                                |

| 4.  | <sup>2</sup> LDA T <sub>j</sub>                           | T <sub>j</sub>              | $L[T_{j}] \implies R(A)$ $[T_{j}] \implies E$            | A "Right Half Load" -<br>the left half of A is<br>not affected.                                                             |

<sup>\*\*</sup>All examples apply directly to LDA, LDB, LDC, and LDD. LDE is essentially the same - only the final M to E copy is omitted.

| LDA, | 24 |   | LDA |

|------|----|---|-----|

| LDB, | 25 | * | 24  |

| LDC, | 26 |   |     |

| LDD, | 27 |   |     |

| T.DR | 20 |   |     |

| 5. | <sup>2</sup> LDA A                                           | A (Before                      | ) L[A] ==> R(A) [A] ==> E                                                                              | The left half of A is unchanged. The right half becomes the same as the left. In a similar manner, <sup>22</sup> LDA A sets the left equal to the right. <sup>12</sup> LDA would clear the left half word through sign extension. |

|----|--------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6. | 16 <sub>LDA</sub> T <sub>j</sub><br>[F <sub>16</sub> ] = 163 | T <sub>j</sub>                 | $q^{4}[T_{j}] =\Rightarrow qL(A)$ $Sq^{4}[T_{j}] =\Rightarrow q^{2}, 3, 4(A)$ $[T_{j}] =\Rightarrow E$ | The nine bit number in quarter 4 of T, is expanded to 36 bits in A.                                                                                                                                                               |

| 7. | <sup>l</sup> LDA {T <sub>k</sub> }*                          | (T <sub>k</sub> ) <sub>j</sub> | $R[(T_k)_j] \Longrightarrow R(A)$ $[(T_k)_j] \Longrightarrow E$                                        | This is double indexing. $ (T_k)_j \equiv T + [X_k] + [X_j]. $ (It is not always faster because the defer cycle takes time also.)                                                                                                 |

| STORE AE (34-37) STORE E (30) | STA,<br>STB,<br>STC,<br>STD, | 35 34<br>36<br>37 |

|-------------------------------|------------------------------|-------------------|

|                               | STE,                         | 30                |

| A = A | a <sub>STA T</sub> | α[A] ==> T <sub>j</sub> |

|-------|--------------------|-------------------------|

|-------|--------------------|-------------------------|

STORE is a non-destructive copy from AE to STUV memory. With a partially active configuration it becomes a <u>partial</u> store. Subword form is meaningless - only active pathways are used. The E register is set from the memory word after the store operation (except for STE which does not change E).

EXAMPLES: \*\*(Standard F Memory - Chart 7-2)

| EXAMPLES: **(Standard F Memory - Chart 7-2) |                                 |                          |                                |                                                                                                                                                    |  |  |

|---------------------------------------------|---------------------------------|--------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.                                         | INSTRUCTION                     | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>DESCRIPTION     | COMMENT                                                                                                                                            |  |  |

| 1.                                          | STA T                           | Tj                       | [A] ==> T <sub>j</sub> **      | T <sub>j</sub> is set from A, A is not changed. Since all quarters are active, all are copied into T <sub>j</sub> .                                |  |  |

| 2.                                          | <sup>1</sup> STA T <sub>j</sub> | T <sub>j</sub>           | R[A] ==> R(T <sub>j</sub> ) ** | Since there is no sign extension, $^{11}STA$ would have the same affect. $[F_{11}] = 140$                                                          |  |  |

| 3.                                          | <sup>2</sup> sta t <sub>j</sub> | T <sub>j</sub>           | R[A] ==> L(T <sub>j</sub> ) ** | $^{12}STA$ would be exactly the same. $ [F_{12}] = 142 $                                                                                           |  |  |

| 4.                                          | <sup>2</sup> sta a              | A A                      | R[A] ==> L(A) **               | This sets the left equal to the right (as does <sup>22</sup> LDA A). Since there is no sign extension on STA, <sup>12</sup> STA would do the same. |  |  |

|                                             |                                 | Α                        |                                |                                                                                                                                                    |  |  |

<sup>\*\*</sup> After the store operation is complete, the new content of  $\mathbf{T}_{\mathbf{j}}$  is copied into E except for the STE instruction which does not change E.

STA, 34 STA STB, 35 34 STC, 36 STD, 37 STE, 30

| 5. | <sup>5</sup> STA T <sub>j</sub><br>[F <sub>5</sub> ] = 762 | T <sub>j</sub>                 | q1[A] ==> q3(T <sub>j</sub> ) **          | Quarter l is copied into quarter 3 of T <sub>j</sub> . The rest of T <sub>j</sub> is unchanged.                                |

|----|------------------------------------------------------------|--------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 6. | l <sub>STE</sub> T <sub>j</sub><br>(Store <u>E</u> )       | T <sub>j</sub>                 | R[E] ==> L(T <sub>j</sub> )               | Stores in the right half only - useful for setting address sections - (For example, at start of subroutines entered via hJPQ). |

| 7. | STA {T <sub>k</sub> }*                                     | (T <sub>k</sub> ) <sub>j</sub> | [A] ==> (T <sub>k</sub> ) <sub>j</sub> ** | Double indexing - $(T_k)_j \equiv T+[X_k]+[X_j]$                                                                               |

| α <sub>EXA</sub> Τ. | $\alpha_{[A]} => T_{j}$ |

|---------------------|-------------------------|

| EXA T<br>           | $\alpha_{[T_j]} => A$   |

EXCHANGE A is a combination of STA and LDA. Sign extension, if any, occurs only in A and  $\underline{\text{after}}$  the exchange of data. Subword form, Activity, and permutation are all used.

The E register is set equal to the STUV memory word used.

#### EXAMPLES:

| EXAM | PLES:                                                     |                          |                                                              |                                                             |

|------|-----------------------------------------------------------|--------------------------|--------------------------------------------------------------|-------------------------------------------------------------|

| NO.  | INSTRUCTION                                               | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>DESCRIPTION                                   | COMMENT                                                     |

| 1.   | EXA T <sub>j</sub>                                        | Tj                       | [T <sub>j</sub> ] ==> A<br>[A] ==> T <sub>j</sub>            | **                                                          |

| 2.   | <sup>l</sup> exa T <sub>j</sub>                           | T <sub>j</sub>           | $R[T_{j}] ==> R(A)$ $R[A] ==> R(T_{j})$                      | **                                                          |

| 3.   | 11 <sub>EXA</sub> T <sub>j</sub> [F <sub>11</sub> ] = 140 | T <sub>j</sub>           | $SR[T_{j}] ==> L(A)$ $R[T_{j}] ==> R(A)$ $R[A] ==> R(T_{j})$ | Sign extension occurs in A, but not in T <sub>j</sub> .  ** |

| ù.   | <sup>2</sup> EXA T <sub>j</sub>                           | T <sub>j</sub>           | $L[T_{j}] ==> R(A)$ $R[A] ==> L(T_{j})$                      | **                                                          |

<sup>\*\*</sup> The two copy operations that perform an exchange take place simultaneously. Remember also that E is changed - it is set equal to the final contents of the STUV memory word.

| 5. | <sup>5</sup> EXA T <sub>j</sub><br>[F <sub>5</sub> ] = 762 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <sup>T</sup> j                           | $q3[T_{j}] ==> q1A$ $q1[A] ==> q3(T_{j})$ | **                                                                                                                            |

|----|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 6. | <sup>2</sup> exa a                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A (After)                                | R[A] ==> L(A)                             | When "A" is used as the address section, EXA has the same affect as STA.  No exchange is made, and there is no sign extension |

| 7. | exa {t <sub>k</sub> }*                                     | \(\frac{1}{1} \dots \dot | $(\mathtt{T}_{\mathrm{k}})_{\mathtt{j}}$ | $[(T_k)_j] ==> A$ $[A] ==> (T_k)_j$       | Double indexing: $\left(\mathbf{T}_{k}\right)_{j} = \mathbf{T} + \left[\mathbf{X}_{k}\right] + \left[\mathbf{X}_{j}\right]$   |

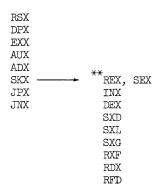

# 3-2.2 Index Register Class

\*\* Supernumerary Mnemonics for SKX.

| $\begin{bmatrix} RSX & T & T \\ T & T \end{bmatrix} = X$ |

|----------------------------------------------------------|

|----------------------------------------------------------|

RESET is a non-destructive copy from STUV memory into  $\boldsymbol{X}$  memory.

Subword form, Activity, and Permutation are used.

The E register is set equal to the STUV memory word  $\underline{\text{used}}$ . (Usually "T", but see example 7.)

EXAMPLES: (Standard Configurations - Chart 7-2)

| NO. | INSTRUCTION                                     | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>EXPLANATION                             | COMMENT                                                                                                                                                |

|-----|-------------------------------------------------|--------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | <sup>l</sup> rsx <sub>j</sub> T                 | T X J                    | R[T] ==> X <sub>j</sub><br>[T] ==>E                    | ORSX would do the same.                                                                                                                                |

| 2.  | <sup>2</sup> RSX <sub>j</sub> T                 | T X <sub>j</sub>         | L[T] ==> X <sub>j</sub> [T] ==> E                      | $^{12}$ RSX would do the same. $ [F_{12}] = 142 $                                                                                                      |

| 3.  | <sup>3</sup> rsx <sub>,</sub> T                 | T x <sub>j</sub>         | ql[T] ==> R(X <sub>j</sub> ) [T] ==> E                 | The right half of $X_j$ is set from $T$ . The left nine bits are not changed.                                                                          |

| 4.  | 13 <sub>RSX</sub> T [F <sub>13</sub> ] = 160    | T X                      | $q1[T] ==> R(X_{j})$ $Sq1(T) ==> L(X_{j})$ $[T] ==> E$ | Sign of quarter 1 of T is extended throughout the left half of $X_j$ . The right half is set as above. $^{33}$ RSX would do the same. $[F_{33}] = 320$ |

| 5.  | 21 <sub>RSX</sub> T<br>[F <sub>21</sub> ] = 230 | T x <sub>j</sub>         | [T] ==> E                                              | Nothing happens (other than changing E).                                                                                                               |

| 6. | $\alpha_{\text{RSX}_{j}}$ T $[F_{\alpha}] = 030$ | T x <sub>j</sub> | Sql+(T) ==> X<br>[T] ==> E                                    | This time $\mathbf{X}_{\mathbf{j}}$ is cleared because of sign extension.                               |

|----|--------------------------------------------------|------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 7. | $RSX_j^*{\mathbb{T}_k}$                          | T <sub>k</sub>   | R[T <sub>k</sub> ] ==> X <sub>j</sub> [T <sub>k</sub> ] ==> E | With a deferred address, RSX is indexable. Note that E is set from $\mathbf{T}_{\mathbf{k}}$ this time. |

| 8. | а <sub>RSX</sub> т                               |                  | [T] ==> E                                                     | Nothing happens because X register 0 cannot be changed. $ [X_{0}] = 0 \text{ permanently.} $            |

| DPX T |

|-------|

|-------|

DEPOSIT is a non-destructive copy from  $\boldsymbol{X}$  memory into STUV memory.

Activity and Permutation are used.

The X memory word is expanded to a full 36 bit subword by extending bit 2.9 (the X register sign bit) but only  $\underline{\text{active}}$   $\underline{\text{quarters}}$  are used. (The subword form is immaterial.)

The E register is set equal to the STUV memory used. (Usually "T", but see examples 8 and 10.)

EXAMPLES: (Standard F Memory - Chart 7-2)

| NO. | INSTRUCTION                                                  | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>EXPLANATION                                                       | COMMENT                                                                                                                             |

|-----|--------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | <sup>l</sup> dpx <sub>j</sub> T                              | ↑ ↑ x <sub>j</sub>       | $\left[X_{j}\right]\Rightarrow R(T)$                                             | Only the right half of T is changed.                                                                                                |

| 2.  | <sup>2</sup> dpx <sub>j</sub> t                              | T x <sub>j</sub>         | $\left[X_{j}^{-}\right] \Rightarrow L(T)$                                        | Only the left half of T is changed.                                                                                                 |

| 3.  | DPX <sub>,</sub> T                                           | † † † † x <sub>j</sub>   | $\begin{bmatrix} X_{j} \end{bmatrix} \Rightarrow R(T)$ $SX_{j} \Rightarrow L(T)$ | All of T is used. Note that DPX <sub>O</sub> T (or DPX T) is a handy clear instruction. ( $[X_O] \equiv +0$ and cannot be changed.) |

| 4.  | <sup>3</sup> dpx <sub>j</sub> T                              | ↑ x <sub>j</sub>         | $R[X_j] \Rightarrow ql(T)$                                                       | Only quarter l of T is changed.                                                                                                     |

| 5.  | <sup>16</sup> DPX <sub>j</sub> T<br>[F <sub>16</sub> ] = 163 | T x <sub>j</sub>         | $\mathbb{R}\left[X_{j}\right] \Rightarrow q^{1/4}(\mathbb{T})$                   | Only quarter 4 is changed for only one path is active.                                                                              |

| 6.  | <sup>17</sup> DPX <sub>j</sub> T [F <sub>17</sub> ] = 202 | x <sub>j</sub>           | $SX_{j} \Longrightarrow R(T)$ $[X_{j}] \Longrightarrow L(T)$                                                                                                                       | All of T is affected.                                                                                                                           |

|-----|-----------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.  | 21 <sub>DPX</sub> , T [F <sub>21</sub> ] = 230            | T x <sub>j</sub>         | $SX_j \Longrightarrow L(T)$                                                                                                                                                        | Surprisingly enough, this does do something. (See example 5, RSX.)                                                                              |

| 8.  | ldpx <sub>j</sub> {T <sub>k</sub> }*                      | T <sub>k</sub>           | $\begin{bmatrix} \mathbf{X}_{\mathbf{j}} \end{bmatrix} \Longrightarrow \mathbf{T}_{\mathbf{k}}$ $\begin{bmatrix} \mathbf{T}_{\mathbf{k}} \end{bmatrix} \Longrightarrow \mathbf{E}$ | Deposit is indexable with deferred addressing.                                                                                                  |

| 9.  | $33_{DPX_{j}}$ T [F <sub>33</sub> ] = 320                 | <b>▼</b> ↑ ↑  ×   x      | $SX_{j} \Longrightarrow q3(T)$ $[X_{j}] \Longrightarrow q1(T)$                                                                                                                     | Note that bit 2.9 of X is used even though quarter 2 is not active.                                                                             |

| 10. | DPX 377720                                                | T † † † † x <sub>j</sub> | $\begin{bmatrix} X_{j} \end{bmatrix} \Longrightarrow R(E)$ $SX_{j} \Longrightarrow L(E)$                                                                                           | V memory, except the A, B, C, D, and E registers can not be changed by any instruc- tion. Note that E is set to "what-would-have-gone-into- T." |

| α <sub>EXX</sub> Τ | $\alpha[x_j] => T$      |

|--------------------|-------------------------|

| j                  | α[T] ==> X <sub>ĵ</sub> |

EXX is a combination of RSX and DPX. Except for sign extension, it does just what its name implies - i.e. it will interchange words between X memory and STUV memory.

Subword Form, Activity, and Permutation are used. The E register is set equal to the STUV memory word used.

| EXAMPLES: | (Standard | F | Memory | _ | Chart | 7-2. | Ì |

|-----------|-----------|---|--------|---|-------|------|---|

|           |           |   |        |   |       |      |   |

| EXAMI | PLES: (Standard                              | F Memory - Chart 7-2.)   |                                                                                                                 |                                       |

|-------|----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------|

| NO.   | INSTRUCTION                                  | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>EXPLANATION                                                                                      | COMMENT                               |

| 1.    | <sup>1</sup> EXX <sub>j</sub> T              |                          | R[T] ==> X<br>[X j] ==> R(T)<br>[T] ==> E                                                                       |                                       |

| 2.    | <sup>2</sup> EXX <sub>j</sub> T              | T x <sub>j</sub>         | L[T] ==> X <sub>j</sub> [X <sub>j</sub> ] ==> L(T) [T] ==> E                                                    |                                       |

| 3.    | EXX <sub>j</sub> T                           | T                        | R[T] ==> X<br>[X <sub>j</sub> ] ==> R(T)<br>S(X <sub>j</sub> ) ==> L(T)<br>[T] ==> E                            | Note that left half of T is cleared.  |

| 4.    | 3 <sub>EXX</sub> , T                         | T<br>†<br>X              | ql[T] ==> R(X <sub>j</sub> ) R[X <sub>j</sub> ] ==> ql(T) [T] ==> E                                             | Nine bit exchange.                    |

| 5.    | 16 <sub>EXX</sub> T [F <sub>16</sub> ] = 163 | T X                      | $R[X_{j}] ==> q^{\downarrow}(T)$ $q^{\downarrow}[T] ==> R(X_{j})$ $Sq^{\downarrow}(T) ==> L(X_{j})$ $[T] ==> E$ | Sign is extended in X j but not in T. |

| 6.  | <sup>17</sup> EXX <sub>j</sub> T<br>[F <sub>17</sub> ] = 202 | T x <sub>j</sub>   | $ \begin{bmatrix} X_{j} \end{bmatrix} ==> L(T) $ $ L[T] ==> X_{j} $ $ S(X_{j}) ==> R(T) $ $ [T] ==> E $ | Sign of X is extended into the right half of T.                                                                      |

|-----|--------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 7.  | <sup>21</sup> EXX <sub>j</sub> T<br>[F <sub>21</sub> ] = 230 | T x <sub>j</sub>   | S(X <sub>j</sub> ) ==> L(T) [T] ==> E                                                                   | Same as <sup>21</sup> DFX <sub>j</sub> T.                                                                            |

| 8.  | lexx <sub>j</sub> {T <sub>k</sub> }*                         | T <sub>k</sub>     | $R[T_{k}] ==> X_{j}$ $[X_{j}] ==> R(T_{k})$ $[T_{k}] ==> E$                                             | EXX is indexable if a deferred address is used.                                                                      |

| 9.  | 33 <sub>EXX</sub> , T [F <sub>33</sub> ] = 320               | T x <sub>j</sub>   | $Sql[T] ==> L(X_j)$ $ql[T] ==> R(X_j)$ $R[X_j] ==> ql(T)$ $S(X_j) ==> q3(T)$ $[T] ==> E$                | Note that bit 2.9 is used for sign extension (not 1.9).                                                              |

| 10. | <sup>1</sup> EXX <sub>,</sub> 377720                         | TSS X <sub>j</sub> | R[377720] ==> X <sub>j</sub><br>[X <sub>j</sub> ] ==> R(E)<br>L[377720] ==> L(E)                        | Same as RSX, 377720. (Tog-gle registers must be changed by hand. Note that E is set to what would have gone into T.) |

| α <sub>AUX</sub> τ | $[x_j] + \alpha[T] => x_j$ |

|--------------------|----------------------------|

|--------------------|----------------------------|

AUX forms an 18 bit ring sum in  $x_j$ . There is no overflow detection. All of  $x_j$  is affected. STUV memory is not affected.

Activity and permutation are used. Sign extension applies to the operand taken from STUV memory. If quarters 1 and 2 are active, subword form is immaterial.

If one quarter of the STUV memory operand is inactive (as in standard configuration #3, for example), +0 is used for that quarter.

The E register is set equal to the STUV memory word. (This is "T" except when a deferred address is used. See example 6.)

EXAMPLES: (Standard F Memory - Chart 7-2.)

|             | LED: (Boardard                                    | F Memory - Chart (-2     | /                                                                       |                                                                                                                   |

|-------------|---------------------------------------------------|--------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| NO.         | INSTRUCTION                                       | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>EXPLANATION                                              | COMMENT                                                                                                           |

| 1.          | <sup>1</sup> AUX <sub>j</sub> T                   | T X                      | [X <sub>j</sub> ] + R[T] ==> X <sub>j</sub> [T] ==> E                   | Standard configurations #0, 11, 20, and 30 would do the same $ [F_{11} = 140  [F_{20}] = 200 $ $ [F_{30}] = 600 $ |

| 2.          | <sup>2</sup> AUX <sub>j</sub> T                   | T x <sub>j</sub>         | [X <sub>j</sub> ] + L[T] ==> X <sub>j</sub> [T] ==> E                   | Standard configuration #12 would do the same. $ [F_{12}] = 142 $                                                  |

| 3.          | 13 <sub>AUX</sub> T [F <sub>13</sub> ] = 160      | x <sub>j</sub>           | [X <sub>j</sub> ] + ql[T] <sub>SE</sub> ==> X <sub>j</sub> [T] ==> E    | Standard configuration #33 would do the same (but NOT #3!) (See note on next page.) [F33] = 320                   |

| <u>1</u> 4. | α <sub>AUX,j</sub> Τ [F <sub>α</sub> ] = -220 350 | T X                      | [X <sub>j</sub> ] + q2[T] <sub>SE</sub> ==> X <sub>j</sub><br>[T] ==> E | This has sign extension to the right. (There is no suitable standard configuration.)                              |

| 5. | <sup>21</sup> AUX <sub>j</sub> T                  | T X X J        | [X <sub>j</sub> ] + (+0) ==> X <sub>j</sub> [T] ==> E | Register T is ignored, and X <sub>j</sub> is not changed. Except for E, this instruction is innocuous. |

|----|---------------------------------------------------|----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 6. | $^{1}$ AUX $_{j}$ ${\{}^{\mathrm{T}}_{k}{\}}^{*}$ | T <sub>k</sub> | $ [X_{j}] + R[T_{k}] ==> X_{j} $ $ [T_{k}] ==> E $    | . Same as example 1, but indexed via a deferred address.                                               |

NOTE: E is cleared and then loaded as if by  $\alpha_{LDE}$ . The sum of R[E] and [X] then goes into X (circuitously) and E is set equal to the STUV register used (ie.[T] or  $[T_k]$  if a deferred address was used). X is always set. Note - If either quarter 1 or 2 is not part of an active subword, (as, for example, with standard configuration #3) one operand of the sum is not completely specified and +0 will be used as that part of the operand.

| α <sub>ADX</sub> Τ | $[X_j] + \alpha[T] ==> T$ |

|--------------------|---------------------------|

|--------------------|---------------------------|

ADX forms an 18 bit ring sum usually in STUV memory although only the active quarters are stored. There is no overflow detection. The operands are always 18 bit words - one from X memory the other from STUV memory. A configuration should be chosen such that the word from STUV memory has both quarters active, or is an extended 9 bit subword. If only one quarter is active, the inactive quarter of the operand is set to +0.

Activity and Permutation are used. Only active quarters are stored, but sign extension applies to the operand taken from STUV memory.

The E register is set equal to the STUV memory word used. (This is "T" except when a defer is involved. See example 6.)

EXAMPLES: (Standard F Memory - Chart 7-2)

| NO. | INSTRUCTION                                                  | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>EXPLANATION                 | COMMENT                                                                                                                                  |

|-----|--------------------------------------------------------------|--------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | <sup>1</sup> ADX <sub>j</sub> T                              | T t t x j                | [X <sub>j</sub> ] + R[T] ==> RT [T] ==> E  | Left half of T is not changed. The sum is standard 18 bit ring sum, also called "ones complement sum."                                   |

| 2.  | <sup>2</sup> ADX, T                                          | T x <sub>j</sub>         | [X <sub>j</sub> ] + L[T] ==> LT [T] ==> E  | Right half of T is not changed.                                                                                                          |

| 3.  | <sup>13</sup> ADX <sub>j</sub> T<br>[F <sub>13</sub> ] = 160 | T                        | $[X_j] + ql[T]_{SE} ==> ql(T)$ $[T] ==> E$ | This gives a 9 bit ring sum. Configuration 33 would do the same, #3 would not. See note next page. The subword length should be 18 bits. |

NOTE: In example 3, the <u>9 bit result</u> is an honest 9 bit ring sum <u>only</u> when X; contains an extended 9 bit word. (See RSX, example 4.) ADX cannot be used to add a 9 bit word to an 18 bit word. Use AUX.

| 4. | $\alpha_{ADX_j}$ T $[F_{\alpha}] = 220$                      | T              | [X <sub>j</sub> ] + q2[T] <sub>SE</sub> ==> q2(T) | Essentially the same as example 3 except that the <u>left</u> half of $X_j$ is significant. $[F_{\alpha}]$ illustrated is 220. There is no suitable standard configuration. |

|----|--------------------------------------------------------------|----------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5. | <sup>21</sup> ADX <sub>j</sub> T<br>[F <sub>21</sub> ] = 230 | T              | [T] ==> E                                         | "Nothing" is done here because quarters 1 and 2 are both inactive.                                                                                                          |

| 6. | ladx <sub>j</sub> {T <sub>k</sub> }*                         | T <sub>k</sub> | $[X_j] + R[T_k] ==> RT_k$ $[T_k] ==> E$           | Same as example 1, but indexed via deferred indexing.                                                                                                                       |

NOTE: E is cleared and then loaded as if by  $\alpha$ LDE. The sum of R[E] and [X] then goes into E and an  $\alpha$ STE is performed. Inactive quarters of the STUV memory word therefore remain unchanged. If either quarter 1 or 2 is not part of an active subword (as, for example, with standard configuration #3), one operand of the sum is not fully specified and +0 is used to fill out the operand.

$^{lpha}_{ exttt{SKX}_{ exttt{j}}}$  T

SKX (or REX, or SEX) provides 32 combinations of setting, adding, comparing, skipping, flag raising, and dismissing - all relating to X memory and without changing the AE or the E register. (See examples below.)

F memory is not used. The configuration syllable specifies the desired combination. (Examples 1-8 show the use of bits 4.6, 5, 4 and examples 10-12 illustrate bits 4.8 and 4.7.)

"T", the address syllable, (or the final deferred address) is used as an OPERAND.

#### EXAMPLES:

| LIA AIV | PLES:                           |                                                                         |                                                                      |                                                                                                                                                                                         |

|---------|---------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.     | INSTRUCTION                     | MNEMONIC<br>ABBREVIATION<br>(See Chart 7-3)                             | ABBREVIATED<br>DESCRIPTION                                           | COMMENT                                                                                                                                                                                 |

| 1.      | <sup>O</sup> skx <sub>j</sub> t | SKX <sub>j</sub> T<br>REX <sub>j</sub> T<br>SEX <sub>j</sub> T<br>(Set) | T ==> X <sub>j</sub>                                                 | STUV memory is not used - "T" is the operand, not its location. The brackets []. were left out on purpose.                                                                              |

| 2.      | <sup>1</sup> skx <sub>j</sub> T | (Set negative)                                                          | -T ==> X <sub>j</sub>                                                | "Minus" T - i.e. its ones complement is used to set X <sub>j</sub> .                                                                                                                    |

| 3.      | <sup>2</sup> skx <sub>j</sub> t | INX <sub>j</sub> T<br>(Increase)                                        | [X <sub>j</sub> ] + T ==> X <sub>j</sub>                             | If the sum is zero, it will be -0 (all ones) unless [X] was initially +0.                                                                                                               |

| 4.      | <sup>3</sup> skx <sub>j</sub> T | DEX <sub>j</sub> T<br>(Decrease)                                        | [X <sub>j</sub> ] + (-T) ==>X <sub>j</sub>                           | "-T" is added to $[X_j]$ . Zero is -0. It cannot be +0.                                                                                                                                 |

| 5•      | <sup>4</sup> skx <sub>j</sub> T | SXD <sub>j</sub> T<br>(Skip if X<br>differs.)                           | If [X <sub>j</sub> ] # T Skip - (i.e. #+2 ==> P)                     | Skip if $[X_j]$ differs from T.  Note: $(+0) = (-0)$ and if $[X_j]$ is initially $(+0)$ , it is changed to $(-0)$ .                                                                     |

| 6.      | <sup>5</sup> sĸx <sub>j</sub> T | (Skip if X<br>differs from<br>negative.)                                | If [X <sub>j</sub> ] \( \neq -T\) Skip - (i.e. \( \psi + 2 == > P \) | Skip if $[X_j]$ differs from  -T. Note: $(-0) = (+0)$ and  if $[X_j]$ is initially $(-0)$ ,  it is changed to $+0$ .                                                                    |

| 7.      | <sup>6</sup> skx <sub>;</sub> T | SXL <sub>j</sub> T<br>(Skip if X<br>is less.)                           | If [X <sub>j</sub> ] < T Skip - (i.e. #+2 ==> P)                     | Skip if [X <sub>j</sub> ] is less than T and if [X <sub>j</sub> ] -T does not overflow. (Skip range: T-377777 to T) Note: If [X <sub>j</sub> ]is initially (+0), it is changed to (-0). |

| 8.  | <sup>7</sup> sкх <sub>ј</sub> т  | SXG T<br>(Skip if X<br>is greater.)                 | If [X <sub>j</sub> ] > -T<br>Skip<br>i.e. #+2 ==> P | Skip if [X <sub>j</sub> ] is greater than  -T and if [X <sub>j</sub> ] + T does not overflow. (Skip range: -T to 377777-T) Note: If [X <sub>j</sub> ] is initially (-0), it is changed to (+0). |

|-----|----------------------------------|-----------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.  | $skx_j {\{T_k\}}^*$              | rex <sub>j</sub> {T <sub>k</sub> }*                 | T+[X <sub>k</sub> ] ==> X <sub>j</sub>              | [X <sub>j</sub> ] is set equal to $T_k$ . e.g.<br>a) $SKX_j \{O_k\}^* \equiv set X_j$<br>from $X_k$ .<br>b) $^1SKX_j \{O_j\}^* \equiv Comple-$<br>ment $X_j$ .                                  |

| 10. | <sup>10</sup> skx <sub>j</sub> T | RXF T<br>(Reset and<br>raise flag.)                 | T ==> X <sub>j</sub><br>l ==> Flag <sub>j</sub>     | For $j = 1$ to $37_8$ , RXF is the same as ${}^0$ SKX for there are no flags for these numbers.  Note that flag zero <u>can</u> be raised.                                                      |

| 11. | <sup>20</sup> skx <sub>j</sub> T | RXD, T (Reset and Dismiss.) (See note 3)            | T ==> X <sub>j</sub><br>DISMISS                     | See Chapter 4 for the rami- fications of "DISMISS."  If j = the current sequence number, "T" is nearly imma- terial for the subsequent change of sequence will change X j                       |

| 12. | <sup>30</sup> skx <sub>j</sub> T | RFD, T<br>(Reset, Raise<br>flag, and Dis-<br>miss.) | T ==> X<br>1 ==> Flag<br>DISMISS                    | This is used to change sequence number - often in the form - <sup>30</sup> SKX, #+1. It is ignored if j = current sequence number.                                                              |

Notes: 1. "Skip" means "omit the next instruction." i.e. "Go to #+2."

- 2. The configuration syllable is united with the rest of the instruction. It may be given redundantly. e.g. DEX is the same as  $^3\text{SKX}$  or  $^1\text{INX}$  or  $^3\text{DEX}$ .

- 3. The hold bit cancels DISMISS. (h 20 SKX is the same as SKX alone.)

- 4. RXF cannot be used as a Jump. Index register "j" is indeed set, but it will not be copied into the P register, unless a change of sequence number occurs. (See Chapter 4.)

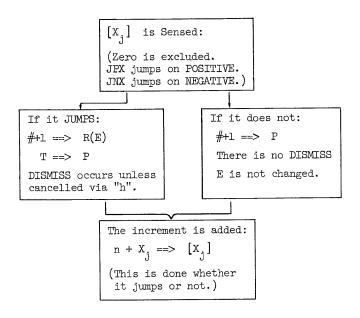

JPX and JNX are "Loop-closing", "Index-sensing" jump instructions. Their operation is as follows:

Note:

- 1. If the sum is zero, it is -0.

- 2. "n" is a signed integer: -17 to  $+17_8$ .

- 3. F Memory is not used.

- $\bar{\mu}$ . A deferred address determines where to jump to, but not if, and the second index register is not modified.

#### EXAMPLES:

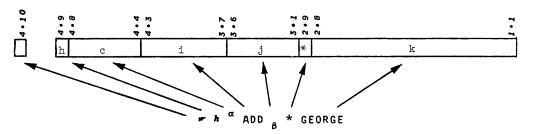

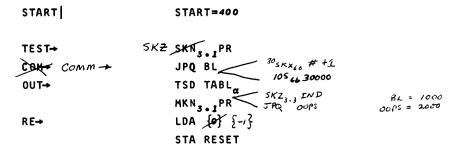

Straight Table Scan (100 register table located at "TABL.")

This program scans the table "backward through the manuscript." (i.e., highest memory location first.) Note:  $X_j$  is initially set to + (n-1).

This program scans "forward through the manuscript." (i.e., lowest memory location first.)

Note: X. is initially set to - (n-l).

2. To scan every nth table register

a) START

$$\rightarrow$$

REX<sub>j</sub> (TL - n) b) START  $\rightarrow$   $^{1}$ REX<sub>j</sub> (TL - n) LDA<sub>j</sub> TABL + TL - n h<sup>-n</sup> JPX<sub>j</sub> #-1

These programs run for  $(\frac{TL}{n})$  iterations if we assume that TL (Table Length) is an integer multiple of n. As written, they scan the first register of each block of n registers. To scan register "i" of each block, the LDA instruction could be written LDA (TABL + i)  $_j$  for example "a" (JPX) and LDA (TABL + i + TL - n)  $_j$  for example "b" (JNX).

#### 3. Interlaced Table Scan

Scope flicker can be reduced by an interlaced table scan. The fact that the change in  $X_j$  is made <u>after</u> the jump decision causes a somewhat peculiar parameter configuration, but the program logic is essentially the same as above. For example, if "C" is the interlace, "TL" is the Table Length, and if "C" is <u>not</u> a factor of "TL," the program below scans the whole table with an interlace of C. (If "C" is a factor of TL, the program degenerates to example 2a.)

If C = 3, and TL = 7, the table is scanned in the following order: 6, 3, 0, 4, 1, 5, 2, 6, 3, 0, etc.

NOTE: 1. "Zero" used as an address (as above) is always +0.

- 2. M4 automatically puts a hold bit on JPX and JNX to cancel the automatic dismiss (see Chapter 4 and Chapter 6).

- 3. The address of a deferred JNX or JPX is completely determined <u>before</u> the index register is changed. Therefore a  $^{-1}$ JPX $_{a|a}$ S would jump to S $_{a}$  as defined by the <u>original</u> contents of X $_{a}$  if it jumps at all.

# 3-2.3 JUMP SKIP CLASS

JMP JPA JNA JOV SKM

SED

# α<sub>JMP</sub> Τ<sub>j</sub>

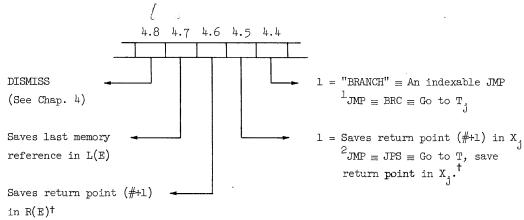

JMP is an unconditional transfer of control. It means go to T (or  $T_j$ ) for the next set of instructions. The configuration syllable " $\alpha$ " does not refer to F memory but is used directly to provide 32 variations of JMP as illustrated below:

EXAMPLES: (See #10.)

|     |                                 |                                               | r · · · · · · · · · · · · · · · · · · · |                                                                                                                                      |

|-----|---------------------------------|-----------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| NO. | INSTRUCTION                     | SUPERNUMERARY<br>MNEMONIC                     | JUMPS<br>TO                             | COMMENT                                                                                                                              |

| 1.  | O <sub>JMP</sub> T <sub>j</sub> | JMP T <sub>.j</sub>                           | T                                       | X <sub>j</sub> is ignored.                                                                                                           |

| 2.  | ljmp T <sub>j</sub>             | BRC T <sub>j</sub><br>(Branch)                | Тj                                      | Indexable Jump ≡ BRANCH                                                                                                              |

| 3-  | <sup>2</sup> JMP I <sub>j</sub> | JPS T.<br>(Jump and Save)                     | T                                       | Jump and save return point $(\#+1)$ in the specified index register $(X_1)$ .                                                        |

| 4.  | 3 <sub>JMP</sub> T <sub>j</sub> | BRS $	extsf{T}_{	extsf{j}}$ (Branch and Save) | тj                                      | Branch and save. X <sub>j</sub> is used to evaluate the jump destination T <sub>j</sub> and is then reset to the return point (#+1). |

| 5.  | ·¼jmp tj                        | -                                             | Т                                       | X <sub>j</sub> is ignored, #+1 is saved in R(E)                                                                                      |

| 6.  | <sup>5</sup> JMP T <sub>j</sub> | <sup>4</sup> BRC T <sub>j</sub>               | Тj                                      | Return point (#+1) is saved in R(E)                                                                                                  |

| 7.  | 6 <sub>JMP</sub> T <sub>j</sub> | <sup>4</sup> JPS T <sub>j</sub>               | Т                                       | Return point ( $\#$ +1) is saved in R(E) and also in $X_j$ .                                                                         |

<sup>†</sup> In M4 terminology, the symbol "#" is an abbreviation for the location of the current instruction. (See Chapter 6.)

| 8.  | 7 <sub>JMP</sub> T <sub>j</sub>  | <sup>4</sup> brs T <sub>j</sub> | Тj | $X_j$ is used to determine the jump destination $T_j$ and is then reset to the return point (#+1). The return point is saved in $R(E)$ as well.            |

|-----|----------------------------------|---------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.  | 10 <sub>JMP</sub> T              | -                               | Т  | The memory location of the last data reference is saved in L(E).  (i.e. the contents of the Q register)                                                    |

| 10. | 1 <sup>1</sup> JMP T             | JPQ T                           | Т  | Jump, save "p" (i.e. #+1) and "q" (location of last data reference).  This is the recommended jump, for the information saved is often of use in checkout. |

| 11. | 15 <sub>JMP</sub> T              | BPQ I                           | Тj | This instruction is the same as JPQ except that the jump destination is indexed.                                                                           |

| 12. | 16 <sub>JMP</sub> T <sub>j</sub> | JES T                           | Т  | Jump, save in E, and in $X_j$ .                                                                                                                            |

| 13. | 20 <sub>JMP</sub> T <sub>j</sub> | JPD T                           | Т  | Jump, Dismiss.                                                                                                                                             |

| 14. | <sup>21</sup> JMP <sup>T</sup> j | BRD T                           | Тj | Branch, Dismiss.                                                                                                                                           |

| 15. | 22 <sub>JMP</sub> T <sub>j</sub> | JDS T                           | Т  | Jump, Dismiss, Save in $X_{\hat{j}}$ .                                                                                                                     |

| 16. | <sup>23</sup> JMP <sup>T</sup> j | BDS T                           | Тj | Branch, Dismiss, Save in X <sub>j</sub> .                                                                                                                  |

Jump and save return point (#+1) in the specified index register (X<sub>j</sub>).

NOTE: A superscript numeral can be used redundantly on supernumerary mnemonics. For example:  $^{16}$ JMP  $\equiv$   $^{16}$ JES  $\equiv$  JES  $\equiv$   $^{2}$ JPQ  $\equiv$   $^{14}$ JPS etc. (M4 "unites" them into the word.)

JPA (46) JNA (47) JOV (45)

JPA - Jump on Positive Accumulator

JNA - Jump on Negative Accumulator

JOV - Jump on Overflow

$$\alpha_{\text{JPA T}_{j}}$$

$\alpha_{\text{JNA T}_{j}}$

$\alpha_{\text{JOV T}_{j}}$

The conditional jumps go to  $T_j$  if the conditions are satisfied by <u>any active subword</u>. Permutation is ignored. The return point (#+1) is saved in E if the jump takes place. The accumulator and overflow flip-flops are not changed. Note that these conditional jumps are indexable.

#### EXAMPLES:

#### #1. A Four-way Switch:

```

JOV OF ** Goes to OF if overflow exists (Z_{\downarrow_{\!\!4}}=1)

JNA Nl ** Goes to Nl if A is negative.

JPA Pl ** Goes to Pl if A is positive.

** Continues if A is zero.

```

#### #2. Overflow:

$^{30}\text{JOV}~\text{T}_{\text{j}}$  is equivalent to  $^{37}\text{JOV}~\text{T}_{\text{j}},$  for both configurations specify the same active subwords. If any of the four overflow flip-flops are set to 1, control will go to  $\text{T}_{\text{j}}.$  The overflow indicators  $(\text{Z}_{\text{l}},\text{Z}_{\text{3}},\text{Z}_{\text{2}},\text{Z}_{\text{1}})$  are not cleared by JOV.

Active subwords use the overflow indicator associated with the sign quarter, e.g.  $Z_2$  is associated with the right half word,  $Z_4$  with the left half word.

#### #3. To Detect Minus Zero in an Index Register:

```

DPX A

ldi DPX A

x** (0,,-0) or (0,,+0) now in A

JPA Tl

x** Goes to Tl if -0 in right half word.

```

(JNX, T or JPX, T will not jump on either + or - zero.)

\*\* Continues if +O in both halves.

# #4. 18 Bit Zeros Again:

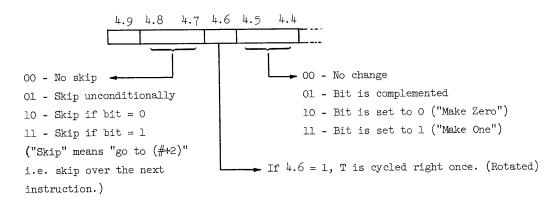

"Skip-on-a-bit" uses a one bit operand. It has 32 variations - some with M4 Supernumerary Mnemonics. The basic variations are as follows:

The bit in question is identified by its quarter number and bit number as diagrammed below:

The meta bit is No. 10 (dec.). (SKM is the <u>only</u> instruction that can affect it.)

The parity bit is No. 11 (dec.).

These can not be changed by SKM.

The parity circuit is No. 12 (dec.).

(Any quarter number will do for the parity and meta bits.)

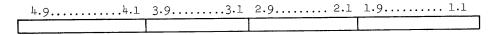

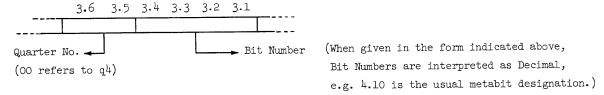

Bits and quarters are numbered from right to left and should be in subscript when used with SKM. (See chapter 6, page 6-7.) The bit designation goes in the "j bits" (3.6 - 3.1), as follows:

SKM is therefore non-indexable except through deferred addressing.

If a non-existent bit is selected, e.g. bit 0.0,1.0,2.0,3.0 for example, Unconditional Skips (SKU) and Rotate (CYR) will still work, but "makes" will do nothing, and conditional skips will not skip.

# SUPERNUMERARY MNEMONICS (See Chart 7-3)

MKC - 1SKM - Make complement

MKZ - <sup>2</sup>SKM - Make zero

MKN -  $^{3}$ SKM - Make one

SKU -  $^{10}$ SKM - Skip unconditionally, (go to #+2)

SUC - 11 SKM - Skip and complement

SUZ - 12 SKM - Skip and make zero

$SUN - {}^{13}SKM - Skip$  and make one

SKZ - <sup>20</sup>SKM - Skip if bit =0

SZC - <sup>21</sup>SKM - Skip on zero and complement

SZZ - <sup>22</sup>SKM - Skip on zero and make zero

$SZN - {}^{23}SKM - Skip on zero and make one$

$SKN - {}^{30}SKM - Skip on one$

$SNC - \frac{31}{SKM} - Skip on one and complement$

SNZ - <sup>32</sup>SKM - Skip on one and make zero

$SNN - ^{33}SKM - Skip on one and make one$

CYR - <sup>1</sup>SKM - Cycle memory once to the right (rotate)

MCR - <sup>5</sup>SKM - Make complement and rotate

MZR - 6SKM - Make zero and rotate

$MNR - {}^{7}SKM - Make one and rotate$

$SNR - \frac{34}{SKM} - Skip$  on one and rotate

SZR - 24SKM - Skip on zero and rotate

SUR - 14SKM - Skip and rotate

NOTE: "Skip" is first, "make" next, and "rotate" last.  $^{4}SZZ \equiv ^{26}SKM \equiv Skip$  on zero, make zero, and then rotate.

# EXAMPLES:

- 1. To copy a bit:

- $\begin{array}{c} \text{SKZ } \mathbb{Q}_{2.3} \\ \text{SUN } \mathbb{T}_{1.1} \\ \text{MKZ } \mathbb{T}_{1.1} \end{array} \qquad \begin{array}{c} \text{Sets bit } \mathbb{T}_{1.1} \\ \text{equal to} \\ \text{bit } \mathbb{Q}_{2.3} \end{array}$

- 2. To clear n metabits starting at T

| α <sub>SED T</sub> j | Only P can<br>be changed. |

|----------------------|---------------------------|

|----------------------|---------------------------|

SED compares all active quarters of E and  $T_j$  according to the given permutation. If any difference exists the next instruction is skipped over. No registers other than P (the central Program Counter) can be changed. (E is <u>not</u> changed.) Subword Form is immaterial.

EXAMPLES: (Standard F Memory - Chart 7-2.)

| NO. | INSTRUCTION                     | DIAGRAM        | COMMENT                                                                                                                                                           |

|-----|---------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | SED T <sub>j</sub>              | T <sub>j</sub> | #+2 -> P if E differs from T j #+1 -> P if they are identical                                                                                                     |

| 2.  | <sup>2</sup> SED T <sub>j</sub> | T <sub>j</sub> | The left half of $T_j$ is compared to the right half of $E$ . ( $^{12}SED$ is identical.) $[F_{12}] = 142$ .                                                      |

| 3.  | <sup>22</sup> sed e             | E E            | The right and left halves of E are compared. <sup>17</sup> SED E, <sup>2</sup> SED E, <sup>12</sup> SED E, or <sup>22</sup> SED E would have an identical result. |

# 3-2.4 SCALE, NORMALIZE, CYCLE

SCA SCB SAB NOA NAB CYA CYB CAB

3-37

$$\begin{bmatrix} \alpha_{\text{SCA T}_{j}} & \alpha_{\text{[A] x 2}}^{\alpha_{\text{[T]}}} \end{bmatrix} ==> A$$

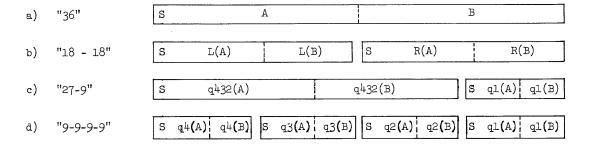

"SCALE" multiplies each active subword by "a power of 2," i.e. by  $2^n$  where n is a signed integer specified in  $T_j$ . Each active subword can be scaled a different amount. The D register is used to count the binary shifts. The details are as follows:

- a) An  $^{\alpha}\!\text{LDD}$  T  $_{j}$  is performed (with permutation and sign extension as called for).

- b) Each active subword (of A or AB) is scaled according to its sign quarter in D, and these sign quarters are left set to -0.

- c) If an overflow exists for an active subword, the proper result is recovered by complementing the sign digit after the first shift, and the indicator is cleared. This rule is used for all operands left (+), right (\_), and zero. Overflow can <u>not</u> affect SCB.

Notice that SCALE amounts to shifting all the bits except the sign left or right and filling the vacant positions with copies of the sign bit (i.e. with +0). SCALE senses overflow and corrects the sign bit if necessary. SCA and SAB always <u>clear</u> the overflow flip-flop - even if bits are lost off the left end. SCALE <u>never</u> sets the overflow flip-flop.

EXAMPLES: (SCB is illustrated to avoid overflow complications.)

| NO. | INSTRUCTION                                | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>DESCRIPTION                                                                                  | COMMENT                                                                                                                |

|-----|--------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1.  | SCB{-4,}                                   | {-4,}                    | [B] $\times 2^{-\frac{1}{4}} ==> B$<br>$-0 ==> q^{\frac{1}{4}}(D)$<br>$q_{3,2,1}[T_{j}] ==> q_{321}(D)$     | {-4,} is a M4 convention for A register with -4 in quarter 4. See Chapter 6, page 6-7 and 6-10.                        |

| 2.  | <sup>30</sup> SCB {N}<br>N = 2775003000(8) | [N]                      | $q4[B] \times 2^2 ==> q4(B)$<br>$q3[B] \times 2^{-2} ==> q3(B)$<br>$q2[B] \times 2^3 ==> q2(B)$<br>-0 ==> D | Quarter 1 of B is not changed. The sign bits are never changed. Bits may be lost off either end without any alarm.     |

| 3•  | <sup>2</sup> SCB {N}<br>N = 2775003000(8)  | D {N}                    | $R[B] \times 2^2 ==> R(B)$<br>-0 ==> q2(D)<br>775 ==> q1(D)                                                 | The <u>left</u> halves of B and D are not changed.  Note that q4 of {N} specifies the argument of the scale operation. |

Note: Scale can of course be indexed - e.g. SCA  $T_j$  where the argument comes from  $T_j$ . It is more common programming practice to use an RC word - e.g. SCA{-1,}.

### 4. Overflow: (SCA and SAB)

a) To "recover an overflow":

LDA {200 000 000 000 000}  $\begin{cases} \text{**Acc. will now be 400 000 000 000 (a negative number), and } Z_{1} \text{ (overflow bit $\#4$) will be "1".} \\ \text{SCA {-3,}} \end{cases}$   $\begin{cases} \text{**-3,} \equiv 774 \text{ 000 000 000. After the scale,} \\ \text{Acc. will be 040 000 000 000 and } Z_{1} \text{ will be "0".} \\ Z_{3}, Z_{2}, Z_{1} \text{ are not sensed nor changed.} \end{cases}$  (Any negative argument will suffice.)

b) Only active subwords are processed:

Note that  $Z_1, Z_2, Z_1$  are overflow indicators. They tell whether overflow has occurred. An overflow resulting from negative numbers (as in q2 above) is not treated any differently.

## 5. Subword forms for the AB register:

Note that all of B is part of the subword. There is only one sign bit in an AB subword.

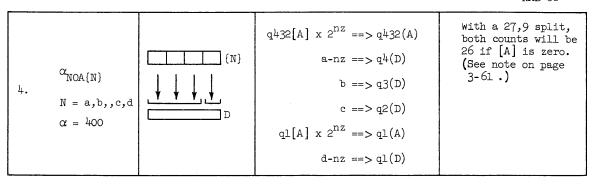

$$\alpha_{\text{NOA T}_{j}} \qquad \alpha_{\text{[A] x 2}^{\text{nz}}} ==> A$$

$$\alpha_{\text{[T}_{j}]} - \text{nz} ==> \text{Sq(D)}$$

NORMALIZE scales just enough to remove leading zeros or to "recover" from OVERFLOW. It clears the active overflow indicators. The number of leading zeros (nz) is subtracted from the argument from  $T_j$  ( $^{\alpha}[T_j]$ ) and this difference is left in the Sign Quarter of D. If an overflow condition exists at the start, "nz" is -1, the scale is one place to the right, and the sign is complemented - just as for SCA or SAB. If nz is zero, it is +0. (See Note 4 also.)

NOA and NAB start with an  $^{\alpha}$ LDD T<sub>j</sub>. "nz" is subtracted from the sign quarter(s) and the rest of D is not changed. The E register becomes a copy of T<sub>j</sub>.

EXAMPLES:  $^{\dagger\dagger}$  (Assume that  $\underline{\text{NO OVERFLOW}}$  exists.)

| No. | INSTRUCTION                                                 | DIAGRAM | ABBREVIATED<br>DESCRIPTION                                                                                                | COMMENTS                                                                                                                                                                   |

|-----|-------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | NOA{O}                                                      | [+0}    | [A] x 2 <sup>nz</sup> ==> A<br>-nz ==> q4(D)<br>+0 ==> q3,2,1(D)                                                          | "nz" is the number of leading "zeros" in the original contents of A.  ("Zeros" can be positive zeros or negative zeros.)                                                   |

| 2.  | <sup>2</sup> noa{o}                                         | [+0}    | R[A] x 2 <sup>nz</sup> ==> R(A) -nz ==> q2(D) +0 ==> q1(D)                                                                | The left halves of A and D are not changed. "nz" is the number of "zero" in the original contents of the right half of A. Note that the result in D is a nine bit numeral. |

| 3.  | 17 <sub>NOA</sub> (N) N = a,b,,c,d [F <sub>17</sub> ] = 202 | D (N)   | $R[A] \times 2^{ZR} ==> R(A)$ $a-ZR ==> q2(D)$ $b ==> q1(D)$ $L[A] \times 2^{ZL} ==> L(A)$ $c-ZL ==> q4(D)$ $d ==> q3(D)$ | "ZR" and "ZL" are the leading zeros of the right and left 18 bit words of A. {N} is a register containing a,b,c, and d in quarters 4,3,2, and 1.                           |

<sup>††</sup> Brackets{} are used in the TX-2 M4 Assembly Program to indicate "Register Containing". See Chapter 6, page 6-10.

### 5 - A sample program → Evaluate V = xyz

This product could have 105 significant bits (3 word lengths). One must resort to programmed arithmetic to get them all, but normalize can be used to get the 34 most significant bits. Consider the programs below.

#### Without Normalize:

| LDA X                | LDA | Х   |

|----------------------|-----|-----|

| MUL Y                | MUL | Y   |

| MUL Z                | NAB | {0} |

|                      | STD | T   |

| uts the 35 left bits | MUL | Z   |

| product in A and     | SAB | T   |

This program puts the 35 left bits of the 105 bit product in A and essentially worthless numerals in B. The answer in A may be too small by 1 (in the 35th place).

With normalize, the product is given in AB, to 35+nz places from the sign. (It may low by 1 in the (35+nz)th place.) "nz", the number of zeros, is in T (in negative form). nz could be as much as 69 so the last SAB may not be desired. For example, if the NAB instruction above were replaced with NAB{34.,} the answer in AB can be considered a 71 bit integer.

With Normalize:

NOTE: 1. NOA and NAB leave E set the same as the memory register used.

- 2. If overflow exists, "nz" is -l so  $[T_{j}]+l ==> Sq(D)$ .

- 3. NAB is essentially the same instruction using the double length word (AB) instead. (See page 3-39 "Subword forms for the AB register".)

- 4. Normalize is an arithmetic instruction. The sign bit is not counted. "Leading zeros" will, of course, be plus or minus zeros i.e., the same as the sign.

$\alpha_{ ext{CYA} \ ext{T}_{ ext{j}}}$

CYCLE logically falls in a class with LDA and STA, for it is most easily considered as a bit shifting instruction and the sign bit has no special significance. Bits shifted off one end are inserted at the other. None are lost. However, since the practical details of its use are so similar to SCALE, it is usually grouped with SCALE and NORMALIZE. The use of the memory word is the same as SCALE.

- a.) An  $\alpha_{\text{LDD T}_{j}}$  is the first step.

- b.) Each active subword is "cycled" or "rotated" according to its Sign Quarter in D and the sign quarter is left at -0. For cycle, the active subword has its ends connected and can be considered as a ring of bits. If the number of places equals the subword length, the instruction does not change the subword. You can therefore arrive at any new position by cycling either way the short way takes less computer time. The sign bit is handled no differently than the others and no bits are lost.

- c.) Overflow is ignored.

- d.) The E register becomes a copy of the memory register used.

EXAMPLES: Assume [A] = 123 456 765 432(8) at the start

| NO. | INSTRUCTION                     | CONFIGURATION<br>DIAGRAM | ABBREVIATED<br>DESCRITPION                                       | COMMENT                                                                                     |

|-----|---------------------------------|--------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1.  | CYA{+l,}                        | (+1,)                    | 247 135 753 064 ==> A<br>-0 ==> q4(D)<br>+0 ==> q3,2,1(D)        | One 36 bit ring cycled once to the left.                                                    |

| 2.  | 30 <sub>CYA{N}</sub> N=1,1,,1,1 | [N]                      | 246 ==> q4(A)<br>135 ==> q3(A)<br>753 ==> q2(A)<br>065 ==> q1(A) | The four quarters are cycled separately i.e. four nine-bit rings, each one bit to the left. |

Assume [A] = 123 456 765 432(8) at the start.

| 3.         | <sup>2</sup> CYA{-3, }     | [-3, ] | 276 543 ==> R(A)<br>-0 ==> R(D)                                                                                | The left halves of A and D are not changed. The right half of A (a ring of 18 bits) is cycled 3 places to the right. i.e. one octal place.) |

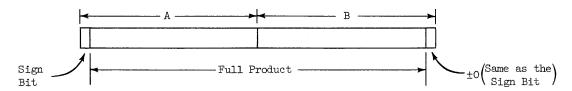

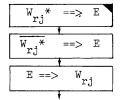

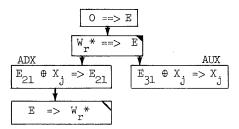

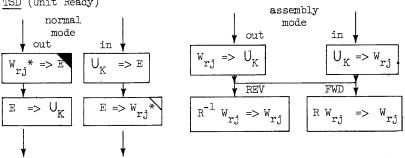

|------------|----------------------------|--------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|