# Supellam<sup>™</sup> 16k-A User's Manual

### TABLE OF CONTENTS

| Introduction                             | 1  |

|------------------------------------------|----|

| Operating Instructions                   | 2  |

| Memory Diagnostic                        | 5  |

| Parts List                               | 10 |

| Assembly Instructions                    | 11 |

| Power Supply/Voltage Regulator Check Out | 14 |

| Theory of Operation                      | 16 |

| Warranty                                 | 18 |

| Schematics                               | 19 |

Copyright 1978 G. Morrow

# SuperRam<sup>TM</sup> 16K-A

### INTRODUCTION

The SuperRam 16K-A utilizes the MM5257/4044 4096 x 1 static memory I.C. As with other memories from Thinker Toys, all data and address lines are fully buffered for enhanced data integrity. The board is designed to give the user maximum flexibility by splitting the memory into four independent 4K blocks which can be separately write protected. Each 4K block may be independently addressed at any 4K boundary in memory.

The PHANTOM line can be conditionally enabled to turn off the board during power-up procedures. The board uses DIP switches located at the top of the board so that address selection is easy to accomplish. Finally, SIP (single-in-line package) resistor networks have been utilized throughout the board to keep the parts count down. A lower parts count means higher reliability and quicker assembly for the end user.

We at Thinker Toys have tried to make this manual clear and accurate. Comments on improving this document are welcome. Thank you for purchasing the SuperRam 16K-A memory. We hope it will serve your needs.

### OPERATING INSTRUCTIONS

NOTE: TURN OFF THE POWER IN YOUR COMPUTER BEFORE PLUGGING IN OR REMOVING THE SUPERRAM! YOU MAY DAMAGE ONE OR MORE OF THE RESIDENT CIRCUIT BOARDS IF YOU DO NOT FOLLOW THIS PROCEDURE.

### <u>ADDRESSING</u>

At the top of the circuit board, there are three eight-position DIP switches. The left two determine the addressing of the memory. The DIP switch on the left is for write protection and PHANTOM enabling. The two switches on the left are illustrated below:

|   | ADDRESS<br>BANK A |     |     |     | ADDRESS<br>BANK B |     |     | ADDRESS<br>BANK C |     |     | ADDRESS<br>BANK D |     |     |     |     |     |

|---|-------------------|-----|-----|-----|-------------------|-----|-----|-------------------|-----|-----|-------------------|-----|-----|-----|-----|-----|

| إ | Ø                 | Ø   | l Ø | Ø   | Ø                 | Ø   | Ø   | Ø                 | Ø   | Ø   | Ø                 | Ø   | Ø   | Ø   | Ø   | Ø   |

|   |                   |     |     |     |                   |     |     |                   |     |     |                   |     |     |     |     |     |

| - | 1                 | 1   | 1   | 1   | 1                 | 1   | 1   | 1                 | 1   | 1   | 1                 | 1   | 1   | 1   | 1   | 1   |

|   | A15               | A14 | A13 | A12 | A15               | A14 | A13 | A12               | A15 | A14 | A13               | A12 | A15 | A14 | A13 | A12 |

In the 64K bytes of address space of the S-100 bus, there are sixteen 4K blocks. The positions of the four switches associated with blocks A, B, C and D as illustrated above determines which 4K segment of address space a particular block will occupy. For example, if the switches associated with block A are all ON (up), block A will occupy locations 000:000 through 17:377 octal or 0000 through 0FFF hex. If the switches associated with block B are ON (15 through 13) and 0FF (12), block B will occupy memory locations 20:000 through 37:377 octal or 1000 through 1FFF hex.

Note that in the illustration above there is an address bit above each switch. Block positions are formed by making a hex digit pattern with each group of four switches. The high order bit of this hex digit is to the left as is the high order address bit. These hex digits represent the starting address of the block associated with the switches (when followed by three hex zeros). Following is a table of switch positions and corresponding starting addresses

|      | rting<br>dress | А    | А    | А    | А    | Corre     | sponding<br>Binary |  |

|------|----------------|------|------|------|------|-----------|--------------------|--|

| Hex  | Octal          | 15   | 14   | 13   | 12   | Hex Digit | Number             |  |

| 0000 | 000:000        | up   | up   | up   | up   | 0         | 0000               |  |

| 1000 | 020:000        | up   | up   | up   | down | 1         | 0001               |  |

| 2000 | 040:000        | up   | up   | down | up   | . 2       | 0010               |  |

| 3000 | 060:000        | up   | up   | down | down | 3         | 0011               |  |

| 4000 | 100:000        | up   | down | up   | up   | 4         | 0100               |  |

| 5000 | 120:000        | up   | down | up   | down | 5         | 0101               |  |

| 6000 | 140:000        | up   | down | down | up   | 6         | 0110               |  |

| 7000 | 160:000        | up   | down | down | down | 7         | 0111               |  |

| 8000 | 200:000        | down | up   | up   | up   | 8         | 1000               |  |

| 9000 | 220:000        | down | up   | up   | down | 9         | 1001               |  |

| A000 | 240:000        | down | up   | down | up   | А         | 1010               |  |

| B000 | 260:000        | down | up   | down | down | В         | 1011               |  |

| C000 | 300:000        | down | down | up   | up   | С         | 1100               |  |

| D000 | 320:000        | down | down | up   | down | D         | 1101               |  |

| E000 | 340:000        | down | down | down | up   | E         | 1110               |  |

| F000 | 360:000        | down | down | down | down | F         | 1111               |  |

Note: up = on; down = off.

### WRITE PROTECTION LOGIC

|        | BANK A        | BANK B        | BANK C        | BANK D        |     |     |     |                 |

|--------|---------------|---------------|---------------|---------------|-----|-----|-----|-----------------|

|        | WRITE<br>ENBL | WRITE<br>ENBL | WRITE<br>ENBL | WRITE<br>ENBL | N/C | N/C | N/C | PHANTOM<br>ENBL |

| ON OFF |               |               |               |               |     |     |     |                 |

|        | WRITE<br>PROT | WRITE<br>PROT | WRITE<br>PROT | WRITE<br>PROT |     |     |     | PHANTOM<br>DSBL |

The left most four switches of the DIP switch on the far right (DIP switch array #3) are devoted to write protection for the four blocks A, B, C and D. If the switch associated with a particular block is OFF (down), that block of memory is write protected. For example, if the left most switch above is OFF, it is impossible for the CPU, i.e., the 8080 processor, to alter any of the 4096 memory locations spanned by block A. The switches have been arranged in the same order as the address selection switches (A to the left, D to the right) to help minimize errors when these switches are manipulated.

### PHANTOM ENABLE

The right most switch of DIP switch #3 is used to enable or disable the PHANTOM line on the S-100 bus (pin #67). The PHANTOM signal is used to disable normal memory during power-up situations or other emergencies. Typically, special purpose ROM is enabled on the bus during the time the PHANTOM signal is active and so normal memory is disabled. If your mainframe has logic which utilizes the PHANTOM line as described above, the PHANTOM switch should be up (ON). If the PHANTOM line is not used in your system or used for some other purpose, the switch should be down (OFF).

### MEMORY DIAGNOSTIC

The memory test described below was designed by Phil Meads of William Brobeck Associates to exercise the most sensitive circuitry of the memory chips -- the address buffers. The test starts from the middle and works its way outward alternately to the top and bottom of memory. This type of test inverts the address lines more often than sequential ones. This continual inversion process punishes and eventually breaks down weak or faulty address buffers in the device.

### USING THE TEST

The test itself  $\underline{\text{must}}$  be placed in an area which is different than the location of the board(s) to be tested. The test starts on a page boundary to make the task of relocating the binary code easier.

There are two parameters in the test to be set by the user:

- (1) The number of 4K blocks to be tested -- keep in mind that there are four 4K blocks per board. This constant is called BLKCNT and is located at the eleventh byte of the test.

- (2) The starting <u>page</u> number of the <u>lowest</u> 4K block to be tested is called PAGENO and is located at the ninth byte of the test.

When testing more than one 4K block of memory, be sure that they occupy contiguous memory.

The page number of the position of the test itself must be entered wherever a  $(YYY)_8$  or  $(YY)_{16}$  occurs in the test listing. This is necessary because JMP and CALL need both the page number and the location within the page to execute correctly.

The only other thing to remember when loading the test is that it  $\underline{\text{must}}$  be placed at the starting address of a page.

Start the test at the first instruction. Once started, the test will run continuously unless an error is detected. If the test encounters an error, all the data pertinent to this error is stored in the last ten locations of the test. After storing this data, the test comes to a dynamic halt at the label STALL. The test may be restarted by stopping the computer and restarting it at the POP PSW instruction following JMP STALL. The user may also restart the test from the beginning. If errors indicate the board is malfunctioning, return it as soon as possible for service.

# MEMORY TEST PROGRAM FOR 4K NMOS RAMS

# Octa1

| ΥΥΥ | 000 061 175 003 001 000 006 305 007 006 100 011 016 004 013 041 377 016 170 017 204 020 147 021 345 022 315 114 025 167 026 315 123 031 315 114 034 167 035 315 134 040 302 022 043 341 | 000<br>007<br>YYY<br>YYY<br>YYY | NEWCYL<br>LOOP | MVI<br>MVI                                                                | SP,STACK B,0 B B,PAGENO C,BLKCNT H,7:377Q A,B H H,A H TWORD M,A COMP TWORD M,A INCR WRITE H | INITIALIZE CYCLE COUNT UPDATE CYCLE COUNT STARTING ADDR OF TEST MEM # OF 4K BLOCKS TO TEST HALF SIZE OF MEMORY -1  CALCULATE MIDDLE OF CURRENT BLOCK |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| ΥΥΥ | 044 315 114<br>047 256<br>050 304 145<br>053 315 123<br>056 315 114<br>061 256<br>062 304 145<br>065 315 134<br>070 302 044                                                             | YYY<br>YYY<br>YYY<br>YYY<br>YYY | READ           | CALL<br>XRA<br>CNZ<br>CALL<br>CALL<br>XRA<br>CNZ<br>CALL<br>JNZ           | TWORD M ERROR COMP TWORD M ERROR INCR READ                                                  | GET TEST WORD COMPARE  COMPLEMENT ADDRESS GET TEST WORD COMPARE  COMPLEMENT & DECREMENT ADDRESS                                                      |

| YYY | 073 076 020<br>075 200<br>076 107<br>077 015<br>100 302 013<br>103 173<br>104 306 207<br>106 137<br>107 301<br>110 003<br>111 303 006                                                   |                                 |                | MVI<br>ADD<br>MOV<br>DCR<br>JNZ<br>MOV<br>ADI<br>MOV<br>POP<br>INX<br>JMP | A,20Q<br>B<br>B,A<br>C<br>LOOP<br>A,E<br>135<br>E,A<br>B<br>B                               | ADVANCE THE BLOCK DECREMENT BLOCK COUNT  CALCULATE NEW BASE FOR TEST WORD  INCREMENT CYCLE COUNT                                                     |

|     | 114 175<br>115 007<br>116 207<br>117 204<br>120 203<br>121 127<br>122 311                                                                                                               |                                 | TWORD          | MOV<br>RLC<br>ADD<br>ADD<br>ADD<br>MOV<br>RET                             | A,L<br>A<br>H<br>E<br>D,A                                                                   | GET LOWER BYTE OF ADDRESS<br>ROTATE<br>SHIFT<br>ADD HIGHER BYTE OF ADDR<br>ADD BASE<br>SAVE TEST WORD                                                |

| ΥΥΥ | 123 174<br>124 356 017<br>126 147<br>127 175<br>130 356 377<br>132 157<br>133 311                                          | COMP  | MOV<br>XRI<br>MOV<br>MOV<br>XRI<br>MOV<br>RET  | A,H<br>17Q<br>H,A<br>A,L<br>377Q<br>L,A | COMPLEMENT THE UPPER BYTE ADDRESS WITH RESPECT TO MEM SIZE COMPLEMENT THE LOWER BYTE OF THE ADDRESS                                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ΥΥΥ | 134 315 123 YYY<br>137 053<br>140 300<br>141 170<br>142 075<br>143 274<br>144 311                                          | INCR  | CALL<br>DCX<br>RNZ<br>MOV<br>DCR<br>CMP<br>RET | COMP<br>H<br>A,B<br>A                   | RESTORE ADDR TO NORMAL SIZE DECREMENT TEST IF LOWER BYTE ZERO TEST UPPER BYTE EQUAL TO BLOCK BOUNDARY                                                                        |

| ΥΥΥ | 145 345<br>146 305<br>147 325<br>150 365<br>151 303 151 YYY<br>154 361<br>155 321<br>156 301<br>157 341<br>160 311         | ERROR | PUSH<br>PUSH<br>PUSH                           | D<br>PSW                                | SAVE ERROR ADDRESS SAVE CURRENT BLOCK SAVE TEST WORD SAVE ERROR BITS DYNAMIC HALT RESTORE THE STATE OF THE CPU                                                               |

| ΥΥΥ | 161 000<br>162 000<br>163 000<br>164 000<br>165 000<br>166 000<br>167 000 000<br>171 000 000<br>173 000 000<br>175 000 000 | TABLE | DB DB DB DB DB DB DW DW DW DW                  | 0<br>0<br>0<br>0<br>0<br>0<br>0         | FLAGS ACC - ONES ARE ERROR BITS E - CURRENT RANDOM OFFSET D - CURRENT TEST WORD C - CURRENT BLOCK COUNT B - CURRENT BLOCK PAGE HL - ERROR ADDRESS RETURN ADDRESS CYCLE COUNT |

# MEMORY TEST PROGRAM FOR 4K NMOS RAMS

Hex

| YY | 00<br>03<br>06<br>07<br>09<br>0B<br>0E<br>0F<br>10<br>11<br>12<br>15<br>16<br>19<br>1C<br>1D<br>20<br>23 | 31 7D YY 01 00 00 C5 06 40 0E 04 21 FF 07 78 84 67 E5 CD 4C YY 77 CD 53 YY CD 4C YY 77 CD 5C YY CD 5C YY C2 12 YY E1 | START NEWCYL LOOP WRITE | LXI LXI PUSH MVI MVI LXI MOV ADD MOV PUSH CALL MOV CALL CALL MOV CALL JNZ POP | SP,STACK B,O B B,PAGENO C,BLKCNT H,7:377Q A,B H H,A H TWORD M,A COMP TWORD M,A INCR WRITE H |

|----|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| ΥΥ | 24<br>27<br>28<br>2B<br>2E<br>31<br>32<br>35<br>38                                                       | CD 4C YY AE C4 65 YY CD 53 YY CD 4C YY AE C4 65 YY CD 5C YY CD 5C YY C2 24 YY                                        | READ                    | CALL<br>XRA<br>CNZ<br>CALL<br>CALL<br>XRA<br>CNZ<br>CALL<br>JNZ               | TWORD<br>M<br>ERROR<br>COMP<br>TWORD<br>M<br>ERROR<br>INCR<br>READ                          |

| ΥΥ | 3B<br>3D<br>3E<br>3F<br>40<br>43<br>44<br>46<br>47<br>48                                                 | 3E 10<br>80<br>47<br>0D<br>C2 0B YY<br>7B<br>C6 87<br>5F<br>C1<br>03<br>C3 06 YY                                     |                         | MVI<br>ADD<br>MOV<br>DCR<br>JNZ<br>MOV<br>ADI<br>MOV<br>POP<br>INX<br>JMP     | A,20Q<br>B<br>B,A<br>C<br>LOOP<br>A,E<br>135<br>E,A<br>B                                    |

| ΥΥ | 4C<br>4D<br>4E<br>4F<br>50<br>51<br>52                                                                   | 7D<br>07<br>87<br>84<br>83<br>57<br>C9                                                                               | TWORD                   | MOV<br>RLC<br>ADD<br>ADD<br>ADD<br>MOV<br>RET                                 | A,L<br>A<br>H<br>E<br>D,A                                                                   |

| ΥΥ | 53<br>54<br>56<br>57<br>58<br>5A<br>5B                   | 7C<br>EE OF<br>67<br>7D<br>EE FF<br>6F<br>C9                         | COMP           | MOV<br>XRI<br>MOV<br>MOV<br>XRI<br>MOV<br>RET                  | A,H<br>17Q<br>H,A<br>A,L<br>377Q<br>L,A      |                                                                                                                                                                              |

|----|----------------------------------------------------------|----------------------------------------------------------------------|----------------|----------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ΥΥ | 5C<br>5F<br>60<br>61<br>62<br>63<br>64                   | CD 53 YY<br>2B<br>CO<br>78<br>3D<br>BC<br>C9                         | INCR           | CALL<br>DCX<br>RNZ<br>MOV<br>DCR<br>CMP<br>RET                 | COMP<br>H<br>A,B<br>A<br>H                   |                                                                                                                                                                              |

| YY | 65<br>66<br>67<br>68<br>69<br>6C<br>6D<br>6E<br>6F<br>70 | E5<br>C5<br>D5<br>F5<br>C3 69 YY<br>F1<br>D1<br>C1<br>E1             | ERROR<br>STALL | PUSH<br>PUSH<br>PUSH<br>JMP<br>POP<br>POP<br>POP<br>POP<br>RET | H<br>B<br>D<br>PSW<br>STALL<br>PSW<br>D<br>B |                                                                                                                                                                              |

| ΥΥ | 71<br>72<br>73<br>74<br>75<br>76<br>77<br>79<br>7B<br>7D | 00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00 | TABLE          | DB DB DB DB DB DB DW DW DW DW                                  | 0<br>0<br>0<br>0<br>0<br>0<br>0              | FLAGS ACC - ONES ARE ERROR BITS E - CURRENT RANDOM OFFSET D - CURRENT TEST WORD C - BLOCKS LEFT TO TEST B - CURRENT BLOCK PAGE HL - ERROR ADDRESS RETURN ADDRESS CYCLE COUNT |

### PARTS LIST

- O 1 8" x 10" photo

- O 1 5" x 10" printed circuit board

- O 3 SIP resistor packs

- O 21 by-pass capacitors\*

- O 5 39  $\mu$ fd tantalum capacitors

- O 10 14-pin low profile sockets

- O 3 16-pin low profile sockets

- O 32 18-pin low profile sockets

- O 3 8-position DIP switches

- O 4 heat sinks

- O 4 6-32 x 5/16 machine screws

- O 4 6-32 hex nuts

- O 1 74LS00/74LS132 quad 2 input NAND gate

- O 2 74LS04/74LS14 hex inverters

- O 1 74LS20 dual 4 input NAND gate

- O 1 74LSO2 quad 2-input NOR gate

- O 1 74LS32 quad 2 input OR gate

- O 4 74LS266 quad EXCLUSIVE NOR gates

- O 3 74LS367/74LS368 hex tristate\*\* buffer

- O 32 MM5257/4044 4096 x 1 static RAMS

- O 4 7805/LM340.5 5 volt regulators

<sup>\*</sup>by-pass capacitors will vary in value between .01  $\mu fd$  and .1  $\mu fd$ .

<sup>\*\*</sup>tristate is a trademark of National Semiconductor.

## ASSEMBLY INSTRUCTIONS

DO NOT INSTALL OR SOLDER ANY PARTS UNTIL YOU HAVE READ THE INSTRUCTIONS AND UNDERSTAND THEM!

CAUTION -- DO NOT SOLDER OR CLIP COMPONENT LEADS WITHOUT USING SAFETY GLASSES!

### **INSPECTION**

Use the Parts List to make sure that there are no missing items in your kit. Please notify us of any shortages. Be sure to check for missing parts before you start assembling.

### SOCKETS

A socket is furnished for <u>every</u> integrated circuit. It is important that you use the sockets; otherwise, a defective part will be extremely difficult to replace.

NO REPAIR OR SERVICE WILL BE PERFORMED ON A CIRCUIT BOARD WHICH HAS HAD INTEGRATED CIRCUITS SOLDERED TO IT.

### PARTS ORIENTATION

In all references throughout the instructions, the convention used is that the gold edge connector is the <u>bottom</u> of the board. Orientation identification is molded into the plastic of the sockets either with numbers or in the manner illustrated below.

This orientation or an embossed "1" identifies where pin #1 of the integrated circuit is to be positioned when inserted into the socket. The sockets should be inserted in the board so that the orientation mark is in the  $\underline{lower}$  left hand corner.

The tantalum capacitors should be oriented so that the red strip or positive mark is to the left when the part is inserted in the board. The three DIP switches at the top of the board should be positioned so that switch #1 is to the left.

The SIP resistor packs have an orientation dot at one end. The pin associated with this dot is the common point of the nine resistors in this package and must be to the left when the parts are soldered to the board.

### SOLDERING AND SOLDER IRONS

The most desirable soldering iron for complex electronic kits is a constant temperature soldering iron with an element regulated at  $650^{\rm O}$  F. The tip should be fine so that it can be brought in intimate contact with the pads of the circuit board. Both Unger and Weller have excellent products which fit the above requirements.

There are three important soldering requirements for building this kit:

- 1. Do not use an iron that is too cold (less than  $600^{\circ}$  F) or too hot (more than  $750^{\circ}$ ).

- 2. Do not apply the iron to a pad for extended periods.

- 3. Do not apply excessive amounts of solder.

The proper procedure for soldering components to the circuit board is as follows:

- 1. Bring the iron in contact with both the component lead and the pad.

- 2. Apply a <u>small</u> amount of solder at the point where the iron, component lead, and pad <u>all</u> make contact.

- 3. After the initial application of solder has been accomplished with the solder flowing to the pad and component lead, the heat of the iron will have transferred to <u>both</u> the pad and the lead. Apply a small amount of additional solder to cover the joint between the pad and the lead. DO NOT PILE SOLDER ON THE JOINT! EXCESSIVE HEAT AND SOLDER CAUSE PADS AND LEADS TO LIFT FROM THE CIRCUIT BOARD. EXCESSIVE SOLDER IS THE PRIMARY CAUSE FOR BOARD SHORTS AND BRIDGED CONNECTIONS.

### PARTS INSTALLATION

| Inst | all:                                                                                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Sockets 1A-8A, 1B-8B, 1C-8C, 1D-8D. 18-pin low profile. Pin #1 to the lower left.                                                                                                      |

|      | Sockets 1E-5E, 1F-5F. 14-pin low profile. Pin #1 to the lower left.                                                                                                                    |

|      | Sockets 6E-8E. 16-pin low profile. Pin #1 to the lower left.                                                                                                                           |

|      | C1-C5 39 $\mu fd$ tantalum capacitors. Orientation mark to the left. Bend leads .6" wide before insertion.                                                                             |

|      | SIP resistor packs. RN1, RN2, and RN3. Orientation dot to the left.                                                                                                                    |

|      | By-pass capacitors (21 each) as shown by the silk screen legend on the circuit board.                                                                                                  |

|      | DIP switches 1, 2 and 3. Switch #1 of each switch array should be to the left when inserted.                                                                                           |

|      | 7805/LM340.5 5 volt regulators (4 each) by bending the leads, inserting and hand tightening the nut and bolt through the circuit board, heat sink and regulator, in that order. Solder |

For parts placement, please see the silk screen legend on the printed circuit board and the  $8"\ x\ 10"$  photograph.

the leads. If heat sink grease is available, apply a thin film between the board and heat sink and between the heat sink and the regulator before inserting the parts and soldering the

leads. Finally, tighten the nut firmly.

### POWER SUPPLY/VOLTAGE REGULATOR CHECK OUT

Voltage requirements: (reference to ground - pins 50 and 100)

Pins 1 and 51: not less than 7 volts approx. 1700 ma not more than 10 volts

Before installing any of the integrated circuits, apply power to pins 1 and 51 as specified above. Power can come from external supplies or from a host S-100 mainframe. After applying power, perform the following measurements:

| (1) | 1F pin | 14 | + | 5 | volts |

|-----|--------|----|---|---|-------|

| (2) | 2F pin | 14 | + | 5 | volts |

| (3) | 3F pin | 14 | + | 5 | volts |

| (4) | 4F pin | 14 | + | 5 | volts |

| (5) | 5F pin | 14 | + | 5 | volts |

| (6) | 6E pin | 16 | + | 5 | volts |

| (7) | 7E pin | 16 | + | 5 | volts |

| (8) | 8E pin | 16 | + | 5 | volts |

If the voltage at any of the check points differs by more than 5% if the required value, return the board for service.

### POWER-UP CHECK OUT

Install the integrated circuits. Be very careful not to bend pins of the ICs under the package. Frequently, a pin which is bent under appears to be inserted in the socket.

BENT PINS ARE THE MOST COMMON REASON FOR A MALFUNCTIONING BOARD!

After the parts have been installed, repeat the eight voltage measurements specified above. If the test points differ from the required values, return the board for service. UNDER NO CIRCUMSTANCES SHOULD THE SOCKETS BE REMOVED FROM THE BOARD. Such abuse will void the warranty under which repair and service is performed.

### SYSTEM CHECK OUT

Select four different bank positions for the four blocks of memory on the board. Make sure that the write protect/enable switches are all on. Select the position of the PHANTOM switch that is appropriate for your system. Next with power OFF, plug the board into an empty slot of main frame and apply power. Examine several locations in each of the four different blocks and verify that all zeros and all ones can be written into and read from each of the four blocks.

Finally, a memory test (either the one included in this manual or one of your choosing) should be run for several hours over the entire 16K. After completion of these steps, the memory is ready for use in your mainframe.

### THEORY OF OPERATION

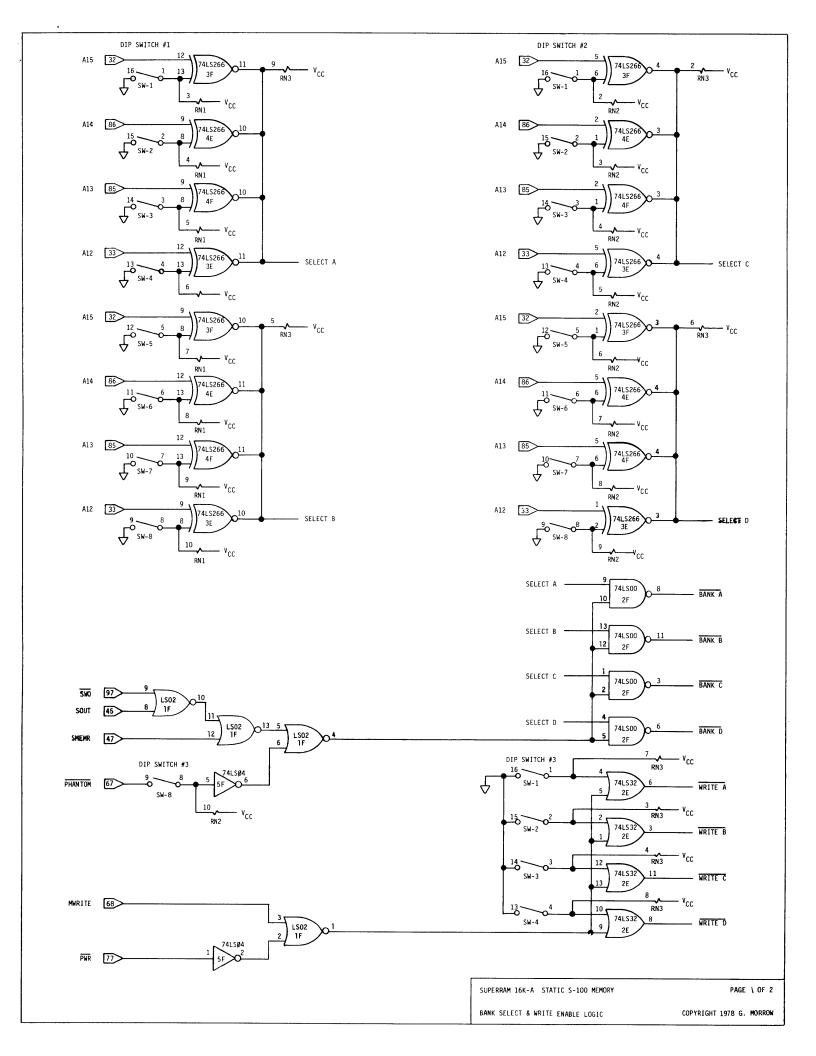

### ADDRESS SELECT LOGIC

The SuperRam 16K-A is configured as four 4K blocks of memory. The board has circuitry which allows each of these four blocks to be independently addressed. Each block uses a 74LS266 open collector quad exclusive-NOR pack and four switches of an eight position DIP switch to select one of sixteen possible 4K boundaries at which the block is to be located.

One input of each of the four gates is connected to address lines A15, A14, A13 and A12, respectively. The other input is connected to an address select switch and pull-up resistor. If the switch is open, the pull-up resistor forces a logic "1" to the input. The output transistor will then be in the OFF state if and only if the corresponding address line connected to the other input is also a logic "1". If the switch is closed, the input will be grounded (logic "0"). In this case, the output transistor will be in the OFF state if and only if the corresponding address line connected to the other input is also a logic "0". The four outputs of these exclusive-NOR gates are connected together along with a pull-up resistor.

If all four of the output transistors are in the OFF state, the common output node will be pulled up to +5 volts through the resistor and will be at a logic "1". This common output node will be at a logic "1" when the logic level on each address line A15-A12 independently matches the logic level determined by the switch associated with the address line. If there are any mismatches, one or more of the output transistors of the exclusive-NOR gates will be ON (i.e., conducting to ground) and the common output node of the four gates will be at a logic "0". There are four of these common output nodes. They are labeled SELECT A, SELECT B, SELECT C and SELECT D. When one of these select lines is high, the 4K block of memory associated with this line will be selected if the status signals \$\overline{SWO}\$, \$\overline{SWO}\$, \$\overline{SUUT}\$, \$\overline{SMEMR}\$ and (conditionally) \$\overline{PHANTOM}\$ are at the appropriate levels to signal a memory reference.

### BOARD SELECTION LOGIC

In order to reference one of the four 4K blocks on the board, one or more of the select signals discussed above must be at a logic "1". But this is not enough. The only bus cycle which the board will respond to are memory references.

SWO is a status signal which is active (logic "0") during bus cycles which transfer data from the CPU to a bus slave (memory, I/O, etc.). SOUT is active (logic "1") when the CPU is transferring data to an I/O device. Thus the CPU is writing into memory when SOUT and SWO are both in a logic "0" state. When the CPU is reading memory SMEMR is active (logic "1").

PHANTOM is active (logic "O") when phantom ROM or other exceptional memory must usurp the bus and lock out normal to furnish the CPU with special instructions. This is most common during power-up when the CPU's program counter is forced to zero.

We shall define memory write cycle to be a bus cycle during which PHANTOM is a logic "1" and SMEMR is a logic "1". The SuperRam 16K-A board is selected whenever a memory read or a memory write is in progress and at least one of the select lines SELECT A, SELECT B, SELECT C, or SELECT D is at a logic "1" level. During memory reads or writes, SELECT A activates BANK A, SELECT B activates BANK B, etc.

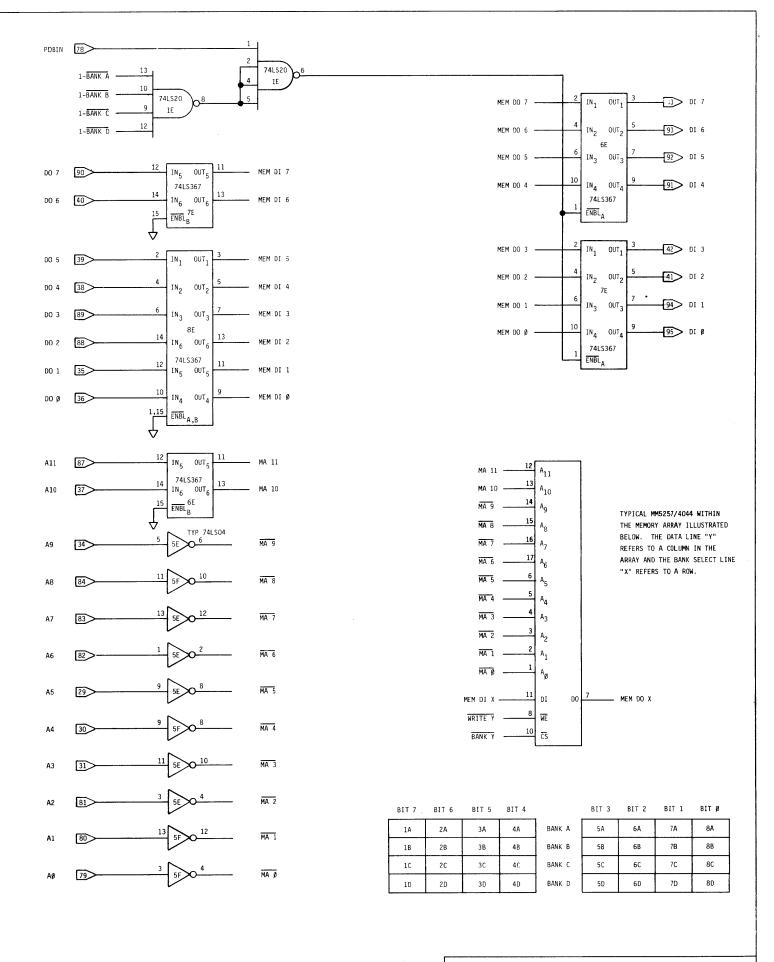

### DATA TRANSFER LOGIC

PDBIN is the data input strobe signals. The CPU drives this line high during the period of a bus cycle when an addressed peripheral is to place its data on the input lines. On the 16K-A board, the PDBIN signal turns on the tri-state\*\* buffers to the CPU's input lines whenever one of the banks on the board is selected. This logic is implemented with a pair of 4-input NAND gates at position 1E of the circuit board and appears at the upper left hand corner of page 2 of the schematics.

Both  $\overline{\text{PWR}}$  and MWRITE are strobe signals active when the CPU transfers data to a peripheral device.  $\overline{\text{PWR}}$  is the logic "0" strobe for both memory and I/O writes while MWRITE is the logic "1" strobe for memory writes only. However, not all CPUs generate the MWRITE signal. On both the original ALTAIR and IMSAI machines, the MWRITE signal is generated by the front panel.

The only time information can be written into the MM5257/4044 memory chips when both the chip select  $(\overline{CS})$  and the write enable  $(\overline{WE})$  inputs are at a logic "0" level. The  $\overline{CS}$  inputs are connected to the BANK A, BANK B, BANK C or BANK D signals on page 1 of the schematics and is low only when the proper block of memory on the board is selected. The  $\overline{WE}$  inputs are connected to the  $\overline{WRITE}$  A,  $\overline{WRITE}$  B,  $\overline{WRITE}$  C, or  $\overline{WRITE}$  D signals also on page 1 of the schematics. These signals are low whenever either of the data output strobes is active and the write enable switch corresponding to the proper block of memory is closed. Thus, memory must be write enabled and selected before it can be written into.

### WARRANTY SupeRam 16K-A

Parts are warranted to be free from defects in material and workmanship. Defective parts returned postpaid will be exchanged free of charge. SupeRams purchased in kit form are warranted for six months from date of invoice; SupeRams purchased as assembled units are warranted for one year from invoice date. Malfunctioning units will be repaired, tested and returned with minimal charge for handling if in the opinion of Morrow's Micro-Stuff/Thinker Toys care has been exercised in their assembly and/or use. If improper operation is due to assembly or other errors on the part of the purchaser, repair fees will be charged. Purchaser will be notified if the charge exceeds \$25.80. Warranty is void if on inspection it is found that the product has been subject to improper assembly or abuse, or if the malfunction is due to failure to follow printed instructions, unauthorized modifications, or use in applications other than intended. Units returned for warranty service must be accompanied by proof of purchase and a letter describing the problems.

The foregoing warranty is in lieu of all other warranties expressed or implied and in any event is limited to product repair or replacement.