# Wunderbuss Input/Output Controller Technical Manual

# TABLE OF CONTENTS

| 1. | INTRODUCTION              | 1                                                              |

|----|---------------------------|----------------------------------------------------------------|

| 2. | WB I/O ACTIVE TERMINATION | 2                                                              |

| 3. | I/O ADDRESSING            | 3                                                              |

| 4. | THE INTERRUPT SYSTEM      | 56<br>67<br>88<br>88<br>99<br>99<br>10<br>10<br>10<br>11<br>11 |

| 5. | PROGRAMMING THE PIC       | 111<br>111<br>121<br>141<br>141<br>151<br>161<br>171<br>171    |

| 6. | ACE SERIAL PORTS          | 20                                                             |

| 7. | PROGRAMMING THE 8250      | 21<br>22<br>23<br>26                                           |

# TABLE OF CONTENTS, CONT.

| 8.   | THE PARALLEL DAISY-WHEEL PRINTER PORT                     | 27<br>31<br>32<br>32                                     |

|------|-----------------------------------------------------------|----------------------------------------------------------|

| 9.   | THE AUXILIARY PARALLEL PORT                               | 33                                                       |

| 10.  | THE 1990 CALENDAR/CLOCK CHIP.  10.1. Clock Initialization | 35<br>37<br>38<br>41<br>41<br>42<br>42<br>43<br>43<br>44 |

| 11.  | LIST OF REFERENCES                                        | 45                                                       |

| Appe | endices                                                   |                                                          |

|      | A. SOME NOTES AND CAUTIONS                                | L                                                        |

SUBJECT INDEX

# L I S T O F T A B L E S

| 2-1:                         | S-100 Power Connections                                                                                                   | 2                          |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3-2:<br>3-3:                 | DIP Switch 7C  Output to GROUP SELECT Port BASE+7  I/O Map-out BASE+7  GROUP Assignments                                  | 3<br>4<br>4<br>5           |

| 4-1:                         | Map of the Hardware Devices Associated With PIC Input                                                                     | 8                          |

| 5-2:<br>5-3:<br>5-4:<br>5-5: | ICWl Bit Assignments                                                                                                      | 12<br>13<br>15<br>16<br>18 |

|                              | ACE I/O GROUP Description                                                                                                 | 2Ø<br>21                   |

| 7-2:<br>7-3:                 | Registers for the 8250                                                                                                    | 22<br>23<br>24<br>26       |

| 8-2:<br>8-3:                 | Printer Strobe Lines  Printer Line Commands  Daisy-Wheel Printer Signals and I/O Map  Printer Port P5 - Connector Pinouts | 27<br>28<br>30<br>31       |

|                              | Parallel Port Switch Configuration                                                                                        | 33<br>34                   |

| 10-2:<br>10-3:               | 1990 Calendar/Clock I/O Map                                                                                               | 35<br>35<br>39<br>43       |

#### 1. INTRODUCTION

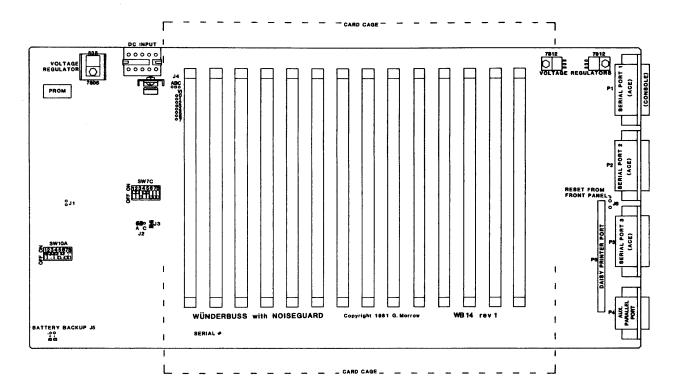

The Wunderbuss Input/Output Controller (WB I/O) is the heart of a general purpose S-100 system that combines all the features necessary for an efficient interrupt-driven, multi-user system. The WB I/O is built on a motherboard capable of holding up to 14 additional S-100 utility cards. Its features include:

- 1. A patented active termination system that reduces noise inherent to connection of S-100 signal lines.

- 2. An 8259-A Programmable Interrupt Controller (PIC) device designed to monitor up to eight peripheral devices and set priorities for their service.

- 3. Three 40-pin programmable Asynchronous Communication Elements (8250 ACE serial interfacing devices) capable of generating CPU interrupts in response to RS 232 signals and communication events.

- 4. A 50-pin connector for a daisy-wheel printer.

- 5. A bi-directional, undedicated, multi-purpose parallel port.

- 6. A CMOS crystal-controlled, multi-functional calendar/clock chip.

The serial, parallel, clock and PIC devices on the WB I/O are all I/O mapped. They are accessed through switch selectable I/O port addresses. These devices may be programmed to generate interrupts to the CPU via the PIC based on a rich selection of status conditions.

The design and versatility of the WB I/O ensures the user of a long useful life, even in a system subject to frequent upgrading. Like all Morrow Design products, it should give the user years of satisfaction.

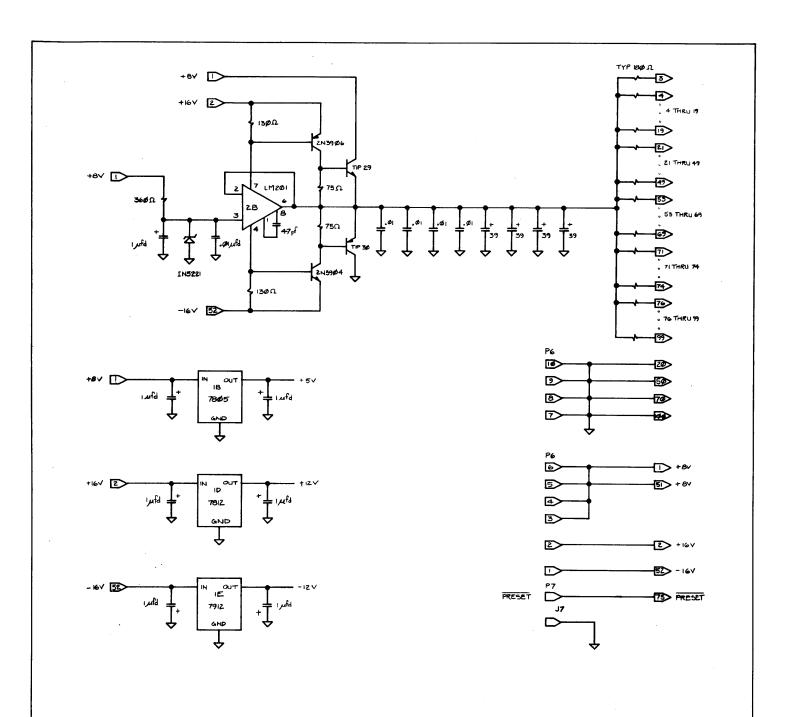

### 2. WB I/O ACTIVE TERMINATION

The WB I/O features a 14 slot IEEE 696 standard S-100 motherboard with a patented active termination system referred to as Noise Guard. The structure and pinout of the S-100 bus normally lends itself to crosstalk and signal noise in an inproperly or unterminated bus. But the WB I/O eliminates this problem by the use of active termination. All IEEE 696 signal lines are actively pulled up through 180 Ohm resistors. One exception to this is PRESET, line 75. This line is pulled high on the MPZ80 CPU card. The table below depicts the power connections for the S-100 pins.

Table 2-1: S-100 Power Connections

| tion        | nnect | Cc | Pins |

|-------------|-------|----|------|

| unregulated | 8 V   | +  | 1,51 |

| unregulated | 16 V  | +  | 2    |

| unregulated | 16 V  | -  | 52   |

|             | ound  | gr | 2Ø   |

|             | ound  | gr | 5Ø   |

|             | ound  | gr | 7Ø   |

|             | ound  | gr | 100  |

The design of the WBI /O motherboard allows the bus to meet or exceed all the specifications for the S-100 bus at 6 Mhz making the board the heart of a powerful, reliable and expandable system. For a complete description of the S-100 bus, refer to the reference on specifications for the S-100 bus interface devices.

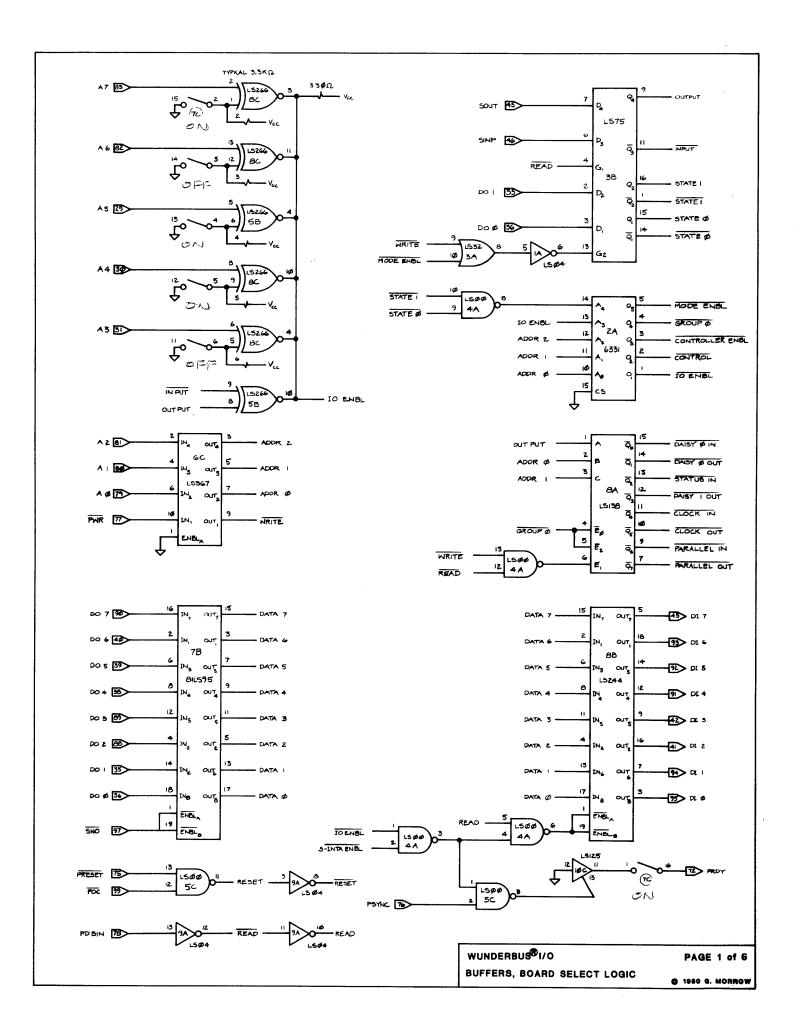

#### 3. I/O ADDRESSING

All devices on the WB I/O are associated with some S-100 I/O port. In all, almost 30 distinct I/O registers are used to control the many device functions available on the board. Yet the WB I/O takes up only eight I/O port addresses. To understand how so many registers can be accessed through so few ports, it is useful to think of the port addressing scheme of the WB I/O as 'bank-select I/O'. As the name suggests, this is analogous to conventional bank-select memory schemes. Specifically, banks of registers are allowed to share the same block of consecutive I/O addresses while a dedicated I/O port is used to enable one bank, and at the same time, disable all other similarly addressed banks.

The WB I/O is divided into four I/O banks, (hereafter called groups) with each group occupying the same eight I/O port addresses - BASE to BASE+7. Port address BASE+7 is the GROUP SELECT port, and establishes which of the four I/O groups will be active at any given time. By outputting some number between Ø and 3 to the GROUP SELECT port the user enables operations directed to ports between BASE and BASE+6. To enable a different group, the user must output a different group number to GROUP SELECT port BASE+7. While this port selection technique is extremely efficient in conserving I/O space, it does impose the responsibility of keeping track of which I/O group is currently active.

#### 3.1. I/O Port Addressing

DIP switch 7C is used to determine the BASE port address of the I/O groups on the WB I/O. Paddles 2 through 6 of switch 7C are compared with S-100 address lines A3 through A7 allowing BASE to be located at any eight byte I/O boundary. The relationship between the the paddles and the address lines are as follows:

Table 3-1: DIP Switch 7C

| Paddle | Number | Address | Line |

|--------|--------|---------|------|

| 2      |        | A7      |      |

| 3      | ·      | A6      |      |

| 4      |        | A5      |      |

| 5      |        | A4      |      |

| 6      |        | A3      |      |

|        |        |         |      |

Setting a paddle to the ON position causes a match to occur when its associated address line is a low logic level. If all five switches are ON, the BASE address is at port  $\emptyset$ . The standard address in all Morrow Design systems is port 48 hex.

#### 3.2. GROUP SELECT Port BASE+7

Once the base address has been established by setting DIP switch 7C, the addresses of all I/O functions on the WB I/O are determined (see I/O MAP on the following page). In order to gain access to a specific device function, however, the group number of that device function must first be output to I/O port BASE+7. The I/O group is selected by executing an output instruction to port BASE+7 with data bits Ø and l set as follows:

Table 3-2: Output to GROUP SELECT Port BASE+7

| Data Bit-1 | Data Bit-Ø | Group Number |

|------------|------------|--------------|

| Ø          | Ø          | Ø            |

| Ø          | 1          | 1            |

| 1          | Ø          | 2            |

| 1          | 1 .        | 3            |

Use of the group select port is best described by example. pose you want the I/O space taken by the WB I/O to extend from 48 hex to 4F hex and you want to access serial port and daisywheel printer port  $\emptyset$ . First set the I/O base by turning 7C, paddles 3 and 6 ON and paddles 2, 4 and 5 OFF. With this base address selected, the GROUP SELECT port is at BASE+7, or port 4F hex. In order to read serial device number two, the user first outputs a 2 to the GROUP SELECT port. Further outputting or inputting to ports 48 hex through 4F hex controls the registers for the number two ACE serial device. To access the parallel daisy-wheel printer port, the user would then output a Ø to the GROUP SELECT port. It is important to remember that the functions of ports at BASE to BASE+6 change from device to device depending upon the last value sent to the group select port. following chart depicts the configuration of the GROUP SELECT port.

Table 3-3: I/O Map-out BASE+7

| D 1 | D Ø    | Gp.# | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | l<br>Ø |      | For a just the common of the c |

The GROUP control register is I/O port BASE+7. To select an I/O group, output to port BASE+7 with data bits  $\emptyset$  and 1 set as indicated above. Once a group is selected, ports are assigned as follows:

#### Table 3-4: GROUP Assignments

#### GROUP Ø

| I/O Address                                  | Input                                                                                                         | Output                                                               |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| BASE<br>BASE+1<br>BASE+2<br>BASE+3<br>BASE+4 | DAISY Ø IN (STATUS) Switch/Parallel port flags R.T. Clock IN/RESET CLK. Int. Parallel data IN 8259 Ø register | DAISY Ø OUT DAISY 1 OUT R.T. Clock OUT Par. data OUT 8259 Ø register |

| BASE+5<br>BASE+6                             | 8259 1 register<br>not used                                                                                   | 8259 l register<br>Par. port cntrl.                                  |

#### GROUPS 1, 2 & 3 - 8250 ACE Serial I/O Ports

|        | Input                  | Output                    |

|--------|------------------------|---------------------------|

| BASE   | Receive buffer         | Transmit buffer/LSB baud  |

| BASE+1 | Interrupt Enable       | Interrupt Enable/MSB baud |

| BASE+2 | Interrupt Identify     | not used                  |

| BASE+3 | Line Control register  | Line Control register     |

| BASE+4 | Modem Control register | Modem Control register    |

| BASE+5 | Line status register   | not used                  |

| BASE+6 | Modem status register  | not used                  |

Note that an output to BASE+7 always assigns an I/O group but has no function within any given I/O group.

#### 4. THE INTERRUPT SYSTEM

Microcomputer systems in general are required to communicate with peripheral devices such as printers, CRT terminals and various types of parallel devices. There are classically two ways of approaching the way a CPU may service these devices - polled and interrupt.

In a polled mode, every device in the system is periodically querried about its service requirements. When a device requires servicing (for example, a person has just typed a character on a CRT terminal), the CPU stops polling all other devices until it has finished servicing the user's request. From a system viewpoint the CPU should handle these requests as quickly as possible. The total system throughput is a function of the number of devices on the system, the length of time to poll each device and service each device request. The operating system is never idle; it is always polling the devices searching for activity.

There is a direct analogy here to hardware design: This type of operation is said to be synchronous, meaning the CPU may branch to a service request subroutine only after it has determined from the device, through polling, that it is necessary to do so. There are certain problems with this approach, though. These lie in the amount of time needed to service each request. Another disadvantage lies in the lack of priority-setting for the peripheral devices. In a polled system, each device has equal status, which is unfortunate because in a real environment some devices require faster, more frequent service response than others. Polling high priority devices more frequently is one solution, but this burdens the system I/O subroutines with complex algorithms. Another disadvantage is that the processor is always occupied with the polling process and not able to perform other tasks.

An interrupt-driven system is much different in its implementation. Although requiring more hardware and more complex software, the system has none of the problems associated with a polled system. With correct hardware, the devices are all prioritized according to their service requirements and the CPU is free to handle other tasks until a device requires service. The I/O devices themselves in this system interrupt whatever the CPU is presently doing only when they require something from the host processor. This type of system is more analogous to an asynchronous hardware design - one where events can occur at random intervals not related to the CPU's operations. Its randomness corresponds nicely with the relative randomness of device requirements tied into the system and allows maximum system response to these peripherals.

#### 4.1. The Programmable Interrupt Controller (PIC)

This section describes the use of the PIC in the WB I/O, but before going any further, one assumption must be made: If using a Z80 CPU chip, an Enable Interrupt (EI) instruction must be executed and the Z80 set to Interrupt Mode 0 (8080 mode). The PIC instructions and modes are described in further detail in the following pages.

The additional hardware design requirements in an interrupt system have been kept to a minimum in this system by using an 8259-A programmable interrupt controller integrated circuit chip. By using this chip in conjunction with standard integrated circuits a powerful interrupt driven system has been implemented. This section describes the software requirements necessary to utilize the PIC to its fullest.

The PIC can directly monitor the requirements of eight separate devices and prioritize them according to system requirements. The system has three serial channels (the hardware uses three Universal Asynchronous Receive Transmit integrated circuits called UARTs) which are normally connected to CRT terminals or a serial printer. These three devices are tied directly to the

PIC to provide a signal when they require servicing. The WB I/O also has a DAISY port which can generate a signal for the printer whenever it requires servicing. Besides the UARTs and the DAISY port, the on-board real-time clock may be programmed to generate interrupts at precise, software-selected intervals. Multi-user systems in general require a real-time clock to insure proper allocation of the CPU's time among various tasks.

So far we have described five of eight possible events the PIC may monitor. Besides these, the system provides the user with the option to monitor three of the S-100 vectored interrupt lines. These lines are jumper options on the WB I/O which allow the the on-board PIC to monitor and prioritize interrupts generated by boards plugged into the S-100 bus such as disk controllers or MultI/O boards.

#### 4.2. PIC Interrupt Vectors

To signal the host CPU that one of the monitored devices requests service, the PIC must issue a signal called PINT (processor interrupt, line-73 of the S-100 bus) to the host CPU. The host CPU completes its current instruction and issues a signal called SINTA (interrupt acknowledged, line-96 of the S-100 bus) indicating it has recognized the requested interrupt and is willing to receive its next instruction from the interrupting device, in this case, the PIC.

At this point, a device may generate any instruction it wishes and the host CPU will execute it. Two logical instructions might be asked of the CPU in such a case - a Restart or a Call. These are logical choices because both of them predictably alter the current flow of instruction by changing the value of the Program Counter to a given address, then saves the location where the CPU is to return afterwards by pushing the current Program Counter onto the stack. The Restart instruction is limited to eight locations where the program may branch, making this instruction dependent on hardware and software environments and leaves us with the Call instruction.

The PIC has been designed to generate a Call instruction upon receiving the SINTA response from the host CPU. The CPU then fetches a 16-bit address of the location of the interrupt vector. Hardware on the WB I/O counts the next two CPU fetches (the address vector) and enables the PIC to output this address to the data-in bus. When programmed, the PIC has eight vector addresses associated with it that correspond to the eight interrupt devices it monitors. The vector contains a jump instruction to the address of the routine responsible for handling it.

The PIC generates interrupt vectors at either eight-byte or four-byte intervals in the 16-bit address space, limited by both the PIC and the CPU to a 64K address space. For compactness, most routines use the four-byte separation since a jump instruction is only three bytes long and few interrupt service routines fit in

less than an eight byte address space. The eight-byte interval is provided for compatibility with the use of the 8080 and Z80 restart instructions which are spaced eight bytes apart. The following is a map of the hardware devices associated with the PIC input line.

Table 4-1: Map of the Hardware Devices Associated With PIC Input Lines

|         | IRQ Line | Device                     |

|---------|----------|----------------------------|

| Highest | Ø        | S-100 vectored interrupt 0 |

|         | 1        | S-100 vectored interrupt 1 |

|         | 2        | S-100 vectored interrupt 2 |

|         | 3        | Serial Device #1           |

|         | 4        | Serial Device #2           |

|         | 5        | Serial Device #3           |

|         | 6        | DAISY print wheel ready    |

| Lowest  | 7        | Real-time clock TP line    |

#### 4.3. PIC Modes

The PIC, being a software programmable device, can be set up in many different modes allowing itself to be tailored to any operating environment. The Decision 1 environment takes advantage of some of these features and the user is free to explore others. This section explores some of the more common PIC modes. For a rigorous description of the different modes please refer to the Intel Data Sheet and Application Note.

# 4.3.1. Triggered Modes

The PIC may be programmed to monitor the eight devices in either edge-triggered or level-triggered mode. In the edge-triggered mode, the PIC generates an interrupt when it senses a change on one of its eight input lines (IRQØ - IRQ7). This is suitable for events that do not latch their interrupt requests to the PIC. However, this does cause a problem when the UARTs generate one edge only for one or more interrupts. The result is a possible loss of some interrupt requests. For this reason, all Morrow Designs software use only the level-triggered mode.

#### 4.3.2. Master/Slave Mode

The PIC may be programmed to be either a single system PIC or part of a larger interrupt system involving up to four PICs. This would be the case in a system where more I/O is required and one or more Morrow Designs I/O controller boards has been installed. In a multiple configuration, one PIC is designated as the Master and is the only device which may control the PINT line on the S-100 bus. All other PICs drive the selected S-100 vectored interrupt lines monitored by the Master PIC. However, cascading of multiple PICs is not supported in the WB I/O hardware implementation.

#### 4.3.3. Buffered Mode

The buffered mode option for the PIC is not implemented on the WB I/O board.

#### 4.3.4. End of Interrupt (EOI) Mode

An in-service bit (IS) on the PIC indicates a pending interrupt. This may be reset manually by the interrupt service routine of the CPU, or automatically after the third byte of the Call instruction has been sent by the PIC. An automatic End of Interrupt (AEOI) instruction is programmable at the time of initialization only, so once set, the PIC must be re-initialized to change this mode. In AEOI mode, the full nesting capabilities of the PIC are lost. For this reason, and for maximum system flexibility, all Morrow Designs software has been written with the AEOI feature disabled.

#### 4.3.5. Polled Mode

The PIC may be configured to resemble a polled I/O system by setting the Poll bit to a logic 'l'. In this mode, the PIC does not generate an interrupt with a change in state on any of its IRQØ - IRQ7 lines. The CPU issues a Poll command to the PIC, the PIC then gates a byte onto the data-in lines to the CPU indicating the highest priority interrupt pending. The lower three bits of the byte are used to indicate which device requires service. The highest bit, if set, indicates a device is requesting service.

#### 4.3.6. Nested Mode

The nested mode of the PIC allows service requests from I/O devices to be prioritized. When a device is in need of service, the PIC issues an interrupt to the host CPU only if there are no higher priority devices requesting service via the PIC. If a lower priority device requires service, it must wait until all higher priority devices are serviced and the interrupt-handling subroutine has issued an EOI command to that PIC. If a device of higher priority requires service, the lower priority device's service subroutine is interrupted until the higher priority device has been serviced. Although this requires intricate software routines to keep track of the signals, this mode allows maximum system response to devices which require immediate service. All Morrow Designs software take advantage of the PIC nesting.

# 4.3.7. Rotating Priority - Mode A

In the nested mode, devices are prioritized and the device with highest priority obtains service. The priorities are assigned according to which input line (IRQØ - IRQ7) a device is connected. This scheme works well for devices not inherently equal. In some instances all eight devices connected to the PIC have the same priority. The PIC may be programmed to rotate the priority through all devices. In this mode, each device gets rotated to the lowest priority after it has been serviced; all other devices are raised one level in the priority ladder. At present, Morrow designs software does not implement the rotating priority option.

# 4.3.8. Rotating Priority - Mode B

This mode is very similar to Mode A, the difference being rotation in Mode B can be controlled with software as opposed to a fixed rotation controlled by hardware internal to the PIC, as in Mode A. The software is only allowed, however, to set that device with the lowest priority. All other devices are ordered by priority via the PIC. The next lowest priority device is then shifted into the highest priority spot. For instance, if IRQ2 was set as the lowest priority, the PIC automatically sets IRQ3 as the highest.

#### 4.4. PIC Status Registers

The PIC status registers may be read to determine the current state of the PIC. These registers place IRQ0 - IRQ7 status on data-in bits,  $\emptyset$  - 7 respectively. IRQ0 is assumed to be the highest priority and IRQ7 the lowest.

#### 4.4.1. Interrupt Mask Register (IMR)

The PIC has the capability of masking any one of eight interrupt inputs - i.e. not allowing that particular device to generate an interrupt. The mask register contains eight bits, any of which, when high, shut off the appropriate IRQ input to the PIC. If all the bits are set high, no interrupts are generated. If all are set low, all devices are recognized in their normal prioritized sequence. This allows the software complete control over each individual device's service requests. The register can be written and read by the system software.

#### 4.4.2. In-Service Register (ISR)

The in-service register allows the software to query the PIC for those devices currently being serviced. Each of the eight lines are associated with eight bits. A high level indicates that device being serviced. Bits in this register are reset by the software issuing an EOI (either specific or non-specific) at the end of the associated interrupt service routine.

#### 4.4.3. Interrupt Request Register (IRR)

This eight-bit register is read to determine which of the eight devices is requesting service. The highest pending priority is reset whenever an interrupt from the PIC has been acknowledged by the CPU. (This register is not affected by the IMR - a device may request an interrupt and be masked out.)

#### 5. PROGRAMMING THE PIC

The PIC is a programmable device and must be initialized for correct operation.

NOTE: If the PIC is not initialized, it is still possible for it to generate spurious interrupt requests to the host CPU. Programs such as DDT - the Dynamic Debugging Tool by Digital Research - only aggravate this problem by issuing Enable Interrupt instructions whenever the 'GO' command is invoked. This caution should be followed in systems where interrupts are not implemented as well.

The PIC is accessed through system ports BASE+4 and BASE+5. Since context plays an important role in determining what each of these ports control, remember this rule: outputting to BASE+4 sets PIC address bit-AØ to a 'Ø' or low logic level; outputting to BASE+5 sets PIC address line AØ to a 'l' or high logic level. There are two types of registers internal to the PIC. Registers referred to as ICW are initialization registers and are typically accessed only when the PIC has been first powered up. Registers referred to as OCW are operation control registers and are read from and written to during regular PIC operation (subsequent to initialization).

#### 5.1. Initialization Registers

The PIC is ready to accept commands for initialization on power-up. There are a minimum of two registers in the PIC which must be initialized for the PIC to begin servicing interrupt requests. Depending on the mode the user operates in, as many as four registers must be initialized prior to operation. These registers are detailed below.

#### 5.1.1. Initialization Control Word 1 (ICW1)

The first word written to initialize the PIC is ICW1. It is specified by outputting to port BASE+4 a value with data bit-4 set logic high. This informs the PIC that the initialization sequence is beginning. In addition to bit-4 being set, the other bits are assigned the following function:

# Table 5-1: ICWl Bit Assignments

| Bit | Function                                                                                                                                                                                                                                                                                                          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Part of the high byte of the beginning address of the interrupt vectors; bit-A7 of the call address.                                                                                                                                                                                                              |

| 6   | Part of the low byte of the beginning address of the interrupt vectors; bit-A6 of the call address.                                                                                                                                                                                                               |

| 5   | Part of the low byte of the beginning address of the interrupt vectors; bit-A5 of the call address.                                                                                                                                                                                                               |

| 4   | Set high to begin initialization sequence.                                                                                                                                                                                                                                                                        |

| 3   | LTIM - set to 1 for level-triggered mode (normally high for all Morrow Designs software).                                                                                                                                                                                                                         |

| 2   | ADI - Call address interval. Low for call address at eight-byte intervals, high for four-byte intervals (normally high for all Morrow Designs software).                                                                                                                                                          |

| 1   | SNGL - Single or multiple PICs in the system to be used in cascade mode. Since WB I/O does not support cascading, this bit set to a 1.                                                                                                                                                                            |

| Ø   | ICW4 - This bit set high allows access to the Initialization Control Word 4 for selection of operation modes. If this bit is set low, the PIC initialized as master, non-buffered mode, no AEOI and in the normal nested mode (normally low for all Morrow Designs software; set this bit low when initializing). |

# 5.1.2. Initialization Control Word 2 (ICW2)

Initialization Control Word 2 is available at BASE+5 after ICWl has been selected and initialized. The ICW2 register contains the high byte of the call address vector starting address. The bits are configured as follows:

# Table 5-2: ICW2 Bit Assignment

| Bit | Function                                                                                                                     |

|-----|------------------------------------------------------------------------------------------------------------------------------|

| 7   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-Al5 of the call address.                |

| 6   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-Al4 of the call address.                |

| 5   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-Al3 of the call address.                |

| 4   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-Al2 of the call address.                |

| 3   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-All of the call address.                |

| 2   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-Al $\emptyset$ bit of the call address. |

| 1   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-A9 of the call address.                 |

| Ø   | Part of the high byte of the beginning address of the interrupt vectors. This is bit-A8 of the call address.                 |

#### 5.1.3. Initialization Control Word 3 (ICW3)

Morrow Designs implementation does not require the initialization of ICW3. If the cascade feature is absolutely required within a system configuration, a Morrow Designs Mult I/O board should be installed to become the master PIC for the system. The user is free to explore this option and is referred to the Mult I/O manual for details on both that board and on cascading PICs.

#### 5.1.4. Initialization Control Word 4 (ICW4)

This register is available at BASE+5 if the ICW4 access bit of register ICW1 (bit-0) was not set when beginning the PIC initialization routine. Normally, this register need not be accessed as all bits are automatically cleared to the mode that Morrow Design's software uses. If the user wishes to change to AEOI, buffered, slave or fully nested mode, he is free to program this register appropriately.

#### 5.2. Operation Control Registers

One the PIC is initialized, it is ready to function as the system interrupt controller. Further changes in the PIC operating parameters are accomplished by programming a set of registers referred to as the Operation Control Registers.

## 5.2.1. Operation Control Word 1 (OCW1)

This register contains a software mask that allows the operating system to mask out any of the eight interrupt inputs and is available any time after initialization sequence through port BASE+5. Setting any of the bits high forces the PIC to ignore the interrupt request line associated with that bit. The bits are arranged with data bit-7 corresponding to IRQ7 and data bit-0 corresponding with IRQ0. As indicated, a bit set high masks the interrupt request; a bit set low unmasks it. The PIC clears this register to 0 (all enabled) on power up.

# 5.2.2. Operation Control Word 2 (OCW2)

Operation Control Word 2 (OCW2) is selected by outputting to BASE+4 with bits 3 and 4 reset (logic  $\emptyset$ ) any time after the initialization sequence. On power up, these bits are all reset (logic  $\emptyset$ ). This registers allows control over the following functions:

Table 5-3: OCW2 Bit Assignments

| Bit | Function                                   |

|-----|--------------------------------------------|

| 4   | Must be low to access OCW2.                |

| 3   | Must be low to access OCW2.                |

| 2   | L2 - Specific end of interrupt bit-2 (MSB) |

| 1   | Ll - Specific end of interrupt bit-l       |

| Ø   | LØ - Specific end of interrupt bit-Ø (LSB) |

Bits 5, 6 and 7 are multiplexed and have the following functions:

| Function                                      | Bit-5 | Bit-6 | Bit-7 |

|-----------------------------------------------|-------|-------|-------|

| Clears rotate priority -                      |       |       |       |

| Mode A flip-flop                              | Ø     | Ø     | Ø     |

| End of Interrupt                              | 1     | Ø     | Ø     |

| Specific Interrupt                            | 1     | 1     | Ø     |

| Sets rotate<br>priority -<br>Mode A flip-flop | Ø     | Ø     | 1     |

| EOI causes<br>rotate -<br>priority Mode A     | 1     | Ø     | 1     |

| Sets rotate<br>priority Mode B                | Ø     | 1     | 1     |

| EOI causes rotate priority Mode B             | 1     | 1     | . 1   |

#### 5.2.3. Operation Control Word 3 (OCW3)

Operation Control Word 3 (OCW3) is selected by outputting to BASE+4 with data bit-3 set and bit-4 reset (logic  $\emptyset$ ) any time after the initialization sequence. On power up, these bits are all reset (logic  $\emptyset$ ). Morrow Designs software does not use this register and leaves all bits reset. This register allows control over the following functions:

Table 5-4: OCW3 Bit Assignments

| Bit | Function                                                                                                                                                                                           |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Not used                                                                                                                                                                                           |

| 6   | ESMM - Enable Special Mask Mode when high.                                                                                                                                                         |

| 5   | SMM - Special Mask Mode when high.                                                                                                                                                                 |

| 4   | Must be Ø to access OCW3                                                                                                                                                                           |

| 3   | Must be 1 to access OCW3                                                                                                                                                                           |

| 2   | Enter poll mode when high, interrupt mode when low. A high on this line allows the next read BASE+5 to read the BCD code of the highest interrupt request pending (in non-interrupt environments). |

| 1   | SRIS - allows access to the Interrupt Request register (IRR) and the In-service register (ISR).                                                                                                    |

| Ø   | RIS - when low, allows access to the IRR by reading port BASE+5. When high, allows access to the ISR by reading port BASE+5.                                                                       |

# 5.3. Interrupt Status Registers

During normal PIC operation it may be desirable to examine the status and operating parameters of the device. There are three readable registers on the PIC which contain status information. They are accessed by inputting from the appropriate port and are defined as follows:

#### 5.3.1. Interrupt Mask Register (IMR)

The interrupt mask register may be read at any time by inputting from WB I/O port BASE+5. This eight-bit port contains a map of the IRQ lines which have been previously masked by outputting to BASE+5, the OCWl. If no IRQ lines are masked, all bits are low (logic  $\emptyset$ ) which is the normal condition on power-up. Any IRQ line that is masked has its appropriate bit set. IRQ7 is data bit-7 and IRQ $\emptyset$  is data bit- $\emptyset$ .

NOTE: The following two status registers are selected by setting the appropriate bits with OCW3. The registers is then available through BASE+4. The state of OCW3 bits Ø and l, (SRIS and RIS) once set, will allow continuous access to the selected register until the bits are changed (bits are internally latched by the PIC).

#### 5.3.2. Interrupt Request Register (IRR)

The IRR is an eight-bit register which, when read by inputting from WB I/O BASE+4, tells which of the IRQ lines are currently asserted at a high logic level and are awaiting acknowledgement. By reading this register, it is possible to determine which interrupt requests have been recognized and which have yet to be acknowledged. Bit-7 maps to IRQ7 and bit-0 maps to IRQ0. After initialization, this register may be read from BASE+5 as long as OCW3 is not changed (i.e. OCW3 bits ERIS = 1 and RIS = 0). The register is updated each time an interrupt request is acknowledged by the CPU.

#### 5.3.3. In-service Register (ISR)

The in-service register (ISR) is an eight-bit register containing information on which priority levels are currently being serviced. By reading this register (inputting BASE+4 with the OCW3 bits ERIS = 1 and RIS = 1), the user determines the number of the IRQ lines being serviced. IRQ7 maps to data bit-7 and IRQ0 maps to data bit-0. A logic high level on any bit indicates that the associated IRQ line is in service. The register is updated each time an EOI is issued.

#### Table 5-5: Typical Initialization Sequence

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

This routine will initialize the PIC as a single, master PIC, non-buffered mode, level-triggered, no automatic End of Interrupt (AEOI disabled), regular nested mode with the call vectors at 4 byte intervals. Although ICW4 and OCW1 are cleared to zero on power-up, the routine initializes them for completeness.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

```

base

Ø48h

equ

;base port address

grpsel

equ

base + 7

;group select port

group@

equ

init

Ø1Øh

equ

; bit high to initialize the PIC

icwl

equ

base + 4

; initialization control word 1

icw2

base + 5

equ

;initialization control word 2

base + 5

icw3

equ

;initialization control word 3

icw4

base + 5

equ

;initialization control word 4

ltim

Ø8

equ

;Level-triggered mode

adi

Ø4

equ

;Call address interval = 4 bytes

Ø2

sngl

equ

; one PIC in the system

IC4

equ

Øl

;ICW4 access bit

lovect

ØEØh

; low byte of interrupt vector address

equ

Øffh

hivect

equ

; high byte of interrupt vector address

normal

equ

;master/req. nest/non-buffered/no

;AEOI/8Ø85

; -normal mode for Morrow software

base + 5

ocwl

equ

;operation control word 1 - MASK

begin:

a, group@

mvi

out

grpsel

mvi

a, lovect + init + ltim + adi + snql + IC4

out

icwl

mvi

a, hivect

out

icw2

; vectors begin at address FFE0h

mvi

a, normal

icw4

out

out

ocwl

ret

```

This code initializes the PIC to generate the call instructions to addresses at four byte intervals beginning at FFEØh. Jump vectors to the interrupt service routines must be placed in these locations by the system software. The interrupt service vectors are as follows:

Table 5-6: Interrupt Service Vectors

| IRQ Line | Device           | Call Vector | (hex address) |

|----------|------------------|-------------|---------------|

| Ø        | S-100 V0         | FFEØ        |               |

| 1        | S-100 V1         | FFE4        |               |

| 2        | S-100 V2         | FFE8        |               |

| 3        | Serial Device 1  | FFEC        |               |

| 4        | Serial Device 2  | FFFØ        |               |

| 5        | Serial Device 3  | FFF4        | 9             |

| 6        | Daisy PWR line   | FFF8        | *             |

| 7        | RT Clock TP line | FFFC        |               |

#### 5.4. System Software Requirements

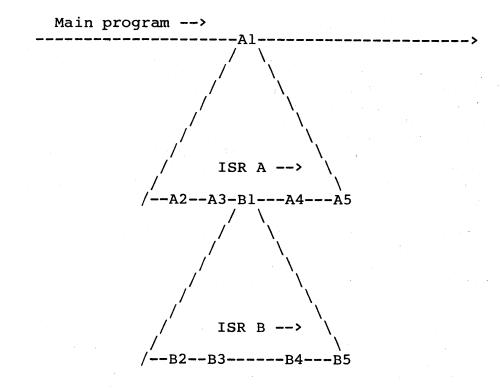

A typical system interrupt service routine (ISR) to service the PIC on the WBI/O must perform the following functions:

- 1. Enable interrupt instructions to the CPU.

- 2. When the interrupt occurs, the ISR saves the registers to be restored when the interrupt routine returns to the routine it interrupted.

- 3. Service the device which generated the interrupt.

- 4. Send an Enable Interrupt (EI) instruction to the CPU. This is necessary because interrupts are automatically disabled by the CPU whenever an interrupt has been received. Failure to do so prevents further interrupts to be acknowledged by the CPU. Once enabled, higher priority interrupts than the one being serviced are honored by CPU.

- 5. Send and EOI (end of interrupt) to the PIC. This would mean sending a 20h to WB I/O port BASE+4 of GROUP 0. This allows the current ISR to be interrupted by a device of same or lower priority.

- 6. Restore all the registers of the interrupted routine and return to that routine. Since the ISR was invoked through use of a Call instruction, a Return instruction must be executed to restore the Stack Pointer to its original position.

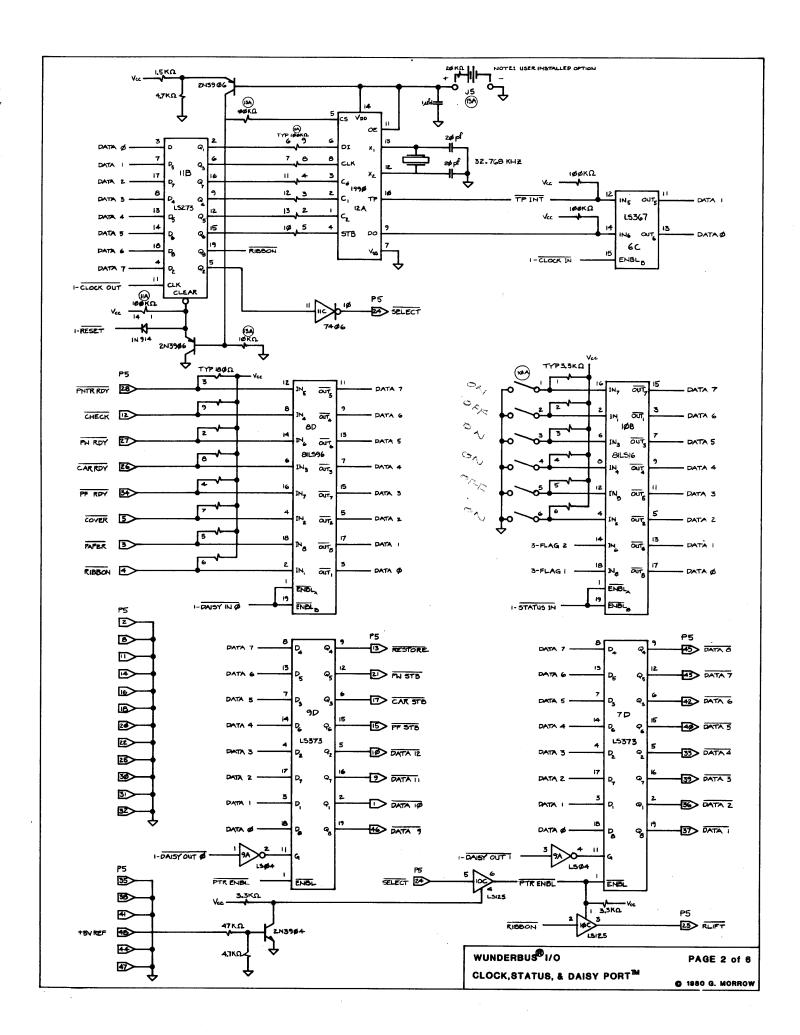

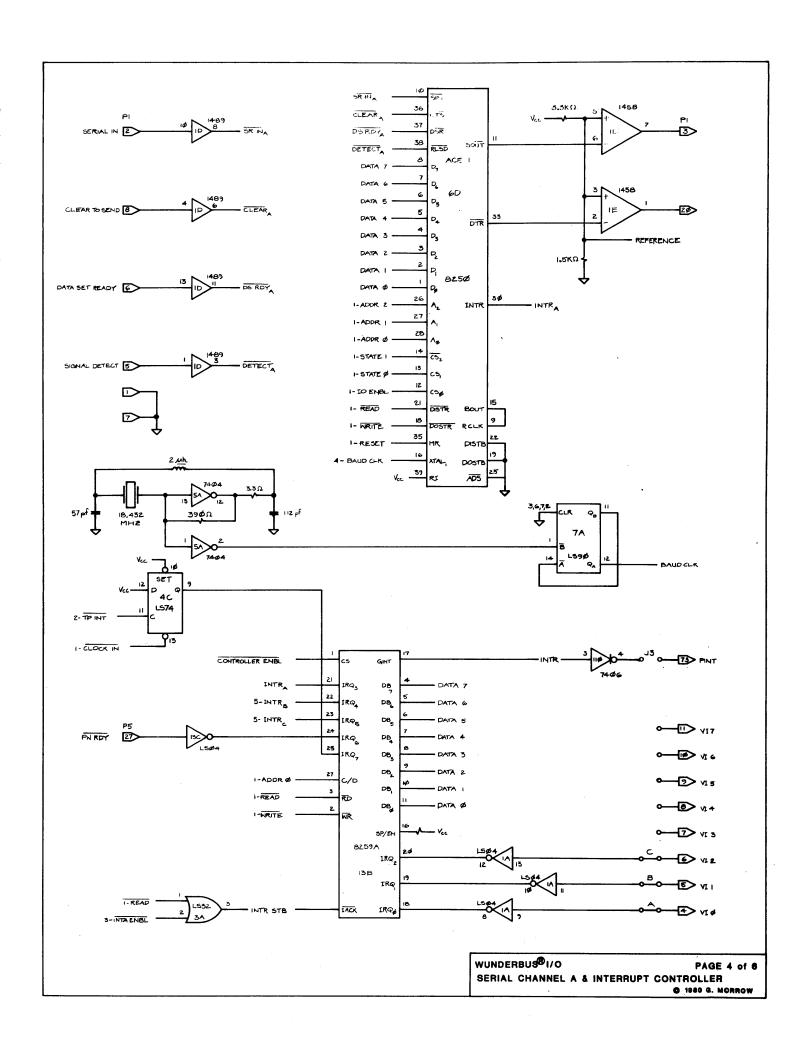

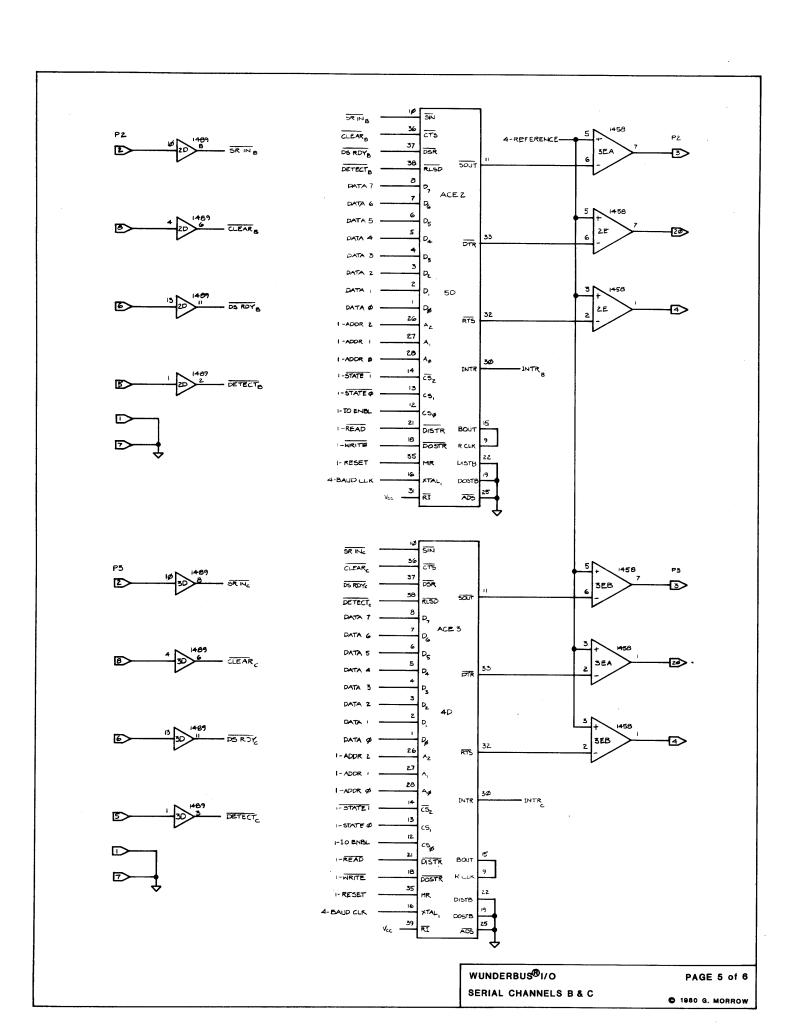

#### 6. ACE SERIAL PORTS

The WB I/Ohas three 825Ø programmable Asynchronous Communications Elements (ACE's) which can be connected to RS-232 devices via three 25-pin D-type connectors. Each ACE has an I/O group dedicated to it - GROUPS 1, 2 and 3. The ACE's are programmable and must be initialized before they can be used. tialization includes setting the baud rate, word length, parity, number of stop bits, and interrupt conditions. Each ACE can be programmed to generate an interrupt in response to up to conditions (e.g., data available, transmitter buffer em etc.). The interrupt is sent directly to the WB I/O PIC which can in turn pass it on to the host CPU. The interrupt handling routine then interrogates the interrupt status register of the responsible for generating the interrupt, and is thus able to determine the precise cause of the interrupt.

The following chart describes the ACE devices on the WB I/O, including the location of the 8250 on the circuit board, the location of the 26-pin ribbon cable connector associated with each ACE, the I/O GROUP controlling each ACE, and the interrupt level assigned to each device by the 8259-A PIC.

Table 6-1: ACE I/O GROUP Description

|         | I/O<br>GROUP # | 25-pin<br>Connector | Board<br>Location | Interrupt<br>Level |

|---------|----------------|---------------------|-------------------|--------------------|

| ACE # 1 | 1              | Pl                  | 6D                | 3                  |

| ACE # 2 | 2              | P2                  | 5D                | 4                  |

| ACE # 3 | 3              | P3                  | 4D                | 5                  |

Pl is the right-most connector with the board-oriented connectors facing you. P2 is the connector immediately left of Pl and P3 is to the left of P2.

The pins on the DB25-S type connectors P1-P3 are configured as follows (as viewed from the rear of the computer):

The pins have been arranged to conform as closely as possible to the IEEE RS-232 communications equipment standards for data terminal equipment. The following is a pinout guide for the DB-25 connector.

Table 6-2: ACE Serial Connectors

|              | Connector Pin | Definition ACE            | Mnemonic |

|--------------|---------------|---------------------------|----------|

| Output       | 3             | Transmit data             | SOUT     |

| From         | 4             | Request to Send           | RTS      |

| WB I/O       | 20            | Data Terminal<br>Ready    | DTR      |

| Input        | 2             | Receive data              | SIN      |

| To<br>WB I/O | 5             | Received Signal<br>Detect | RCSD     |

| WB 1/0       | 6             | Data Set Ready            | DSR      |

|              | 8             | Clear to Send             | CTS      |

|              | 1             | (chassis ground)          |          |

|              | 7             | (signal ground)           |          |

#### 7. PROGRAMMING THE 8250

Any 8250 device on the WB I/O can be accessed if its I/O group is currently selected. Once a 1, 2 or 3 has been output to GROUP SELECT port BASE+7, ACE device number 1, 2 or 3 can be accessed. Each ACE contains internal 8-bit registers which occupy the first seven I/O ports of the WB I/O space, or ports BASE to BASE+6. The ACE registers accessed after the correct group has been selected are dependent on the status of the Most Significant Bit (MSB) of the line control register (BASE+3). If this bit is high, BASE and BASE+1 access the divisor latch low byte and high byte, respectively. Since the ACE has programmed baud rates, these registers must be programmed for the desired baud rate (refer to the data sheet on the 8250 for the common divisor latch If the MSB of the line control register is low, values). register at BASE becomes the RECEIVE buffer or TRANSMIT buffer, depending on whether it is a read or write operation. The register at BASE+1 becomes the Interrupt Enable register. The following is a summary of the 8250 registers:

Table 7-1: Registers for the 8250

| I/O Port | Operation  | Condition<br>of DLAB | Register                  |

|----------|------------|----------------------|---------------------------|

| BASE     | Write      | Ø                    | Transmitter buffer        |

| BASE     | Read       | Ø                    | Receiver buffer           |

| BASE     | Write      | 1                    | Divisor latch - low byte  |

| BASE+1   | Read/Write | Ø                    | Interrupt Enable register |

| BASE+1   | Write      | 1                    | Divisor latch - high byte |

| BASE+2   | Read       | X                    | Interrupt ID register     |

| BASE+3   | Read/Write | x                    | Line Control register     |

| BASE+4   | Read/Write | х                    | Modem Control register    |

| BASE+5   | Read/Write | x                    | Line Status register      |

| BASE+6   | Read/Write | Х                    | Modem Status register     |

# X= Not important

#### 7.1. Baud Rate

The 8250s on the WB I/O have been hard wired so the baud rate for data coming in is the same as for data going out. The crystal used to provide the reference frequency for the three ACE devices on the WB I/O is 1.8432 Mhz. The data sheets give a broad sample of the divisors which must go into the divisor latch in order to generate the most common baud rates, and generally any baud rate may be generated from DC to 56.000 baud (a zero in the divisor latch inhibits all data transmission). The formula for determining the divisor constant to produce a given baud rate is:

# DIVISOR = 1.8432 M/ (BAUD RATE X 16)

Although in most applications the user will simply look up the baud rate divisor in the data sheet table, there are instances when odd ball baud rates may be useful. For example, an ACE is being used to generate interrupts at timed intervals based on the Transmitter Holding Register Empty Interrupt (see Serial Device Interrupts).

The following is a list of the divisor latch constants for the standard baud rates (values are in decimal):

Table 7-2: Divisor Latch Constants for Standard Baud Rates

| Contents | Baud rate |

|----------|-----------|

| 23Ø4     | 5Ø        |

| 1536     | 75        |

| 1047     | 110       |

| 857      | 134.5     |

| 768      | 15Ø       |

| 384      | 3ØØ       |

| 192      | 6ØØ       |

| 96       | 1200      |

| 64       | 1800      |

| 58       | 2000      |

| 48       | 2400      |

| 32       | 3600      |

| 24       | 4800      |

| 16       | 72ØØ      |

| 12       | 96ØØ      |

| 6        | 19200     |

| 3        | 384ØØ     |

| 2        | 56ØØØ     |

#### 7.2. Initialization

Though the reset pin (MR) of each 8250 is asserted during power ON or RESET, no assumptions should be made about the contents of any 8250 register unless that register has been initialized. Keep in mind that an on-board ACE cannot be accessed, much less initialized, unless its I/O group is selected. Furthermore, the Line Control, Modem Control, Interrupt Enable and Divisor Registers are normally initialized before any data can be transferred to or from an 8250.

The following three software routines are brief samples of how a WB I/O ACE device could be driven in a CP/M\* type environment. All these routines adhere to CP/M\* I/O protocol. The INIT routine sets up ACE # 1 to run at 9600 baud with an eight bit word, no parity and two stop bits. The Interrupt Enable Register is set to generate no interrupts, and the Modem Control Register is ignored. This initialization would be appropriate for most RS-232 CRT terminals in a non-interrupt driven environment. Assume that the WB I/O I/O has been set to begin at 48H. The cluster of assembler directives (equ's) at the beginning of these routines establish constants which hold for all three specimen routines. The comments included with these routines may be used as a general flow analysis of ACE programming.

<sup>\*</sup>CP/M is a trademark of the Digital Research Corporation.

Table 7-3: Sample I/O Routines

```

groupl

equ

; code for first ACE (attached to J1)

base

48h

;base I/O address set by SW-7C

equ

dll

equ

base

; ACE baud rate divisor (lsb)

dlm

equ

base+1

; ACE baud rate divisor (msb)

ier

base+1

equ

; ACE interrupt enable register

lcr

equ

base+3

;ACE line control register

lsr

equ

base+5

;ACE line status register

rbr

equ

base

;ACE receiver buffer register

thr

base

equ

; ACE transmitter holding register

dlab

8Øh

equ

;divisor latch access bit

thre

2Øh

equ

; line status register THRE bit

dr

1

equ

; line status register DR bit

baudl

12

equ

;divisor latch low byte-- 9600 baud

baudh

Ø

equ

;divisor latch high byte-- 9600 baud

wlsØ

1

equ

;word length select bit 0-- 8 bit word

wlsl

2

equ

;word length select bit 1-- 8 bit word

4

stb

equ

;stop bit count-- 2 stop bits

imask

equ

Ø

;interrupt mask-- disable all

```

```

;The following routine initializes the ACE as described above

init:

mvi

a, groupl ; set up desired I/O group

out

grpctl

;select first serial device

; next set up format and set dlab

mvi

a,dlab+wlsØ+wlsl+stb

out

; base reg is now lsb baud rate req

mvi

a, baudl ; low byte of baud rate constant

out

; into low baud rate register

mvi

a, baudh ; high byte of baud rate constant

out

; into high baud rate register

; set up format and clear dlab

mvi

a,wlØ+wll+stb

out

lcr

; into line control register

xra

а

;zero register a

lsr

; clear data available flag in line status

out

a, imask ; interrupt mask set up

mvi

out

ier

;base+l now interrupt mask- not baud

ret

; end of initialization routine

```

#### Table 7-3 Cont.

```

;The following routine will return in the accumulator any new

;character typed to ACE # 1

conin:

mvi

a,groupl

out

; put a 1 into WB I/O group select port

grpctl

; make sure dlab is cleared

mvi

a, wls0+wlsl+stb

out

lcr

; make base port the ACE data register

coninl: in

lsr

; get line status register

ani

dr

; any new data from terminal?

jΖ

coninl

; if no then keep waiting

in

;get data

rbr

7fh

ani

;strip off bit 7 of input character

ret

; return with data in accumulator

;

;The following routine will output the character in Register C

;to ACE # 1

conout:

mvi

a, groupl

out

; put a 1 into WB I/O GROUP SELECT port

grpctl

make sure dlab is low

mvi

a, wlsØ+wlsl+stb

out

lcr

; make base port the ACE data register

conoutl: in

lsr

; get line status

ani

; is ACE ready to transmit?

thre

jΖ

conoutl; if not then keep waiting

;transfer data from reg c to reg a

mov

a,c

out

thr

;output character typed from terminal

ret

;return to calling program

;

;The following routine will return an FF in the Register A if ACE

;device # 1 has received a new character (i.e., DR is set in the

; ACE line status register). Otherwise, return a \emptyset.

status:

mvi

a, groupl

out

; put a 1 into WB I/O GROUP SELECT port

grpctl

in

lsr

; get line status

ani

dr

; check DR bit

;return if reg a is zero-- no character

rz

mvi

a, Offh ; ff into reg a since character is ready

ret

```

In the above examples, it should be noted that the GROUP SELECT port is re-initialized at the beginning of every routine. This is done to insure against inadvertently sending serial I/O instructions to the clock, parallel ports or interrupt controller of the WB I/O. Further note that before accessing the ACE data register, the format word is sent again to the Line Control Register. This is done so that port BASE of GROUP I will be interpreted as a data port rather than as a divisor port. This guards against a situation such as losing access to the console device due to a careless reading of the divisor latch (from a monitor or front panel, for example) without subsequently clearing DLAB.

#### 7.3. Serial Device Interrupts

The three 8250 ACE devices on the WB I/O each have a dedicated interrupt request line on the 8259 PIC. The chart below describes the PIC interrupt level assigned to each ACE:

Table 7-4: ACE Interrupt Assignments - 8259 PIC

| Serial | Device | PIC Interrupt<br>Request Line |

|--------|--------|-------------------------------|

| ACE    | # 1    | IR3                           |

| ACE    | # 2    | IR4                           |

| ACE    | # 3    | IR5                           |

#### 7.4. ACE Interrupt Programming

As explained in the data sheet on the 8250, each ACE device can be programmed to generate an interrupt on any of four general conditions. These conditions are, in order of descending priority: Receiver Line Status, Received Data Available, Transmitter Holding Register Empty, and Modem Status. The Received Data Available and the Transmitter Holding Register Empty interrupts can be identified directly from the Interrupt ID Register of the source ACE.

The remaining two interrupts must use the Interrupt ID Register to point to either the Receiver Line Status Register or the Modem Status Register. These two registers each have four interrupt flags which can be read to identify the source of an ACE-generated interrupt. (The third interrupt of the Modem Status Register - The Trailing Edge of Ring Indicator, or TERI - is not usefully supported by the WB I/O, since the Ring Indicator line of each ACE is tied to +5V.) Because the 8250 prioritizes its interrupts, the Interrupt ID Register will 'freeze' the highest priority interrupt pending by ignoring all further interrupts until the previous interrupt has been serviced. See the data sheets for further information on the 8250.

When using the 8250's ACE devices on the WB I/O to generate interrupts, it is advisable to set the 8259-A PIC to operate in level-mode, rather than edge-mode. In edge-mode, it is possible under certain circumstances for an ACE-generated interrupt to be 'lost'- that is, to go unrecognized. The 8250 generates one edge for an interrupt and all interrupts which occur during the time when the first interrupt is active will not generate additional edges. In this situation, the interrupt line of the 8250 remains low until all interrupts have been acknowledged, but the 8259 PIC in edge-triggered mode has seen no additional edges to indicate the presence of further interrupts.

#### 8. THE PARALLEL DAISY-WHEEL PRINTER PORT

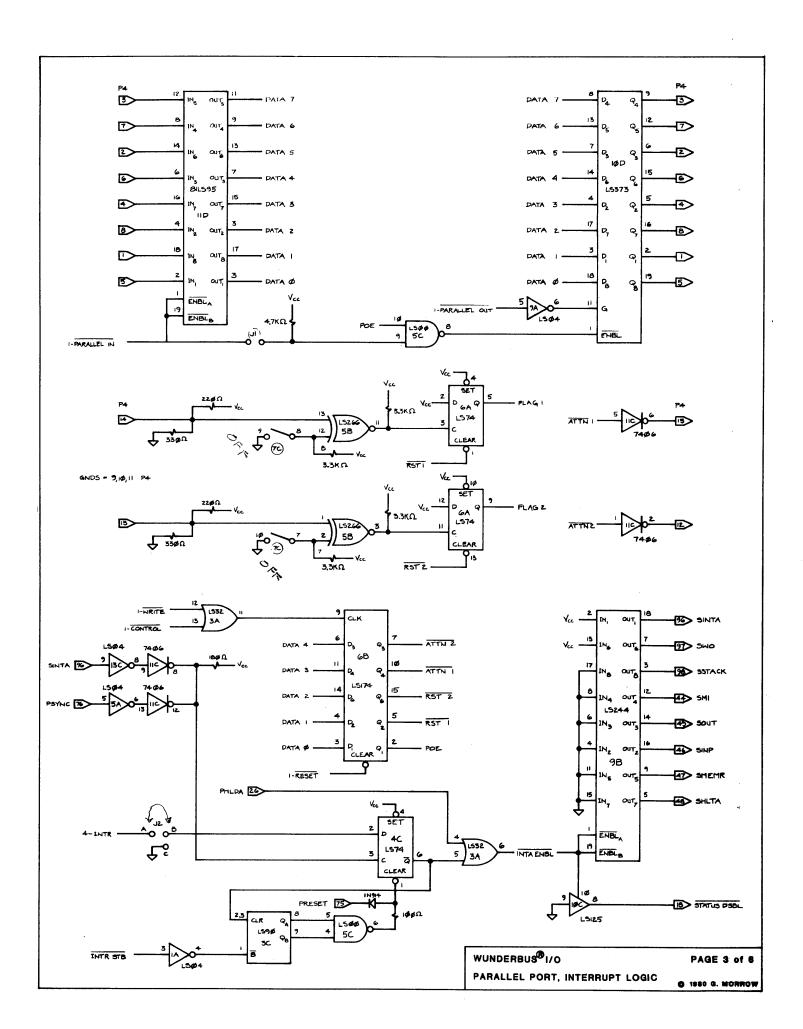

SELECT

The WB I/O contains parallel I/O ports configured to accommodate a standard Diablo-type daisy-wheel R/O printer. These ports are brought out to the 50-pin ribbon cable connector at P5 (board location 8E - llE) for easy attachment. The pin assignments of P5 correspond exactly to those of an internal Diablo 50 conductor flat cable connector, so simply tying the Diablo to the WB I/O via a ribbon cable with female sockets at either end is the only hardware requirement for interfacing the two devices.

The daisy-wheel interface standard requires 12 bits of data information and four strobe lines which determine the meaning of the data lines. These four strobes are:

#### Table 8-1: Printer Strobe Lines

| RESTORE -               | Send the print head to the 'home' position (position assumed when the printer is powered up).                    |

|-------------------------|------------------------------------------------------------------------------------------------------------------|

| PRINT WHEEL -<br>STROBE | Indicates 12 bits of data on data lines contain characters to be printed and the strike intensity of the hammer. |

| CARRIAGE -<br>STROBE    | Indicates that data lines contain the appropriate number of steps and direction the print head is to be moved.   |

| PAPER FEED -            | Indicates that data lines contain valid number representing amount of paper to advance or retract.               |

| RIBBON -                | Lifts the ribbon cartridge in preparation to print a character.                                                  |

- Low to select the printer.

The last two lines are additional daisy-wheel printer control They are accessed through GROUP Ø BASE+2 output port. Bit-6 generates the ribbon lift signal and bit-7 is an inverted version of the select signal. All software must account for this inversion for correct selection. (For more information on printer standards for Diablo-type systems, see referenced manual.)

latched output ports (plus an extra latched output bit) one transparent input port are used to communicate with the daisy-wheel printer. These ports can be used with almost parallel device (e.g., a Centronics-style printer or a keyboard) provided that the I/O lines are properly routed from the WB I/O connector at P5 to the target device. This additional cabling burden is standard in parallel I/O interfacing, and so should not be considered as a major disadvantage by those using the DAISY port with a non-Diablo parallel device.

The WB I/O daisy-wheel printer port occupies I/O ports BASE BASE+1 plus a part of BASE+2 - all within I/O GROUP Ø. A single input line (BASE+1 bit-5, or the Print Wheel Ready line when interfacing with a daisy-wheel printer) is, after going to the DAISY port, inverted, then brought to IRQ 6 of the 8259-A controller to generate an interrupt whenever it goes interrupt to a low logic state. The eight input lines brought to daisywheel printer port BASE are also pulled up to +5V through Ohms (nominal), and may be used with open-collector devices.

These eight input lines are inverted by an input buffer; if left unconnected, appear to software as a high.

signal returning from the daisy-wheel printer indicates whether it can accept a new command from the WB I/O. The lines are defined as:

#### Table 8-2: Printer Line Commands

address.

| PRINTER  | READY | -            | Power is ON and printer is ready to accept commands.                                                                                          |

|----------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CHECK    |       | <del>-</del> | Fault condition indicating either a software error (e.g. sending the print head too far in one direction) or hardware failure in the printer. |

| P.W. REA | DŸ    |              | Print wheel can accept a new character                                                                                                        |

#### Table 8-2 Cont.

CARRIAGE READY - Carriage is ready to be repositioned.

P.F. READY - Platen motor ready to advance or

retract the paper.

COVER OPEN - Case cover was removed.

OUT OF PAPER - Printer has run out of paper.

RIBBON OUT - A print ribbon cartridge has not

been inserted or has run out.

Connector P5, line 48, enables all daisy-wheel printer port output drivers. If this line is not tied to nominal +5 volts (if it is grounded or allowed to float) the DAISY port output lines controlled by I/O ports BASE, BASE+1 and BASE+2, remain at a high impedance state regardless of any software commands. (Note that some printers such as C. Itoh do not supply this level and are non-standard Diablo interfaces.) In the event you have chosen such a printer and are not able to jumper pin-48 of the daisy-wheel printer connector to +5 volts, you may lift 4 of chip 10C and tie it to pin 7 of 10C using a short piece of 30 gauge insulated wire.

WARNING: In no way does Morrow Designs support this modification or take responsibility for products which have been modified. This solution is provided here in the unlikely event you have purchased a non-standard daisy-wheel printer and have no way in which to modify the printer itself. It should be considered a temporary solution.

The parallel ports have no special facility for generating a strobe on output or latching a strobe on input. All data lines operate as levels, so strobes must be generated in software.

The following page depicts the parallel lines available on the WB I/O, including the I/O port and bit number controlling each line and the function assigned to each line on a standard parallel Diablo-type interface. Remember, these functions have no inherent meaning to the WB I/O; it only sees so many latches. Do not preclude interfacing the WB I/O with parallel devices other than daisy-wheel printers.

Table 8-3: Daisy-Wheel Printer Signals and I/O Map

I/O Group Ø

|        | I/O<br>Port | Data<br>Bit                                        | WB I/O and<br>Diablo Pin #                   | Diablo Function                                                                                                                                                                                   |

|--------|-------------|----------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input  | BASE*       | Ø<br>1<br>2<br>3<br>4<br>5<br>6<br>7               | 4<br>3<br>5<br>34<br>26<br>27 **<br>12<br>28 | End of Ribbon (-)<br>  Paper Out (-)<br>  Cover Open (-)<br>  Paper Feed Ready (-)<br>  Carriage Ready (-)<br>  Print Wheel Ready (-)<br>  Check (-)<br>  Printer Ready (-)                       |

| Output | BASE        | Ø  <br>1  <br>2  <br>3  <br>4  <br>5  <br>6  <br>7 | 46<br>1<br>9<br>10<br>15<br>17<br>21         | Data Bit 9 (256) (-)     Data Bit 10 (512) (-)     Data Bit 11 (1024) (-)     Data Bit 12 (2048) (-)     Paper Feed Strobe (-)     Carriage Strobe (-)     Print Wheel Strobe (-)     Restore (-) |

| Output | BASE+1      | Ø   1   2   3   4   5   6   7   1                  | 37<br>36<br>39<br>33<br>40<br>42<br>43       | Data Bit 1 (1) (-) Data Bit 2 (2) (-) Data Bit 3 (4) (-) Data Bit 4 (8) (-) Data Bit 5 (16) (-) Data Bit 6 (32) (-) Data Bit 7 (64) (-) Data Bit 8 (128) (-)                                      |

| Output | BASE+2      | 6  <br>7                                           | 23<br>24                                     | Ribbon Lift (-)<br>Select (-)                                                                                                                                                                     |

<sup>\*</sup>These eight input lines are pulled up to +5 volts by 180 Ohms and inverted.

The following lines on WB I/O connector P5 are tied to ground as described by Diablo interface standards:

2, 8, 11, 14, 18, 20, 22, 25, 30, 31, 32, 35, 38, 41, 44, 47.

(Line 24, defined by Diablo as Select (-), is also grounded.)

Unimplemented (left floating) are lines 6, 7, 29, and 50.

<sup>\*\*</sup>In addition to being associated with bit-6 of the input port BASE, the Diablo Print Wheel Ready line (pin-27 of P5) is connected through an inverter to Interrupt Request line 6 (pin-24) of the 8259-A PIC. Thus, this line may be used to generate an interrupt whenever any external device brings it low (e.g., when the print wheel is ready).

Table 8-4: Printer Port P5 - Connector Pinouts

Top View

Back

49 47 45 43 41 ... 9 7 5 3 1

Right

Left

50 48 46 44 42 ... 10 8 6 4 2

Front

#### 8.1. Programming the Daisy-Wheel Printer Port

As with all I/O devices on the WB I/O, the user must be careful when accessing the daisy-wheel printer port to initialize the correct I/O group - in this case, GROUP Ø. Once the proper I/O group has been selected, all data output from the CPU to the parallel ports will be latched (if P5, pin-48 is at a high level) or ignored (if P5, pin-48 is grounded or allowed to float). Latched means the data output to a parallel port appears on the appropriate pins on the P5 connector, and remains there until either different data is output to the port in question or until pin-48 is floated or grounded. When pin-48 is grounded or allowed to float, all 17 parallel output pins of connector P5 enter a high impedance state.

The eight input lines from the daisy-wheel printer port are available to the CPU by reading BASE+Ø (48h in standard configuration) with GROUP Ø selected. When an input instruction is directed at daisy-wheel printer port Ø, the CPU reads whatever data is on the appropriate lines of connector P5 at the time the instruction is executed. There is no provision for latching the daisy-wheel printer port input data because this data is buffered only. The input daisy-wheel printer port/pin assignments are listed in the tables beginning on page 27.

The WB I/O daisy-wheel printer port inverts its input lines but does not invert its output lines. Daisy-wheel printers use negative logic: a low signal is taken as active. To activate any output line when talking to a daisy-wheel printer, the software must put the line low. Input lines from a daisy-wheel printer, on the other hand, are inverted in hardware, and so will appear to software to be active high.

# 8.2. Generating an Output Strobe

Generating an output strobe off any of the parallel output ports on the WB I/O requires the use of a software mask. This means the line to be strobed must be output (at most) three times in succession, changing state each time, while the data lines associated with the same port be allowed to remain unchanged. For example, to output a strobe going high-low-high on bit-6 of port BASE without changing the other seven bits being output from that port, the following routine could be used:

| mvi | a,data | original data into register A  |      |

|-----|--------|--------------------------------|------|

| ori | 40h    | ;preserve data but bring bit-6 | high |

| out | base   | ;output data with bit-6 high   | -    |

| ani | Øbfh   | ;preserve data but bring bit 6 | low  |

| out | base   | output data with bit-6 low     |      |

| ori | 40h    | ;preserve data but bring bit 6 | high |

| out | base   | output data with bit-6 high;   | _    |

NOTE: GROUP  $\emptyset$  port BASE+2 is shared with another device on the WB I/O-- the real time clock. Be careful when outputting to this port.

# 8.3. The Daisy-Wheel Printer Port and Interrupts

The Print Wheel Ready status line of the daisy-wheel printer port (P5 connector, pin-27, BASE input port bit-5) is brought through an inverter to Interrupt Request line 6 of the 8259-A PIC. The PIC can generate an interrupt whenever this line goes to an active (i.e. logic low) state. To take full advantage of this interrupt option, the printer driver software should be written so that the Print Wheel Strobe (P5, pin-21, BASE output port bit-6) is not activated until all carriage positioning commands have first been sent to the printer. Print-after-space will execute significantly faster than space-after-print. When the Print Wheel Ready line goes active the printer should be able to accept another motion-then-print sequence.

A sample Diablo printer driver, including source code for the WB I/O, can be obtained from Morrow Designs.

### 9. THE AUXILIARY PARALLEL PORT

Besides the daisy-wheel printer port, the WB I/O contains an eight-bit, bi-directional parallel port with handshaking. The port is available at the DB15-S type connector P4 (location 12 and 13E) on the PC board.